Page 1

Cat. No. W451-E1-03

SYSMAC CP Series

CP1H-X40D@-@, CP1H-XA40D@-@,

CP1H-Y20DT-D

CP1L-L14D@-@, CP1L-L20D@-@,

CP1L-M30D@-@, CP1L-M40D@-@

CP1H/CP1L CPU Unit

PROGRAMMING MANUAL

Page 2

SYSMAC CP Series

CP1H-X40D@-@, CP1H-XA40D@-@,

CP1H-Y20DT-D

CP1H CPU Units

CP1L-L14D@-@, CP1L-L20D@-@,

CP1L-M30D@-@, CP1L-M40D@-@

CP1L CPU Units

Programming Manual

Revised May 2007

Page 3

iv

Page 4

Notice:

r

f

OMRON products are manufactured for use according to proper procedures

by a qualified operator and only for the purposes described in this manual.

The following conventions are used to indicate and classify precautions in this

manual. Always heed the information provided with them. Failure to heed precautions can result in injury to people or damage to property.

!DANGER Indicates an imminently hazardous situation which, if not avoided, will result in death or

serious injury. Additionally, there may be severe property damage.

!WARNING Indicates a potentially hazardous situation which, if not avoided, could result in death or

serious injury. Additionally, there may be severe property damage.

!Caution Indicates a potentially hazardous situation which, if not avoided, may result in minor or

moderate injury, or property damage.

OMRON Product References

All OMRON products are capitalized in this manual. The word “Unit” is also

capitalized when it refers to an OMRON product, regardless of whether or not

it appears in the proper name of the product.

The abbreviation “Ch,” which appears in some displays and on some OMRON

products, often means “word” and is abbreviated “Wd” in documentation in

this sense.

The abbreviation “PLC” means Programmable Controller. “PC” is used, however, in some CX-Programmer displays to mean Programmable Controller.

Visual Aids

OMRON, 2005

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form, o

by any means, mechanical, electronic, photocopying, recording, or otherwise, without the prior written permission o

OMRON.

No patent liability is assumed with respect to the use of the information contained herein. Moreover, because OMRON is constantly striving to improve its high-quality products, the information contained in this manual is subject to change without

notice. Every precaution has been taken in the preparation of this manual. Nevertheless, OMRON assumes no responsibility

for errors or omissions. Neither is any liability assumed for damages resulting from the use of the information contained in

this publication.

The following headings appear in the left column of the manual to help you

locate different types of information.

Note Indicates information of particular interest for efficient and convenient opera-

tion of the product.

1,2,3... 1. Indicates lists of one sort or another, such as procedures, checklists, etc.

v

Page 5

Unit Versions of CP-series CPU Units

Unit Versions A “unit version” has been introduced to manage CPU Units in the CP Series

according to differences in functionality accompanying Unit upgrades.

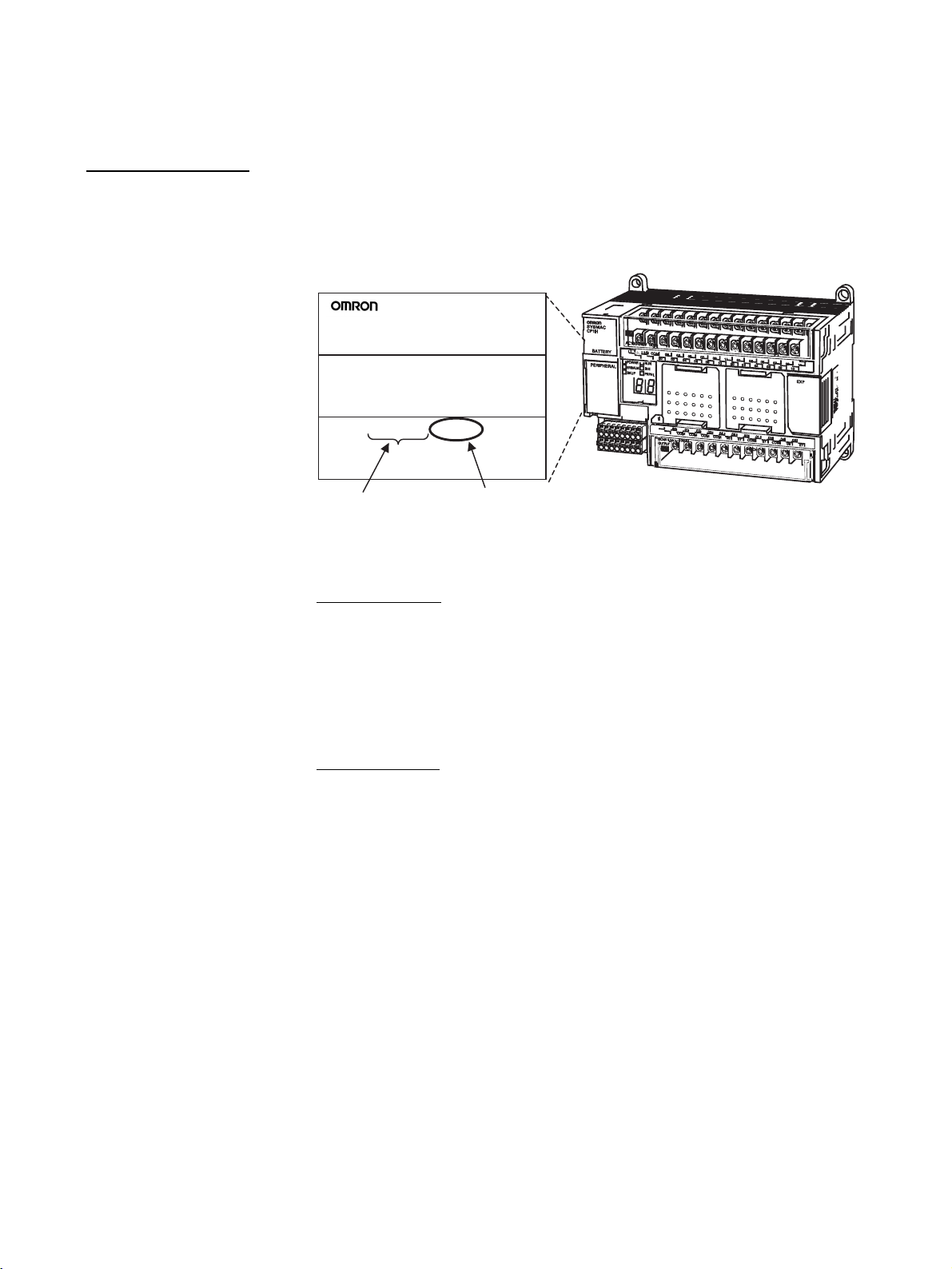

Notation of Unit Versions

on Products

Confirming Unit Versions

with Support Software

The unit version is given to the right of the lot number on the nameplate of the

products for which unit versions are being managed, as shown below.

Product nameplate

CP1H-XA40DR-A

CPU UNIT

Lot No. 28705 0000 Ver.1.0

OMRON Corporation MADE IN JAPAN

Lot No.

The methods used to confirm the unit version for the CP-series CP1H and

CP1L CPU Units are somewhat different.

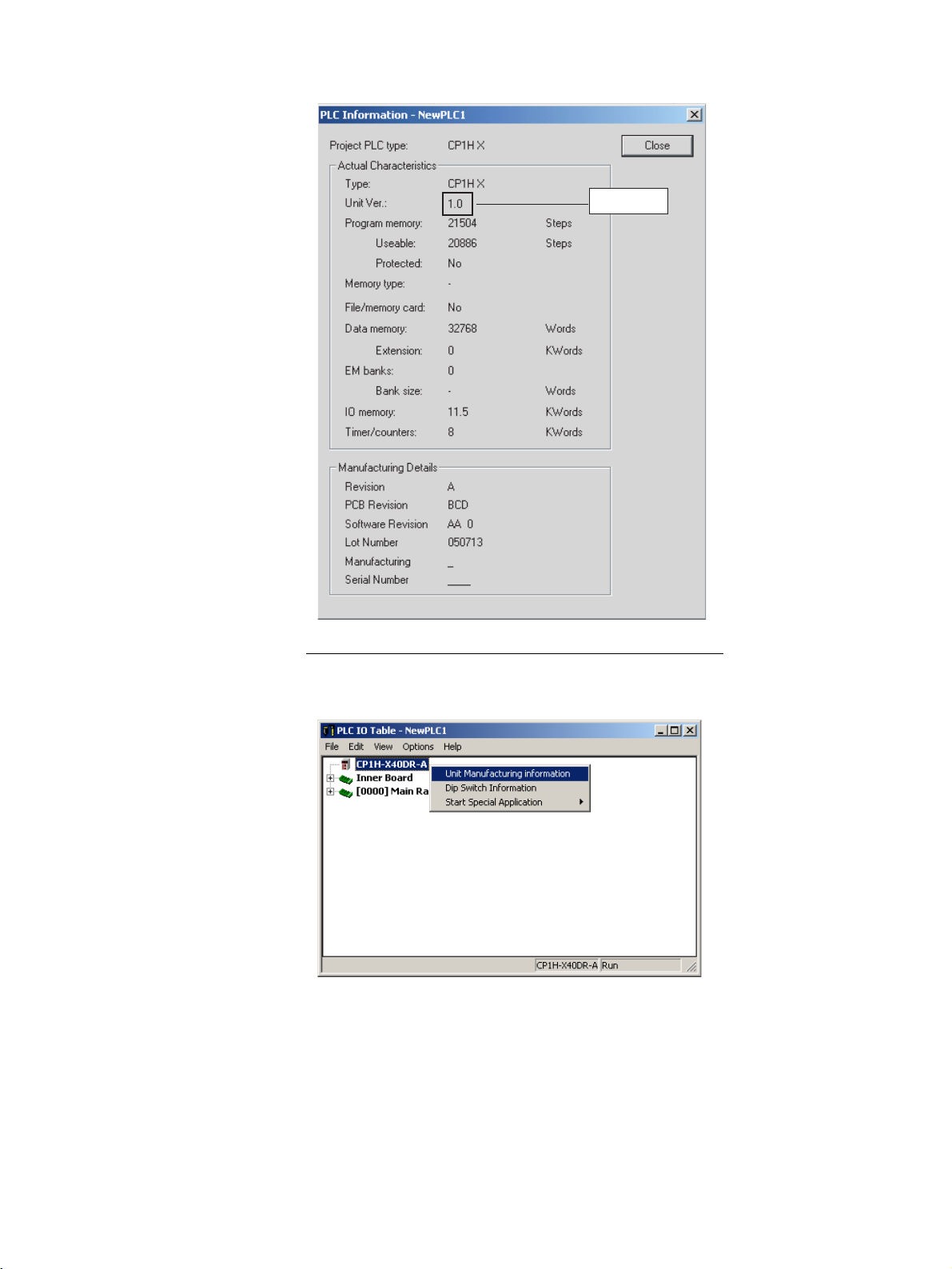

CP1H CPU Units

CX-Programmer version 6.1 or higher can be used to confirm the unit version

using one of the following two methods. (See note.)

• Using the PLC Information

• Using the Unit Manufacturing Information

Unit version

(Example for Unit version 1.0)

CP-series CPU Unit

Note CX-Programmer versions lower than version 6.1 cannot be used to confirm

unit versions for CP1L CPU Units.

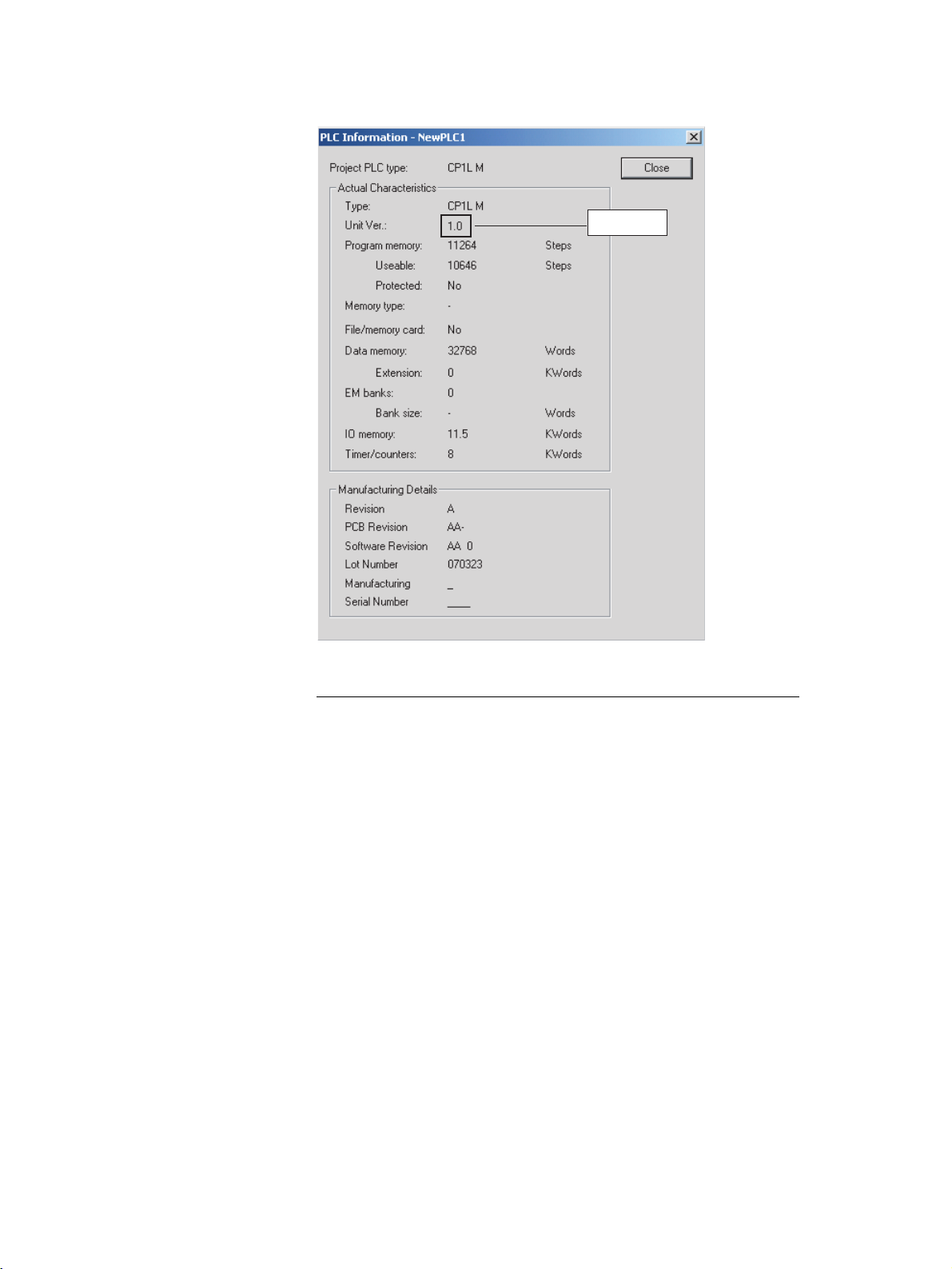

CP1L CPU Units

CX-Programmer version 7.1 or higher can be used to confirm the unit version

using the PLC Information. (See note.) The Unit Manufacturing Informa-

tion cannot be used.

Note CX-Programmer versions lower than version 7.1 cannot be used to confirm

unit versions for CP1L CPU Units.

vi

Page 6

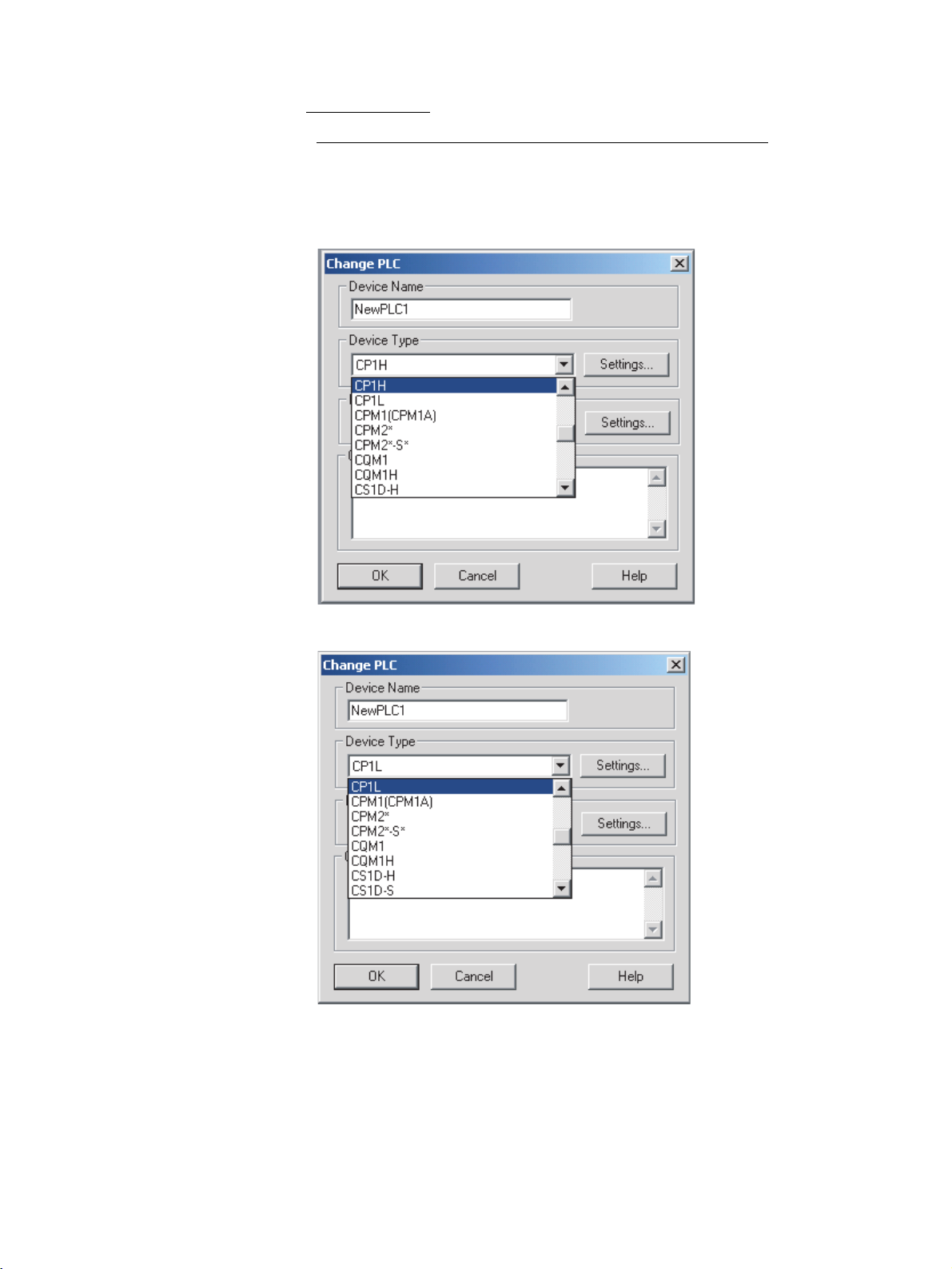

■ PLC Information

Procedure When the Device Type and CPU Type Are Known

1,2,3... 1. If you know the device type and CPU type, select them in the Change PLC

Dialog Box, go online, and select PLC - Edit - Information from the

menus. The following Change PLC Dialog Box will be displayed.

Example for CP1H

Example for CP1L

vii

Page 7

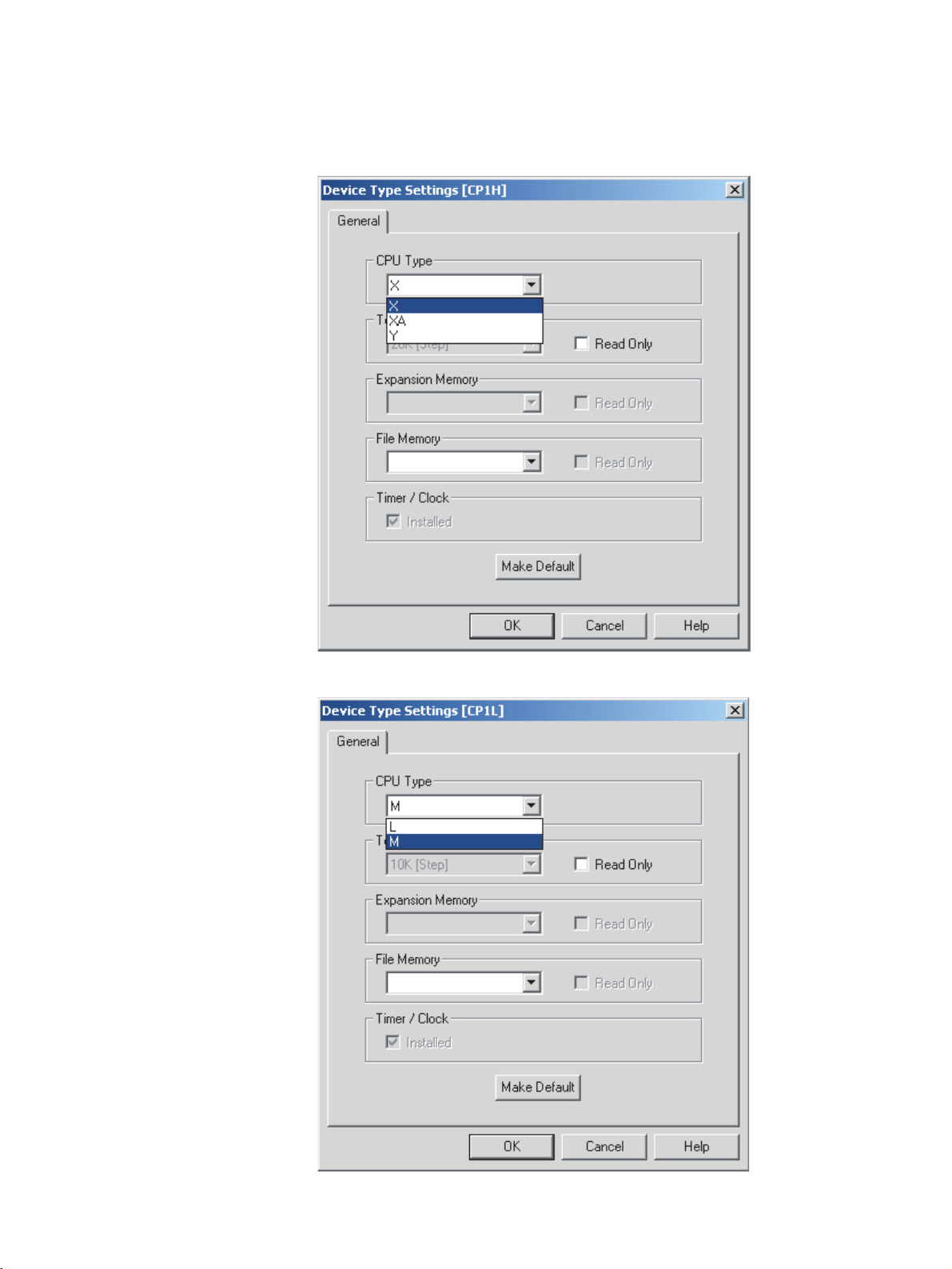

2. Click the Settings Button and, when the Device Type Settings Dialog Box

is displayed, select the CPU type.

Example for CP1H

Example for CP1L

viii

Page 8

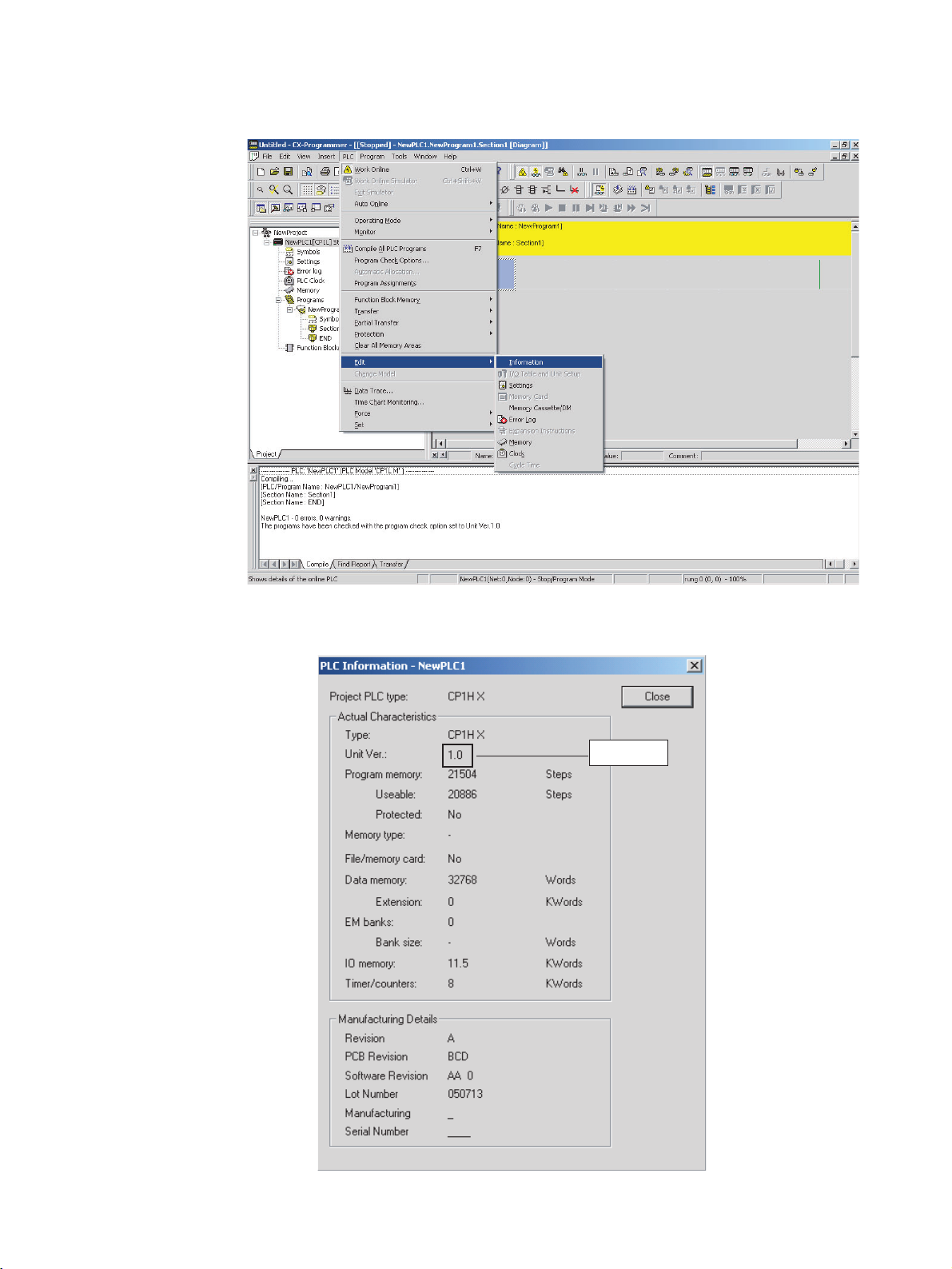

3. Go online and select PLC - Edit - Information

The PLC Information Dialog Box will be displayed.

Example for the CP1H

▲

Unit version

ix

Page 9

Example for the CP1L

▲

Unit version

Use the above display to confirm the unit version of the CPU Unit.

Procedure When the Device Type and CPU Type Are Not Known

This procedure is possible only when connected directly to the CPU Unit with

a serial connection.

If you don't know the device type and CPU type but are connected directly to

the CPU Unit on a serial line, select PLC - Auto Online to go online, and then

select PLC - Edit - Information from the menus.

The PLC Information Dialog Box will be displayed and can be used to confirm

the unit version of the CPU Unit.

x

Page 10

▲

Unit version

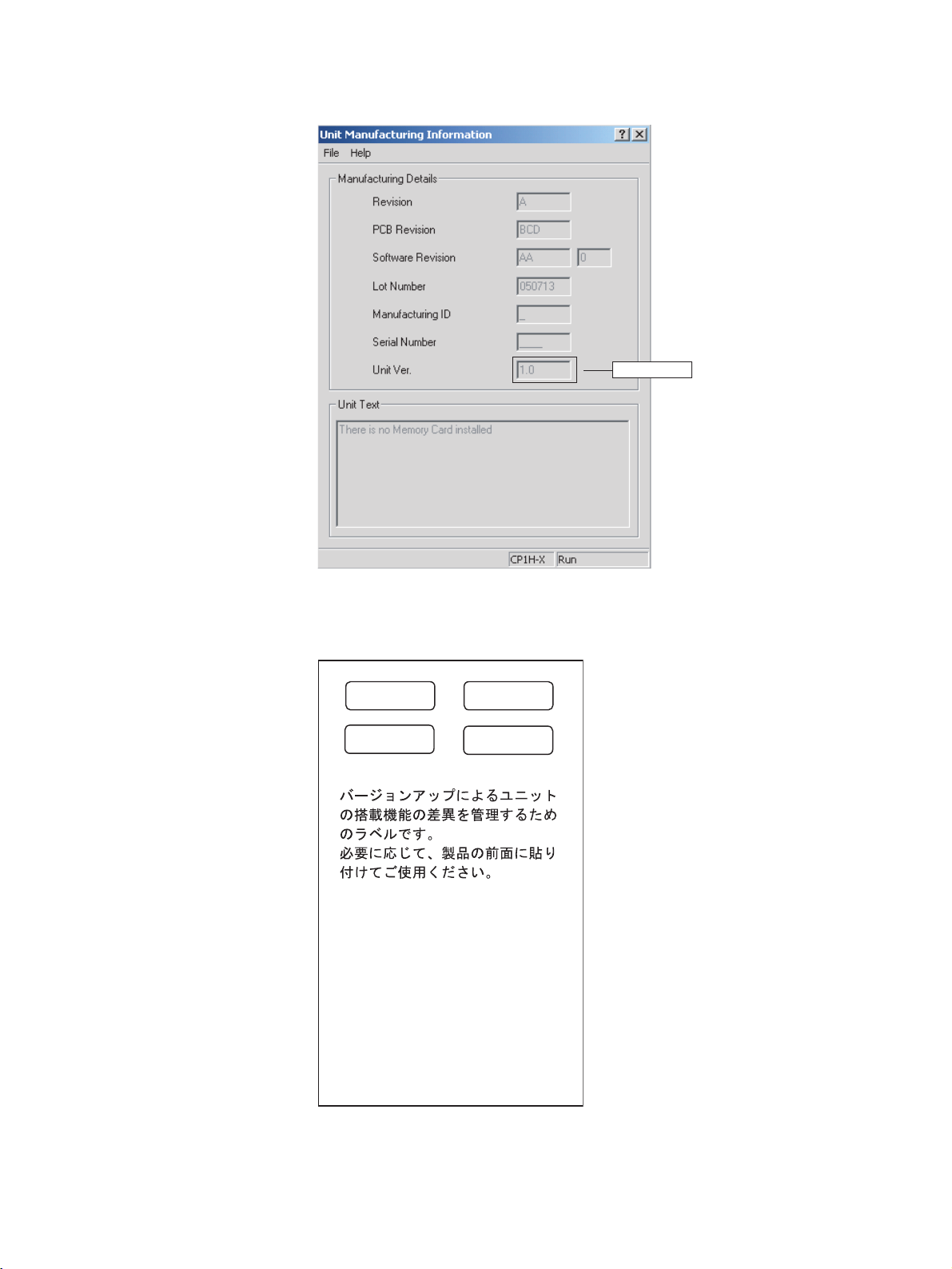

■ Unit Manufacturing Information (CP1H CPU Units Only)

1,2,3... 1. In the IO Table Window, right-click and select Unit Manufacturing infor-

mation - CPU Unit.

xi

Page 11

2. The following Unit Manufacturing information Dialog Box will be displayed.

Unit version

▲

Using the Unit Version

Labels

Use the above display to confirm the unit version of the CPU Unit connected

online.

The following unit version labels are provided with the CPU Unit.

Ver.

Ver.

Ver.

1.0

Ver.

1.0

These Labels can be

used to manage

differences in the

available functions

among the Units.

Place the appropriate

label on the front of

the Unit to show what

Unit version is actually

being used.

xii

These labels can be attached to the front of previous CPU Units to differentiate between CPU Units of different unit versions.

Page 12

TABLE OF CONTENTS

PRECAUTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xxiii

1 Intended Audience. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xxiv

2 General Precautions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xxiv

3 Safety Precautions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xxiv

4 Operating Environment Precautions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xxvi

5 Application Precautions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .xxvii

6 Conformance to EC Directives . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xxx

SECTION 1

Programming Concepts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

1-1 Programming Concepts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2

1-2 Precautions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

1-3 Checking Programs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

1-4 Introducing Function Blocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

SECTION 2

Tasks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

2-1 Programming with Tasks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .50

2-2 Using Tasks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

2-3 Interrupt Tasks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

2-4 CX-Programmer Operations for Tasks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

SECTION 3

Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

3-1 Notation and Layout of Instruction Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

3-2 Sequence Input Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .89

3-3 Sequence Output Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

3-4 Sequence Control Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 132

3-5 Timer and Counter Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 168

3-6 Comparison Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 209

3-7 Data Movement Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 247

3-8 Data Shift Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 274

3-9 Increment/Decrement Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 320

3-10 Symbol Math Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .336

3-11 Conversion Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 389

3-12 Logic Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 436

3-13 Special Math Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 451

3-14 Floating-point Math Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 472

3-15 Double-precision Floating-point Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 525

3-16 Table Data Processing Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 567

3-17 Data Control Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 615

xiii

Page 13

TABLE OF CONTENTS

3-18 Subroutines . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 668

3-19 Interrupt Control Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 692

3-20 High-speed Counter/Pulse Output Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 705

3-21 Step Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 751

3-22 Basic I/O Unit Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 769

3-23 Serial Communications Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 805

3-24 Network Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 844

3-25 Display Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 911

3-26 Clock Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 918

3-27 Debugging Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 932

3-28 Failure Diagnosis Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .936

3-29 Other Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 961

3-30 Block Programming Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 975

3-31 Text String Processing Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1008

3-32 Task Control Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1040

3-33 Model Conversion Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1047

SECTION 4

Instruction Execution Times and Number of Steps. . . . . . . 1065

4-1 Instruction Execution Times and Number of Steps. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1066

4-2 Function Block Instance Execution Time . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1088

Appendices

A Instruction Classifications by Function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1091

B List of Instructions by Function Code . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1099

C Alphabetical List of Instructions by Mnemonic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1115

Index. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1129

Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1139

xiv

Page 14

About this Manual:

This manual describes programming the CP-series Programmable Controllers (PLCs) and includes

the sections described below. The CP1H and CP1L are advanced package-type PLCs based on

OMRON’s advanced control technologies and vast experience in automated control.

Please read this manual carefully and be sure you understand the information provided before

attempting to install or operate a CP1H or CP1L PLC. Be sure to read the precautions provided in the

following section.

Definition of the CP Series

The CP Series is centered around the CP1H and CP1L CPU Units and is designed with the same

basic architecture as the CS and CJ Series. The Special I/O Units and CPU Bus Units of the CJ Series

can thus be used with the CP1H CPU Units. CJ-series Basic I/O Units, however, cannot be used.

Always use CPM1A Expansion Units or CPM1A Expansion I/O Units when expanding the I/O capacity

of CP1H or CP1L PLCs.

I/O words are allocated in the same way as the CPM1A/CPM2A PLCs, i.e., using fixed areas for inputs

and outputs.

CS/CJ/CP Series

CS Series

CS1-H CPU Units

CS1H-CPU@@H

CS1G-CPU@@H

CS1 CPU Units

CS1H-CPU@@ (-V1)

CS1G-CPU@@ (-V1)

CS1D CPU Units

CS1D CPU Units for

Duplex-CPU System

CS1D-CPU

CS1D CPU Units for

Single-CPU System

CS1D-CPU S

CS1D Process CPU Units

CS1D-CPU

CS-series Basic I/O Units

CS-series Special I/O Units

CS-series CPU Bus Units

CS-series Power Supply Units

Note: Products specifically for the CS1D

Series are required to use CS1D

CPU Units.

@@H

@@

@@P

CJ Series

CJ1-H CPU Units

CJ1H-CPU@@H

CJ1G-CPU@@H

CJ1G -CPU@@P

(Loop CPU Unit)

CJ1M CPU Unit

CJ1M-CPU@@

CJ1 CPU Unit

CJ1G-CPU@@

CJ-series Basic I/O Units

CJ-series Special I/O Units

CJ-series CPU Bus Units

CJ-series Power Supply Units

CP Series

CP1H CPU Units

CP1H-X@@@@-@

CP1H-XA@@@@-@

CP1H-Y@@@@-@

CP1L CPU Unit

CP1L-L14D@-@

CP1L-L20D@-@

CP1L-M30D@-@

CP1L-M40D@-@

CP-series Expansion I/O Units

CP-series Expansion Units

CPM1A Expansion I/O Units

CPM1A Expansion Units

CJ-series Special I/O Units (See note.)

CJ-series CPU Bus Units (See note.)

Note: Can be used with only a CP1H

CPU Unit.

xv

Page 15

Precautions provides general precautions for using the Programmable Controller and related devices.

Section 1 describes the basic concepts required to program the CP1H.

Section 2 describes the operation of tasks and how to use tasks in programming.

Section 3 describes each of the instructions that can be used in programming CP-series PLCs.

Instructions are described in order of function.

Section 4 lists the execution times and number of steps for all instructions supported by the CP1H

PLCs, and describes the execution times for function block instances.

The Appendices provide lists of the programming instructions in order of function and in order of function number.

xvi

Page 16

Related Manuals

The following manuals are used for the CP-series CPU Units. Refer to these manuals as required.

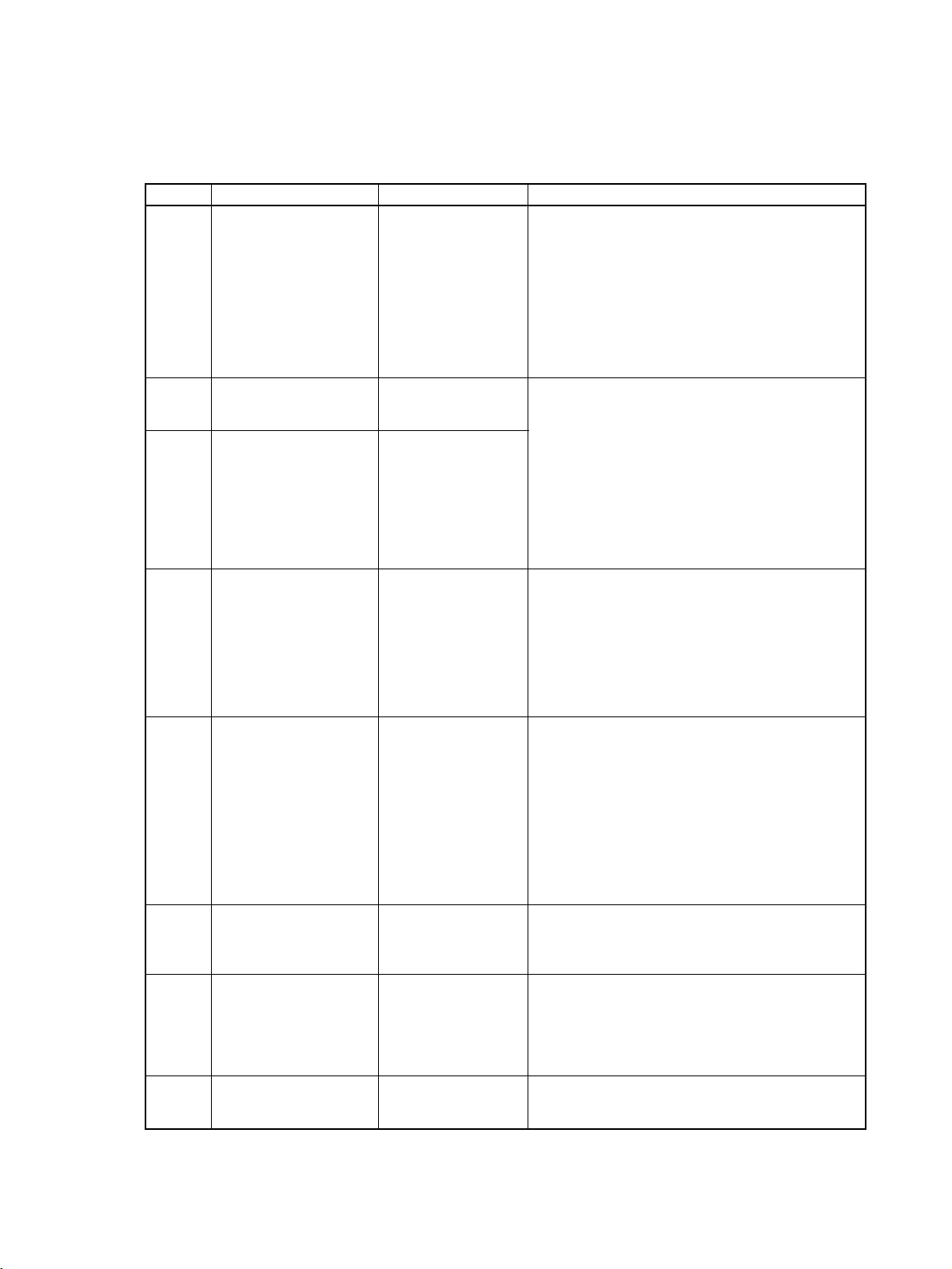

Cat. No. Model numbers Manual name Description

W451 CP1H-X40D@-@

CP1H-XA40D@-@

CP1H-Y20DT-D

CP1L-L14D@-@

CP1L-L20D@-@

CP1L-M30D@-@

CP1L-M40D@-@

W450 CP1H-X40D@-@

CP1H-XA40D@-@

CP1H-Y20DT-D

W462 CP1L-L14D@-@

CP1L-L20D@-@

CP1L-M30D@-@

CP1L-M40D@-@

W461 CP1L-L14D@-@

CP1L-L20D@-@

CP1L-M30D@-@

CP1L-M40D@-@

W342 CS1G/H-CPU@@H

CS1G/H-CPU@@-V1

CS1D-CPU@@H

CS1D-CPU@@S

CS1W-SCU21

CS1W-SCB21-V1/41-V1

CJ1G/H-CPU@@H

CJ1G-CPU@@P

CP1H-CPU@@

CJ1G-CPU@@

CJ1W-SCU21-V1/41-V1

W446 WS02-CXPC1-E-V70 SYSMAC CX-Pro-

W447 WS02-CXPC1-E-V70 SYSMAC CX-Pro-

W444 CXONE-AL@@C-E CX-One FA Inte-

SYSMAC CP Series

CP1H and CP1L CPU

Unit Programming

Manual

(This manual)

SYSMAC CP Series

CP1H CPU Unit

Operation Manual

SYSMAC CP Series

CP1L CPU Unit Operation Manual

SYSMAC CP Series

CP1L Introduction

Manual

SYSMAC CS/CJseries Communications Commands Reference Manual

grammer

Ver. 7.0 Operation

Manual

grammer Ver. 7.0

Operation Manual

Function Blocks

grated Tool Package

Setup Manual

Provides the following information on the CP Series:

• Programming instructions

• Programming methods

•Tasks

• File memory

• Functions

Use this manual together with the CP Series CP1H

CPU Units Operation Manual (W450) and CP

Series CP1L CPU Units Operation Manual (W462)

Provide the following information on the CP Series:

• Overview, design, installation, maintenance, and

other basic specifications

•Features

• System configuration

• Mounting and wiring

• I/O memory allocation

• Troubleshooting

Use this manual together with the CP1H Program-

mable Controllers Programming Manual (W451).

Provides basic setup information for CP1L PLCs,

including the following.

• Basic configuration and part names

• Mounting and wiring procedures

• Programming, program transfer, and debugging

with the CX-Programmer

• Application programming examples using the

CP1L

Describes commands addressed to CS-series, and

CJ-series CPU Units, including C-mode commands

and FINS commands.

Note This manual describes on commands

address to CPU Units regardless of the communications path. (CPU Unit serial ports,

Serial Communications Unit/Board ports, and

Communications Unit ports can be used.)

Refer to the relevant operation manuals for

information on commands addresses to Special I/O Units and CPU Bus Units.

Provides information on installing and operating the

CX-Programmer for all functions except for function

blocks.

Provides specifications and operating procedures

for function blocks. Function blocks can be used

with CX-Programmer Ver. 6.1 or higher and either a

CS1-H/CJ1-H CPU Unit with a unit version of 3.0 or

a CP1H CPU Unit. Refer to W446 for operating procedures for functions other than function blocks.

Provides an overview of the CX-One FA Integrated

Tool and installation procedures.

xvii

Page 17

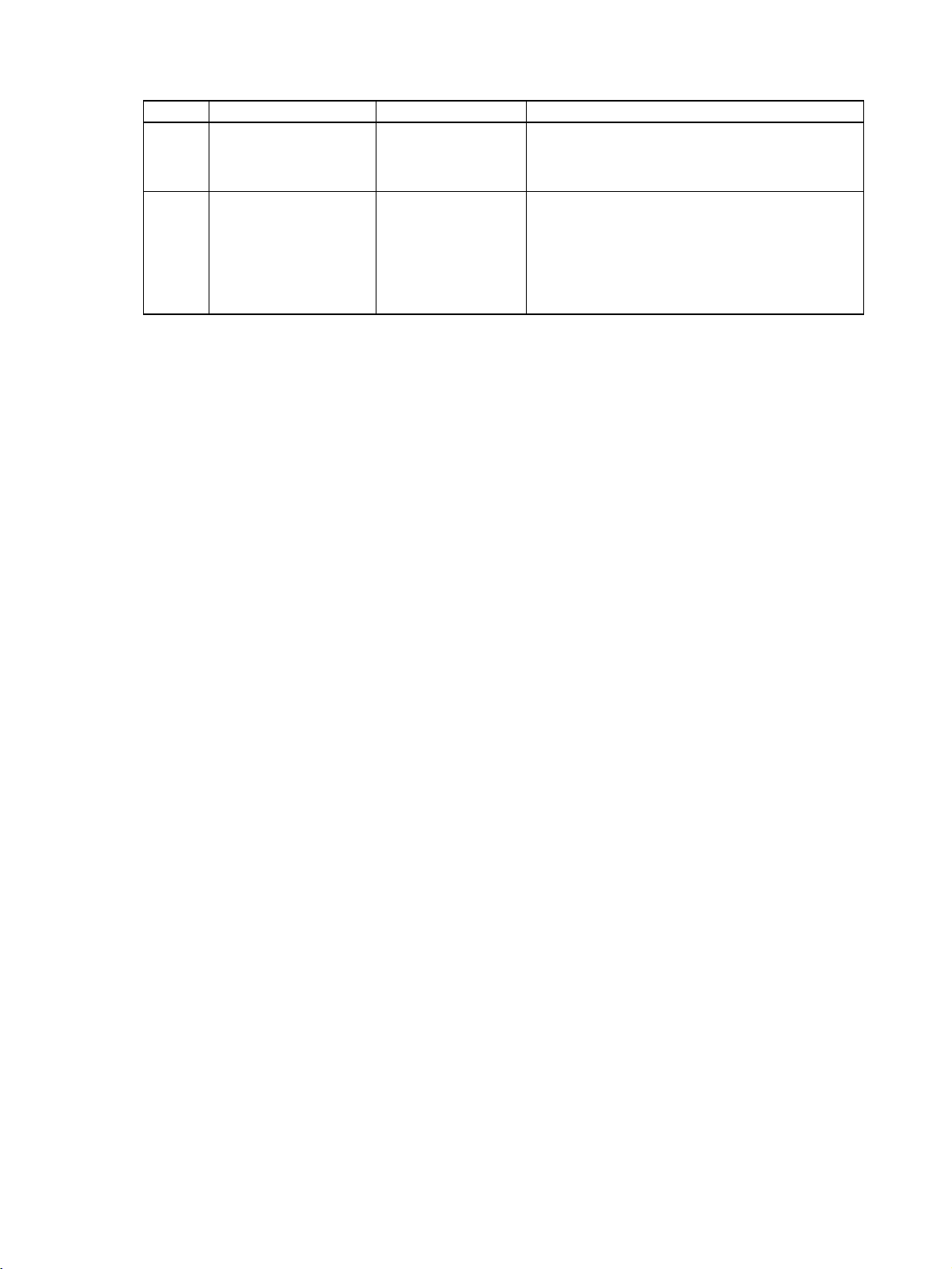

Cat. No. Model numbers Manual name Description

W445 CXONE-AL@@C-E CX-Integrator Opera-

tion Manual

W344 WS02-PSTC1-E CX-Protocol Opera-

tion Manual

Describes CX-Integrator operating procedures and

provides information on network configuration (data

links, routing tables, Communications Units setup,

etc.

Provides operating procedures for creating protocol

macros (i.e., communications sequences) with the

CX-Protocol and other information on protocol macros.

The CX-Protocol is required to create protocol macros for user-specific serial communications or to

customize the standard system protocols.

xviii

Page 18

Read and Understand this Manual

Please read and understand this manual before using the product. Please consult your OMRON

representative if you have any questions or comments.

Warranty and Limitations of Liability

WARRANTY

OMRON's exclusive warranty is that the products are free from defects in materials and workmanship for a

period of one year (or other period if specified) from date of sale by OMRON.

OMRON MAKES NO WARRANTY OR REPRESENTATION, EXPRESS OR IMPLIED, REGARDING NONINFRINGEMENT, MERCHANTABILITY, OR FITNESS FOR PARTICULAR PURPOSE OF THE

PRODUCTS. ANY BUYER OR USER ACKNOWLEDGES THAT THE BUYER OR USER ALONE HAS

DETERMINED THAT THE PRODUCTS WILL SUITABLY MEET THE REQUIREMENTS OF THEIR

INTENDED USE. OMRON DISCLAIMS ALL OTHER WARRANTIES, EXPRESS OR IMPLIED.

LIMITATIONS OF LIABILITY

OMRON SHALL NOT BE RESPONSIBLE FOR SPECIAL, INDIRECT, OR CONSEQUENTIAL DAMAGES,

LOSS OF PROFITS OR COMMERCIAL LOSS IN ANY WAY CONNECTED WITH THE PRODUCTS,

WHETHER SUCH CLAIM IS BASED ON CONTRACT, WARRANTY, NEGLIGENCE, OR STRICT

LIABILITY.

In no event shall the responsibility of OMRON for any act exceed the individual price of the product on which

liability is asserted.

IN NO EVENT SHALL OMRON BE RESPONSIBLE FOR WARRANTY, REPAIR, OR OTHER CLAIMS

REGARDING THE PRODUCTS UNLESS OMRON'S ANALYSIS CONFIRMS THAT THE PRODUCTS

WERE PROPERLY HANDLED, STORED, INSTALLED, AND MAINTAINED AND NOT SUBJECT TO

CONTAMINATION, ABUSE, MISUSE, OR INAPPROPRIATE MODIFICATION OR REPAIR.

xix

Page 19

Application Considerations

SUITABILITY FOR USE

OMRON shall not be responsible for conformity with any standards, codes, or regulations that apply to the

combination of products in the customer's application or use of the products.

At the customer's request, OMRON will provide applicable third party certification documents identifying

ratings and limitations of use that apply to the products. This information by itself is not sufficient for a

complete determination of the suitability of the products in combination with the end product, machine,

system, or other application or use.

The following are some examples of applications for which particular attention must be given. This is not

intended to be an exhaustive list of all possible uses of the products, nor is it intended to imply that the uses

listed may be suitable for the products:

• Outdoor use, uses involving potential chemical contamination or electrical interference, or conditions or

uses not described in this manual.

• Nuclear energy control systems, combustion systems, railroad systems, aviation systems, medical

equipment, amusement machines, vehicles, safety equipment, and installations subject to separate

industry or government regulations.

• Systems, machines, and equipment that could present a risk to life or property.

Please know and observe all prohibitions of use applicable to the products.

NEVER USE THE PRODUCTS FOR AN APPLICATION INVOLVING SERIOUS RISK TO LIFE OR

PROPERTY WITHOUT ENSURING THAT THE SYSTEM AS A WHOLE HAS BEEN DESIGNED TO

ADDRESS THE RISKS, AND THAT THE OMRON PRODUCTS ARE PROPERLY RATED AND INSTALLED

FOR THE INTENDED USE WITHIN THE OVERALL EQUIPMENT OR SYSTEM.

PROGRAMMABLE PRODUCTS

OMRON shall not be responsible for the user's programming of a programmable product, or any

consequence thereof.

xx

Page 20

Disclaimers

CHANGE IN SPECIFICATIONS

Product specifications and accessories may be changed at any time based on improvements and other

reasons.

It is our practice to change model numbers when published ratings or features are changed, or when

significant construction changes are made. However, some specifications of the products may be changed

without any notice. When in doubt, special model numbers may be assigned to fix or establish key

specifications for your application on your request. Please consult with your OMRON representative at any

time to confirm actual specifications of purchased products.

DIMENSIONS AND WEIGHTS

Dimensions and weights are nominal and are not to be used for manufacturing purposes, even when

tolerances are shown.

PERFORMANCE DATA

Performance data given in this manual is provided as a guide for the user in determining suitability and does

not constitute a warranty. It may represent the result of OMRON's test conditions, and the users must

correlate it to actual application requirements. Actual performance is subject to the OMRON Warranty and

Limitations of Liability.

ERRORS AND OMISSIONS

The information in this manual has been carefully checked and is believed to be accurate; however, no

responsibility is assumed for clerical, typographical, or proofreading errors, or omissions.

xxi

Page 21

xxii

Page 22

PRECAUTIONS

This section provides general precautions for using the CP-series Programmable Controllers (PLCs) and related devices.

The information contained in this section is important for the safe and reliable application of Programmable

Controllers. You must read this section and understand the information contained before attempting to set up or

operate a PLC system.

1 Intended Audience . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xxiv

2 General Precautions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xxiv

3 Safety Precautions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xxiv

4 Operating Environment Precautions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xxvi

5 Application Precautions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xxvii

6 Conformance to EC Directives . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xxx

6-1 Applicable Directives . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xxx

6-2 Concepts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xxx

6-3 Conformance to EC Directives . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xxx

6-4 Relay Output Noise Reduction Methods . . . . . . . . . . . . . . . . . . . . . xxxi

6-5 Conditions for Meeting EMC Directives when Using CP1,

CP-series, or CPM1A Relay Expansion I/O Units. . . . . . . . . . . . . . xxxii

xxiii

Page 23

Intended Audience 1

1 Intended Audience

This manual is intended for the following personnel, who must also have

knowledge of electrical systems (an electrical engineer or the equivalent).

• Personnel in charge of installing FA systems.

• Personnel in charge of designing FA systems.

• Personnel in charge of managing FA systems and facilities.

2 General Precautions

The user must operate the product according to the performance specifications described in the operation manuals.

Before using the product under conditions which are not described in the

manual or applying the product to nuclear control systems, railroad systems,

aviation systems, vehicles, combustion systems, medical equipment, amusement machines, safety equipment, and other systems, machines, and equipment that may have a serious influence on lives and property if used

improperly, consult your OMRON representative.

Make sure that the ratings and performance characteristics of the product are

sufficient for the systems, machines, and equipment, and be sure to provide

the systems, machines, and equipment with double safety mechanisms.

This manual provides information for programming and operating the Unit. Be

sure to read this manual before attempting to use the Unit and keep this manual close at hand for reference during operation.

!WARNING It is extremely important that a PLC and all PLC Units be used for the speci-

fied purpose and under the specified conditions, especially in applications that

can directly or indirectly affect human life. You must consult with your OMRON

representative before applying a PLC System to the above-mentioned applications.

3 Safety Precautions

!WARNING Do not attempt to take any Unit apart while the power is being supplied. Doing

so may result in electric shock.

!WARNING Do not touch any of the terminals or terminal blocks while the power is being

supplied. Doing so may result in electric shock.

!WARNING Do not attempt to disassemble, repair, or modify any Units. Any attempt to do

so may result in malfunction, fire, or electric shock.

!WARNING Provide safety measures in external circuits (i.e., not in the Programmable

Controller), including the following items, to ensure safety in the system if an

abnormality occurs due to malfunction of the PLC or another external factor

affecting the PLC operation. Not doing so may result in serious accidents.

xxiv

• Emergency stop circuits, interlock circuits, limit circuits, and similar safety

measures must be provided in external control circuits.

Page 24

Safety Precautions 3

• The PLC will turn OFF all outputs when its self-diagnosis function detects

any error or when a severe failure alarm (FALS) instruction is executed.

As a countermeasure for such errors, external safety measures must be

provided to ensure safety in the system.

• The PLC or outputs may remain ON or OFF due to deposits on or burning

of the output relays, or destruction of the output transistors. As a countermeasure for such problems, external safety measures must be provided

to ensure safety in the system.

• When the 24-V DC output (service power supply to the PLC) is overloaded or short-circuited, the voltage may drop and result in the outputs

being turned OFF. As a countermeasure for such problems, external

safety measures must be provided to ensure safety in the system.

!WARNING Fail-safe measures must be taken by the customer to ensure safety in the

event of incorrect, missing, or abnormal signals caused by broken signal lines,

momentary power interruptions, or other causes. Not doing so may result in

serious accidents.

!Caution Execute online edit only after confirming that no adverse effects will be

caused by extending the cycle time. Otherwise, the input signals may not be

readable.

!Caution Confirm safety at the destination node before transferring a program to

another node or editing the I/O area. Doing either of these without confirming

safety may result in injury.

!Caution Tighten the screws on the terminal block of the AC Power Supply Unit to the

torque specified in this manual. The loose screws may result in burning or

malfunction.

!Caution Do not touch anywhere near the power supply parts or I/O terminals while the

power is ON, and immediately after turning OFF the power. The hot surface

may cause burn injury.

!Caution Pay careful attention to the polarities (+/-) when wiring the DC power supply. A

wrong connection may cause malfunction of the system.

!Caution When connecting the PLC to a computer or other peripheral device, either

ground the 0 V side of the external power supply or do not ground the external

power supply at all. Otherwise the external power supply may be shorted

depending on the connection methods of the peripheral device. DO NOT

ground the 24 V side of the external power supply, as shown in the following

diagram.

Non-insulated DC power supply

24 V

Twisted-pair

cable

FG

0 V

0 V

CPU Unit

FG

FG

0 V

Peripheral device

FG

xxv

Page 25

Operating Environment Precautions 4

!Caution After programming (or reprogramming) using the IOWR instruction, confirm

that correct operation is possible with the new ladder program and data before

starting actual operation. Any irregularities may cause the product to stop

operating, resulting in unexpected operation in machinery or equipment.

!Caution The CP-series CPU Units automatically back up the user program and param-

eter data to flash memory when these are written to the CPU Unit. I/O memory (including the DM Area, Counter present values and Completion Flags,

and HR Area), however, is not written to flash memory. The DM Area, Counter

present values and Completion Flags, and HR Area can be held during power

interruptions with a battery. If there is a battery error, the contents of these

areas may not be accurate after a power interruption. If the contents of the

DM Area, Counter present values and Completion Flags, and HR Area are

used to control external outputs, prevent inappropriate outputs from being

made whenever the Battery Error Flag (A402.04) is ON.

4 Operating Environment Precautions

!Caution Do not operate the control system in the following locations:

• Locations subject to direct sunlight.

• Locations subject to temperatures or humidity outside the range specified

in the specifications.

• Locations subject to condensation as the result of severe changes in temperature.

• Locations subject to corrosive or flammable gases.

• Locations subject to dust (especially iron dust) or salts.

• Locations subject to exposure to water, oil, or chemicals.

• Locations subject to shock or vibration.

!Caution Take appropriate and sufficient countermeasures when installing systems in

the following locations:

• Locations subject to static electricity or other forms of noise.

• Locations subject to strong electromagnetic fields.

• Locations subject to possible exposure to radioactivity.

• Locations close to power supplies.

!Caution The operating environment of the PLC System can have a large effect on the

longevity and reliability of the system. Improper operating environments can

lead to malfunction, failure, and other unforeseeable problems with the PLC

System. Make sure that the operating environment is within the specified conditions at installation and remains within the specified conditions during the

life of the system.

xxvi

Page 26

Application Precautions 5

5 Application Precautions

Observe the following precautions when using the PLC System.

!WARNING Always heed these precautions. Failure to abide by the following precautions

could lead to serious or possibly fatal injury.

• Always connect to 100

to a ground of 100

• Always turn OFF the power supply to the PLC before attempting any of

the following. Not turning OFF the power supply may result in malfunction

or electric shock.

• Mounting or dismounting Expansion Units or any other Units

• Connecting or removing the Memory Cassette or Option Board

• Setting DIP switches or rotary switches

• Connecting or wiring the cables

• Connecting or disconnecting the connectors

!Caution Failure to abide by the following precautions could lead to faulty operation of

the PLC or the system, or could damage the PLC or PLC Units. Always heed

these precautions.

• Install external breakers and take other safety measures against short-circuiting in external wiring. Insufficient safety measures against short-circuiting may result in burning.

• Mount the Unit only after checking the connectors and terminal blocks

completely.

• Be sure that all the terminal screws and cable connector screws are tightened to the torque specified in the relevant manuals. Incorrect tightening

torque may result in malfunction.

• Wire all connections correctly according to instructions in this manual.

• Always use the power supply voltage specified in the operation manuals.

An incorrect voltage may result in malfunction or burning.

• Take appropriate measures to ensure that the specified power with the

rated voltage and frequency is supplied. Be particularly careful in places

where the power supply is unstable. An incorrect power supply may result

in malfunction.

• Leave the label attached to the Unit when wiring. Removing the label may

result in malfunction.

• Remove the label after the completion of wiring to ensure proper heat dissipation. Leaving the label attached may result in malfunction.

• Use crimp terminals for wiring. Do not connect bare stranded wires

directly to terminals. Connection of bare stranded wires may result in

burning.

• Do not apply voltages to the input terminals in excess of the rated input

voltage. Excess voltages may result in burning.

• Do not apply voltages or connect loads to the output terminals in excess

of the maximum switching capacity. Excess voltage or loads may result in

burning.

Ω or less when installing the Units. Not connecting

Ω or less may result in electric shock.

xxvii

Page 27

Application Precautions 5

• Be sure that the terminal blocks, connectors, Option Boards, and other

items with locking devices are properly locked into place. Improper locking

may result in malfunction.

• Disconnect the functional ground terminal when performing withstand

voltage tests. Not disconnecting the functional ground terminal may result

in burning.

• Wire correctly and double-check all the wiring or the setting switches

before turning ON the power supply. Incorrect wiring may result in burning.

• Check that the DIP switches and data memory (DM) are properly set

before starting operation.

• Check the user program for proper execution before actually running it on

the Unit. Not checking the program may result in an unexpected operation.

• Resume operation only after transferring to the new CPU Unit and/or Special I/O Units the contents of the DM, HR, and CNT Areas required for

resuming operation. Not doing so may result in an unexpected operation.

• Confirm that no adverse effect will occur in the system before attempting

any of the following. Not doing so may result in an unexpected operation.

• Changing the operating mode of the PLC (including the setting of the

startup operating mode).

• Force-setting/force-resetting any bit in memory.

• Changing the present value of any word or any set value in memory.

• Do not pull on the cables or bend the cables beyond their natural limit.

Doing either of these may break the cables.

• Do not place objects on top of the cables. Doing so may break the cables.

• When replacing parts, be sure to confirm that the rating of a new part is

correct. Not doing so may result in malfunction or burning.

• Before touching the Unit, be sure to first touch a grounded metallic object

in order to discharge any static buildup. Not doing so may result in malfunction or damage.

• Do not touch the Expansion I/O Unit Connecting Cable while the power is

being supplied in order to prevent malfunction due to static electricity.

• Do not turn OFF the power supply to the Unit while data is being transferred.

• When transporting or storing the product, cover the PCBs with electrically

conductive materials to prevent LSIs and ICs from being damaged by

static electricity, and also keep the product within the specified storage

temperature range.

• Do not touch the mounted parts or the rear surface of PCBs because

PCBs have sharp edges such as electrical leads.

• Double-check the pin numbers when assembling and wiring the connectors.

• Wire correctly according to specified procedures.

• Do not connect pin 6 (+5V) on the RS-232C Option Board on the CPU

Unit to any external device other than the NT-AL001 or CJ1W-CIF11 Conversion Adapter. The external device and the CPU Unit may be damaged.

• Use the dedicated connecting cables specified in this manual to connect

the Units. Using commercially available RS-232C computer cables may

cause failures in external devices or the CPU Unit.

xxviii

Page 28

Application Precautions 5

• Check that data link tables and parameters are properly set before starting operation. Not doing so may result in unexpected operation. Even if

the tables and parameters are properly set, confirm that no adverse

effects will occur in the system before running or stopping data links.

• Transfer a routing table to the CPU Unit only after confirming that no

adverse effects will be caused by restarting CPU Bus Units, which is automatically done to make the new tables effective.

• The user program and parameter area data in the CP-series CPU Unit is

backed up in the built-in flash memory. The BKUP indicator will light on

the front of the CPU Unit when the backup operation is in progress. Do

not turn OFF the power supply to the CPU Unit when the BKUP indicator

is lit. The data will not be backed up if power is turned OFF.

• Do not turn OFF the power supply to the PLC while the Memory Cassette

is being written. Doing so may corrupt the data in the Memory Cassette.

The BKUP indicator will light while the Memory Cassette is being written.

With a CP1H CPU Unit, the 7-segment display will also light to indicate

writing progress. Wait for the BKUP indicator and 7-segment display to go

out before turning OFF the power supply to the PLC.

• Before replacing the battery, supply power to the CPU Unit for at least 5

minutes and then complete battery replacement within 5 minutes of turn

OFF the power supply. Memory data may be corrupted if this precaution is

not observed.

• Always use the following size wire when connecting I/O Units, Special I/O

Units, and CPU Bus Units: AWG22 to AWG18 (0.32 to 0.82 mm

• UL standards required that batteries be replaced only by experienced

technicians. Do not allow unqualified persons to replace batteries. Also,

always follow the replacement procedure provided in the manual.

• Never short-circuit the positive and negative terminals of a battery or

charge, disassemble, heat, or incinerate the battery. Do not subject the

battery to strong shocks or deform the barry by applying pressure. Doing

any of these may result in leakage, rupture, heat generation, or ignition of

the battery. Dispose of any battery that has been dropped on the floor or

otherwise subjected to excessive shock. Batteries that have been subjected to shock may leak if they are used.

• Always construct external circuits so that the power to the PLC it turned

ON before the power to the control system is turned ON. If the PLC power

supply is turned ON after the control power supply, temporary errors may

result in control system signals because the output terminals on DC Output Units and other Units will momentarily turn ON when power is turned

ON to the PLC.

• Fail-safe measures must be taken by the customer to ensure safety in the

event that outputs from Output Units remain ON as a result of internal circuit failures, which can occur in relays, transistors, and other elements.

• If the I/O Hold Bit is turned ON, the outputs from the PLC will not be

turned OFF and will maintain their previous status when the PLC is

switched from RUN or MONITOR mode to PROGRAM mode. Make sure

that the external loads will not produce dangerous conditions when this

occurs. (When operation stops for a fatal error, including those produced

with the FALS(007) instruction, all outputs from Output Unit will be turned

OFF and only the internal output status will be maintained.)

2

).

xxix

Page 29

Conformance to EC Directives 6

• Dispose of the product and batteries according to local ordinances as

they apply.

Have qualified specialists properly dispose of used batteries as industrial

waste.

6 Conformance to EC Directives

6-1 Applicable Directives

•EMC Directives

• Low Voltage Directive

6-2 Concepts

EMC Directives

OMRON devices that comply with EC Directives also conform to the related

EMC standards so that they can be more easily built into other devices or the

overall machine. The actual products have been checked for conformity to

EMC standards (see the following note). Whether the products conform to the

standards in the system used by the customer, however, must be checked by

the customer.

EMC-related performance of the OMRON devices that comply with EC Directives will vary depending on the configuration, wiring, and other conditions of

the equipment or control panel on which the OMRON devices are installed.

The customer must, therefore, perform the final check to confirm that devices

and the overall machine conform to EMC standards.

Note The applicable EMC (Electromagnetic Compatibility) standard is EN61131-2.

Low Voltage Directive

Always ensure that devices operating at voltages of 50 to 1,000 V AC and 75

to 1,500 V DC meet the required safety standards for the PLC (EN61131-2).

6-3 Conformance to EC Directives

The CP1H/CP1L PLCs comply with EC Directives. To ensure that the

machine or device in which the CP1H/CP1L PLC is used complies with EC

Directives, the PLC must be installed as follows:

1,2,3... 1. The CP1H/CP1L PLC must be installed within a control panel.

2. You must use reinforced insulation or double insulation for the DC power

supplies used for I/O Units and CPU Units requiring DC power. The output

holding time must be 10 ms minimum for the DC power supply connected

to the power supply terminals on Units requiring DC power.

3. CP1H/CP1L PLCs complying with EC Directives also conform to

EN61131-2. Radiated emission characteristics (10-m regulations) may

vary depending on the configuration of the control panel used, other devices connected to the control panel, wiring, and other conditions. You must

therefore confirm that the overall machine or equipment complies with EC

Directives.

xxx

Page 30

Conformance to EC Directives 6

6-4 Relay Output Noise Reduction Methods

The CP1H/CP1L PLCs conforms to the Common Emission Standards

(EN61131-2) of the EMC Directives. However, noise generated by relay output switching may not satisfy these Standards. In such a case, a noise filter

must be connected to the load side or other appropriate countermeasures

must be provided external to the PLC.

Countermeasures taken to satisfy the standards vary depending on the

devices on the load side, wiring, configuration of machines, etc. Following are

examples of countermeasures for reducing the generated noise.

Countermeasures

Countermeasures are not required if the frequency of load switching for the

whole system with the PLC included is less than 5 times per minute.

Countermeasures are required if the frequency of load switching for the whole

system with the PLC included is more than 5 times per minute.

Note Refer to EN61131-2 for more details.

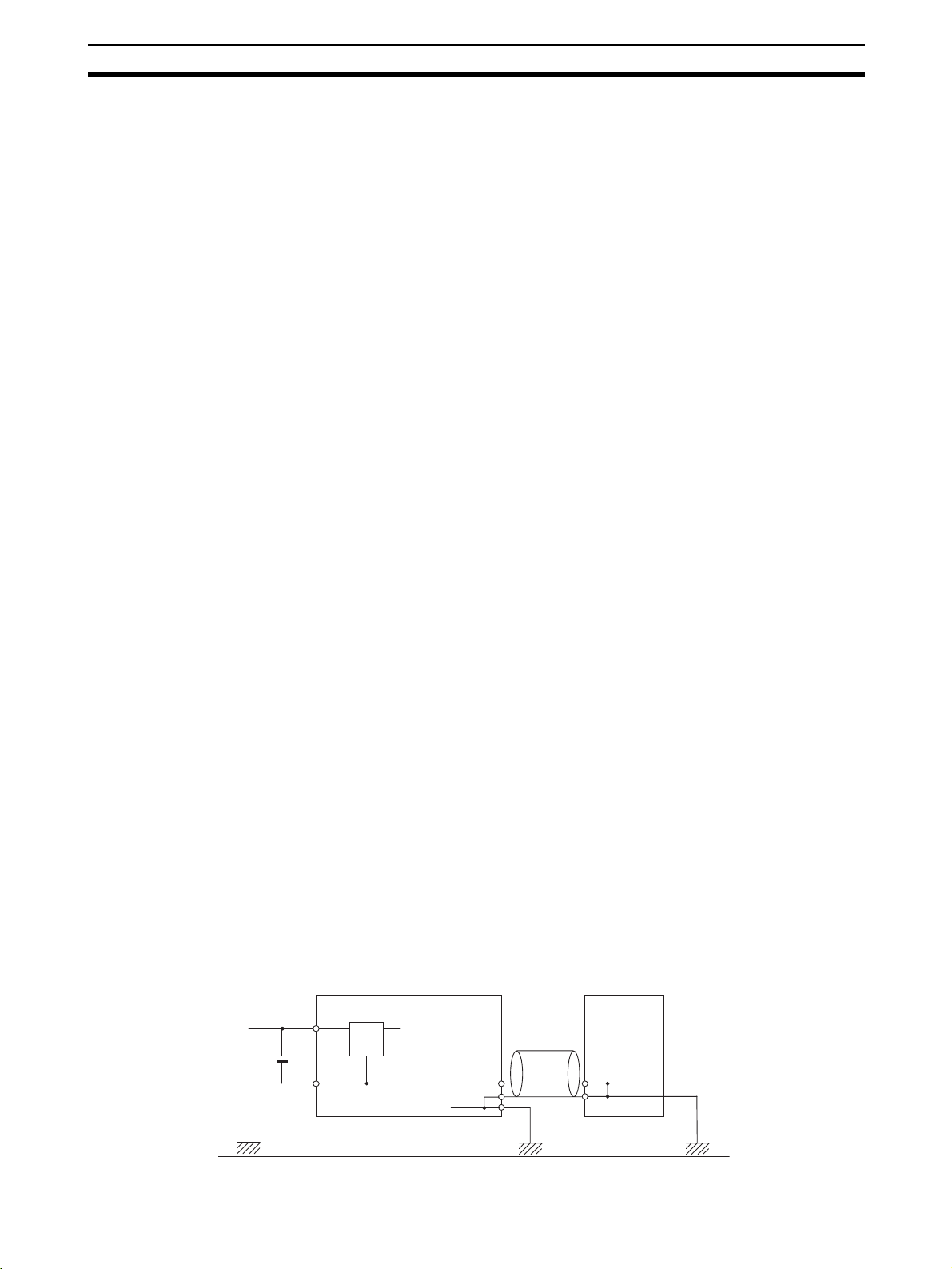

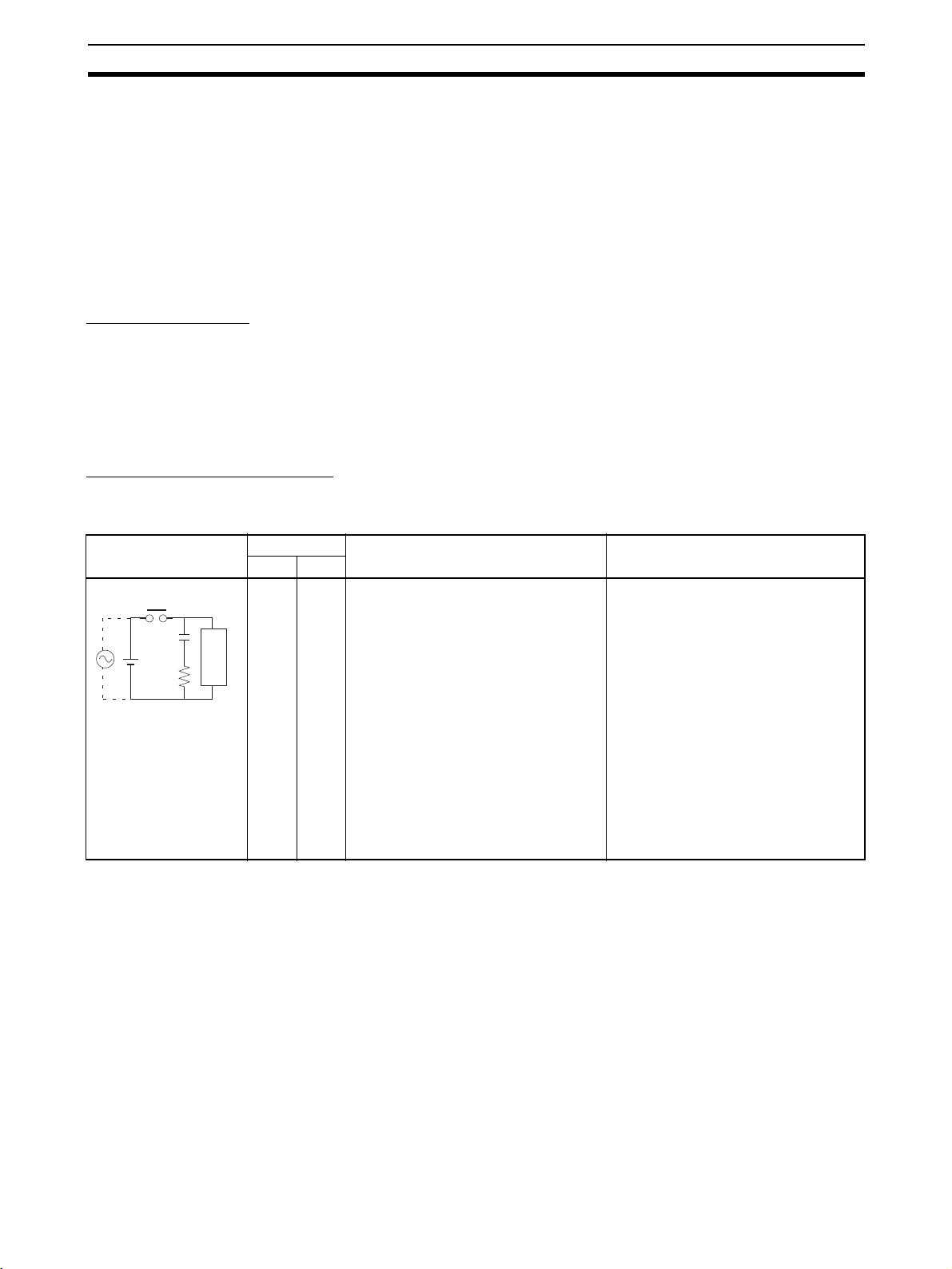

Countermeasure Examples

When switching an inductive load, connect an surge protector, diodes, etc., in

parallel with the load or contact as shown below.

Circuit Current Characteristic Required element

CR method

Powe r

supply

AC DC

Yes Yes If the load is a relay or solenoid, there is

C

R

Inductive

load

a time lag between the moment the circuit is opened and the moment the load

is reset.

If the supply voltage is 24 or 48 V, insert

the surge protector in parallel with the

load. If the supply voltage is 100 to

200 V, insert the surge protector

between the contacts.

The capacitance of the capacitor must

be 1 to 0.5 µF per contact current of

1 A and resistance of the resistor must

be 0.5 to 1 Ω per contact voltage of 1 V.

These values, however, vary with the

load and the characteristics of the

relay. Decide these values from experiments, and take into consideration that

the capacitance suppresses spark discharge when the contacts are separated and the resistance limits the

current that flows into the load when

the circuit is closed again.

The dielectric strength of the capacitor

must be 200 to 300 V. If the circuit is an

AC circuit, use a capacitor with no

polarity.

xxxi

Page 31

Conformance to EC Directives 6

Circuit Current Characteristic Required element

AC DC

Diode method

Powe r

supply

Varistor method

Power

supply

No Yes The diode connected in parallel with

the load changes energy accumulated

by the coil into a current, which then

flows into the coil so that the current will

be converted into Joule heat by the

Inductive

load

resistance of the inductive load.

This time lag, between the moment the

circuit is opened and the moment the

load is reset, caused by this method is

longer than that caused by the CR

method.

Yes Yes The varistor method prevents the impo-

sition of high voltage between the contacts by using the constant voltage

characteristic of the varistor. There is

time lag between the moment the cir-

Inductive

load

cuit is opened and the moment the load

is reset.

If the supply voltage is 24 or 48 V, insert

the varistor in parallel with the load. If

the supply voltage is 100 to 200 V,

insert the varistor between the contacts.

The reversed dielectric strength value

of the diode must be at least 10 times

as large as the circuit voltage value.

The forward current of the diode must

be the same as or larger than the load

current.

The reversed dielectric strength value

of the diode may be two to three times

larger than the supply voltage if the

surge protector is applied to electronic

circuits with low circuit voltages.

---

When switching a load with a high inrush current such as an incandescent

lamp, suppress the inrush current as shown below.

Countermeasure 1

OUT

R

COM

Providing a dark current of

approx. one-third of the rated

value through an incandescent

lamp

Countermeasure 2

R

OUT

COM

Providing a limiting resistor

6-5 Conditions for Meeting EMC Directives when Using CP1, CP-

series, or CPM1A Relay Expansion I/O Units

EN 61131-2 immunity testing conditions when using the CP1W-40EDR,

CPM1A-40EDR, CP1W-16ER or CPM1A-16ER with an CP1W-CN811 I/O

Connecting Cable are given below.

Recommended Ferrite Core

Ferrite Core (Data Line Filter): 0443-164151 manufactured by Nisshin Electric

Minimum impedance: 90 Ω at 25 MHz, 160 Ω at 100 MHz

xxxii

30

32 33

Page 32

Conformance to EC Directives 6

Recommended Connection Method

1,2,3... 1. Cable Connection Method

2. Connection Method

As shown below, connect a ferrite core to each end of the CP1W-CN811

I/O Connecting Cable.

SYSMAC

IN

CP1H

AC100-240V

L1 L2/N COM 01 03 05 07 09 11 01 03 05 07 09 11

BATTERY

00 02 04 06 08 10 00 02 04 06 08 10

POWER

PERIPHERAL

ERR/ALM

BKUP

MEMORY

00 01 02 03 04 06 00 01 03 04 06

COM COM COM COM 05 07 COM 02 COM 05 07

100CH 101CH

OUT

EXP

1CH

NCNCNC

COM

01 03 05 07 09 11 01 03 05 07 09 11

NC

00 02 04 06 08 10

CH CH

CH

IN

CH

CH

0706050403020100

OUT

CH

0706050403020100

CH CH

NC

00 01 02 04 05 07 00 02 04 05 07

NC

COM COM COM COM COM COM03 06 01 03 06

111009080706050403020100

111009080706050403020100

00 02 04 06 08 10

40EDR

EXP

xxxiii

Page 33

Conformance to EC Directives 6

xxxiv

Page 34

Programming Concepts

This section describes the basic concepts required to program the CP1H.

1-1 Programming Concepts. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

1-1-1 Programs and Tasks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

1-1-2 Basic Information on Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . 4

1-1-3 Instruction Location and Execution Conditions . . . . . . . . . . . . . . . . 6

1-1-4 Addressing I/O Memory Areas. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

1-1-5 Specifying Instruction Operands . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

1-1-6 Data Formats. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

1-1-7 Instruction Variations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

1-1-8 Execution Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

1-1-9 I/O Instruction Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

1-1-10 Refresh Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

1-1-11 Program Capacity . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

1-1-12 Basic Ladder Programming Concepts . . . . . . . . . . . . . . . . . . . . . . . 22

1-1-13 Inputting Mnemonics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

1-1-14 Program Examples . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

1-2 Precautions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

1-2-1 Condition Flags. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

1-2-2 Special Program Sections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

1-3 Checking Programs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

1-3-1 CX-Programmer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

1-3-2 Program Checks with the CX-Programmer . . . . . . . . . . . . . . . . . . . 42

1-3-3 Program Execution Check . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

1-3-4 Checking Fatal Errors. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

1-4 Introducing Function Blocks. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

1-4-1 Overview and Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

1-4-2 Function Block Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

1-4-3 Files Created with CX-Programmer. . . . . . . . . . . . . . . . . . . . . . . . . 48

SECTION 1

1

Page 35

Programming Concepts Section 1-1

1-1 Programming Concepts

1-1-1 Programs and Tasks

Tasks specify the sequence and interrupt conditions under which individual

programs will be executed. They are broadly grouped into the following types:

1,2,3... 1. Tasks executed sequentially that are called cyclic tasks.

2. Tasks executed by interrupt conditions that are called interrupt tasks.

Note Interrupt tasks can be executed cyclically in the same way as cyclic tasks.

These are called “extra cyclic tasks.”

Programs allocated to cyclic tasks will be executed sequentially by task number and I/O will be refreshed once per cycle after all tasks (more precisely

tasks that are in executable status) are executed. If an interrupt condition

goes into effect during processing of the cyclic tasks, the cyclic task will be

interrupted and the program allocated to the interrupt task will be executed.

Program A

Cyclic

task 0

Cyclic

task 1

Cyclic

task n

I/O refreshing

Interrupt condition

goes into effect

Allocation

Allocation

Allocation

Interrupt

task 100

Program B

Allocation

Program C

Program D

In the above example, programming would be executed in the following order:

start of A, B, remainder of A, C, and then D. This assumes that the interrupt

condition for interrupt task 100 was established during execution of program

A. When execution of program B is completed, the rest of program A would be

executed from the place where execution was interrupted.

With earlier OMRON PLCs, one continuous program is formed from several

continuous parts. The programs allocated to each task are single programs

that terminate with an END instruction, just like the single program in earlier

PLCs.

2

Page 36

Programming Concepts Section 1-1

One feature of the cyclic tasks is that they can be enabled (executable status)

and disabled (standby status) by the task control instructions. This means that

several program components can be assembled as a task, and that only specific programs (tasks) can then be executed as needed for the current product

model or process being performed (program step switching). Therefore performance (cycle time) is greatly improved because only required programs will

be executed as needed.

Earlier system

One continuous

subprogram

I/O refreshing

CP1H

Task 1

Allocation

Task 2

Task 3

I/O refreshing

Tasks can be put into nonexecuting (standby) status.

A task that has been executed will be executed in subsequent cycles, and a

task that is on standby will remain on standby in subsequent cycles unless it is

executed again from another task.

Note Unlike earlier programs that can be compared to reading a scroll, tasks can

be compared to reading through a series of individual cards.

• All cards are read in a preset sequence starting from the lowest number.

• All cards are designated as either active or inactive, and cards that are

inactive will be skipped. (Cards are activated or deactivated by task control instructions.)

• A card that is activated will remain activated and will be read in subsequent sequences. A card that is deactivated will remain deactivated and

will be skipped until it is reactivated by another card.

3

Page 37

Programming Concepts Section 1-1

Earlier program:

Like a scroll

1-1-2 Basic Information on Instructions

Programs consist of instructions. The conceptual structure of the inputs to and

outputs from an instruction is shown in the following diagram.

Power flow (P.F., execution condition)

Instruction condition

Instruction

CP-series program:

Like a series of cards that can be activated

or deactivated by other cards.

Activated Deactivated

Power flow (P.F., execution condition)

2

Instruction condition

*

*

1

Flags

Operands

(sources)

Memory

Operands

(destinations)

Flag

*1: Input instructions only.

*2: Not output for all instructions.

Power Flow The power flow is the execution condition that is used to control the execute

and instructions when programs are executing normally. In a ladder program,

power flow represents the status of the execution condition.

Input Instructions

• Load instructions indicate a logical start and outputs the execution condition.

Outputs the

execution condition.

• Intermediate instructions input the power flow as an execution condition

and output the power flow to an intermediate or output instruction.

Outputs the

execution condition.

=

D0

#1215

4

Page 38

Programming Concepts Section 1-1

Output Instructions

Output instructions execute all functions, using the power flow as an execution

condition.

LD power flow

Input block

Output block

Power flow for

output instruction

Instruction Conditions Instruction conditions are special conditions related to overall instruction exe-

cution that are output by the following instructions. Instruction conditions have

a higher priority than power flow (P.F.) when it comes to deciding whether or

not to execute an instruction. An instruction may become not be executed or

may act differently depending on instruction conditions. Instruction conditions

are reset (canceled) at the start of each task, i.e., they are reset when the task

changes.

The following instructions are used in pairs to set and cancel certain instruction conditions. These paired instructions must be in the same task.

Instruction

condition

Interlocked An interlock turns OFF part of the program. Special conditions, such as

turning OFF output bits, resetting timers, and holding counters are in

effect.

BREAK(514)

execution

Block program

execution

Ends a FOR(512) - NEXT(513) loop during execution. (Prevents execution of all instructions until to the NEXT(513) instruction.)

Executes a JMP0(515) to JME0(516) jump. JMP0(515) JME0(516)

Executes a program block from BPRG(096) to BEND(801). BPRG(096) BEND(801)

Description Setting

instruction

IL(002) ILC(003)

BREAK(514) NEXT(513)

Canceling

instruction

Flags In this context, a flag is a bit that serves as an interface between instructions.

Input flags Output flags

• Differentiation Flags

Differentiation result flags. The status of these flags

are input automatically to the instruction for all differentiated up/down output instructions and the

DIFU(013)/DIFD(014) instructions.

•Carry (CY) Flag

The Carry Flag is used as an unspecified operand

in data shift instructions and addition/subtraction

instructions.

• Flags for Special Instructions

These include teaching flags for FPD(269) instructions and network communications enabled flags

• Differentiation Flags

Differentiation result flags. The status of these flags are output

automatically from the instruction for all differentiated up/down

output instructions and the UP(521)/DOWN(522) instruction.

• Condition Flags

Condition Flags include the Always ON/OFF Flags, as well as

flags that are updated by results of instruction execution. In user

programs, these flags can be specified by labels, such as ER, CY,

>, =, A1, A0, rather than by addresses.

• Flags for Special Instructions

These include MSG(046) execution completed flags.

Operands Operands specify preset instruction parameters (boxes in ladder diagrams)

that are used to specify I/O memory area contents or constants. An instruction

can be executed entering an address or constant as the operands. Operands

are classified as source, destination, or number operands.

Example

#0

D0

S (source)

D (destination)

N (number)

5

Page 39

Programming Concepts Section 1-1

Operand types Operand

Source Specifies the address of the data

to be read or a constant.

Destination

(Results)

Number Specifies a particular number used

Specifies the address where data

will be written.

in the instruction, such as a jump

number or subroutine number.

symbol

S Source Oper-

and

C Control data Compound data in a source oper-

D (R) ---

N---

Source operand other than control

data (C)

and that has different meanings

depending bit status.

Note Operands are also called the first operand, second operand, and so on, start-

ing from the top of the instruction.

#0

D0

First operand

Second operand

1-1-3 Instruction Location and Execution Conditions

The following table shows the possible locations for instructions. Instructions

are grouped into those that do and those do not require execution conditions.

Description

Instruction type Possible location Execution

Input instructions Logical start (Load

instructions)

Intermediate

instructions

Output instructions Connected directly

Connected directly

to the left bus bar

or is at the beginning of an instruction block.

Between a logical

start and the output instruction.

to the right bus

bar.

Note (1) There is another group of instruction that executes a series of mnemonic

instructions based on a single input. These are called block programming

instructions. Refer to the CP-series CP1H/CP1L CPU Unit Programming

Manual for details on these block programs.

(2) If an instruction requiring an execution condition is connected directly to

the left bus bar without a logical start instruction, a program error will occur when checking the program on a CX-Programmer.

condition

Diagram Examples

Not required. LD, LD TST(350),

LD > (and other

symbol comparison instructions)

Required. AND, OR, AND

TEST(350), AND

> (and other ADD

symbol comparison instructions),

UP(521),

DOWN(522),

NOT(520), etc.

Required. Most instructions

including OUT and

MOV(021).

Not required. END(001),

JME(005),

FOR(512),

ILC(003), etc.

6

Page 40

Programming Concepts Section 1-1

r

1-1-4 Addressing I/O Memory Areas

Bit Addresses

@@@@.@@

Bit number (00 to 15)

Word address

(Leading zeros are omitted.)

Example: The address of bit 03 in word 0001 in the CIO Area would be as

shown below. This address is given as “CIO 1.03” in this manual.

1.03

Bit number (03)

Word address: CIO 1

Word

15 14 13 12 11 10 08 07 06 05 04 0309 02 01 00

CIO 0

CIO 1

CIO 2

Word Addresses

Bit address:

CIO 1.03 (CIO 1.03)

Bit numbe

Example: Bit 08 in word H010 in the HR Area is given as shown below.

H10.08

Bit number: 08

Word address: H10

@@@@

Word address

(Leading zeros are omitted.)

Example: The address of word 0010 (bits 00 to 15) in the CIO Area is given

as shown below. This address is given as “CIO 10” in this manual.

10

Word address

7

Page 41

Programming Concepts Section 1-1

y

Example: The address of word W5 (bits 00 to 15) in the Work Area is given

as shown below.

W5

Word address

Example: The address of word D200 (bits 00 to 15) in the DM Area is given

as shown below.

D200

Word address

1-1-5 Specifying Instruction Operands

Operand Description Notation Application

examples

Specifying bit

addresses

The word and bit numbers are specified

directly to specify a bit (input bits).

@@@@.@@

Bit number

(00 to 15)

Word address

1.02

1.02

Bit number: 02

Word number: CIO 1

Note The same addresses are used to

access timer/counter Completion Flags

and Present Values. There is also only

one address for a Task Flag.

Specifying

word

addresses

Specifying

indirect DM

addresses in

Binary Mode

The word number is specified directly to specify the 16-bit word.

@@@@

Word address

The offset from the beginning of the area is

specified. The contents of the address will be

treated as binary data (00000 to 32767) to

specify the word address in Data Memory

(DM). Add the @ symbol at the front to specify

an indirect ad-dress in Binary Mode.

3

Word number: 3

D200

@D300

0 1 0 0

Hexadecimal 256

Specifies D256.

Word number: D200

Contents

MOV(021)

D200

MOV(021)

#1

@D300

3

Contents

@D@@@@@

Add the @ s

00000 to 32767

(0000 to 7FFF hex)

D

mbol.

8

Page 42

Programming Concepts Section 1-1

s

Operand Description Notation Application

examples

Specifying

indirect DM

addresses in

BCD Mode

Specifying a

register

directly

The offset from the beginning of the area is

specified. The contents of the address will be

treated as BCD data (0000 to 9999) to specify

the word address in Data Memory (DM). Add

an asterisk (*) at the front to specify an indirect

address in BCD Mode.

*D@@@@@

Contents

D

00000 to 9999

(BCD)

An index register (IR) or a data register (DR) is

specified directly by specifying IR@ (@: 0 to

15) or DR@ (@: 0 to 15).

*D200

0 1 0 0

BCD: 100

Specifies D100.

Add an asterisk (*).

IR0

Content

MOV(021)

#1

*D200

MOVR(560)

1.02

IR0

Stores the PLC

memory

address for

CIO 10 in IR0.

IR1

MOVR(560)

10

IR1

Stores the PLC

memory

address for

CIO 10 in IR1.

Operand Description Notation Application examples

Specifying

an indirect

address

using a register

Indirect

address

(No offset)

The bit or word with the PLC memory

address contained in IR@ will be specified.

Specify ,IR@ to specify bits and words

for instruction operands.

,IR0

,IR1

,IR0

Loads the bit with the PLC memory

address in IR0.

MOV(021)

#1

,IR1

Stores #0001 in the word with the PLC

memory in IR1.

Constant

offset

The bit or word with the PLC memory

address in IR@ + or – the constant is

+5,IR0

+5,IR0

specified.

Specify +/– constant ,IR@. Constant off-

sets range from –2048 to +2047 (decimal). The offset is converted to binary

data when the instruction is executed.

+31,IR1

Loads the bit with the PLC memory

address in IR0 + 5.

MOV(021)

#1

+31 ,IR1

Stores #0001 in the word with the PLC

memory address in IR1 + 31

9

Page 43

Programming Concepts Section 1-1

0

Operand Description Notation Application examples

Specifying

an indirect

address

using a register

DR offset The bit or word with the PLC memory

address in IR@ + the contents of DR@ is

specified.

Specify DR@ ,IR@. DR (data register)

contents are treated as signed-binary

data. The contents of IR@ will be given a

negative offset if the signed binary value

is negative.

Auto Increment

The contents of IR@ is incremented by

+1 or +2 after referencing the value as

an PLC memory address.

+1: Specify ,IR@+

+2: Specify ,IR@ + +

Note The auto increment operation will

not be executed for a CP1L CPU

Unit if a P_ER or P_AER error

occurs during instruction execution.

DR0 ,IR0

DR0 ,IR1

,IR0 ++

,IR1 +

DR0,IR

Loads the bit with the PLC memory

address in IR0 + the value in DR0.

MOV(021)

#1

DR0 ,IR1

Stores #0001 in the word with the PLC

memory address in IR1 + the value in

DR0.

,IR0 ++

Increments the contents of IR0 by 2

after the bit with the PLC memory

address in IR0 is loaded.

MOV(021)

#1

,IR1 +

Auto Decrement

The contents of IR@ is decremented by

–1 or –2 after referencing the value as

an PLC memory address.

–1: Specify ,–IR@

–2: Specify ,– –IR@

Note The auto decrement operation will

not be executed for a CP1L CPU

Unit if a P_ER or P_AER error

occurs during instruction execution.

,– –IR0

,–IR1

Increments the contents of IR1 by 1

after #0001 is stored in the word with

the PLC memory address in IR1.

,−−IR

After decrementing the contents of IR0

by 2, the bit with the PLC memory

address in IR0 is loaded.

MOV(021)

#1

,−IR1

After decrementing the contents of IR1

by 1, #0001 is stored in the word with

the PLC memory address in IR1.

10

Page 44

Programming Concepts Section 1-1

Data Operand Data form Symbol Range Application example

16-bit constant

All binary data or

a limited range of

binary data

Unsigned binary # #0000 to #FFFF

MOV(021)

#5A

D100

32-bit constant

All BCD data or a

limited range of

BCD data

All binary data or

a limited range of

binary data

Signed decimal ± –32768 to

+32767

Unsigned deci-

& &0 to &65535

mal

BCD # #0000 to #9999

Unsigned binary # #00000000 to

#FFFFFFFF

Signed binary + –2147483648 to

+2147483647

+(400)

D200

−128

D300

CMP(020)

D400

&999

−B(414)

D500

#2000

D600

MOVL(498)

#17FFF

D100

+L(401)

D200

−65536

D300

All BCD data or a

limited range of

BCD data

Unsigned decimal

& (See Note.) &0 to

&429467295

BCD # #00000000 to

#99999999

CMPL(060)

D400

&99999

−BL(415)

D500

#1000000

D600

11

Page 45

Programming Concepts Section 1-1

Data Operand Data form Symbol Range Application example

Text string Description Symbol Examples

Text string data is stored in ASCII

(one byte except for special characters) in order from the leftmost to the

rightmost byte and from the rightmost (smallest) to the leftmost word.

00 hex (NUL code) is stored in the

rightmost byte of the last word if

there is an odd number of characters.

0000 hex (2 NUL codes) is stored in

the leftmost and rightmost vacant

bytes of the last word + 1 if there is

an even number of characters.

ASCII characters that can be used in a text string includes alphanumeric characters, Katakana and symbols (except for special characters). The characters are shown in the following table.

---

'ABCDE'

↓

'A' 'B'

'C'

'E'

41

43

45

'ABCD'

'A'

'C'

NUL

41

43

00

'D'

NUL

42

44

00

'B'

'D'

NUL

42

44

00

MOV$(664)

D100

D200

D100

D101

D102

D200

D201

D202

41