Page 1

Cat. No. W483-E1-03

SYSMAC CP Series

CP1E-E@@D@-@

CP1E-N@@D@-@

CP1E-NA@@D@-@

CP1E CPU Unit

INSTRUCTIONS

REFERENCE MANUAL

Page 2

OMRON, 2009

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form, or

by any means, mechanical, electronic, photocopying, recording, or otherwise, without the prior written permission of

OMRON.

No patent liability is assumed with respect to the use of the information contained herein. Moreover, because OMRON is constantly striving to improve its high-quality products, the information contained in this manual is subject to change without

notice. Every precaution has been taken in the preparation of this manual. Nevertheless, OMRON assumes no responsibility

for errors or omissions. Neither is any liability assumed for damages resulting from the use of the information contained in

this publication.

Page 3

SYSMAC CP Series

CP1E-E@@D@-@

CP1E-N@@D@-@

CP1E-NA@@D@-@

CP1E CPU Unit

Instructions Reference Manual

Revised December 2009

Page 4

Introduction

Thank you for purchasing a SYSMAC CP-series CP1E Programmable Controller.

This manual contains information required to use the CP1E. Read this manual completely and be sure

you understand the contents before attempting to use the CP1E.

Intended Audience

This manual is intended for the following personnel, who must also have knowledge of electrical systems (an electrical engineer or the equivalent).

• Personnel in charge of installing FA systems

• Personnel in charge of designing FA systems

• Personnel in charge of managing FA systems and facilities

Applicable Products

CP-series CP1E CPU Units

• Basic Models CP1E-ED-

A basic model of CPU Unit that support basic control applications using instructions such as

basic, movement, arithmetic, and comparison instructions.

• Application Models CP1E-N/NAD-

An application model of CPU Unit that supports connections to Programmable Terminals, inverters, and servo drives.

The CP Series is centered around the CP1H, CP1L, and CP1E CPU Units and is designed with the

same basic architecture as the CS and CJ Series.

Always use CP-series Expansion Units and CP-series Expansion I/O Units when expanding I/O

capacity. I/O words are allocated in the same way as for the CPM1A/CPM2A PLCs, i.e., using fixed

areas for inputs and outputs.

CP1E CPU Unit Instructions Reference Manual(W483)

1

Page 5

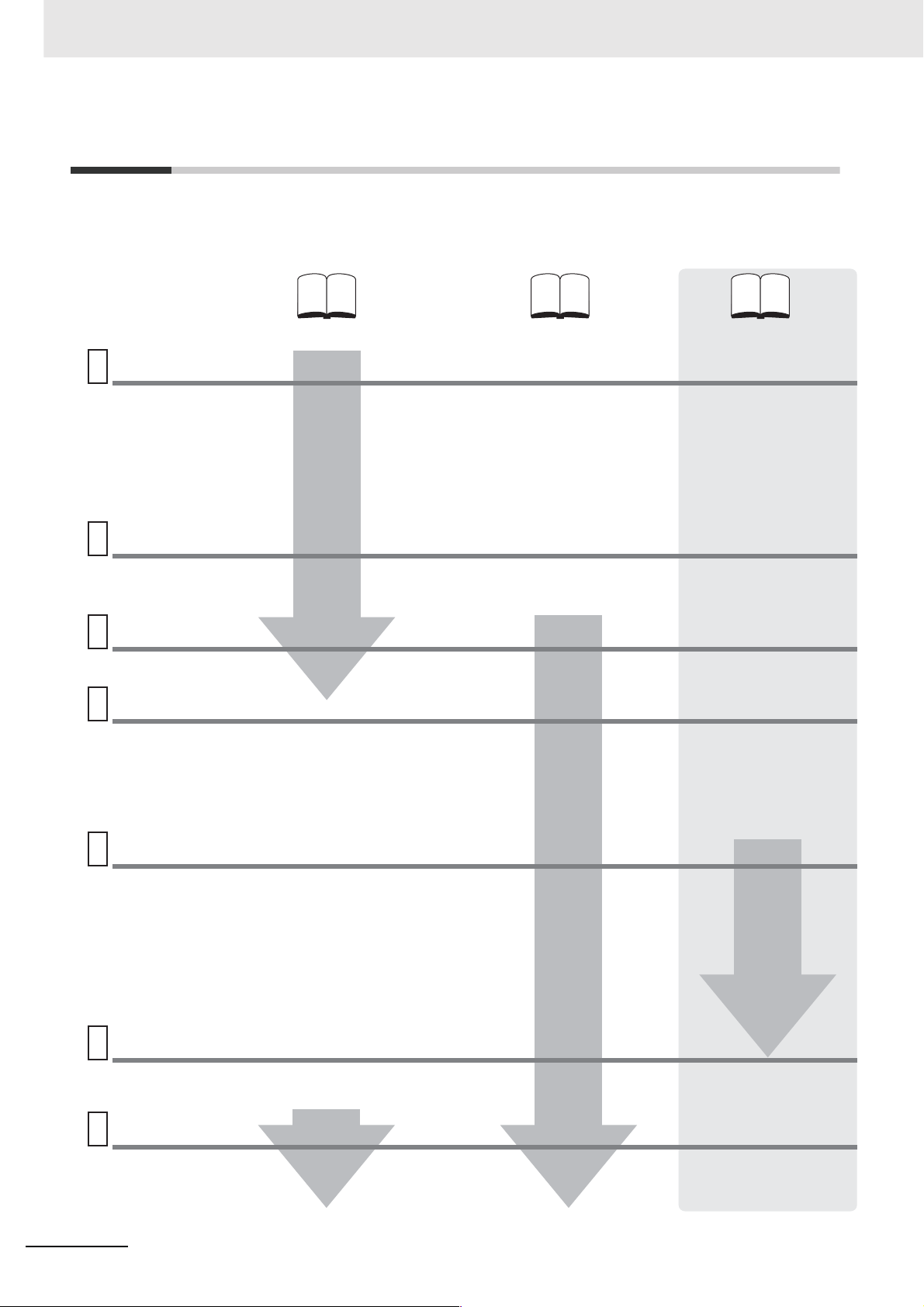

CP1E CPU Unit Manuals

Information on the CP1E CPU Units is provided in the following manuals.

Refer to the appropriate manual for the information that is required.

This

Manual

Mounting and

1

Setting Hardware

2

Wiring

Connecting

3

Online to the PLC

4

Software Setup

CP1E CPU Unit Hardware

User’s Manual(Cat. No. W479)

· Names and specifications of the parts of all Units

· Basic system configuration for each CPU Unit

· Connection methods for Expansion I/O Units

and Expansion Units

· Wiring methods for the power supply

· Wiring methods between external I/O devices

and Expansion I/O Units or Expansion Units

Connecting Cables for CX-Programmer

Support Software

CP1E CPU Unit Software

User’s Manual(Cat. No. W480)

Procedures for connecting the

CX-Programmer Support Software

Software setting methods for the CPU

Units (PLC Setup)

CP1E CPU Unit Instructions

Reference Manual(Cat. No. W483)

5

Creating the Program

· Program types and basic information

· CPU Unit operation

· Internal memory

· Built-in CPU functions

· Settings

Checking and

6

Debugging Operation

· Checking I/O wiring, setting the Auxiliary Area

settings, and performing trial operation

· Monitoring and debugging with the

Maintenance and

7

Troubleshooting

Error codes and remedies if a problem occurs

2

CX-Programmer

CP1E CPU Unit Instructions Reference Manual(W483)

Detailed information on

programming instructions

Page 6

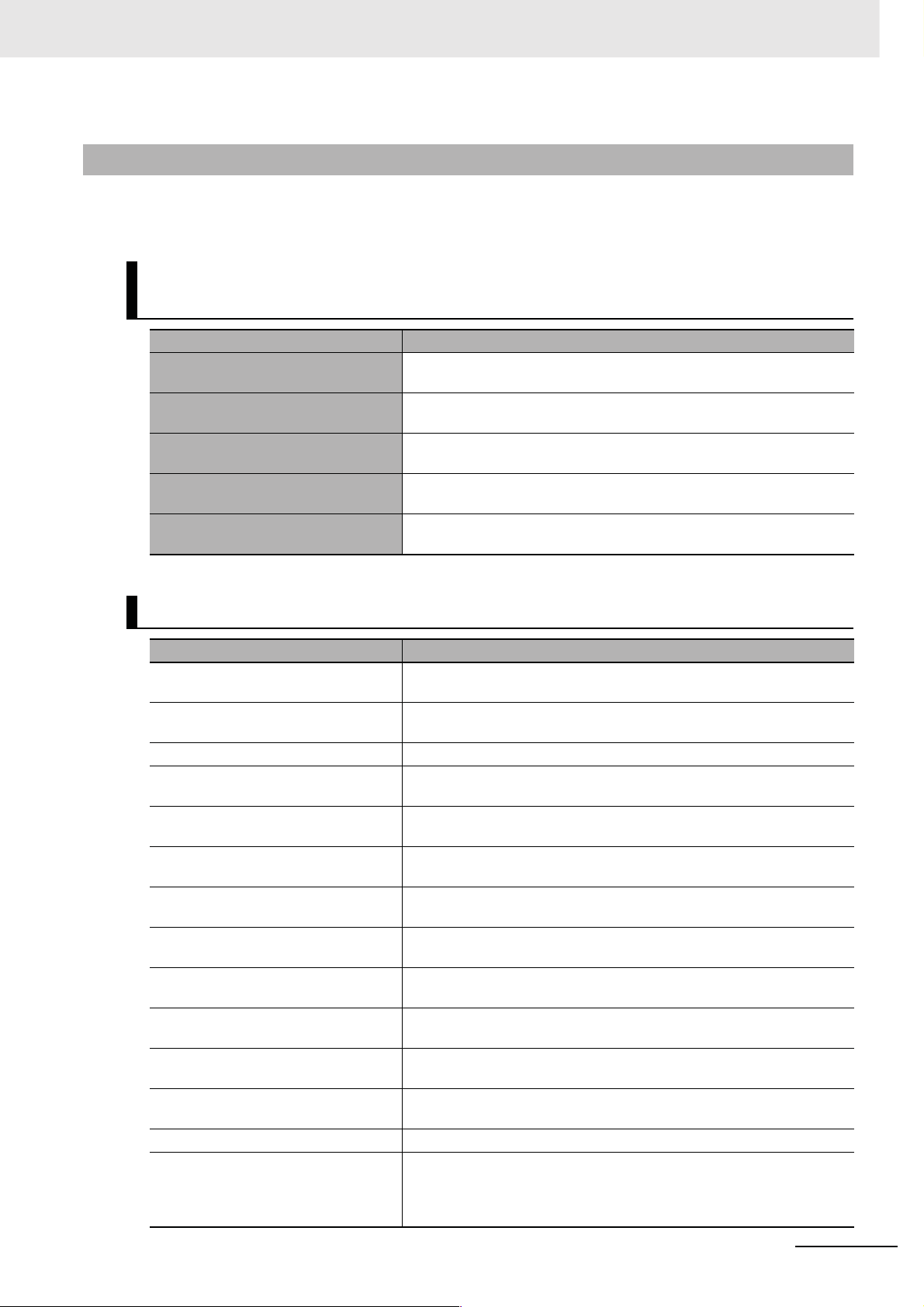

Manual Configuration

The CP1E CPU manuals are organized in the sections listed in the following tables. Refer to the appropriate section in the manuals as required.

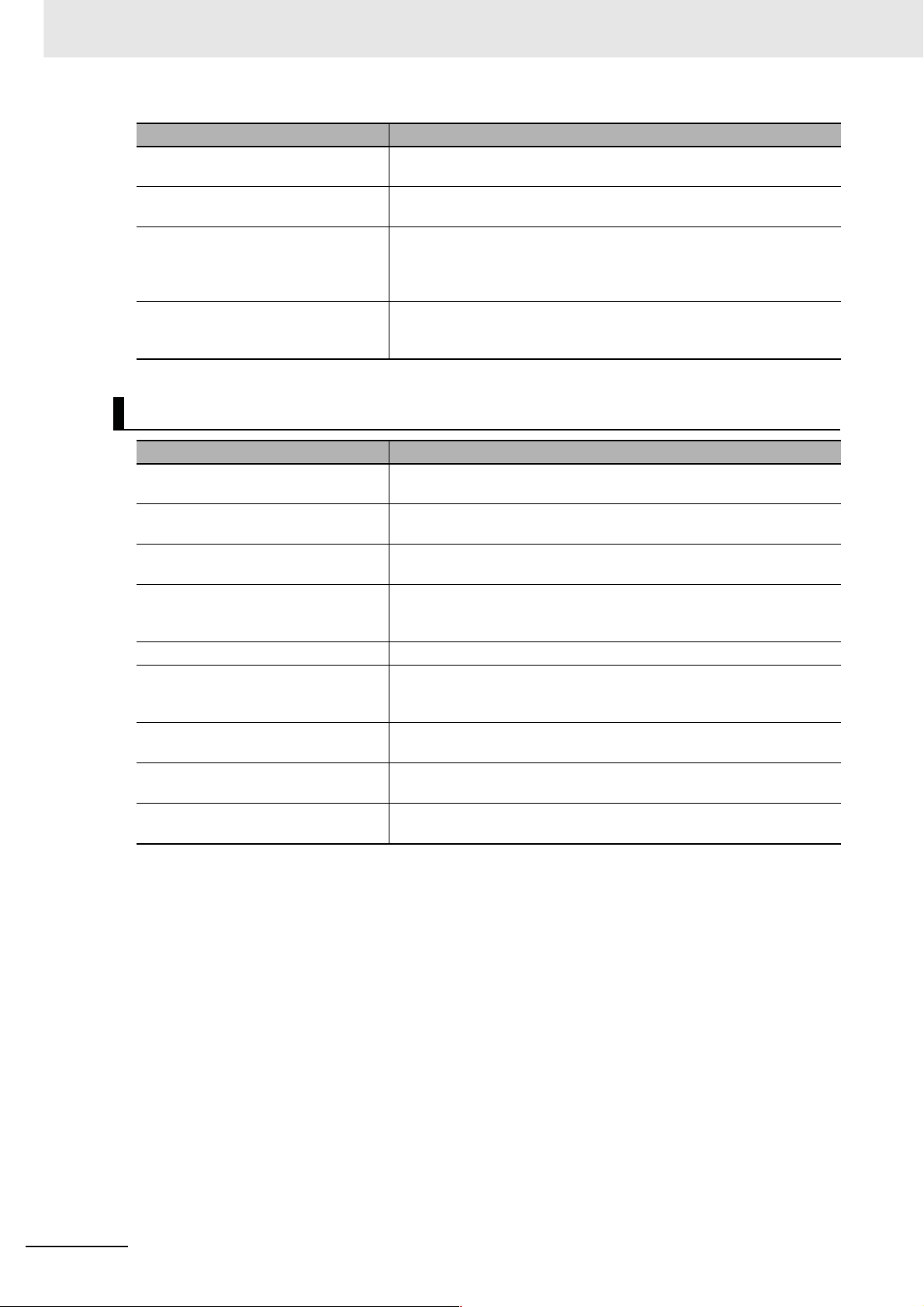

CP1E CPU Unit Instructions Reference Manual (Cat. No. W483)

(This Manual)

Section Contents

Section 1 Summary of Instructions This section provides a summary of instructions used with a CP1E CPU

Section 2 Instruction This section describes the functions, operands and sample programs of

Section 3 Instruction Execution

Times and Number of Steps

Section 4 Monitoring and

Computing the Cycle Time

Appendices The appendices provide a list of instructions by Mnemonic and ASCII

Unit.

the instructions that are supported by a CP1E CPU Unit.

This section provides the execution times for all instructions used with a

CP1E CPU Unit.

This section describes how to monitor and calculate the cycle time of a

CP1E CPU Unit that can be used in the programs.

code table for the CP1E CPU Unit.

CP1E CPU Unit Software User’s Manual (Cat. No. W480)

Section Contents

Section 1 Overview This section gives an overview of the CP1E, describes its application

procedures.

Section 2 CPU Unit Memory This section describes the types of internal memory in a CP1E CPU

Unit and the data that is stored.

Section 3 CPU Unit Operation This section describes the operation of a CP1E CPU Unit.

Section 4 Programming Concepts This section provides basic information on designing ladder programs

for a CP1E CPU Unit.

Section 5 I/O Memory This section describes the types of I/O memory areas in a CP1E CPU

Unit and the details.

Section 6 I/O Allocation This section describes I/O allocation used to exchange data between

the CP1E CPU Unit and other units.

Section 7 PLC Setup This section describes the PLC Setup, which are used to perform basic

settings for a CP1E CPU Unit.

Section 8 Overview and Allocation

of Built-in Functions

Section 9 Quick-response Inputs This section describes the quick-response inputs that can be used to

Section 10 Interrupts This section describes the interrupts that can be used with CP1E PLCs,

Section 11 High-speed Counters This section describes the high-speed counter inputs, high-speed

Section 12 Pulse Outputs This section describes positioning functions such as trapezoidal control,

Section 13 PWM Outputs This section describes the variable-duty-factor pulse (PWM) outputs.

Section 14 Serial Communications This section describes communications with Programmable Terminals

This section lists the built-in functions and describes the overall application flow and the allocation of the functions.

read signals that are shorter than the cycle time.

including input interrupts and scheduled interrupts.

counter interrupts, and the frequency measurement function.

jogging, and origin searches.

(PTs) without using communications programming, no-protocol communications with general components, and connections with a ModbusRTU Easy Master, Serial PLC Link, and host computer.

CP1E CPU Unit Instructions Reference Manual(W483)

3

Page 7

Section Contents

Section 15 Analog I/O Function This section describes the built-in analog function for NA-type CPU

Units.

Section 16 Built-in Functions This section describes PID temperature control, clock functions, DM

backup functions, security functions.

Section 17 Operating the Programming Device

Appendices The appendices provide lists of programming instructions, the Auxiliary

This section describes basic functions of the CX-Programmer, such as

using the CX-Programmer to write ladder programs to control the CP1E

CPU Unit, to transfer the programs to the CP1E CPU Unit, and to debug

the programs.

Area, cycle time response performance, PLC performance at power

interruptions.

CP1E CPU Unit Hardware User’s Manual (Cat. No. W479)

Section Contents

Section 1 Overview and Specifications

Section 2 Basic System Configuration and Devices

Section 3 Part Names and Functions This section describes the part names and functions of the CPU Unit,

Section 4 Programming Device This section describes the features of the CX-Programmer used for pro-

Section 5 Installation and Wiring This section describes how to install and wire CP1E Units.

Section 6 Troubleshooting This section describes how to troubleshoot problems that may occur

Section 7 Maintenance and Inspection

Section 8 Using Expansion Units

and Expansion I/O Units

Appendices The appendices provide information on dimensions, wiring diagrams,

This section gives an overview of the CP1E, describes its features, and

provides its specifications.

This section describes the basic system configuration and unit models

of the CP1E.

Expansion I/O Units, and Expansion Units in a CP1E PLC .

gramming and debugging PLCs, as well as how to connect the PLC with

the Programming Device by USB.

with a CP1E PLC, including the error indications provided by the CP1E

Units.

This section describes periodic inspections, the service life of the Battery, and how to replace the Battery.

This section describes application methods for Expansion Units.

and wiring serial communications for the CP1E.

4

CP1E CPU Unit Instructions Reference Manual(W483)

Page 8

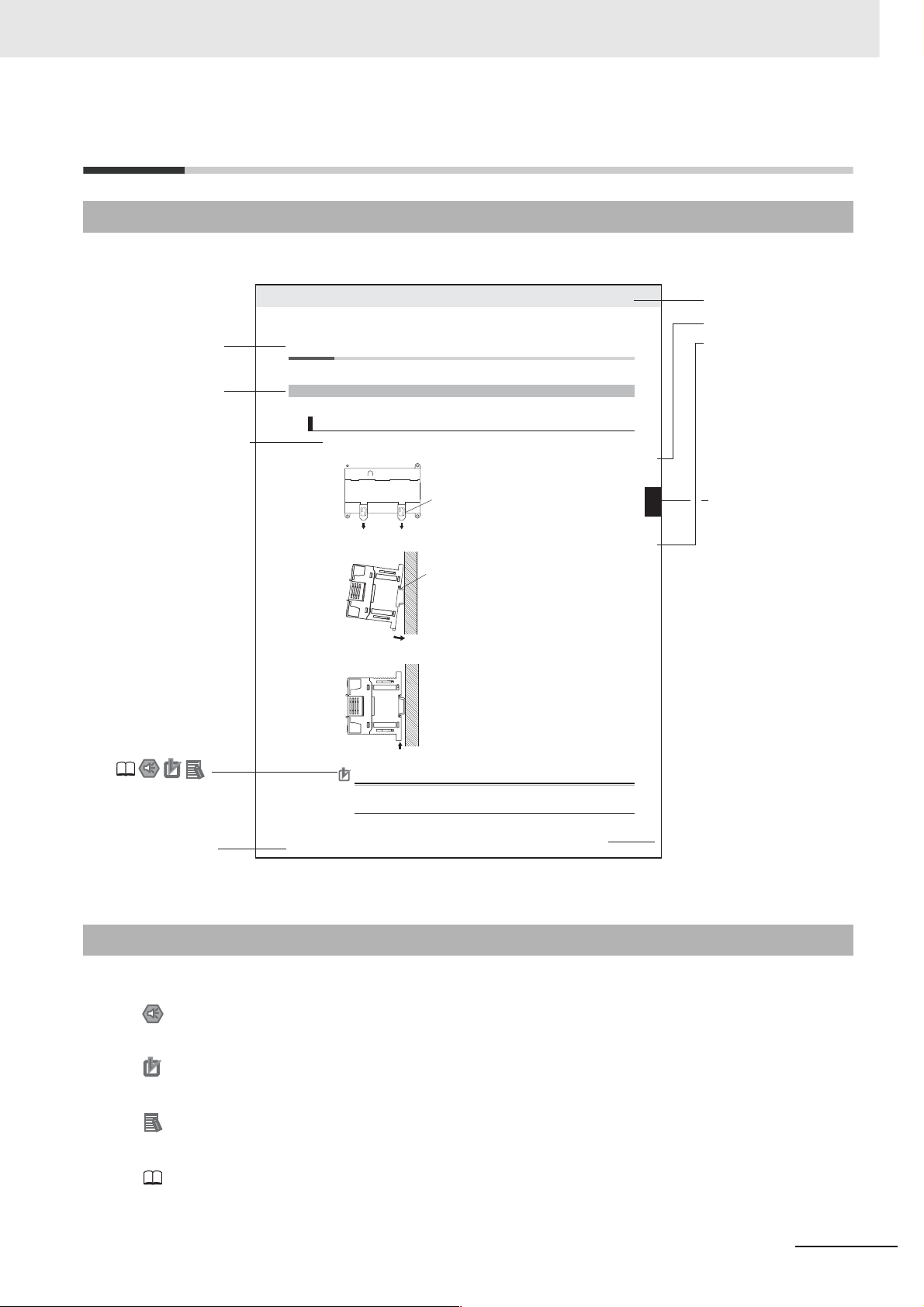

Manual Structure

Page Structure and Icons

The following page structure and icons are used in this manual.

Level 2 heading

Level 3 heading

Step in a procedure

Indicates a step in a

procedure.

Special Information

(See below.)

Icons are used to indicate

precautions and

additional information.

5-2 Installation

5-2-1 Installation Location

DIN Track Installation

1

Use a screwdriver to pull down the DIN Track mounting pins from the back of the Units to release

them, and mount the Units to the DIN Track.

Fit the back of the Units onto the DIN Track by catching the top of the Units on the Track and then

2

pressing in at the bottom of the Units, as shown below.

Press in all of the DIN Track mounting pins to securely lock the Units in place.

3

DIN Track mounting pins

5 Installation and wiring

Level 1 heading

Level 2 heading

Level 3 heading

Gives the current

headings.

5-2 Installation

DIN Track mounting pins

Release

DIN Track

5

5-2-1 Installation Location

Page tab

Gives the number

of the section.

Manual name

This illustration is provided only as a sample and may not literally appear in this manual.

Special Information

Special information in this manual is classified as follows:

Precautions for Safe Use

Precautions on what to do and what not to do to ensure using the product safely.

Precautions for Correct Use

Precautions on what to do and what not to do to ensure proper operation and performance.

Additional Information

Additional information to increase understanding or make operation easier.

References to the location of more detailed or related information.

Precautions for Correct Use

Tighten terminal block screws and cable screws to the following torques.

M4: 1.2 N·m

M3: 0.5 N·m

CP1E CPU Unit Hardware User’s Manual(W479)

5 - 3

CP1E CPU Unit Instructions Reference Manual(W483)

5

Page 9

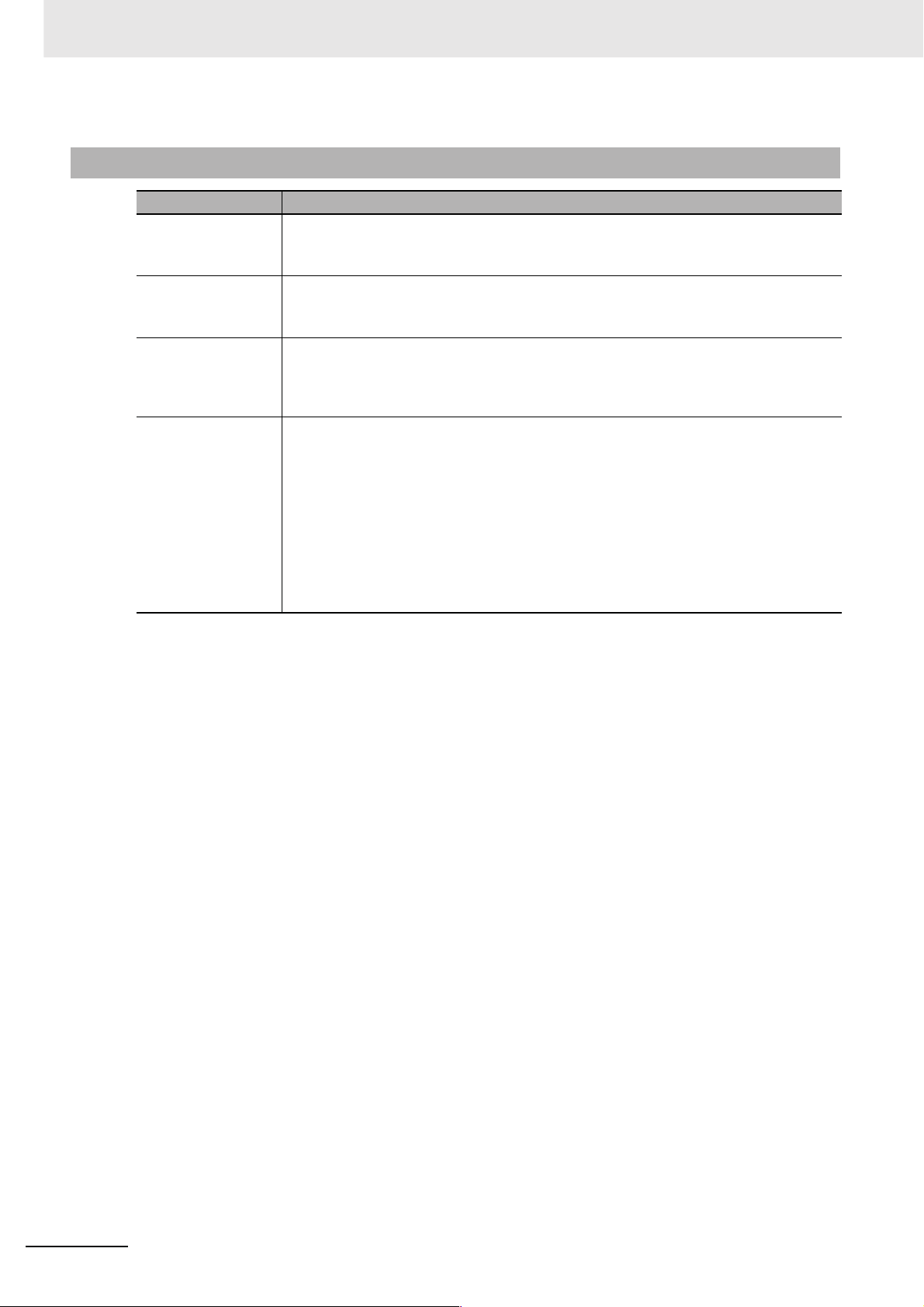

Terminology and Notation

Ter m Description

E-type CPU Unit A basic model of CPU Unit that support basic control applications using instructions such

as basic, movement, arithmetic, and comparison instructions.

Basic models of CPU Units are called “E-type CPU Units” in this manual.

N-type CPU Unit An application model of CPU Unit that supports connections to Programmable Terminals,

inverters, and servo drives.

Application models of CPU Units are called “N-type CPU Units” in this manual.

NA-type CPU Unit An application model of CPU Unit that supports built-in analog and connections to Pro-

grammable Terminals, inverters, and servo drives.

Application models of CPU Units with built-in analog are called “NA-type CPU Units” in

this manual.

CX-Programmer A programming device that applies for programming and debugging PLCs.

The CX-Programmer includes the Micro PLC Edition CX-Programmer (CX-One Lite), the

CX-Programmer (CX-One) and the CX-Programmer for CP1E.

This manual describes the unique applications and functions of the Micro PLC Edition

CX-Programmer version 9.03 or higher CX-Programmer for CP1E.

“CX-Programmer” refers to the Micro PLC Edition CX-Programmer version 9.03 or higher

CX-Programmer for CP1E in this manual.

Note E20/30/40 and N20/30/40 CPU Units are supported by CX-Programmer version 8.2

or higher. E10/14, N14/60 and NA20 CPU Units are supported by CX-Programmer

version 9.03 or higher.

6

CP1E CPU Unit Instructions Reference Manual(W483)

Page 10

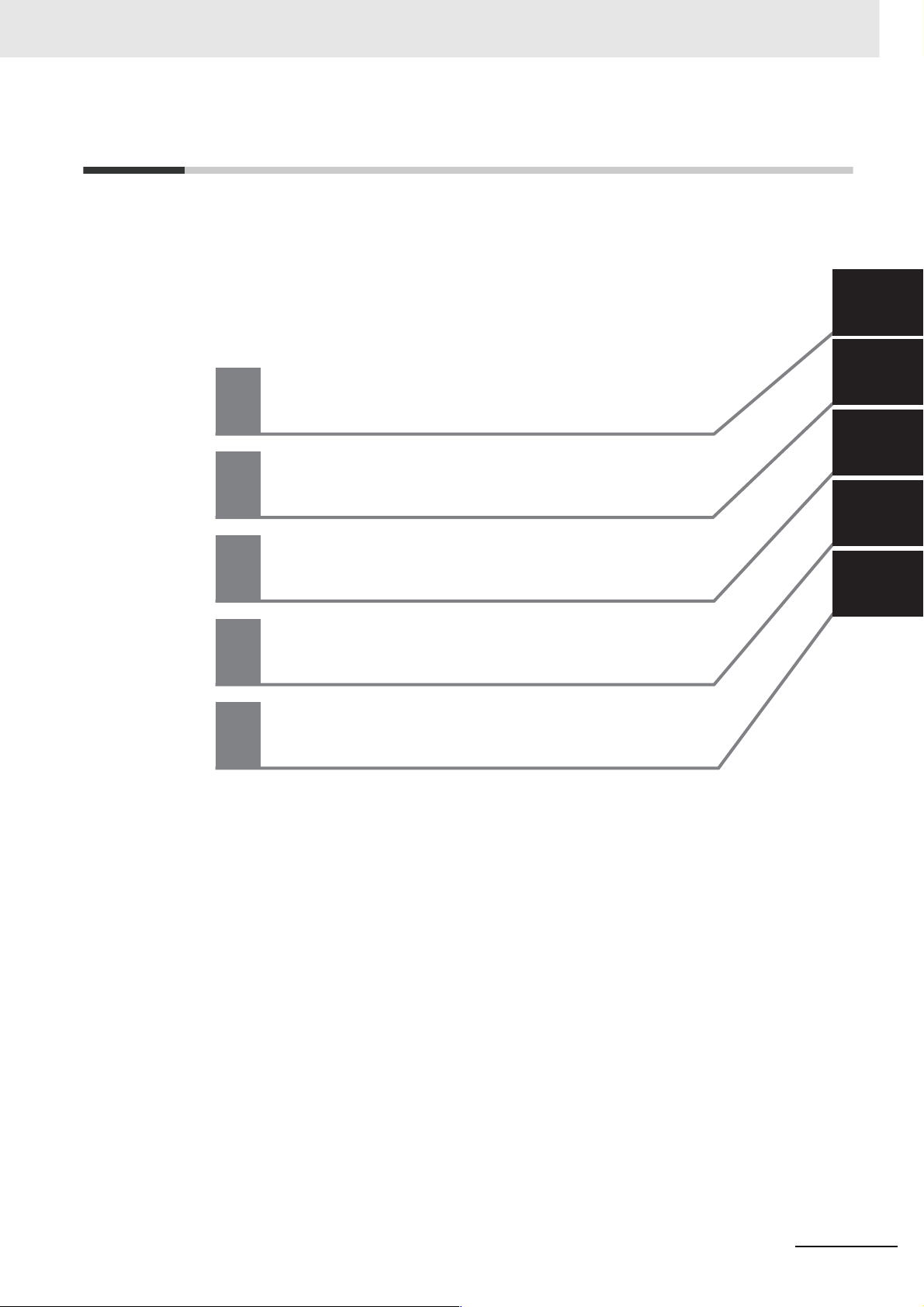

Sections in this Manual

1

2

1

2

3

4

A

Summary of Instructions

Instructions

Instruction Execution Times and Number

of Steps

Monitoring and Computing the Cycle Time

Appendices

3

4

A

CP1E CPU Unit Instructions Reference Manual(W483)

7

Page 11

CONTENTS

Introduction ...............................................................................................................1

CP1E CPU Unit Manuals ...........................................................................................2

Manual Structure .......................................................................................................5

Safety Precautions .................................................................................................. 15

Precautions for Safe Use ........................................................................................18

Regulations and Standards....................................................................................19

Related Manuals ...................................................................................................... 20

Section 1 Summary of Instructions .............................................. 1-1

1-1 Summary of Instructions ........................................................................................................ 1-2

Section 2 Instructions .................................................................... 2-1

Notation and Layout of Instruction Descriptions ......................................................................... 2-2

Sequence Input Instructions .......................................................................................................... 2-5

LD/LD NOT ................................................................................................................................................ 2-7

AND/AND NOT .......................................................................................................................................... 2-9

OR/OR NOT .............................................................................................................................................2-11

AND LD/OR LD ........................................................................................................................................ 2-13

NOT .......................................................................................................................................................... 2-16

UP/DOWN ................................................................................................................................................ 2-17

Sequence Output Instructions ..................................................................................................... 2-18

OUT/OUT NOT ........................................................................................................................................ 2-18

TR ............................................................................................................................................................ 2-20

KEEP ....................................................................................................................................................... 2-21

DIFU ......................................................................................................................................................... 2-25

DIFD ......................................................................................................................................................... 2-27

SET/RSET ............................................................................................................................................... 2-29

SETA/RSTA .............................................................................................................................................. 2-31

SETB/RSTB .............................................................................................................................................2-33

Sequence Control Instructions..................................................................................................... 2-35

END ......................................................................................................................................................... 2-38

NOP ......................................................................................................................................................... 2-39

IL/ILC ....................................................................................................................................................... 2-40

MILH/MILR/MILC ..................................................................................................................................... 2-44

JMP/CJP/JME .......................................................................................................................................... 2-53

FOR/NEXT ............................................................................................................................................... 2-56

BREAK ..................................................................................................................................................... 2-59

Timer and Counter Instructions ................................................................................................... 2-60

TIM/TIMX ................................................................................................................................................. 2-66

TIMH/TIMHX ............................................................................................................................................ 2-69

TMHH/TMHHX ......................................................................................................................................... 2-72

TTIM/TTIMX .............................................................................................................................................2-74

TIML/TIMLX .............................................................................................................................................2-77

CNT/CNTX ............................................................................................................................................... 2-80

8

CP1E CPU Unit Instructions Reference Manual(W483)

Page 12

CNTR/CNTRX ......................................................................................................................................... 2-83

CNR/CNRX .............................................................................................................................................. 2-86

Comparison Instructions .............................................................................................................. 2-88

=, <>, <, <=, >, >= .................................................................................................................................... 2-88

=DT, <>DT, <DT, <=DT, >DT, >=DT ......................................................................................................... 2-91

CMP/CMPL .............................................................................................................................................. 2-95

CPS/CPSL ............................................................................................................................................... 2-98

TCMP .................................................................................................................................................... 2-101

BCMP .................................................................................................................................................... 2-103

ZCP/ZCPL ............................................................................................................................................. 2-105

Data Movement Instructions....................................................................................................... 2-108

MOV/MOVL/MVN ................................................................................................................................... 2-108

MOVB .................................................................................................................................................... 2-111

MOVD .................................................................................................................................................... 2-113

XFRB ..................................................................................................................................................... 2-115

XFER ..................................................................................................................................................... 2-117

BSET ..................................................................................................................................................... 2-119

XCHG .................................................................................................................................................... 2-121

DIST ...................................................................................................................................................... 2-123

COLL ..................................................................................................................................................... 2-125

Data Shift Instructions ................................................................................................................ 2-127

SFT ........................................................................................................................................................ 2-127

SFTR ..................................................................................................................................................... 2-129

WSFT .................................................................................................................................................... 2-131

ASL ........................................................................................................................................................ 2-133

ASR ....................................................................................................................................................... 2-134

ROL ....................................................................................................................................................... 2-135

ROR ....................................................................................................................................................... 2-137

SLD/SRD ............................................................................................................................................... 2-139

NASL/NSLL ........................................................................................................................................... 2-141

NASR/NSRL .......................................................................................................................................... 2-144

Increment/Decrement Instructions ............................................................................................ 2-147

++/++L ................................................................................................................................................... 2-147

--/--L ...................................................................................................................................................... 2-150

++B/++BL .............................................................................................................................................. 2-153

--B/--BL ................................................................................................................................................. 2-156

Symbol Math Instructions........................................................................................................... 2-158

+/+L ....................................................................................................................................................... 2-158

+C/+CL .................................................................................................................................................. 2-160

+B/+BL ................................................................................................................................................... 2-162

+BC/+BCL ............................................................................................................................................. 2-164

–/–L ........................................................................................................................................................ 2-166

–C/–CL .................................................................................................................................................. 2-170

–B/–BL ................................................................................................................................................... 2-172

–BC/–BCL .............................................................................................................................................. 2-175

*/*L ......................................................................................................................................................... 2-177

*B/*BL .................................................................................................................................................... 2-179

/, /L ......................................................................................................................................................... 2-181

/B, /BL .................................................................................................................................................... 2-183

Conversion Instructions.............................................................................................................. 2-185

BIN/BINL ................................................................................................................................................ 2-185

BCD/BCDL ............................................................................................................................................ 2-187

NEG ....................................................................................................................................................... 2-189

MLPX ..................................................................................................................................................... 2-191

DMPX .................................................................................................................................................... 2-196

ASC ....................................................................................................................................................... 2-201

HEX ....................................................................................................................................................... 2-205

Logic Instructions........................................................................................................................ 2-210

ANDW/ANDL ......................................................................................................................................... 2-210

ORW/ORWL .......................................................................................................................................... 2-212

CP1E CPU Unit Instructions Reference Manual(W483)

9

Page 13

XORW/XORL .........................................................................................................................................2-214

COM/COML ...........................................................................................................................................2-216

Special Math Instructions ........................................................................................................... 2-218

APR ........................................................................................................................................................2-218

BCNT .....................................................................................................................................................2-227

Floating-point Math Instructions ................................................................................................ 2-229

FIX/FIXL .................................................................................................................................................2-233

FLT/FLTL ................................................................................................................................................2-235

+F, –F, *F, /F ........................................................................................................................................... 2-237

=F, <>F, <F, <=F, >F, >=F ........................................................................................................................2-241

FSTR ......................................................................................................................................................2-244

FVAL ......................................................................................................................................................2-249

Table Data Processing Instructions ........................................................................................... 2-253

SWAP .....................................................................................................................................................2-253

FCS ........................................................................................................................................................2-255

Data Control Instructions............................................................................................................ 2-257

PIDAT .....................................................................................................................................................2-257

TPO ........................................................................................................................................................2-269

SCL ........................................................................................................................................................2-276

SCL2 ......................................................................................................................................................2-280

SCL3 ......................................................................................................................................................2-284

AVG ........................................................................................................................................................2-287

Subroutines Instructions ............................................................................................................ 2-290

SBS ........................................................................................................................................................2-290

SBN/RET ...............................................................................................................................................2-295

Interrupt Control Instructions..................................................................................................... 2-298

MSKS .....................................................................................................................................................2-300

CLI .........................................................................................................................................................2-303

DI ...........................................................................................................................................................2-306

EI ............................................................................................................................................................2-307

High-speed Counter/Pulse Output Instructions........................................................................ 2-308

INI ..........................................................................................................................................................2-308

PRV ........................................................................................................................................................2-311

CTBL ......................................................................................................................................................2-315

SPED .....................................................................................................................................................2-319

PULS ......................................................................................................................................................2-323

PLS2 ......................................................................................................................................................2-325

ACC ....................................................................................................................................................... 2-331

ORG .......................................................................................................................................................2-336

PWM ......................................................................................................................................................2-339

Step Instructions ......................................................................................................................... 2-341

SNXT/STEP ...........................................................................................................................................2-342

Basic I/O Unit Instructions.......................................................................................................... 2-352

IORF ......................................................................................................................................................2-352

SDEC .....................................................................................................................................................2-354

DSW .......................................................................................................................................................2-357

MTR .......................................................................................................................................................2-361

7SEG .....................................................................................................................................................2-365

Serial Communication Instructions ........................................................................................... 2-369

TXD ........................................................................................................................................................2-369

RXD .......................................................................................................................................................2-374

Clock Instructions........................................................................................................................ 2-380

CADD/CSUB ..........................................................................................................................................2-380

DATE ......................................................................................................................................................2-385

Failure Diagnosis Instructions ................................................................................................... 2-387

FAL .........................................................................................................................................................2-387

FALS ......................................................................................................................................................2-393

10

CP1E CPU Unit Instructions Reference Manual(W483)

Page 14

Other Instructions........................................................................................................................ 2-398

STC/CLC ............................................................................................................................................... 2-398

WDT ...................................................................................................................................................... 2-399

Section 3 Instruction Execution Times and Number of Steps ... 3-1

3-1 CP1E CPU Unit Instruction Execution Times and Number of Steps .................................. 3-2

Section 4 Monitoring and Computing the Cycle Time................. 4-1

4-1 Monitoring the Cycle Time...................................................................................................... 4-2

4-1-1 Monitoring the Cycle Time.......................................................................................................... 4-2

4-2 Computing the Cycle Time .....................................................................................................4-3

4-2-1 CPU Unit Operation Flowchart ................................................................................................... 4-3

4-2-2 Cycle Time Overview.................................................................................................................. 4-4

4-2-3 I/O Refresh Times for PLC Units ................................................................................................ 4-5

4-2-4 Cycle Time Calculation Example ................................................................................................ 4-6

4-2-5 Increase in Cycle Time for Online Editing................................................................................... 4-6

Section A Appendices ....................................................................A-1

Alphabetical List of Instructions by Mnemonic .............................................................................A-2

Revision History ....................................................................................... Revision-1

CP1E CPU Unit Instructions Reference Manual(W483)

11

Page 15

Read and Understand this Manual

Please read and understand this manual before using the product. Please consult your OMRON representative

if you have any questions or comments.

Warranty and Limitations of Liability

WARRANTY

OMRON’s exclusive warranty is that the products are free from defects in materials and workmanship for a

period of one year (or other period if specified) from date of sale by OMRON.

OMRON MAKES NO WARRANTY OR REPRESENTATION, EXPRESS OR IMPLIED, REGARDING NONINFRINGEMENT, MERCHANTABILITY, OR FITNESS FOR PARTICULAR PURPOSE OF THE

PRODUCTS. ANY BUYER OR USER ACKNOWLEDGES THAT THE BUYER OR USER ALONE HAS

DETERMINED THAT THE PRODUCTS WILL SUITABLY MEET THE REQUIREMENTS OF THEIR

INTENDED USE. OMRON DISCLAIMS ALL OTHER WARRANTIES, EXPRESS OR IMPLIED.

LIMITATIONS OF LIABILITY

OMRON SHALL NOT BE RESPONSIBLE FOR SPECIAL, INDIRECT, OR CONSEQUENTIAL DAMAGES,

LOSS OF PROFITS OR COMMERCIAL LOSS IN ANY WAY CONNECTED WITH THE PRODUCTS,

WHETHER SUCH CLAIM IS BASED ON CONTRACT, WARRANTY, NEGLIGENCE, OR STRICT

LIABILITY.

In no event shall the responsibility of OMRON for any act exceed the individual price of the product on which

liability is asserted.

IN NO EVENT SHALL OMRON BE RESPONSIBLE FOR WARRANTY, REPAIR, OR OTHER CLAIMS

REGARDING THE PRODUCTS UNLESS OMRON’S ANALYSIS CONFIRMS THAT THE PRODUCTS

WERE PROPERLY HANDLED, STORED, INSTALLED, AND MAINTAINED AND NOT SUBJECT TO

CONTAMINATION, ABUSE, MISUSE, OR INAPPROPRIATE MODIFICATION OR REPAIR.

12

CP1E CPU Unit Instructions Reference Manual(W483)

Page 16

Application Considerations

SUITABILITY FOR USE

OMRON shall not be responsible for conformity with any standards, codes, or regulations that apply to the

combination of products in the customer’s application or use of the products.

At the customer’s request, OMRON will provide applicable third party certification documents identifying

ratings and limitations of use that apply to the products. This information by itself is not sufficient for a

complete determination of the suitability of the products in combination with the end product, machine,

system, or other application or use.

The following are some examples of applications for which particular attention must be given. This is not

intended to be an exhaustive list of all possible uses of the products, nor is it intended to imply that the uses

listed may be suitable for the products:

• Outdoor use, uses involving potential chemical contamination or electrical interference, or conditions or

uses not described in this manual.

• Nuclear energy control systems, combustion systems, railroad systems, aviation systems, medical

equipment, amusement machines, vehicles, safety equipment, and installations subject to separate

industry or government regulations.

• Systems, machines, and equipment that could present a risk to life or property.

Please know and observe all prohibitions of use applicable to the products.

NEVER USE THE PRODUCTS FOR AN APPLICATION INVOLVING SERIOUS RISK TO LIFE OR

PROPERTY WITHOUT ENSURING THAT THE SYSTEM AS A WHOLE HAS BEEN DESIGNED TO

ADDRESS THE RISKS, AND THAT THE OMRON PRODUCTS ARE PROPERLY RATED AND INSTALLED

FOR THE INTENDED USE WITHIN THE OVERALL EQUIPMENT OR SYSTEM.

PROGRAMMABLE PRODUCTS

OMRON shall not be responsible for the user’s programming of a programmable product, or any

consequence thereof.

CP1E CPU Unit Instructions Reference Manual(W483)

13

Page 17

Disclaimers

CHANGE IN SPECIFICATIONS

Product specifications and accessories may be changed at any time based on improvements and other

reasons.

It is our practice to change model numbers when published ratings or features are changed, or when

significant construction changes are made. However, some specifications of the products may be changed

without any notice. When in doubt, special model numbers may be assigned to fix or establish key

specifications for your application on your request. Please consult with your OMRON representative at any

time to confirm actual specifications of purchased products.

DIMENSIONS AND WEIGHTS

Dimensions and weights are nominal and are not to be used for manufacturing purposes, even when

tolerances are shown.

PERFORMANCE DATA

Performance data given in this manual is provided as a guide for the user in determining suitability and does

not constitute a warranty. It may represent the result of OMRON’s test conditions, and the users must

correlate it to actual application requirements. Actual performance is subject to the OMRON Warranty and

Limitations of Liability.

ERRORS AND OMISSIONS

The information in this manual has been carefully checked and is believed to be accurate; however, no

responsibility is assumed for clerical, typographical, or proofreading errors, or omissions.

14

CP1E CPU Unit Instructions Reference Manual(W483)

Page 18

Safety Precautions

Definition of Precautionary Information

The following notation is used in this manual to provide precautions required to ensure safe usage of a

CP-series PLC. The safety precautions that are provided are extremely important to safety. Always read

and heed the information provided in all safety precautions.

Indicates an imminently hazardous situation which,

WARNING

Caution

Precautions for Safe Use

Indicates precautions on what to do and what not to do to ensure using the product safely.

Precautions for Correct Use

Indicates precautions on what to do and what not to do to ensure proper operation

and performance.

if not avoided, will result in death or serious injury.

Additionally, there may be severe property damage.

Indicates a potentially hazardous situation which,

if not avoided, may result in minor or moderate

injury, or property damage.

Symbols

The triangle symbol indicates precautions (including

warnings). The specific operation is shown in the triangle

and explained in text. This example indicates a precaution for electric shock.

The circle and slash symbol indicates operations that you

must not do. The specific operation is shown in the circle

and explained in text.

The filled circle symbol indicates operations that you

must do. The specific operation is shown in the circle and

explained in text. This example shows a general precaution for something that you must do.

The triangle symbol indicates precautions (including

warnings). The specific operation is shown in the triangle

and explained in text. This example indicates a general

precaution.

The triangle symbol indicates precautions (including

warnings). The specific operation is shown in the triangle

and explained in text. This example indicates a precaution for hot surfaces.

CP1E CPU Unit Instructions Reference Manual(W483)

15

Page 19

CautionCaution

Be sure to sufficiently confirm the safety at the destination when you transfer

the program or I/O memory or perform procedures to change the I/O memory.

Devices connected to PLC outputs may incorrectly operate regardless of the operating mode of the CPU Unit.

With an E-type CPU Unit or with an N/NA-type CPU Unit without a Battery, the contents of the DM Area (D) *, Holding Area (H), the Counter Present Values (C), the status of Counter Completion Flags (C), and the status of bits in the Auxiliary Area (A)

related to clock functions may be unstable when the power supply is turned ON.

*This does not apply to areas backed up to EEPROM using the DM backup function.

If the DM backup function is being used, be sure to use one of the following methods

for initialization.

1. Clearing All Areas to All Zeros

Select the Clear Held Memory (HR/DM/CNT) to Zero Check Box in the Startup

Data Read Area in the PLC Setup.

2. Clearing Specific Areas to All Zeros or Initializing to Specific Values

Make the settings from a ladder program.

If the data is not initialized, the unit or device may operate unexpectedly because of

unstable data.

Execute online edit only after confirming that no adverse effects will be caused

by extending the cycle time.

Otherwise, the input signals may not be readable.

The DM Area (D), Holding Area (H), Counter Completion Flags (C), and Counter

Present Values (C) will be held by the Battery if a Battery is mounted in a CP1EN/NAD- CPU Unit. When the battery voltage is low, however, I/O memory

areas that are held (including the DM, Holding, and Counter Areas) will be unstable.

The unit or device may operate unexpectedly because of unstable data.

Use the Battery Error Flag or other measures to stop outputs if external outputs are performed from a ladder program based on the contents of the DM

Area or other I/O memory areas.

Sufficiently check safety if I/O bit status or present values are monitored in the

Ladder Section Pane or present values are monitored in the Watch Pane.

If bits are set, reset, force-set, or force-reset by inadvertently pressing a shortcut key,

devices connected to PLC outputs may operate incorrectly regardless of the operating mode.

16

CP1E CPU Unit Instructions Reference Manual(W483)

Page 20

Caution

Program so that the memory area of the start address is not exceeded when

using a word address or symbol for the offset.

For example, write the program so that processing is executed only when the indirect

specification does not cause the final address to exceed the memory area by using

an input comparison instruction or other instruction.

If an indirect specification causes the address to exceed the area of the start address,

the system will access data in other area, and unexpected operation may occur.

Set the temperature range according to the type of temperature sensor connected to the Unit.

Temperature data will not be converted correctly if the temperature range does not

match the sensor.

Do not set the temperature range to any values other than those for which temperature ranges are given in the following table.

An incorrect setting may cause operating errors.

CP1E CPU Unit Instructions Reference Manual(W483)

17

Page 21

Precautions for Safe Use

Observe the following precautions when using a CP-series PLC.

Handling

• To initialize the DM Area, back up the initial contents for the DM Area to backup memory using

one of the following methods.

• Set the number of words of the DM Area to be backed up starting with D0 in the Number of

CH of DM for backup Box in the Startup Data Read Area.

• Include programming to back up specified words in the DM Area to built-in EEPROM by turning ON A751.15 (DM Backup Save Start Bit).

• Check the ladder program for proper execution before actually running it on the Unit. Not checking

the program may result in an unexpected operation.

• The ladder program and parameter area data in the CP1E CPU Units are backed up in the built-in

EEPROM backup memory. The BKUP indicator will light on the front of the CPU Unit when the

backup operation is in progress. Do not turn OFF the power supply to the CPU Unit when the

BKUP indicator is lit. The data will not be backed up if power is turned OFF and a memory error

will occur the next time the power supply is turned ON.

• With a CP1E CPU Unit, data memory can be backed up to the built-in EEPROM backup memory.

The BKUP indicator will light on the front of the CPU Unit when backup is in progress. Do not turn

OFF the power supply to the CPU Unit when the BKUP indicator is lit. If the power is turned OFF

during a backup, the data will not be backed up and will not be transferred to the DM Area in RAM

the next time the power supply is turned ON.

• Before replacing the battery, supply power to the CPU Unit for at least 30 minutes and then complete battery replacement within 5 minutes. Memory data may be corrupted if this precaution is

not observed.

• The equipment may operate unexpectedly if inappropriate parameters are set. Even if the appropriate parameters are set, confirm that equipment will not be adversely affected before transferring the parameters to the CPU Unit.

• Before starting operation, confirm that the contents of the DM Area is correct.

• After replacing the CPU Unit, make sure that the required data for the DM Area, Holding Area, and

other memory areas has been transferred to the new CPU Unit before restarting operation.

• Do not attempt to disassemble, repair, or modify any Units. Any attempt to do so may result in malfunction, fire, or electric shock.

• Confirm that no adverse effect will occur in the system before attempting any of the following. Not

doing so may result in an unexpected operation.

• Changing the operating mode of the PLC (including the setting of the startup operating mode).

• Force-setting/force-resetting any bit in memory.

• Changing the present value of any word or any set value in memory.

18

External Circuits

• Always configure the external circuits to turn ON power to the PLC before turning ON power to the

control system. If the PLC power supply is turned ON after the control power supply, temporary

errors may result in control system signals because the output terminals on DC Output Units and

other Units will momentarily turn ON when power is turned ON to the PLC.

• Fail-safe measures must be taken by the customer to ensure safety in the event that outputs from

output terminals remain ON as a result of internal circuit failures, which can occur in relays, transistors, and other elements.

• If the I/O Hold Bit is turned ON, the outputs from the PLC will not be turned OFF and will maintain

their previous status when the PLC is switched from RUN or MONITOR mode to PROGRAM mode.

Make sure that the external loads will not produce dangerous conditions when this occurs. (When

operation stops for a fatal error, including those produced with the FALS instruction, all outputs from

PLC will be turned OFF and only the internal output status in the CPU Unit will be maintained.)

CP1E CPU Unit Instructions Reference Manual(W483)

Page 22

Regulations and Standards

Trademarks

SYSMAC is a registered trademark for Programmable Controllers made by OMRON Corporation.

CX-One is a registered trademark for Programming Software made by OMRON Corporation.

Windows is a registered trademark of Microsoft Corporation.

Other system names and product names in this document are the trademarks or registered trademarks

of their respective companies.

CP1E CPU Unit Instructions Reference Manual(W483)

19

Page 23

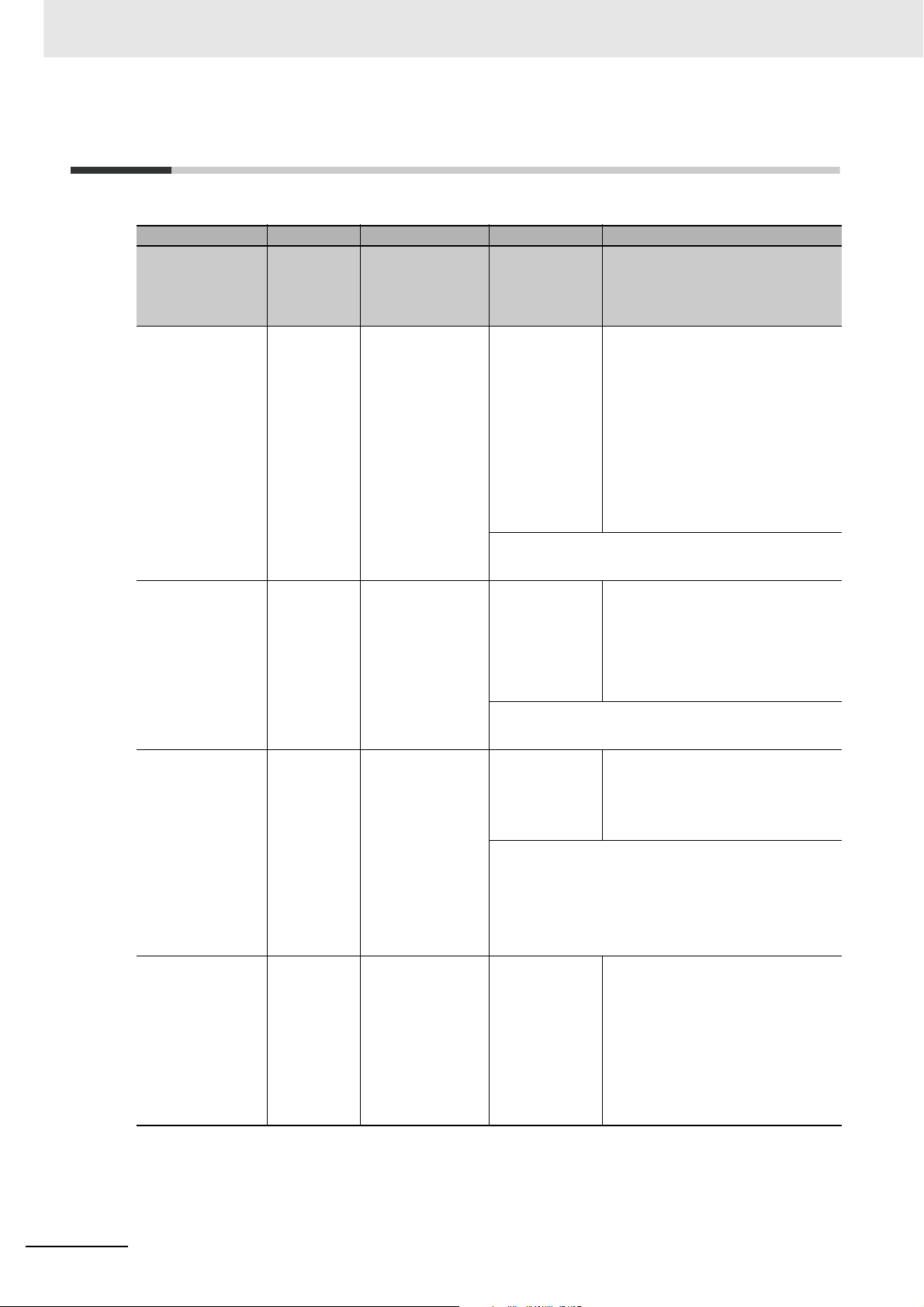

Related Manuals

The following manuals are related to the CP1E. Use them together with this manual.

Manual name Cat. No. Model numbers Application Contents

SYSMAC CP Series

CP1E CPU Unit Instructions Reference Manual

(this manual)

SYSMAC CP Series

CP1E CPU Unit Software User’s Manual

SYSMAC CP Series

CP1E CPU Unit Hardware User’s Manual

CS/CJ/CP/NSJ Series

Communications Commands Reference Manual

SYSMAC CP Series

CP1L/CP1E CPU Unit

Introduction Manual

W483 CP1E-ED-

W480 CP1E-ED-

W479 CP1E-ED-

W342 CS1G/H-CPUH

W461

CP1E-ND-

CP1E-NAD-

CP1E-ND-

CP1E-NAD-

CP1E-ND-

CP1E-NAD-

CS1G/H-CPU-V1

CS1D-CPUH

CS1D-CPUS

CS1W-SCU

1W-SCB-V1

CS

CJ1G/H-CPUH

CJ1G-CPUP

CJ1M-CPU

CJ1G-CPU

CJ1W-SCU-V1

CP1L-L10D-

CP1L-L14D-

CP1L-L20D-

CP1L-M30D-

CP1L-M40D-

CP1L-M60D-

CP1E-ED-

CP1E-ND-

CP1E-NAD-

-V1

To learn programming instructions in

detail

To learn the software

specifications of the

CP1E PLCs

Use this manual together with the CP1E CPU Unit Hardware User’s

Manual (Cat. No. W479) and Instructions Reference Manual (Cat. No.

W483).

To learn the hardware specifications

of the CP1E PLCs

Use this manual together with the CP1E CPU Unit Software User’s

Manual (Cat. No. W480) and Instructions Reference Manual (Cat. No.

W483).

To learn communications commands for

CS/CJ/CP/NSJseries Controllers in

detail

Note This manual describes commands addressed to CPU Units. It

does not cover commands addressed to other Units or ports (e.g.,

serial communications ports on CPU Units, communications ports

on Serial Communications Units/Boards, and other Communications Units).

To learn the basic

setup methods of the

CP1L/CP1E PLCs

Describes each programming instruction in

detail.

When programming, use this manual together

with the CP1E CPU Unit Software User’s Manual (Cat. No. W480).

Describes the following information for CP1E

PLCs.

• CPU Unit operation

• Internal memory

• Programming

• Settings

• CPU Unit built-in functions

• Interrupts

• High-speed counter inputs

• Pulse outputs

• Serial communications

• Other functions

Describes the following information for CP1E

PLCs.

• Overview and features

• Basic system configuration

• Part names and functions

• Installation and settings

• Troubleshooting

Describes

1) C-mode commands and

2) FINS commands in detail.

Read this manual for details on C-mode and

FINS commands addressed to CPU Units.

Describes the following information for

CP1L/CP1E PLCs.

• Basic configuration and component names

• Mounting and wiring

• Programming, data transfer, and debugging

using the CX-Programmer

• Application program examples

20

CP1E CPU Unit Instructions Reference Manual(W483)

Page 24

Page 25

Summary of Instructions

This section provides a summary of instructions used with a CP1E CPU Unit.

1-1 Summary of Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-2

1

CP1E CPU Unit Instructions Reference Manual(W483)

1-1

Page 26

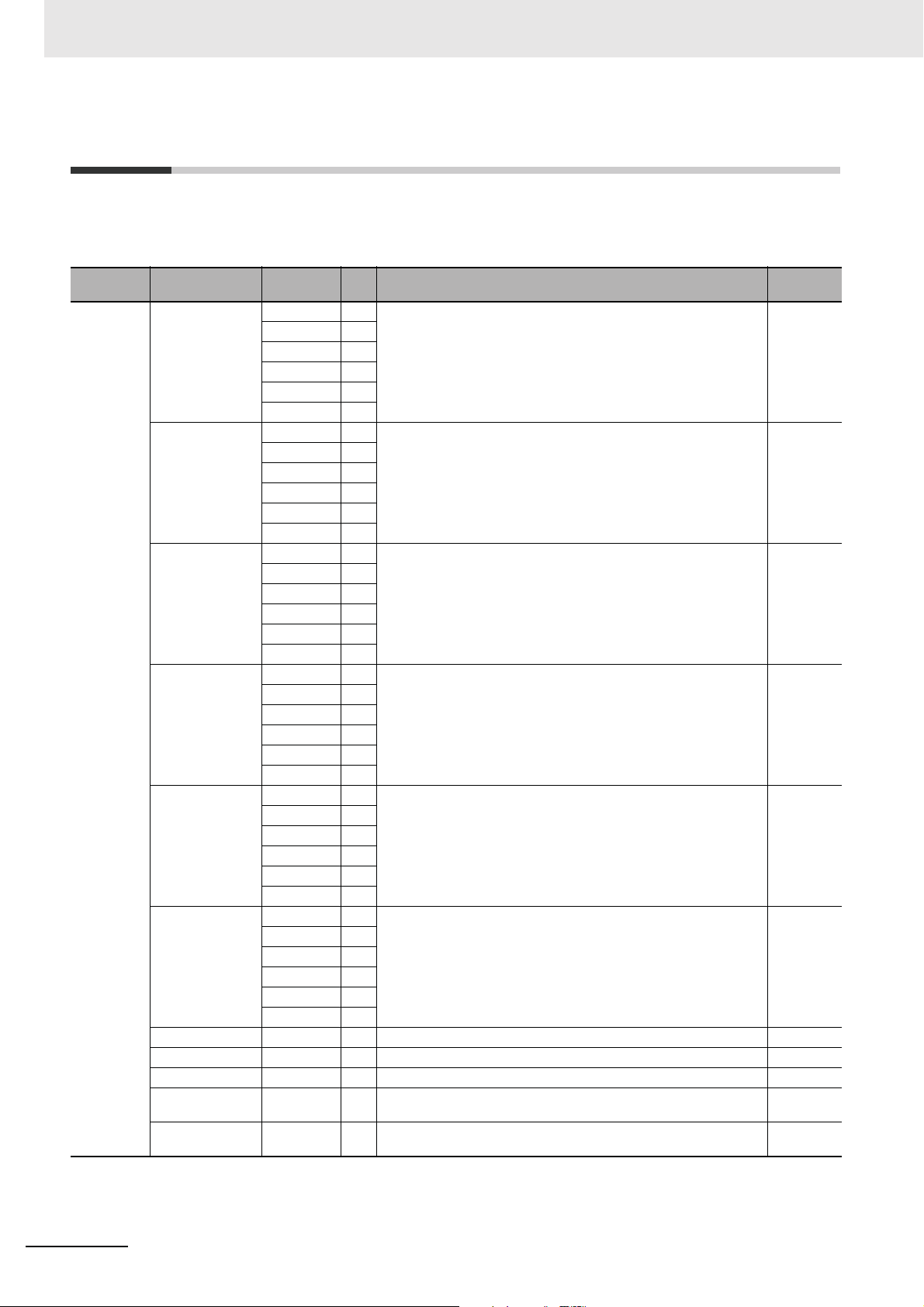

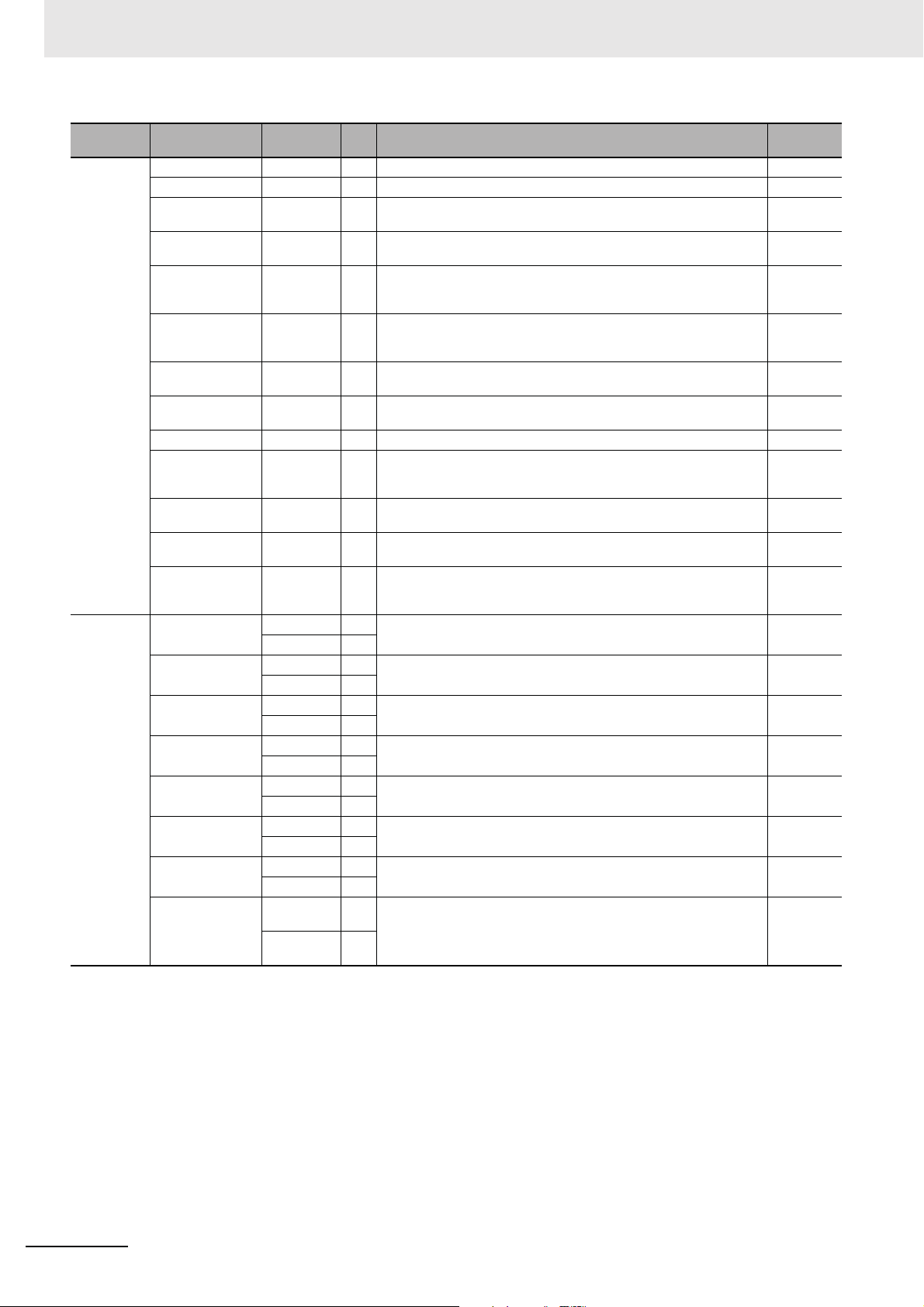

1 Summary of Instructions

1-1 Summary of Instructions

There are 200 types of instructions can be used by CP1E.

The following table lists the instructions by function. Refer to the reference pages for the

detail of each instruction.

Instrucion

Typ e

Sequence

Input Instructions

Instruction Mnemonic

LOAD LD

@LD

%LD

!LD

!@LD

!%LD

LOAD NOT LD NOT

@LD NOT

%LD NOT

!LD NOT

!@LD NOT

!%LD NOT

AND AND

@AND

%AND

!AND

!@AND

!%AND

AND NOT AND NOT

@AND NOT

%AND NOT

!AND NOT

!@AND NOT

!%AND NOT

OR OR

@OR

%OR

!OR

!@OR

!%OR

OR NOT OR NOT

@OR NOT

%OR NOT

!OR NOT

!@OR NOT

!%OR NOT

AND LOAD AND LD

OR LOAD OR LD

NOT NOT 520 Reverses the execution condition. 2-16

CONDITION ON UP 521 UP(521) turns ON the execution condition for one cycle when the execution

CONDITION OFF DOWN 522 DOWN(522) turns ON the execution condition for one cycle when the execution

FUN

No.

-

Indicates a logical start and creates an ON/OFF execution condition based on

the ON/OFF status of the specified operand bit.

-

-

-

-

-

-

Indicates a logical start and creates an ON/OFF execution condition based on

the reverse of the ON/OFF status of the specified operand bit.

-

-

-

-

-

-

Takes a logical AND of the status of the specified operand bit and the current

execution condition.

-

-

-

-

-

-

Reverses the status of the specified operand bit and takes a logical AND with

the current execution condition.

-

-

-

-

-

-

Takes a logical OR of the ON/OFF status of the specified operand bit and the

current execution condition.

-

-

-

-

-

-

Reverses the status of the specified bit and takes a logical OR with the current

execution condition.

-

-

-

-

-

-

Takes a logical AND between logic blocks. 2-13

-

Takes a logical OR between logic blocks. 2-13

condition goes from OFF to ON.

condition goes from ON to OFF.

Function Page

2-7

2-7

2-9

2-9

2-11

2-11

2-17

2-17

1-2

CP1E CPU Unit Instructions Reference Manual(W483)

Page 27

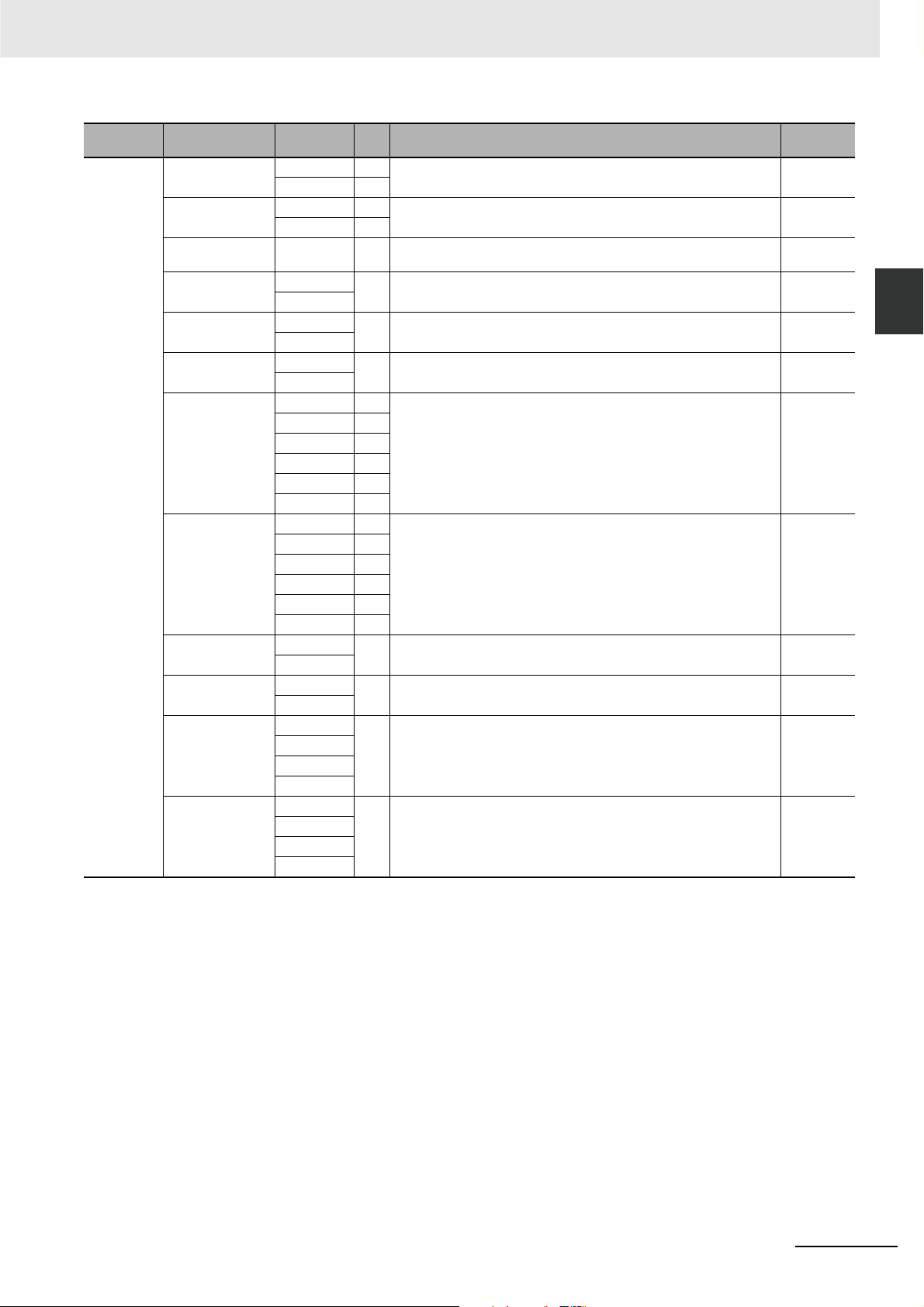

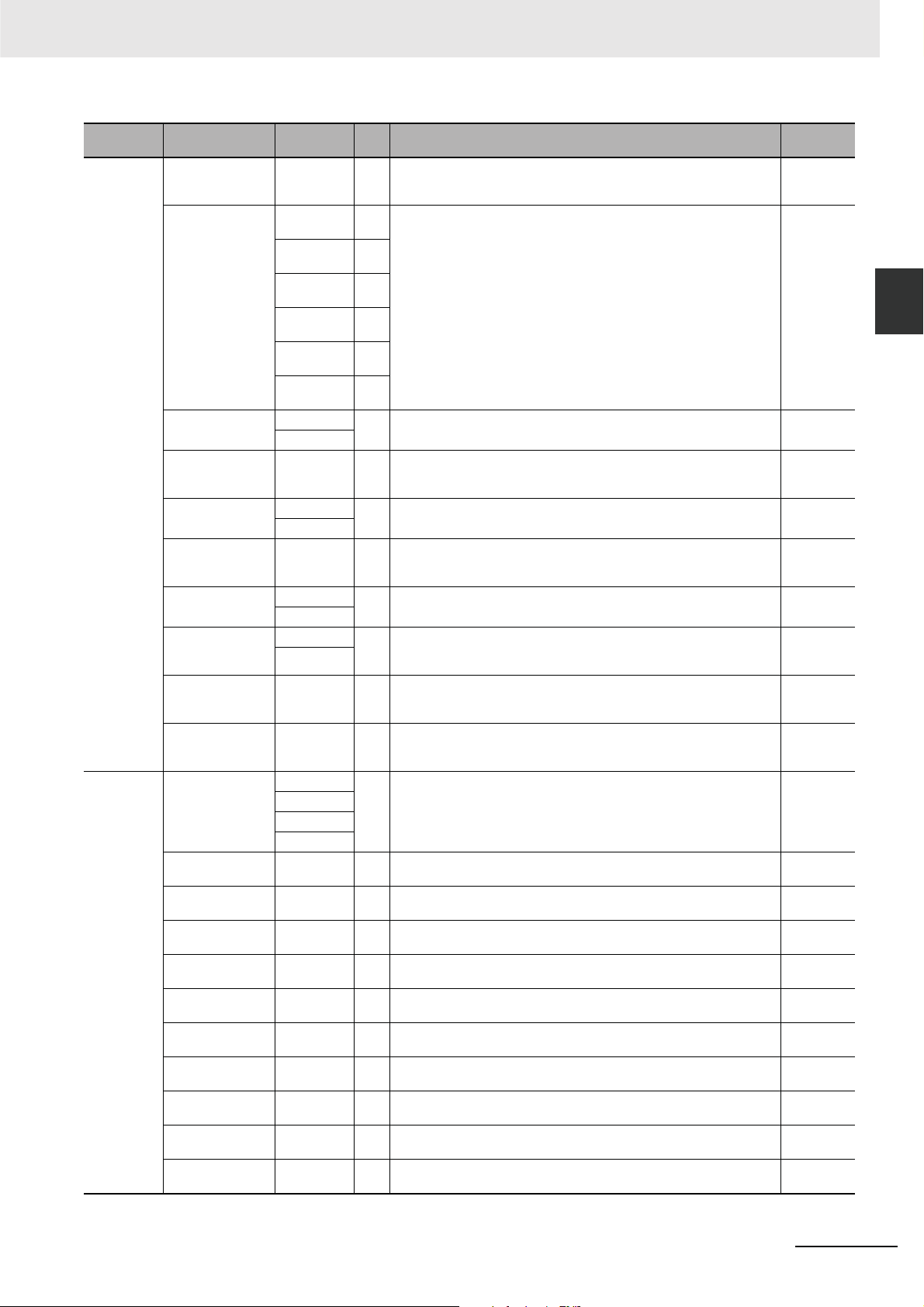

1 Summary of Instructions

1-1 Summary of Instructions

Instrucion

Type

Sequence

Output

Instructions

Instruction Mnemonic

OUTPUT OUT

!OUT

OUTPUT NOT OUT NOT

!OUT NOT

TR Bits TR

KEEP KEEP 011 Operates as a latching relay. 2-21

!KEEP

DIFFERENTIATEUPDIFU 013 DIFU(013) turns the designated bit ON for one cycle when the execution condi-

!DIFU

DIFFERENTIATE

DOWN

SET SET

RESET RSET

MULTIPLE BIT SET SETA 530 SETA(530) turns ON the specified number of consecutive bits. 2-31

MULTIPLE BIT

RESET

SINGLE BIT SET SETB 532 SETB(532) turns ON the specified bit in the specified word when the execution

SINGLE BIT RESET RSTB 533 RSTB(533) turns OFF the specified bit in the specified word when the execu-

DIFD 014 DIFD(014) turns the designated bit ON for one cycle when the execution condi-

!DIFD

@SET

%SET

!SET

!@SET

!%SET

@RSET

%RSET

!RSET

!@RSET

!%RSET

@SETA

RSTA 531 RSTA(531) turns OFF the specified number of consecutive bits. 2-31

@RSTA

@SETB

!SETB

!@SETB

@RSTB

!RSTB

!@RSTB

FUN

No.

-

Outputs the result (execution condition) of the logical processing to the specified bit.

-

-

Reverses the result (execution condition) of the logical processing, and outputs

it to the specified bit.

-

-

TR bits are used to temporarily retain the ON/OFF status of execution conditions in a program when programming in mnemonic code.

tion goes from OFF to ON (rising edge).

tion goes from ON to OFF (falling edge).

-

SET turns the operand bit ON when the execution condition is ON. 2-29

-

-

-

-

-

-

RSET turns the operand bit OFF when the execution condition is ON. 2-29

-

-

-

-

-

condition is ON.

Unlike the SET instruction, SETB(532) can be used to set a bit in a DM word.

tion condition is ON.

Unlike the RSET instruction, RSTB(533) can be used to reset a bit in a DM

word.

Function Page

2-18

2-18

2-20

2-25

2-27

2-33

2-33

1

CP1E CPU Unit Instructions Reference Manual(W483)

1-3

Page 28

1 Summary of Instructions

Instrucion

Typ e

Sequence

Control

Instructions

Timer and

Counter

Instructions

Instruction Mnemonic

END END 001 Indicates the end of a program. 2-38

NO OPERATION NOP 000 This instruction has no function. (No processing is performed for NOP(000).) 2-39

INTERLOCK IL 002 Interlocks all outputs between IL(002) and ILC(003) when the execution condi-

INTERLOCK

CLEAR

MULTI-INTERLOCK

DIFFERENTIATION

HOLD

MULTI-INTERLOCK

DIFFERENTIATION

RELEASE

MULTI-INTERLOCK

CLEAR

JUMP JMP 004 When the execution condition for JMP(004) is OFF, program execution jumps

JUMP END JME 005 Indicates the end of a jump initiated by JMP(004) or CJP(510). 2-53

CONDITIONAL

JUMP

FOR LOOP FOR 512 The instructions between FOR(512) and NEXT(513) are repeated a specified

NEXT LOOP NEXT 513 The instructions between FOR(512) and NEXT(513) are repeated a specified

BREAK LOOP BREAK 514 Programmed in a FOR-NEXT loop to cancel the execution of the loop for a

HUNDRED-MS

TIMER

TEN-MS TIMER TIMH 015 TIMH(015)/TIMHX(551) operates a decrementing timer with units of 10-ms. 2-69

ONE-MS TIMER TMHH 540 TMHH(540)/TMHHX(552) operates a decrementing timer with units of 1-ms. 2-72

ACCUMULATIVE

TIMER

LONG TIMER TIML 542 TIML(542)/TIMLX(553) operates a decrementing timer with units of 0.1-s. 2-77

COUNTER CNT

REVERSIBLE

COUNTER

RESET TIMER/

COUNTER

ILC 003 All outputs between IL(002) and ILC(003) are interlocked when the execution

MILH 517 When the execution condition for MILH(517) is OFF, the outputs for all instruc-

MILR 518 When the execution condition for MILR(518) is OFF, the outputs for all instruc-

MILC 519 Clears an interlock started by an MILH(517) or MILR(518) with the same inter-

CJP 510 The operation of CJP(510) is the basically the opposite of JMP(004). When the

TIM

TIMX 550

TIMHX 551

TMHHX 552

TTIM 087 TTIM(087)/TTIMX(555) operates an incrementing timer with units of 0.1-s. 2-74

TTIMX 555

TIMLX 553

CNTX 546

CNTR 012 CNTR(012)/CNTRX(548) operates a reversible counter. 2-83

CNTRX 548

CNR/

@CNR

CNRX/

@CNRX

FUN

No.

tion for IL(002) is OFF.

condition for IL(002) is OFF.

tions between that MILH(517) instruction and the next MILC(519) instruction

are interlocked.

tions between that MILR(518) instruction and the next MILC(519) instruction

are interlocked.

lock number.

directly to the first JME(005) in the program with the same jump number.

execution condition for CJP(510) is ON, program execution jumps directly to the

first JME(005) in the program with the same jump number.

number of times.

number of times.

given execution condition. The remaining instructions in the loop are processed

as NOP(000) instructions.

-

TIM/TIMX(550) operates a decrementing timer with units of 0.1-s. 2-66

-

CNT/CNTX(546) operates a decrementing counter. 2-80

545 CNR(545)/CNRX(547) resets the timers or counters within the specified range

of timer or counter numbers.

547

Function Page

2-40

2-40

2-44

2-44

2-44

2-53

2-53

2-56

2-56

2-59

2-86

1-4

CP1E CPU Unit Instructions Reference Manual(W483)

Page 29

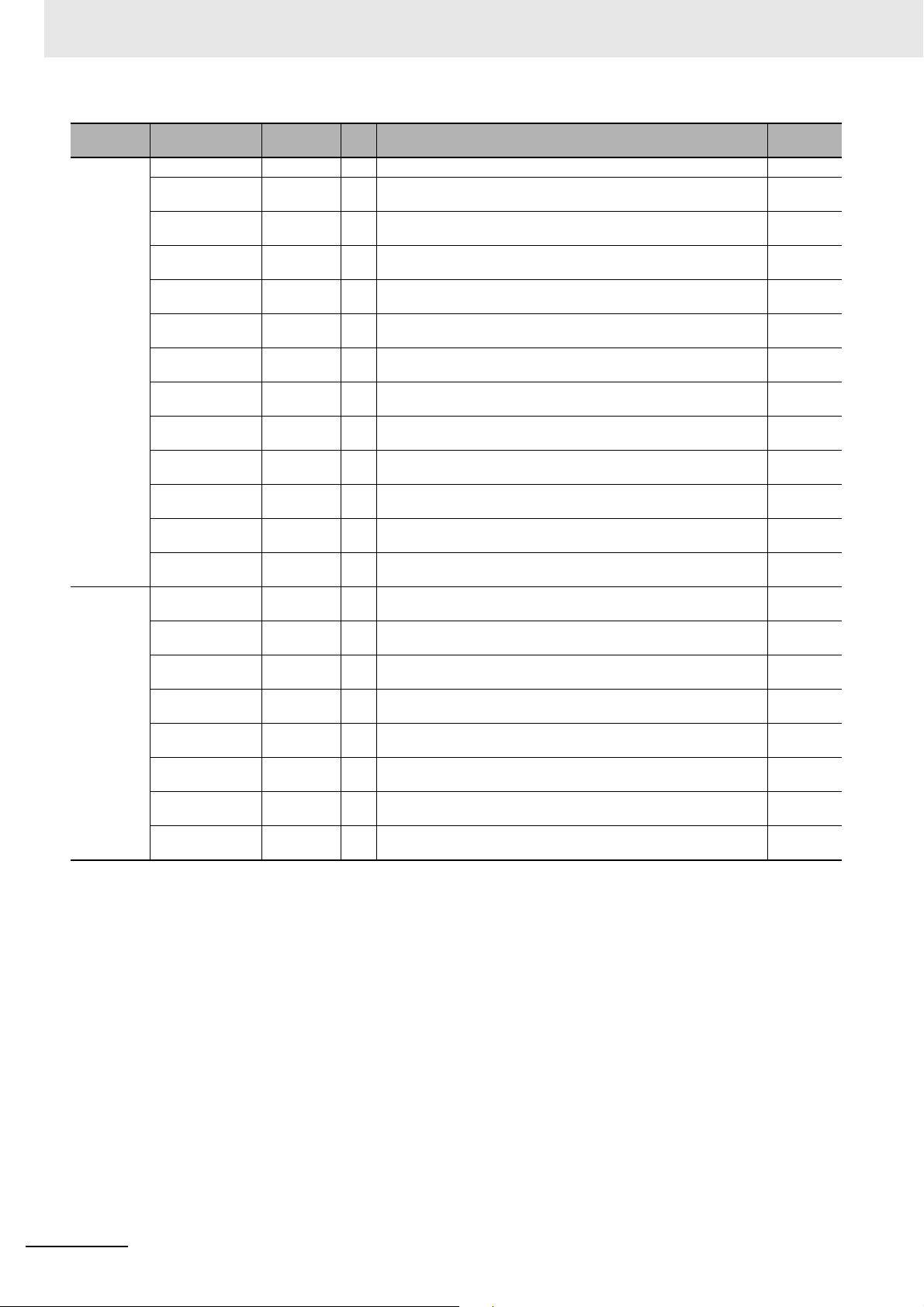

1 Summary of Instructions

1-1 Summary of Instructions

Instrucion

Type

Comparison

Instructions

Data Movement Instructions

Instruction Mnemonic

Symbol Comparison = , <> , < , <= ,

Time Comparison LD, AND,

UNSIGNED

COMPARE

DOUBLE

UNSIGNED

COMPARE

SIGNED BINARY

COMPARE

DOUBLE SIGNED

BINARY COMPARE

TABLE COMPARE TCMP 085 Compares the source data to the contents of 16 words and turns ON the corre-

UNSIGNED BLOCK

COMPARE

AREA RANGE

COMPARE

DOUBLE AREA

RANGE COMPARE

MOVE MOV 021 Transfers a word of data to the specified word. 2-108

DOUBLE MOVE MOVL/

MOVE NOT MVN/

MOVE BIT MOVB/

MOVE DIGIT MOVD/

MULTIPLE BIT

TRANSFER

BLOCK TRANSFER XFER/

BLOCK SET BSET/

DATA EXCHANGE XCHG/

SINGLE WORD

DISTRIBUTE

DATA COLLECT COLL/

> , >=

OR+=DT

LD, AND,

OR+<>DT

LD, AND,

OR+<DT

LD, AND,

OR+<=DT

LD, AND,

OR+>DT

LD, AND,

OR+>=DT

CMP 020 Compares two unsigned binary values (constants and/or the contents of speci-

!CMP

CMPL 060 Compares two double unsigned binary values (constants and/or the contents of

CPS 114 Compares two signed binary values (constants and/or the contents of specified

!CPS

CPSL 115 Compares two double signed binary values (constants and/or the contents of

@TCMP

BCMP 068 Compares the source data to 16 ranges (defined by 16 lower limits and 16

@BCMP

ZCP 088 Compares the 16-bit unsigned binary value in CD (word contents or constant)

ZCPL 116 Compares the 32-bit unsigned binary value in CD and CD+1 (word contents or

@MOV

!MOV

!@MOV

@MOVL

@MVN

@MOVB

@MOVD

XFRB/

@XFRB

@XFER

@BSET

@XCHG

DIST/

@DIST

@COLL

FUN

No.

300

Symbol comparison instructions compare two values and create an ON execu-

∼

tion condition when the comparison condition is true.

328

341 Time comparison instructions compare two BCD time values and create an ON

execution condition when the comparison condition is true.

342

343

344

345

346

fied words) and outputs the result to the Arithmetic Flags in the Auxiliary Area.

specified words) and outputs the result to the Arithmetic Flags in the Auxiliary

Area.

words) and outputs the result to the Arithmetic Flags in the Auxiliary Area.

specified words) and outputs the result to the Arithmetic Flags in the Auxiliary

Area.

sponding bit in the result word when the contents are equal.

upper limits) and turns ON the corresponding bit in the result word when the

source data is within the range.

to the range defined by LL and UL and outputs the results to the Arithmetic

Flags in the Auxiliary Area.

constant) to the range defined by LL and UL and outputs the results to the

Arithmetic Flags in the Auxiliary Area.

498 Transfers two words of data to the specified words. 2-108

022 Transfers the complement of a word of data to the specified word. 2-108

082 Transfers the specified bit. 2-111

083 Transfers the specified digit or digits. (Each digit is made up of 4 bits.) 2-113

Transfers the specified number of consecutive bits. 2-115

062

070 Transfers the specified number of consecutive words. 2-117

071 Copies the same word to a range of consecutive words. 2-119

073 Exchanges the contents of the two specified words. 2-121

080 Transfers the source word to a destination word calculated by adding an offset

value to the base address.

081 Transfers the source word (calculated by adding an offset value to the base

address) to the destination word.

Function Page

2-88

2-91

2-95

2-95

2-98

2-98

2-101

2-103

2-105

2-105

2-123

2-125

1

CP1E CPU Unit Instructions Reference Manual(W483)

1-5

Page 30

1 Summary of Instructions

Instrucion

Typ e

Data Shift

Instructions

Increment/

Decrement

Instructions

Instruction Mnemonic

SHIFT REGISTER SFT 010 Operates a shift register. 2-127

REVERSIBLE

SHIFT REGISTER

WORD SHIFT WSFT/

ARITHMETIC

SHIFT LEFT

ARITHMETIC

SHIFT RIGHT

ROTATE LEFT ROL/

ROTATE RIGHT ROR/

ONE DIGIT SHIFT

LEFT

ONE DIGIT SHIFT

RIGHT

SHIFT N-BITS LEFT NASL/

DOUBLE SHIFT

N-BITS LEFT

SHIFT N-BITS

RIGHT

DOUBLE SHIFT

N-BITS RIGHT

INCREMENT

BINARY

DOUBLE INCREMENT BINARY

DECREMENT

BINARY

DOUBLE DECREMENT BINARY

INCREMENT BCD ++B/

DOUBLE INCREMENT BCD

DECREMENT BCD

DOUBLE DECREMENT BCD

SFTR/

@SFTR

@WSFT

ASL/

@ASL

ASR/

@ASR

@ROL

@ROR

SLD/

@SLD

SRD/

@SRD

@NASL

NSLL/

@NSLL

NASR/

@NASR

NSRL/

@NSRL

++/

@++

++L/

@++L

--

/

@

--

--

L/

@

--

L

@++B

++BL/

@++BL

--

B/

@

--

B

--

BL/

@

--

BL

FUN

No.

084 Creates a shift register that shifts data to either the right or the left. 2-129

016 Shifts data between St and E in word units. 2-131

025

Shifts the contents of Wd one bit to the left.

026 Shifts the contents of Wd one bit to the right. 2-134

027 Shifts all Wd bits one bit to the left including the Carry Flag (CY). 2-135

028 Shifts all Wd bits one bit to the right including the Carry Flag (CY). 2-137

074 Shifts data by one digit (4 bits) to the left. 2-139

075 Shifts data by one digit (4 bits) to the right. 2-139

580 Shifts the specified 16 bits of word data to the left by the specified number of

bits.

582 Shifts the specified 32 bits of word data to the left by the specified number of

bits.

581 Shifts the specified 16 bits of word data to the right by the specified number of

bits.

583 Shifts the specified 32 bits of word data to the right by the specified number of

bits.

590 Increments the 4-digit hexadecimal content of the specified word by 1. 2-147

591 Increments the 8-digit hexadecimal content of the specified words by 1. 2-147

592 Decrements the 4-digit hexadecimal content of the specified word by 1. 2-150

593 Decrements the 8-digit hexadecimal content of the specified words by 1. 2-150

594 Increments the 4-digit BCD content of the specified word by 1. 2-153

595 Increments the 8-digit BCD content of the specified words by 1. 2-153

596 Decrements the 4-digit BCD content of the specified word by 1. 2-156

597 Decrements the 8-digit BCD content of the specified words by 1. 2-156

Function Page

2-133

2-141

2-141

2-144

2-144

1-6

CP1E CPU Unit Instructions Reference Manual(W483)

Page 31

1 Summary of Instructions

1-1 Summary of Instructions

Instrucion

Type

Symbol Math

Instructions

Instruction Mnemonic

SIGNED BINARY

ADD WITHOUT

CARRY

DOUBLE SIGNED

BINARY ADD

WITHOUT CARRY

SIGNED BINARY

ADD WITH CARRY

DOUBLE SIGNED

BINARY ADD WITH

CARRY

BCD ADD

WITHOUT CARRY

DOUBLE BCD ADD

WITHOUT CARRY

BCD ADD WITH

CARRY

DOUBLE BCD ADD

WITH CARRY

SIGNED BINARY

SUBTRACT

WITHOUT CARRY

DOUBLE SIGNED

BINARY

SUBTRACT WITHOUT CARRY

SIGNED BINARY

SUBTRACT WITH

CARRY

DOUBLE SIGNED

BINARY WITH

CARRY

BCD SUBTRACT

WITHOUT CARRY

DOUBLE BCD

SUBTRACT

WITHOUT CARRY

BCD SUBTRACT

WITH CARRY

DOUBLE BCD

SUBTRACT

WITH CARRY

SIGNED BINARY

MULTIPLY

DOUBLE SIGNED

BINARY MULTIPLY

BCD MULTIPLY ∗B/

DOUBLE BCD

MULTIPLY

SIGNED BINARY

DIVIDE

DOUBLE SIGNED

BINARY DIVIDE

BCD DIVIDE /B

DOUBLE BCD

DIVIDE

+/

@+

+L/

@+L

+C/

@+C

+CL/

@+CL

+B/

@+B

+BL/

@+BL

+BC/

@+BC

+BCL/

@+BCL

@

@

@

@

@

@

@

@

∗/

@∗

∗L/

@∗L

@∗B

∗BL/

@∗BL

/

@/

/L

@/L

@/B

/BL

@/BL

/

-

L/

-

L

C/

-

C

CL/

-

CL

B/

-

B

BL/

-

BL

BC/

-

BC

BCL/

-

BCL

FUN

No.

400 Adds 4-digit (single-word) hexadecimal data and/or constants. 2-158

401 Adds 8-digit (double-word) hexadecimal data and/or constants. 2-158

402 Adds 4-digit (single-word) hexadecimal data and/or constants with the Carry

Flag (CY).

403 Adds 8-digit (double-word) hexadecimal data and/or constants with the Carry

Flag (CY).

404 Adds 4-digit (single-word) BCD data and/or constants. 2-162

405 Adds 8-digit (double-word) BCD data and/or constants. 2-162

406 Adds 4-digit (single-word) BCD data and/or constants with the Carry Flag (CY). 2-164