Page 1

Cat. No. W480-E1-04

SYSMAC CP Series

CP1E-E@@D@-@

CP1E-N@@D@-@

CP1E-NA@@D@-@

CP1E CPU Unit Software

USER’S MANUAL

Page 2

Page 3

© OMRON, 2009

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form, or

by any means, mechanical, electronic, photocopying, recording, or otherwise, without the prior written permission of

OMRON.

No patent liability is assumed with respect to the use of the information contained herein. Moreover, because OMRON is constantly striving to improve its high-quality products, the information contained in this manual is subject to change without

notice. Every precaution has been taken in the preparation of this manual. Nevertheless, OMRON assumes no responsibility

for errors or omissions. Neither is any liability assumed for damages resulting from the use of the information contained in

this publication.

Page 4

SYSMAC CP Series

CP1E-E@@D@-@

CP1E-N@@D@-@

CP1E-NA@@D@-@

CP1E CPU Unit Software

User’s Manual

Revised June 2010

Page 5

Introduction

Thank you for purchasing a SYSMAC CP-series CP1E Programmable Controller.

This manual contains information required to use the CP1E. Read this manual completely and be sure

you understand the contents before attempting to use the CP1E.

Intended Audience

This manual is intended for the following personnel, who must also have knowledge of electrical systems (an electrical engineer or the equivalent).

• Personnel in charge of installing FA systems

• Personnel in charge of designing FA systems

• Personnel in charge of managing FA systems and facilities

Applicable Products

CP-series CP1E CPU Units

• Basic Models CP1E-ED-

A basic model of CPU Unit that support basic control applications using instructions such as

basic, movement, arithmetic, and comparison instructions.

• Application Models CP1E-N/NAD-

An application model of CPU Unit that supports connections to Programmable Terminals, inverters, and servo drives.

The CP Series is centered around the CP1H, CP1L, and CP1E CPU Units and is designed with the

same basic architecture as the CS and CJ Series.

Always use CP-series Expansion Units and CP-series Expansion I/O Units when expanding I/O

capacity. I/O words are allocated in the same way as for the CPM1A/CPM2A PLCs, i.e., using fixed

areas for inputs and outputs.

CP1E CPU Unit Software User’s Manual(W480)

1

Page 6

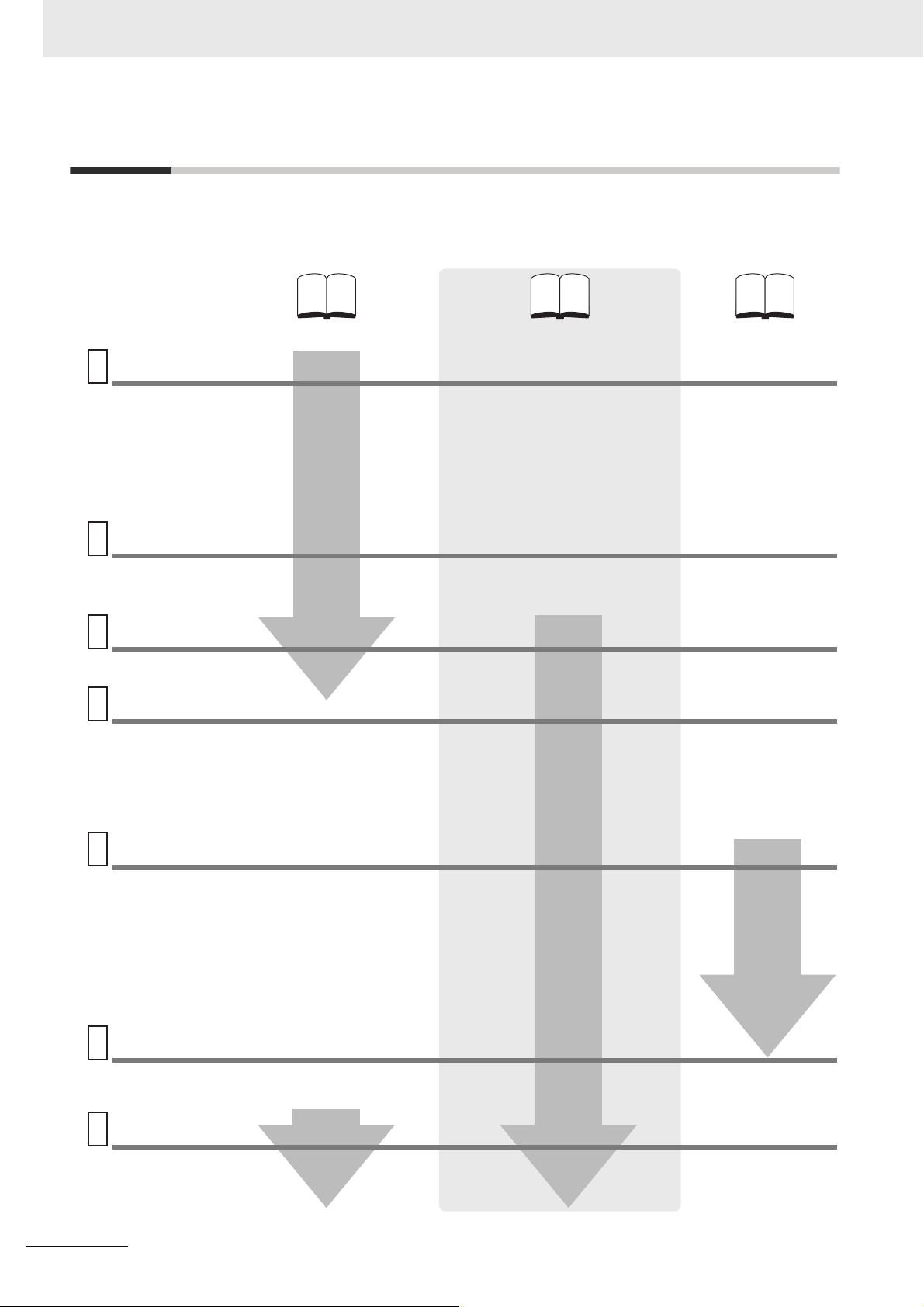

CP1E CPU Unit Manuals

Information on the CP1E CPU Units is provided in the following manuals.

Refer to the appropriate manual for the information that is required.

This Manual

Mounting and

1

Setting Hardware

2

Wiring

Connecting

3

Online to the PLC

4

Software Setup

CP1E CPU Unit Hardware

User’s Manual(Cat. No. W479)

· Names and specifications of the parts of all Units

· Basic system configuration for each CPU Unit

· Connection methods for Expansion I/O Units

and Expansion Units

· Wiring methods for the power supply

· Wiring methods between external I/O devices

and Expansion I/O Units or Expansion Units

Connecting Cables for CX-Programmer

Support Software

CP1E CPU Unit Software

User’s Manual(Cat. No. W480)

Procedures for connecting the

CX-Programmer Support Software

Software setting methods for the CPU

Units (PLC Setup)

CP1E CPU Unit Instructions

Reference Manual(Cat. No. W483)

5

Creating the Program

Checking and

6

Debugging Operation

Maintenance and

7

Troubleshooting

2

Error codes and remedies if a problem occurs

· Program types and basic information

· CPU Unit operation

· Internal memory

· Built-in CPU functions

· Settings

· Checking I/O wiring, setting the Auxiliary Area

settings, and performing trial operation

· Monitoring and debugging with the

CX-Programmer

CP1E CPU Unit Software User’s Manual(W480)

Detailed information on

programming instructions

Page 7

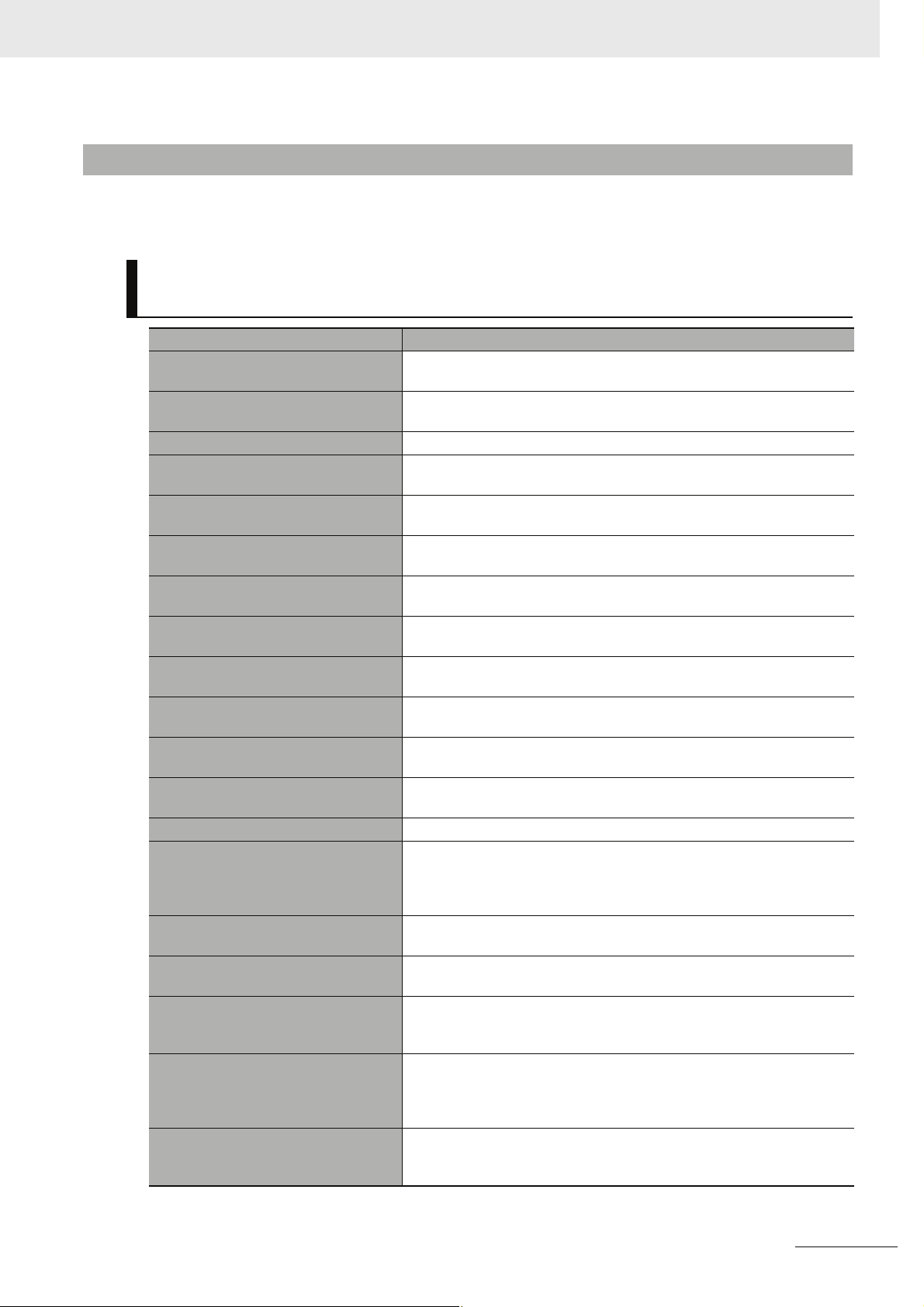

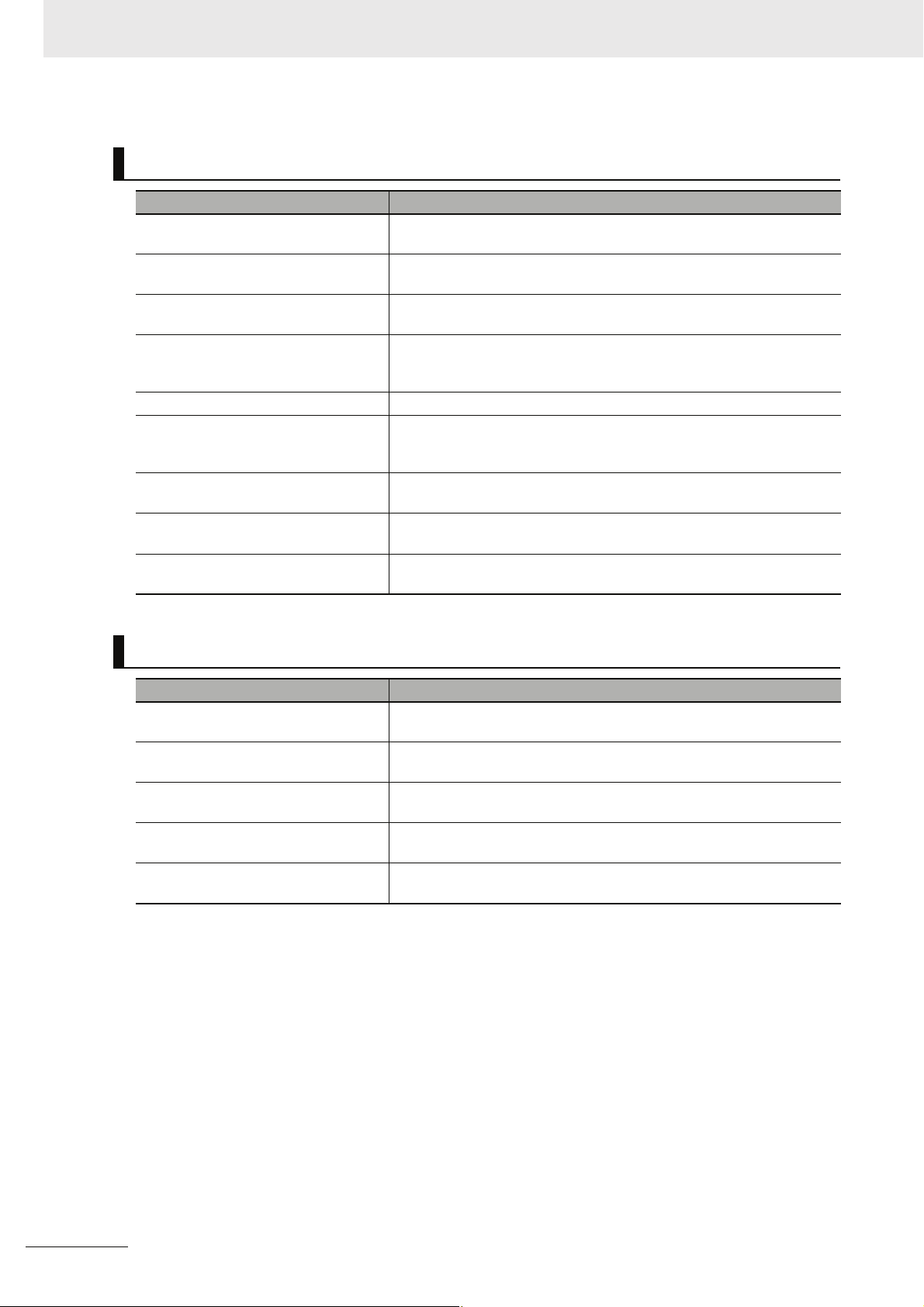

Manual Configuration

The CP1E CPU manuals are organized in the sections listed in the following tables. Refer to the appropriate section in the manuals as required.

CP1E CPU Unit Software User’s Manual (Cat. No. W480)

(This Manual)

Section Contents

Section 1 Overview This section gives an overview of the CP1E, describes its application

Section 2 CPU Unit Memory This section describes the types of internal memory in a CP1E CPU

Section 3 CPU Unit Operation This section describes the operation of a CP1E CPU Unit.

Section 4 Programming Concepts This section provides basic information on designing ladder programs

Section 5 I/O Memory This section describes the types of I/O memory areas in a CP1E CPU

Section 6 I/O Allocation This section describes I/O allocation used to exchange data between

Section 7 PLC Setup This section describes the PLC Setup, which are used to perform basic

Section 8 Overview and Allocation

of Built-in Functions

Section 9 Quick-response Inputs This section describes the quick-response inputs that can be used to

Section 10 Interrupts This section describes the interrupts that can be used with CP1E PLCs,

Section 11 High-speed Counters This section describes the high-speed counter inputs, high-speed

Section 12 Pulse Outputs This section describes positioning functions such as trapezoidal control,

Section 13 PWM Outputs This section describes the variable-duty-factor pulse (PWM) outputs.

Section 14 Serial Communications This section describes communications with Programmable Terminals

Section 15 Analog I/O Function This section describes the built-in analog function for NA-type CPU

Section 16 Built-in Functions This section describes PID temperature control, clock functions, DM

Section 17 Ethernet Option Board This section gives an overview of the Ethernet Option Board, describes

Section 18 Operating the Programming Device

Appendices The appendices provide lists of programming instructions, the Auxiliary

procedures.

Unit and the data that is stored.

for a CP1E CPU Unit.

Unit and the details.

the CP1E CPU Unit and other units.

settings for a CP1E CPU Unit.

This section lists the built-in functions and describes the overall application flow and the allocation of the functions.

read signals that are shorter than the cycle time.

including input interrupts and scheduled interrupts.

counter interrupts, and the frequency measurement function.

jogging, and origin searches.

(PTs) without using communications programming, no-protocol communications with general components, and connections with a ModbusRTU Easy Master, Serial PLC Link, and host computer.

Units.

backup functions, security functions.

its setting methods, I/O memory allocations, troubleshooting, how to

connect the CX-Programmer, and how to install an Ethernet network.

This section describes basic functions of the CX-Programmer, such as

using the CX-Programmer to write ladder programs to control the CP1E

CPU Unit, to transfer the programs to the CP1E CPU Unit, and to debug

the programs.

Area, cycle time response performance, PLC performance at power

interruptions.

CP1E CPU Unit Software User’s Manual(W480)

3

Page 8

CP1E CPU Unit Hardware User’s Manual (Cat. No. W479)

Section Contents

Section 1 Overview and Specifications

Section 2 Basic System Configuration and Devices

Section 3 Part Names and Functions This section describes the part names and functions of the CPU Unit,

Section 4 Programming Device This section describes the features of the CX-Programmer used for pro-

Section 5 Installation and Wiring This section describes how to install and wire CP1E Units.

Section 6 Troubleshooting This section describes how to troubleshoot problems that may occur

Section 7 Maintenance and Inspection

Section 8 Using Expansion Units

and Expansion I/O Units

Appendices The appendices provide information on dimensions, wiring diagrams,

This section gives an overview of the CP1E, describes its features, and

provides its specifications.

This section describes the basic system configuration and unit models

of the CP1E.

Expansion I/O Units, and Expansion Units in a CP1E PLC .

gramming and debugging PLCs, as well as how to connect the PLC with

the Programming Device by USB.

with a CP1E PLC, including the error indications provided by the CP1E

Units.

This section describes periodic inspections, the service life of the Battery, and how to replace the Battery.

This section describes application methods for Expansion Units.

and wiring serial communications for the CP1E.

CP1E CPU Unit Instructions Reference Manual (Cat. No. W483)

Section Contents

Section 1 Summary of Instructions This section provides a summary of instructions used with a CP1E CPU

Unit.

Section 2 Instruction This section describes the functions, operands and sample programs of

the instructions that are supported by a CP1E CPU Unit.

Section 3 Instruction Execution

Times and Number of Steps

Section 4 Monitoring and

Computing the Cycle Time

Appendices The appendices provide a list of instructions by Mnemonic and ASCII

This section provides the execution times for all instructions used with a

CP1E CPU Unit.

This section describes how to monitor and calculate the cycle time of a

CP1E CPU Unit that can be used in the programs.

code table for the CP1E CPU Unit.

4

CP1E CPU Unit Software User’s Manual(W480)

Page 9

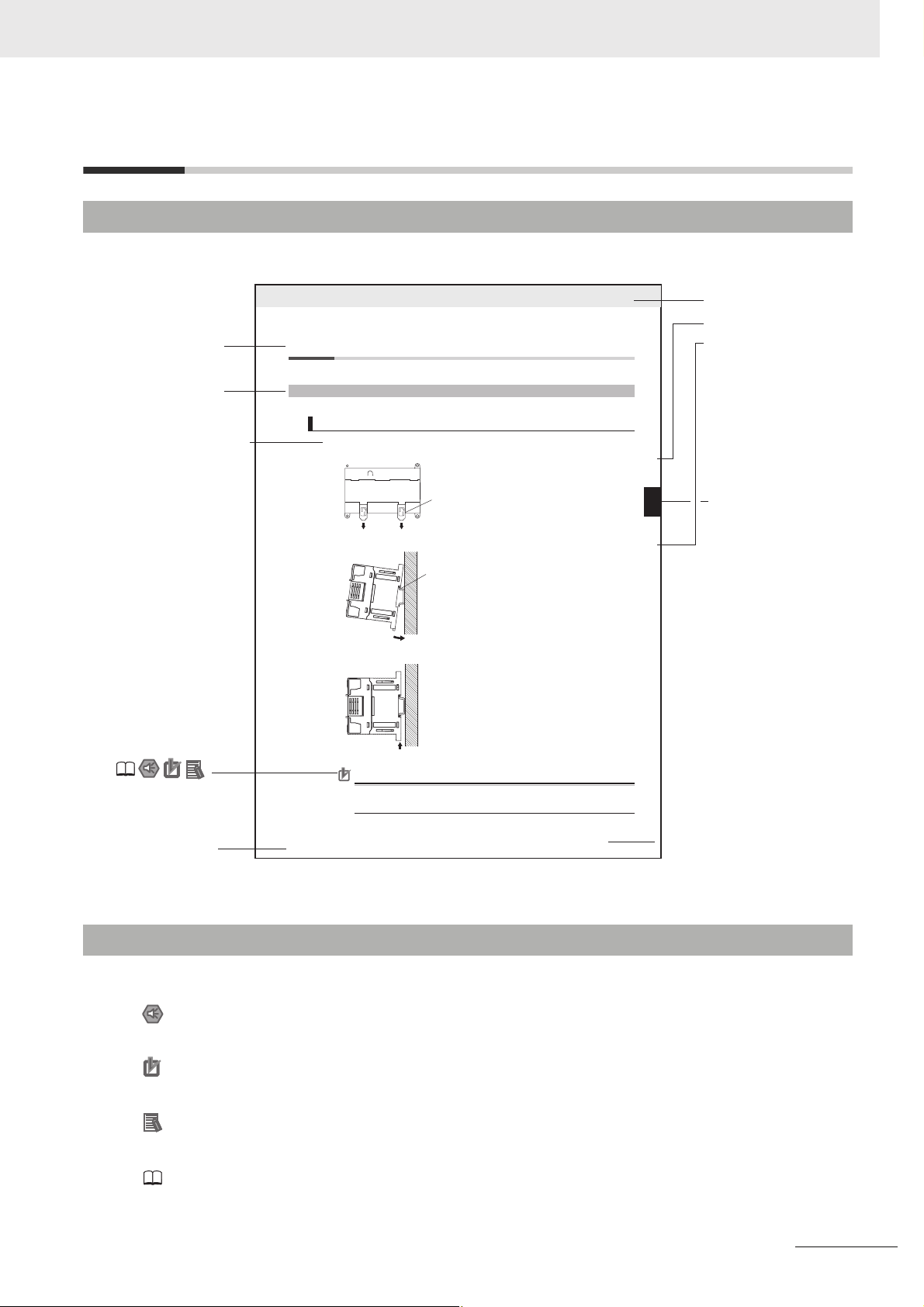

Manual Structure

Page Structure and Icons

The following page structure and icons are used in this manual.

Level 2 heading

Level 3 heading

Step in a procedure

Indicates a step in a

procedure.

Special Information

(See below.)

Icons are used to indicate

precautions and

additional information.

5-2 Installation

5-2-1 Installation Location

DIN Track Installation

1

Use a screwdriver to pull down the DIN Track mounting pins from the back of the Units to release

them, and mount the Units to the DIN Track.

Fit the back of the Units onto the DIN Track by catching the top of the Units on the Track and then

2

pressing in at the bottom of the Units, as shown below.

Press in all of the DIN Track mounting pins to securely lock the Units in place.

3

DIN Track mounting pins

5 Installation and wiring

Level 1 heading

Level 2 heading

Level 3 heading

Gives the current

headings.

5-2 Installation

DIN Track mounting pins

Release

DIN Track

5

5-2-1 Installation Location

Page tab

Gives the number

of the section.

Manual name

This illustration is provided only as a sample and may not literally appear in this manual.

Special Information

Special information in this manual is classified as follows:

Precautions for Safe Use

Precautions on what to do and what not to do to ensure using the product safely.

Precautions for Correct Use

Precautions on what to do and what not to do to ensure proper operation and performance.

Additional Information

Additional information to increase understanding or make operation easier.

References to the location of more detailed or related information.

Precautions for Correct Use

Tighten terminal block screws and cable screws to the following torques.

M4: 1.2 N·m

M3: 0.5 N·m

CP1E CPU Unit Hardware User’s Manual(W479)

5 - 3

CP1E CPU Unit Software User’s Manual(W480)

5

Page 10

Terminology and Notation

Ter m Description

E-type CPU Unit A basic model of CPU Unit that support basic control applications using instructions such

as basic, movement, arithmetic, and comparison instructions.

Basic models of CPU Units are called “E-type CPU Units” in this manual.

N-type CPU Unit An application model of CPU Unit that supports connections to Programmable Terminals,

inverters, and servo drives.

Application models of CPU Units are called “N-type CPU Units” in this manual.

NA-type CPU Unit An application model of CPU Unit that supports built-in analog and connections to Pro-

grammable Terminals, inverters, and servo drives.

Application models of CPU Units with built-in analog are called “NA-type CPU Units” in

this manual.

CX-Programmer A programming device that applies for programming and debugging PLCs.

The CX-Programmer includes the Micro PLC Edition CX-Programmer (CX-One Lite), the

CX-Programmer (CX-One) and the CX-Programmer for CP1E.

This manual describes the unique applications and functions of the Micro PLC Edition

CX-Programmer version 9.03 or higher/CX-Programmer for CP1E.

“CX-Programmer” refers to the Micro PLC Edition CX-Programmer version 9.03 or higher/

CX-Programmer for CP1E in this manual.

Note E20/30/40 and N20/30/40 CPU Units are supported by CX-Programmer version 8.2

or higher. E10/14, N14/60 and NA20 CPU Units are supported by CX-Programmer

version 9.03 or higher.

6

CP1E CPU Unit Software User’s Manual(W480)

Page 11

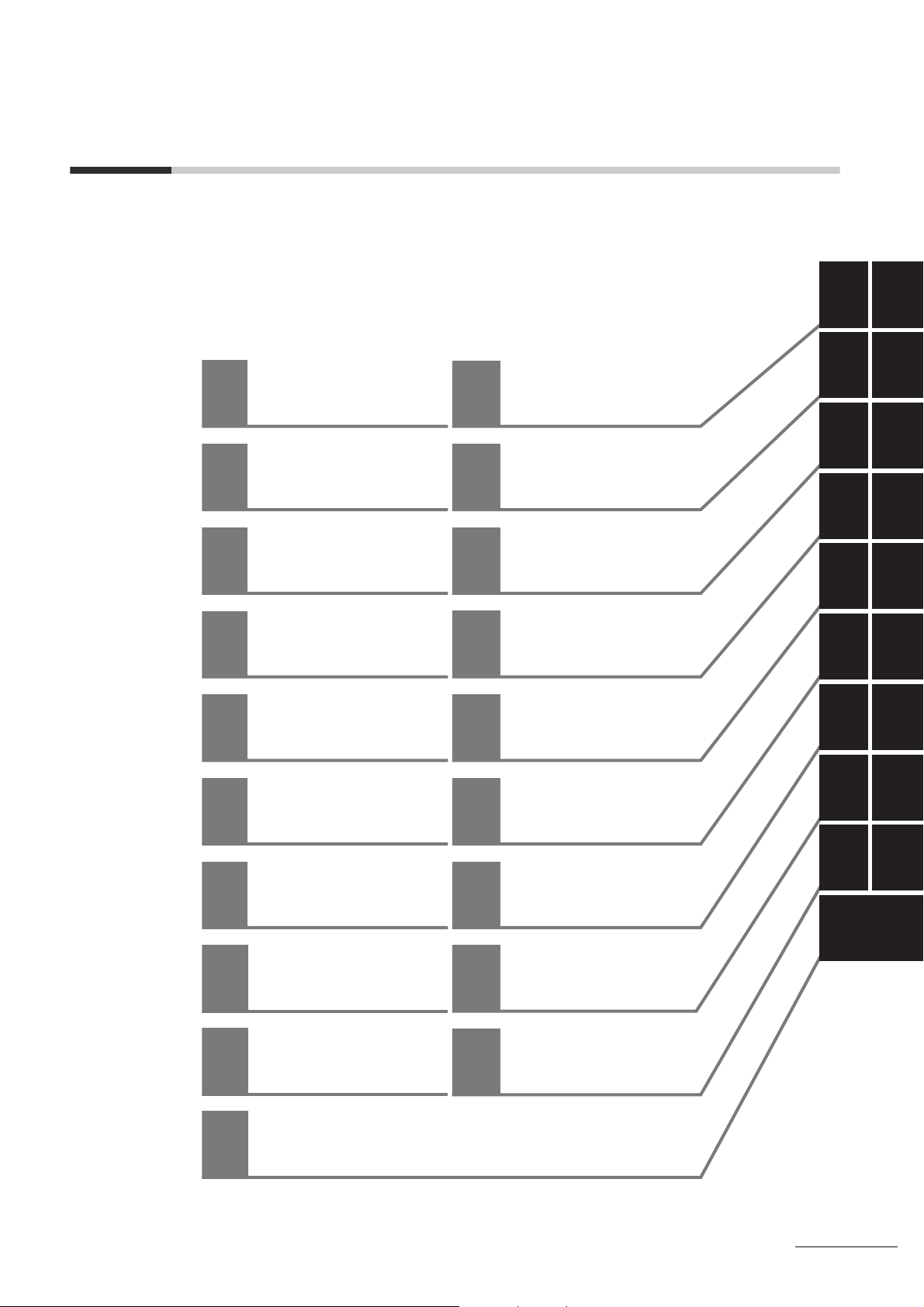

Sections in this Manual

111

Overview

1 11

2 12

High-speed Counters

3 13

2

3

4

5

6

7

Internal Memory

in the CPU Unit

CPU Unit Operation

Understanding

Programming

I/O Memory

I/O Allocation

PLC Setup

12

13

14

15

16

17

Pulse Outputs

PWM Outputs

Serial

Communications

Analog I/O Function

Other Functions

Ethernet

Option Board

4

5

6

7

8

9

10

14

15

16

17

18

APP

Overview of Built-in

8

9

10

CP1E CPU Unit Software User’s Manual(W480)

Functions and

Allocations

Quick-response

Inputs

Interrupts

18

A

Programming

Device Operations

Appendices

7

Page 12

CONTENTS

Introduction ...............................................................................................................1

CP1E CPU Unit Manuals...........................................................................................2

Manual Structure.......................................................................................................5

Safety Precautions..................................................................................................18

Precautions for Safe Use ........................................................................................21

Regulations and Standards....................................................................................23

Related Manuals......................................................................................................24

Section 1 Overview

1-1 CP1E Overview ........................................................................................................................ 1-2

1-1-1 Overview of Features .................................................................................................................. 1-2

1-2 Basic Operating Procedure ....................................................................................................1-3

Section 2 Internal Memory in the CPU Unit

2-1 Internal Memory in the CPU Unit............................................................................................ 2-2

2-1-1 CPU Unit Memory Backup Structure .......................................................................................... 2-2

2-1-2 Memory Areas and Stored Data ................................................................................................. 2-3

2-1-3 Transferring Data from a Programming Device........................................................................... 2-4

2-1-4 Backup ........................................................................................................................................2-4

Section 3 CPU Unit Operation

3-1 CPU Unit Operation ................................................................................................................. 3-2

3-1-1 Overview of CPU Unit Operation ................................................................................................3-2

3-1-2 CPU Unit Operating Modes.........................................................................................................3-3

3-2 Backing Up Memory ................................................................................................................ 3-5

3-2-1 CPU Unit Memory Configuration................................................................................................. 3-5

3-2-2 Backing Up Ladder Programs and PLC Setup............................................................................3-6

3-2-3 I/O Memory Backup ....................................................................................................................3-6

3-2-4 Initializing I/O Memory at Startup................................................................................................ 3-8

Section 4 Understanding Programming

4-1 Programming ........................................................................................................................... 4-2

4-1-1 User Programs............................................................................................................................4-2

4-1-2 Program Capacity ....................................................................................................................... 4-3

4-1-3 Basics of Programming...............................................................................................................4-3

4-2 Tasks, Sections, and Symbols ............................................................................................... 4-6

4-2-1 Overview of Tasks.......................................................................................................................4-6

4-2-2 Overview of Sections ..................................................................................................................4-6

4-2-3 Overview of Symbols ..................................................................................................................4-6

8

CP1E CPU Unit Software User’s Manual(W480)

Page 13

4-3 Programming Instructions...................................................................................................... 4-8

4-3-1 Basic Understanding of Instructions ........................................................................................... 4-8

4-3-2 Operands ....................................................................................................................................4-9

4-3-3 Instruction Variations................................................................................................................. 4-10

4-3-4 Execution Conditions ................................................................................................................4-10

4-3-5 Specifying Data in Operands ....................................................................................................4-12

4-3-6 Data Formats ............................................................................................................................ 4-13

4-3-7 I/O Refresh Timing....................................................................................................................4-15

4-4 Constants ............................................................................................................................... 4-16

4-5 Specifying Offsets for Addresses ........................................................................................ 4-19

4-5-1 Overview ................................................................................................................................... 4-19

4-5-2 Application Examples for Address Offsets ................................................................................ 4-21

4-6 Ladder Programming Precautions...................................................................................... 4-22

4-6-1 Special Program Sections.........................................................................................................4-22

Section 5 I/O Memory

5-1 Overview of I/O Memory Areas............................................................................................... 5-2

5-1-1 I/O Memory Areas.......................................................................................................................5-2

5-1-2 I/O Memory Area Address Notation............................................................................................5-5

5-1-3 I/O Memory Areas.......................................................................................................................5-6

5-2 I/O Bits ...................................................................................................................................... 5-7

5-3 Work Area (W) .......................................................................................................................... 5-8

5-4 Holding Area (H) ...................................................................................................................... 5-9

5-5 Data Memory Area (D) ........................................................................................................... 5-11

5-6 Timer Area (T) ........................................................................................................................ 5-13

5-7 Counter Area (C) .................................................................................................................... 5-15

5-8 Auxiliary Area (A)................................................................................................................... 5-17

5-9 Condition Flags...................................................................................................................... 5-19

5-10 Clock Pulses .......................................................................................................................... 5-21

Section 6 I/O Allocation

6-1 Allocation of Input Bits and Output Bits ............................................................................... 6-2

6-1-1 I/O Allocation...............................................................................................................................6-2

6-1-2 I/O Allocation Concepts...............................................................................................................6-3

6-1-3 Allocations on the CPU Unit........................................................................................................6-3

6-1-4 Allocations to Expansion Units and Expansion I/O Units............................................................6-4

Section 7 PLC Setup

7-1 Overview of the PLC Setup..................................................................................................... 7-2

7-2 PLC Setup Settings ................................................................................................................. 7-3

7-2-1 Startup and CPU Unit Settings ...................................................................................................7-3

7-2-2 Timing and Interrupt Settings......................................................................................................7-3

7-2-3 Input Constant Settings...............................................................................................................7-4

7-2-4 Built-in RS-232C Port..................................................................................................................7-5

7-2-5 Serial Option Port........................................................................................................................7-8

7-2-6 Built-in Inputs ............................................................................................................................7-11

7-2-7 Pulse Output 0 Settings ............................................................................................................ 7-13

7-2-8 Pulse Output 1 Settings ............................................................................................................ 7-14

7-2-9 Built-in AD/DA: Built-in Analog I/O Settings ..............................................................................7-16

CP1E CPU Unit Software User’s Manual(W480)

9

Page 14

Section 8 Overview of Built-in Functions and Allocations

8-1 Built-in Functions .................................................................................................................... 8-2

8-2 Overall Procedure for Using CP1E Built-in Functions ......................................................... 8-3

8-3 Terminal Allocations for Built-in Functions ................... ... ........ ... .... ....8-4

8-3-1 Specifying the Functions to Use.................................................................................................. 8-4

8-3-2 Selecting Functions in the PLC Setup......................................................................................... 8-4

8-3-3 Allocating Built-in Input Terminals ...............................................................................................8-6

8-3-4 Allocating Built-in Output Temrinals ............................................................................................8-8

Section 9 Quick-response Inputs

9-1 Quick-response Inputs............................................................................................................ 9-2

9-1-1 Overview .....................................................................................................................................9-2

9-1-2 Flow of Operation........................................................................................................................ 9-3

Section 10 Interrupts

10-1 Interrupts................................................................................................................................ 10-2

10-1-1 Overview ...................................................................................................................................10-2

10-2 Input Interrupts ...................................................................................................................... 10-3

10-2-1 Overview ...................................................................................................................................10-3

10-2-2 Flow of Operation......................................................................................................................10-4

10-2-3 Application Example..................................................................................................................10-7

10-3 Scheduled Interrupts........................................................................................................... 10-10

10-3-1 Overview .................................................................................................................................10-10

10-3-2 Flow of Operation....................................................................................................................10-11

10-4 Precautions for Using Interrupts........................................................................................ 10-13

10-4-1 Interrupt Task Priority and Order of Execution ........................................................................ 10-13

10-4-2 Related Auxiliary Area Words and Bits...................................................................................10-13

10-4-3 Duplicate Processing in each Task .........................................................................................10-13

Section 11 High-speed Counters

11-1 Overview................................................................................................................................. 11-2

11-1-1 Overview ...................................................................................................................................11-2

11-1-2 Flow of Operation......................................................................................................................11-3

11-1-3 Specifications............................................................................................................................ 11-7

11-2 High-speed Counter Inputs...................................................................................................11-8

11-2-1 Pulse Input Methods Settings ...................................................................................................11-8

11-2-2 Counting Ranges Settings ......................................................................................................11-10

11-2-3 Reset Methods........................................................................................................................11-11

11-2-4 Reading the Present Value .....................................................................................................11-12

11-2-5 Frequency Measurement ........................................................................................................11-13

11-3 High-speed Counter Interrupts........................................................................................... 11-14

11-3-1 Overview .................................................................................................................................11-14

11-3-2 Present Value Comparison .....................................................................................................11-17

11-3-3 High-speed Counter Interrupt Instruction................................................................................11-21

11-4 Related Auxiliary Area Bits and Words ............................................................................. 11-26

11-5 Application Example .......................................................................................................... 11-27

10

CP1E CPU Unit Software User’s Manual(W480)

Page 15

Section 12 Pulse Outputs

12-1 Overview................................................................................................................................. 12-2

12-1-1 Overview................................................................................................................................... 12-2

12-1-2 Flow of Operation ..................................................................................................................... 12-3

12-1-3 Specifications.......................................................................................................................... 12-10

12-2 Positioning Control ............................................................................................................. 12-11

12-2-1 Positioning Control Configuration ........................................................................................... 12-11

12-2-2 Relative Positioning and Absolute Positioning ........................................................................ 12-11

12-2-3 Application Example............................................................................................................... 12-13

12-3 Jogging................................................................................................................................. 12-15

12-3-1 High-speed Jogging................................................................................................................ 12-15

12-3-2 Low-speed Jogging................................................................................................................. 12-15

12-3-3 Application Example............................................................................................................... 12-15

12-4 Defining Origin Position...................................................................................................... 12-18

12-4-1 Origin Searches...................................................................................................................... 12-18

12-4-2 Flow of Operation ................................................................................................................... 12-19

12-4-3 Settings in PLC Setup............................................................................................................. 12-19

12-4-4 Origin Search Instructions ...................................................................................................... 12-22

12-4-5 Origin Search Operations....................................................................................................... 12-23

12-4-6 Origin Return .......................................................................................................................... 12-30

12-4-7 Changing the Present Value of the Pulse Output................................................................... 12-31

12-5 Reading the Pulse Output Present Value .......................................................................... 12-32

12-6 Related Auxiliary Area Flags .............................................................................................. 12-33

12-7 Application Examples ......................................................................................................... 12-34

12-7-1 Vertically Conveying PCBs (Multiple Progressive Positioning) ............................................... 12-34

12-7-2 Feeding Wrapping Material: Interrupt Feeding ....................................................................... 12-39

12-8 Precautions when Using Pulse Outputs ........................................................................... 12-42

12-9 Pulse Output Pattern........................................................................................................... 12-47

12-9-1 Speed Control (Continuous Mode) ......................................................................................... 12-47

12-9-2 Positioning Control (Independent Mode) ................................................................................ 12-49

Section 13 PWM Outputs

13-1 PWM Outputs (Variable-duty-factor Pulse Outputs)........................................................... 13-2

13-1-1 Flow of Operation ..................................................................................................................... 13-3

13-1-2 Ladder Program Example......................................................................................................... 13-3

Section 14 Serial Communications

14-1 Serial Communications......................................................................................................... 14-2

14-1-1 Types of CPU Units and Serial Ports ........................................................................................ 14-2

14-1-2 Overview of Serial Communications.........................................................................................14-3

14-2 Program-free Communications with Programmable Terminals ........................................ 14-5

14-2-1 Overview................................................................................................................................... 14-5

14-2-2 Flow of Connection................................................................................................................... 14-6

14-2-3 PLC Setup and PT System Settings......................................................................................... 14-6

14-3 No-protocol Communications with General Components................................................. 14-8

14-3-1 Overview................................................................................................................................... 14-8

14-3-2 Flow of Operation ..................................................................................................................... 14-9

14-3-3 PLC Setup ................................................................................................................................ 14-9

14-3-4 Related Auxiliary Area Bits and Words................................................................................... 14-10

14-4 Modbus-RTU Easy Master Function .................................................................................. 14-11

14-4-1 Overview................................................................................................................................. 14-11

14-4-2 Flow of Operation ................................................................................................................... 14-11

CP1E CPU Unit Software User’s Manual(W480)

11

Page 16

14-4-3 Setting and Word Allocation....................................................................................................14-12

14-4-4 Programming Examples..........................................................................................................14-14

14-5 Serial PLC Links .................................................................................................................. 14-20

14-5-1 Overview .................................................................................................................................14-20

14-5-2 Flow of Operation....................................................................................................................14-21

14-5-3 PLC Setup...............................................................................................................................14-21

14-5-4 Operating Specifications .........................................................................................................14-23

14-5-5 Example Application................................................................................................................14-28

14-6 Connecting the Host Computer (Not Including Support Software) ................................ 14-30

14-6-1 Overview .................................................................................................................................14-30

14-6-2 Flow of Operation....................................................................................................................14-30

14-6-3 Command/response Format and List of Commands ..............................................................14-31

Section 15 Analog I/O Function

15-1 Overview................................................................................................................................. 15-2

15-1-1 Flow of Operation......................................................................................................................15-2

15-1-2 Analog I/O Specifications..........................................................................................................15-6

15-2 Analog Input and Output Signal Ranges............................................................................. 15-7

15-2-1 Analog Input Signal Ranges......................................................................................................15-7

15-2-2 Analog Output Signal Ranges...................................................................................................15-9

15-2-3 Special functions..................................................................................................................... 15-11

15-3 I/O Allocation and Related Auxiliary Area Flags............................................................... 15-12

15-3-1 I/O Allocation...........................................................................................................................15-12

15-3-2 Related Auxiliary Area Flags...................................................................................................15-12

Section 16 Other Functions

16-1 PID Temperature Control ...................................................................................................... 16-2

16-1-1 Overview ...................................................................................................................................16-2

16-1-2 Flow of Operation......................................................................................................................16-3

16-1-3 Application Example..................................................................................................................16-4

16-2 Clock ....................................................................................................................................... 16-7

16-3 DM Backup Function ............................................................................................................. 16-8

16-3-1 Backing Up and Restoring DM Area Data.................................................................................16-8

16-3-2 Procedure................................................................................................................................16-10

16-4 Security Functions .............................................................................................................. 16-12

16-4-1 Ladder Program Read Protection ...........................................................................................16-12

Section 17 Ethernet Option Board

17-1 Features and Specifications.................................................................................................17-2

17-1-1 Ethernet Option Board Function Guide.....................................................................................17-2

17-1-2 Features.................................................................................................................................... 17-3

17-1-3 Specifications............................................................................................................................ 17-5

17-1-4 Software Configuration..............................................................................................................17-5

17-1-5 FINS Communications..............................................................................................................17-6

17-1-6 Differences in version of the Ethernet Option Board................................................................. 17-8

17-2 Startup Procedure ................................................................................................................. 17-9

17-2-1 Startup Procedure.....................................................................................................................17-9

17-3 Settings ................................................................................................................................ 17-11

17-3-1 Ethernet Option Board Setup..................................................................................................17-11

17-3-2 Transferring Data from the CPU Unit ......................................................................................17-12

17-3-3 Default Settings.......................................................................................................................17-13

12

CP1E CPU Unit Software User’s Manual(W480)

Page 17

17-3-4 Web Browser Setting Function ............................................................................................... 17-15

17-4 Memory Allocations ............................................................................................................ 17-25

17-4-1 DM Area Allocation................................................................................................................. 17-25

17-4-2 CIO Area Allocation................................................................................................................ 17-30

17-5 Trouble Shooting ................................................................................................................. 17-32

17-5-1 Error Log................................................................................................................................. 17-32

17-5-2 Error Codes ............................................................................................................................ 17-33

17-5-3 Error Status............................................................................................................................. 17-35

17-6 Connection Method with the CX-Programmer.................................................................. 17-36

17-7 Network Installation............................................................................................................. 17-39

17-7-1 Devices Required for Constructing a Network........................................................................ 17-39

17-7-2 Network Installation ................................................................................................................ 17-39

17-8 Comparison with Previous Models .................................................................................... 17-41

Section 18 Programming Device Operations

18-1 Programming Devices Usable with the CP1E ..................................................................... 18-2

18-2 Overview of CX-Programmer................................................................................................ 18-3

18-2-1 CX-Programmer........................................................................................................................ 18-3

18-2-2 CX-Programmer Flow from Startup to Operation ..................................................................... 18-3

18-2-3 Help .......................................................................................................................................... 18-6

18-3 Creating a Ladder Program .................................................................................................. 18-7

18-3-1 Inputting a Ladder Program...................................................................................................... 18-7

18-3-2 Saving and Reading Ladder Programs................................................................................... 18-14

18-3-3 Editing Ladder Programs ........................................................................................................ 18-15

18-4 Connecting Online to the CP1E and Transferring the Program ...................................... 18-18

18-4-1 Connecting Online.................................................................................................................. 18-18

18-4-2 Changing Operating Modes.................................................................................................... 18-19

18-4-3 Transferring a Ladder Program and the PLC Setup................................................................ 18-20

18-4-4 Starting Operation .................................................................................................................. 18-21

18-5 Online Monitoring and Debugging..................................................................................... 18-23

18-5-1 Monitoring Status.................................................................................................................... 18-23

18-5-2 Force-set/Reset Bits............................................................................................................... 18-25

18-5-3 Online Editing ......................................................................................................................... 18-26

Section A Appendices

A-1 Instruction Functions..............................................................................................................A-2

A-1-1 Sequence Input Instructions.......................................................................................................A-2

A-1-2 Sequence Output Instructions ....................................................................................................A-3

A-1-3 Sequence Control Instructions ...................................................................................................A-5

A-1-4 Timer and Counter Instructions .................................................................................................. A-7

A-1-5 Comparison Instructions...........................................................................................................A-10

A-1-6 Data Movement Instructions .....................................................................................................A-12

A-1-7 Data Shift Instructions ..............................................................................................................A-15

A-1-8 Increment/Decrement Instructions............................................................................................ A-17

A-1-9 Symbol Math Instructions .........................................................................................................A-18

A-1-10 Conversion Instructions ............................................................................................................A-22

A-1-11 Logic Instructions...................................................................................................................... A-26

A-1-12 Special Math Instructions .........................................................................................................A-27

A-1-13 Floating-point Math Instructions ...............................................................................................A-27

A-1-14 Table Data Processing Instructions ..........................................................................................A-30

A-1-15 Data Control Instructions.......................................................................................................... A-31

A-1-16 Subroutine Instructions.............................................................................................................A-35

A-1-17 Interrupt Control Instructions ....................................................................................................A-36

A-1-18 High-speed Counter/Pulse Output Instructions ........................................................................A-37

CP1E CPU Unit Software User’s Manual(W480)

13

Page 18

A-1-19 Step Instructions .......................................................................................................................A-44

A-1-20 Basic I/O Unit Instructions.........................................................................................................A-45

A-1-21 Serial Communications Instructions..........................................................................................A-49

A-1-22 Clock Instructions......................................................................................................................A-50

A-1-23 Failure Diagnosis Instructions ...................................................................................................A-51

A-1-24 Other Instructions......................................................................................................................A-51

A-2 Auxiliary Area Allocations by Address................................................................................A-52

A-2-1 Read-only Words ......................................................................................................................A-52

A-2-2 Read/Write Words.....................................................................................................................A-70

A-3 Response Performance.........................................................................................................A-80

A-3-1 I/O Response Time...................................................................................................................A-80

A-3-2 Interrupt Response Time ..........................................................................................................A-82

A-3-3 Serial PLC Link Response Performance...................................................................................A-83

A-3-4 Pulse Output Start Time............................................................................................................A-84

A-3-5 Pulse Output Change Response Time......................................................................................A-84

A-4 PLC Operation for Power Interruptions ...............................................................................A-85

Index ..................................................................................................................................Index-1

Revision History ................................................................................Revision-1

14

CP1E CPU Unit Software User’s Manual(W480)

Page 19

Read and Understand this Manual

Please read and understand this manual before using the product. Please consult your OMRON representative

if you have any questions or comments.

Warranty and Limitations of Liability

WARRANTY

OMRON’s exclusive warranty is that the products are free from defects in materials and workmanship for a

period of one year (or other period if specified) from date of sale by OMRON.

OMRON MAKES NO WARRANTY OR REPRESENTATION, EXPRESS OR IMPLIED, REGARDING NONINFRINGEMENT, MERCHANTABILITY, OR FITNESS FOR PARTICULAR PURPOSE OF THE

PRODUCTS. ANY BUYER OR USER ACKNOWLEDGES THAT THE BUYER OR USER ALONE HAS

DETERMINED THAT THE PRODUCTS WILL SUITABLY MEET THE REQUIREMENTS OF THEIR

INTENDED USE. OMRON DISCLAIMS ALL OTHER WARRANTIES, EXPRESS OR IMPLIED.

LIMITATIONS OF LIABILITY

OMRON SHALL NOT BE RESPONSIBLE FOR SPECIAL, INDIRECT, OR CONSEQUENTIAL DAMAGES,

LOSS OF PROFITS OR COMMERCIAL LOSS IN ANY WAY CONNECTED WITH THE PRODUCTS,

WHETHER SUCH CLAIM IS BASED ON CONTRACT, WARRANTY, NEGLIGENCE, OR STRICT

LIABILITY.

In no event shall the responsibility of OMRON for any act exceed the individual price of the product on which

liability is asserted.

IN NO EVENT SHALL OMRON BE RESPONSIBLE FOR WARRANTY, REPAIR, OR OTHER CLAIMS

REGARDING THE PRODUCTS UNLESS OMRON’S ANALYSIS CONFIRMS THAT THE PRODUCTS

WERE PROPERLY HANDLED, STORED, INSTALLED, AND MAINTAINED AND NOT SUBJECT TO

CONTAMINATION, ABUSE, MISUSE, OR INAPPROPRIATE MODIFICATION OR REPAIR.

CP1E CPU Unit Software User’s Manual(W480)

15

Page 20

Application Considerations

SUITABILITY FOR USE

OMRON shall not be responsible for conformity with any standards, codes, or regulations that apply to the

combination of products in the customer’s application or use of the products.

At the customer’s request, OMRON will provide applicable third party certification documents identifying

ratings and limitations of use that apply to the products. This information by itself is not sufficient for a

complete determination of the suitability of the products in combination with the end product, machine,

system, or other application or use.

The following are some examples of applications for which particular attention must be given. This is not

intended to be an exhaustive list of all possible uses of the products, nor is it intended to imply that the uses

listed may be suitable for the products:

• Outdoor use, uses involving potential chemical contamination or electrical interference, or conditions or

uses not described in this manual.

• Nuclear energy control systems, combustion systems, railroad systems, aviation systems, medical

equipment, amusement machines, vehicles, safety equipment, and installations subject to separate

industry or government regulations.

• Systems, machines, and equipment that could present a risk to life or property.

Please know and observe all prohibitions of use applicable to the products.

NEVER USE THE PRODUCTS FOR AN APPLICATION INVOLVING SERIOUS RISK TO LIFE OR

PROPERTY WITHOUT ENSURING THAT THE SYSTEM AS A WHOLE HAS BEEN DESIGNED TO

ADDRESS THE RISKS, AND THAT THE OMRON PRODUCTS ARE PROPERLY RATED AND INSTALLED

FOR THE INTENDED USE WITHIN THE OVERALL EQUIPMENT OR SYSTEM.

PROGRAMMABLE PRODUCTS

OMRON shall not be responsible for the user’s programming of a programmable product, or any

consequence thereof.

16

CP1E CPU Unit Software User’s Manual(W480)

Page 21

Disclaimers

CHANGE IN SPECIFICATIONS

Product specifications and accessories may be changed at any time based on improvements and other

reasons.

It is our practice to change model numbers when published ratings or features are changed, or when

significant construction changes are made. However, some specifications of the products may be changed

without any notice. When in doubt, special model numbers may be assigned to fix or establish key

specifications for your application on your request. Please consult with your OMRON representative at any

time to confirm actual specifications of purchased products.

DIMENSIONS AND WEIGHTS

Dimensions and weights are nominal and are not to be used for manufacturing purposes, even when

tolerances are shown.

PERFORMANCE DATA

Performance data given in this manual is provided as a guide for the user in determining suitability and does

not constitute a warranty. It may represent the result of OMRON’s test conditions, and the users must

correlate it to actual application requirements. Actual performance is subject to the OMRON Warranty and

Limitations of Liability.

ERRORS AND OMISSIONS

The information in this manual has been carefully checked and is believed to be accurate; however, no

responsibility is assumed for clerical, typographical, or proofreading errors, or omissions.

CP1E CPU Unit Software User’s Manual(W480)

17

Page 22

Safety Precautions

Definition of Precautionary Information

The following notation is used in this manual to provide precautions required to ensure safe usage of a

CP-series PLC. The safety precautions that are provided are extremely important to safety. Always read

and heed the information provided in all safety precautions.

Indicates an imminently hazardous situation which,

WARNING

Caution

if not avoided, will result in death or serious injury.

Additionally, there may be severe property damage.

Indicates a potentially hazardous situation which,

if not avoided, may result in minor or moderate

injury, or property damage.

Precautions for Safe Use

Indicates precautions on what to do and what not to do to ensure using the product safely.

Precautions for Correct Use

Indicates precautions on what to do and what not to do to ensure proper operation

and performance.

Symbols

The triangle symbol indicates precautions (including

warnings). The specific operation is shown in the triangle

and explained in text. This example indicates a precaution for electric shock.

The circle and slash symbol indicates operations that you

must not do. The specific operation is shown in the circle

and explained in text.

The filled circle symbol indicates operations that you

must do. The specific operation is shown in the circle and

explained in text. This example shows a general precaution for something that you must do.

18

The triangle symbol indicates precautions (including

warnings). The specific operation is shown in the triangle

and explained in text. This example indicates a general

precaution.

The triangle symbol indicates precautions (including

warnings). The specific operation is shown in the triangle

and explained in text. This example indicates a precaution for hot surfaces.

CP1E CPU Unit Software User’s Manual(W480)

Page 23

CautionCaution

Be sure to sufficiently confirm the safety at the destination when you transfer

the program or I/O memory or perform procedures to change the I/O memory.

Devices connected to PLC outputs may incorrectly operate regardless of the operating mode of the CPU Unit.

With an E-type CPU Unit or with an N/NA-type CPU Unit without a Battery, the contents of the DM Area (D) *, Holding Area (H), the Counter Present Values (C), the status of Counter Completion Flags (C), and the status of bits in the Auxiliary Area (A)

related to clock functions may be unstable when the power supply is turned ON.

*This does not apply to areas backed up to EEPROM using the DM backup function.

If the DM backup function is being used, be sure to use one of the following methods

for initialization.

1. Clearing All Areas to All Zeros

Select the Clear Held Memory (HR/DM/CNT) to Zero Check Box in the Startup

Data Read Area in the PLC Setup.

2. Clearing Specific Areas to All Zeros or Initializing to Specific Values

Make the settings from a ladder program.

If the data is not initialized, the unit or device may operate unexpectedly because of

unstable data.

Execute online edit only after confirming that no adverse effects will be caused

by extending the cycle time.

Otherwise, the input signals may not be readable.

The DM Area (D), Holding Area (H), Counter Completion Flags (C), and Counter

Present Values (C) will be held by the Battery if a Battery is mounted in a CP1EN/NAD- CPU Unit. When the battery voltage is low, however, I/O memory

areas that are held (including the DM, Holding, and Counter Areas) will be unstable.

The unit or device may operate unexpectedly because of unstable data.

Use the Battery Error Flag or other measures to stop outputs if external outputs are performed from a ladder program based on the contents of the DM

Area or other I/O memory areas.

Sufficiently check safety if I/O bit status or present values are monitored in the

Ladder Section Pane or present values are monitored in the Watch Pane.

If bits are set, reset, force-set, or force-reset by inadvertently pressing a shortcut key,

devices connected to PLC outputs may operate incorrectly regardless of the operating mode.

CP1E CPU Unit Software User’s Manual(W480)

19

Page 24

Caution

Program so that the memory area of the start address is not exceeded when

using a word address or symbol for the offset.

For example, write the program so that processing is executed only when the indirect

specification does not cause the final address to exceed the memory area by using

an input comparison instruction or other instruction.

If an indirect specification causes the address to exceed the area of the start address,

the system will access data in other area, and unexpected operation may occur.

Set the temperature range according to the type of temperature sensor connected to the Unit.

Temperature data will not be converted correctly if the temperature range does not

match the sensor.

Do not set the temperature range to any values other than those for which temperature ranges are given in the following table.

An incorrect setting may cause operating errors.

20

CP1E CPU Unit Software User’s Manual(W480)

Page 25

Precautions for Safe Use

Observe the following precautions when using a CP-series PLC.

Handling

• To initialize the DM Area, back up the initial contents for the DM Area to backup memory using

one of the following methods.

• Set the number of words of the DM Area to be backed up starting with D0 in the Number of CH

of DM for backup Box in the Startup Data Read Area.

• Include programming to back up specified words in the DM Area to built-in EEPROM by turning

ON A751.15 (DM Backup Save Start Bit).

• Check the ladder program for proper execution before actually running it on the Unit. Not checking

the program may result in an unexpected operation.

• The ladder program and parameter area data in the CP1E CPU Units are backed up in the built-in

EEPROM backup memory. The BKUP indicator will light on the front of the CPU Unit when the

backup operation is in progress. Do not turn OFF the power supply to the CPU Unit when the

BKUP indicator is lit. The data will not be backed up if power is turned OFF and a memory error

will occur the next time the power supply is turned ON.

• With a CP1E CPU Unit, data memory can be backed up to the built-in EEPROM backup memory.

The BKUP indicator will light on the front of the CPU Unit when backup is in progress. Do not turn

OFF the power supply to the CPU Unit when the BKUP indicator is lit. If the power is turned OFF

during a backup, the data will not be backed up and will not be transferred to the DM Area in RAM

the next time the power supply is turned ON.

• Before replacing the battery, supply power to the CPU Unit for at least 30 minutes and then complete battery replacement within 5 minutes. Memory data may be corrupted if this precaution is

not observed.

• The equipment may operate unexpectedly if inappropriate parameters are set. Even if the appropriate parameters are set, confirm that equipment will not be adversely affected before transferring the parameters to the CPU Unit.

• Before starting operation, confirm that the contents of the DM Area is correct.

• After replacing the CPU Unit, make sure that the required data for the DM Area, Holding Area, and

other memory areas has been transferred to the new CPU Unit before restarting operation.

• Do not attempt to disassemble, repair, or modify any Units. Any attempt to do so may result in malfunction, fire, or electric shock.

• Confirm that no adverse effect will occur in the system before attempting any of the following. Not

doing so may result in an unexpected operation.

• Changing the operating mode of the PLC (including the setting of the startup operating mode).

• Force-setting/force-resetting any bit in memory.

• Changing the present value of any word or any set value in memory.

External Circuits

• Always configure the external circuits to turn ON power to the PLC before turning ON power to the

control system. If the PLC power supply is turned ON after the control power supply, temporary

errors may result in control system signals because the output terminals on DC Output Units and

other Units will momentarily turn ON when power is turned ON to the PLC.

• Fail-safe measures must be taken by the customer to ensure safety in the event that outputs from

output terminals remain ON as a result of internal circuit failures, which can occur in relays, transistors, and other elements.

CP1E CPU Unit Software User’s Manual(W480)

21

Page 26

• If the I/O Hold Bit is turned ON, the outputs from the PLC will not be turned OFF and will maintain

their previous status when the PLC is switched from RUN or MONITOR mode to PROGRAM

mode. Make sure that the external loads will not produce dangerous conditions when this occurs.

(When operation stops for a fatal error, including those produced with the FALS instruction, all outputs from PLC will be turned OFF and only the internal output status in the CPU Unit will be maintained.)

22

CP1E CPU Unit Software User’s Manual(W480)

Page 27

Regulations and Standards

Trademarks

SYSMAC is a registered trademark for Programmable Controllers made by OMRON Corporation.

CX-One is a registered trademark for Programming Software made by OMRON Corporation.

Windows is a registered trademark of Microsoft Corporation.

Other system names and product names in this document are the trademarks or registered trademarks

of their respective companies.

CP1E CPU Unit Software User’s Manual(W480)

23

Page 28

Related Manuals

The following manuals are related to the CP1E. Use them together with this manual.

Manual name Cat. No. Model numbers Application Contents

SYSMAC CP Series

CP1E CPU Unit Software User’s Manual

(this manual)

SYSMAC CP Series

CP1E CPU Unit Hardware User’s Manual

SYSMAC CP Series

CP1E CPU Unit Instructions Reference Manual

CS/CJ/CP/NSJ Series

Communications Commands Reference Manual

SYSMAC CP Series

CP1L/CP1E CPU Unit

Introduction M anual

W480 CP1E-ED-

W479 CP1E-ED-

W483 CP1E-ED-

W342 CS1G/H-CPUH

W461 CP1L-L10D-

CP1E-ND-

CP1E-NAD-

CP1E-ND-

CP1E-NAD-

CP1E-ND-

CP1E-NAD-

CS1G/H-CPU-V1

CS1D-CPUH

CS1D-CPUS

CS1W-SCU-V1

CS1W-SCB-V1

CJ1G/H-CPUH

CJ1G-CPUP

CJ1M-CPU

CJ1G-CPU

CJ1W-SCU-V1

CP1L-L14D-

CP1L-L20D-

CP1L-M30D-

CP1L-M40D-

CP1L-M60D-

CP1E-ED-

CP1E-ND-

CP1E-NAD-

To learn the software

specifications of the

CP1E PLCs

Use this manual together with the CP1E CPU Unit Hardware User’s

Manual (Cat. No. W479) and Instructions Reference Manual (Cat. No.

W483).

To learn the hardware specifications

of the CP1E PLCs

Use this manual together with the CP1E CPU Unit Software User’s

Manual (Cat. No. W480) and Instructions Reference Manual (Cat. No.

W483).

To learn programming instructions in

detail

To learn communications commands for

CS/CJ/CP/NSJseries Controllers in

detail

Note This manual describes commands addressed to CPU Units. It

does not cover commands addressed to other Units or por ts (e.g.,

serial communications ports on CPU Units, communications ports

on Serial Communications Units/Boards, and other Communications Units).

To learn the basic

setup methods of the

CP1L/CP1E PLCs

Describes the following information for CP1E

PLCs.

• CPU Unit operation

• Internal memory

• Programming

• Settings

• CPU Unit built-in functions

• Interrupts

• High-speed counter inputs

• Pulse outputs

• Serial communications

• Analog I/O function

• Other functions

Describes the following information for CP1E

PLCs.

• Overview and features

• Basic system configuration

• Part names and functions

• Installation and settings

• Troubleshooting

Describes each programming instruction in

detail.

When programming, use this manual together

with the CP1E CPU Unit Software User’s Manual (Cat. No. W480).

Describes

1) C-mode commands and

2) FINS commands in detail.

R

ead this manual for details on C-mode and

FINS commands addressed to CPU Units.

Describes the following information for

CP1L/CP1E PLCs.

• Basic configuration and component names

• Mounting and wiring

• Programming, data transfer, and debugging

using the CX-Programmer

• Application program examples

24

CP1E CPU Unit Software User’s Manual(W480)

Page 29

Overview

This section gives an overview of the CP1E and describes its procedures.

1-1 CP1E Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-2

1-2 Basic Operating Procedure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-3

1

1

1-1-1 Overview of Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-2

CP1E CPU Unit Software User’s Manual(W480)

1-1

Page 30

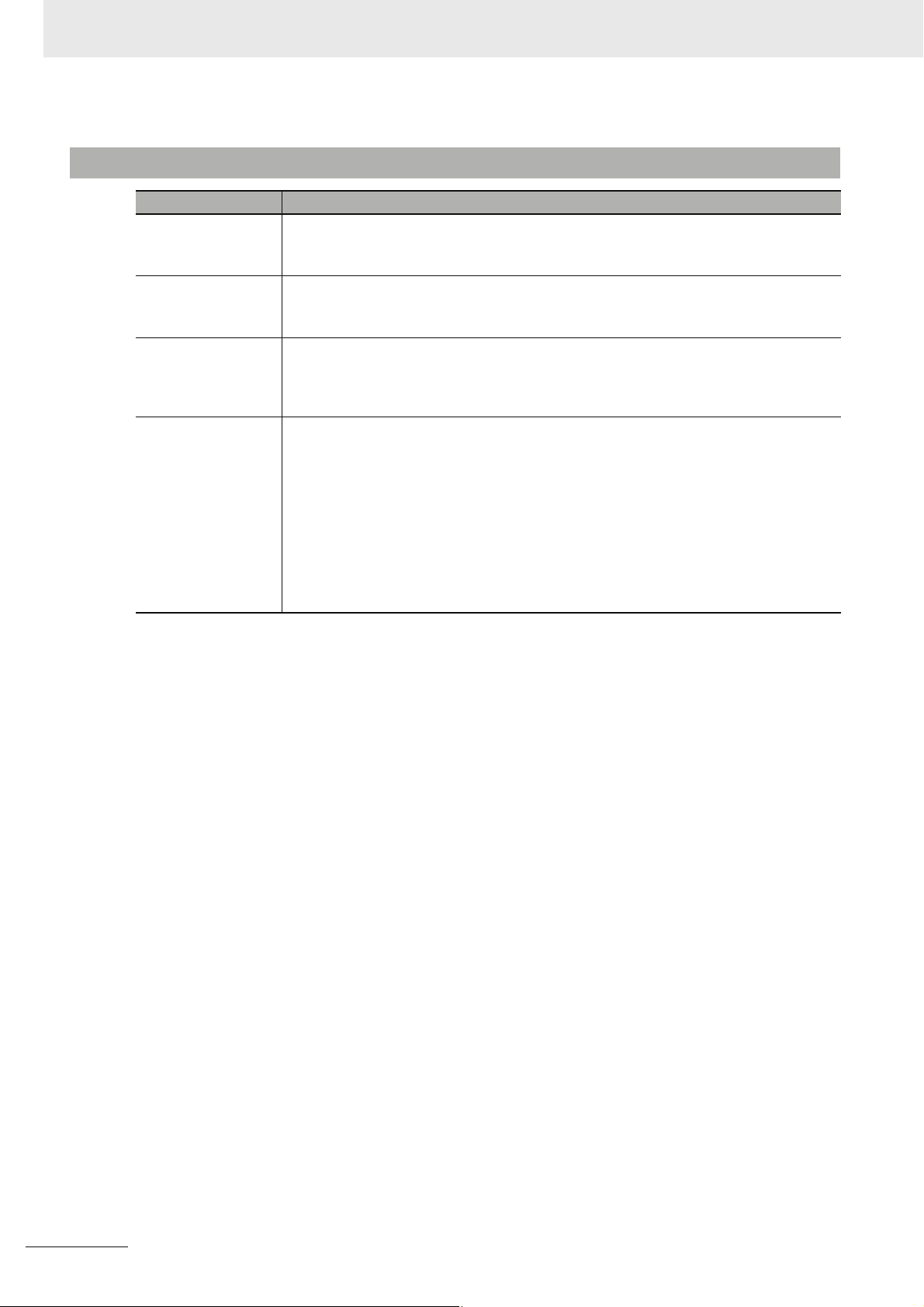

1 Overview

1-1 CP1E Overview

1-1-1 Overview of Features

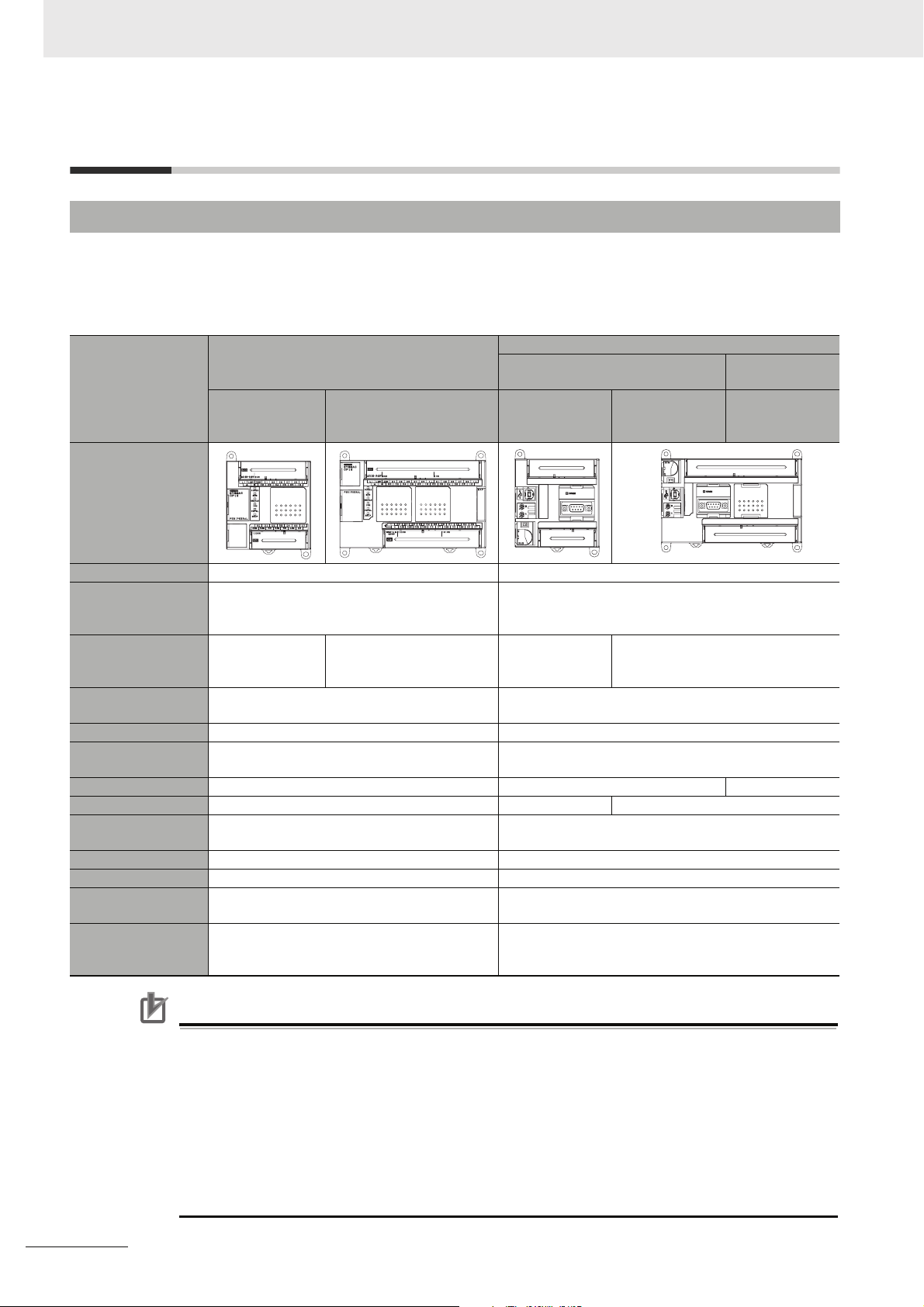

The SYSMAC CP1E Programmable Controller is a package-type PLC made by OMRON that i

designed for easy application. The CP1E includes E-type CPU Units (basic models) for standard control

operations using basic, movement, arithmetic, and comparison instructions, and N/NA-type CPU Units

(application models) that supports connections to Programmable Terminals, Inverters, and Servo Drives.

Basic Models

(E-type CPU Units)

CPU with 10, 14

or 20 I/O Points

Appearance

Program capacity 2K steps 8K steps

DM Area capacity 2K words

Of these 1,500 words can be written to the

built-in EEPROM.

Mounting Expansion I/O Units and

Expansion Units

Model with transistor outputs

Pulse outputs Not supported. Supported (Model with transistor outputs only)

Built-in serial communications port

Built-in analog Not available. Not available. Available

Option Board Not supported. Not supported. Supported (for one port)

Connection port for

Programming Device

Clock Not provided. Provided

Using a Battery Cannot be used. Can be used (sold separately).

Backup time of

built-in capacitor

Battery-free operation

Not possible. 3 Units maximum Not possible. 3 Units maximum

Available (CPU Unit with 10 I/O points only) Available

Not provided. RS-232C port provided

USB port USB port

50 hours at 25°C 40 hours at 25°C

Always battery-free operation.

Only data in the built-in EEPROM will be retained

if power is interrupted for longer than 50 hours.

CPU Unit with 30 or 40

I/O Points

CPU with 14 or

20 I/O Points

8K words

Of these 7,000 words can be written to the built-in

EEPROM.

Battery-free operation if no battery is attached. Only

data in the built-in EEPROM will be retained if power is

interrupted for longer than 40 hours.

CP1E Application Models

N-type CPU Units

CPU Unit with

30, 40 or 60 I/O

Points

NA-type CPU

Units

CPU Unit with

20 I/O Points

s

1-2

Precautions for Correct UsePrecautions for Correct Use

For CP1E CPU Units, the following I/O memory area will be unstable after a power interruption.

• DM Area (D) (excluding words backed up to the EEPROM using the DM function)

• Holding Area (H)

• Counter Present Values and Completion Flags (C)

• Auxiliary Area related to clock functions(A)

Mount the CP1W-BAT01 Battery (sold separately) to an N/NA-type CPU Unit if data in the above

areas need to be retained after a power interruption. A Battery cannot be mounted to an E-type

CPU Unit.

CP1E CPU Unit Software User’s Manual(W480)

Page 31

1-2 Basic Operating Procedure

In general, use the following procedure.

1. Setting Devices and Hardware

Connect the CPU Unit, Expansion I/O Units, and Expansion Units.

Set the DIP switches on the Option Board and Expansion Units as required.

Refer to Section 3 Part Names and Functions and Section 5 Installation and Wiring in the CP1E CPU Unit

Hardware User’s Manual (Cat. No. W479).

2. Wiring

Wire the power supply, I/O, and communications.

Refer to Section 5 Installation and Wiring in the CP1E CPU Unit Hardware User’s Manual (Cat. No. W479).

3. Connecting Online to the PLC

Connect the personal computer online to the PLC.

Refer to Section 4 Programming Device in the CP1E CPU Unit Hardware User’s Manual (Cat. No. W479).

1 Overview

1-2 Basic Operating Procedure

1

4. I/O Allocations

Allocations for built-in I/O on the CPU Unit are predetermined and memory is allocated automatically

to Expansion I/O Units and Expansion Units, so the user does not have to do anything.

Refer to Section 6 I/O Allocation in the CP1E CPU Unit Software User’s Manual (Cat. No. W480).

5. Software Setup

Make the PLC software settings.

With a CP1E CPU Unit, all you have to do is set the PLC Setup.

When using an E-type CPU Unit or when using an N/NA-type CPU Unit without a Battery, be sure to

consider selecting the Clear retained memory area (HR/DM/CNT) Check Box in the Startup Data

Read Area in the PLC Settings.

Refer to 3-2-4 Initializing I/O Memory at Startup, Section 7 PLC Setup in the CP1E CPU Unit Software

User’s Manual (Cat. No. W480).

6. Writing the Programs

Write the programs using the CX-Programmer.