OKI MSM82C54-2GS-K, MSM82C54-2JS, MSM82C54-2RS Datasheet

E2O0019-27-X2

¡ Semiconductor MSM82C54-2RS/GS/JS

¡ Semiconductor

This version: Jan. 1998

Previous version: Aug. 1996

MSM82C54-2RS/GS/JS

CMOS PROGRAMMABLE INTERVAL TIMER

GENERAL DESCRIPTION

The MSM82C54-2RS/GS/JS is a programmable universal timer designed for use in

microcomputer systems. Based on silicon gate CMOS technology, it requires a standby current

of only 10 mA (max.) when the chip is in the non-selected state. And during timer operation, the

power consumption is still very low with only 10mA (max.) of current required.

It consists of three independent counters, and can count up to a maximum of 10 MHz. The timer

features six different counter modes, and binary count/BCD count functions. Count values can

be set in byte or word units, and all functions are freely programmable.

FEATURES

• Maximum operating frequency of 10 MHz (VCC=5 V)

• High speed and low power consumption achieved by silicon gate CMOS technology

• Completely static operation

• Three independent 16-bit down-counters

• Status Read Back Command

• Six counter modes available for each counter

• Binary and decimal counting possible

• 24-pin Plastic DIP (DIP24-P-600-2.54): (Product name: MSM82C54-2RS)

• 28-pin Plastic QFJ (QFJ28-P-S450-1.27): (Product name: MSM82C54-2JS)

• 32-pin Plastic SSOP (SSOP32-P-430-1.00-K): (Product name: MSM82C54-2GS-K)

1/23

¡ Semiconductor MSM82C54-2RS/GS/JS

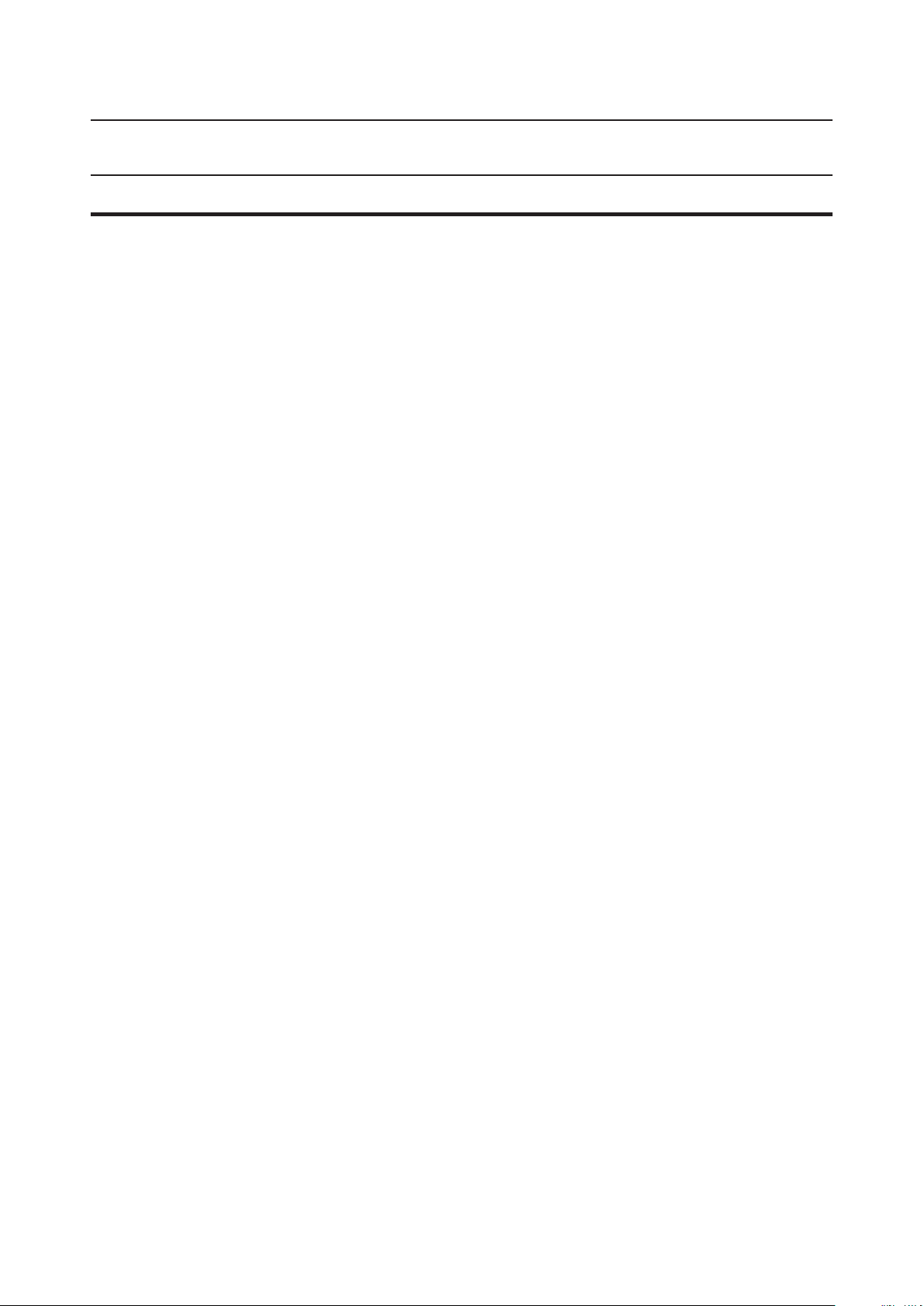

FUNCTIONAL BLOCK DIAGRAM

V

CC

GND

8

D

- D

7

0

Data

Bus

Buffer

Counter

#0

CLK

GATE

OUT

0

0

0

8

WR

RD

A

A

Read/

Write

0

1

Logic

Counter

#1

CLK

GATE

OUT

1

1

1

CS

Control

Word

Register

Counter

#2

CLK

GATE

OUT

2

2

2

Internal Bus

2/23

¡ Semiconductor MSM82C54-2RS/GS/JS

(

)

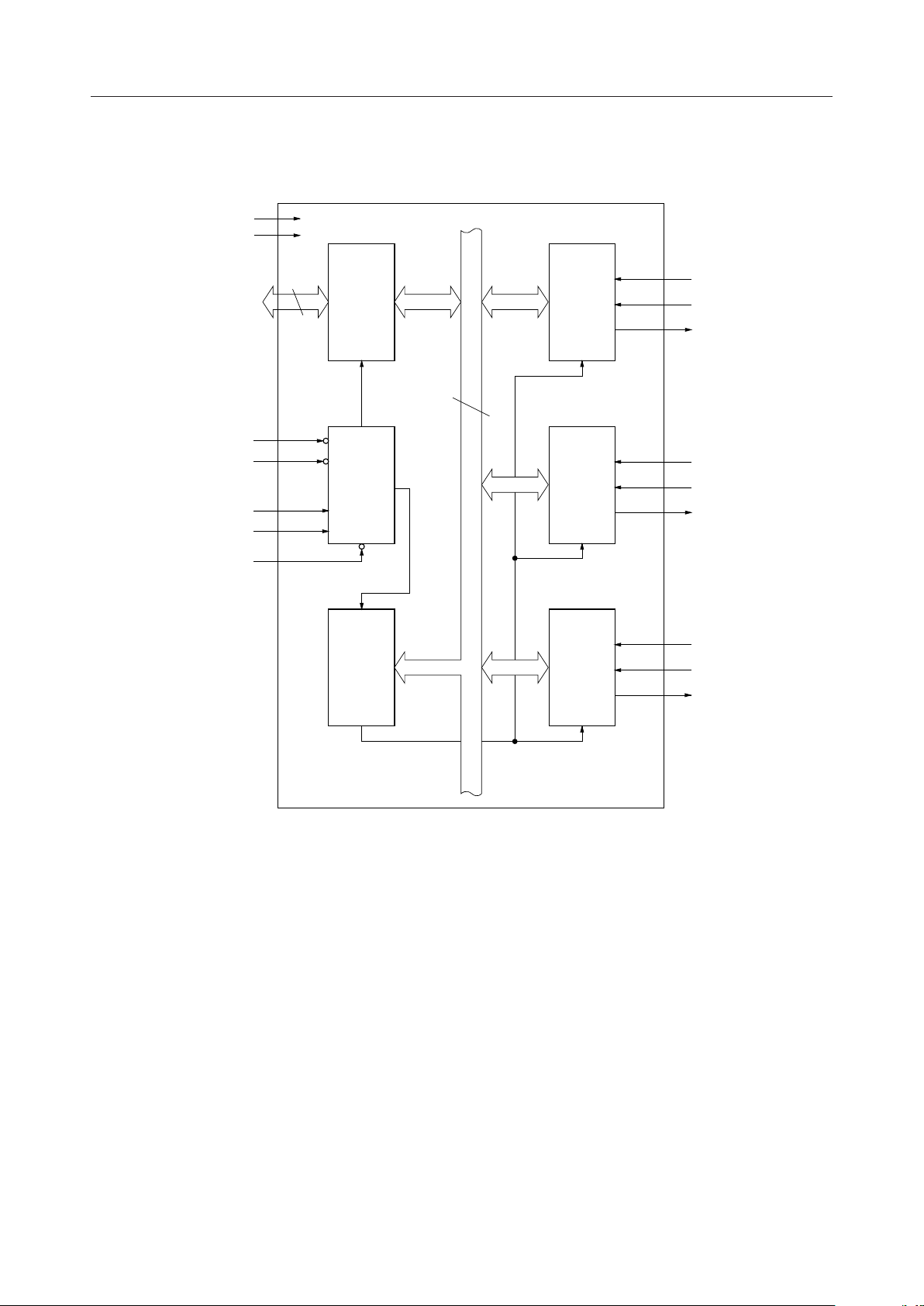

PIN CONFIGURATION (TOP VIEW)

24 pin Plastic DIP

32 pin Plastic SSOP

GATE

CLK

OUT

GATE

GND

CLK

OUT

GND

NC

D

D

D

NC

D

D

D

D

D

NC

NC

D

1

7

D

2

6

D

3

5

D

4

4

D

5

3

D

6

2

D

7

1

D

8

0

9

0

10

0

11

0

12

1

2

7

3

6

4

5

5

6

4

7

3

8

2

9

1

10

0

11

0

12

13

0

14

0

15

16

24

23

22

21

20

19

18

17

16

15

14

13

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

V

cc

WR

RD

CS

A

1

A

0

CLK

OUT

GATE

CLK

GATE

OUT

NC

V

cc

WR

RD

NC

CS

A

1

A

0

CLK

OUT

GATE

NC

CLK

GATE

OUT

NC

2

2

2

1

1

1

2

2

2

1

1

1

28 pin Plastic QFJ

CLK

NC

5D6D7

D

4

D

5

4

D

6

3

D

7

2

D

8

1

D

9

0

10

0

11

12

0

OUT

3

13

0

GATE

2

14

GND

NC

1

15

NC

VCCWR

28

27

16

17

1

1

OUT

GATE

RD

26

18

1

CLK

25

24

23

22

21

20

19

NC

CS

A

1

A

0

CLK

OUT

GATE

2

2

2

NC denotes "not connected".

3/23

¡ Semiconductor MSM82C54-2RS/GS/JS

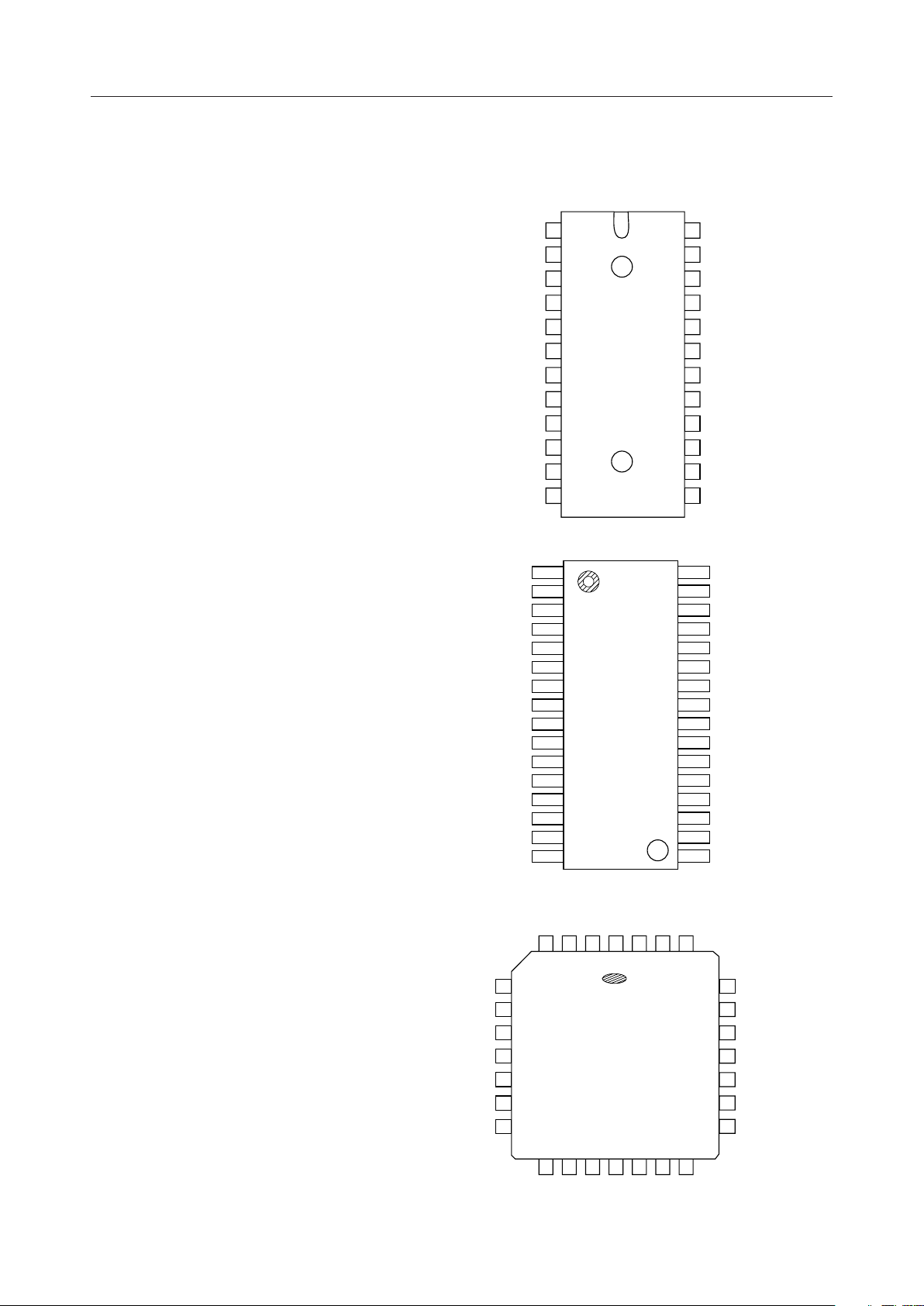

ABSOLUTE MAXIMUM RATING

Parameter Unit

Power Supply Voltage

Input Voltage

Output Voltage

Storage Temperature

Power Dissipation

Symbol

V

CC

V

IN

V

OUT

T

STG

P

D

Condition

With

respect to GND

—

Ta = 25°C

MSM82C54-2RS

MSM82C54-2GS MSM82C54-2JS

–0.5 to +7

–0.5 to V

–0.5 to V

CC

CC

+0.5

+0.5

–55 to +150

0.7

0.90.9

RECOMMENDED OPERATING CONDITIONS

Rating

Parameter UnitSymbol

Power Supply Voltage

Operating Temperature

"L" Input Voltage V

"H" Input Voltage

Min.

V

CC

T

op

IL

V

IH

4.5

–40

–0.5

2.2

Typ.

5V

+25

—

—

Max.

V

CC

5.5

+85

+0.8

+ 0.5

DC CHARACTERISTICS

V

V

V

°C

W

°C

V

V

Parameter Unit

"L" Output Voltage

"H" Output Voltage

Input Leak Current

Output Leak Current

Standby Supply

Current

Symbol

V

OL

V

OH

I

LI

I

LO

I

CCS

I

OL

I

OH

I

OH

0 £ V

0 £ V

cs ≥ V

V

≥ V

IH

V

IH £

Conditions

= 2.5 mA

= –2.5 mA

= –100 mA

£ V

IN

CC

£ V

OUT

CC

CC

CC

–0.2 V

–0.2 V

0.2 V

V

= 4.5 V to 5.5 V

CC

Ta

= –40°C to +85°C

V

CC

Min.

—

3.0

–0.4

–10

–10

—

Typ. Max.

—

—

—

—

—

—

Operating Supply

Curent

I

t

CC

=100 ns, CL = O pF

CLK

—

—

0.4 V

—V

—V

10 mA

10 mA

10

mA

10 mA

4/23

¡ Semiconductor MSM82C54-2RS/GS/JS

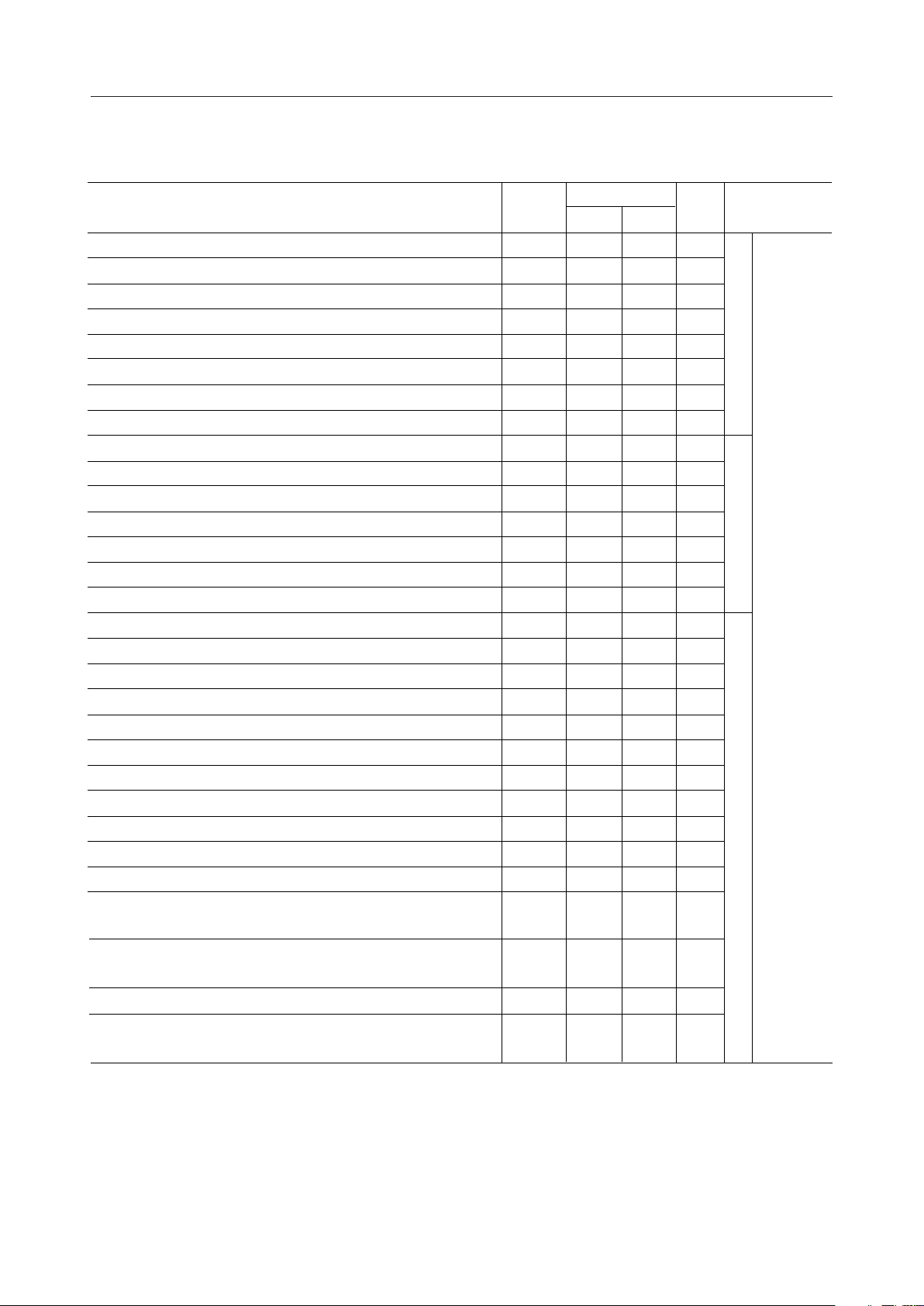

AC CHARACTERISTICS

= 4.5 V to 5.5 V, Ta = –40°C to +85°C)

(V

CC

Parameter

Address Set-up Times to Falling Edge of RD

Chip Select Input Set-up Time to Falling Edge of RD

Address Hold Time from Rising Edge of RD

RD Pulse Width

Data Access Time from Falling Edge of RD

Data Access Time after Address Determination

Delay Time from Rising Edge of RD to Data Floting State

RD Recovery Time

Address Set-up Time to Falling Edge of WR

Chip Select Input Set-up Time to Falling Edge of WR

Address Hold Time from Rising Edge of WR

WR Pulse Width

Data Determination Set-up Time to Rising Edge of WR

Data Hold Time after Rising Edge of WR

WR Recovery Time

CLK Cycle Time

CLK "H" Level Width

CLK "L" Level Width

CLK Rise Time

CLK Fall Time

GATE "H" Level Width

GATE "L" Level Width

GATE Input Set-up Time before Rising Edge of CLK

GATE Input Hold Time before Rising Edge of CLK

Output Delay Time after Falling Edge of CLK

Output Delay Time after Falling Edge of GATE

CLK Rise Delay Time after Rising Edge of WR for Count Value

Loading

t

t

t

t

t

RD

t

t

t

t

AW

t

SW

t

WA

t

WW

t

DW

t

WD

t

t

CLK

t

PWH

t

PWL

t

GW

t

t

t

t

t

ODG

t

WC

AR

SR

RA

RR

AD

DF

RV

RV

t

t

GL

GS

GH

OD

r

f

82C54-2

Min. Max.

30

0

0

95

—ns

—ns

—ns

—ns

—94

—

5

165

0

0

0

95

85

0

165

100

30

50

—

—

50

50

40

50

—

—

0

184 ns

65 ns

—ns

—ns

—ns

—ns

—ns

—ns

—ns

—ns

D.C. ns

—ns

—ns

25 ns

25 ns

—ns

—ns

—ns

—ns

100 ns

100 ns

55 ns

UnitSymbol

Conditions

ns

Read Timing

Write Timing

CL = 150 pF

Clock Gate Timing

GATE sampling delay time after rising edge of WR for count

loading

CLK Fall Set-up Time to Falling Edge of WR for Counter Latch

Command

t

WG

t

WO

t

CL

–5

—

–40

40 ns

240 nsOutput Delay Time after Falling Edge of WR for Mode Set

40 ns

Note: Timing measured at VL = 0.8 V and VH = 2.2 V for both inputs and outputs.

5/23

¡ Semiconductor MSM82C54-2RS/GS/JS

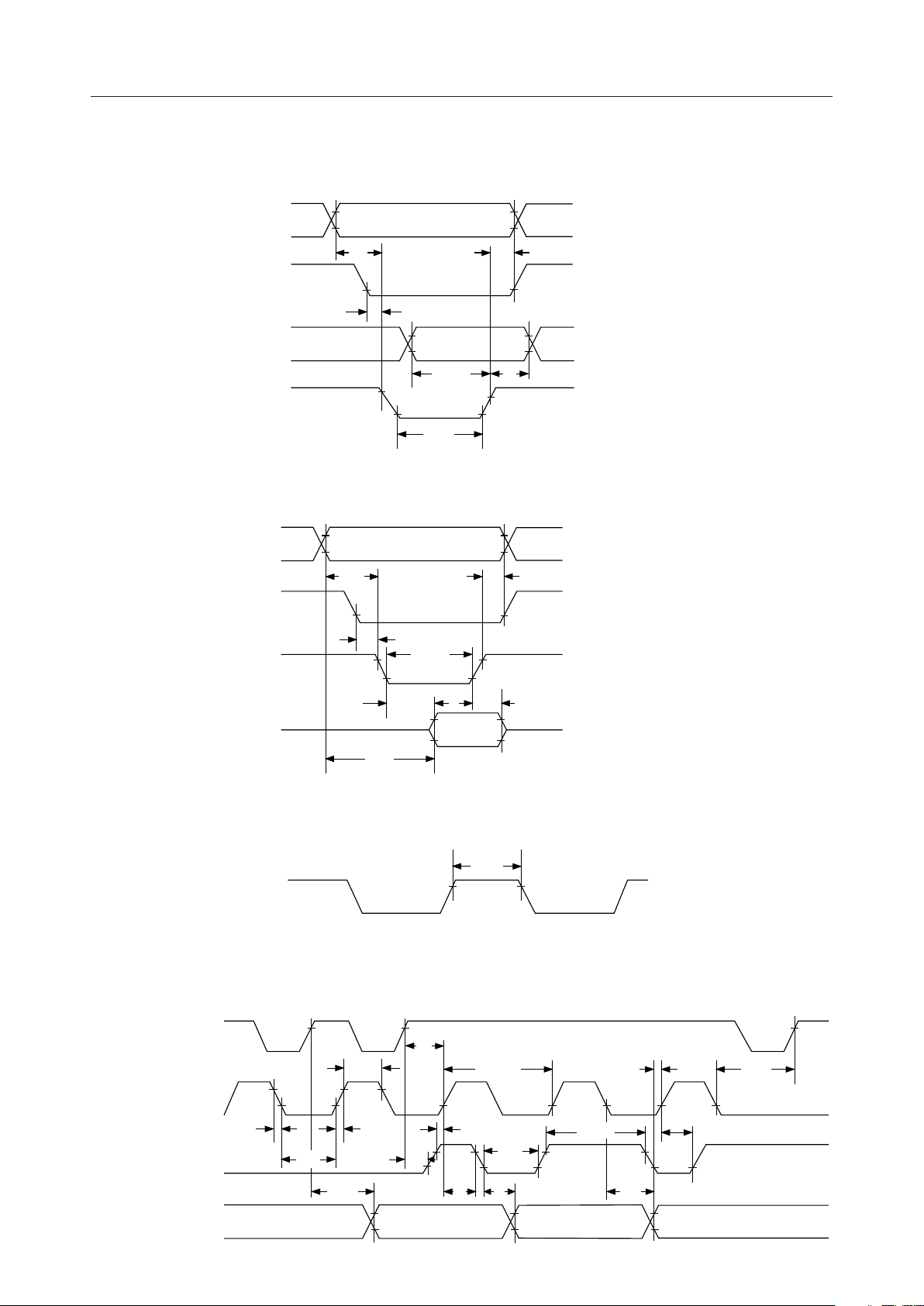

TIMING CHART

WriteTiming

A

0 - 1

Read Timing

D

CS

0 - 7

WR

t

AW

t

SW

t

DW

t

WW

t

WA

t

WD

A

0 - 1

CS

RD

D

0 - 7

Recovery Timing

RD, WR

Clock & Gate Timing

t

AR

t

SR

t

RR

t

RD

t

RA

t

DF

Valid

t

AD

t

RV

WR

CLK

GATE

OUT

Mode Count

t

PWH

t

PWL

t

f

t

WO

t

t

r

WG

t

WC

t

GH

Counter

Latch

t

CLK

t

GS

t

GL

t

ODG

t

GW

t

OD

t

GS

t

GH

t

CL

6/23

¡ Semiconductor MSM82C54-2RS/GS/JS

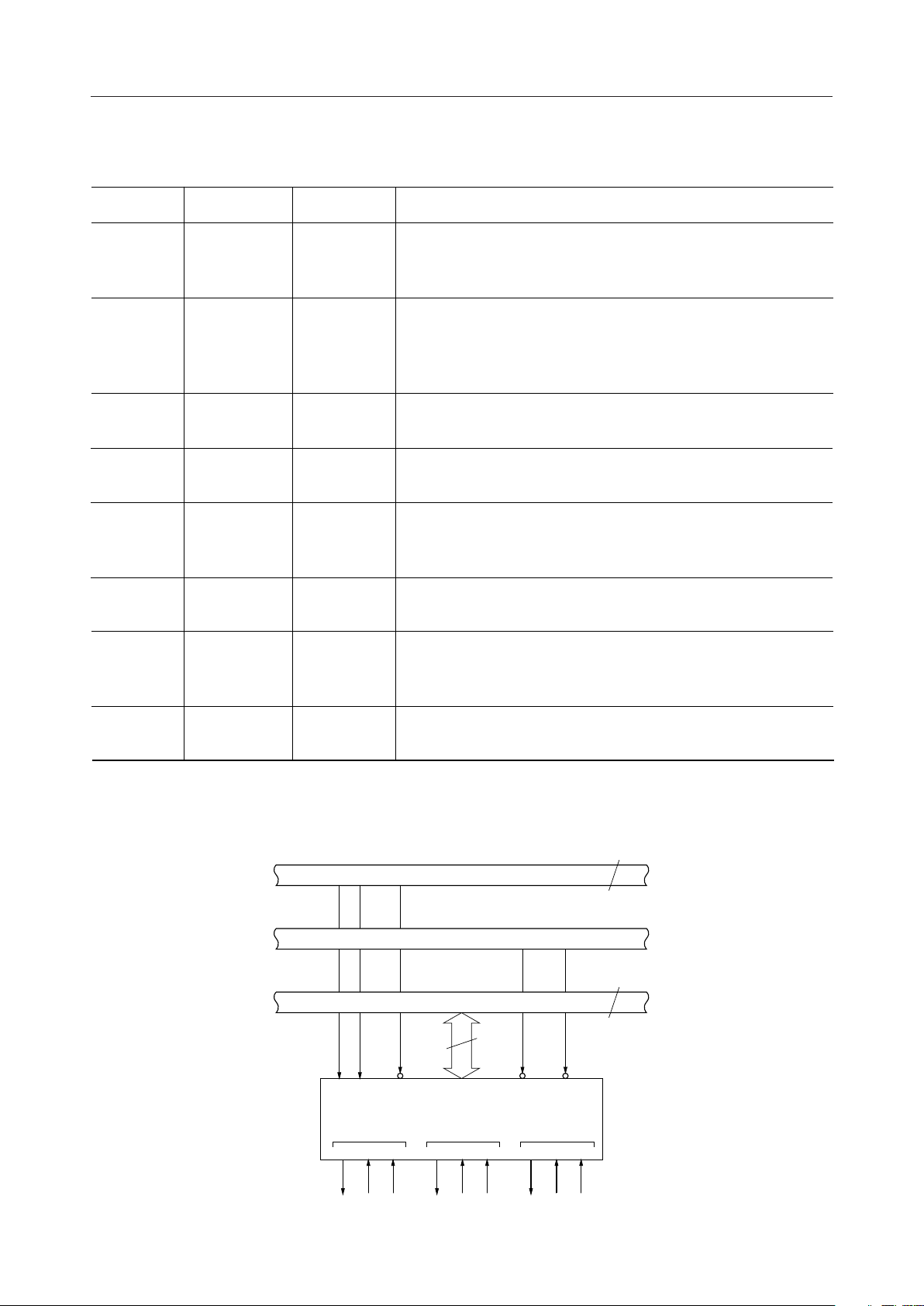

DESCRIPTION OF PIN FUNCTIONS

Pin Symbol

D7 - D

0

CS

RD

WR

A

, A

0

1

CLK0 -

2

GATE

-

0

2

Name

Bidirectional

Data Bus

Chip Select

Input

Read Input

Input/Output

Input/Output

Input

Input

Write Input Input

Address Input Input

Clock Input

Input

Gate Input Input

Function

Three-state 8-bit bidirectional data bus used when writing control

words and count value, and reading count values upon reception of

WR and RD signals from CPU.

Data transfer with the CPU is enabled when this pin is at low level.

When at high level, the data bus (D

thru D7) is switched to high

0

impedance state where neither writing nor reading can be executed.

Internal registers, however, remain unchanged.

Data can be transferred from MSM82C54-2 to CPU when this pin is

at low level.

Data can be transferred from CPU to MSM82C54-2 when this pin is

at low level.

One of the three internal counters or the control word register is

selected by A

combination. These two pins are normally

0/A1

connected to the two lower order bits of the address bus.

Supply of three clock signals to the three counters incorporated in

MSM82C54-2.

Control of starting, interruption, and restarting of counting in the

three respective counters in accordance with the set control word

contents.

OUT

- 2Counter Output Output

0

SYSTEM INTERFACING

A1A

0

A1A0CS

Counter #0

OUT GATE CLK

Output of counter output wave form in accordance with the set

mode and count value.

Adress Bus

16 bits

Control Bus

Data Bus

8 bits

8 bits

0

RD WR

D

-

7

MSM82C54-2

Counter #1

OUT GATE CLK

Counter #2

OUT GATE CLK

7/23

Loading...

Loading...