Page 1

MSM80C154S/83C154S¡ Semiconductor

¡ Semiconductor

MSM80C154S/83C154S

CMOS 8-bit Microcontroller

GENERAL DESCRIPTION

The MSM80C154S/MSM83C154S, designed for the high speed version of the existing

MSM80C154/MSM83C154, is a higher performance 8-bit microcontroller providing low-power

consumption.

The MSM80C154S/MSM83C154S covers the functions and operating range of the existing

MSM80C154/83C154/80C51F/80C31F.

The MSM80C154S is identical to the MSM83C154S except it does not contain the internal

program memory (ROM).

FEATURES

• Operating range

Operating frequency : 0 to 3 MHz (Vcc=2.2 to 6.0 V)

0 to 12 MHz (Vcc=3.0 to 6.0 V)

0 to 24 MHz (Vcc=4.5 to 6.0 V)

Operating voltage : 2.2 to 6.0 V

Operating temperature : –40 to +85°C (Operation at +125°C conforms to

the other specification.)

• Fully static circuit

• Upward compatible with the MSM80C51F/80C31F

• On-chip program memory : 16K words x 8 bits ROM (MSM83C154S only)

• On-chip data memory : 256 words x 8 bits RAM

• External program memory address space : 64K bytes ROM (Max)

• External data memory address space : 64K bytes RAM

• I/O ports : 4 ports x 8 bits

(Port 1, 2, 3, impedance programmable) : 32

• 16-bit timer/counters : 3

• Multifunctional serial port : I/O Expansion mode

: UART mode (featuring error detection)

• 6-source 2-priority level

Interrupt and multi-level

Interrupt available by programming IP and IE registers

• Memory-mapped special function registers

• Bit addressable data memory and SFRs

• Minimum instruction cycle : 500 ns @ 24 MHz operation

• Standby functions : Power-down mode (oscillator stop)

Activated by software or hardware; providing

ports with floating or active status

The software power-down stet mode is terminated by interrupt signal enabling execution from

the interrupted address.

259

Page 2

¡ SemiconductorMSM80C154S/83C154S

• Package options

40-pin plastic DIP (DIP40-P-600-2.54) :

44-pin plastic QFP (QFP44-P-910-0.80-2K) :

44-pin QFJ (QFJ44-P-S650-1.27) : (Product name: MSM80C154SJS/

44-pin TQFP (TQFP44-P-1010-0.80-K) : (Product name: MSM80C154STS-K/

(Product name: MSM80C154SRS/

MSM83C154S-xxxRS)

(Product name: MSM80C154SGS-2K/

MSM83C154S-xxxGS-2K)

MSM83C154S

MSM83C154S-xxxTS-K)

xxx: indicates the code number

-xxx

JS)

260

Page 3

P2.0

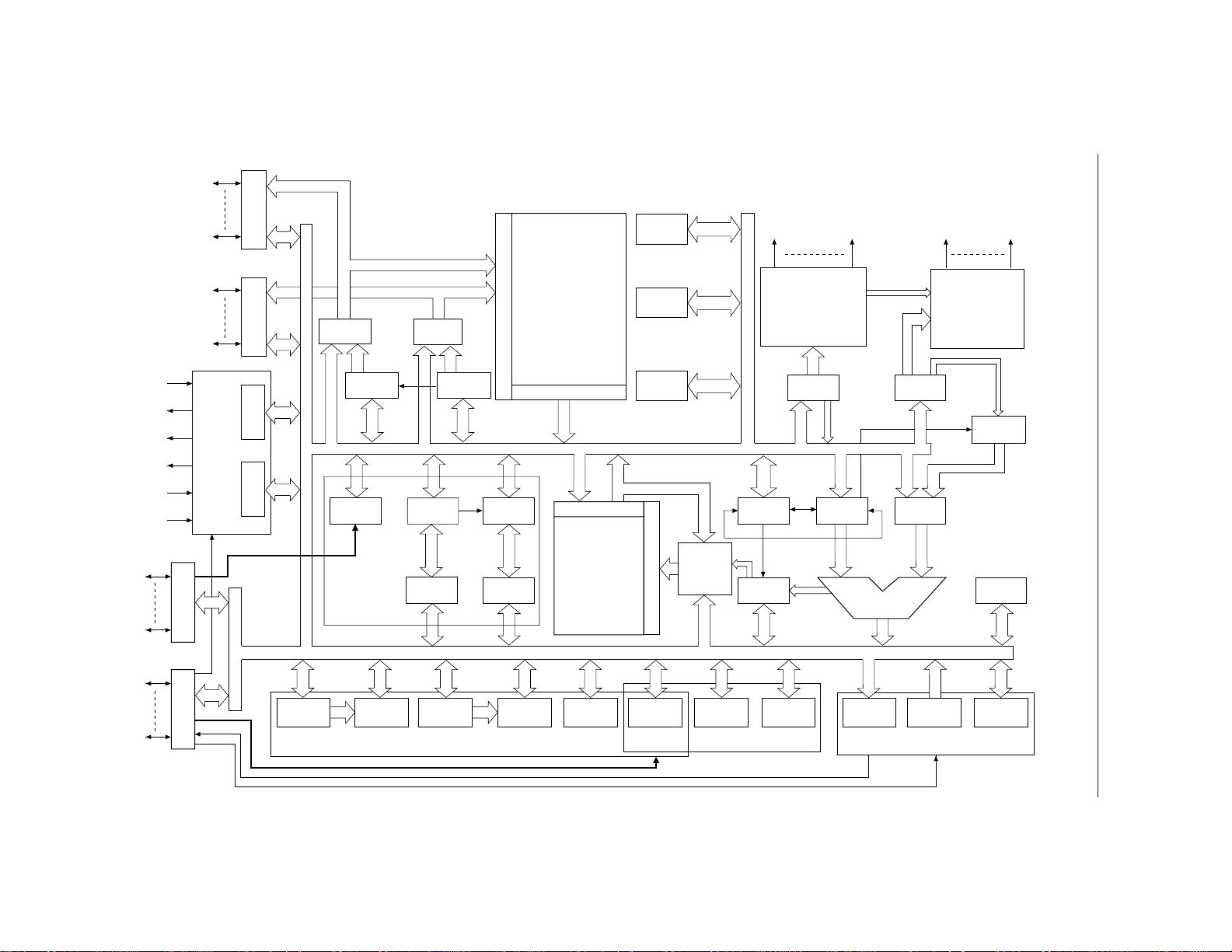

BLOCK DIAGRAM (MSM83C154S)

XTAL1

XTAL2

RESET

P1.0

P1.7

ALE

PSEN

EA

P2.7

P0.0

P0.7

OSC and TIMING

PORT 1PORT 3

PORT 2PORT 0

PCONIOCON

PCHL

PCH

T2CON

TIMER/

COUNTER 2

PCLL

TL2

RCAP2L

PCL

ROM

16K WORDS x 8BITS

ADDRESS DECODER

SENSE AMP

TH2

RCAP2H

R/W AMP

RAM

256 WORDS

x 8BITS

DPH

DPL

SP

RAMDP

CONTROL SIGNAL

PLA

IR AIR

TR2ACC

PSW

SIGNALR/W

SPECIAL

FUNCTION

REGISTER

ADDRESS

DECODER

C-ROM

TR1

BR

ALU

MSM80C154S/83C154S¡ Semiconductor

261

P3.0

P3.7

TH1 TL1 TH0 TL0 TMOD TCON IE IP SBUF(T) SBUF(R)

TIMER/COUNTER 0 & 1

INTERRUPT

SERIAL IO

SCON

Page 4

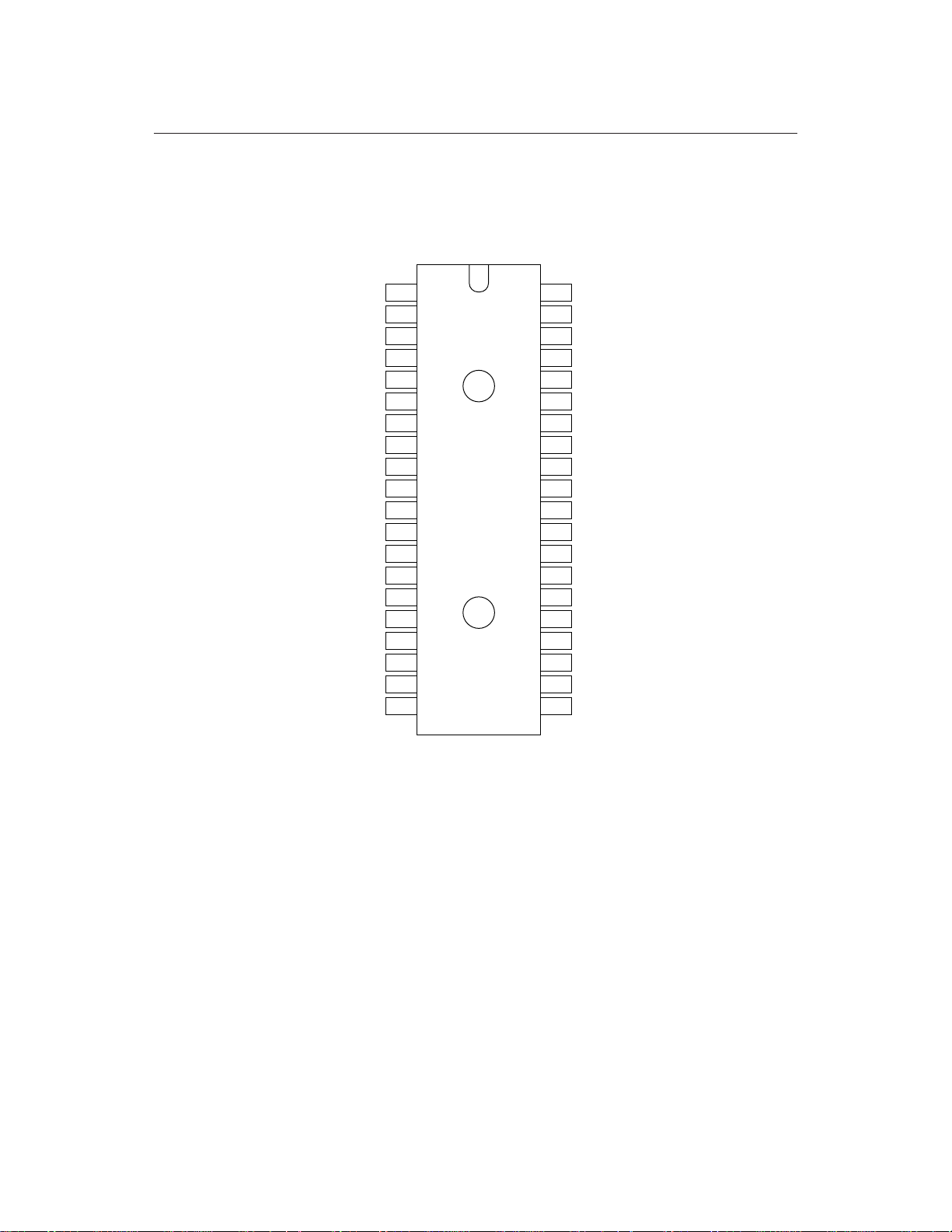

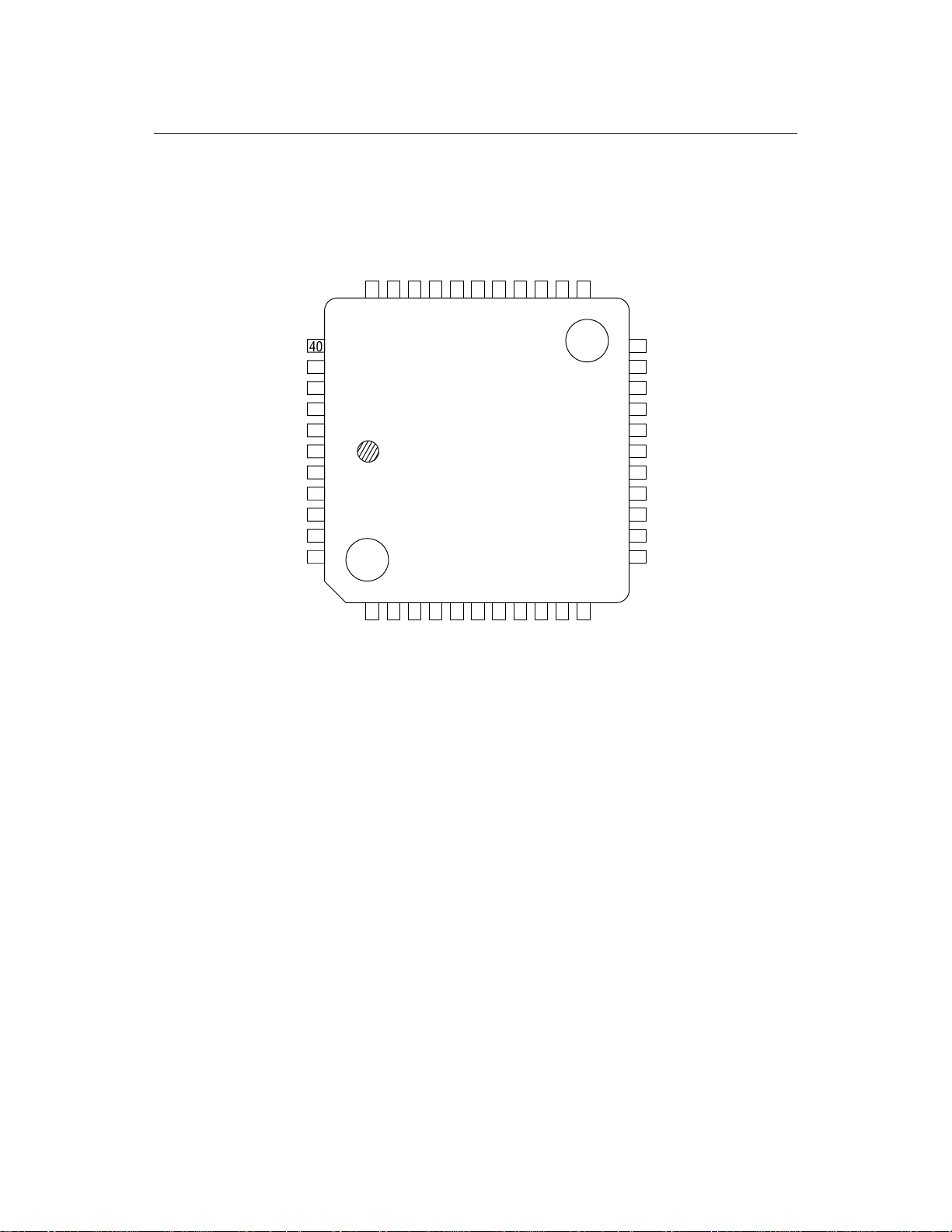

PIN CONFIGURATION (TOP VIEW)

¡ SemiconductorMSM80C154S/83C154S

P1.0/T2

P1.1/T2EX

P1.2

P1.3

P1.4

P1.5

P1.6

P1.7

RESET

P3.0/RXD

P3.1/TXD

P3.2/INT0

P3.3/INT1

P3.4/T0

P3.5/T1/HPDI

P3.6/WR

P3.7/RD

XTAL2

XTAL1

V

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

SS

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

V

CC

P0.0

P0.1

P0.2

P0.3

P0.4

P0.5

P0.6

P0.7

EA

ALE

PSEN

P2.7

P2.6

P2.5

P2.4

P2.3

P2.2

P2.1

P2.0

262

40-Pin Plastic DIP

Page 5

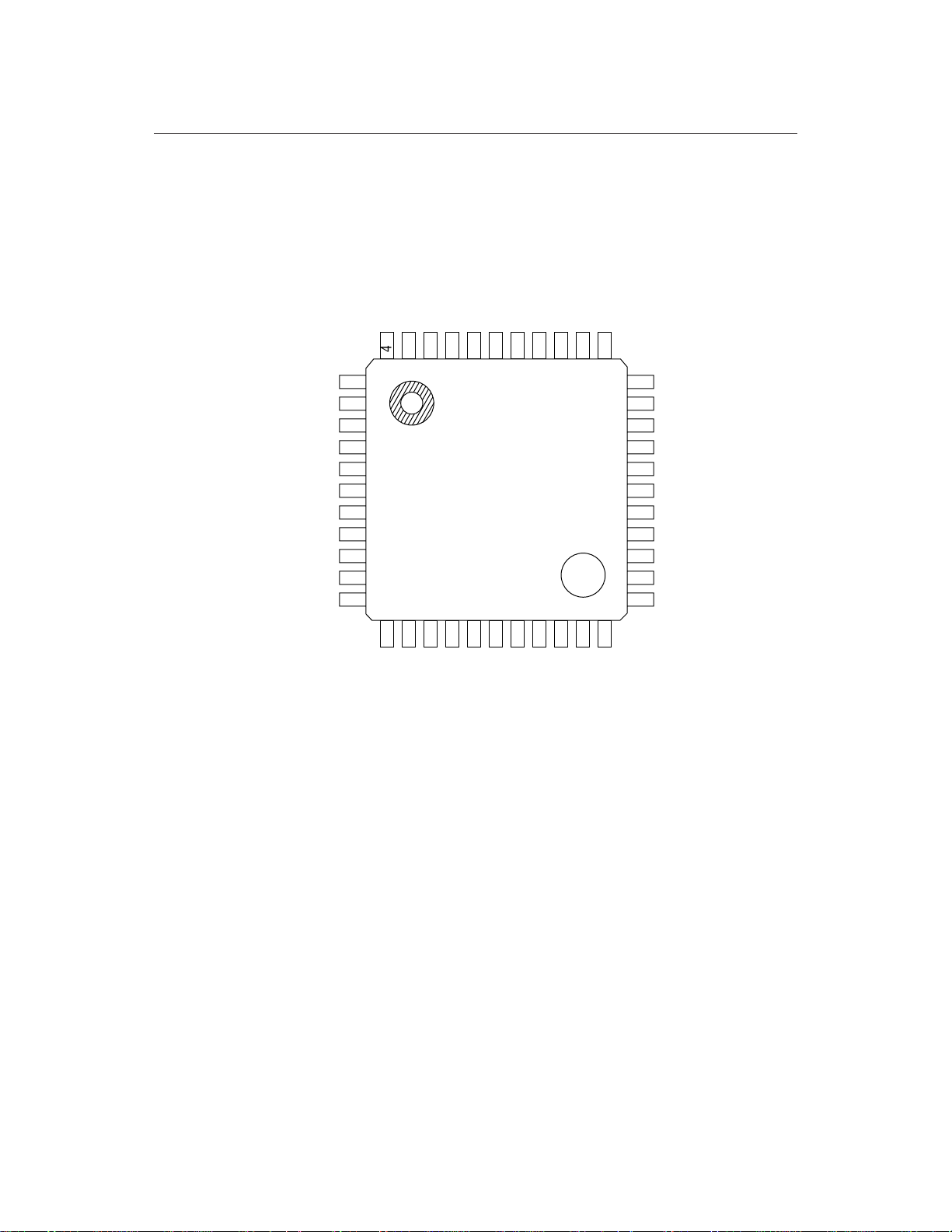

PIN CONFIGURATION (Continued)

P1.4

4443424140393837363534

P1.3

P1.2

P1.1

P1.0NCV

MSM80C154S/83C154S¡ Semiconductor

CC

P0.0

P0.1

P0.2

P0.3

P1.5

P1.6

P1.7

RESET

P3.0/RXD

NC

P3.1/TXD

P3.2/INT0

P3.3/INT1

P3.4/T0

P3.5/T1/HPDI

1

2

3

4

5

6

7

8

9

10

11

1213141516171819202122

SSVSS

V

XTAL2

XTAL1

P3.7/RD

P3.6/WR

NC : No-connection pin

44-Pin Plastic QFP

P2.0

P2.1

P2.2

P2.3

P2.4

33

32

31

30

29

28

27

26

25

24

23

P0.4

P0.5

P0.6

P0.7

EA

NC

ALE

PSEN

P2.7

P2.6

P2.5

263

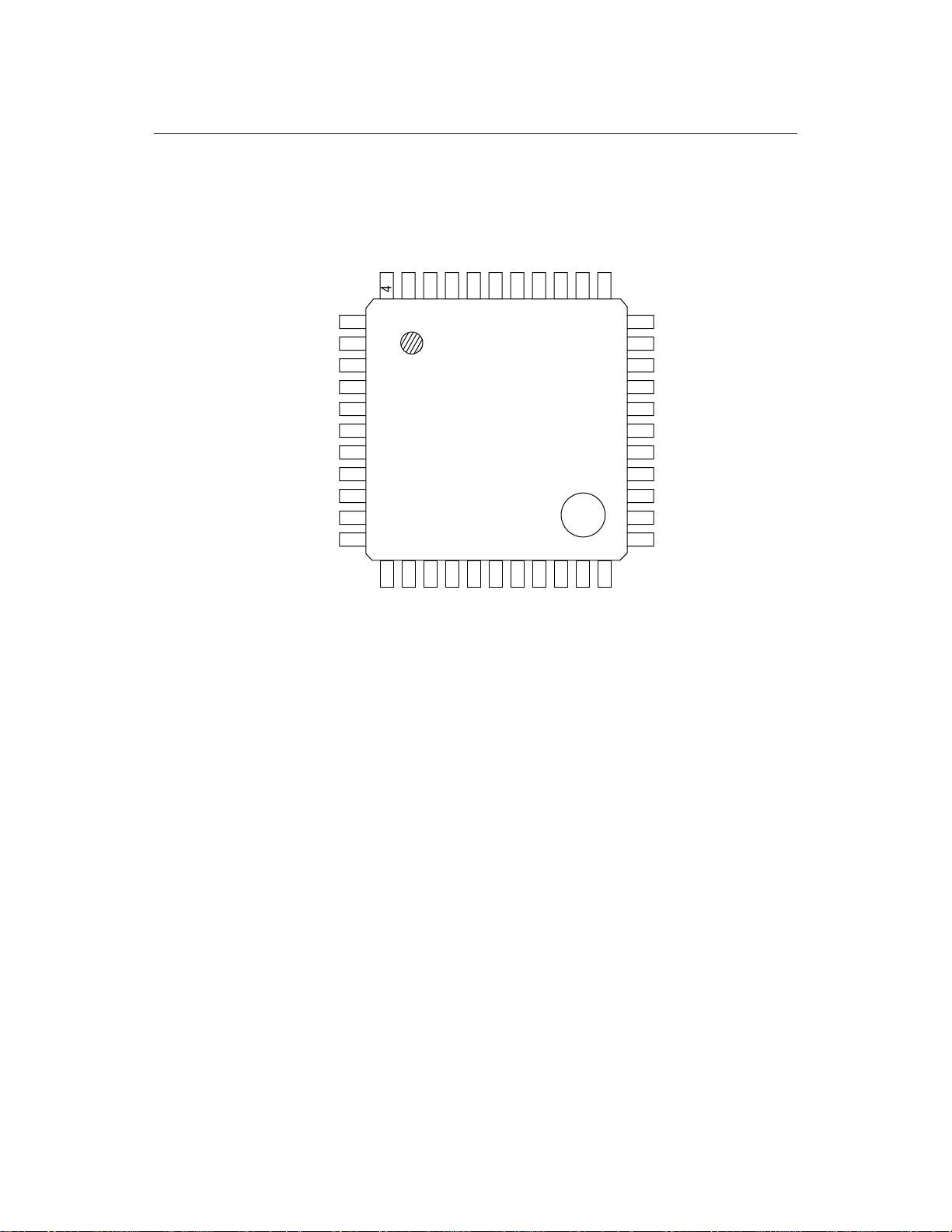

Page 6

CC

P0.0

P0.1

P0.2

P1.4

P1.3

P1.2

P1.1

P1.0NCV

4443424140393837363534

P0.3

¡ SemiconductorMSM80C154S/83C154S

P1.5

P1.6

P1.7

RESET

P3.0/RXD

NC

P3.1/TXD

P3.2/INT0

P3.3/INT1

P3.4/T0

P3.5/T1/HPDI

1

2

3

4

5

6

7

8

9

10

11

1213141516171819202122

SSVSS

V

XTAL2

XTAL1

P3.7/RD

P3.6/WR

NC : No-connection pin

44-Pin Plastic TQFP

P2.0

P2.1

P2.2

P2.3

P2.4

33

32

31

30

29

28

27

26

25

24

23

P0.4

P0.5

P0.6

P0.7

EA

NC

ALE

PSEN

P2.7

P2.6

P2.5

264

Page 7

PIN CONFIGURATION (Continued)

P0.5

P0.4

3938373635343332313029

P0.6

P0.7EANC

ALE

PSEN

P2.7

P2.6

MSM80C154S/83C154S¡ Semiconductor

P2.5

P0.3

P0.2

P0.1

P0.0

V

NC

P1.0/T2

P1.1/T2EX

P1.2

P1.3

P1.4

40

41

42

43

44

CC

1

2

3

4

5

6

7

8

9

P1.5

10111213141516

P1.6

P1.7

NC

RESET

P3.0/RXD

P3.1/TXD

P3.2/INT0

P3.3/INT1

17

P3.4/T0

P3.5/T1/HPDI

28

27

26

25

24

23

22

21

20

19

18

P2.4

P2.3

P2.2

P2.1

P2.0

NC

V

SS

XTAL1

XTAL2

P3.7/RD

P3.6/WR

NC : No-connection pin

44-Pin Plastic QFJ

265

Page 8

PIN DESCRIPTIONS

Symbol Descriptipn

P0.0 to P0.7

Bidirectional I/O ports. They are also the data/address bus (input/output of data and output of

lower 8-bit address when external memory is accessed).

They are open-drain outputs when used as I/O ports, but 3-state outputs when used as data/address

bus.

¡ SemiconductorMSM80C154S/83C154S

P1.0 to P1.7

P2.0 to P2.7

P3.0 to P3.7

P1.0 to P1.7 are quasi-bidirectional I/O ports. They are pulled up internally when used as input

ports. Two of them have the following secondary functions:

•P1.0 (T2)

•P1.1 (T2EX)

P2.0 to P2.7 are quasi-bidirectional I/O ports. They also output the higher 8-bit address when

an external memory is accessed. They are pulled up internally when used as input ports.

P3.0 to P3.7 are quasi-bidirectional I/O ports. They are pulled up internally when used as input

ports. They also have the following secondary functions:

•P3.0 (RXD)

Serial data input/output in the I/O expansion mode and serial data input in the UART mode when

the serial port is used.

•3.1 (TXD)

Synchronous clock output in the I/O expansion mode and serial data output in the UART mode

when the serial port is used.

•3.2 (INT0)

Used as input pin for the external interrupt 0, and as count-up control pin for the timer/counter 0.

•3.3 (INT1)

Used as input pin for the external interrupt 1, and as count-up control pin for the timer/counter 1.

•3.4 (T0)

Used as external clock input pin for the timer/counter 0.

•3.5 (T1)

Used as external clock input pin for the timer/counter 1 and power-down-mode control input pin.

•3.6 (WR)

Output of the write-strobe signal when data is written into external data memory.

•3.7 (RD)

Output of the read-strobe signal when data is read from external data memory.

: used as external clock input pins for the timer/counter 2.

: used as trigger input for the timer/counter 2 to be reloaded or captured;

causing the timer/counter 2 interrupt.

ALE

PSEN

EA

266

Address latch enable output for latching the lower 8-bit address during external memory access.

Two ALE pulses are activated per machine cycle except during external data memory access at

which time one ALE pulse is skipped.

Program store enable output which enables the external memory output to the bus during external

program memory access. Two PSEN pulses are activated per machine cycle except during

external data memory access at which two PSEN pulses are skipped.

When EA is held at "H" level, the MSM 83C154S executes instructions from internal program

memory at address 0000H to 3FFFH, and executes instructions from external program memory

above address 3FFFH.

When EA is held at "L" level, the MSM80C154S/MSM83C154S executes instructions from external

program memory for all addresses.

Page 9

PIN Descriptions (Continued)

Symbol Descriptipn

RESET

If this pin remains "H" for at least one machine cycle, the MSM80C154S/MSM83C154S is reset.

Since this pin is pulled down internally, a power-on reset is achieved by simply connecting a

capacitor between V

and this pin.

CC

MSM80C154S/83C154S¡ Semiconductor

XTAL1

XTAL2

V

CC

V

SS

Oscillator inverter input pin. External clock is input through XTAL1 pin.

Oscillator inverter output pin.

Power supply pin during both normal operation and standby operations.

GND pin.

267

Page 10

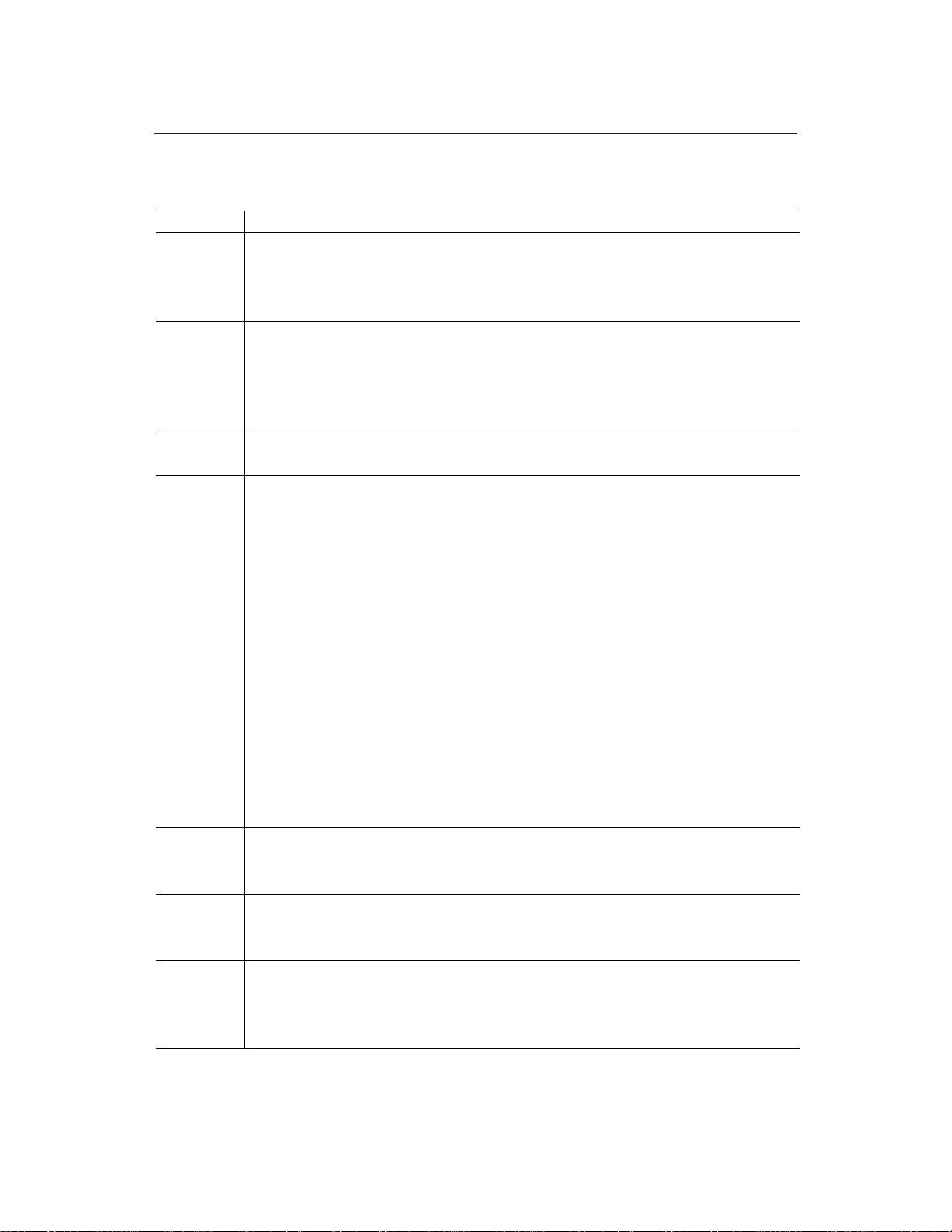

REGISTERS

Diagram of Special Function Registers

¡ SemiconductorMSM80C154S/83C154S

REGISTER

NAME

IOCON

B

ACC

PSW

TH2

TL2

RCAP2H

RCAP2L

T2CON

IP

P3

IE

P2

SBUF

SCON

P1

TH1

TH0

TL1

TL0

TMOD

TCON

PCON

DPH

DPL

SP

P0

b7 b5 b4 b3 b2 b1 b0b6

FF

F7

E7

D7

CF

BF

B7

AF

A7

9F

97

8F

87

FE

F6

E6

D6

CE

BE

B6

AE

A6

9E

96

8E

86

BIT ADDRESS

FD

F5

E5

D5

CD

BD

B5

AD

A5

9D

95

8D

85

FC

F4

E4

D4

CC

BC

B4

AC

A4

9C

94

8C

84

FB

F3

E3

D3

CB

BB

B3

AB

A3

9B

93

8B

83

FA

F2

E2

D2

CA

BA

B2

AA

A2

9A

92

8A

82

F9

F1

E1

D1

C9

B9

B1

A9

A1

99

91

89

81

F8

F0

E0

D0

C8

B8

B0

A8

A0

98

90

88

80

DIRECT

ADDRESS

0F8H (248)

0F0H (240)

0E0H (224)

0D0H (208)

0CDH (205)

0CCH (204)

0CBH (203)

0CAH (202)

0C8H (200)

0B8H (184)

0B0H (176)

0A8H (168)

0A0H (160)

99H (153)

98H (152)

90H (144)

8DH (141)

8CH (140)

8BH (139)

8AH (138)

89H (137)

88H (136)

87H (135)

83H (131)

82H (130)

81H (129)

80H (128)

268

Page 11

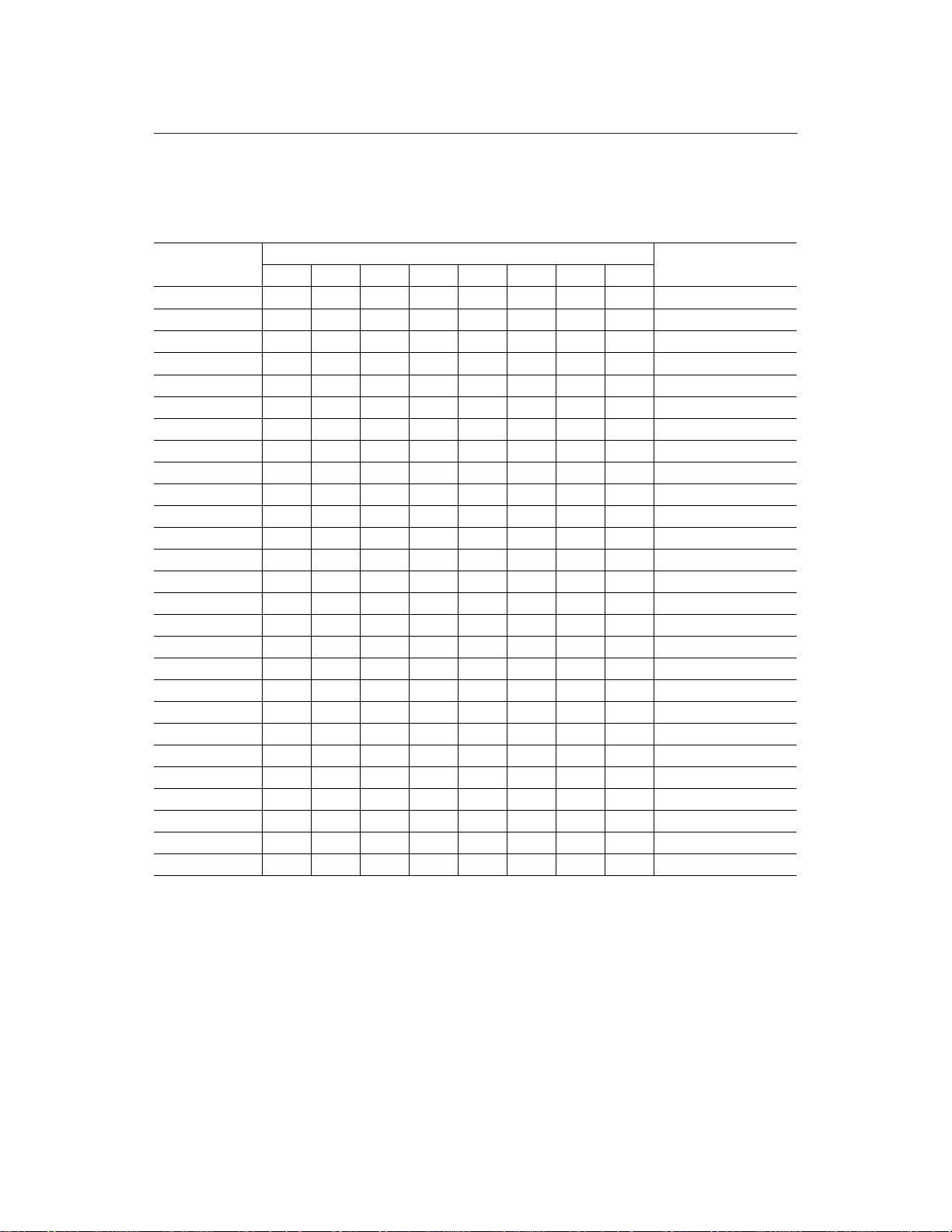

Special Function Registers

Timer mode register (TMOD)

MSM80C154S/83C154S¡ Semiconductor

NAME

TMOD 89H GATE C/T M1 M0 GATE C/T M1 M0

BIT LOCATION FLAG FUNCTION

TMOD.0 M0 M1 M0

TMOD.2 C/T

TMOD.3 GATE

TMOD.4 M0 M1 M0

TMOD.5 M1

TMOD.6 C/T

TMOD.7 GATE

ADDRESS

MSB LSB

76543210

Timer/counter 0 mode setting

00

01

10

11TMOD.1 M1

Timer/counter 0 count clock designation control bit.

XTAL1•2 divided by 12 clocks is the input applied to timer/counter 0 when

C/T = "0".

The external clock applied to the T0 pin is the input applied to timer/counter 0

when C/T = "1".

When this bit is "0", the TR0 bit of TCON (timer control register) is used to

control the start and stop of timer/counter 0 counting.

If this bit is "1", timer/counter 0 starts counting when both the TR0 bit of TCON

and INT0 pin input signal are "1", and stops counting when either is changed

to "0".

00

01

10

11

Timer/counter 1 count clock designation control bit.

XTAL1•2 divided by 12 clocks is the input applied to timer/counter 1 when

C/T = "0".

The external clock applied to the T1 pin is the input applied to timer/counter 1

when C/T = "1".

When this bit is "0", the TR1 bit of TCON is used to control the start and stop of

timer/counter 1 counting.

If this bit is "1", timer/counter 1 starts counting when both the TR1 bit of TCON

and INT1 pin input signal are "1", and stops counting when either is changed

to "0".

8-bit timer/counter with 5-bit prescalar.

16-bit timer/counter.

8-bit timer/counter with 8-bit auto reloading.

Timer/counter 0 separated into TLO (8-bit) timer/counter

and TH0 (8-bit) timer/counter. TF0 is set by TL0 carry, and

TF1 is set by TH0 carry.

Timer/counter 1 mode setting

8-bit timer/counter with 5-bit prescalar.

16-bit timer/counter

8-bit timer/counter with 8-bit auto reloading.

Timer/counter 1 operation stopped.

269

Page 12

Power control register (PCON)

¡ SemiconductorMSM80C154S/83C154S

NAME

PCON 87H SMOD HPD RPD — GF1 GF0 PD IDL

BIT LOCATION FLAG FUNCTION

PCON.0 IDL

PCON.1 PD

PCON.5 RPD

ADDRESS

MSB LSB

76543210

IDLE mode is set when this bit is set to "1". CPU operations are stopped when

IDLE mode is set, but XTAL1•2, timer/counters 0, 1 and 2, the interrupt circuits,

and the serial port remain active. IDLE mode is cancelled when the CPU is reset

or when an interrupt is generated.

PD mode is set when this bit is set to "1". CPU operations and XTAL1•2 are

stopped when PD mode is set. PD mode is cancelled when the CPU is reset or

when an interrupt is generated.

General purpose bit.PCON.2 GF0

General purpose bit.PCON.3 GF1

Reserved bit. The output data is "1", if the bit is read.PCON.4 —

This bit is used to specify cancellation of CPU power down mode (IDLE or PD) by an

interrupt signal.

Power-down mode cannot be cancelled by an interrupt signal if the interrupt is not

enabled by IE (interrupt enable register) when this bit is "0".

If the interrupt flag is set to "1" by an interrupt request signal when this bit is

"1" (even if interrupt is disabled), the program is executed from the next address

of the power-down-mode setting instruction.

The flag is reset to "0" by software.

PCON.6 HPD

PCON.7 SMOD

The hard power-down setting mode in enabled when this bit is set to "1".

If the level of the power failure detect signal applied to the HPDI pin (pin 3.5)

is changed from "1" to "0" when this bit is "1", XTAL1•2 oscillation is stopped and

the system is put into hard power down mode. HPD mode is cancelled when the

CPU is reset.

When the timer/counter 1 carry signal is used as a clock in mode 1, 2 or 3 of

the serial port, this bit has the following functions.

The serial port operation clock is reduced by 1/2 when the bit is "0" for delayed

processing. When the bit is "1", the serial port operation clock is normal

for faster processing.

270

Page 13

Timer control register (TCON)

MSM80C154S/83C154S¡ Semiconductor

NAME

TCON 88H TF1 TR1 TF0 TR0 IE1 IT1 IE0 IT0

BIT LOCATION FLAG FUNCTION

TCON.0 IT0

TCON.1 IE0

TCON.2 IT1

TCON.3 IE1

TCON.4 TR0

TCON.5 TF0

TCON.6 TR1

ADDRESS

MSB LSB

76543210

External interrupt 0 signal is used in level-detect mode when this bit is "0" and in

trigger detect mode when "1".

Interrupt request flag for external interrupt 0.

The bit is reset automatically when an interrupt is serviced.

The bit can be set and reset by software when IT0 = "1".

External interrupt 1 signal is used in level detect mode when this bit is "0", and in

trigger detect mode when "1".

Interrupt request flag for external interrupt 1.

The bit is reset automatically when an interrupt is serviced.

The bit can be set and reset by software when IT1 = "1".

Counting start and stop control bit for timer/counter 0.

Timer/counter 0 starts counting when this bit is "1", and stops counitng when "0".

Interrupt request flag for timer interrupt 0.

The bit is reset automatically when an interrupt is serviced.

The bit is set to "1" when a carry signal is generated from timer/counter 0.

Counting start and stop control bit for timer/counter 1.

The timer/counter 1 starts counting when this bit is "1", and stops counting when "0".

TCON.7 TF1

Interrupt request flag for timer interrupt 1.

The bit is reset automatically when interrupt is serviced.

The bit is set to "1" when carry signal is generated from timer/counter 1.

271

Page 14

Serial port control register (SCON)

¡ SemiconductorMSM80C154S/83C154S

NAME

SCON 98H SM0 SM1 SM2 REN TB8 RB8 TI RI

BIT LOCATION FLAG FUNCTION

SCON.0 RI

SCON.1 TI

SCON.2 RB8

SCON.3 TB8

SCON.4 REN

ADDRESS

MSB LSB

76543210

"End of serial port reception" interrupt request flag.

This flag must be reset by software during interrupt service routine.

This flag is set after the eighth bit of data has been received when in mode 0, or

by the STOP bit when in any other mode.

In mode 2 or 3, however, RI is not set if the RB8 data is "0" with SM2 = "1".

RI is set in mode 1 if STOP bit is received when SM2 = "1".

"End of serial port tramsmission" interrupt request flag. This flag must be reset

by software during interrupt service routine.

This flag is set after the eighth bit of data has been sent when in mode 0, or after

the last bit of data has been sent when in any other mode.

The ninth bit of data received in mode 2 or 3 is passed to RB8.

The STOP bit is applied to RB8 if SM2 = "0" when in mode 1.

RB8 can not be used in mode 0.

The TB8 data is sent as the ninth data bit when in mode 2 or 3.

Any desired data can be set in TB8 by software.

Reception enable control bit.

No reception when REN = "0".

Reception enabled when REN = "1".

SCON.5 SM2

SCON.6 SM1 SM0 SM1

SCON.7 SM0

If the ninth bit of received data is "0" with SM2 = "1" in mode 2 or 3, the "end of

reception" signal is not set in the RI flag.

The "end of reception" signal set in the RI flag if the STOP bit is not "1" when

SM2 = "1" in mode 1.

00

01

10

11

MODE

0

1

2

3

8-bit shift register I/O

8-bit UART variable baud rate

9-bit UART 1/32 XTAL1, 1/64 XTAL1 baud rate

9-bit UART variable baud rate

272

Page 15

Interrupt enable register (IE)

MSM80C154S/83C154S¡ Semiconductor

NAME

IE 0A8H EA — ET2 ES ET1 EX1 ET0 EX0

BIT LOCATION FLAG FUNCTION

IE.0 EX0

IE.1 ET0

IE.2 EX1

IE.3 ET1

IE.4 ES

IE.5 ET2

ADDRESS

MSB LSB

76543210

Interrupt control bit for external interrupt 0.

Interrupt disabled when bit is "0".

Interrupt enabled when bit is "1".

Interrupt control bit for timer interrupt 0.

Interrupt disabled when bit is "0".

Interrupt enabled when bit is "1".

Interrupt control bit for external interrupt 1.

Interrupt disabled when bit is "0".

Interrupt enabled when bit is "1".

Interrupt control bit for timer interrupt 1.

Interrupt disabled when bit is "0".

Interrupt enabled when bit is "1".

Interrupt control bit for serial port.

Interrupt disabled when bit is "0".

Interrupt enabled when bit is "1".

Interrupt control bit for timer interrupt 2.

Interrupt disabled when bit is "0".

Interrupt enabled when bit is "1".

IE.6 —

IE.7 EA

Reserved bit. The output data is "1" if the bit is read.

Overall interrupt control bit.

All interrupts are disabled when bit is "0".

All interrupts are controlled by IE.0 thru IE.5 when bit is "1".

273

Page 16

Interrupt priority register (IP)

¡ SemiconductorMSM80C154S/83C154S

NAME

IP 0B8H PCT — PT2 PS PT1 PX1 PT0 PX0

BIT LOCATION FLAG FUNCTION

IP.0 PX0

IP.1 PT0

IP.2 PX1

IP.3 PT1

IP.4 PS

IP.5 PT2

IP.6 —

IP.7 PCT

ADDRESS

MSB LSB

76543210

Interrupt priority bit for external interrupt 0.

Priority is assigned when bit is "1".

Interrupt priority bit for timer interrupt 0.

Priority is assigned when bit is "1".

Interrupt priority bit for external interrupt 1.

Priority is assigned when bit is "1".

Interrupt priority bit for timer interrupt 1.

Priority is assigned when bit is "1".

Interrupt priority bit for serial port.

Priority is assigned when bit is "1".

Interrupt priority bit for timer interrupt 2.

Priority is assigned when bit is "1".

Reserved bit. The output data is "1" if the bit is read.

Priority interrupt circuit control bit.

The priority register contents are valid and priority assigned interrupts can be

processed when this bit is "0". When the bit is "1", the priority interrupt circuit is

stopped, and interrupts can only be controlled by the interrupt enable register (IE).

274

Page 17

Program status word register (PSW)

MSM80C154S/83C154S¡ Semiconductor

NAME

ADDRESS

MSB LSB

76543210

PSW 0D0H CY AC F0 RS1 RS0 OV F1 P

BIT LOCATION FLAG FUNCTION

PSW.0 P

Accumulator (ACC) parity indicator.

This bit is "1" when the "1" bit number in the accumulator is an odd number, and

"0" when an even number.

User flag which may be set to "0" or "1" as desired by the user.PSW.1 F1

PSW.2 OV

Overflow flag which is set if the carry C6 from bit 6 of the ALU or CY is "1" as a

result of an arithmetic operation. The flag is also set to "1" if the resultant product

of executing multiplication instruction (MUL AB) is greater than 0FFH, but is reset

to "0" if the product is less than or equal to 0FFH.

RAM register bank switchPSW.3 RS0

RAM ADDRESS

PSW.4 RS1

RS1 RS0

00

01

10

11

BANK

0

1

2

3

00H - 07H

08H - 0FH

10H - 17H

18H - 1FH

User flag which may be set to "0" or "1" as desired by the user.PSW.5 F0

PSW.6 AC

Auxiliary carry flag.

This flag is set to "1" if a carry C

is generated from bit 3 of the ALU as a result of

3

executing an arithmetic operation instruction.

In all other cases, the flag is reset to "0".

PSW.7 CY

Main carry flag.

This flag is set to "1" if a carry C

is generated from bit 7 of the ALU as result of

7

executing an arithmetic operation instruction.

If a carry C

is not generated, the flag is reset to "0".

7

275

Page 18

I/O control register (IOCON)

¡ SemiconductorMSM80C154S/83C154S

NAME

IOCON 0F8H — T32 SERR IZC P3HZ P2HZ P1HZ ALF

BIT LOCATION FLAG FUNCTION

IOCON.0 ALF

IOCON.1 P1HZ

IOCON.2 P2HZ

IOCON.3 P3HZ

IOCON.4 IZC

IOCON.5 SERR

IOCON.6 T32

IOCON.7 —

ADDRESS

MSB LSB

76543210

If CPU power down mode (PD, HPD) is activated with this bit set to "1", the

outputs from ports 0, 1, 2, and 3 are switched to floating status.

When this bit is "0", ports 0, 1, 2, and 3 are in output mode.

Port 1 becomes a high impedance input port when this bit is "1".

Port 2 becomes a high impedance input port when this bit is "1".

Port 3 becomes a high impedance input port when this bit is "1".

The 10 kW pull-up resistor for ports 1, 2, and 3 is switched off when this bit

is "1", leaving only the 100 kW pull-up resistor.

Serial port reception error flag.

This flag is set to "1" if an overrun or framing error is generated when data is

received at a serial port.

The flag is reset by software.

Timer/counters 0 and 1 are connected serially to from a 32-bit timer/counter

when this bit is set to "1".

TF1 of TCON is set if a carry is generated in the 32-bit timer/counter.

Leave this bit at "0".

276

Page 19

Timer 2 control register (T2CON)

MSM80C154S/83C154S¡ Semiconductor

NAME

T2CON 0C8H TF2 EXF2 RCLK TCLK EXEN2 TR2 C/T2 CP/RL2

BIT LOCATION FLAG FUNCTION

T2CON.0 CP/RL2

T2CON.1 C/T2

T2CON.2 TR2

T2CON.3 EXEN2

T2CON.4 TCLK

T2CON.5 RCLK

T2CON.6 EXF2

T2CON.7 TF2

ADDRESS

MSB LSB

76543210

Capture mode is set when TCLK + RCLK = "0" and CP/RL2 = "1".

16-bit auto reload mode is set when TCLK + RCLK = "0" and CP/RL2 = "0".

CP/RL2 is ignored when TCLK + RCLK = "1".

Timer/counter 2 count clock designation control bit.

The internal clocks (XTAL1•2 ÷ 12, XTAL1•2 ÷ 2) are used when this bit is "0",

and the external clock applied to the T2 pin is passed to timer/counter 2 when

the bit is "1".

Timer/counter 2 counting start and stop control bit.

Timer/counter 2 commences counting when this bit is "1" and stops counting

when "0".

T2EX timer/counter 2 external control signal control bit.

Input of the T2EX signal is disabled when this bit is "0", and enabled when "1".

Serial port transmit circuit drive clock control bit.

Timer/counter 2 is switched to baud rate generator mode when this bit is "1",

and the timer/counter 2 carry signal becomes the serial port transmit clock.

Note, however, that the serial ports can only use the timer/counter 2 carry signal

in serial port modes 1 and 3.

Serial port receive circuit drive clock control bit.

Timer/counter 2 is switched to baud rate generator mode when this bit is "1",

and the timer/counter 2 carry signal becomes the serial port transmit clock.

Note, however, that the serial ports can only use the timer/counter 2 carry signal

in serial port modes 1 and 3.

Timer/counter 2 external flag.

This bit is set to "1" when the T2EX timer/counter 2 external control signal level

is changed from "1" to "0" while EXEN2 = "1".

This flag serves as the timer interrupt 2 request signal. If an interrupt is

generated, EXF2 must be reset to "0" by software.

Timer/counter 2 carry flag.

This bit is set to "1" by a carry signal when timer/counter 2 is in 16-bit auto

reload mode or in capture mode.

This flag serves as the timer interrupt 2 request signal. If an interrupt is

generated, TF2 must be reset to "0" by software.

277

Page 20

MEMORY MAPS

Program Area

65535

0FFFFH

¡ SemiconductorMSM80C154S/83C154S

002BH43Timer interrupt 2 start

0023H35S I/O interrupt start

001BH27Timer interrupt 1 start

MSM83C154S EXTERNAL ROM AREA

16384

4000H

16383

3FFFH

MSM80C154S EXTERNAL ROM AREA

44 002CH

43

002BH

MSM83C154S INTERNAL ROM AREA

7 6 5 4 3 2 1 00

0013H19External interrupt 1 start

000BH11Timer interrupt 0 start

0003H3External interrupt 0 start

0002H2

0001H1

0000H0CPU reset start

278

Page 21

MSM80C154S/83C154S¡ Semiconductor

Internal Data Memory and Special Function Register Layout Diagram

HEX

0FF

USER DATA RAM

REGISTER INDIRECT ADDRESSING

80

7F

USER DATA RAM

30

2F

20

1F

18

17

10

0F

08

07

00

7F

7

R7

R0

R7

R0

R7

R0

R7

R0

BIT RAM

BANK3

BANK2

BANK1

BANK0

78

0

B

FFH~F8H

F7H~F0H

E7H~E0H

D7H~D0H

CFH~C8H

BFH~B8H

B7H~B0H

AFH~A8H

A7H~A0H

9FH~98H

97H~90H

8FH~88H

87H~80H

BIT ADDRESSING

DATA ADDRESSING

IOCON

ACC

PSW

TH2

TL2

RCAP2H

RCAP2L

T2CON

IP

P3

IE

P2

SBUF

SCON

P1

TH1

SPECIAL FUNCTION REGISTERS

TH0

TL1

TL0

TMOD

TCON

PCON

DPH

DPL

SP

P0

248(0F8H)

240(0F0H)

224(0E0H)

208(0D0H)

205(0CDH)

204(0CCH)

203(OCBH)

202(0CAH)

200(0C8H)

184(0B8H)

176(0B0H)

168(0A8H)

160(0A0H)

153( 99H)

152( 98H)

144( 90H)

141( 8DH)

140( 8CH)

139( 8BH)

138( 8AH)

137( 89H)

136( 88H)

135( 87H)

131( 83H)

130( 82H)

129( 81H)

128( 80H)

279

Page 22

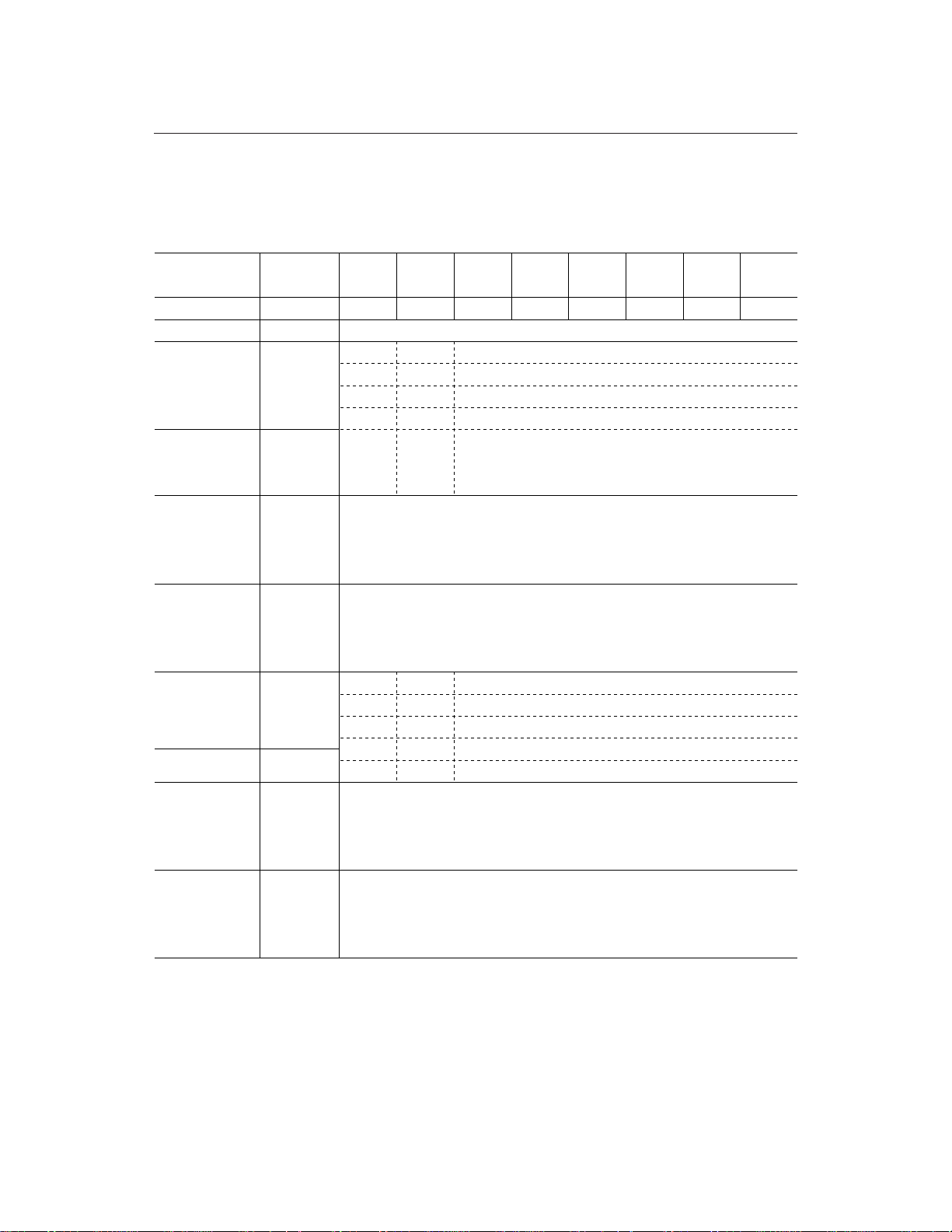

Diagram of Internal Data Memory (RAM)

¡ SemiconductorMSM80C154S/83C154S

0FFH

80H

7FH

30H

2FH

2EH

2DH

2CH

2BH

2AH

29H

28H

27H

26H

25H

24H

7F

77

6F

67

5F

57

4F

47

3F

37

2F

27

7E

76

6E

66

5E

56

4E

46

3E

36

2E

26

USER DATA RAM

USER DATA RAM

7D

7C

75

74

6D

6C

65

64

5D

5C

55

54

4D

4C

45

44

3D

3C

35

34

2D

2C

25

24

7B

73

6B

63

5B

53

4B

43

3B

33

2B

23

7A

72

6A

62

5A

52

4A

42

3A

32

2A

22

79

71

69

61

59

51

49

41

39

31

29

21

78

70

68

60

58

50

48

40

38

30

28

20

255

128

127

48

47

46

45

44

43

42

41

40

39

38

37

36

BIT ADDRESSING

DATA ADDRESSING

REGISTER 0, 1, INDIRECT ADDRESSING

23H

22H

21H

20H

1FH

18H

17H

10H

0FH

08H

07H

00H

1F

17

0F

07

1E

16

0E

06

1D

15

0D

05

1C

14

0C

04

Bank 3

Bank 2

Bank 1

Bank 0

1B

13

0B

03

1A

12

0A

02

19

11

09

01

18

10

08

00

35

34

33

32

31

24

23

16

15

8

7

0

REGISTERS 0-7 DIRIECT ADDRESSING

280

Page 23

MSM80C154S/83C154S¡ Semiconductor

ABSOLUTE MAXIMUM RATINGS

Parameter Symbol Condition Rating Unit

Supply voltage

Input voltage

Storage temperature

V

CC

V

I

T

STG

Ta=25°C –0.5 to 7 V

Ta=25°C –0.5 to VCC+0.5 V

— –55 to +150 °C

RECOMMENDED OPERATING CONDITIONS

Parameter Symbol Condition Range Unit

Power supply voltage

Memory retension voltage

Oxcillation frequency

External clock operating

V

CC

V

CC

f

OSC

f

EXTCLK

frequency

Ambient temperature

Ta — –40 to +85 °C

*1 Depends on the specifications for the oscillator or ceramic resonater.

See below 2.0 to 6.0 V

f

=0 Hz (Oscillation stop) 2.0 to 6.0 V

OSC

See below 1 to 24 MHz

See below 0 to 24 MHz

(ms)

t

12

5

4

3

CY

2

1

0.6

0.5

2.2

23456

Power Supply Voltage (VCC)

1

3

6

12

20

24

(MHz)

EXTCLK

f

OSC

f

281

Page 24

ELECTRICAL CHARACTERISTICS

DC Characteristics 1

Parameter Symbol Condition Min. Typ. Max. Unit

Input Low Voltage V

Input High Voltage V

Input High Voltage V

Output Low Voltage

(PORT 1, 2, 3)

Output Low Voltage

(PORT 0, ALE, PSEN)

Output High Voltage

(PORT 1, 2, 3)

Output High Voltage

(PORT 0, ALE, PSEN)

Logical 0 Input Current/

Logical 1 Output Current/

(PORT 1, 2, 3)

Logical 1 to 0 Transition

Output Current (PORT 1, 2, 3)

Input Leakage Current

(PORT 0 floating, EA)

RESET Pull-down Resistance R

Pin Capacitance C

Power Down Current I

IL

Except XTAL1, EA,

IH

XTAL1, RESET and EA 0.7 V

IH1

V

OL

V

OL1

V

OH

V

OH1

/ I

I

IL

OH

I

TL

I

LI

RST

Ta=25°C, f=1 MHz

IO

PD

¡ SemiconductorMSM80C154S/83C154S

(V

=4.0 to 6.0 V, VSS=0 V, Ta=-40 to +85°C)

CC

— –0.5 — V

0.2 V

+0.9 — V

and RESET

CC

CC

IOL=1.6 mA — — V

IOL=3.2 mA — — V

IOH=–60 mA

V

=5 V±10%

CC

=–30 mA 0.75 V

I

OH

=–10 mA 0.9 V

I

OH

IOH=–400 mA

V

=5 V±10%

CC

=–150 mA 0.75 V

I

OH

=–40 mA 0.9 V

I

OH

VI=0.45 V

V

=0.45 V

O

2.4 — V

CC

CC

2.4 — V

CC

CC

–5 –20 mA

VI=2.0 V — –190 mA

V

< VI < V

SS

CC

—— mA

—2040 kW

(except XTAL1)

—

—— pF

—1 mA

0.2 VCC–0.1

V

+0.5

CC

—V

V

+0.5

CC

0.45

0.45

—

—V

—V

—

—

—

—V

—V

—

—

–80

–500

±10

125

10

50

Meas-

uring

circuit

1

2

3

2

—

4

282

Page 25

Maximum power supply current normal operation ICC (mA)

MSM80C154S/83C154S¡ Semiconductor

V

CC

4 V 5 V 6 V

Freq

2.2 3.1 4.11 MHz

3.9 5.2 7.03 MHz

12.0 16.0 20.012 MHz

16.0 20.0 25.016 MHz

19.0 25.0 30.020 MHz

V

CC

4.5 V 5 V 6 V

Freq

25.0 29.0 35.024 MHz

Maximum power supply current idle mode ICC (mA)

V

CC

Freq

4 V 5 V 6 V

0.8 1.2 1.61 MHz

1.2 1.7 2.33 MHz

3.1 4.4 5.912 MHz

3.8 5.5 7.316 MHz

4.5 6.4 8.620 MHz

V

CC

Freq

4.5 V 5 V 6 V

6.4 7.4 9.824 MHz

283

Page 26

DC Characteristics 2

Parameter Symbol Condition Min. Typ. Max. Unit

Input Low Voltage V

Input High Voltage V

Input High Voltage V

Output Low Voltage

(PORT 1, 2, 3)

Output Low Voltage

(PORT 0, ALE, PSEN)

Output High Voltage

Output High Voltage

(PORT 1, 2, 3)

(PORT 0, ALE, PSEN)

Logical 0 Input Current/

Logical 1 Output Current/

(PORT 1, 2, 3)

Logical 1 to 0 Transition

Output Current (PORT 1, 2, 3)

Input Leakage Current

(PORT 0 floating, EA)

RESET Pull-down Resistance R

Pin Capacitance C

Power Down Current I

¡ SemiconductorMSM80C154S/83C154S

(V

=2.2 to 4.0 V, VSS=0 V, Ta=-40 to +85°C)

CC

Meas-

uring

circuit

IL

IH

XTAL1, RESET, and EA 0.6 VCC+0.6 — V

IH1

V

OL

V

OL1

V

OH

V

OH1

/ I

I

IL

OH

I

TL

I

LI

RST

IO

PD

— –0.5 — V

Except XTAL1, EA,

and RESET

0.25 V

+0.9 — V

CC

IOL=10 mA—— V

IOL=20 mA—— V

IOH=–5 mA

IOH=–20 mA

VI=0.1 V

V

O

=0.1 V

0.75 V

CC

0.75 V

CC

–5 –10 mA

VI=1.9 V — –80 mA

V

< VI < V

SS

CC

—— mA

—2040 kW

Ta=25°C, f=1 MHz

(except XTAL1)

—— pF

——1 mA

0.25 V

—V

—V

V

V

CC

+0.5

CC

+0.5

CC

0.1

0.1

—

—

–40

–300

±10

125

10

10

–0.1

1

2

3

2

—

4

284

Page 27

Maximum power supply current normal operation ICC (mA)

MSM80C154S/83C154S¡ Semiconductor

V

CC

Freq

2.2 V 3.0 V 4.0 V

0.9 1.4 2.21 MHz

1.8 2.4 4.33 MHz

— 8.0 12.012 MHz

— — 16.016 MHz

Maximum power supply current idle mode ICC (mA)

V

CC

Freq

2.2 V 3.0 V 4.0 V

0.3 0.5 0.81 MHz

0.5 0.8 1.23 MHz

— 2.0 3.112 MHz

— — 3.816 MHz

285

Page 28

Measuring circuits

¡ SemiconductorMSM80C154S/83C154S

1

V

CC

V

IH

(*3)

V

IL

INPUT

V

SS

(*2)

OUTPUT

V A

(*1)

I

O

V

A

3

2

V

CC

INPUT

V

SS

4

OUTPUT

A

V

CC

V

IH

(*3)

V

IL

INPUT

V

SS

(*2)

OUTPUT

V A

V

CC

V

IH

(*3)

V

IL

INPUT

OUTPUT

V

SS

*1: Repeated for specified input pins.

*2: Repeated for specified output pins.

*3: Input logic for specified status.

286

Page 29

AC Characteristics

(1) External program memory access AC characteristics

V

PORT 0, ALE, and PSEN connected with 100pF load, other connected with 80pF load

Variable clock from

Parameter Symble Unit

Min. Max.

XTAL1, XTAL 2 Oscillation Cycle

ALE Signal Width

Address Setup Time

(to ALE Falling Edge)

Address Hold Time

(from ALE Falling Edge)

Instruction Data Read Time

(from ALE Falling Edge)

From ALE Falling Edge to PSEN

Falling Edge

PSEN Signal Width

Instruction Data Read Time

(from PSEN Falling Edge)

Instruction Data Hold Time

(from PSEN Rising Edge)

Bus Floating Time after Instruction

Data Read (from PSEN Rising Edge)

Instruction Data Read Time

(from Address Output)

Bus Floating Time(PSEN Rising

Edge from Address float)

Address Output Time from PSEN

Rising Edge

t

CLCL

t

LHLL

t

AVLL

t

LLAX

t

LLPL

t

LLPL

t

PLPH

t

PLIV

t

PXIX

t

PXIZ

t

AVIV

t

AZPL

t

PXAV

41.7 1000 ns

2t

-40 — ns

CLCL

-15 — ns

1t

CLCL

-35 — ns

1t

CLCL

—4t

-30 — ns

1t

CLCL

-35 — ns

3t

CLCL

—3t

0—ns

—1t

—5t

0—ns

-20 — ns

1t

CLCL

MSM80C154S/83C154S¡ Semiconductor

=2.2 to 6.0V, VSS=0V, Ta=–40°C to +85°C

CC

*1

1 to 24 MHz

-100 ns

CLCL

-45 ns

CLCL

-20 ns

CLCL

-105 ns

CLCL

*1 The variable check is from 0 to 24 MHz when the external check is used.

287

Page 30

(2) External program memory read cycle

t

LHLL

ALE

¡ SemiconductorMSM80C154S/83C154S

PSEN

PORT2

t

AVLLtLLPL

t

LLAXtAZPL

A0 to A7

t

AVIV

t

LLIV

t

PLIV

t

PLPH

t

PXIX

INSTR

IN

t

PXIZ

t

PXAV

A0 to A7PORT0

A8 to A15 A8 to A15 A8 to A15

288

Page 31

MSM80C154S/83C154S¡ Semiconductor

(3) External data memory access AC characteristics

V

=2.2 to 6.0V, VSS=0V, Ta=–40°C to +85°C

CC

PORT 0, ALE, and PSEN connected with 100pF load, other connected with 80pF load

Variable clock from

Parameter Symbol Unit

1 to 24 MHz

Min. Max.

XTAL1, XTAL2 Oscillator Cycle

ALE Signal Width

Address Setup Time

(to ALE Falling Edge)

Address Hold Time

(from ALE Falling Edge)

RD Signal Width

WR Signal Width

RAM Data Read Time

(from RD Signal Falling Edge)

RAM Data Read Hold Time

(from RD Signal Rising Edge)

Data Bus Floating Time

(from RD Signal Rising Edge)

RAM Data Read Time

(from ALE Signal Falling Edge)

RAM Data Read Time

(from Address Output)

RD/WR Output Time from ALE

Falling Edge

RD/WR Output Time from Address

Output

WR Output Time from Data Output

Time from Data to WR Rising Edge

Data Hold Time

(from WR Rising Edge)

Time from to Address Float RD

Output

Time from RD/WR Rising Edge to

ALE Rising Edge

t

CLCL

t

LHLL

t

AVLL

t

LLAX

t

RLRL

t

WLWH

t

RLDV

t

RHDX

t

RHDZ

t

LLDV

t

AVDV

t

LLWL

t

AVWL

t

QVWX

t

QVWH

t

WHQX

t

RLAZ

t

WHLH

*2

41.7 1000 ns

2t

-40 — ns

CLCL

-15 — ns

1t

CLCL

-35 — ns

1t

CLCL

-100 — ns

6t

CLCL

6t

-100 — ns

CLCL

—5t

CLCL

0—ns

—2t

—8t

—9t

3t

-40

CLCL

3t

-100

CLCL

-70 — ns

4t

CLCL

1t

-40 — ns

CLCL

7t

-105 — ns

CLCL

-50 — ns

2t

CLCL

CLCL

CLCL

3t

0—ns

-30

1t

CLCL

*2

1t

1t

CLCL

*1 The variable check is from 0 to 24 MHz when the external check is used.

*2 For 2.2£VCC<4 V

*1

-105 ns

-70 ns

CLCL

-100 ns

-105 ns

+40 ns

CLCL

+40

CLCL

+100

ns

289

Page 32

(4) External data memory read cycle

ALE

PSEN

RD

PORT 0

INSTR

IN

A0 to A7

PCL

t

LHLL

t

AVLL

A0 to A7

Rr or DPL

t

LLAX

t

AVWL

t

LLWL

t

AZRL

t

LLDV

t

AVDV

t

RLDV

¡ SemiconductorMSM80C154S/83C154S

t

RLRH

t

RHDX

DATA IN

t

WHLH

t

RHDZ

A0 to A7

PCL

PORT 2

PCH A8 to A15 PCH P2.0 to P2.7 DATA A8 to A15 DPHor A8 to A15 PCH

(5) External data memory write cycle

ALE

PSEN

WR

PORT 0

PORT 2

INSTR

IN

A8 to A15

PCH

A0 to A7

PCL

A8 to A15 PCH P2.0 to P2.7 DATA A8 to A15 DPHor A8 to A15 PCH

t

LHLL

t

AVLL

A0 to A7

Rr or DPL

t

t

AVWL

t

LLWL

LLAX

t

QVWX

t

WLWH

t

QVWH

DATA (ACC)

t

WHLH

t

WHQX

A0 to A7

PCL

290

Page 33

(6) Serial port (I/O Extension Mode) AC characteristics

Parameter Symbol Min. Max. Unit

Serial Port Clock Cycle Time t

Output Data Setup to Clock Rising Edge t

Output Data Hold After Clock Rising Edge t

Input Data Hold After Clock Rising Edge t

Clock Rising Edge to Input Data Valid t

XLXL

QVXH

XHQX

XHDX

XHDV

10t

12t

CLCL

2t

CLCL

MSM80C154S/83C154S¡ Semiconductor

=2.2 to 6.0V, VSS=0V, Ta=–40°C to +85°C)

(V

CC

CLCL

-133 —

-75 —

0—

— 10t

—ns

-133

CLCL

ns

ns

ns

ns

291

Page 34

292

MACHINE

CYCLE

ALE

SHIFT

CLOCK

t

XLXL

OUTPUT

DATA

INPUT

DATA

t

QVXH

VALID VALID VALID VALID VALID VALID VALID VALID

t

XHDV

t

XHQX

t

XHDX

¡ SemiconductorMSM80C154S/83C154S

Page 35

(7) AC Characteristics Measuring Conditions

1.Input/output signal

MSM80C154S/83C154S¡ Semiconductor

V

OH

V

IH

V

IH

V

OH

TEST POINT

V

V

OL

IL

* The input signals in AC test mode are either VOH (logic "1") or V

V

IL

OL

V

OL

(logic "0") input signals

where logic "1" corresponds to a CPU output signal waveform measuring point in excess of

VIH, and logic "0" to a point below VIL.

2.Floating

V

OH

V

OL

V

IH

V

IL

Floating

V

V

IH

V

IL

OH

V

OL

* The port 0 floating interval is measured from the time the port 0 pin voltage drops below V

after sinking to GND at 2.4 mA when switching to floating status from a "1" output, and from

the time the port 0 pin voltage exceeds VIL after connecting to a 400 mA source when switching

to floating status from a "0" output.

(8) XTAL1 external clock input waveform conditions

Parameter Symbol Min. Max. Unit

External Clock Freq. 1/t

Clock Pulse width 1 t

Clock Pulse width 2 t

Rise Time t

Fall Time t

CLCL

CHCx

CLCX

CLCH

CHCL

0 24 MHz

15 —

15 —

—5

—5

ns

ns

ns

ns

IH

External Clock Drive Waveform

EXTERNAL

OSCILLATOR

SIGNAL

t

CHCX

t

CHCL

t

CLCX

t

CLCH

t

CLCL

0.7 V

CC

0.2 VCC - 0.1

293

Page 36

Timing Diagram

,,,,,,

Basic timing

¡ SemiconductorMSM80C154S/83C154S

PCH

M1

M2

M1

DATA STABLE

PC+1PC+1PC+1

Instruction execution

TM+1

S1 S2 S3 S4 S5 S6

Port output/input

instruction execution

TM+1TM+1

ACC & RAM

S1 S2 S3 S4 S5 S6

PORT NEW DATA

Instruction execution

execution

DPL&Rr

External data memory instruction

294

M1

CYCLE

S1 S2 S3 S4 S5 S6

S1 S2 S3 S4 S5 S6

STEP

1

XTAL 1

PCL PCL PCL PCL

Instruction decoding Instruction decodingInstruction decoding

PCL

DATA STABLE

PC+1

PCH PCH PCH PCHPCHDPH & PORT DATAPCH

Instruction execution

PCL

TM+1

PORT OLD DATA

Port output/input

instruction execution

PC+1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

ALE

PSEN

RD/WR

PORT-0

PORT-2

CPU¨PORT

PORT¨CPU

Loading...

Loading...