OKI MSM6996VAS, MSM6996VGS-K, MSM6996VRS, MSM6997HAS, MSM6996HRS Datasheet

...

E2U0010-28-81

¡ Semiconductor MSM6996H/6996V/6997H/6997V/6998/6999

¡ Semiconductor

This version: Aug. 1998

Previous version: Nov. 1996

MSM6996H/6996V/6997H/6997V/6998/6999

Single Chip CODEC

GENERAL DESCRIPTION

The MSM6996H/MSM6996V/MSM6997H/MSM6997V/MSM6998/MSM6999 are a single-channel

CODEC CMOS ICs containing filters for A/D and D/A converting of the voice signal ranging from

300 Hz to 3400 Hz.

FEATURES

• Compliance with ITU-T companding Law

MSM6996H/MSM6996V/MSM6998 : A-law

MSM6997H/MSM6997V/MSM6999 : m-law

• Capable of independent operation of transmission and reception

• Transmission clock in the range of 64 kHz to 2048 kHz

• Adjustable transmit gain

• 600 W drive for analog output

MSM6996H/MSM6996V/MSM6997H/MSM6997V single end drive

MSM6998/MSM6999 Push-pull drive

• Built-in analog loop back fanction

MSM6996V/MSM6997V

• Built-in reference voltage source

• Low Power Dissipation (60 mW to 70 mW Typ.)

• Package options :

16-pin plastic DIP (DIP16-P-300-2.54) (Product name : MSM6996HRS/MSM6997HRS)

(Product name : MSM6996VRS/MSM6997VRS)

(Product name : MSM6998RS/MSM6999RS)

16-pin cer DIP (DIP16-G-300-2.54-1) (Product name : MSM6996HAS/MSM6997HAS)

(Product name : MSM6996VAS/MSM6997VAS)

(Product name : MSM6998AS/MSM6999AS)

24-pin plastic SOP (SOP24-P-430-1.27-K) (Product name : MSM6996HGS-K/MSM6997HGS-K)

(Product name : MSM6996VGS-K/MSM6997VGS-K)

(Product name : MSM6998GS-K/MSM6999GS-K)

1/21

¡ Semiconductor MSM6996H/6996V/6997H/6997V/6998/6999

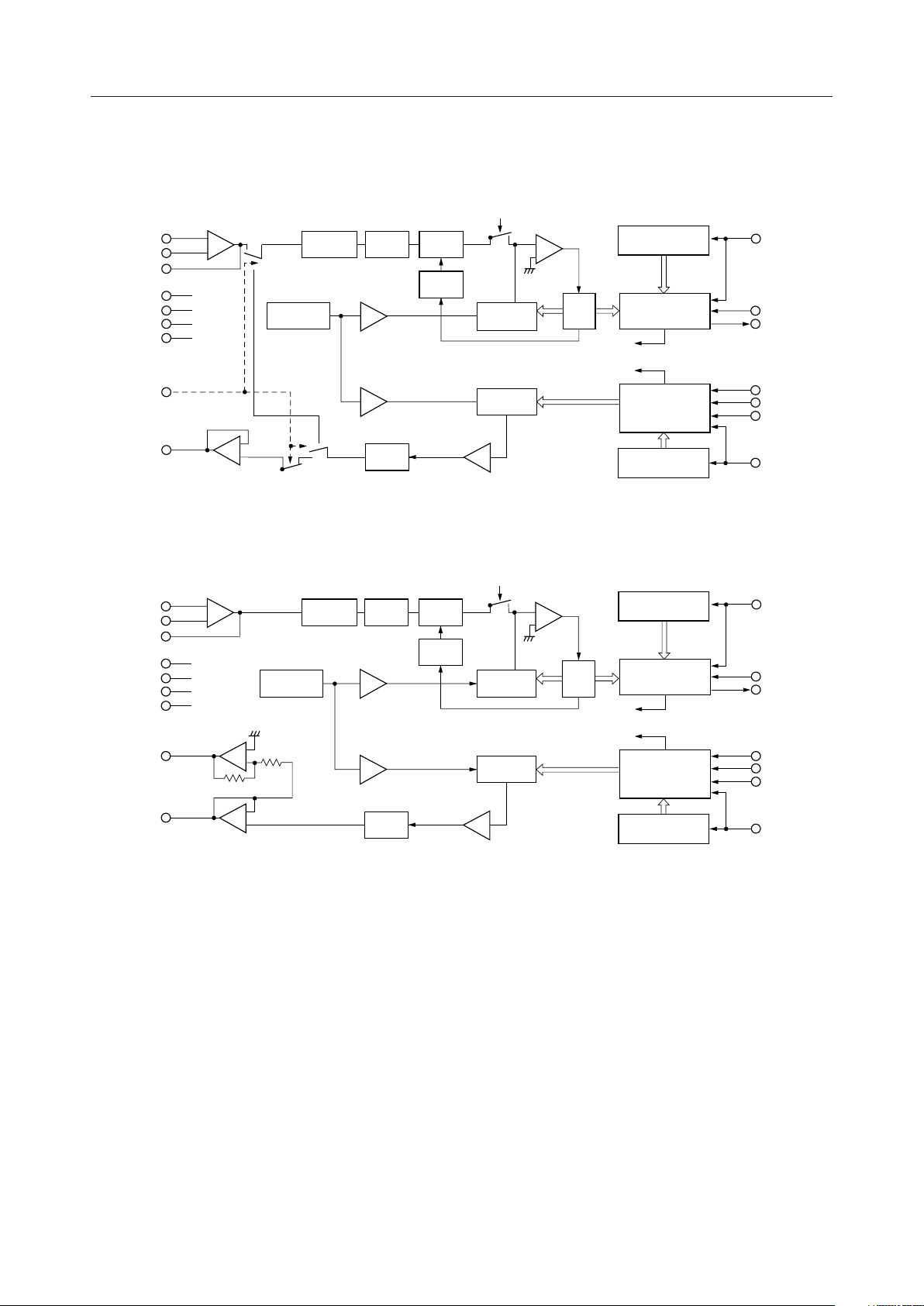

BLOCK DIAGRAM

MSM6996H/V

MSM6997H/V

AIN+

AIN–

GSX

V

DD

V

SS

AG

DG

+

–

Pre Filter

Voltage

REF.

5th

LPF

HPF

Auto

Zero

3rd

SAMPLE

C Ladder

COMP

SAR

T.PWD

Transmit

PLL

Transmit

Controller

XSYNC

XCLOCK

PCMOUT

*2

TMC

AOUT

AIN+

AIN–

GSX

V

DD

V

AG

DG

AOUT–

AOUT+

–

+

MSM6998, MSM6999

+

–

SS

+

–

R

–

+

Voltage

REF.

R

Pre Filter

5th

LPF

5th

LPF

5th

LPF

3rd

HPF

Auto

Zero

C Ladder

SAMPLE

C Ladder

C Ladder

R.PWD

Receive

Controller

Receive

PLL

*

1 BS : Only MSM6997H/V

*

2 Only MSM6996V, MSM6997V

COMP

SAR

Transmit

PLL

Transmit

Controller

T.PWD

R.PWD

Receive

Controller

Receive

PLL

PDN/BS

*1

PCMIN

RCLOCK

RSYNC

XSYNC

XCLOCK

PCMOUT

*3

PDN/BS

PCMIN

RCLOCK

RSYNC

*

3 BS : Only MSM6999

2/21

¡ Semiconductor MSM6996H/6996V/6997H/6997V/6998/6999

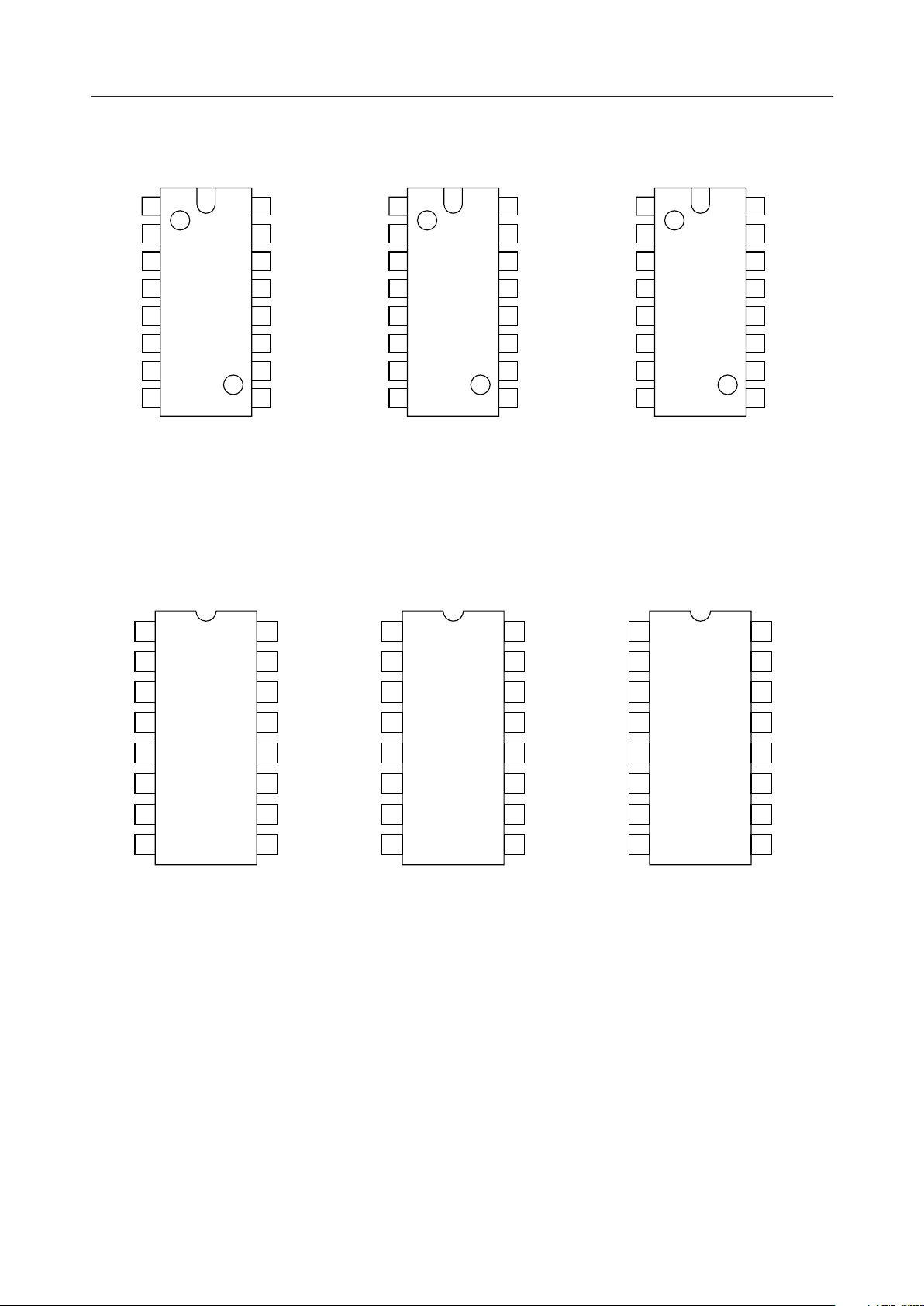

PIN CONFIGURATION (TOP VIEW)

1

AIN+

2

AIN–

3

GSX

4

AG

AOUT

PCMIN

5

6

NC

7

V

DD

8 9

NC : No connect pin

16-Pin Plastic DIP

MSM6996HRS

MSM6997HRS

1

AIN+

16 1

V

SS

15

PCMOUT

14

PDN/BS

13

DG

12

XSYNC

11

RSYNC

10

XCLOCK

RCLOCK

AIN+

AIN–

GSX

AG

AOUT

TMC

V

DD

PCMIN

16-Pin Plastic DIP

16

V

SS

AIN+

1

2

3

4

5

6

7

8 9

MSM6996VRS

MSM6997VRS

16 1

V

SS

15

PCMOUT

14

PDN/BS

13

DG

12

XSYNC

11

RSYNC

10

XCLOCK

RCLOCK

AIN+

AIN–

GSX

AG

AOUT+

AOUT–

V

DD

PCMIN

16-Pin Plastic DIP

16

V

SS

AIN+

1

2

3

4

5

6

7

8 9

MSM6998RS

MSM6999RS

16

V

15

PCMOUT

14

PDN/BS

13

DG

12

XSYNC

11

RSYNC

10

XCLOCK

RCLOCK

16

SS

V

SS

2

AIN–

3

GSX

4

AG

AOUT

5

NC

6

V

7

DD

PCMIN

8 9

NC : No connect pin

16-Pin Cer DIP

MSM6996HAS

MSM6997HAS

15

PCMOUT

14

PDN/BS

13

DG

12

XSYNC

11

RSYNC

XCLOCK

10

RCLOCK

AIN–

GSX

AG

AOUT

TMC

V

DD

PCMIN

2

3

4

5

6

7

8 9

16-Pin Cer DIP

MSM6996VAS

MSM6997VAS

15

PCMOUT

14

PDN/BS

13

DG

12

XSYNC

11

RSYNC

10

XCLOCK

RCLOCK

AIN–

GSX

AG

AOUT+

AOUT–

V

DD

PCMIN

2

3

4

5

6

7

8 9

16-Pin Cer DIP

MSM6998AS

MSM6999AS

15

PCMOUT

14

PDN/BS

13

DG

12

XSYNC

11

RSYNC

XCLOCK

10

RCLOCK

3/21

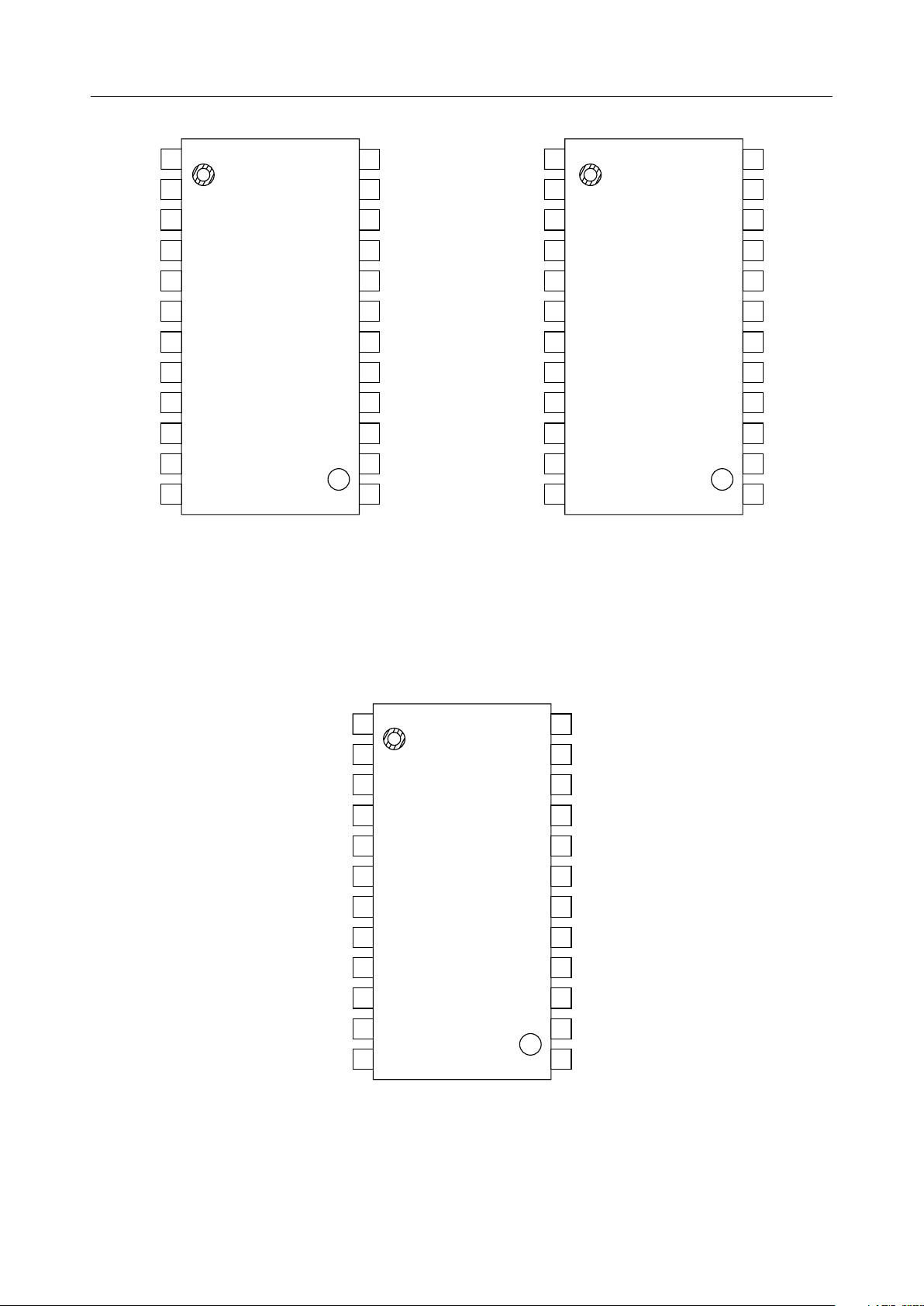

¡ Semiconductor MSM6996H/6996V/6997H/6997V/6998/6999

AIN+

AIN–

GSX

AG

AG

NC

NC

AOUT

NC

NC

V

DD

PCMIN

1

2

3

4

5

6

7

8

9

10

11

12 13

24

23

22

21

20

19

18

17

16

15

14

V

SS

PCMOUT

PDN/BS

DG

NC

NC

NC

NC

XSYNC

RSYNC

XCLOCK

RCLOCK

AIN+

AIN–

GSX

AG

AG

NC

NC

AOUT

NC

TMC

V

DD

PCMIN

1

2

3

4

5

6

7

8

9

10

11

12 13

NC : No connect pin NC : No connect pin

24-Pin Plastic SOP

24-Pin Plastic SOP

24

23

22

21

20

19

18

17

16

15

14

V

SS

PCMOUT

PDN/BS

DG

NC

NC

NC

NC

XSYNC

RSYNC

XCLOCK

RCLOCK

MSM6996HGS-K

MSM6997HGS-K

AIN+

AIN–

GSX

AOUT+

AOUT–

PCMIN

1

2

3

4

AG

AG

5

NC

6

NC

7

8

NC

9

10

V

11

DD

12 13

MSM6996VGS-K

MSM6997VGS-K

24

V

SS

23

PCMOUT

22

PDN/BS

DG

21

NC

20

NC

19

NC

18

NC

17

XSYNC

16

RSYNC

15

14

XCLOCK

RCLOCK

NC : No connect pin

24-Pin Plastic SOP

MSM6998GS-K

MSM6999GS-K

4/21

¡ Semiconductor MSM6996H/6996V/6997H/6997V/6998/6999

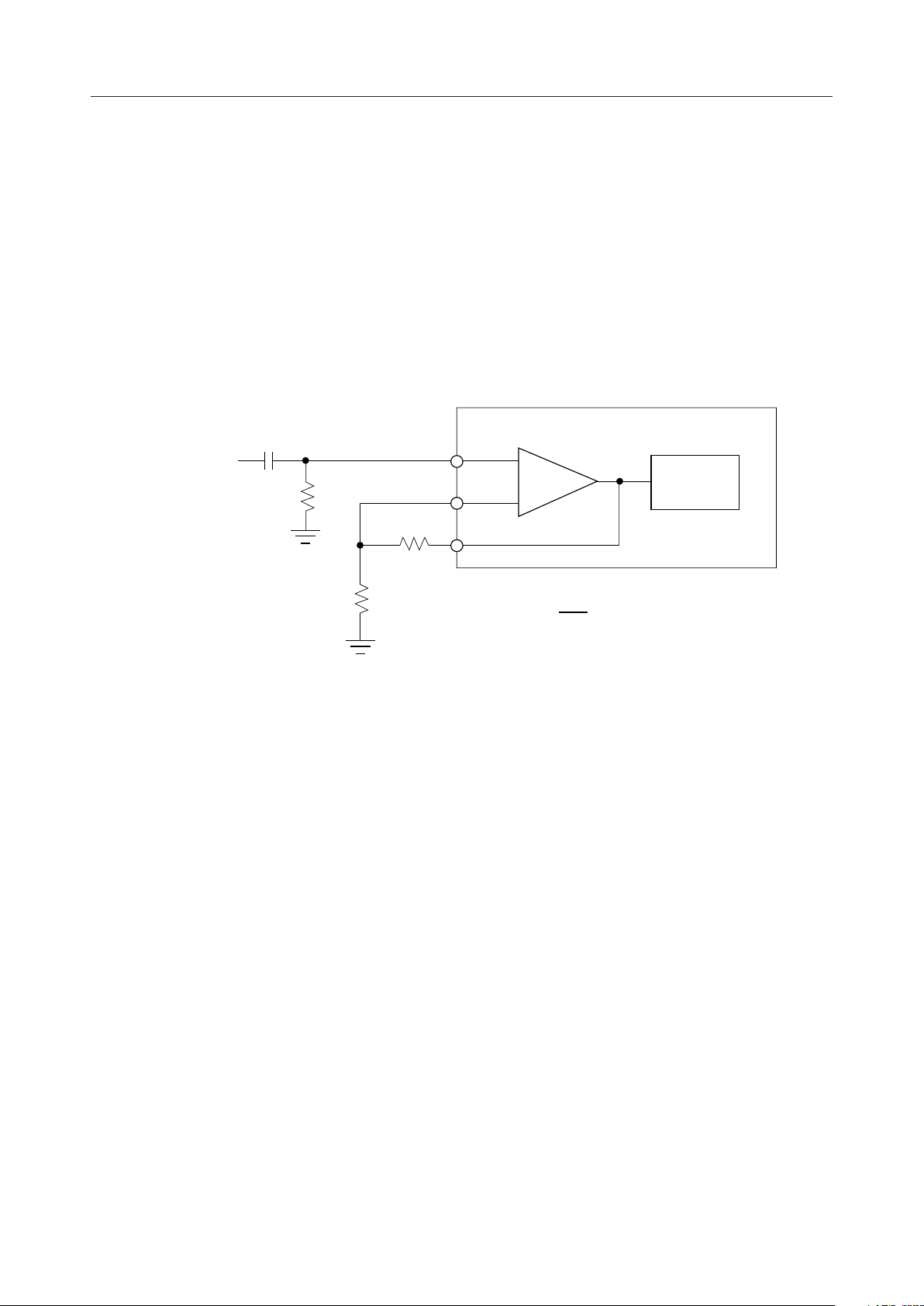

PIN AND FUNCTIONAL DESCRIPTIONS

AIN+, AIN–, GSX

These three pins are used for the transmit level adjustment.

AIN+ is a non-inverting analog input pin which is connected to the non-inverting input of a transmit

amplifier.

AIN– is an inverting analog input pin which is connected to the inverting input of the transmit

amplifier.

GSX is a transmit amplifier output pin.

Adjustment can be done by following method.

Analog

Input

C1

R1

R2

R3

AG

Notes: 1. R2 + R3 > 10 kW

2. When the DC off-set voltage of analog input is more than 20 mV, C1 and R1 should

provide for DC blocking.

In this case, cut-off frequency of HPF, composed by R1 and C1, should be less than 30 Hz.

3. R1 should be less than 20 kW

AG

AG is an analog ground.

AG is connected to the analog system ground.

AIN+

AIN–

GSX

Gain = 1 +

+

–

R2

< 10

R3

RC

Active

Filter

AOUT

AOUT is the analog signal output pin for the MSM6996H/V and MSM6997H/V.

The output voltage range is 5 VPP. This output can drive the 600 W resistor.

AOUT+, AOUT–

Analog output for the MSM6998 and MSM6999.

The output signal amplitudes are 5 VPP. The AOUT– output is inverted to the AOUT+ output. These

outputs can drive a 600 W impedance.

V

DD

VDD is the positive power supply.

The voltage supplied to this pin should be +5 V ±5%.

5/21

¡ Semiconductor MSM6996H/6996V/6997H/6997V/6998/6999

PCMIN

PCM signal input.

The serial input PCM signal is converted from digital to analog, synchronizing with the synchronous

signal RSYNC and clock signal RCLOCK.

The data rate of PCM signal ranges from 64 kbps to 2048 kbps.

The PCM signal is read at the falling edge of the clock signal and latched into the internal register

when finished to read eight bits data.

The top of the PCM data is specified by RSYNC pulse timing.

RCLOCK

Receive clock pulse input.

The frequency of this clock pulse should be identified with the data rate of PCM input signal at the

PCMIN pin.

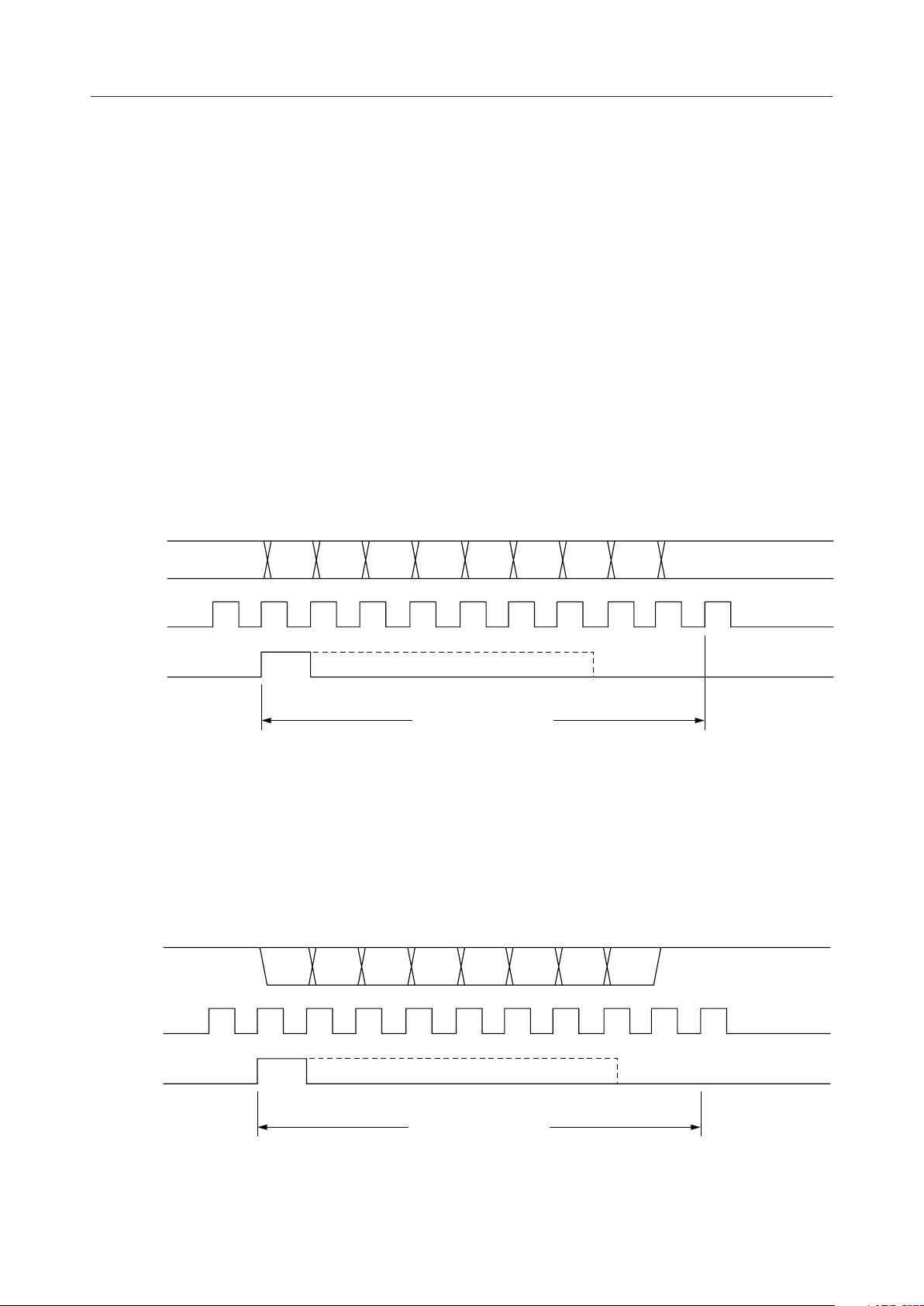

This RCLOCK signal can be a continuous clock or a burst clock with nine bits or more.

In the case of a burst clock, input the following timing.

MSDD2D3D4D5D6D7D8PCMIN

RCLOCK

RSYNC

123456789

9 Clocks are required

XCLOCK

Transmit clock input.

The PCM output data rate from the PCMOUT pin is set by this clock frequency.

The applicable clock frequencies range from 64 kHz to 2048 kHz.

This XCLOCK signal can be a continuous clock or a burst clock with nine bits or more.

In the case of a burst clock, input the following timing.

MSD D2 D3 D4 D5 D6 D7 D8PCMOUT

XCLOCK

XSYNC

123456789

9 Clocks are required

6/21

¡ Semiconductor MSM6996H/6996V/6997H/6997V/6998/6999

RSYNC

Receive synchronizing signal input.

Eight required bits are selected from serial PCM signals on the PCMIN pin by the receive

synchronizing signal.

The whole timing signal in the receive section are synchronize by this synchronizing signal.

This signal must be synchronize in phase with RCLOCK.

The frequency should be 8 kHz ±50 ppm to guarantee the AC characteristics of receive section.

However, same as the RCLOCK frequency, this device can operate in the range of 8 kHz ±2 kHz, with

no guarantee of adherence to the electrical characteristics in this specification as a catalogue value.

Fixing this signal to logic "1" or "0", the receive circuit is driver in a power down state.

XSYNC

Transmit synchronizing signal input.

The PCM output signal from the PCMOUT pin is output in synchronization with this transmit

synchronizing signal.

All transmit timing signals are triggered to synchronize with this signal. This signal should be

synchronized in phase with XCLOCK pulse.

The frequency should be 8 kHz ±50 ppm to guarantee the AC characteristics of transmit section.

Fixing this signal to logic "1" or "0", the transmit circuit is driver in a power down state.

DG

Ground of digital signal.

This pin is electrically separated from the AG pin in this device.

The DG pin must be connected to the AG pin on the printed circuit board to make common to the

AG pin.

PDN/BS

Power down signal input.

When this input is held at low level more than 1 ms, the device is put into the power-down mode.

PCMOUT

PCM signal output.

The PCM output signal is output in synchronization with the rising edge of XCLOCK pulse orderly

from MSD first. (The first bit of the PCM signal may output at the rising edge of XSYNC pulse,

according to the timing of XSYNC and XCLOCK pulse.). During the PCMOUT signal output except

the 8-bit pulses, the pin is in an open state, therefore, multiple connections by wired-OR are easily

possible at this pin.

The code companding law and output code format depend on ITU-T Recommendation G.711, and

for the MSM6996H, MSM6996V, and MSM6998 (A-law) the output PCM signals are obtained by

inverting the even bits of signals.

Input/Output

Level

+Full scale

+0

–0

–Full scale

PCMIN/PCMOUT

MSM6996 (A-law) MSM6997 (m-law)

MSM6998 (A-law) MSM6999 (m-law)

10101010

11010101

01010101

00101010

10000000

11111111

01111111

00000000

7/21

Loading...

Loading...