OKI MSM5718C50-60GS-K, MD5764802-53MC, MSM5718C50-53GS-K, MD5764802-60MC Datasheet

E2G1059-39-21

¡ Semiconductor MSM5718C50/MD5764802

¡ Semiconductor

This version: Feb. 1999

Previous version: Nov. 1998

MSM5718C50/MD5764802

18Mb (2M

¥¥

¥ 9) & 64Mb (8M

¥¥

DESCRIPTION

The 18/64-Megabit Concurrent Rambus™ DRAMs (RDRAM®) are extremely high-speed

CMOS DRAMs organized as 2M or 8M words by 8 or 9 bits. They are capable of bursting unlimited

lengths of data at 1.67 ns per byte (13.3 ns per eight bytes). The use of Rambus Signaling Level (RSL)

technology permits 600 MHz transfer rates while using conventional system and board design

methodologies. Low effective latency is attained by operating the two or four 2KB sense amplifiers

as high speed caches, and by using random access mode (page mode) to facilitate large block

transfers. Concurrent (simultaneous) bank operations permit high effective bandwidth using

interleaved transactions.

RDRAMs are general purpose high-performance memory devices suitable for use in a broad range

of applications including PC and consumer main memory, graphics, video, and any other

application where high-performance at low cost is required.

¥¥

¥ 8) Concurrent RDRAM

¥¥

FEATURES

• Compatible with Base RDRAMs

• 600 MB/s peak transfer rate per RDRAM

• Rambus Signaling Level (RSL) interface

• Synchronous, concurrent protocol for block-oriented, interleaved (overlapped) transfers

• 480 MB/s effective bandwidth for random 32 byte transfers from one RDRAM

• 13 active signals require just 32 total pins on the controller interface (including power)

• 3.3 V operation

• Additional/multiple Rambus Channels each provide an additional 600 MB/s bandwidth

• Two or four 2KByte sense amplifiers may be operated as caches for low latency access

• Random access mode enables any burst order at full bandwidth within a page

• Graphics features include write-per-bit and mask-per-bit operations

• Available in horizontal surface mount plastic package (SHP32-P-1125-0.65-K)

1/45

¡ Semiconductor MSM5718C50/MD5764802

PART NUMBERS

The 18- and 64-Megabit RDRAMs are available in horizontal surface mount plastic package

(SHP),

with 533 and 600 MHz clock rate. The part numbers for the various options are shown in Table 1.

Table 1 Part Numbers by Option

533 MHzOptions 600 MHz

18-Megabit SHP

64-Megabit SHP

MSM5718C50-53GS-K

MD5764802-53MC

MSM5718C50-60GS-K

MD5764802-60MC

2/45

¡ Semiconductor MSM5718C50/MD5764802

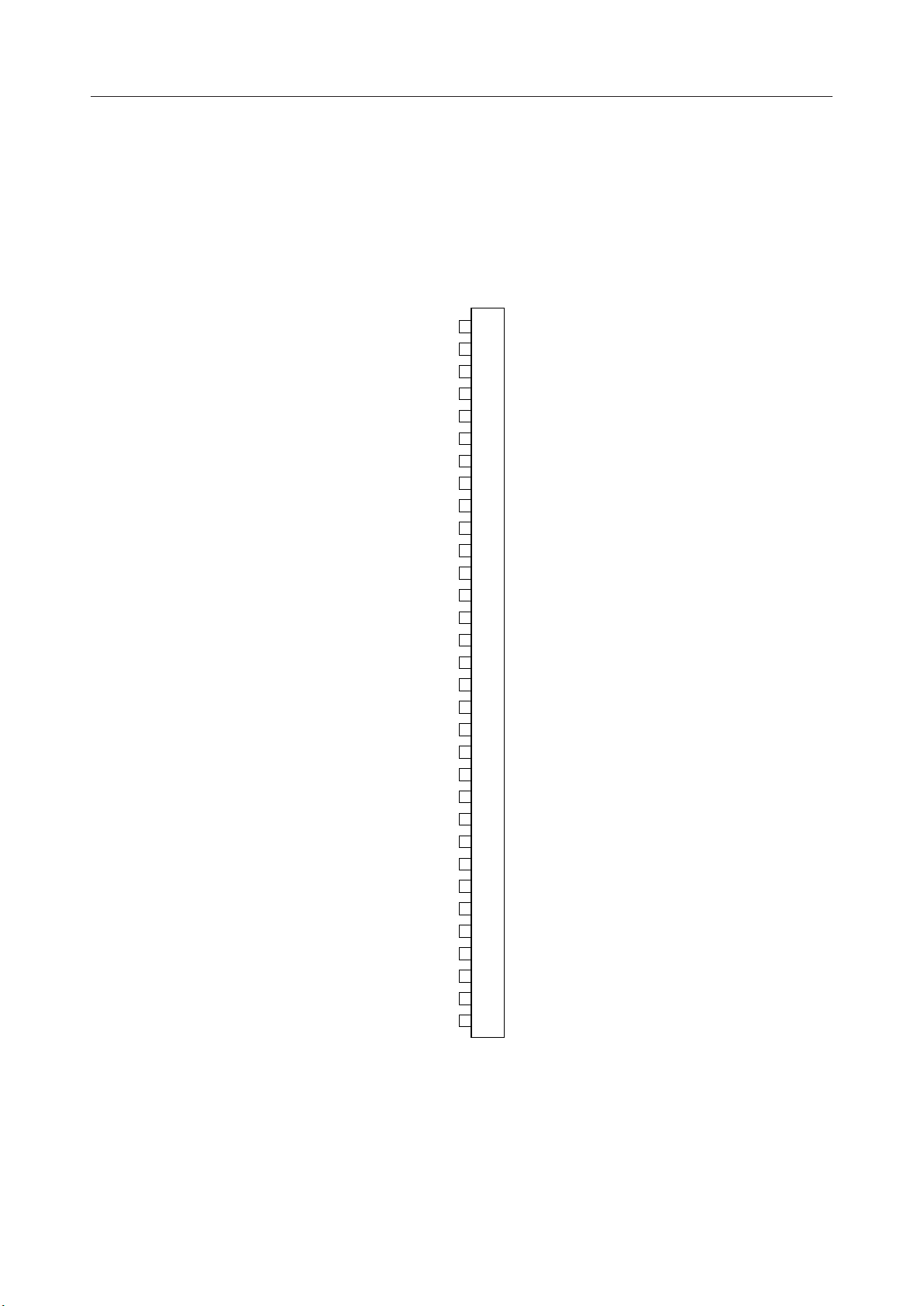

RDRAM PACKAGES AND PINOUTS

RDRAMs are available in horizontal surface mount plastic package (SHP).

The package has 32 signal pins and four mechanical pins that provide support for the device. The

mechanical pins are located on the opposite side from the signal leads in the SHP.

VDD 1

GND

DQ8

GND

DQ7

NC (18M) ; VREF (64M)

ADDRESS

VDD

DQ6

GND

DQ5

VDDA

RXCLK

GNDA

TXCLK

VDD

DQ4

GND

COMMAND

SIN

VREF

SOUT

DQ3

GND

DQ2

(NC)

DQ1

GND

DQ0

(NC)

GND

VDD

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

Fig. 1 SHP Pin Numbering

3/45

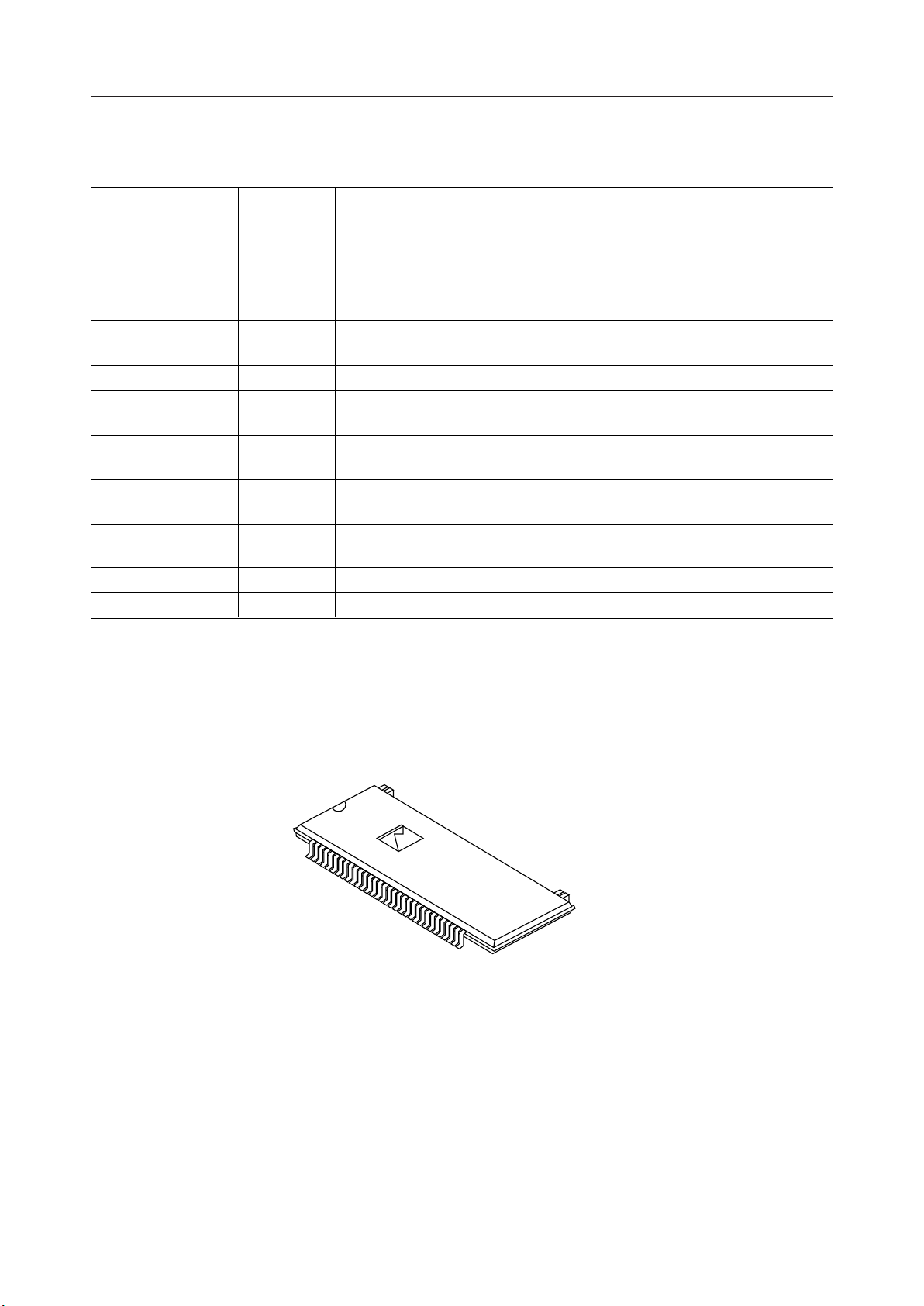

¡ Semiconductor MSM5718C50/MD5764802

Table 2 Pin Descriptions

Signal I/O Description

DQ8..DQ0

(BUSDATA [8:0])

I/O

CLK

(RXCLK)

CLK

(TXCLK)

VREF I

COMMAND

(BUSCTRL)

ADDRESS

(BUSENABLE)

VDD, VDDA

GND, GNDA

—

—

SIN I

SOUT O

I

I

I

I

Signal lines for REQ, DIN, and DOUT packets. The REQ packet contains the

address field, command field, and other control fields. These are RSL

signals.

a

Receive clock. All input packets are aligned to this clock. This is an RSL

a

signal.

Transmit clock. DOUT packets are aligned with this clock. This is an RSL

a

signal.

Logic threshold reference voltage for RSL signals.

Signal line for REQ, RSTRB, RTERM, WSTRB, WTERM, RESET, and CKE

packets. This is an RSL signal.

Signal line for COL packets with column addresses. This is an RSL signal.

a

a

+3.3 V power supply. VDDA is a separate analog supply for clock generation

in the RDRAM.

Circuit ground. GNDA is a separate analog ground for clock generation in

the RDRAM.

Initialization daisy chain input. CMOS levels.

Initialization daisy chain output. CMOS levels.

a. RSL stands for Rambus Signaling Levels, a low-voltage-swing, active-low signaling technology.

Mechanical

Support Pins

Pin 1

Mechanical

Support Pins

Pin 32

Fig. 2 SHP Package

4/45

¡ Semiconductor MSM5718C50/MD5764802

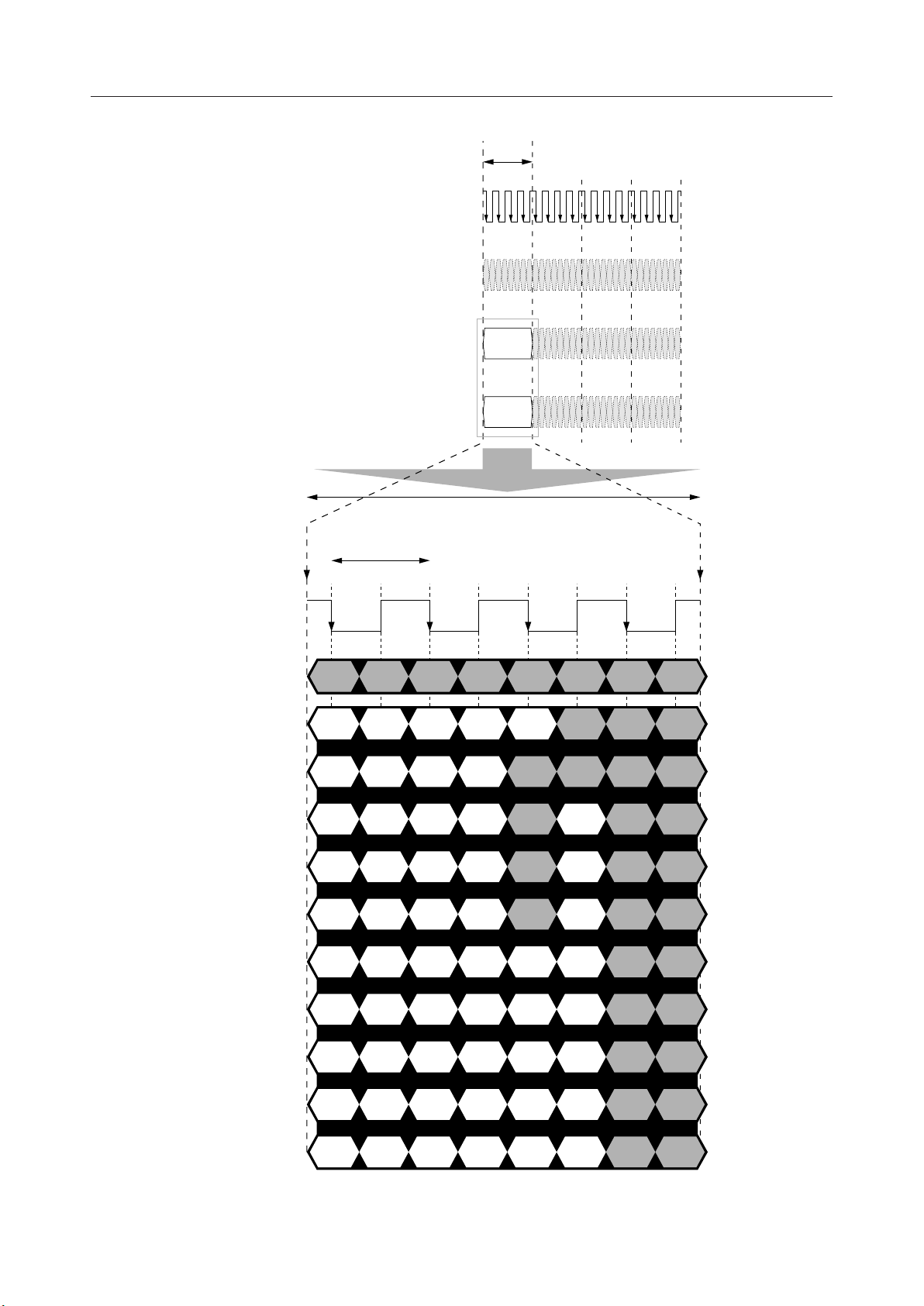

GENERAL DESCRIPTION

Figure 3 is a block diagram of an RDRAM. At the bottom is a standard DRAM core organized as two

or four independent banks, with each bank organized as 512 or 1024 rows, and with each row

consisting of 2KBytes of memory cells. One row of a bank may be “activated” at any time (ACTV

command) and placed in the 2KByte “page” for the bank. Column accesses (READ and WRITE

commands) may be made to this active page.

The smallest block of memory that may be accessed with READ and WRITE commands is an octbyte

(eight bytes). Bitmask and bytemask options are available with the WRITE command to allow finer

write granularity. There are six control registers that are accessed at initialization time to configure

the RDRAM for a particular application.

5/45

¡ Semiconductor MSM5718C50/MD5764802

SIN

SOUT

RXCLK

ADDRESS

(BUSENABLE)

COMMAND

(BUSCTRL)

DQ8, DQ7,...DQ0

(BUSDATA[8:0])

TXCLK

11

Initialize/Powerdown

REQ

RSTRB, RTERM

WSTRB, WTERM

88

CKE, RESET

Control Logic

d64/72:

64/72

1

1

1

1

1

1

99

91

1:8 Demux 8:1 Mux

DIN 64/72

DEVICETYPE Register

DEVICEID Register

MODE Register

DOUT

REFROW Register

RASINTERVAL

DEVICEMFGR Register

64/72

64b for 64M

72b for 18M

d

64/72

d

64/72

64/72

Register

d

1

64/72

MASK Register

64/72

d

d

64/72 ¥ 256 Page

64/72 ¥ 256

64/72 ¥ 256 ¥ 1024

c

Bank 3

c

4 banks per RDRAM for 64M

64/72 ¥ 256 Page

64/72 ¥ 256

64/72 ¥ 256 ¥ 1024

Bank 2

c

64/72 ¥ 256a Page

64/72 ¥ 256

64/72 ¥ 256a ¥ 512

Bank 1

a

256 octbytes per row for 18M

b

512 rows per bank for 18M

64/72 ¥ 256a ¥ 512

Bank 1

a

256 octbytes per row for 64M

b

1024 rows per bank for 64M

64/72 ¥ 256a Page

a

b

64/72 ¥ 256a ¥ 512

64/72 ¥ 256

a

b

Bank 0

b

64/72 ¥ 256

a

¥ 512

b

Bank 0

Fig. 3 18/64-Mbit Concurrent RDRAM Block Diagram

6/45

¡ Semiconductor MSM5718C50/MD5764802

BASIC OPERATION

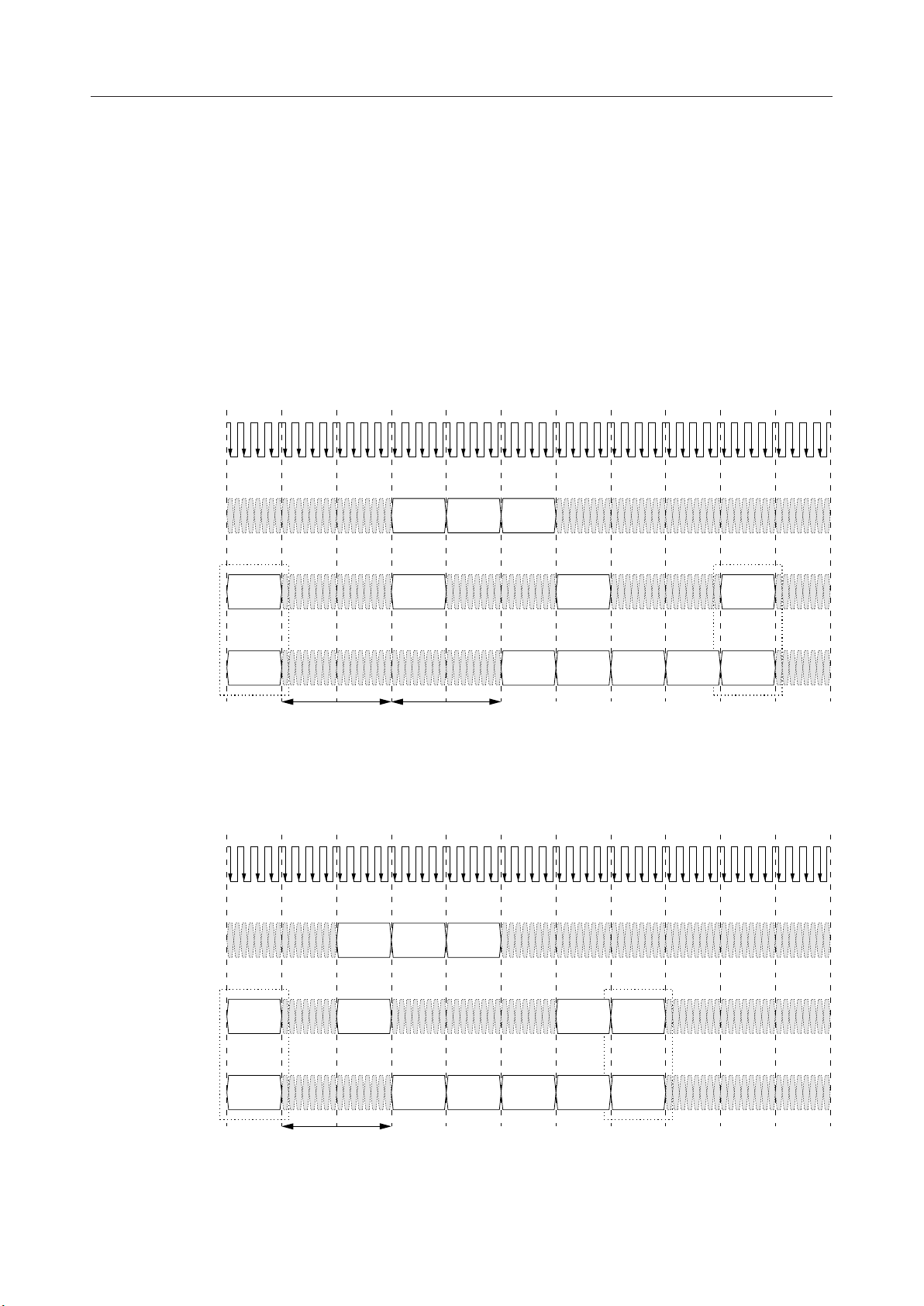

Figure 4 (a) shows an example of a read transaction. A transaction begins in interval T0 with the

transfer of a REQ packet. The REQ packet contains the command (ACTV/READ), a device, bank,

and row address (BNK/ROW) of the page to be activated, and the column address (COLa) of the first

octbyte to be read from the page.

The selected bank performs the activation of the selected row during T1 and T2 (the t

Next, the selected bank reads the selected octbyte during T3 and T4 (the t

interval). A second

CAC

RCD

interval).

command RSTRB (read strobe) is transferred during T3 and causes the first octbyte (DOUTa) to be

transferred during T5.

T

9

10

CLK

(RX/TXCLK)

ADDRESS

(BUSENABLE)

COMMAND

(BUSCTRL)

DQ8,..DQ0

(BUSDATA[8:0])

Bank Operation

T

0

ACTV

/READ

REQ

Packet

BNK/ROW

/COL a

T

1

T

2

T

3

T

4

T

5

T

6

T

7

T

T

8

COL b COL c COL d

RSTRB RTERM

Next

REQ

DOUT a DOUT b DOUT c DOUT d

t

RCD

t

CAC

CLK

(RX/TXCLK)

ADDRESS

(BUSENABLE)

COMMAND

(BUSCTRL)

DQ8,..DQ0

(BUSDATA[8:0])

Bank Operation

(b) BANK ACTIVATE AND RANDOM WRITE CYCLES WITHIN A PAGE

(a) BANK ACTIVATE AND RANDOM READ CYCLES WITHIN A PAGE

T

0

T

1

T

2

T

3

T

4

T

5

T

6

T

7

T

8

COL b COL c COL d

ACTV

/WRITE

REQ

Packet

BNK/ROW

/COL a

WSTRB WTERM

DIN a DIN b DIN c DIN d

t

RCD

Next

REQ

T

T

9

10

Fig. 4 Read and Write Transaction Examples

7/45

¡ Semiconductor MSM5718C50/MD5764802

In this example, three additional octbytes are read from the activated page. These column addresses

(COLb, COLc, and COLd) are transferred in T3, T4, and T5, respectively. The data octbytes (DOUTb,

DOUTc, and DOUTd) are transferred in T6, T7, and T8, The end of the data octbytes is signaled by

a third command RTERM (read terminate) in T6. The next REQ packet may be sent in T9, or in any

interval thereafter.

Figure 4 (b) shows an example of a write transaction. The transaction begins in interval T0 with the

transfer of a REQ packet. The REQ packet contains, the command (ACTV/WRITE), a device, bank,

and row address (BNK/ROW) of the page to be activated, and the column address (COLa) of the first

octbyte to be written to the page.

The selected bank performs the activation of the selected row during T1 and T2 (the t

RCD

interval).

A second command WSTRB (write strobe) is transferred during T2 and causes the first octbyte

(DINa) to be transferred during T3.

In this example, three additional octbytes are written to the activated page. These column addresses

(COLb, COLc, and COLd) are transferred in T2, T3, and T4 respectively. The data octbytes (DINb,

DINc, and DINd) are transferred in T4, T5, and T6. The end of the data octbytes is signaled by a third

command WTERM (write termination) in T6. The next REQ packet may be sent in T7, or in any

interval thereafter.

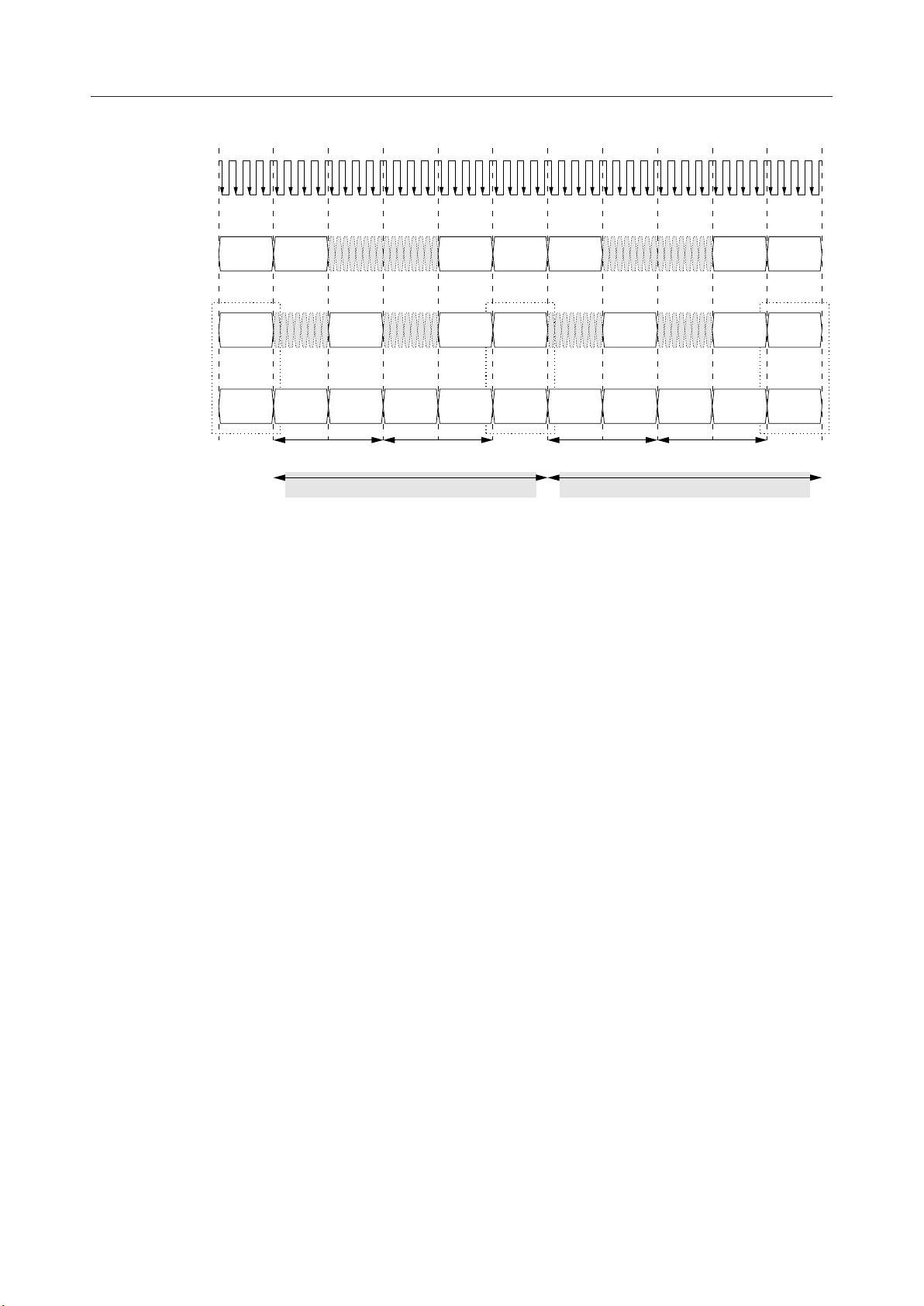

INTERLEAVED TRANSACTIONS

The previous examples showed noninterleaved transactions - the next REQ packet was transferred

after the last data octbyte of the current transaction. In an interleaved transaction, the next REQ packet

is transferred before the first data octbyte of the current transaction. This permits the row and column

access intervals of the next transaction to overlap the data transfer of the current transaction.

Figure 5 shows an example of interleaved read transactions. The first transaction proceeds exactly

as the noninterleaved example of Figure 4 (a) (all packets of the first transaction are labeled with “1”).

However, in T5 the REQ packet for the second transaction is transferred (all packets of the second

transaction are labeled with “2”). The t

octbytes and thus increase the effective bandwidth of the RDRAM since there are no unused

intervals.

RCD2

and t

intervals overlap the transfer of DOUT1 data

CAC2

A transaction consists of an address transfer phase and a data transfer phase. The REQ packet

performs address transfer, and the remaining packets perform data transfer (DOUT, COL, RSTRB,

and RTERM in the case of a read transaction). The time interval between the address and data transfer

phases of the current transaction may be adjusted to match the data length of the previous transaction

(as long as the row and column access times for the current transaction are observed). Thus, there ar e

no limits on the types of memory transaction which may be interleaved; any mixing of transaction

length and command type is permitted.

8/45

¡ Semiconductor MSM5718C50/MD5764802

CLK

(RX/TXCLK)

ADDRESS

(BUSENABLE)

COMMAND

(BUSCTRL)

DQ8,..DQ0

(BUSDATA[8:0])

Bank Operation

T

T

0

T

1

2

T

T

3

4

COL c0 COL d0 COL b1

ACTV

/READ

RTERM1

RSTRB1

REQ

Packet 1

BNK/ROW

/COL a1

DOUT a0 DOUT b0 DOUT c0 DOUT d0

t

RCD1

Data Transport 0 Overlaps Row/Column Access 1 Data Transport 1 Overlaps Row/Column Access 2

t

CAC1

Fig. 5 Interleaved Read Transaction Example

T

5

T

T

6

T

7

T

8

T

9

10

COL c1 COL d1 COL b2 COL c2

ACTV

/READ

REQ

Packet 2

BNK/ROW

/COL a2

RTERM2

RSTRB2

DOUT a1 DOUT b1 DOUT c1 DOUT d1

t

RCD2

t

CAC2

ACTV

/READ

REQ

Packet 3

BNK/ROW

/COL a3

9/45

¡ Semiconductor MSM5718C50/MD5764802

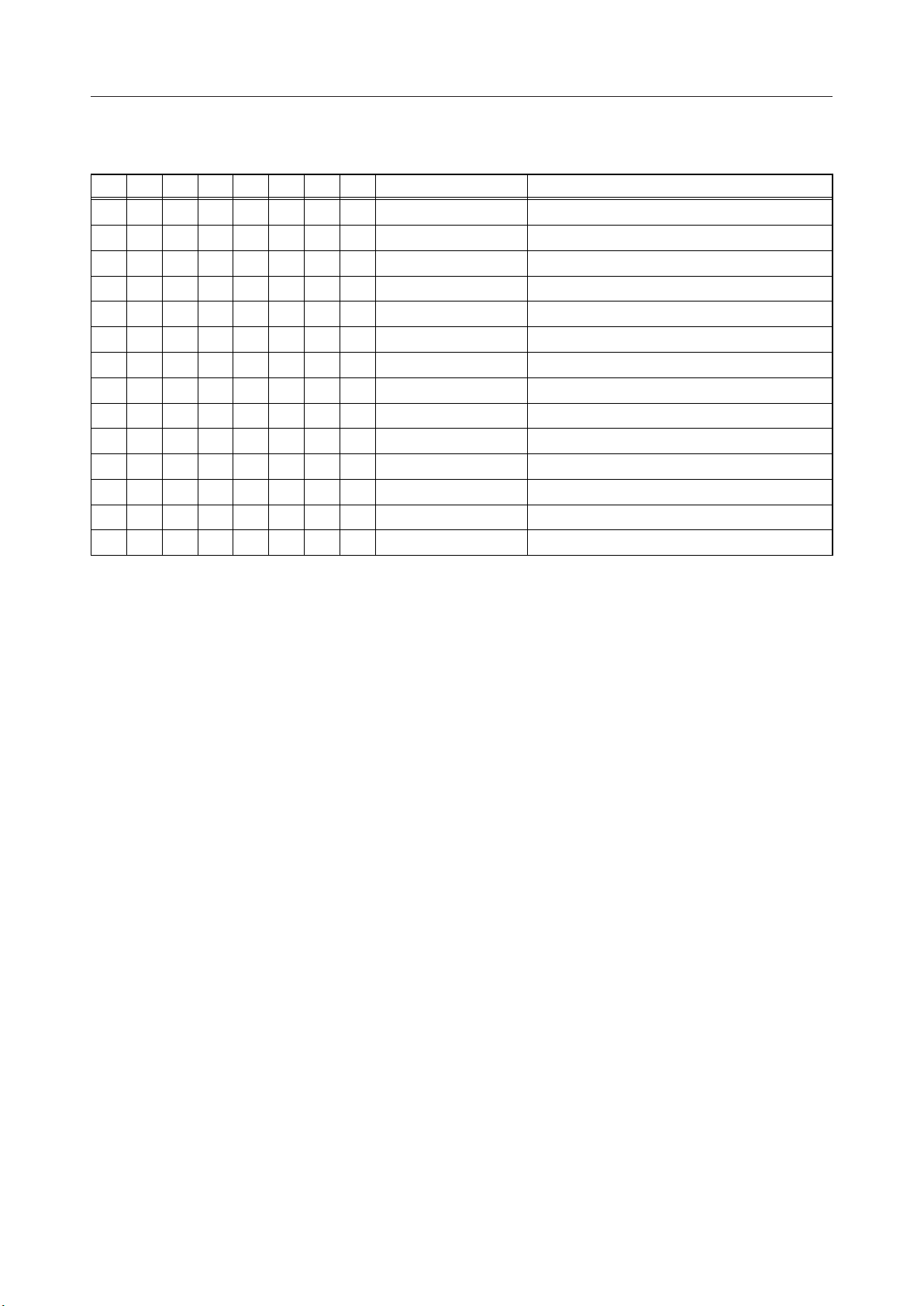

REQ PACKET (ADDRESS TRANSFER)

An REQ packet initiates a transaction by transferring the address and command information to the

RDRAM. Figure 6 shows the format of the REQ packet. Note that each RDRAM wire carries eight

bits of information in each t

PACKET

natural granularity with which to illustrate timing relationships. The clock that is actually used by

the RDRAM has a period of t

times t

CYCLE

.

CYCLE

In the REQ packet, the bits which are gray are reserved, and should be driven with a zero. In

particular, the bits in t

CYCLE t6

A35..A3: The address field A35..A3 consumes the greatest number of bits. These are allocated to

device, bank, row, and column addressing according to Table 3:

. This is the time required to transfer an octbyte of data and is the

, with information transferred on each clock edge. t

PACKET

is four

and t7 are needed for bus-turn-around during read transactions.

Table 3 A35..A3 Address Fields

Field 18M

COL A10..A3

ROW A19..A11

BNK A20

DEV A35..A21

64M

A10..A3

A20..A11

A22, A21

A35..A23

OP5..OP0: The command field OP5..OP0 specifies the type of transaction that is to be performed,

according to Table 4. The OP0 bit selects a read or write transaction, the OP1 bit selects a memory or

register space access, and OP5..OP2 select command options. These command options include B in

OP2 (see byte masking on page 22). D in OP3 for selecting broadcast operations (see refresh on page

35), and b1, b0 in OP5, OP4 (see bit masking on page 23).

ACTV: This bit specifies activation or precharge/activation of a bank at the beginning of a

transaction, and is designated by prepending “ACTV/” or “PRE/ACTV/” to the command.

AUTO: This bit specifies auto-precharge of a bank at the end of the transaction, and is designated

by appending “A” to the command.

START: This bit is always set to a one and indicates the beginning of a request to the RDRAM.

REGSEL: This bit is used for accessing registers.

PEND2...PEND0: This field is set to “000” for noninterleaved transactions, and to a nonzero value

for interleaved transactions. This is the number of previous STRB and TERM packets the RDRAM

is to skip. Refer to the

Concurrent RDRAM Design Guide

for further details.

M7..M0: This field is used to perform byte masking of the first data octbyte DINa for all memory write

transactions (OP1, OP0 = 01). Refer to byte masking on page 22.

10/45

¡ Semiconductor MSM5718C50/MD5764802

Table 4 Command Encoding

ACTV AUTO

00000X00READ Read

0 0 b1 b0 D B 0 1 WRITE Write

00000110RREG Register Read

0000D111WREG Register Write (D)

01000X00READA Read/AutoPrecharge

0 1 b1 b0 D B 0 1 WRITEA Write/AutoPrecharge (b1, b0, D, B)

10000X00ACTV/READ Activate/Read

1 0 b1 b0 D B 0 1 ACTV/WRITE Activate/Write (b1, b0, D, B)

11000X00ACTV/READA Activate/Read/AutoPrecharge

1 1 b1 b0 D B 0 1 ACTV/WRITEA Activate/Write/AutoPrecharge (b1, b0, D, B)

10000X00PRE/ACTV/READ Precharge/Activate/Read

1 0 b1 b0 D B 0 1 PRE/ACTV/WRITE Precharge/Activate/Write (b1, b0, D, B)

11000X00PRE/ACTV/READA Precharge/Activate/Read/AutoPrecharge

1 1 b1 b0 D B 0 1 PRE/ACTV/WRITEA

OP5 OP4 OP3 OP2 OP1 OP0 Command Description

(b1, b0, B masking and D broadcast options)

Precharge/Activate/Write/AutoPrecharge (b1, b0, D, B)

11/45

¡ Semiconductor MSM5718C50/MD5764802

t

PACKET

CLK

T

T

0

T

1

T

2

3

CLK

(RX/TXCLK)

ADDRESS

(BUSENABLE)

COMMAND

(BUSCTRL)

ACTV

/READ

REQ

Packet

DQ8,..DQ0

(BUSDATA[8:0])

t

CYCLE

t

t

0

t

1

2

t

PACKET

t

BNK/ROW

/COL a

= 4 • t

T

0

3

t

4

CYCLE

t

t

5

t

6

7

ADDRESS

COMMAND

DQ8

DQ7

DQ6

DQ5

DQ4

DQ3

DQ2

DQ1

OP4OP2OP5OP1START

A35A26OP3OP0

A34A25A17A9

A33A24A16A8

A32A23A15A7

A31A22A14A6

ACTV

A30A21A13A5

AUTO

A29A20A12A4

PEND2

A28A19A11A3

PEND1

M7

M6

M5

M4

M3

M2

M1

DQ0

REGSEL

A27A18A10

Fig. 6 REQ Packet Format

PEND0

M0

12/45

¡ Semiconductor MSM5718C50/MD5764802

DATA TRANSFER PACKETS

The next set of packet types are used for data transfer. Their formats are summarized in Figure 7.

As in the REQ packet, eight bits are transferred on each wire during each t

PACKET

interval. The rising

and falling edges of the RDRAM clock define the transfer windows for each of these bits. The data

transfer packets will align to the t

PACKET

intervals defined by the START bit of the REQ packet by

simply observing the timing rules that are developed in the next few sections of this document.

DIN and DOUT Packets

There are nine wires allocated for the data bytes. These wires are labeled DQ8..DQ0. The eight bytes

transferred in a DIN or DOUT packet have 72 bits, which are labeled D0..D63 (on the DQ0..DQ7

wires) and E0..E7 (on the DQ8 wire). The 18Mbit RDRAM have storage cells for the E0..E7 bits. The

E0..E7 bits are also used with byte masking operations. This is described in the section on byte

masking on page 22.

COL Packet

The column address A10..A3 of the first octbyte of data (DINa or DOUTa) is provided in the REQ

packet. The COL packet contains an eight bit field A10..A3, which provides the column address for

the second and subsequent data octbytes. The COL packets have a fixed timing relationship with

respect to the DIN and DOUT packets to which they correspond. As the DIN and DOUT packets are

moved (to accommodate interleaving ), the COL packets move with them.

RSTRB and RTERM Packets

The RSTRB and RTERM packets indicate the beginning and end of the DOUT packets that are

transferred during a read transaction. The RSTRB and RTERM packets are each eight bits and consist

of a single “1” in an odd t

position, with the other seven positions “0”. Note that when a

CYCLE

transaction transfers a single data octbyte, the RSTRB and RTERM packets will overlay one another.

This is permitted and is in fact the reason that each packet consists of a single asserted bit. An example

of this case is shown in Figure 14 (a). There will be transaction situations in which the RTERM

overlays a RSTRB packet (two octbyte interleaved transaction). Again, this is permitted. The general

rule is that the RTERM may overlay any of the other packets on the Command (BUSCTRL) wire, and

RSTRB may overlay any other except for a REQ packet.

WSTRB and WTERM Packets

The WSTRB and WTERM packets indicate the beginning and end of the series of DIN packets that

are transferred during a write transaction. The WSTRB and WTERM packets are each eight bits and

consist of a single “1” in an odd t

position, with the other seven positions “0”. Note that when

CYCLE

a transaction transfers a single data octbyte, the WSTRB and WTERM packets will not overlay one

another (unlike the case of a one octbyte read). An example of this case is shown in Figure 14 (b). There

will be transaction situations in which the WSTRB overlays a REQ packet (no bank activate). Again,

this is permitted. An example of this is shown in Figure 9 (a). The general rule is that the WSTRB may

overlay any of the other packets on the Command (BUSCTRL) wire, and WTERM may overlay any

other except for a REQ packet.

13/45

¡ Semiconductor MSM5718C50/MD5764802

CKE PACKET

The average power of the RDRAM can be reduced by using Suspend power mode. This is done by

setting the FR field of the MODE register to a zero (the MODE register is shown in Figure 17). A CKE

packet must be sent a time t

ahead of each REQ packet (this is shown in interval T0 in Figure 21

CKE

(b)). This causes the RDRAM to transition from Suspend to Enable mode. When the RDRAM has

finished the transaction, it returns to Suspend mode. The CKE packet will overlay the RSTRB and

RTERM packets when transactions are interleaved. If the FR field is set to a one, CKE packets are not

used and the RDRAM remains in Enable mode.

RESET PACKET

The RESET packet is used during initialization. When RESET packets are driven for a time t

RESET

or

greater, the RDRAM will assume a known state. Because the RESET packet is limited to this one use,

it will not interact with the other packet types. This is illustrated in Figure 21 (a).

PWRUP PACKET

The PWRUP packet is used to cause an RDRAM to transition from Powerdown to Enable mode. This

is illustrated in Figure 21 (c).

14/45

Loading...

Loading...