OKI MSC23V47257TA60BS18, MSC23V47257SA60BS18, MSC23V47257TA70BS18, MSC23V47257SA70BS18 Datasheet

Preliminary

MSC23V47257TA-xxBS18/MSC23V47257SA-xxBS18¡ Semiconductor

¡ Semiconductor

MSC23V47257TA-xxBS18/

MSC23V47257SA-xxBS18

4,194,304-Word ¥ 72-Bit DRAM MODULE : FAST PAGE MODE TYPE WITH EDO

DESCRIPTION

The Oki MSC23V47257TA-xxBS18/MSC23V47257SA-xxBS18 is a fully decoded 4,194,304-word

¥ 72-bit CMOS dynamic random access memory composed of eighteen 16-Mb DRAMs (4M ¥ 4)

in TSOP or SOJ packages mounted with decoupling capacitors on an 168-pin glass epoxy DIMM

Package supports any application where high density and large capacity of storage memory are

required.

FEATURES

• 4,194,304-word ¥ 72-bit (8 Byte ECC) organization

• 168-pin DIMM

MSC23V47257TA-xxBS18 : TSOP type

MSC23V47257SA-xxBS18 : SOJ type

• Single 3.3 V supply ±0.3 V tolerance

• Input : LVTTL compatible

• Output : LVTTL compatible, 3-state, nonlatch

• Refresh : 2048 cycles/32 ms

• CAS before RAS refresh, CAS before RAS hidden refresh, RAS-only refresh capability

• Multi-bit test mode capability

• Fast Page Mode with EDO capability

• Serial Presence Detect

PRODUCT FAMILY

Family

MSC23V47257TA-60BS18

MSC23V47257SA-60BS18

MSC23V47257TA-70BS18

MSC23V47257SA-70BS18

Access Time (Max.)

RACtAAtCAC

60 ns

30 ns

15 ns

70 ns

35 ns

20 ns

t

OEA

15 ns

20 ns

Cycle Time

(Min.)

110 ns

130 ns

Operating (Max.)

Power Dissipation

Standby (Max.)t

7776 mW

64.8 mW

7128 mW

701

MSC23V47257TA-xxBS18/MSC23V47257SA-xxBS18 ¡ Semiconductor

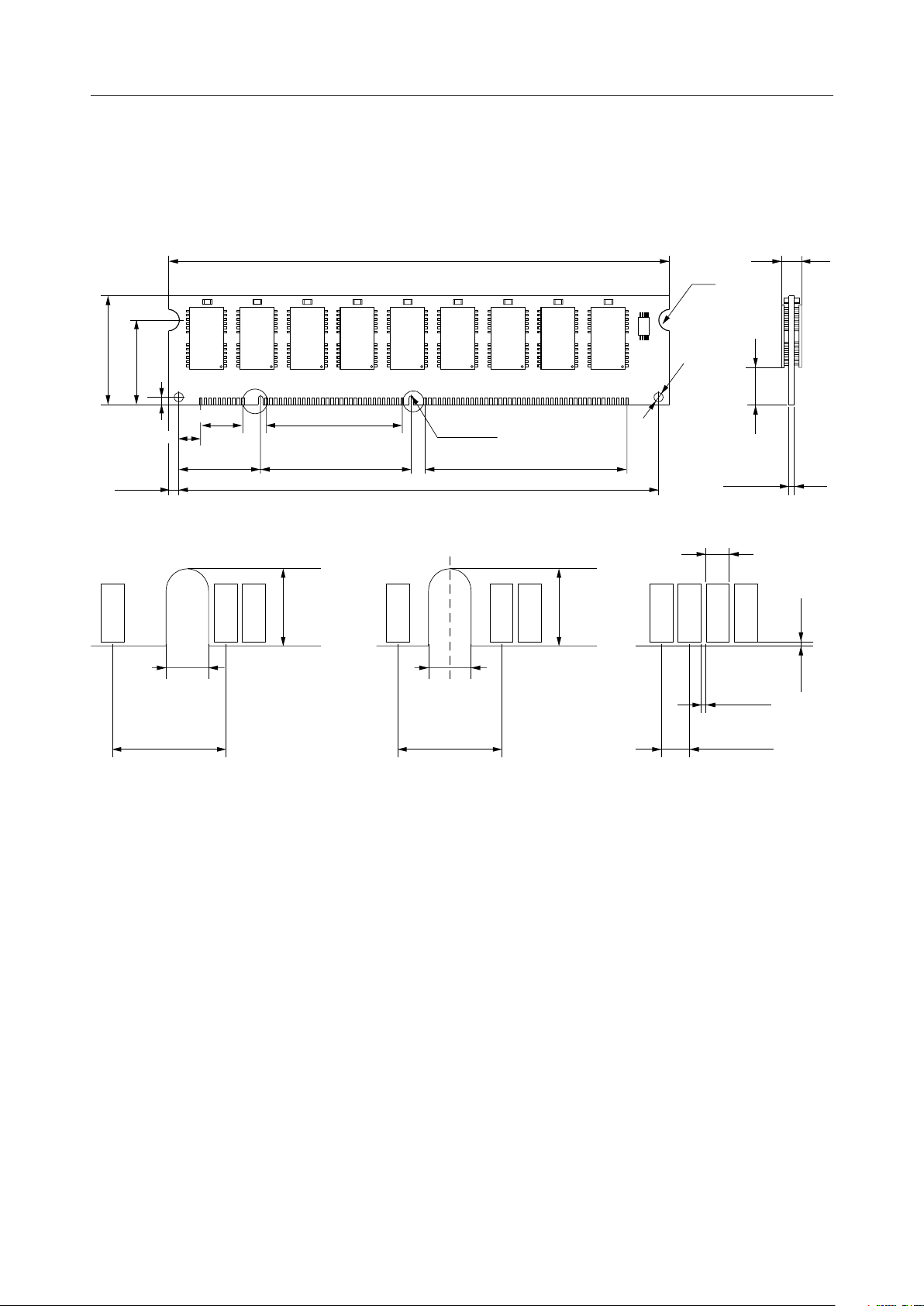

PIN CONFIGURATION

MSC23V47257TA-xxBS18

(Unit : mm)

*1

25.4 ±0.13

17.78 ±0.13

5.89 ±0.13

3.0 ±0.13

11.43 ±0.1

21.495 ±0.13

133.35 ±0.2

36.83 ±0.1

45.18 ±0.13 54.61 ±0.1

127.35 Typ.3.0 ±0.13

2 – R1 ±0.1

2 – R2 ±0.1

2 – φ3 ±0.1

84BA

6.0 Min.

4.00 Max.

1.27 ±0.1

CL

3.00 ±0.13

2.0 ±0.1

6.35 ±0.1

3.00 ±0.13

2.0 ±0.1

6.35 ±0.1

DETAIL BDETAIL A

*1 The common size difference of the board width 19.78 mm of its height is

specified as ±0.2. The value above 19.78 mm is specified as ±0.5.

1.0 ±0.1

0.25 Max.

0.23 Min.

1.27 ±0.1

702

Loading...

Loading...