Page 1

FEDR27V852E-01-01

1

Semiconductor

This version: Jan. 2001

MR27V852E

524,288–Word ×××× 16–Bit or 1,048,576–Word ×××× 8–Bit

8–Word x 16-Bit or 16–Word x 8-Bit Page Mode One Time PROM

GENERAL DESCRIPTION

The MR27V852E is a 8 Mbit electrically One Time Programmable Read-Only Memory with page mode. Its

configuration can be electrically switched betw een 524,28 8-word × 16-bit and 1,048,576-word × 8-bit by the state

of the BYTE pin. The MR27V852E supports high speed asynchronous read operation using a single 3.3V power

supply.

FEATURES

· 524,288-word × 16-bit/1,048,576-word × 8-bit electrically switchable configuration

· Page size of 8-word x 16-Bit or 16-word x 8-Bit

· +3.3 V power supply

· Access time

Random access mode 100 ns MAX

Page access mode 30 ns MAX

· Operating current 80 mA MAX

· Standby current 50 µA MAX

· Input/Output TTL compatible

· Tri-state output

· Packages:

42-pin plastic DIP (DIP42-P-600-2.54) (Product Name : MR27V852ERA)

42-pin plastic SOJ (SOJ42-P-400-1.27) (Product Name : MR27V852EJA)

1/13

Page 2

1

Semiconductor

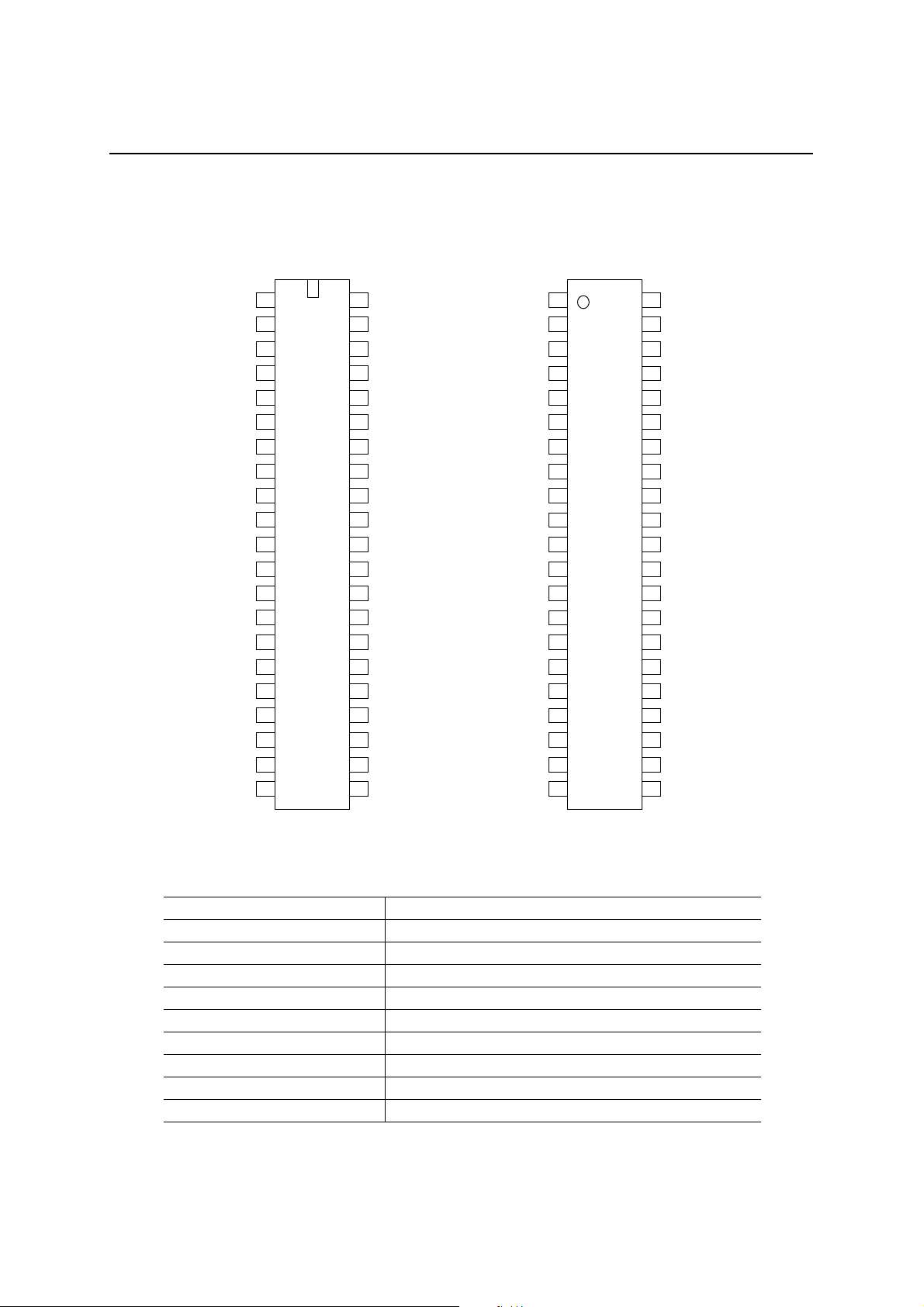

PIN CONFIGURATION (TOP VIEW)

A18

A17

A7

A6

A5

A4

A3

A2

A1

A0

CE

V

OE

D0

D8

D1

D9

D2

D10

D3

D11

1

2

3

4

5

6

7

8

9

10

11

12

SS

13

14

15

16

17

18

19

20

21

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

NC

A8

A9

A10

A11

A12

A13

A14

A15

A16

BYTE/ V

V

D15/A–1

D7

D14

D6

D13

D5

D12

D4

V

FEDR27V852E-01-01

MR27V852E

1

A18

2

A17

3

A7

4

A6

5

A5

6

A4

7

A3

8

A2

9

A1

10

A0

11

PP

SS

CC

CE

V

OE

D0

D8

D1

D9

D2

D10

D3

D11

12

SS

13

14

15

16

17

18

19

20

21

NC

42

A8

41

A9

40

39

A10

A11

38

A12

37

A13

36

35

A14

A15

34

A16

33

BYTE/ V

32

31

V

D15/A–1

30

D7

29

D14

28

27

D6

D13

26

D5

25

D12

24

23

D4

22

V

PP

SS

CC

42-pin DIP

42-pin SOJ

Pin name Functions

D15/A–1 Data output/Address input

A0 to A18 Address input

D0 to D14 Data output

CE Chip enable

OE Output enable

BYTE/V

V

CC

V

SS

PP

Mode switch/Program power supply voltage

Power supply voltage

GND

NC Non connection

2/13

Page 3

1

A0

Semiconductor

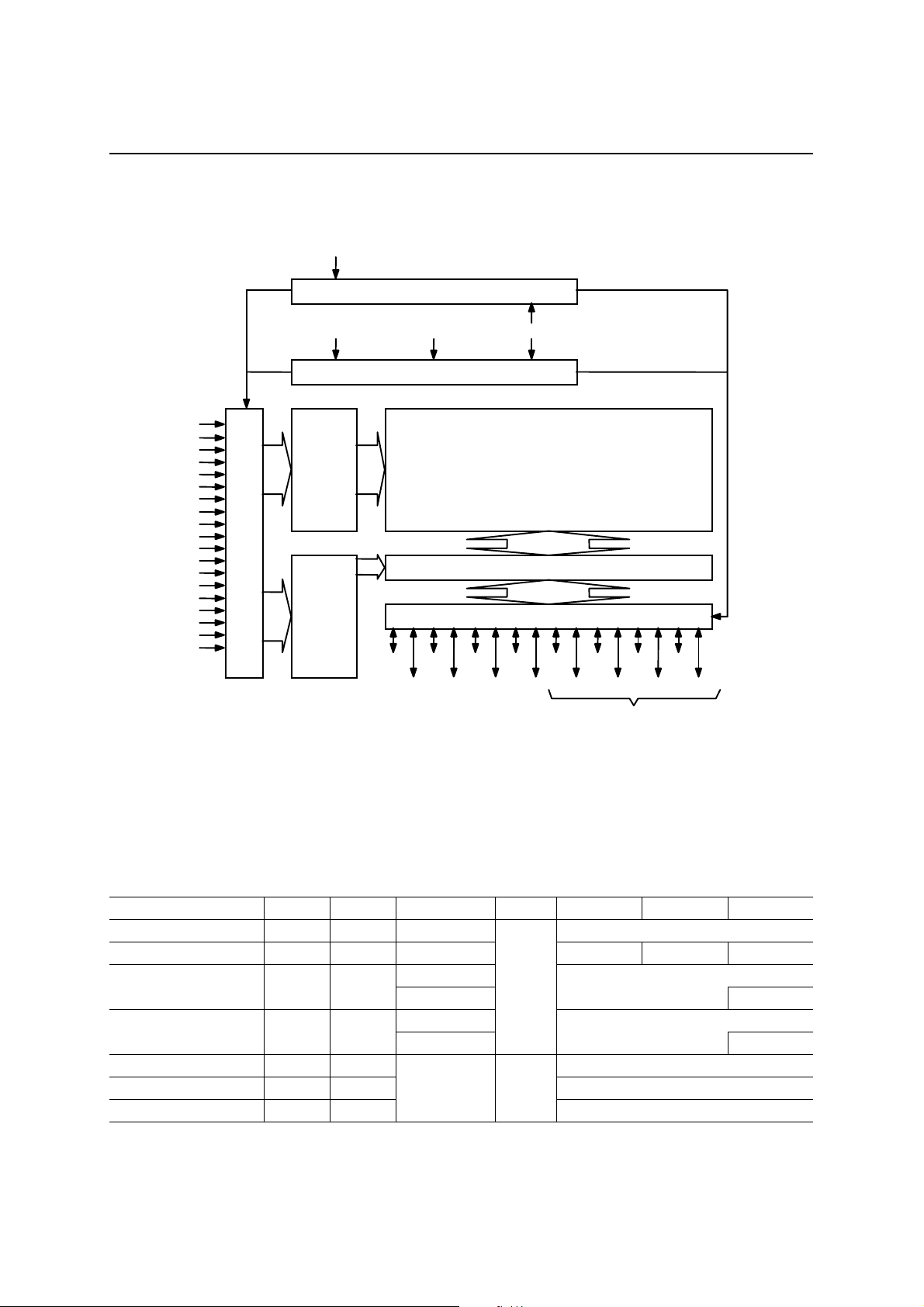

BLOCK DIAGRAM

FEDR27V852E-01-01

MR27V852E

A–1

× 8/× 16 Switch

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

Address Buffer

CE BYTE/V

OE

CE PGMOE

Memory Cell Matrix

524,288 × 16-Bit or 1,048,576× 8-Bit

Row Decoder

Multiplexer

Output Buffer

Column Decoder

D0 D2 D4 D6 D8 D10 D12 D14

D1 D3 D5 D7 D9 D11 D13 D15

PP

In 8-bit output mode, these pins

are placed in a high-Z state and

pin D15 functions as the A-1

address pin.

FUNCTION TABLE

Mode CE OE BYTE/V

PP

Read (16-Bit) L L H D

Read (8-Bit) L L L D

Output disable L H

Standby H ∗

H

L

H

L

Program L H D

Program inhibit H H Hi–Z

9.75 V 4.0 V

Program verify H L

∗: Don’t Care (H or L)

V

CC

3.3 V

D0 to D7 D8 to D14 D15/A–1

OUT

Hi–Z L/H

Hi–Z

Hi–Z

D

OUT

∗

∗

IN

OUT

3/13

Page 4

FEDR27V852E-01-01

1

Semiconductor

MR27V852E

ABSOLUTE MAXIMUM RATINGS

Parameter Symbol Condition Value Unit

Operating temperature under bias Ta 0 to 70 °C

Storage temperature Tstg

Input voltage V

Output voltage V

Power supply voltage V

Program power supply voltage V

Power dissipation per package P

I

O

CC

PP

D

—

–55 to 125 °C

–0.5 to VCC+0.5 V

relative to V

SS

–0.5 to VCC+0.5 V

–0.5 to 5 V

–0.5 to 11.5 V

—1.0W

RECOMMENDED OPERATING CONDITIONS

(Ta = 0 to 70°C)

Parameter Symbol Condition Min. Typ. Max. Unit

VCC power supply voltage V

VPP power supply voltage V

Input “H” level V

Input “L” level V

CC

PP

IH

IL

VCC = 3.0 to 3.6 V

3.0 — 3.6 V

–0.5 — VCC+0.5 V

2.2 — VCC+0.5∗ V

–0.5∗∗ —0.6V

Voltage is relative to VSS.

∗ : Vcc+1.5 V(Max.) when pulse width of overshoot is less than 10 ns.

∗∗ : -1.5 V(Min.) when pulse width of undershoot is less than 10 ns.

4/13

Page 5

1

Semiconductor

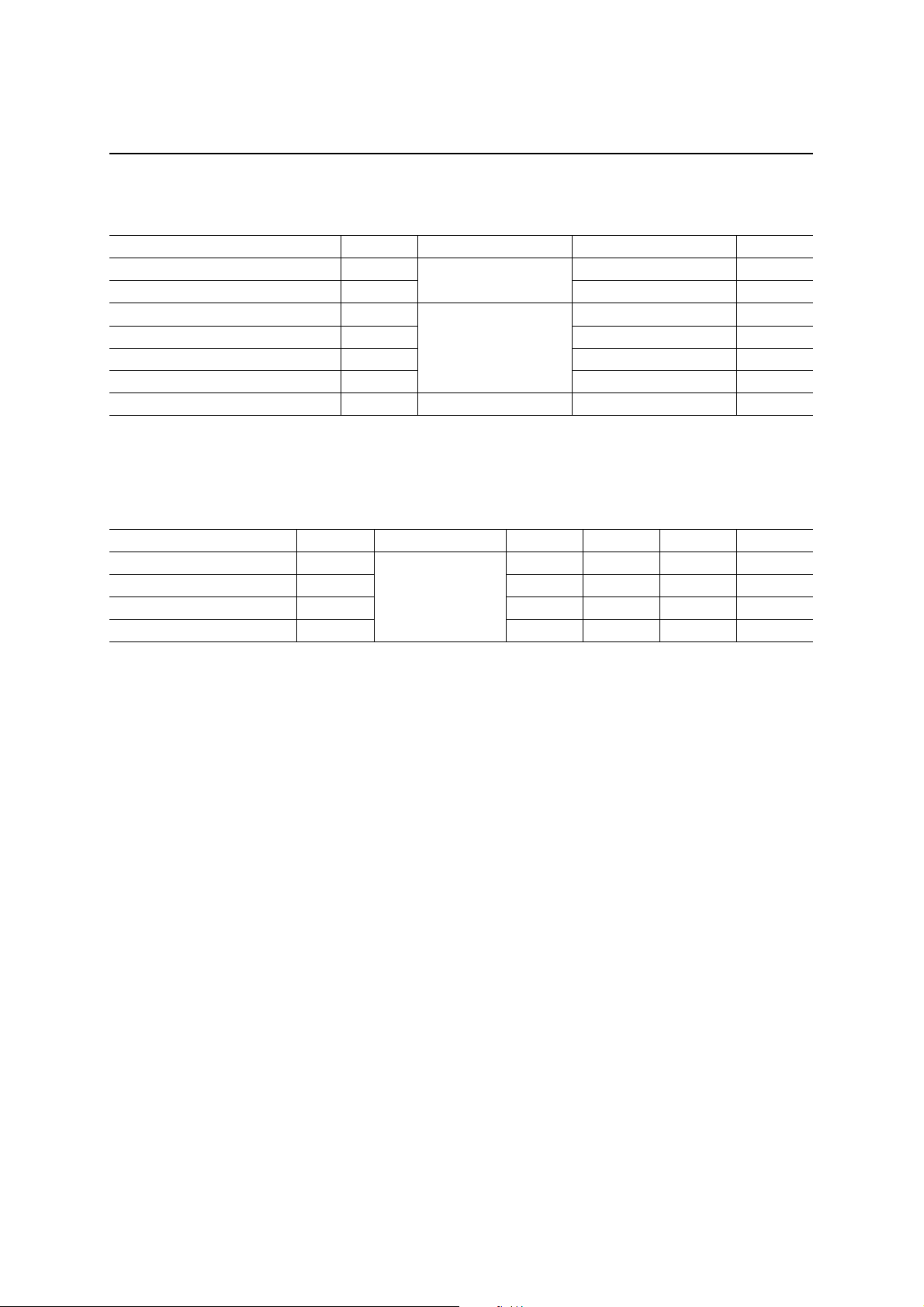

ELECTRICAL CHARACTERISTICS

DC Characteristics

parameter Symbol Condition Min. Typ. Max. Unit

Input leakage current I

Output leakage current I

VCC power supply current

(Standby)

V

power supply current

CC

(Read)

VPP power supply current I

Input “H” level V

Input “L” level V

Output “H” level V

Output “L” level V

I

CCSC

I

CCST

I

CCA

LI

LO

PP

IH

IL

OH

OL

FEDR27V852E-01-01

MR27V852E

(VCC = 3.3 V ±0.3 V, Ta = 0 to 70°C)

VI = 0 to V

VO = 0 to V

CE = V

CE = V

CE = VIL, OE = V

CC

CC

CC

IH

IH

tc = 100 ns

VPP = V

CC

—2.2—V

— –0.5∗∗ —0.6V

IOH = –2 mA 2.4 — — V

IOL = 2.1 mA — — 0.4 V

——10µA

——10µA

——50µA

—— 1mΑ

——80mA

——10µA

+0.5∗ V

CC

Voltage is relative to VSS.

∗ : Vcc+1.5 V(Max.) when pulse width of overshoot is less than 10 ns.

∗∗ : -1.5 V(Min.) when pulse width of undershoot is less than 10 ns.

AC Characteristics

Parameter Symbol Condition Min. Max. Unit

Address cycle time t

Address access time t

Page cycle time t

Page access time t

CE access time t

OE access time t

Output disable time

Output hold time t

t

t

C

ACC

PC

PAC

CE

OE

CHZ

OHZ

OH

— 100 — ns

CE = OE = V

IL

—30—ns

— — 30 ns

OE = V

IL

CE = V

IL

OE = V

IL

CE = V

IL

CE = OE = V

IL

Measurement conditions

Input signal level--------------------------------

Input timing reference level------------------

Output load --------------------------------------

Output timing reference level----------------

0 V/3 V

0.8 V/2.0 V

100 pF

0.8 V/2.0 V

(VCC = 3.3 V ±0.3 V, Ta = 0 to 70°C)

— 100 ns

— 100 ns

—30ns

030ns

025ns

0—ns

5/13

Page 6

1

Semiconductor

Timing Chart (Read Cycle)

Random Access Mode Read Cycle

FEDR27V852E-01-01

MR27V852E

Address

t

CE

CE

t

OE

OE

t

ACC

Dout

Hi-Z

Page Access Mode Read Cycle

A3 to A18

t

C

t

C

Valid Data

t

C

t

OH

t

ACC

t

CHZ

t

OH

t

OHZ

Valid Data

Hi-Z

A-1 to A2 (Byte mode)

A0 to A2 (Word mode)

CE

OE

Dout

Hi-Z

t

ACC

t

PC

t

CE

t

OE

t

PAC

t

PAC

t

PC

t

OH

t

CHZ

t

OHZ

Hi-Z

6/13

Page 7

1

Semiconductor

ELECTRICAL CHARACTERISTICS (PROGRAMMING OPERATION)

DC Characteristics

Parameter Symbol Condition Min. Typ. Max. Unit

Input leakage current I

VPP power supply current (Program) I

VCC power supply current I

Input “H” level V

Input “L” level V

Output “H” level V

Output “L” level V

Program voltage V

VCC power supply voltage (Program) V

VCC power supply voltage (Verify1) V

VCC power supply voltage (Verify2) V

LI

PP2

CC

IH

IL

OH

OL

PP

CC

CV1

CV2

VI = VCC+0.5 V — — 10 µA

CE = V

IL

——50mA

———80mA

—3.0—V

— –0.5 — 0.8 V

IOH = –400 µA2.4 — — V

IOL = 2.1 mA — — 0.45 V

— 9.5 9.75 10.0 V

— 3.9 4.0 4.1 V

— 2.9 3.0 3.1 V

— 3.5 3.6 3.7 V

FEDR27V852E-01-01

MR27V852E

(Ta = 25°C ± 5°C)

+0.5 V

CC

Voltage is relative to VSS.

AC Characteristics

(VCC = 4.0 V ±0.1 V, BYTE/VPP = 9.75 V ±0.25 V, Ta = 25°C ±5°C)

Parameter Symbol Condition Min. Typ. Max. Unit

Address set-up time t

OE set-up time t

Data set-up time t

Address hold time t

Data hold time t

Output float delay time from OE t

V

voltage set-up time t

PP

Program pulse width t

Data valid from OE t

Address hold from OE high t

AS

OES

DS

AH

DH

OHZ

VS

PW

OE

AOH

— 100 — — ns

—2——µs

— 100 — — ns

—2——µs

— 100 — — ns

— 0 — 100 ns

—2——µs

— 9 10 11 µs

— — — 100 ns

—0——ns

Pin Check Function

Pin Check Function is to check contact between each device-pin and each socket-lead with EPROM programmer.

Setting up address as following condition call the preprogrammed codes on device outputs.

(VCC = 3.3 V ±0.1 V, CE = VIL, OE = VIL, BYTE/VPP = VIH, Ta = 25°C ±5°C)

A0 A1 A2 A3 A4 A5 A6 A7 A8 A9

010101010

101010101

A10 A11 A12 A13 A14 A15 A16 A17 A18

∗

010101001FF00

VH

∗

10101011000FF

VH

Other conditions

∗: VH = 8 V ± 0.25 V

DATA

FFFF

7/13

Page 8

1

Semiconductor

Consecutive Programming Waveforms

A0 to A18

FEDR27V852E-01-01

MR27V852E

t

AS

CE

OE

t

DS

D0 to D15

t

VS

BYTE/Vpp

Consecutive Program Verify Waveforms

t

Din

PW

t

AH

High

t

DH

Din

A0 to A18

CE

OE

D0 to D15

BYTE/Vpp

t

ACC

t

OE

High

t

Dout

AHO

t

OHZ

Dout

9.75 V

8/13

Page 9

1

Semiconductor

Program and Program Verify Cycle Waveforms

A0 to A18

FEDR27V852E-01-01

MR27V852E

t

AS

t

AHO

CE

t

PW

t

OES

OE

t

OE

t

OHZ

Dout

D0 to D15

BYTE/Vpp

t

OHZ

t

DS

t

DH

Din

9.75 V

Pin Capacitance

(VCC = 3.3 V, Ta = 25°C, f = 1 MHz)

Parameter Symbol Condition Min. Typ. Max. Unit

Input C

BYTE/V

PP

Output C

IN1

C

IN2

OUT

VI = 0 V

VO = 0 V — — 10(12)

——10

— — 120

( ):DIP only

pF

9/13

Page 10

1

Semiconductor

Programming/Verify Flow Chart

FEDR27V852E-01-01

MR27V852E

Programming

Bad Insertion

Increment Address

Start

NG

Pin Check

PASS

Address = First Location

V

= 4.0 V

CC

= 9.75 V

V

PP

Program 10 µs

NO

Last Address?

YES

Address = First Location

X = 0

Verify

Start

NG

Pin Check

PASS

Address = First Location

VCC = 3.0 V/VPP = 3.0 V (Verify1)

Verify

NG

PASS

V

= 3.6 V/VPP = 3.6 V (Verify2)

CC

Verify

NG

PASS

Device Passed

Bad Insertion

Device Failed

Increment Address

Verify(One Word)

PASS

NO

Last Address?

YES

= 3.0 V/VPP = 3.0 V (Verify1)

V

CC

Verify

PASS

Device Passed

NG

NG

Device Failed

X = X+1

YES

X = 2?

NO

Program 10 µs

10/13

Page 11

1

DIP42-P-600-2.54

Package material Epoxy resin

Lead frame material 42 alloy

Pin treatment

Solder plating (≥5µm)

Package weight (g) 6.20 TYP.

5

Rev. No./Last Revised 2/Dec. 11, 1996

Semiconductor

PACKAGE DIMENSIONS

FEDR27V852E-01-01

MR27V852E

(Unit: mm)

11/13

Page 12

1

SOJ42-P-400-1.27

Mirror finish

Package material Epoxy resin

Lead frame material 42 alloy

Pin treatment

Solder plating (≥5µm)

Package weight (g) 1.86 TYP.

5

Rev. No./Last Revised 5/Dec. 5, 1996

Semiconductor

FEDR27V852E-01-01

MR27V852E

(Unit: mm)

Notes for Mounting the Surface Mount Type Package

The surface mount type packages are very susceptible to heat in reflow mounting and humidity

absorbed in storage.

Therefore, before you perfor m reflow m ounting, c ontac t Ok i’s res ponsibl e s ales per son f or the pro duct

name, package name, pin n umber, package code and desired m ounting conditions (reflow method,

temperature and times).

12/13

Page 13

FEDR27V852E-01-01

1

Semiconductor

MR27V852E

NOTICE

1. The information contained herein can change without notice owing to produ ct and/or technical improvements.

Before using the product, please make sure that the information being referred to is up-to-date.

2. The outline of action and examples for application circuits described herein have been chosen as an

explanation for the standard action an d performan ce of the product. Wh en planning to use t he product, pleas e

ensure that the external conditions are reflected in the actual circuit, assembly, and program designs.

3. When designing your product, please use our product below the specified maximum ratings and within the

specified operating ranges including, but not limited to, operating voltage, power dissipation, and operating

temperature.

4. Oki assumes no responsibility or liability whatsoever for any failure or unusual or unexpected operation

resulting from misuse, neglect, improper installation, repair, alteration or accident, improper handling, or

unusual physical or electrical stress including, but not limited to, exposure to parameters beyond the s pecified

maximum ratings or operation outside the specified operating range.

5. Neither indemnity against nor license of a third party’s industrial and intellectual property right, etc. is

granted by us in connection with the use of the product and/ or the information and draw ings contained h erein.

No responsibility is assumed by us for any infringement of a third party’s right which may result from the use

thereof.

6. The products listed in this document are intended for use in general electronics equipment for commercial

applications (e.g., office automation, communication equipment, measurement equipment, consumer

electronics, etc.). These products are not authorized for u s e in any system or application that requ ires s pecial

or enhanced quality and reliability characteristics nor in any system or applicatio n where the failure of s uch

system or application may result in the loss or damage of property, or death or injury to humans.

Such applications include, but are not limited to, traf fic and automotive equipment, s afety devices, aerospace

equipment, nuclear power control, medical equipment, and life-support systems.

7. Certain products in this document may need government approval before they can be exported to particular

countries. The purchaser assumes the responsibility of determining the legality of export of these products

and will take appropriate and necessary steps at their own expense for these.

8. No part of the contents contained herein may be reprinted or reproduced without our prior permission.

Copyright 2001 Oki Electric Industry Co., Ltd.

13/13

Loading...

Loading...