Page 1

UM10462

LPC11U3x/2x/1x User manual

Rev. 5.5 — 21 December 2016 User manual

Document information

Info Content

Keywords LPC1 1U3x/2x/1x, ARM Cortex-M0, microcontroller, LPC11U12,

LPC1 1U14, LPC11U13, USB, LPC11U22, LPC11U23, LPC1 1U24,

LPC1 1U34, LPC11U35, LPC11U36, LPC11U37, LPC11U37H, I/O Handler

Abstract LPC11U3x/2x/1x User manual

Page 2

NXP Semiconductors

UM10462

LPC11U3x/2x/1x User manual

Revision history

Rev Date Description

5.5 20161221 Modifications:

• Updated Table 200 “USBD_API_INIT_PARAM class structure” with:

Parameters:

a. hUsb = Handle to the USB device stack.

Returns:

The call back should return ErrorCode_t type to indicate success or error condition.

• Updated Table 208 “USBD_HW_API class structure”:

Added GetMemSize to the text: This function is called by application layer before calling

pUsbApi->hw->

Added Parameters:

– hUsb = Handle to the USB device stack.

– EPNum = Endpoint number corresponding to the event as per USB specification. ie.

An EP1_IN isrepresented by 0x81 number. For device events set this param to 0x0.

– event = Type of endpoint event. See USBD_EVENT_T for more details.

– enable = 1 - enable event, 0 - disable event.Returns:Returns ErrorCode_t type to

indicate success or error condition.Return values:1. LPC_OK(0) = - On success2.

ERR_USBD_INVALID_REQ(0x00040001) = - Invalid event type.

• Added on-chip local RAM to Section 20.8.8 “RAM used by ISP command handler”,

Section 20.8.9 “RAM used by IAP command handler”

commands”

• Deleted: The boot sector can not be prepared by this command from Section 20.14.1

“Prepare sector(s) for write operation”, Table 384 “IAP Copy RAM to flash command”,

and Table 385 “IAP Erase Sector(s) command”.

5.4 20161007 Modifications:

• Added text after Table 227 “Endpoint commands”: For EP0 transfers, the hardware will

do auto handshake as long as the ACTIVE bit is set in EP0_IN/OUT command list.

Unlike other endpoints, the hardware will not clear the ACTIVE bit after transfer is done.

Thus, the software should manually clear the bit whenever it receives new setup packet

and set it only after it has queued the data for control transfer.

5.3 20140611 Modifications:

• I/O Handler interrupt added in T able 59 “Connection of interrupt sources to the Vectored

Interrupt Controller”.

• NVIC register description added. See Section 6.5.

, and Section 20.14 “IAP

UM10462 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2016. All rights reserved.

User manual Rev. 5.5 — 21 December 2016 2 of 523

Page 3

NXP Semiconductors

UM10462

LPC11U3x/2x/1x User manual

Revision history

Rev Date Description

5.2 20140331 Modifications:

…continued

• Part LPC11U22FBD48/301 added.

• Use of IAP mode with power profiles clarified. Use power profiles in default mode when

executing IAP commands. See Section 20.14 “IAP commands” and Section 5.3.

• Section 5.3 added to clarify use of power profiles.

• Watchdog interrupt flag polarity corrected: This flag is cleared by writing a 1 to the

WDINT bit in the MOD register (Section 17.8.1 “Watchdog mode register”).

• Figure 69 “Boot process flowchart” corrected.

• T able 15 “Internal resonant crystal control register (IRCCTRL, address 0x4004 8028) bit

description” added.

• Remark added to Section 3.9.4.3 “Wake-up from Deep-sleep mode” and

Section 3.9.5.3 “Wake-up from Power-down mode”: After wake-up, reprogram the clock

source for the main clocks.

• Pin description tables for RESET/PIO0_0 updated: In deep power-down mode, this pin

must be pulled HIGH externally. The RESET pin can be left unconnected or be used as

a GPIO pin if an external RESET function is not needed. See Chapter 8

“LPC1 1U3x/2x/1x Pin configuration”.

• Pin description notes relating to open-drain I2C-bus pins updated for clarity. Chapter 8

“LPC1 1U3x/2x/1x Pin configuration”.

• Pin description of the WAKEUP pin updated for clarity. Chapter 8 “LPC11U3x/2x/1x Pin

configuration”.

5.1 20131220 Modifications:

• Reset value of the SYSAHBCLKCTRL register corrected. See Table 5.

• Reserved function added to IOCON pin configuration registers PIO0_8 and PIO0_9.

See Table 69 and Table 70.

• Changed title to “LPC11U3x/2x/1x User manual”.

5 20131120 Modifications:

• Table 121 “GPIO pins available” corrected.

• Table 343 “ISP entry pins for different boot loader versions” added.

• Bit description of the SLEEPDEEP bit corrected in Table 53 “Power control register

(PCON, address 0x4003 8000) bit description”.

• Part LPC11U37HFBD64/401 added.

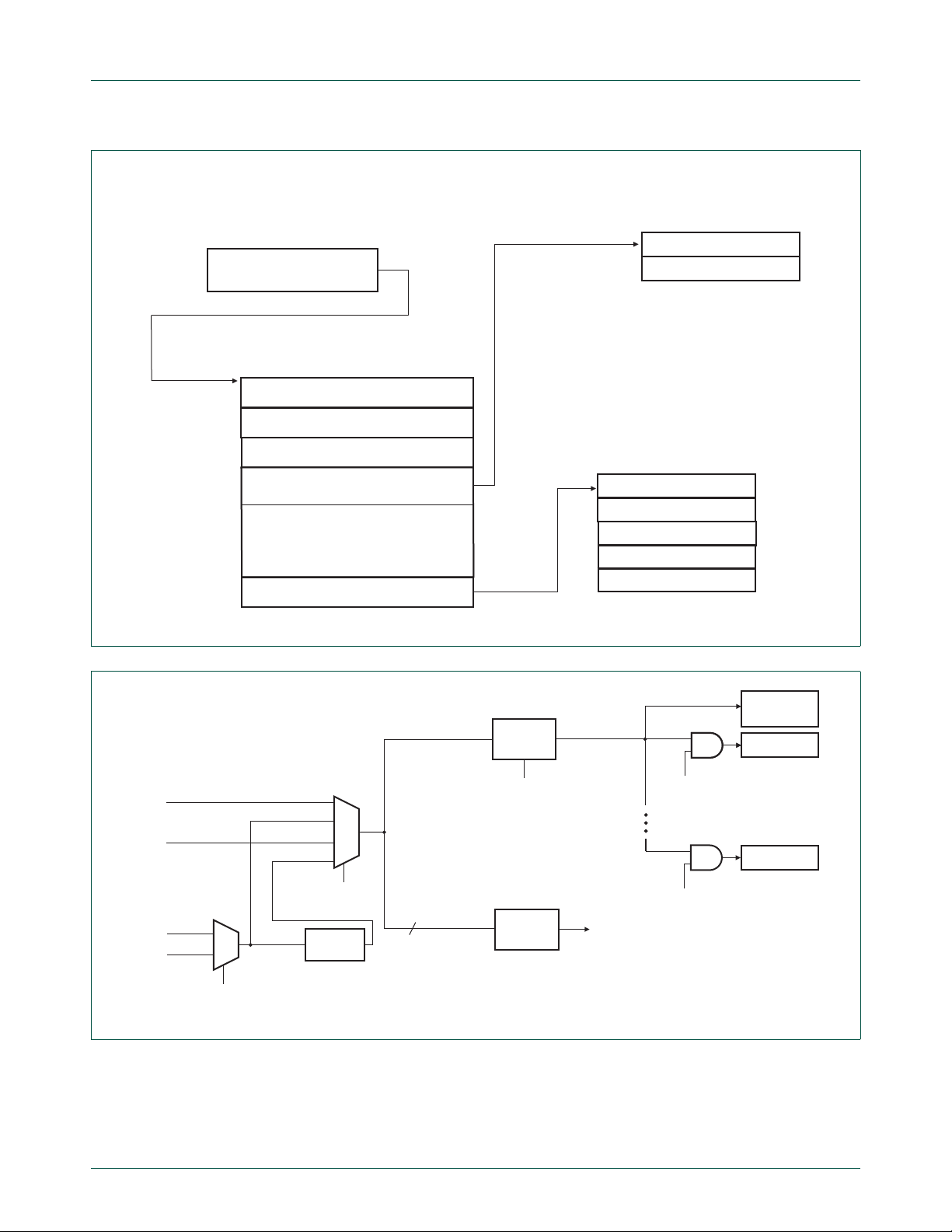

• API pointer structure updated in Figure 73, Figure 10, and Figure 19.

• Power Profiles API pointer definitions corrected. See Section 5.4.

• Chapter 23 “LPC11U3x/2x/1x I/O Handler” added.

UM10462 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2016. All rights reserved.

User manual Rev. 5.5 — 21 December 2016 3 of 523

Page 4

NXP Semiconductors

Revision history …continued

Rev Date Description

4.1 20130719 Modifications:

• Description of the NMISRC register updated. See Section 3.5.32 “NMI source selection

register”.

• Bootloader description clarified. See Section 20.2.

• Code listings corrected in Chapter 10.

• Table 346 “LPC11U3x flash sectors and pages” corrected for LPC11U35 parts.

• Editorial updates in Section 20.14 “IAP commands”.

• Steps to enter Deep-sleep mode and Power-down mode updated in Section 3.9.4.2

“Programming Deep-sleep mode” and Section 3.9.5.2 “Programming Power-down

mode”: Main clock must be switched to IRC before entering either mode.

• Minimum USB AHB clock changed to 6 MHz. See Section 11.4.7.

• Description of ISP GO command expanded. See Section 20.13.8.

4 20121119 Modifications:

• Removed remark “USB ISP commands are supported for the Windows operating

system only.”. USP ISP commands are supported in Windows, Linux, and Mac OS.

• Remove the following step to execute before entering Deep power-down: Enable the

IRC. This step is not longer required. See Section 3.9.6 “Deep power-down mode”.

• Register offset of the CR1 register corrected in timers CT16B0 and CT32B0. See

Table 293 and Table 314.

• Bit position of the CAP1 interrupt flag corrected in the IR registers of timers CT16B0

and CT32B0. See T able 282 and Table 303.

• Bit positions of the CAP1 edge and interrupt control bits corrected in the CCR registers

of timers CT16B0 and CT32B0. See Table 290 and Table 311.

• Bit values of the CAP1 counter mode and capture input select bits corrected in the

CTCR registers of timers CT16B0 and CT32B0. See Table 297 and Table 319.

• Remove instruction breakpoints from feature list for SWD. See Section 21.2.

• Explained use of interrupts with Power profiles in Section 5.3 “General description”.

• BOD interrupt level 0 removed. See Section 3.5.29 “BOD control register”.

• Polarity of the IOCON glitch filter FILTR bit changed: 0 = glitch filter on, 1 = glitch filter

off. See Table 60.

• Reset value of SYSCON registers updated and reset value after boot added. See

Table 5 “Register overview: system control block (base address 0x4004 8000)”.

3 20120716 Modifications:

• Parts LPC11U3x added.

• Editorial updates to Section 9.4.1 and Section 9.6.4.

• USB on-chip driver support for composite device added in Chapter 10.

UM10462

LPC11U3x/2x/1x User manual

Contact information

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: salesaddresses@nxp.com

UM10462 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2016. All rights reserved.

User manual Rev. 5.5 — 21 December 2016 4 of 523

Page 5

NXP Semiconductors

Revision history …continued

Rev Date Description

• Flash page erase command added for LPC11U3x parts in Chapter 20.

• FREQSEL bit values updated in Table 14 “Watchdog oscillator control register

(WDTOSCCTRL, address 0x4004 8024) bit description”.

• SRAM use by bootloader specified in Section 20.2.

• Description of interrupt use with IAP calls updated (see Section 20.8.7).

• Description of ISP Go command updated (only Thumb mode allowed) in Table 357.

• Update EEPROM write command. The top 64 bytes are reserved for the 4 kB EEPROM

only (see Section 20.14.11).

• Description of the BYPASS bit corrected in Table 13 “System oscillator control register

(SYSOSCCTRL, address 0x4004 8020) bit description”.

• Description of USB CDC device class updated in Table 186 “USBD_CDC_API class

structure” and Table 187 “USBD_CDC_INIT_PARAM class structure”.

• IRC suitable for USB clocking in low-speed mode (see Section 11.4.7 and

Section 3.5.12).

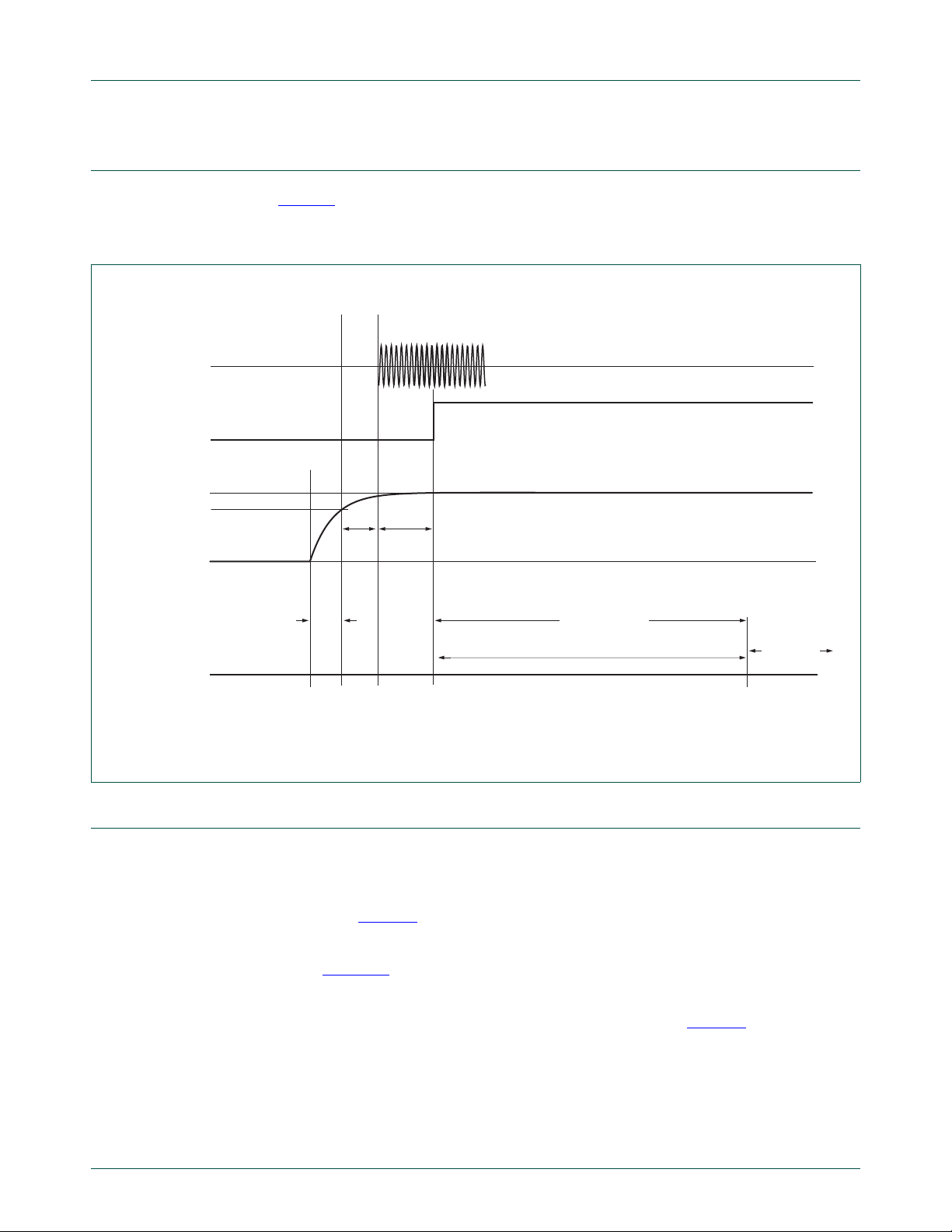

• Figure 8 “Start-up timing” updated (RESET changed to internal reset).

• Figure 66 corrected.

UM10462

Chapter :

2.1 20120113 Modifications:

• Description of PIOPOR1CAP register updated (see Table 34).

• LPM register added (Ta ble 201).

2 20111214 LPC1 1U3x/2x/1x User manual

Modifications:

• Parts LPC11U2x added.

• Chapter 22 added.

• Part LPC11U14FHI33/201 added.

Modifications:

• Parts LPC11U2x added.

• Chapter 22 added.

• Part LPC11U14FHI33/201 added.

• Bit 10 (TD) changed to reserved for PIO0_4 and PIO0_5 registers (Table 65, Table 66).

1 20110414 Initial version

UM10462 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2016. All rights reserved.

User manual Rev. 5.5 — 21 December 2016 5 of 523

Page 6

1.1 Introduction

UM10462

Chapter 1: LPC11U3x/2x/1x Introductory information

Rev. 5.5 — 21 December 2016 User manual

The LPC11U3x/2x/1x are an ARM Cortex-M0 based, low-cost 32-bit MCU family,

designed for 8/16-bit microcontroller applications, of fering performance, low power , simple

instruction set and memory5 addressing together with reduced code size compared to

existing 8/16-bit architectures.

The LPC11U3x/2x/1x operate at CPU frequencies of up to 50 MHz. Equipped with a

highly flexible and configurable full-speed USB 2.0 device controller, the LPC1 1U3x/2x/1x

bring unparalleled design flexibility and seamless integration to today's demanding

connectivity solutions.

1.2 Features

The peripheral complement of the LPC11U3x/2x/1x includes up to 32 kB of flash memory,

up to 8 kB of SRAM data memory, one Fast-mode Plus I

RS-485/EIA-485 USART with support for synchronous mode and smart card interface,

two SSP interfaces, four general purpose counter/timers, a 10-bit ADC, and up to 54

general purpose I/O pins.

The I/O Handler is a software library-supported hardware engine that can be used to add

performance, connectivity and flexibility to system designs. It is available on the

LPC11U37HFBD64/401. The I/O Handler can emulate serial interfaces such as UART,

I2C, and I2S with no or very low additional CPU load and can off-load the CPU by

performing processing-intensive functions like DMA transfers in hardware. Software

libraries for multiple I/O handler applications are available on http://www.LPCware.com

See Section 25.2 “References”

parts.

for additional documentation related to the LPC11Uxx

2

C-bus interface, one

.

• System:

– ARM Cortex-M0 processor, running at frequencies of up to 50 MHz.

– ARM Cortex -M 0 bu ilt- in Ne ste d Vectored Interrupt Controller (NVIC).

– Non Maskable Interrupt (NMI) input selectable from several input sources.

– System tick timer.

• Memory:

– Up to 32 kB on-chip flash program memory.

– LPC11U3x only: Up to 128 kB on-chip flash program memory with sector (4 kB)

and page erase (256 byte) access.

– In-System Programming (ISP) and In-Application Programming (IAP) via on-chip

bootloader software.

– Total SRAM

LPC1 1U1x: up to 6 kB (4 kB main SRAM and 2 kB USB SRAM).

LPC11U2x: up to 10 kB (8 kB main SRAM and 2 kB USB SRAM).

UM10462 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2016. All rights reserved.

User manual Rev. 5.5 — 21 December 2016 6 of 523

Page 7

NXP Semiconductors

• ROM based drivers:

• Debug options:

• Digital peripherals:

• Analog peripherals:

• I/O Handler for hardware emulation of serial interfaces, DMA, and other functionality;

• Serial interfaces:

• Clock generation:

UM10462

Chapter 1: LPC1 1U3x/2x/1x Introductory information

LPC11U3x: up to 12 kB (8 kB main SRAM0, 2 kB SRAM1, 2 kB USB SRAM).

– 16 kB boot ROM.

– LPC11U2x/3x only: Up to 4 kB on-chip EEPROM data memory; byte erasable and

byte programmable; on-chip API supp ort.

– Power profiles.

– 32-bit integer division routines.

– LPC11U2x/3x only: ROM-based USB drivers. Flash updates via USB supported.

Supports Human-Interface Device (HID) class, Mass S torage Device Class (MSC),

and Communication Device Class (CDC).

– LPC11U2x/3x only: IAP EEPROM drivers.

– Standard JTAG test interface for BSDL.

– Serial Wire Debug.

– Up to 54 General Purpose I/O (GPIO) pins with configurable pull-up/pull-down

resistors, repeater mode, and open-drain mode.

– Up to eight GPIO pins can be selected as edge and level sensitive interrupt

sources.

– Two GPIO grouped interrupt modules enables an interrupt based on a

programmable pattern of input states of a group of GPIO pins.

– High-current source output driver (20 mA) on one pin (P0_7).

– High-current sink driver (20 mA) on true open-drain pins (P0_4 and P0_5).

– Four general purpose counter/timers with a total of 8 capture inputs and 13 match

outputs.

– Programmable windowed WatchDog Timer (WDT) with a dedicated, internal

low-power WatchDog Oscillator (WDO).

– 10-bit ADC with input multiplexing among eight pins.

supported through software libraries. (LPC11U37HFBD64/401 only.)

– USB 2.0 full-speed device controller.

– USART with fractional baud rate generation, internal FIFO, a full modem control

handshake interface, and support for RS-485/9-bit mode and synchron ous mode.

USART supports an asynchronous smart card interface (ISO 7816-3).

– Two SSP interfaces with FIFO and multi-protocol capabilities.

2

C-bus interface supporting the full I2C-bus specification and Fast-mode Plus with

– I

a data rate of up to 1 Mbit/s with multiple address recognition and monitor mode.

– Crystal Oscillator with an operating range of 1 MHz to 25 MHz (system oscillator).

UM10462 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2016. All rights reserved.

User manual Rev. 5.5 — 21 December 2016 7 of 523

Page 8

NXP Semiconductors

• Power control:

• Unique device serial number for identification.

• Single 3.3 V power supply (1.8 V to 3.6 V).

• Temperature range 40 C to +85 C.

• Available as LQFP64, LQFP48, TFBGA48 packages, and as HVQFN33 in two

• Pin-compatible to the ARM Cortex-M3 based LPC134x series.

UM10462

Chapter 1: LPC1 1U3x/2x/1x Introductory information

– 12 MHz Internal high-frequency RC oscillator (IRC) that can optionally be used as

a system clock.

– Internal low-power, low-frequency WatchDog Oscillator (WDO) with programmable

frequency output.

– PLL allows CPU operation up to the maximum CPU rate with the system oscillator

or the IRC as clock sources.

– A second, dedicated PLL is provided for USB.

– Clock output function with divider that can reflect the crystal oscillator, the main

clock, the IRC, or the watchdog oscillator.

– Four reduced power modes: Sleep, Deep-sleep, Power-down, and Deep

power-down.

– Power profiles residing in boot ROM allow optimized performance and minimized

power consumption for any given application through one simple function call.

– Processor wake-up from Deep-sleep and Power-down modes via reset, select able

GPIO pins, watchdog interrupt, BOD interrupt, or USB port activity.

– Processor wake-up from Deep power-down mode using one special function pin.

– Integrated PMU (Power Management Unit) to minimize power consumption dur ing

Sleep, Deep-sleep, Power-down, and Deep power-down modes.

– Power-On Reset (POR).

– Brownout detect with four separate thresholds for interrupt and forced reset.

package sizes: 5 x 5 x 0.85 mm and 7 x 7 x 0.85 mm.

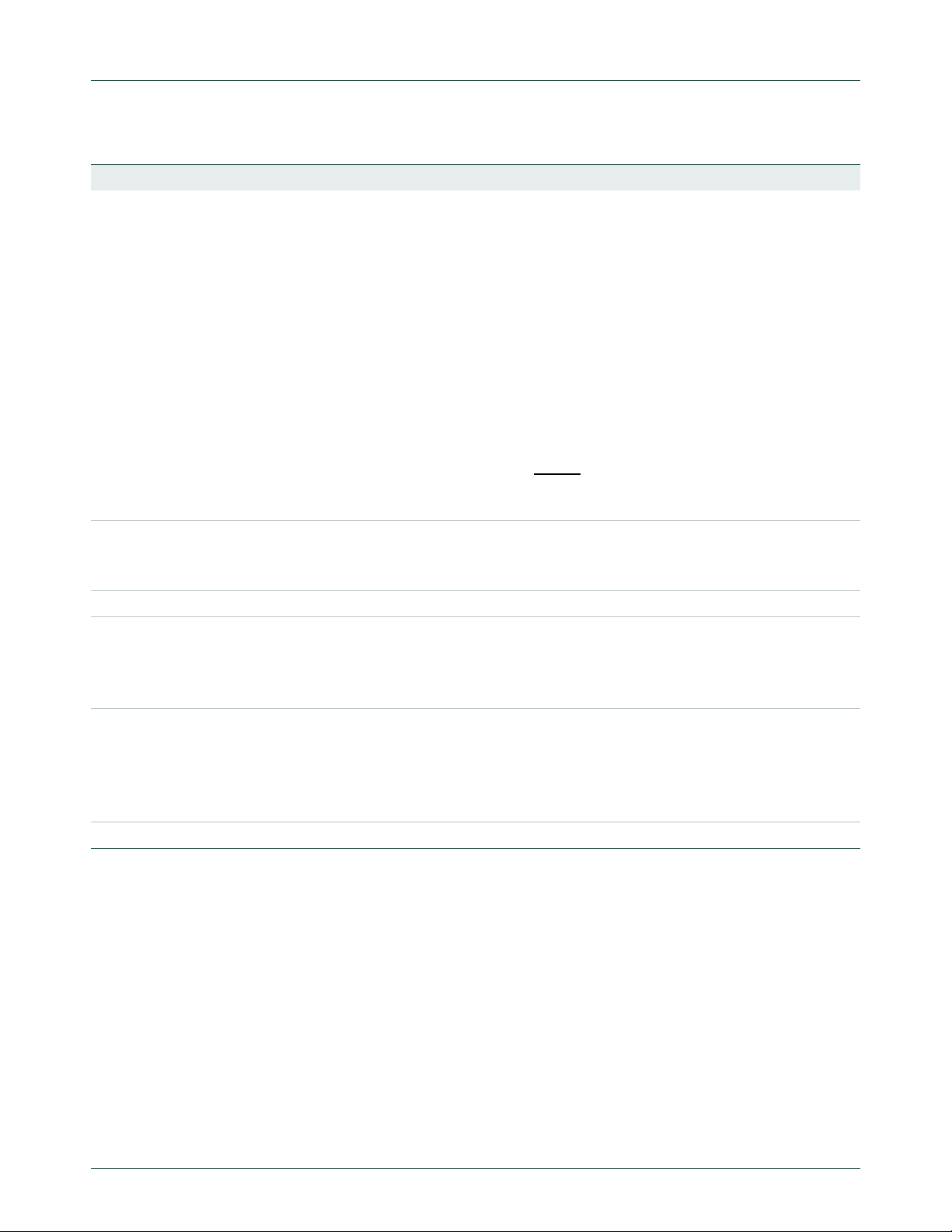

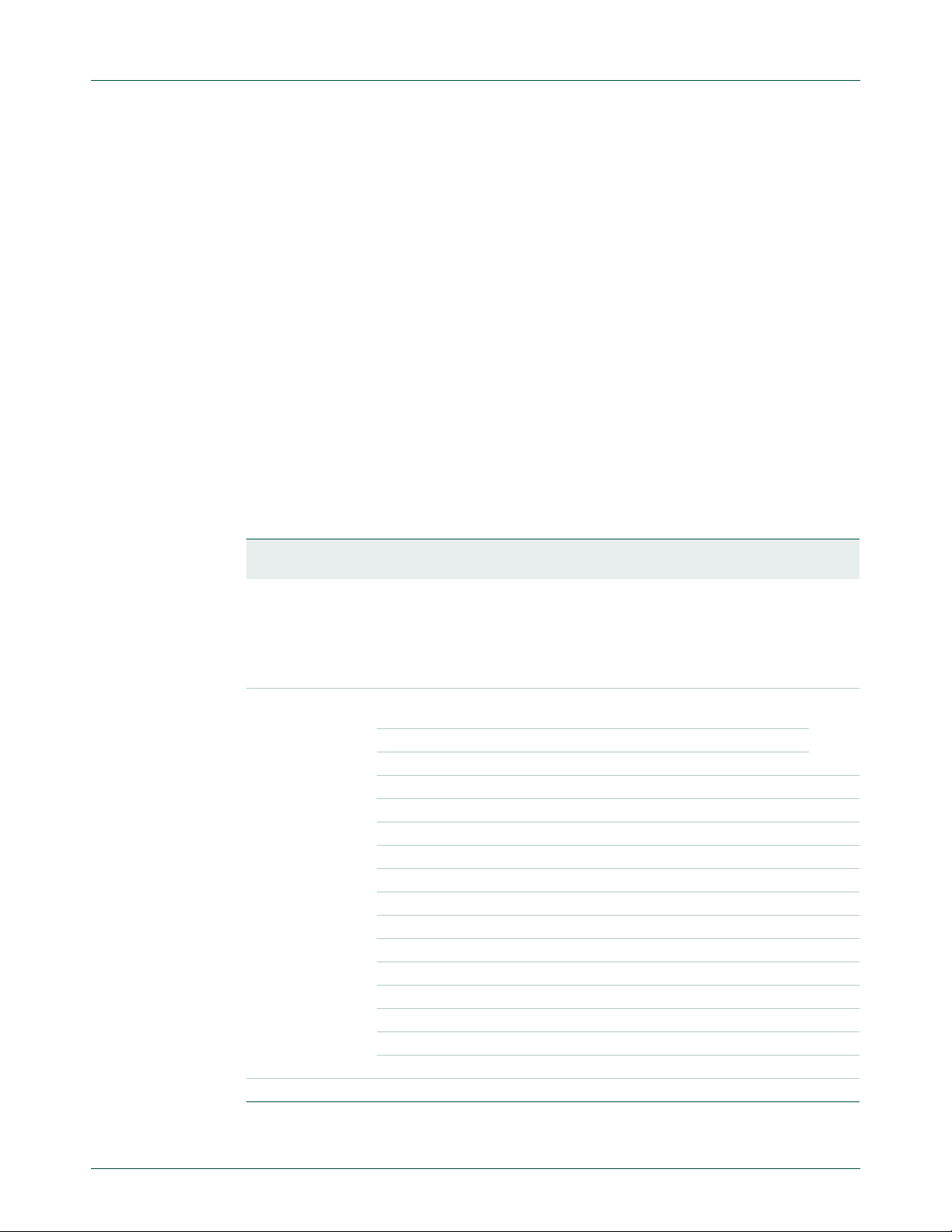

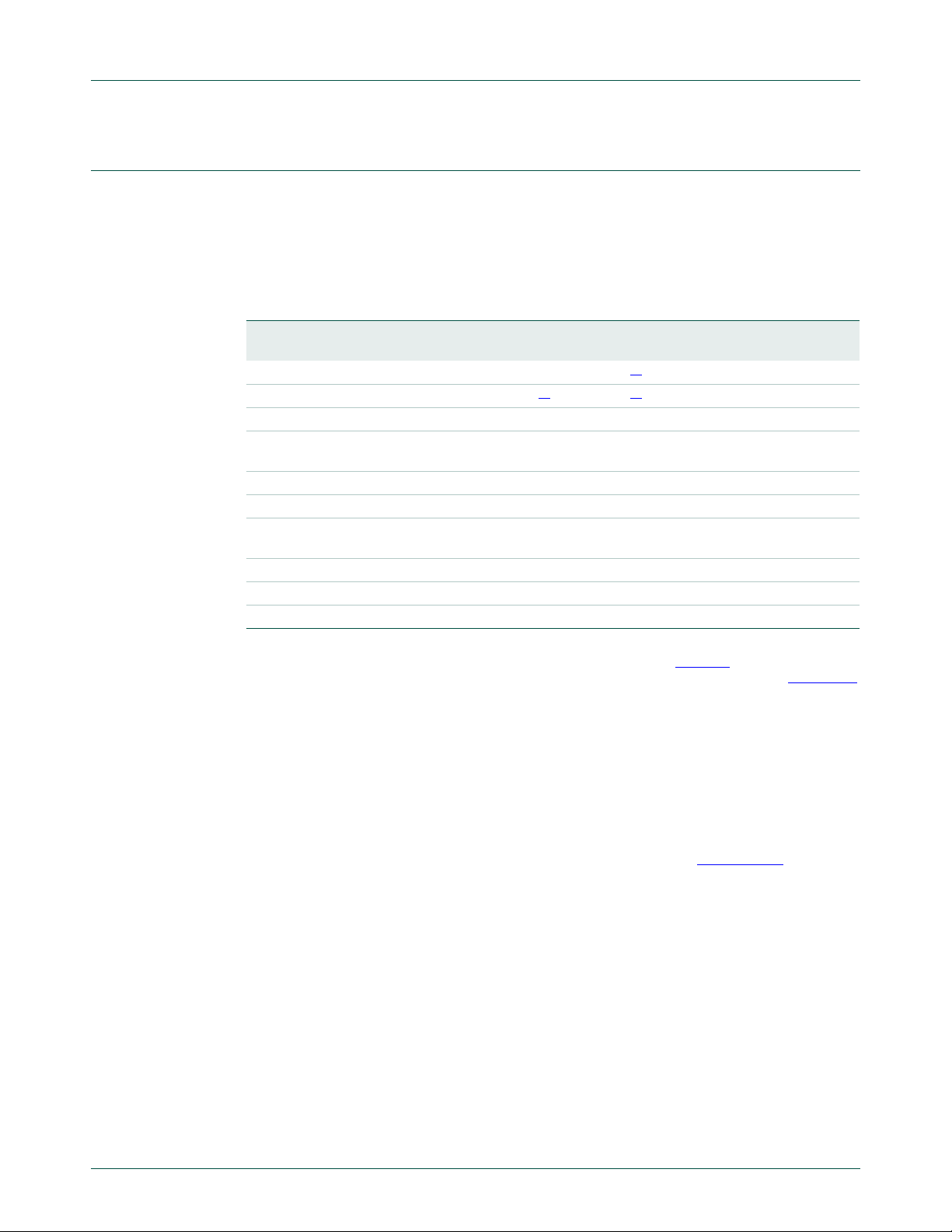

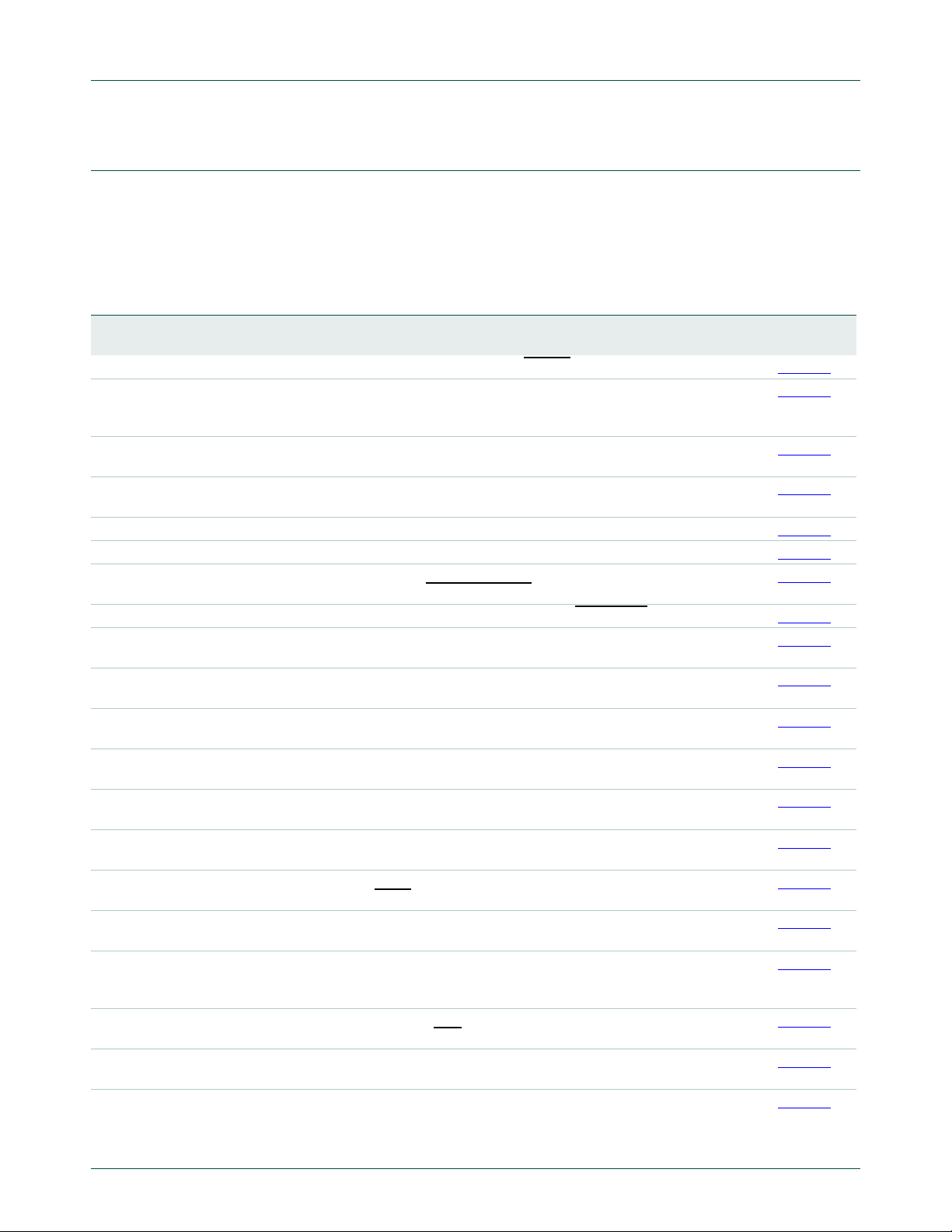

1.3 Ordering information

Table 1. Ordering information

Type number Package

LPC11U12FHN33/201 HVQFN33 plastic thermal enhanced very thin quad flat package; no leads; 33

LPC11U12FBD48/201 LQFP48 plastic low profile quad flat package; 48 leads; body 7 7 1.4 mm SOT313-2

LPC11U13FBD48/201 LQFP48 plastic low profile quad flat package; 48 leads; body 7 7 1.4 mm SOT313-2

LPC11U14FHN33/201 HVQFN33 plastic thermal enhanced very thin quad flat package; no leads; 33

LPC11U14FHI33/201 HVQFN33 HVQFN: plastic thermal enhanced very thin quad flat package; no

LPC11U14FBD48/201 LQFP48 plastic low profile quad flat package; 48 leads; body 7 7 1.4 mm SOT313-2

LPC11U14FET48/201 TFBGA48 plastic thin fine-pitch ball grid array package; 48 balls; body 4.5 4.5

UM10462 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2016. All rights reserved.

User manual Rev. 5.5 — 21 December 2016 8 of 523

Name Description Version

n/a

terminals; body 7 7 0.85 mm

n/a

terminals; body 7 7 0.85 mm

n/a

leads; 33 terminals; body 5 5 0.85 mm

SOT1155-2

0.7 mm

Page 9

NXP Semiconductors

UM10462

Chapter 1: LPC1 1U3x/2x/1x Introductory information

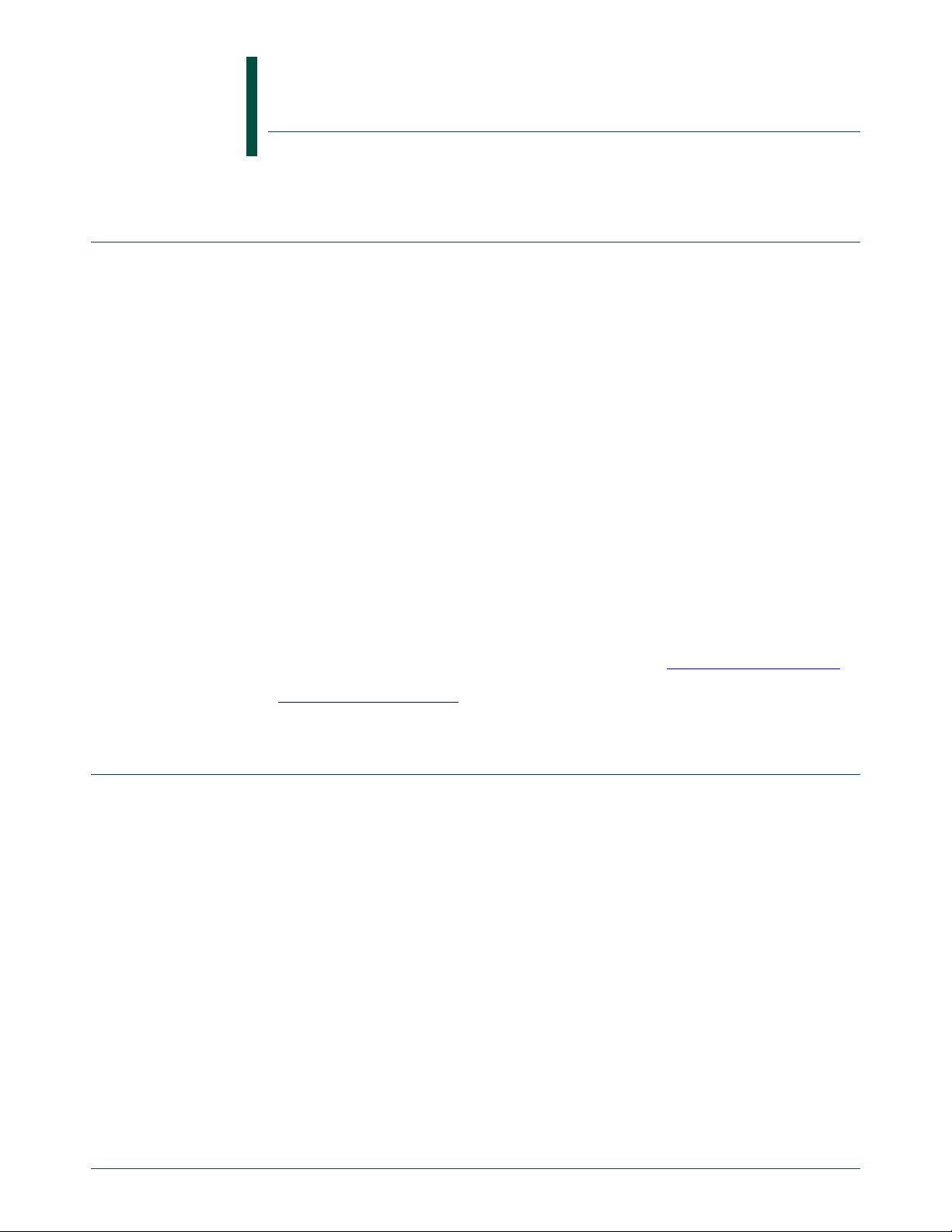

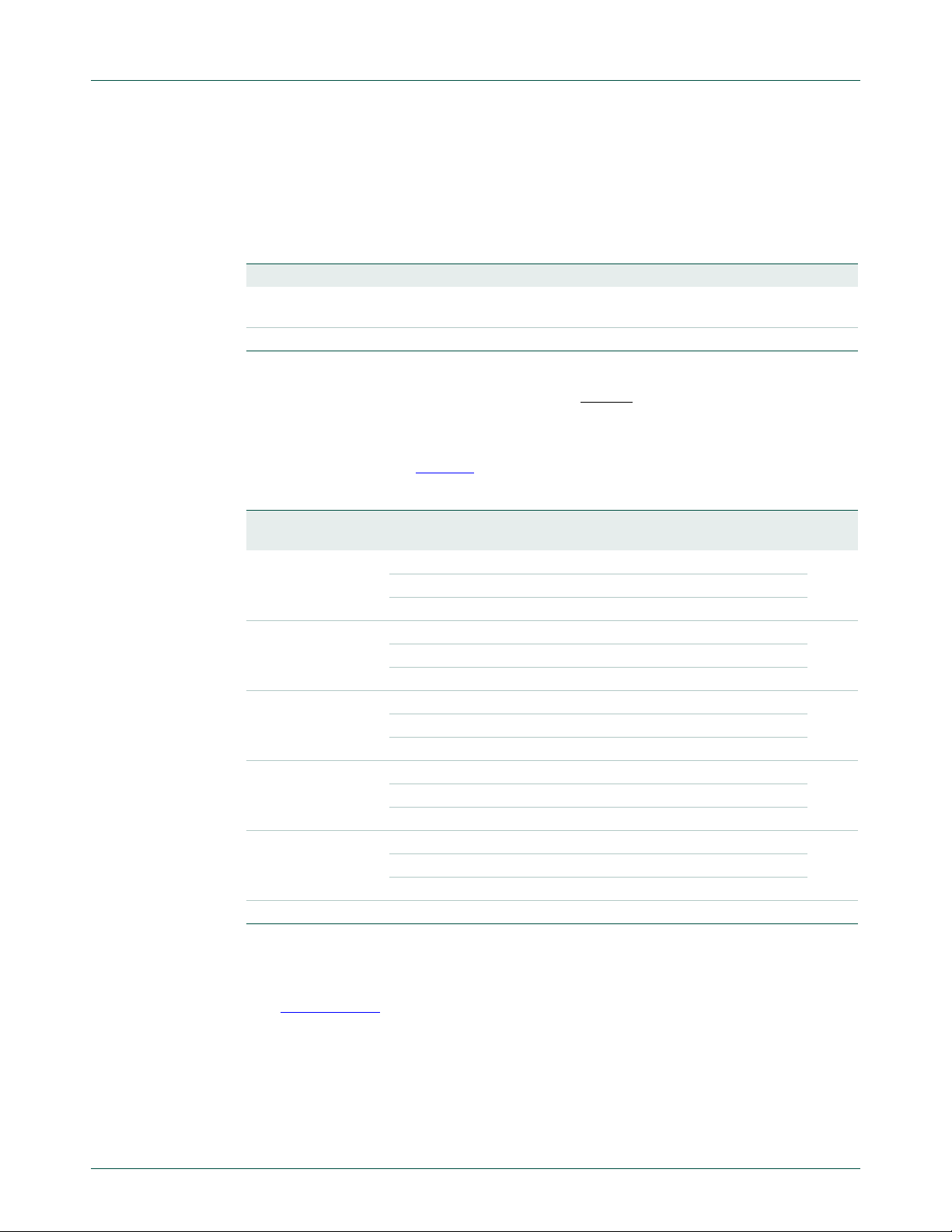

Table 1. Ordering information

Type number Package

Name Description Version

LPC11U22FBD48/301 LQFP48 plastic low profile quad flat package; 48 leads; body 7 7 1.4 mm SOT313-2

LPC11U23FBD48/301 LQFP48 plastic low profile quad flat package; 48 leads; body 7 7 1.4 mm SOT313-2

LPC11U24FHI33/301 HVQFN33 plastic thermal enhanced very thin quad flat package; no leads; 33

LPC11U24FBD48/301 LQFP48 plastic low profile quad flat package; 48 leads; body 7 7 1.4 mm SOT313-2

LPC11U24FET48/301 LQFP48 plastic low profile quad flat package; 48 leads; body 7 7 1.4 mm SOT313-2

LPC11U24FHN33/401 HVQFN33 plastic thermal enhanced very thin quad flat package; no leads; 33

LPC11U24FBD48/401 LQFP48 plastic low profile quad flat package; 48 leads; body 7 7 1.4 mm SOT313-2

LPC11U24FBD64/401 LQFP64 plastic low profile quad flat package; 64 leads; body 10 10 1.4 mm SOT314-2

LPC11U34FHN33/311 HVQFN33 plastic thermal enhanced very thin quad flat package; no leads; 33

LPC11U34FBD48/311 LQFP48 plastic low profile quad flat package; 48 leads; body 7 7 1.4 mm SOT313-2

LPC11U34FHN33/421 HVQFN33 plastic thermal enhanced very thin quad flat package; no leads; 33

LPC11U34FBD48/421 LQFP48 plastic low profile quad flat package; 48 leads; body 7 7 1.4 mm SOT313-2

LPC11U35FHN33/401 HVQFN33 plastic thermal enhanced very thin quad flat package; no leads; 33

LPC11U35FBD48/401 LQFP48 plastic low profile quad flat package; 48 leads; body 7 7 1.4 mm SOT313-2

LPC11U35FBD64/401 LQFP64 plastic low profile quad flat package; 64 leads; body 10 10 1.4 mm SOT314-2

LPC11U35FHI33/501 HVQFN33 plastic thermal enhanced very thin quad flat package; no leads; 33

L

PC11U35FET48/501 TFBGA48 plastic thin fine-pitch ball grid array package; 48 balls; body 4.5 4.5

LPC11U36FBD48/401 LQFP48 plastic low profile quad flat package; 48 leads; body 7 7 1.4 mm SOT313-2

LPC11U36FBD64/401 LQFP64 plastic low profile quad flat package; 64 leads; body 10 10 1.4 mm SOT314-2

LPC11U37FBD48/401 LQFP48 plastic low profile quad flat package; 48 leads; body 7 7 1.4 mm SOT313-2

LPC11U37HFBD64/401 LQFP64 plastic low profile quad flat package; 64 leads; body 10 10 1.4 mm SOT314-2

LPC11U37FBD64/501 LQFP64 plastic low profile quad flat package; 64 leads; body 10 10 1.4 mm SOT314-2

…continued

terminals; body 5 5 0.85 mm

terminals; body 7 7 0.85 mm

terminals; body 7 7 0.85 mm

terminals; body 7 7 0.85 mm

terminals; body 7 7 0.85 mm

terminals; body 5 5 0.

0.7 mm

n/a

n/a

n/a

n/a

n/a

n/a

85 mm

SOT1155-2

Table 2. Part ordering options

Part Number FLASH

LPC11U12FHN33/201 16 4 - 2 6 N/A 1 1 2 8 26

LPC11U12FBD48/201 16 4 - 2 6 N/A 1 1 2 8 40

LPC11U13FBD48/201 24 4 - 2 6 N/A 1 1 2 8 40

LPC11U14FHI33/201 32 4 - 2 6 N/A 1 1 2 8 26

LPC11U14FHN33/201 32 4 - 2 6 N/A 1 1 2 8 26

LPC11U14FBD48/201 32 4 - 2 6 N/A 1 1 2 8 40

LPC11U14FET48/201 32 4 - 2 6 N/A 1 1 2 8 40

LPC11U22FBD48/301 16 6 - 2 8 1 1 1 2 8 40

UM10462 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2016. All rights reserved.

User manual Rev. 5.5 — 21 December 2016 9 of 523

(kB)

SRAM

(kB)

(Main

SRAM)

SRAM1

(kB)

USB

SRAM

(kB)

Total

genera

purpose

SRAM

EEPROM

(kB)

USB I2C/

Fast+

SSP ADC

Chan

nels

GPIO

Page 10

NXP Semiconductors

UM10462

Chapter 1: LPC1 1U3x/2x/1x Introductory information

(kB)

…continued

SRAM

(kB)

(Main

SRAM)

SRAM1

(kB)

[1]

USB

SRAM

(kB)

210 4 112854

Total

genera

purpose

SRAM

EEPROM

(kB)

USB I2C/

Fast+

SSP ADC

Chan

nels

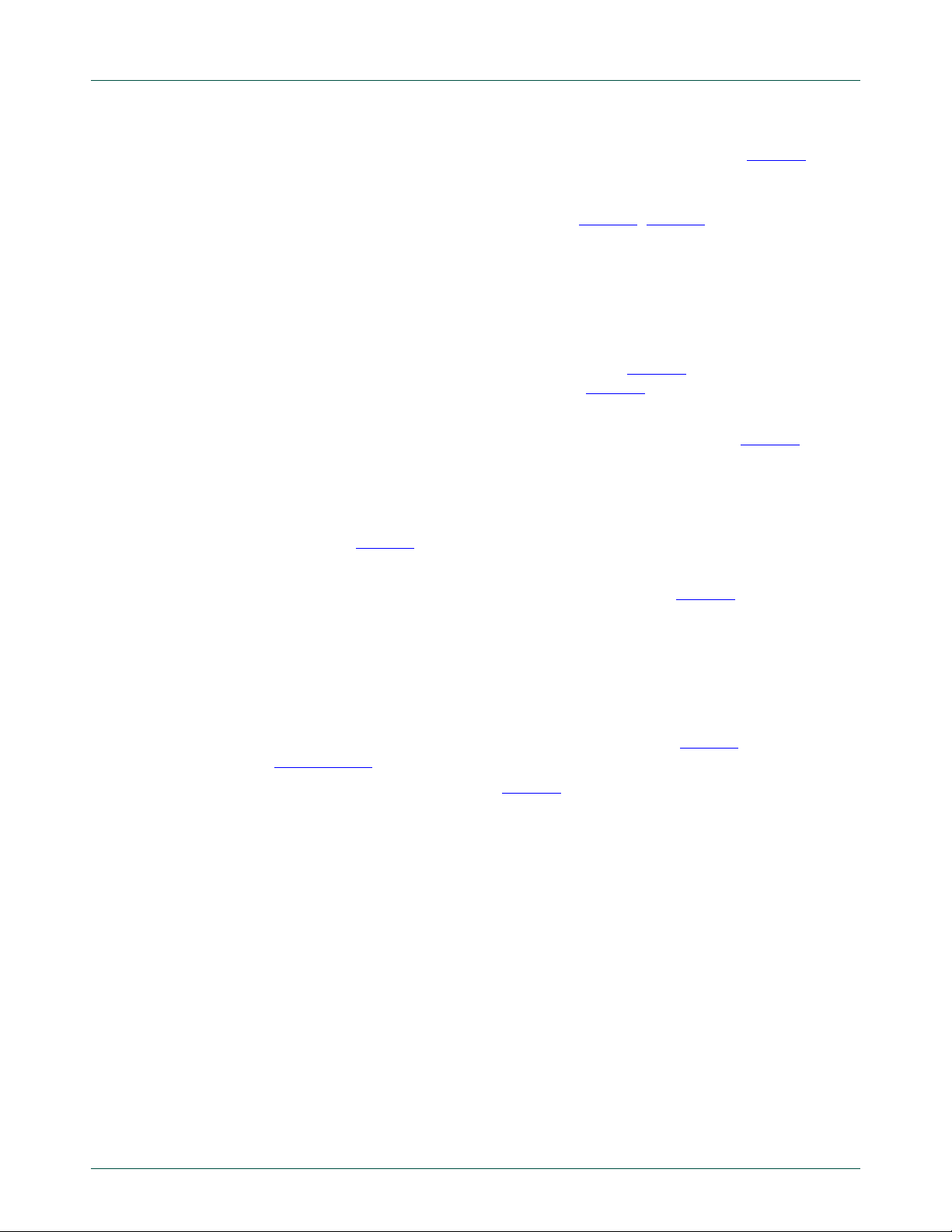

Table 2. Part ordering options

Part Number FLASH

LPC11U23FBD48/301 24 6 - 2 8 1 1 1 2 8 40

LPC11U24FHI33/301 32 6 - 2 8 2 1 1 2 8 26

LPC11U24FBD48/301 32 6 - 2 8 2 1 1 2 8 40

LPC11U24FET48/301 32 6 - 2 8 2 1 1 2 8 40

LPC11U24FHN33/401 32 8 - 2 10 4 1 1 2 8 26

LPC11U24FBD48/401 32 8 - 2 10 4 1 1 2 8 40

LPC11U24FBD64/401 32 8 - 2 10 4 1 1 2 8 54

LPC11U34FHN33/311 40 8 - - 8 4 1 1 2 8 26

LPC11U34FBD48/311 40 8 - - 8 4 1 1 2 8 40

LPC11U34FHN33/421 48 8 - 2 10 4 1 1 2 8 26

LPC11U34FBD48/421 48 8 - 2 10 4 1 1 2 8 40

LPC11U35FHN33/401 64 8 - 2 10 4 1 1 2 8 26

LPC11U35FBD48/401 64 8 - 2 10 4 1 1 2 8 40

LPC11U35FBD64/401 64 8 - 2 10 4 1 1 2 8 54

LPC11U35FHI33/501 64 8 2 2 12 4 1 1 2 8 26

LPC11U35FET48/501 64 8 2 2 12 4 1 1 2 8 40

LPC11U36FBD48/401 96 8 - 2 10 4 1 1 2 8 40

LPC11U36FBD64/401 96 8 - 2 10 4 1 1 2 8 54

LPC11U37FBD48/401 128 8 - 2 10 4 1 1 2 8 40

LPC11U37HFBD64/401 128 8 2

LPC11U37FBD64/501 128 8 2 2 12 4 1 1 2 8 54

GPIO

[1] 2 kB of SRAM1 available for I/O Handler library only.

UM10462 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2016. All rights reserved.

User manual Rev. 5.5 — 21 December 2016 10 of 523

Page 11

NXP Semiconductors

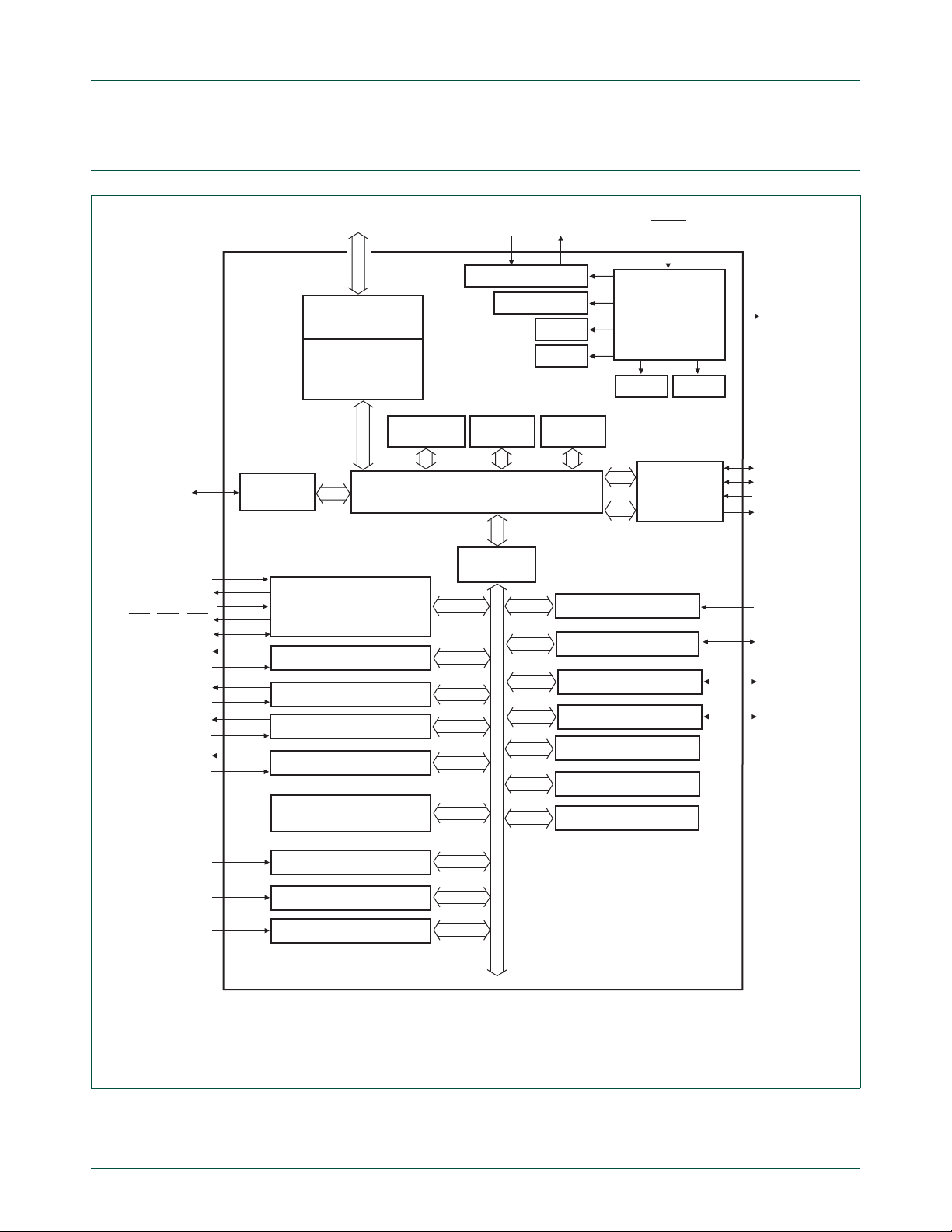

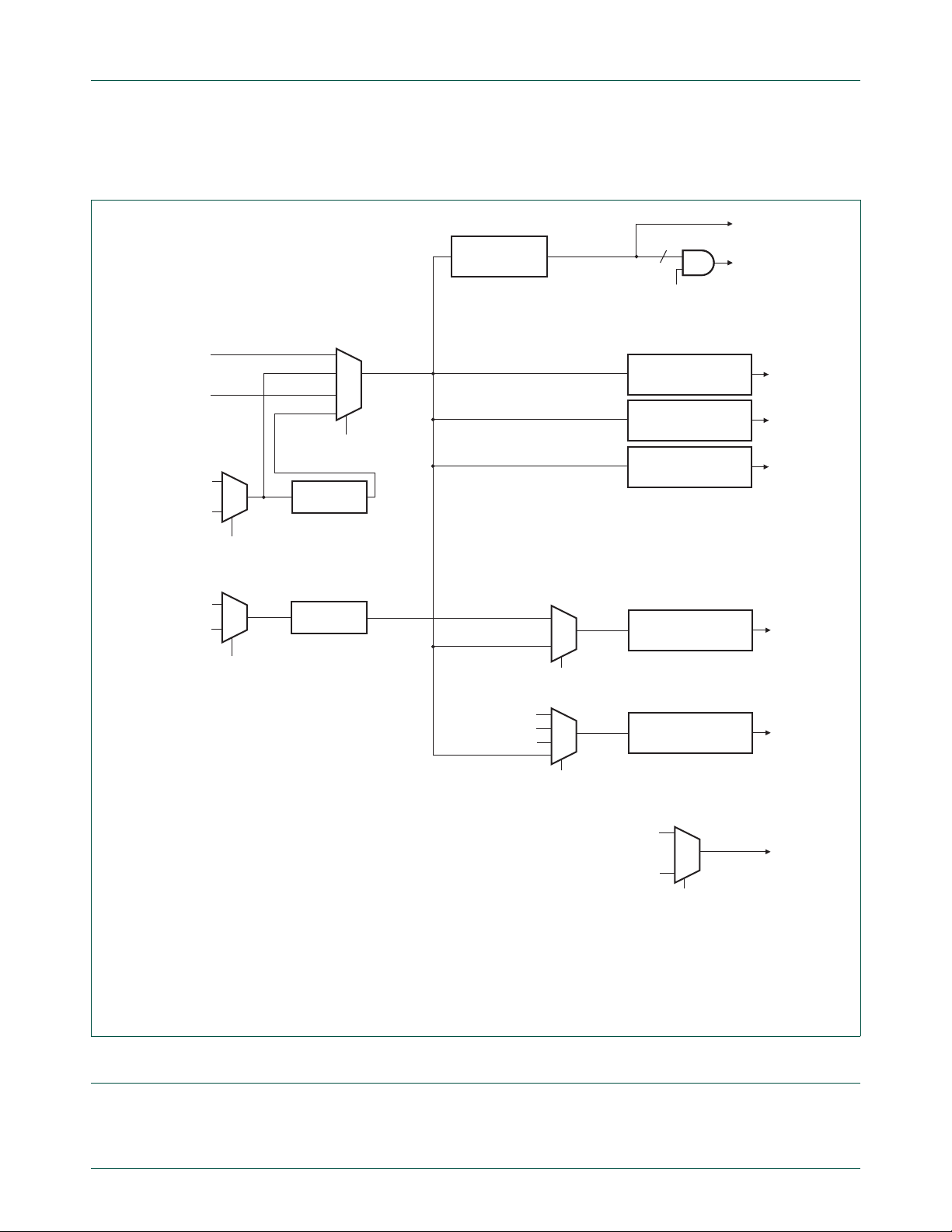

1.4 Block diagram

UM10462

Chapter 1: LPC1 1U3x/2x/1x Introductory information

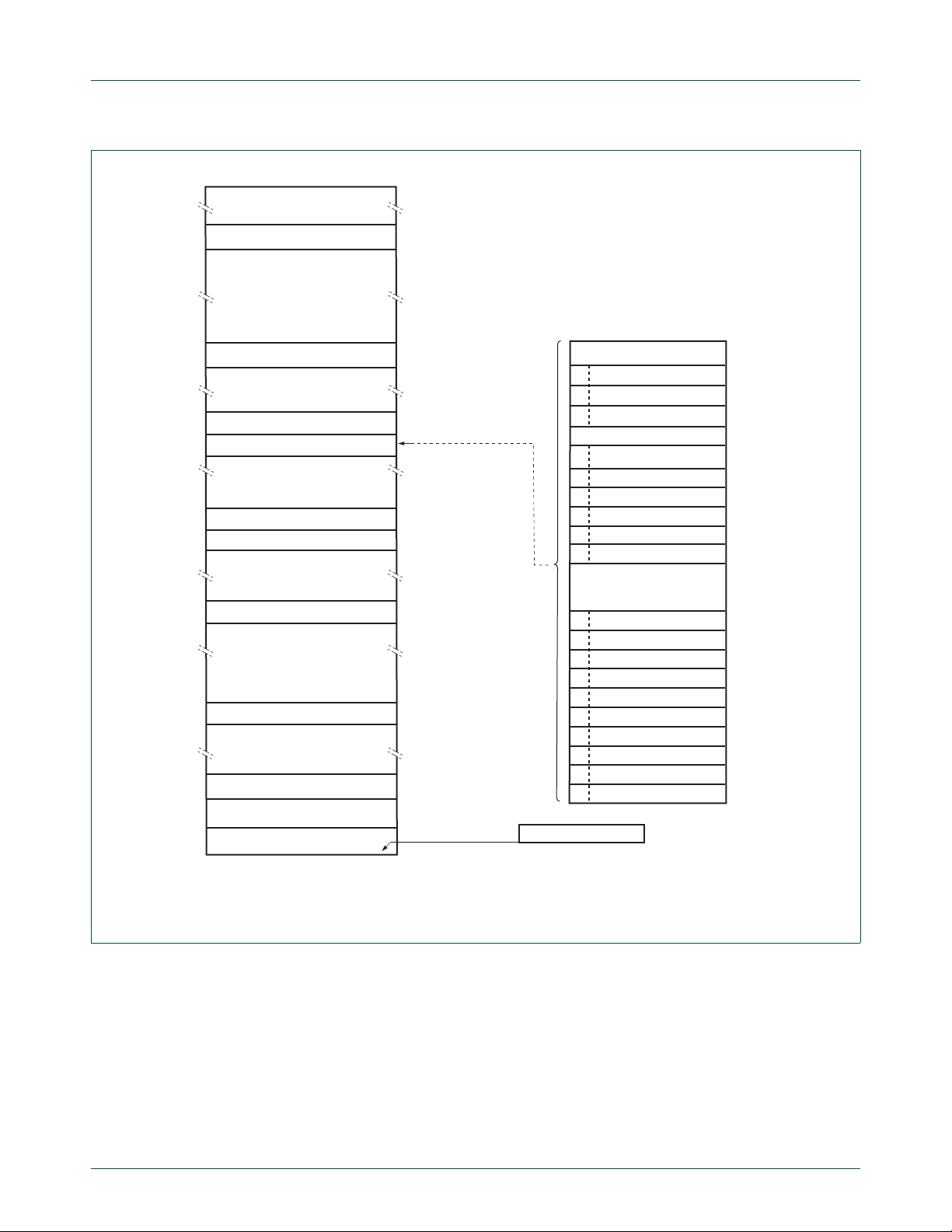

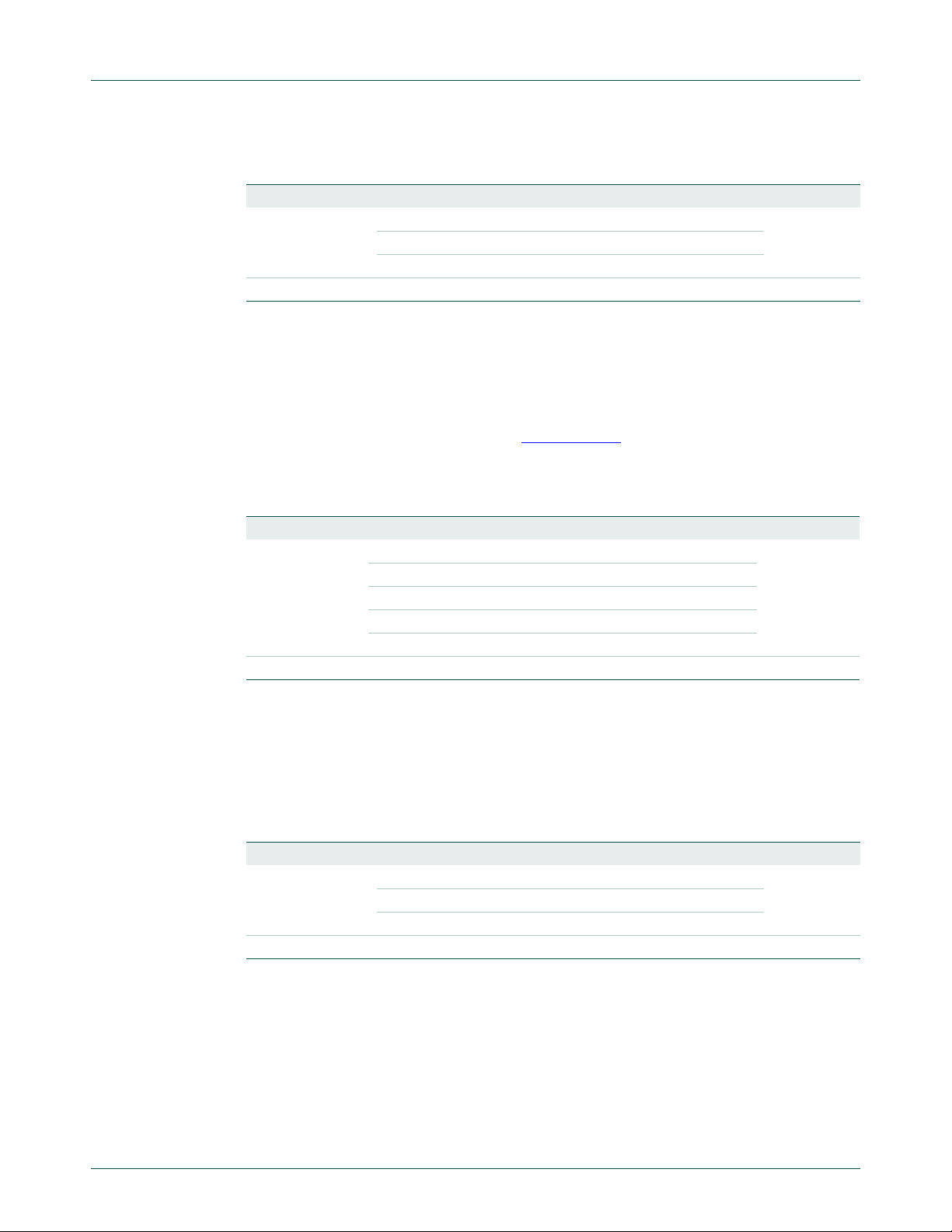

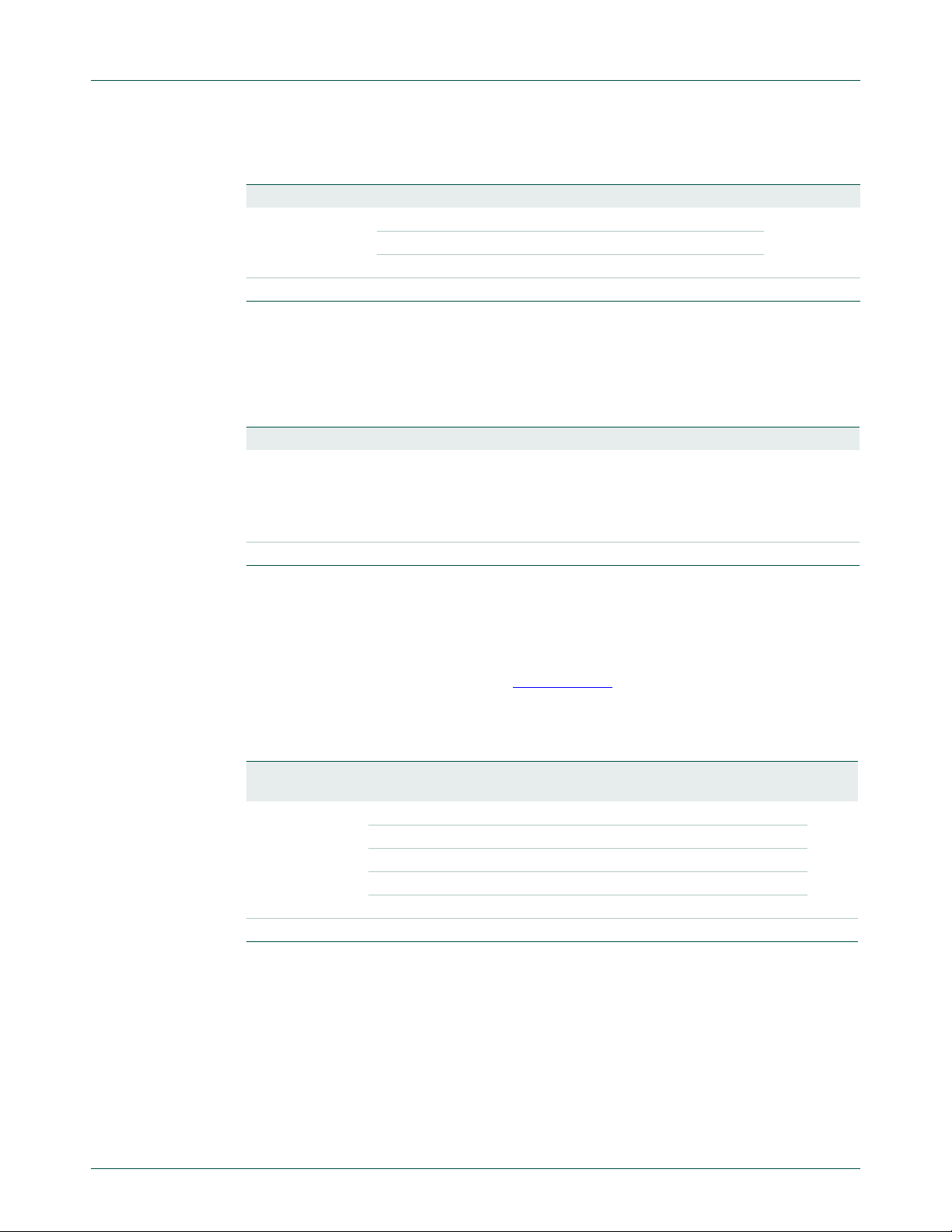

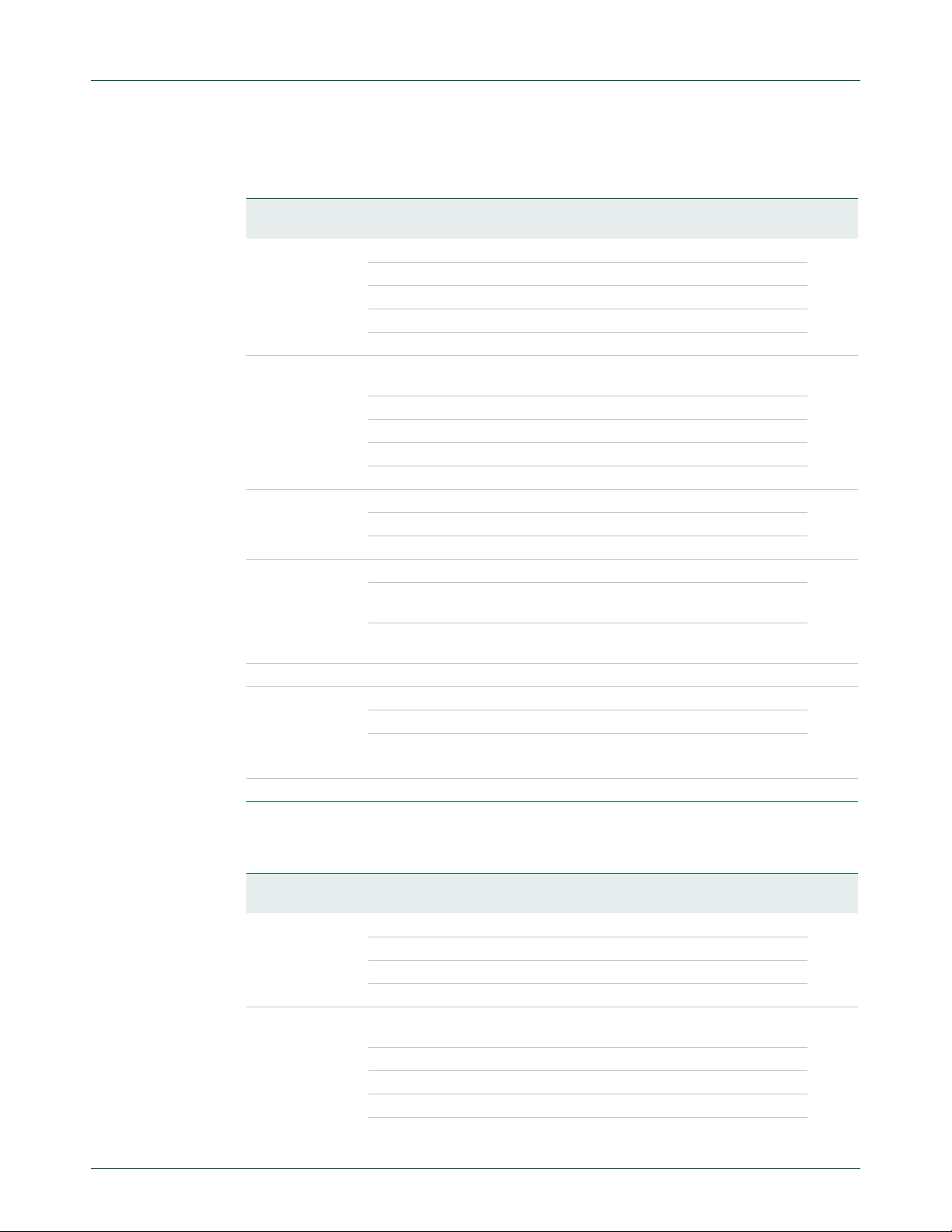

GPIO ports 0/1

RXD

TXD

DCD, DSR

CT16B0_MAT[2:0]

CT16B1_MAT[1:0]

CT32B0_MAT[3:0]

CT32B0_CAP[1:0]

CT32B1_MAT[3:0]

CT32B1_CAP[1:0]

(1)

CTS, RTS, DTR

CT16B0_CAP0

CT16B1_CAP0

, RI

SCLK

LPC11U12/13/14

HIGH-SPEED

(1)

(1)

(2)

SWD, JTAG

TEST/DEBUG

INTERFACE

ARM

CORTEX-M0

system bus

slave

GPIO

USART/

SMARTCARD INTERFACE

16-bit COUNTER/TIMER 0

16-bit COUNTER/TIMER 1

32-bit COUNTER/TIMER 0

32-bit COUNTER/TIMER 1

WINDOWED WATCHDOG

TIMER

SYSTEM OSCILLATOR

FLASH

16/24/32 kB

slave slave

AHB-LITE BUS

slave

AHB TO APB

BRIDGE

XTALIN XTALOUT

IRC, WDO

BOD

POR

SRAM

6 kB

ROM

16 kB

slave

RESET

CLOCK

GENERATION,

POWER CONTROL,

SYSTEM

FUNCTIONS

PLL0 USB PLL

master

USB DEVICE

slave

CONTROLLER

10-bit ADC

I2C-BUS

SSP0

SSP1

IOCON

SYSTEM CONTROL

PMU

CLKOUT

USB_DP

USB_DM

USB_VBUS

USB_FTOGGLE,

USB_CONNECT

AD[7:0]

SCL, SDA

SCK0, SSEL0,

MISO0, MOSI0

SCK1, SSEL1,

MISO1, MOSI1

GPIO pins

GPIO pins

GPIO pins

GPIO PIN INTERRUPTS

GPIO GROUP0 INTERRUPT

GPIO GROUP1 INTERRUPT

002aaf885

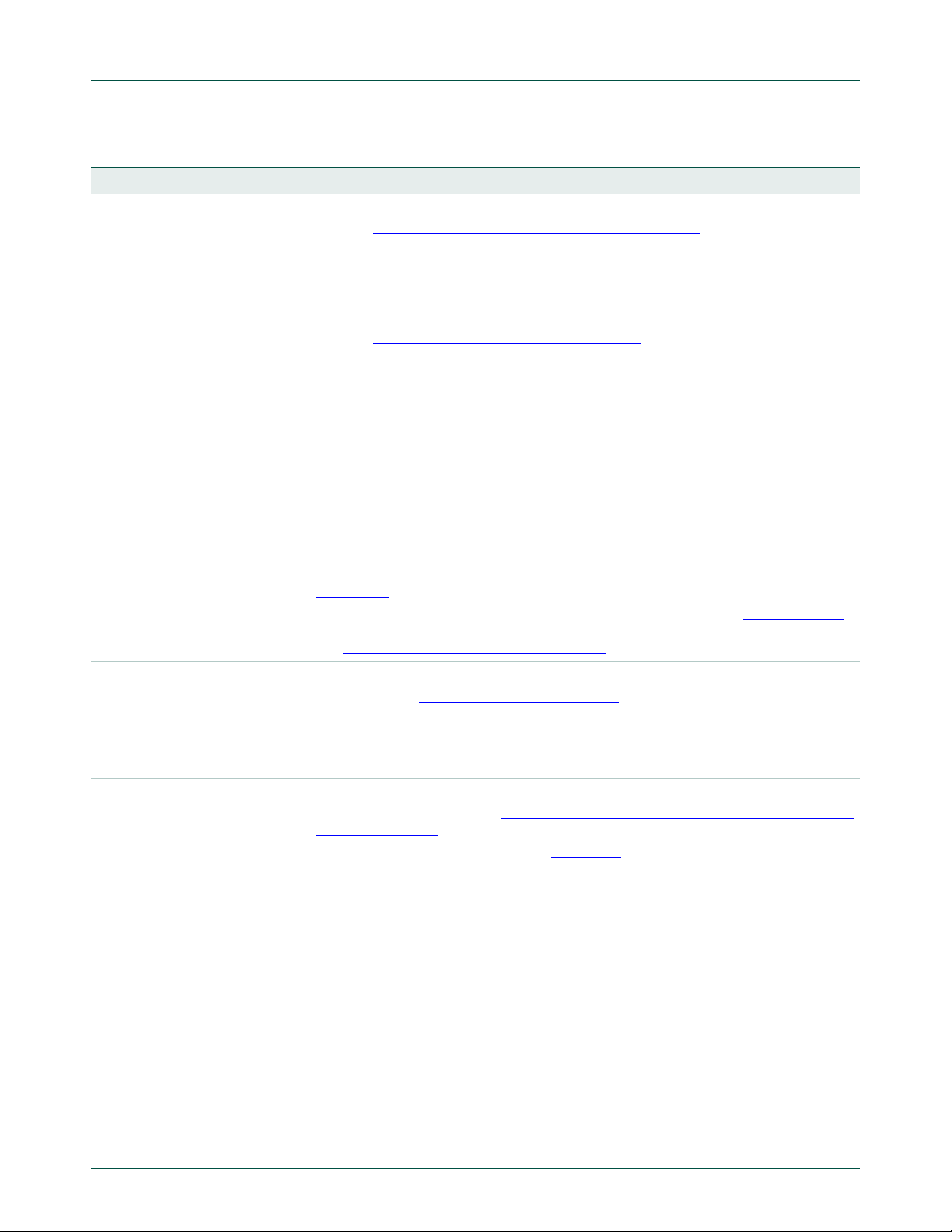

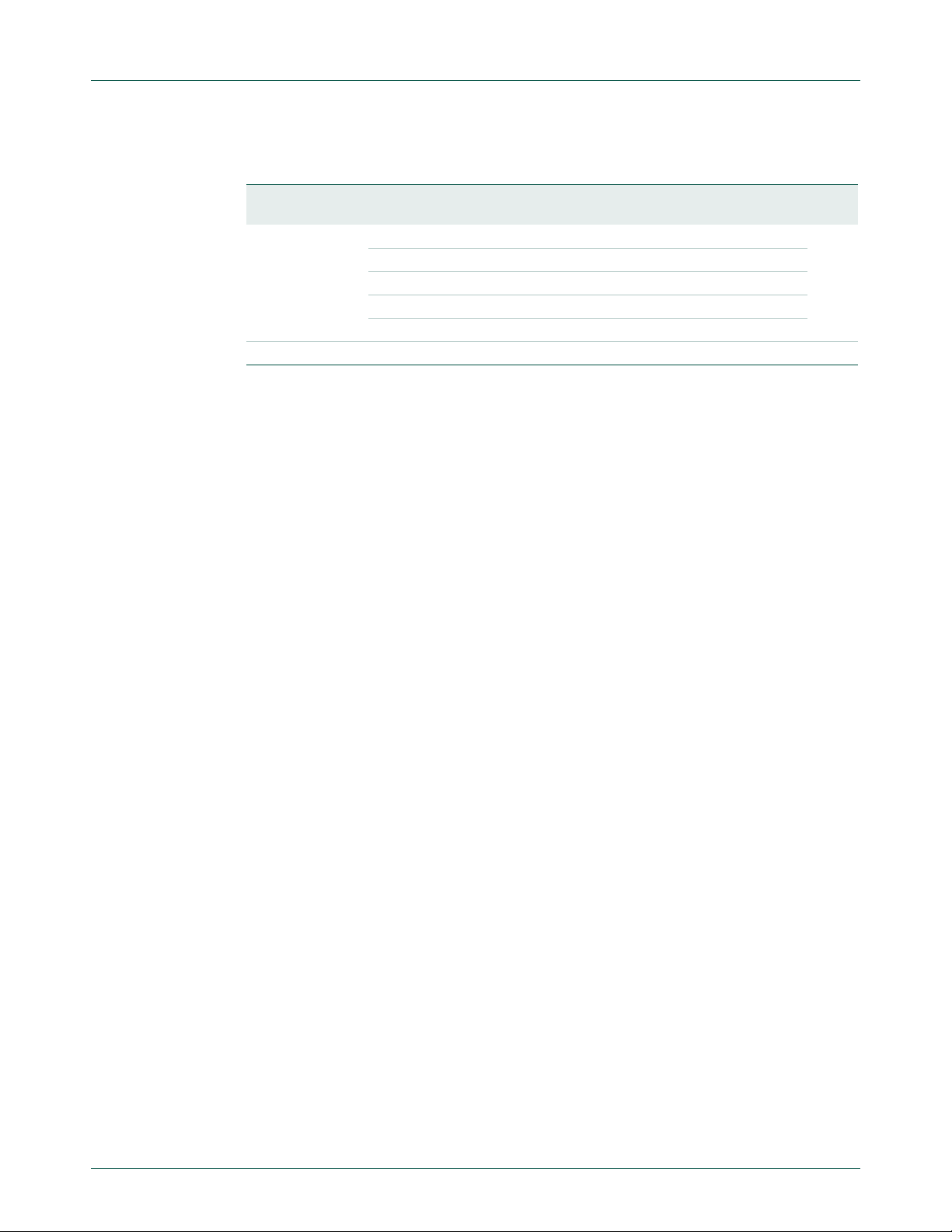

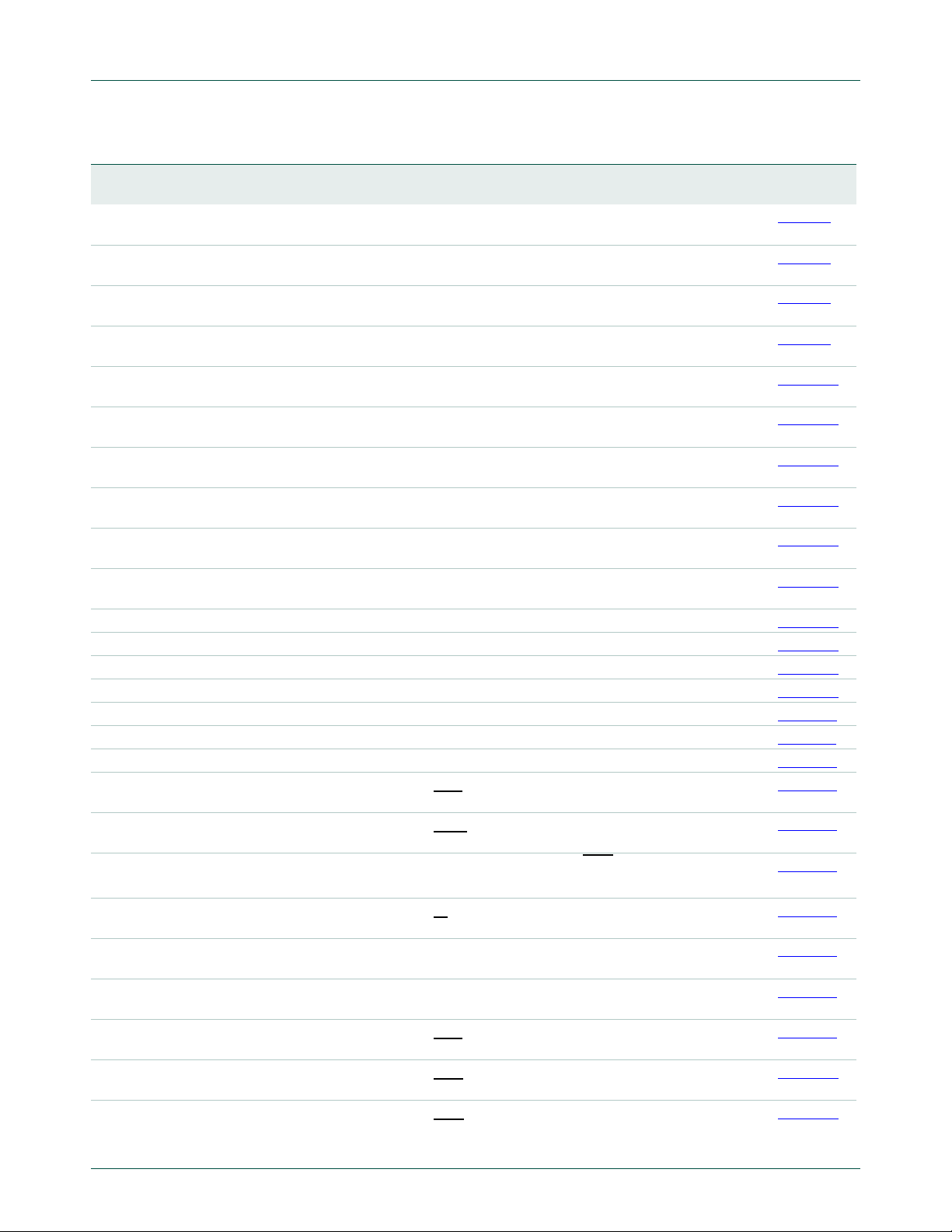

(1) Function not available on the HVQFN33 package.

(2) CT32B1_CAP1 is only available on the TFBGA48 package.

Fig 1. Block diagram (LPC11U1x)

UM10462 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2016. All rights reserved.

User manual Rev. 5.5 — 21 December 2016 11 of 523

Page 12

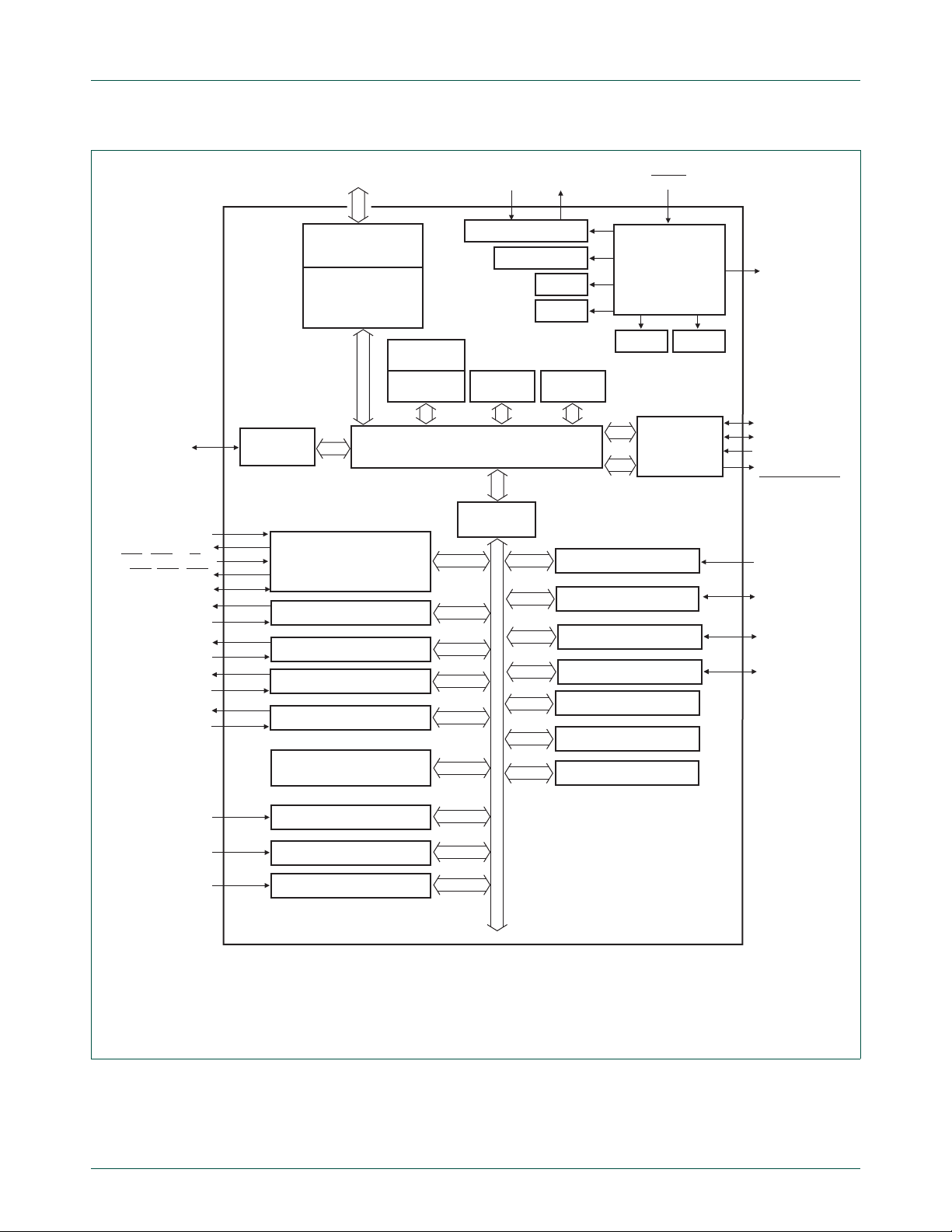

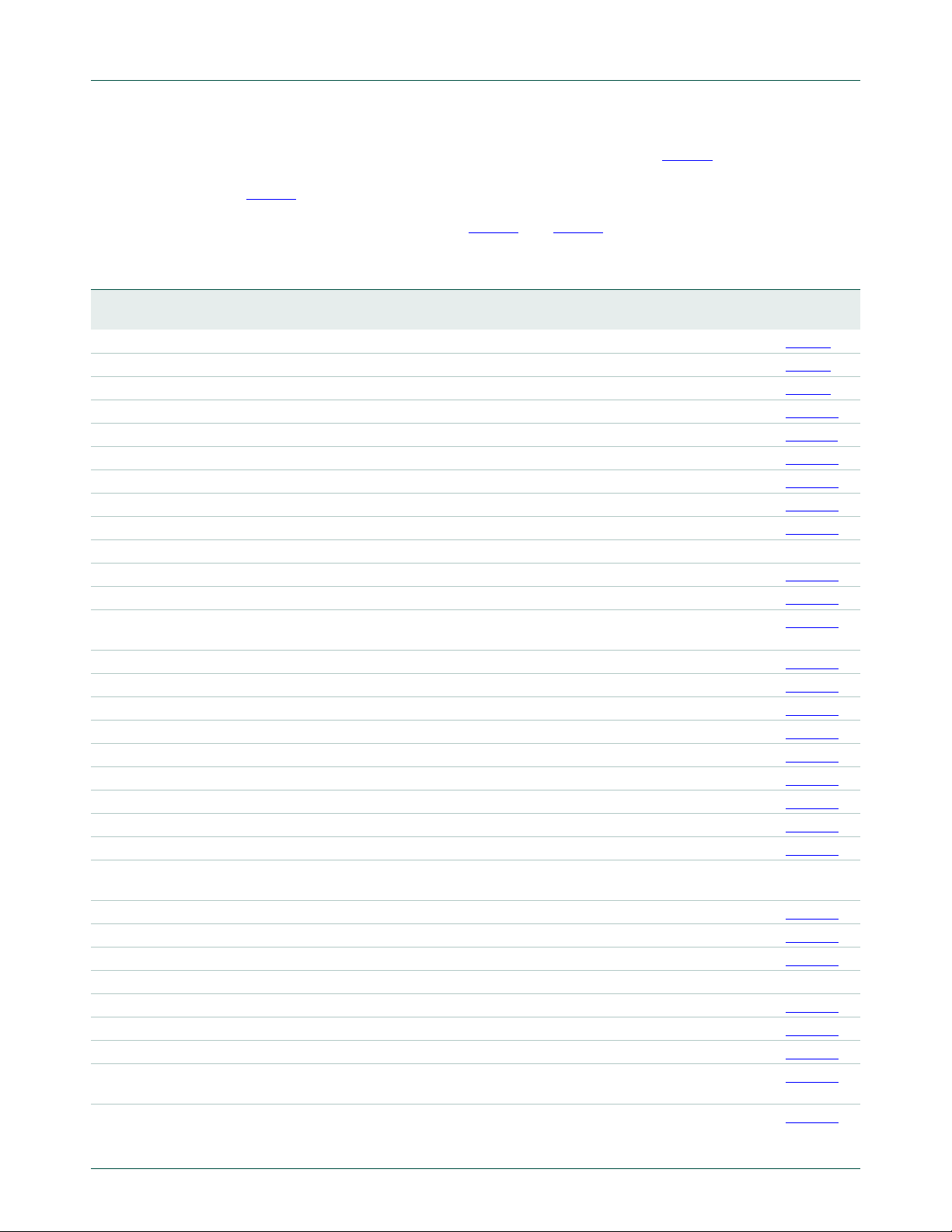

NXP Semiconductors

UM10462

Chapter 1: LPC1 1U3x/2x/1x Introductory information

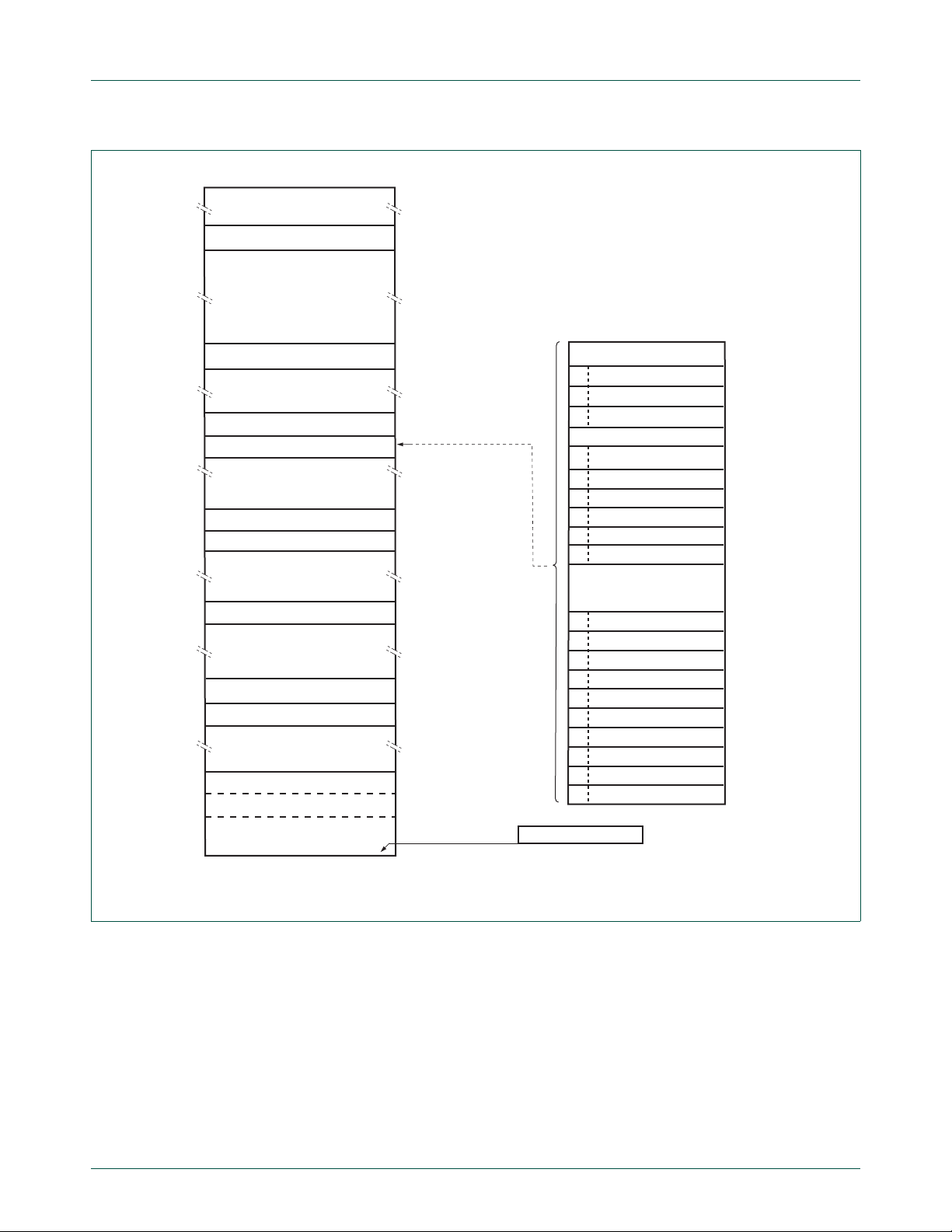

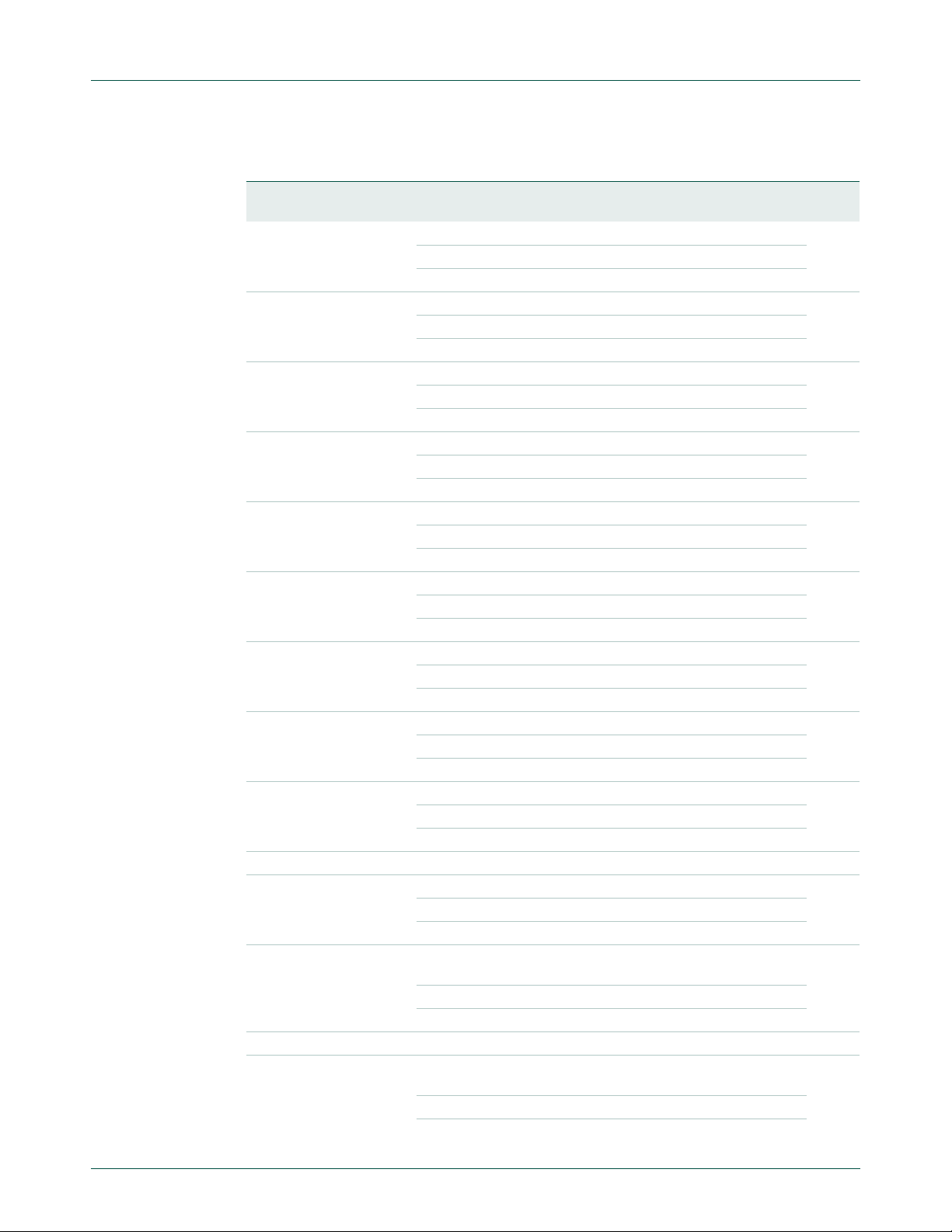

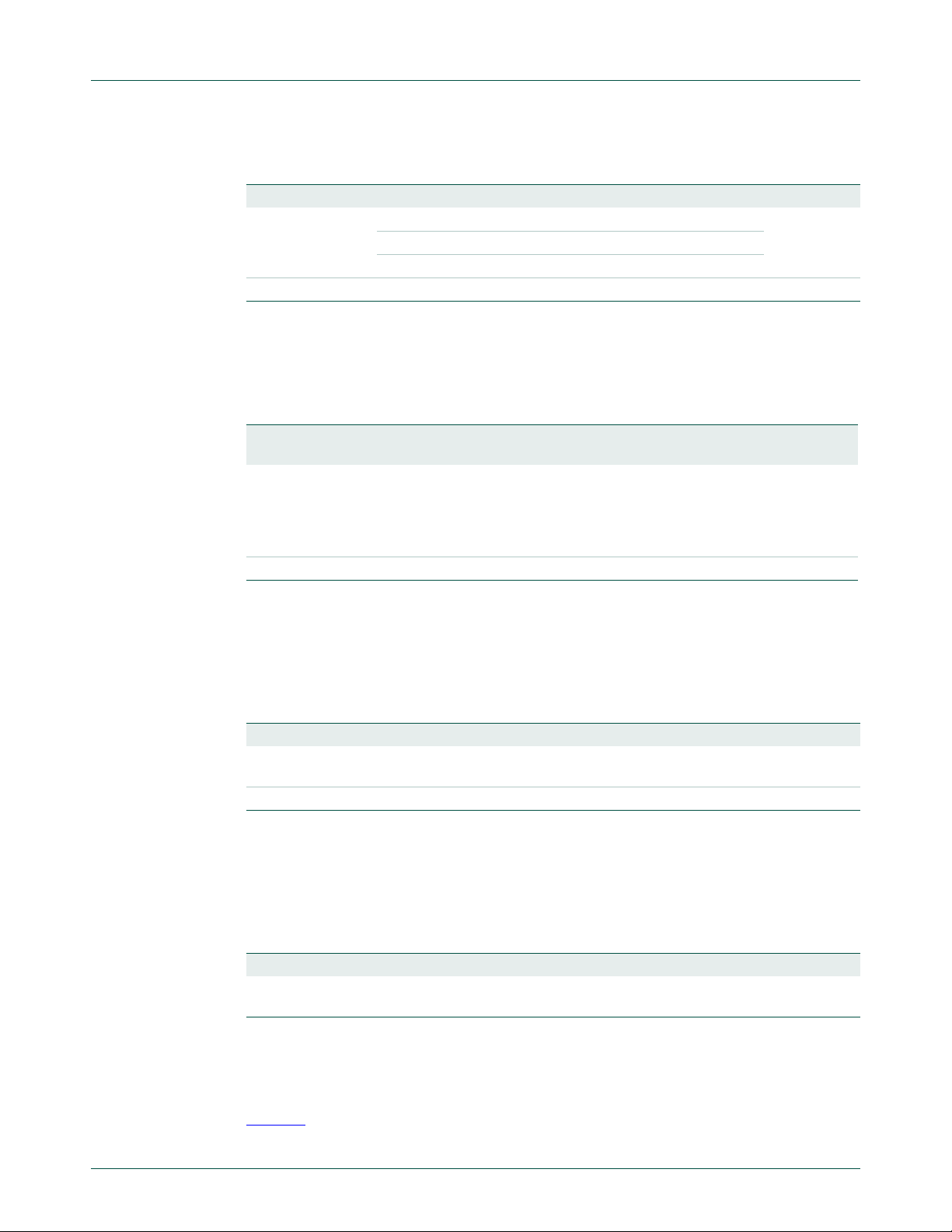

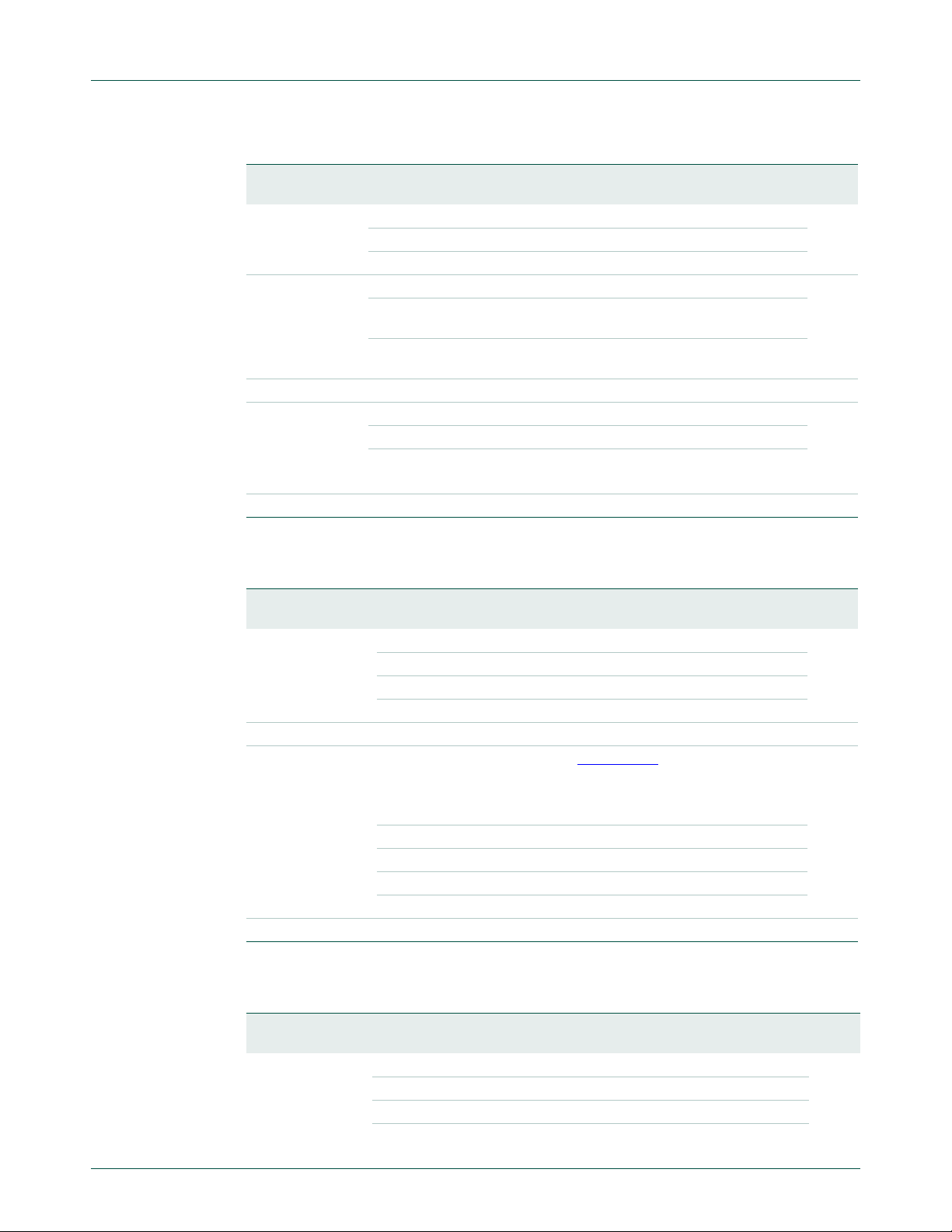

GPIO ports 0/1

RXD

TXD

DCD, DSR

CT16B0_MAT[2:0]

CT16B0_CAP[1:0]

CT16B1_MAT[1:0]

CT16B1_CAP[1:0]

CT32B0_MAT[3:0]

CT32B0_CAP[1:0]

CT32B1_MAT[3:0]

CT32B1_CAP[1:0]

(1)

CTS, RTS, DTR

, RI

SCLK

(1)

(2)

(2)

(2)

(2)

LPC11U2x

HIGH-SPEED

GPIO

SWD, JTAG

TEST/DEBUG

INTERFACE

ARM

CORTEX-M0

EEPROM

system bus

slave

USART/

SMARTCARD INTERFACE

16-bit COUNTER/TIMER 0

16-bit COUNTER/TIMER 1

32-bit COUNTER/TIMER 0

32-bit COUNTER/TIMER 1

WINDOWED WATCHDOG

TIMER

16/24/32 kB

slave slave

1/2/4 kB

FLASH

XTALIN XTALOUT

SYSTEM OSCILLATOR

IRC, WDO

SRAM

8/10 kB

AHB-LITE BUS

slave

AHB TO APB

BRIDGE

BOD

POR

ROM

16 kB

slave

SYSTEM CONTROL

RESET

CLOCK

GENERATION,

POWER CONTROL,

SYSTEM

FUNCTIONS

PLL0 USB PLL

master

USB DEVICE

slave

CONTROLLER

10-bit ADC

I2C-BUS

SSP0

SSP1

IOCON

PMU

CLKOUT

USB_DP

USB_DM

USB_VBUS

USB_FTOGGLE,

USB_CONNECT

AD[7:0]

SCL, SDA

SCK0, SSEL0,

MISO0, MOSI0

SCK1, SSEL1,

MISO1, MOSI1

GPIO pins

GPIO pins

GPIO pins

GPIO INTERRUPTS

GPIO GROUP0 INTERRUPTS

GPIO GROUP1 INTERRUPTS

002aag333

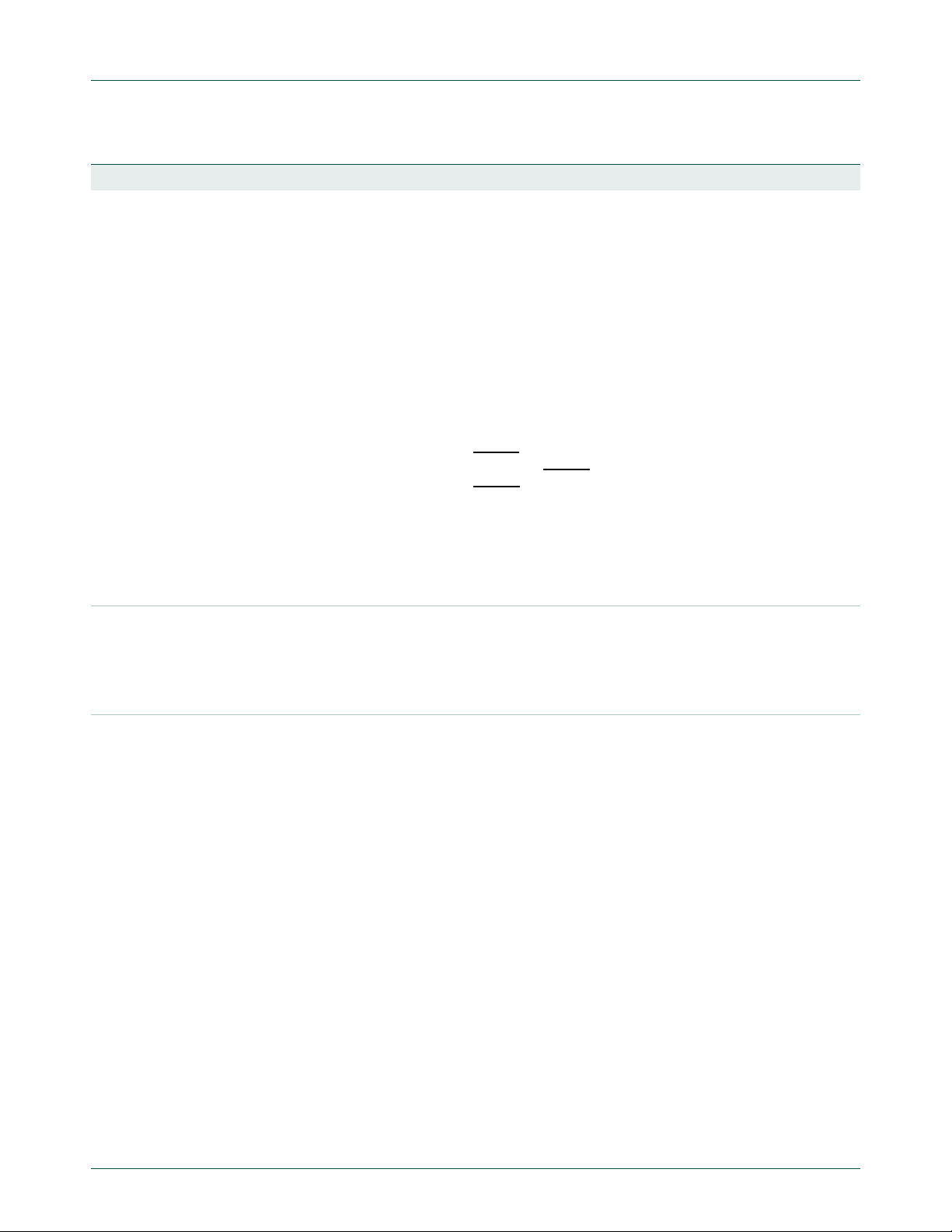

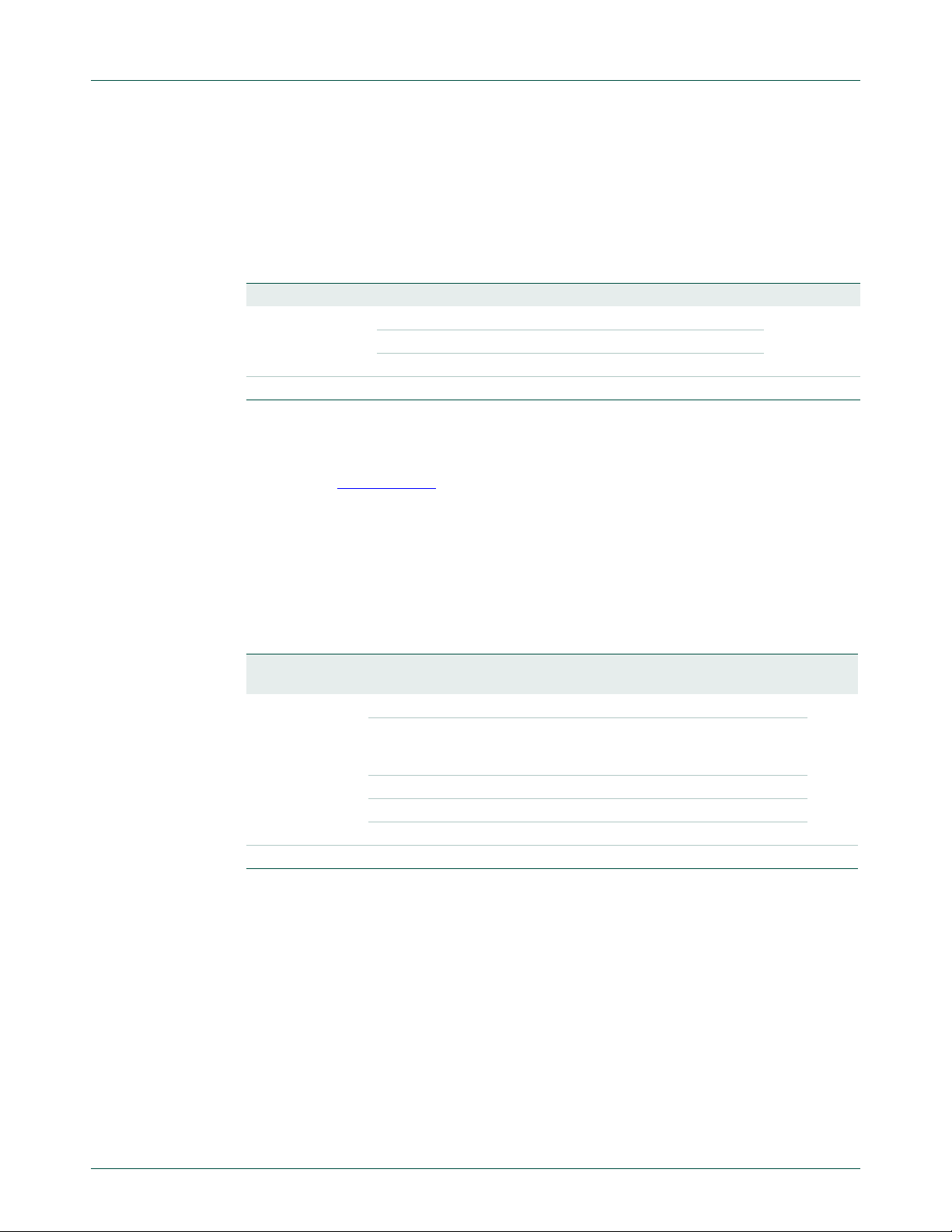

(1) Not available on HVQFN33 packages.

(2) CT32B1_CAP1 available on TFBGA48/LQFP64 packages only. CT16B0_CAP1 and CT16B1_CAP1 available on LQFP64

packages only. CT32B0_CAP1 available on LQFP48/TFBGA48/LQFP64 packages only.

Fig 2. Block diagram (LPC11U2x)

UM10462 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2016. All rights reserved.

User manual Rev. 5.5 — 21 December 2016 12 of 523

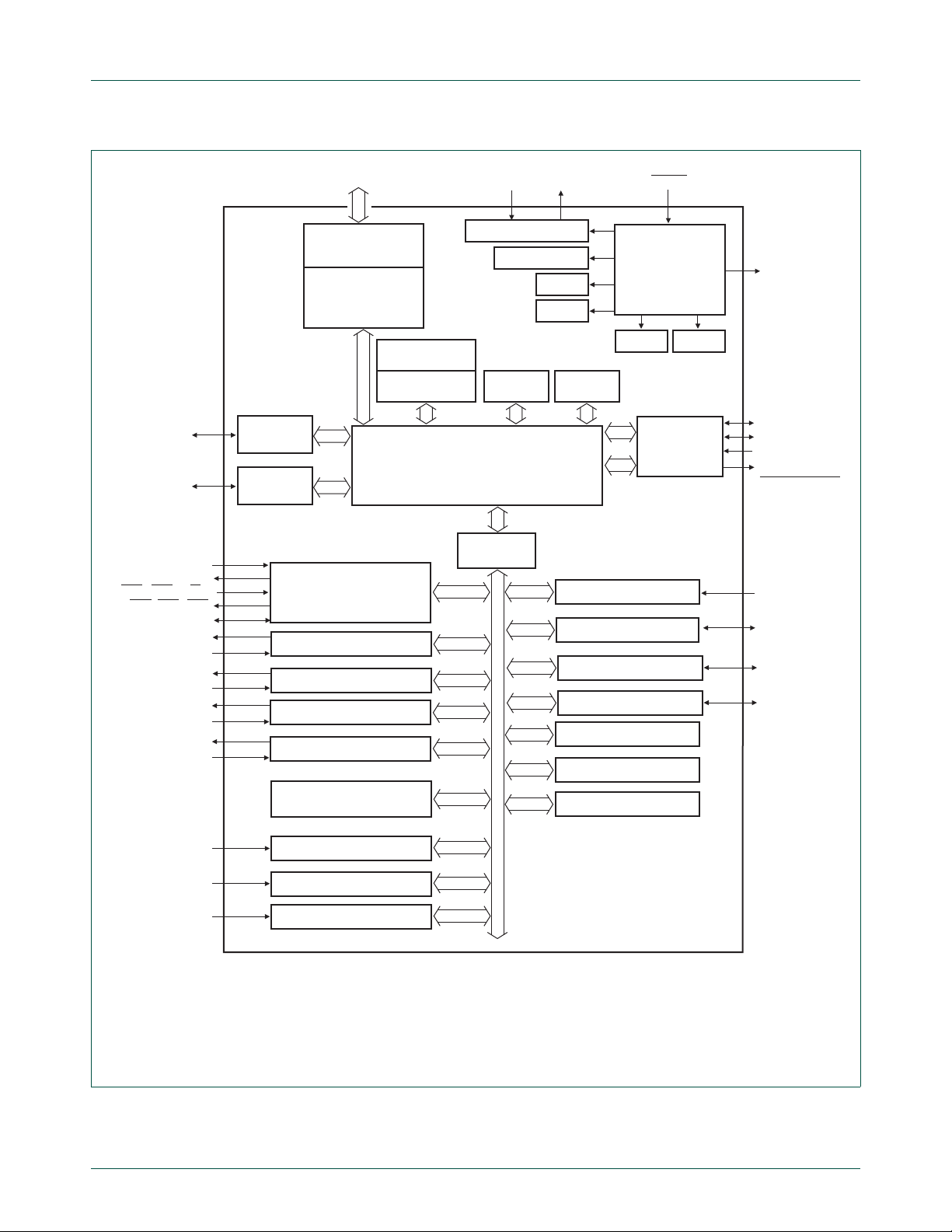

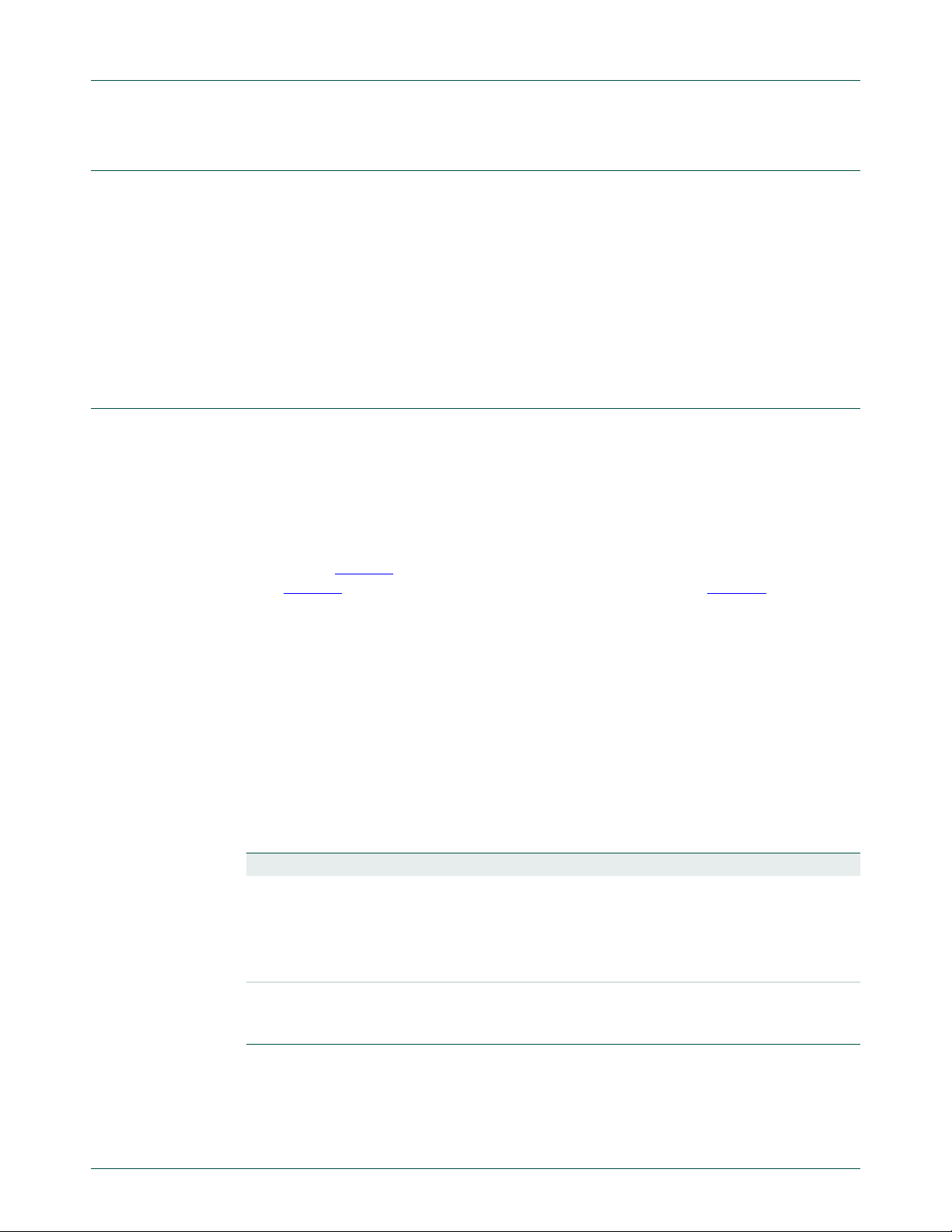

Page 13

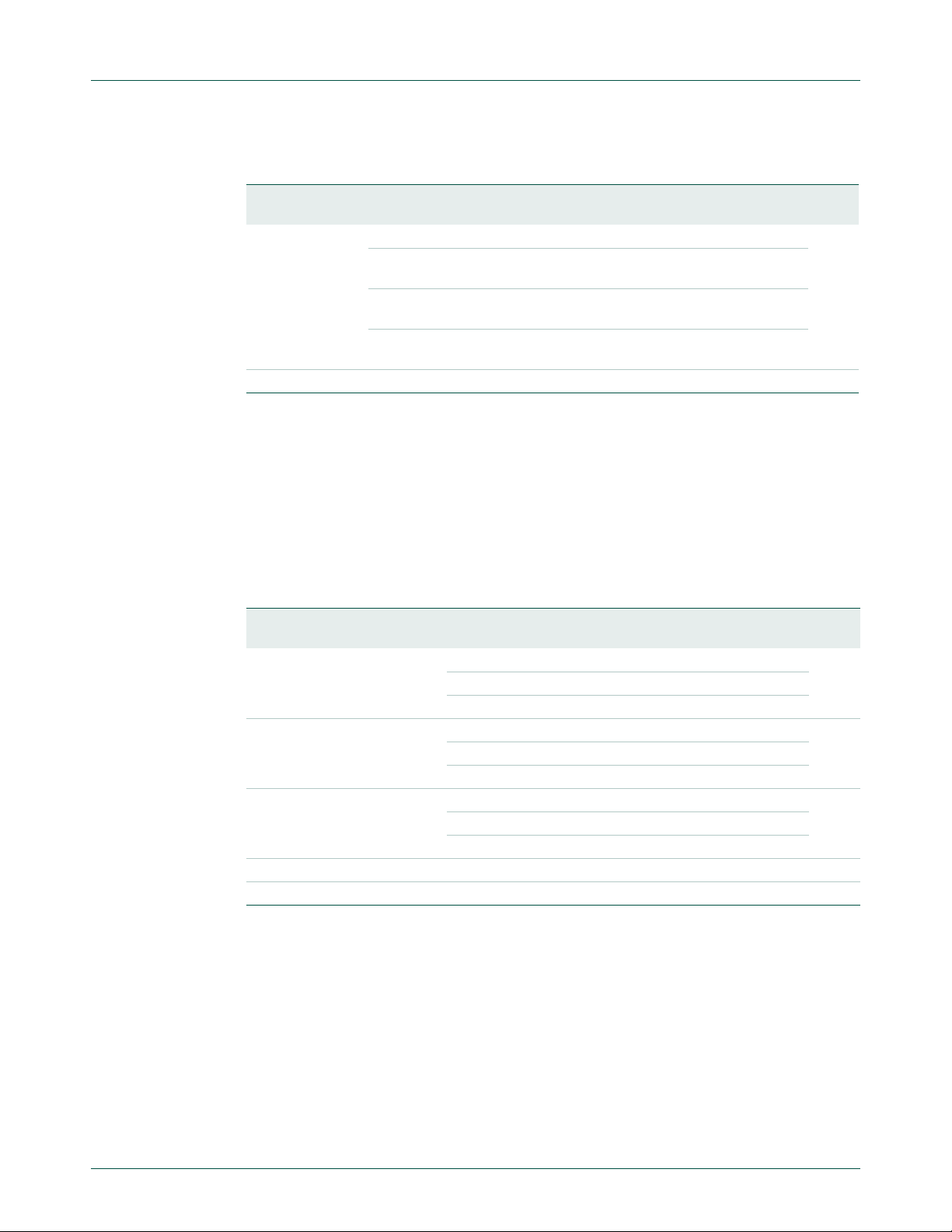

NXP Semiconductors

UM10462

Chapter 1: LPC1 1U3x/2x/1x Introductory information

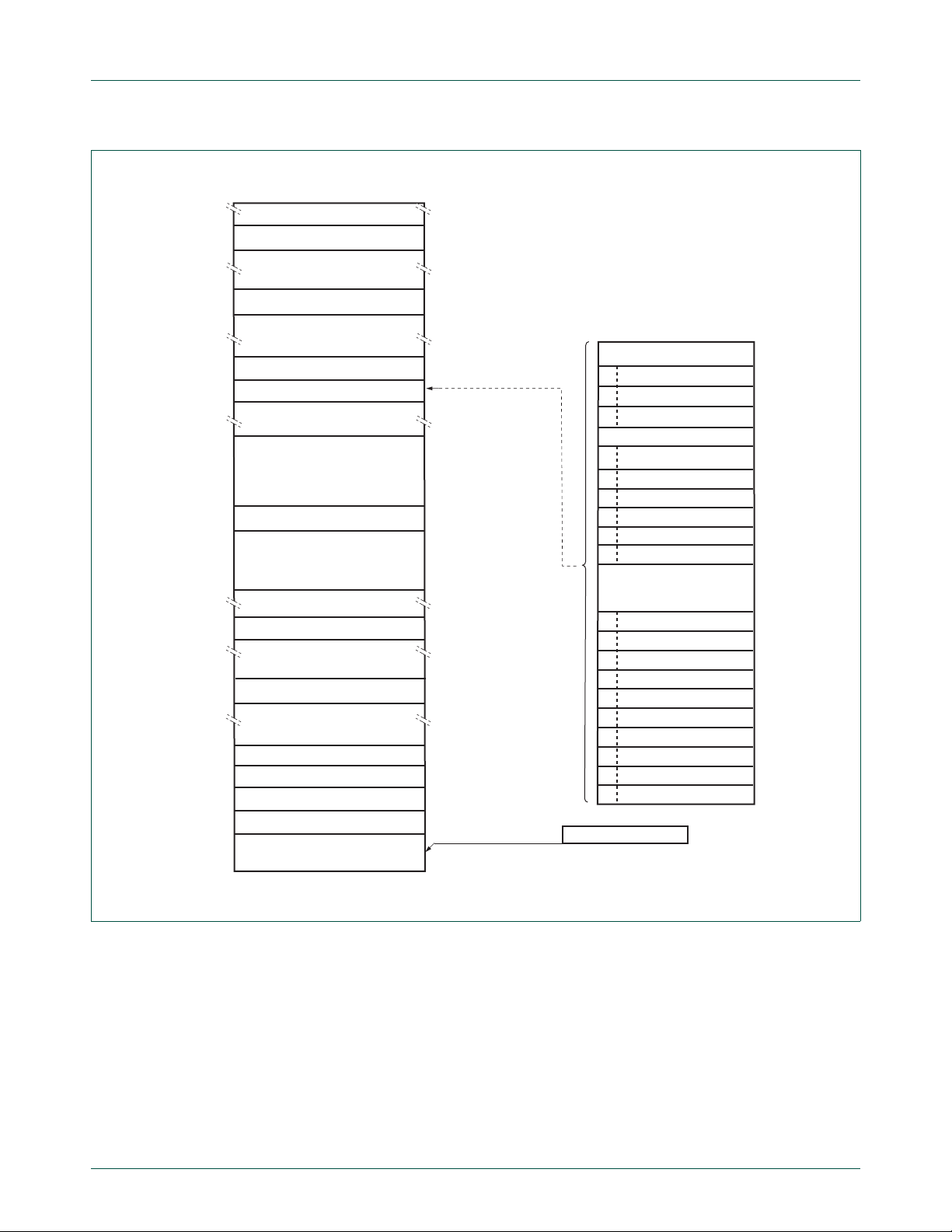

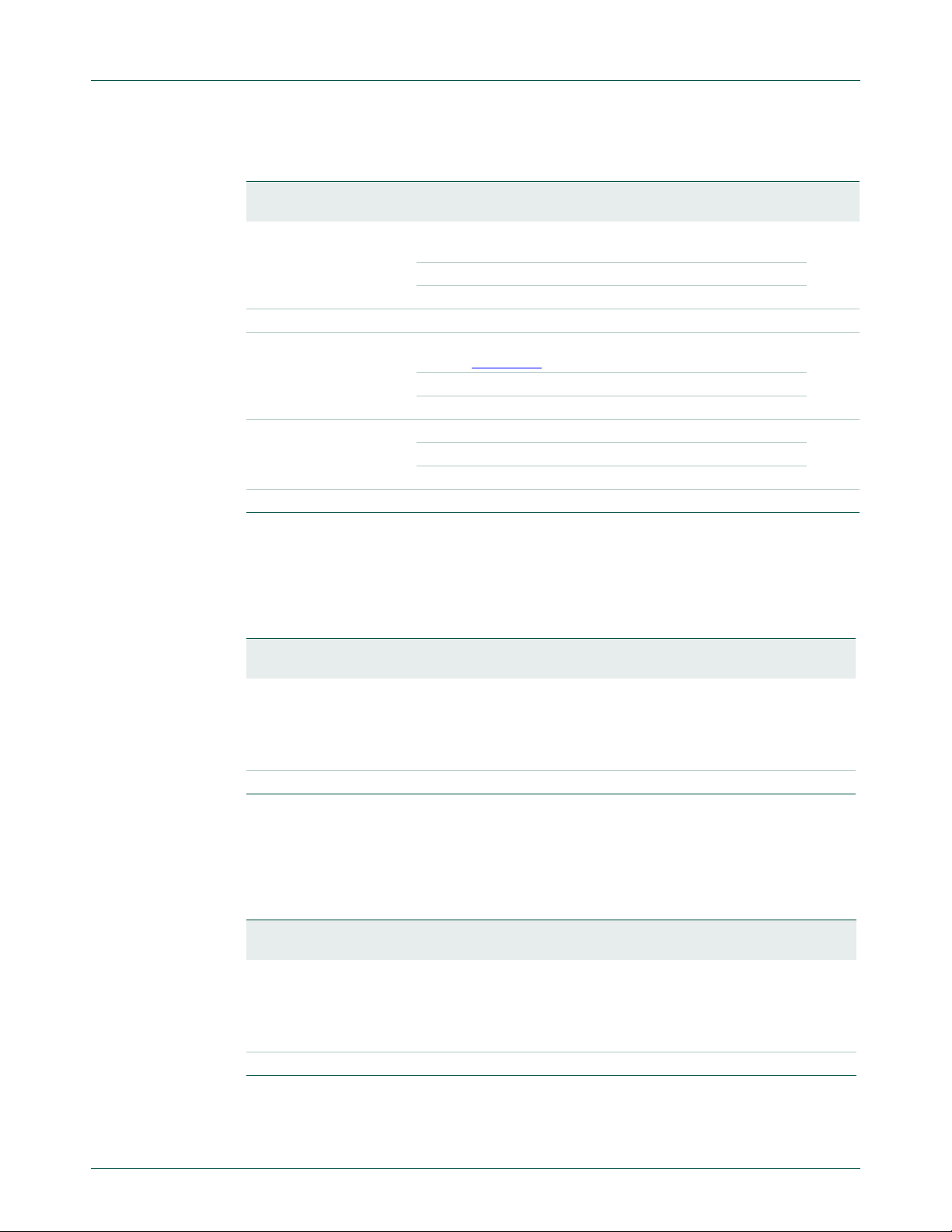

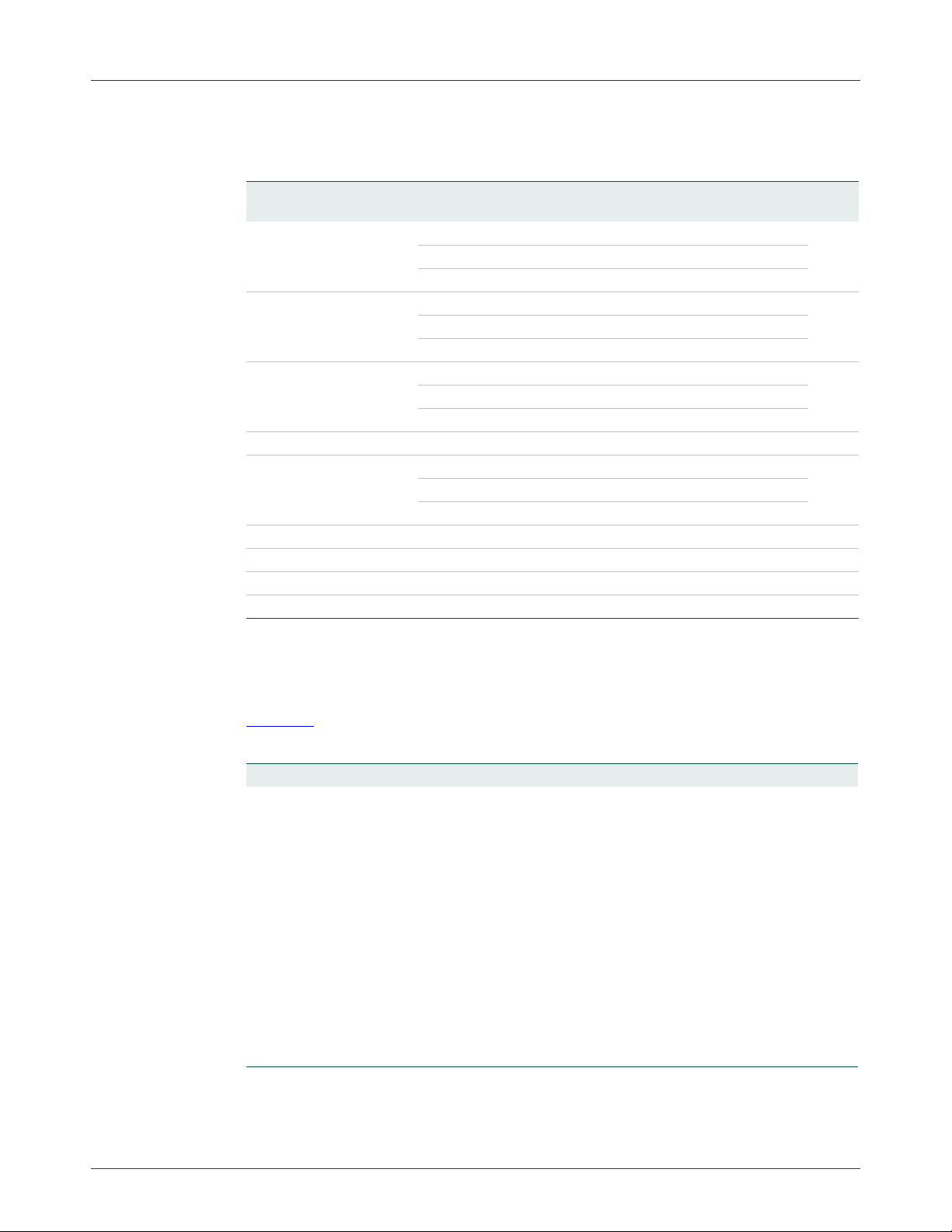

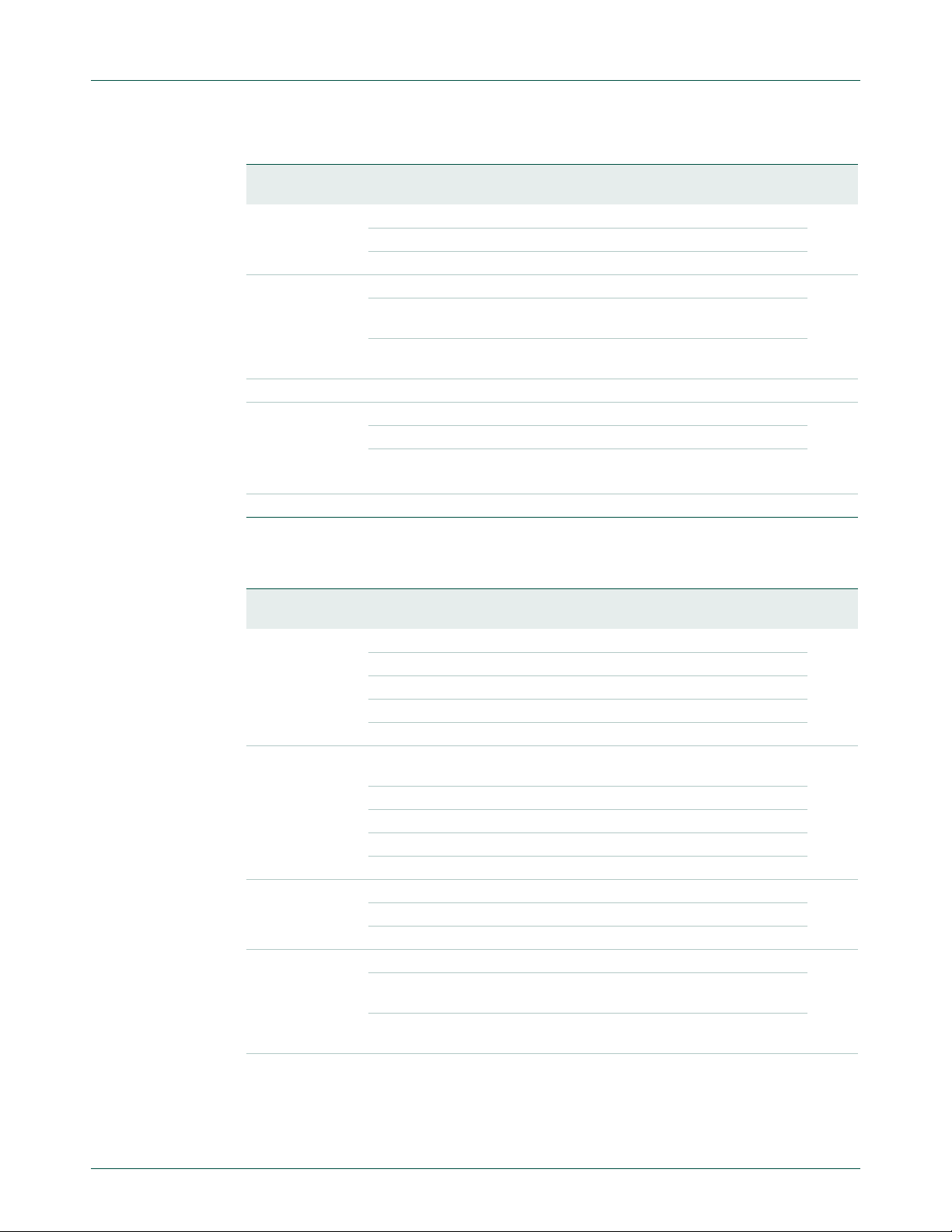

GPIO ports 0/1

IOH_[20:0]

RXD

TXD

DCD, DSR

CT16B0_MAT[2:0]

CT16B0_CAP[1:0]

CT16B1_MAT[1:0]

CT16B1_CAP[1:0]

CT32B0_MAT[3:0]

CT32B0_CAP[1:0]

CT32B1_MAT[3:0]

CT32B1_CAP[1:0]

(1)

CTS, RTS, DTR

, RI

SCLK

(1)

(2)

(2)

(2)

(2)

LPC11U3x

HIGH-SPEED

GPIO

I/O

HANDLER

SWD, JTAG

TEST/DEBUG

INTERFACE

ARM

CORTEX-M0

EEPROM

system bus

slave

master

(3)

USART/

SMARTCARD INTERFACE

16-bit COUNTER/TIMER 0

16-bit COUNTER/TIMER 1

32-bit COUNTER/TIMER 0

32-bit COUNTER/TIMER 1

WINDOWED WATCHDOG

40/48/64/96/128 kB

slave slave

TIMER

4 kB

FLASH

XTALIN XTALOUT

SYSTEM OSCILLATOR

IRC, WDO

SRAM

8/10/12 kB

AHB-LITE BUS

slave

AHB TO APB

BRIDGE

BOD

POR

ROM

16 kB

slave

master

slave

10-bit ADC

SYSTEM CONTROL

RESET

CLOCK

GENERATION,

POWER CONTROL,

SYSTEM

FUNCTIONS

PLL0 USB PLL

USB DEVICE

CONTROLLER

I2C-BUS

SSP0

SSP1

IOCON

PMU

CLKOUT

USB_DP

USB_DM

USB_VBUS

USB_FTOGGLE,

USB_CONNECT

AD[7:0]

SCL, SDA

SCK0, SSEL0,

MISO0, MOSI0

SCK1, SSEL1,

MISO1, MOSI1

GPIO pins

GPIO pins

GPIO pins

GPIO INTERRUPTS

GPIO GROUP0 INTERRUPTS

GPIO GROUP1 INTERRUPTS

002aag345

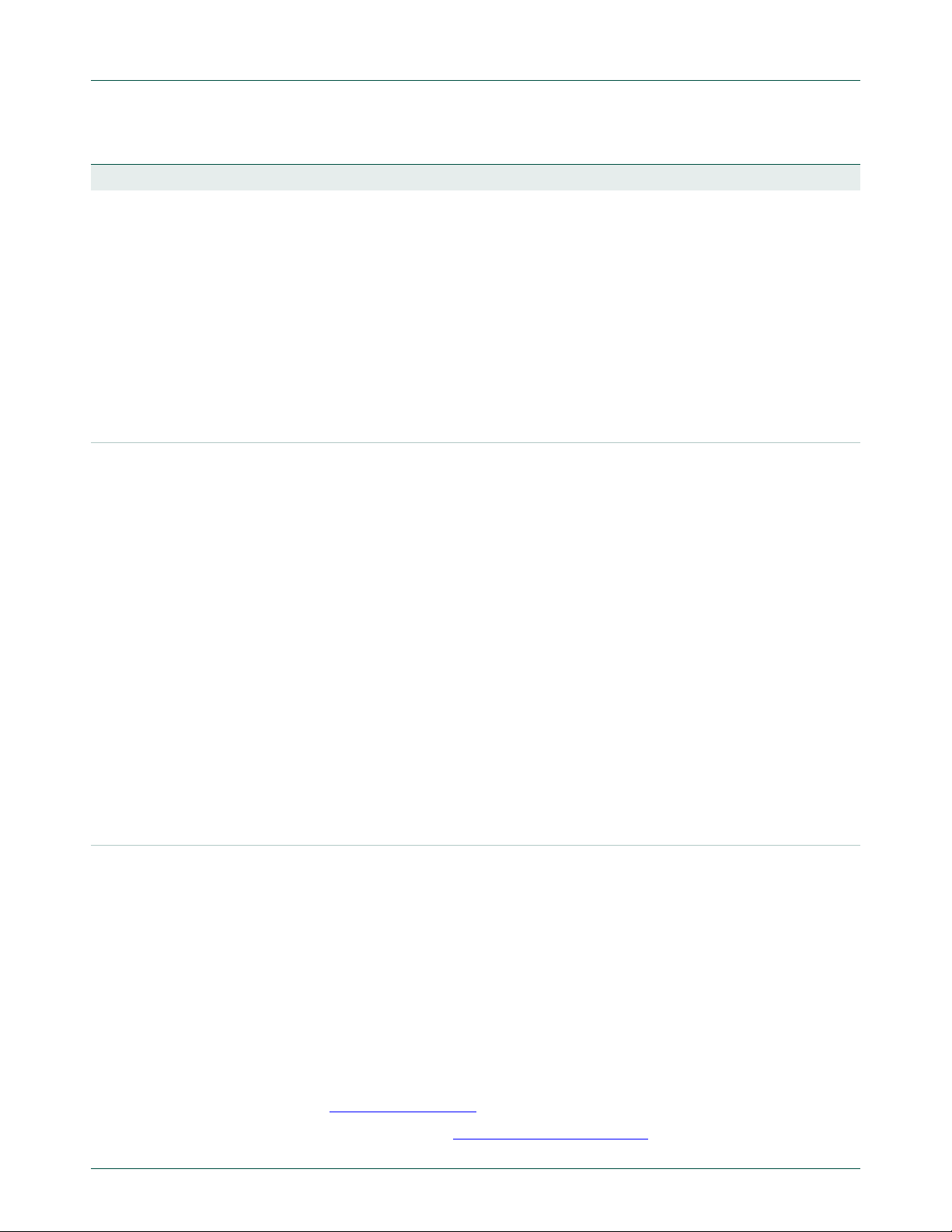

(1) Not available on HVQFN33 packages.

(2) CT16B0_CAP1, CT16B1_CAP1 available on LQFP64 packages only; CT32B0_CAP1 available on TFBGA48, LQFP48, and

LQFP64 packages only; CT32B1_CAP1 available in TFBGA48/LQFP64 packages only.

(3) LPC11U37HFBD64/401 only.

Fig 3. Block diagram (LPC11U3x)

UM10462 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2016. All rights reserved.

User manual Rev. 5.5 — 21 December 2016 13 of 523

Page 14

UM10462

Chapter 2: LPC11U3x/2x/1x Memory mapping

Rev. 5.5 — 21 December 2016 User manual

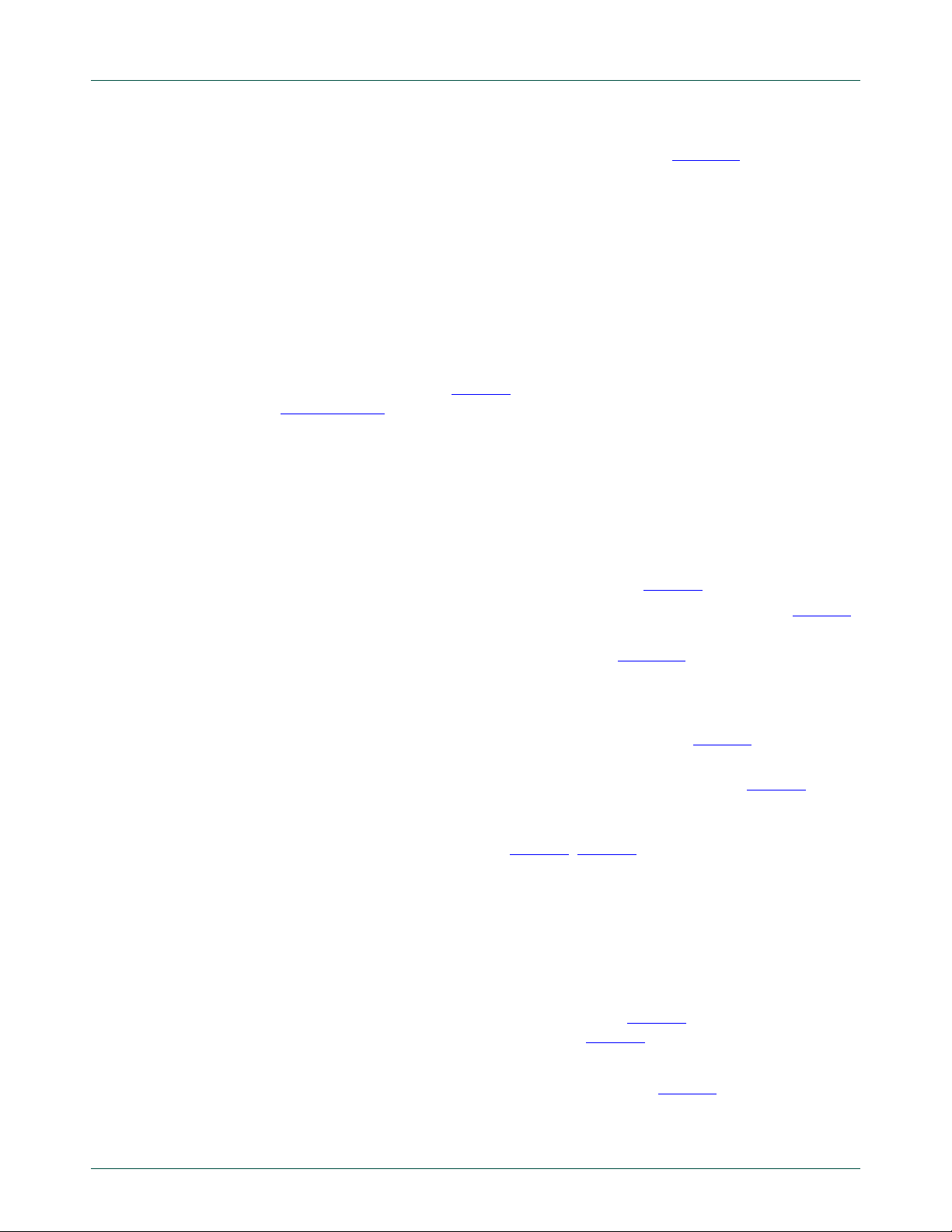

2.1 How to read this chapter

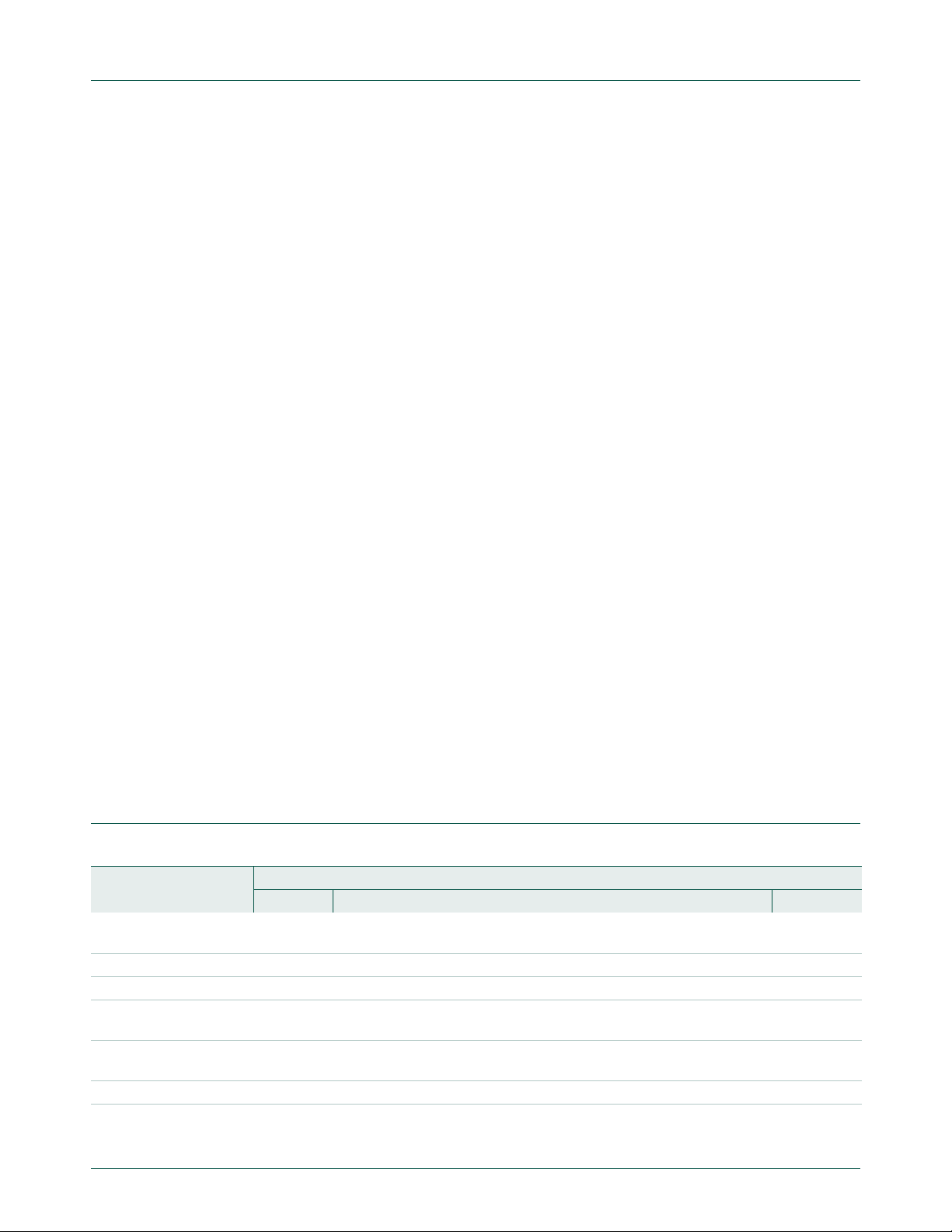

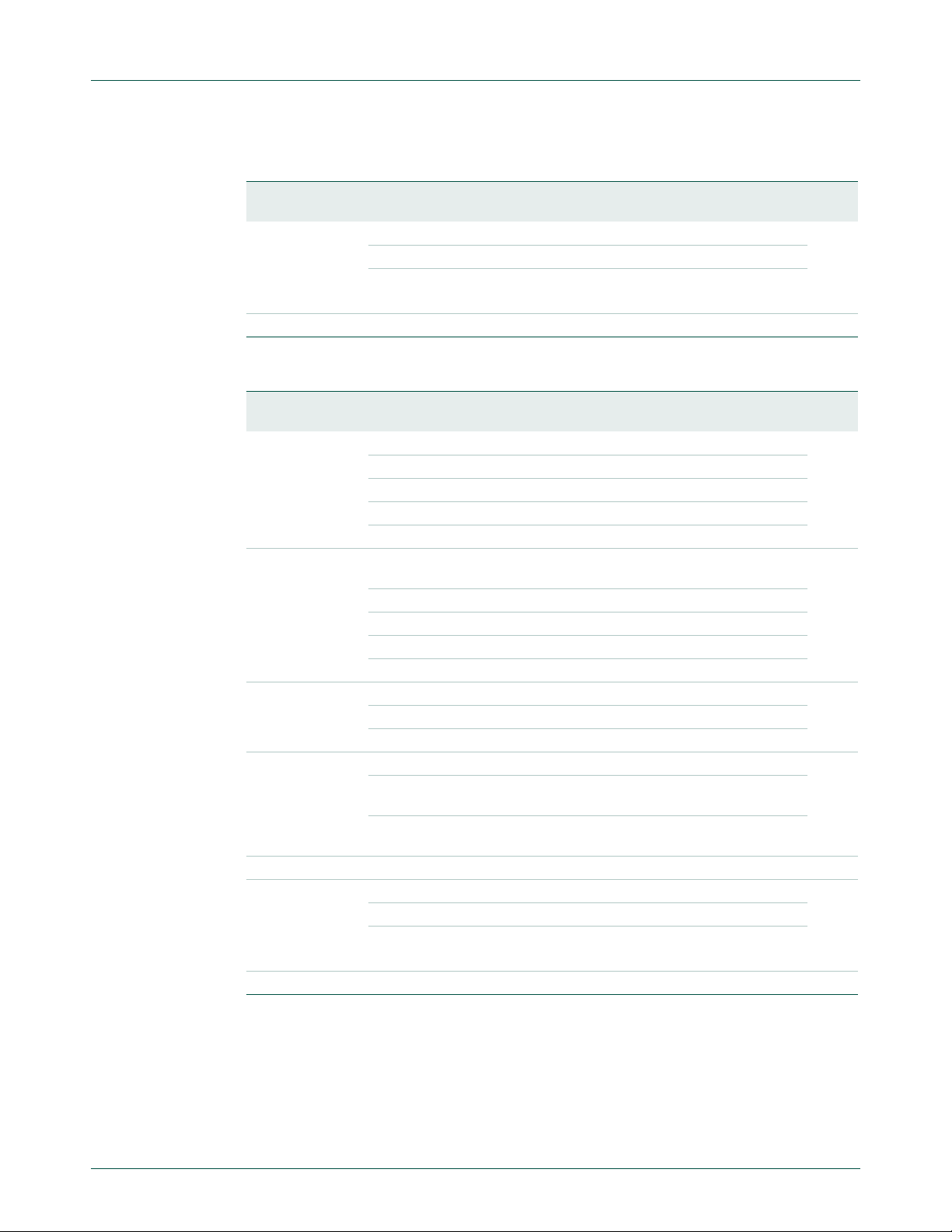

See Table 3 for the memory configuration of the LPC11U3x/2x/1x parts.

Table 3. LPC11U3x/2x/1x memory configuration

Part Flash

LPC11U12FHN33/201 16 4 - 2 n/a Figure 4

LPC11U12FBD48/201 16 4 - 2 n/a Figure 4

LPC11U13FBD48/201 24 4 - 2 n/a Figure 4

LPC11U14FHN33/201 32 4 - 2 n/a Figure 4

LPC11U14FHI33/201 32 4 - 2 n/a Figure 4

LPC11U14FBD48/201 32 4 - 2 n/a Figure 4

LPC11U14FET48/201 32 4 - 2 n/a Figure 4

LPC11U22FBD48/301 16 6 - 2 1 kB Figure 5

LPC11U23FBD48/301 24 6 - 2 1 kB Figure 5

LPC11U24FHI33/301 32 6 - 2 2 kB Figure 5

LPC11U24FBD48/301 32 6 - 2 2 kB Figure 5

LPC11U24FET48/301 32 6 - 2 2 kB Figure 5

LPC11U24FHN33/401 32 8 - 2 4 kB Figure 5

LPC11U24FBD48/401 32 8 - 2 4 kB Figure 5

LPC11U24FBD64/401 32 8 - 2 4 kB Figure 5

LPC11U34FHN33/311 40 8 - - 4 kB Figure 6

LPC11U34FBD48/311 40 8 - - 4 kB Figure 6

LPC11U34FHN33/421 48 8 - 2 4 kB Figure 6

LPC11U34FBD48/421 48 8 - 2 4 kB Figure 6

LPC11U35FHN33/401 64 8 - 2 4 kB Figure 6

LPC11U35FBD48/401 64 8 - 2 4 kB Figure 6

LPC11U35FBD64/401 64 8 - 2 4 kB Figure 6

LPC11U35FHI33/501 64 8 2 2 4 kB Figure 6

LPC11U35FET48/501 64 8 2 2 4 kB Figure 6

LPC11U36FBD48/401 96 8 - 2 4 kB Figure 6

LPC11U36FBD64/401 96 8 - 2 4 kB Figure 6

LPC11U37FBD48/401 128 8 - 2 4 kB Figure 6

LPC11U37HFBD64/401 128 8 2

LPC11U37FBD64/501 128 8 2 2 4 kB Figure 6

in kB

Main

SRAM0 at

0x1000

0000

SRAM1 at

0x2000

0000

[1]

USB SRAM

at 0x2000

4000

24 kBFigure 6

EEPROM Reference

[1] For I/O Handler use only.

UM10462 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2016. All rights reserved.

User manual Rev. 5.5 — 21 December 2016 14 of 523

Page 15

NXP Semiconductors

2.2 Memory map

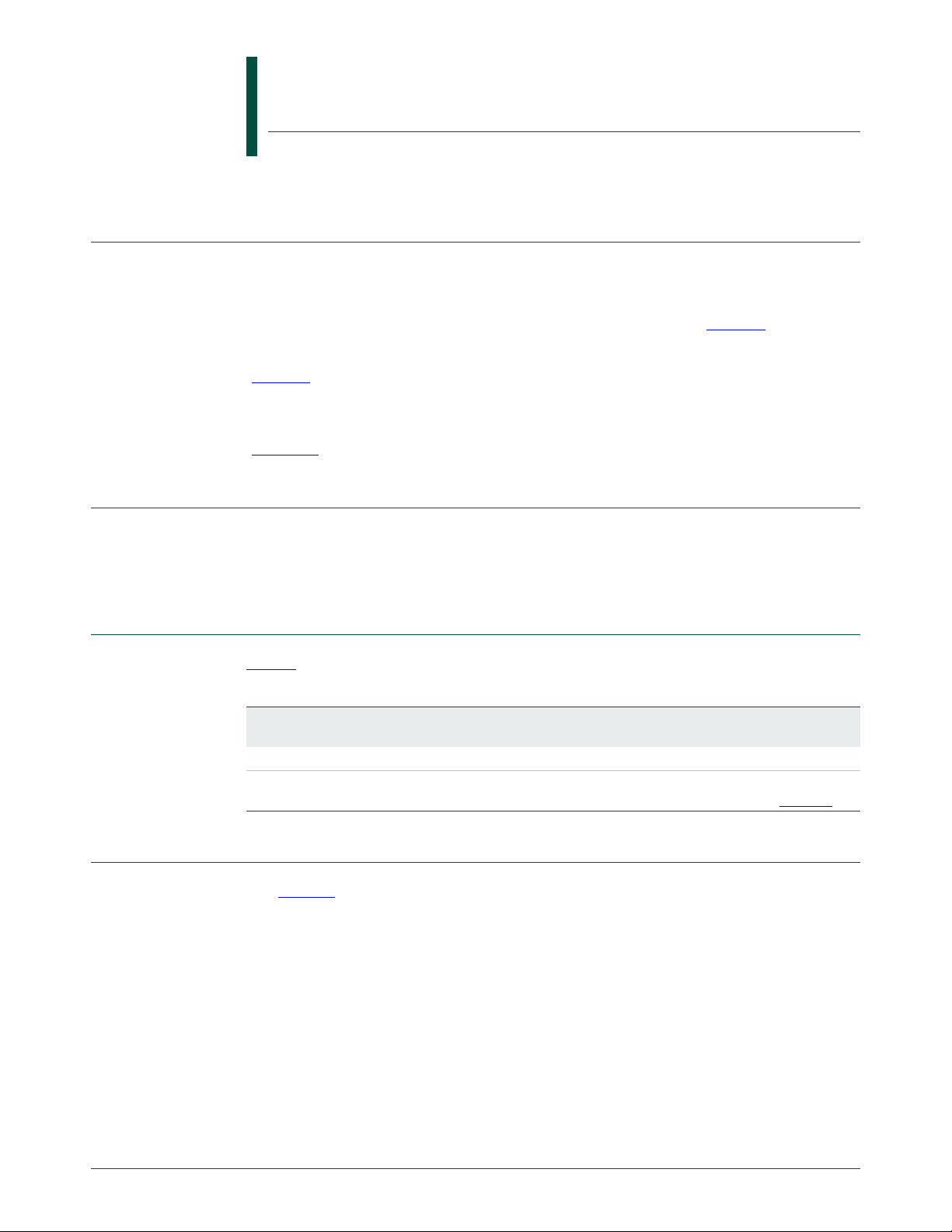

The LPC11U3x/2x/1x incorporates several distinct memory regions, shown in the

following figures. Figure 4

user program viewpoint following reset.

The AHB peripheral area is 2 MB in size and is divided to allow for up to 128 peripherals.

The APB peripheral area is 512 kB in size and is divided to allow for up to 32 peripherals.

Each peripheral of either type is allocated 16 kB of space. This allows simplifying the

address decoding for each peripheral.

UM10462

Chapter 2: LPC11U3x/2x/1x Memory mapping

shows the overall map of the entire address space from the

UM10462 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2016. All rights reserved.

User manual Rev. 5.5 — 21 December 2016 15 of 523

Page 16

NXP Semiconductors

UM10462

Chapter 2: LPC11U3x/2x/1x Memory mapping

4 GB

1 GB

0.5 GB

0 GB

LPC11U12/13/14

reserved

private peripheral bus

reserved

GPIO

reserved

USB

APB peripherals

reserved

2 kB USB RAM

reserved

reserved

16 kB boot ROM

reserved

4 kB SRAM

reserved

32 kB on-chip flash (LPC11U14)

24 kB on-chip flash (LPC11U13)

16 kB on-chip flash (LPC11U12)

0xFFFF FFFF

0xE010 0000

0xE000 0000

0x5000 4000

0x5000 0000

0x4008 4000

0x4008 0000

0x4000 0000

0x2000 4800

0x2000 4000

0x2000 0000

0x1FFF 4000

0x1FFF 0000

0x1000 1000

0x1000 0000

0x0000 8000

0x0000 6000

0x0000 4000

0x0000 0000

APB peripherals

25 - 31 reserved

GPIO GROUP1 INT

24

GPIO GROUP0 INT

23

22

20 - 21 reserved

19

18

17

16

15

14

9

8

7

6

5

4

3

2

1

0

active interrupt vectors

GPIO interrupts

system control

flash controller

10 - 13 reserved

32-bit counter/timer 1

32-bit counter/timer 0

16-bit counter/timer 1

16-bit counter/timer 0

USART/SMART CARD

SSP1

IOCON

SSP0

PMU

reserved

reserved

ADC

WWDT

2

C-bus

I

0x0000 00C0

0x0000 0000

0x4008 0000

0x4006 4000

0x4006 0000

0x4005 C000

0x4005 8000

0x4004 C000

0x4004 C000

0x4004 8000

0x4004 4000

0x4004 0000

0x4003 C000

0x4003 8000

0x4002 8000

0x4002 4000

0x4002 0000

0x4001 C000

0x4001 8000

0x4001 4000

0x4001 0000

0x4000 C000

0x4000 8000

0x4000 4000

0x4000 0000

002aaf891

SSP1 available on 48-pin packages only.

Fig 4. LPC11U1x memory map

UM10462 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2016. All rights reserved.

User manual Rev. 5.5 — 21 December 2016 16 of 523

Page 17

NXP Semiconductors

UM10462

Chapter 2: LPC11U3x/2x/1x Memory mapping

4 GB

1 GB

0.5 GB

0 GB

LPC11U2x

reserved

private peripheral bus

reserved

GPIO

reserved

USB

APB peripherals

reserved

2 kB USB RAM

reserved

reserved

16 kB boot ROM

reserved

8 kB SRAM (LPC11U2x/401)

6 kB SRAM (LPC11U2x/301)

reserved

32 kB on-chip flash (LPC11U24)

24 kB on-chip flash (LPC11U23)

16 kB on-chip flash (LPC11U22)

0xFFFF FFFF

0xE010 0000

0xE000 0000

0x5000 4000

0x5000 0000

0x4008 4000

0x4008 0000

0x4000 0000

0x2000 4800

0x2000 4000

0x2000 0000

0x1FFF 4000

0x1FFF 0000

0x1000 2000

0x1000 1800

0x1000 0000

0x0000 8000

0x0000 6000

0x0000 4000

0x0000 0000

APB peripherals

25 - 31 reserved

GPIO GROUP1 INT

24

GPIO GROUP0 INT

23

22

20 - 21 reserved

19

18

17

16

15

14

9

8

7

6

5

4

3

2

1

0

active interrupt vectors

GPIO interrupts

system control

flash/EEPROM controller

10 - 13 reserved

32-bit counter/timer 1

32-bit counter/timer 0

16-bit counter/timer 1

16-bit counter/timer 0

USART/SMART CARD

SSP1

IOCON

SSP0

PMU

reserved

reserved

ADC

WWDT

2

C-bus

I

0x0000 00C0

0x0000 0000

0x4008 0000

0x4006 4000

0x4006 0000

0x4005 C000

0x4005 8000

0x4004 C000

0x4004 C000

0x4004 8000

0x4004 4000

0x4004 0000

0x4003 C000

0x4003 8000

0x4002 8000

0x4002 4000

0x4002 0000

0x4001 C000

0x4001 8000

0x4001 4000

0x4001 0000

0x4000 C000

0x4000 8000

0x4000 4000

0x4000 0000

002aag594

Fig 5. LPC11U2x memory map

UM10462 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2016. All rights reserved.

User manual Rev. 5.5 — 21 December 2016 17 of 523

Page 18

NXP Semiconductors

UM10462

Chapter 2: LPC11U3x/2x/1x Memory mapping

4 GB

1 GB

0.5 GB

0 GB

LPC11U3x

reserved

private peripheral bus

reserved

GPIO

reserved

USB

APB peripherals

reserved

2 kB USB RAM (LPC11U34/421

LPC11U35/401/501

LPC11U36/401/501

LPC11U37/401/501,

LPC11U37H/401)

reserved

2 kB SRAM1 (LPC11U35/501

LPC11U37/501)

I/O Handler code area

for LPC11U37HFBD64/401

reserved

16 kB boot ROM

reserved

8 kB SRAM0 (LPC11U3x)

reserved

128 kB on-chip flash (LPC11U37/7H)

96 kB on-chip flash (LPC11U36)

64 kB on-chip flash (LPC11U35)

48 kB on-chip flash (LPC11U34/421)

40 kB on-chip flash (LPC11U34/311)

0xFFFF FFFF

0xE010 0000

0xE000 0000

0x5000 4000

0x5000 0000

0x4008 4000

0x4008 0000

0x4000 0000

0x2000 4800

0x2000 4000

0x2000 0800

0x2000 0000

0x1FFF 4000

0x1FFF 0000

0x1000 2000

0x1000 0000

0x0002 0000

0x0001 8000

0x0001 0000

0x0000 C000

0x0000 A000

0x0000 0000

APB peripherals

25 - 31 reserved

GPIO GROUP1 INT

24

GPIO GROUP0 INT

23

22

20 - 21 reserved

19

18

17

16

15

14

9

8

7

6

5

4

3

2

1

0

active interrupt vectors

GPIO interrupts

system control

IOCON

flash/EEPROM controller

10 - 13 reserved

reserved

reserved

32-bit counter/timer 1

32-bit counter/timer 0

16-bit counter/timer 1

16-bit counter/timer 0

USART/SMART CARD

I

SSP1

SSP0

PMU

ADC

WWDT

2

C-bus

0x0000 00C0

0x0000 0000

0x4008 0000

0x4006 4000

0x4006 0000

0x4005 C000

0x4005 8000

0x4004 C000

0x4004 C000

0x4004 8000

0x4004 4000

0x4004 0000

0x4003 C000

0x4003 8000

0x4002 8000

0x4002 4000

0x4002 0000

0x4001 C000

0x4001 8000

0x4001 4000

0x4001 0000

0x4000 C000

0x4000 8000

0x4000 4000

0x4000 0000

002aag813

Fig 6. LPC11U3x memory map

UM10462 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2016. All rights reserved.

User manual Rev. 5.5 — 21 December 2016 18 of 523

Page 19

UM10462

Chapter 3: LPC11U3x/2x/1x System control block

Rev. 5.5 — 21 December 2016 User manual

3.1 How to read this chapter

The system control block is identical for all LPC11U3x/2x/1x parts.

The following register bit is available on LPC11U3x/501 and LPC11U37H only and is

reserved otherwise: SYSAHBCLKCTRL register bit RAM1 (bit 26) (Table 24

Remark: For part LPC11U37H, enable the SRAM1 clock in the SYSAHBCLKCTRL

(Table 24

The DEVICE_ID register contains the device id numbers for the LPC11U1x and

LPC11U2x parts. For LPC11U3x parts, see the ISP/IAP Read Part Id command

(Table 376

3.2 Introduction

) register for running the I/O Handler software library code.

).

).

The system configuration block controls oscillators, some aspects of the power

management, and the clock generation of the LP C11U3x/2x/1x. Also included in this block

is a register for remapping flash, SRAM, and ROM memory areas.

3.3 Pin description

Table 4 shows pins that are assoc iated with system control block functions .

Table 4. Pin summary

Pin name Pin

CLKOUT O Clockout pin

PIO0 and PIO1 pins I Eight pins can be selected as external interrupt

3.4 Clocking and power control

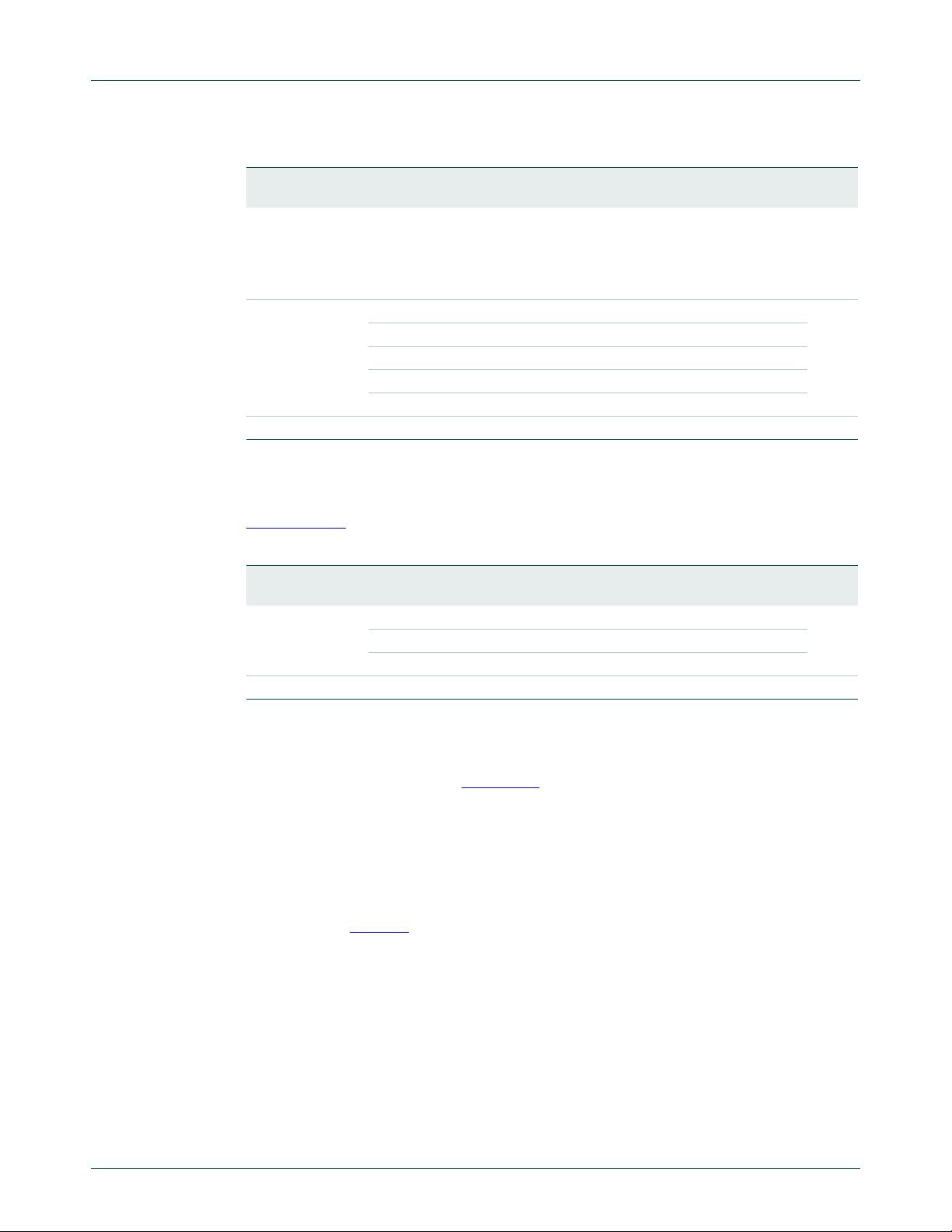

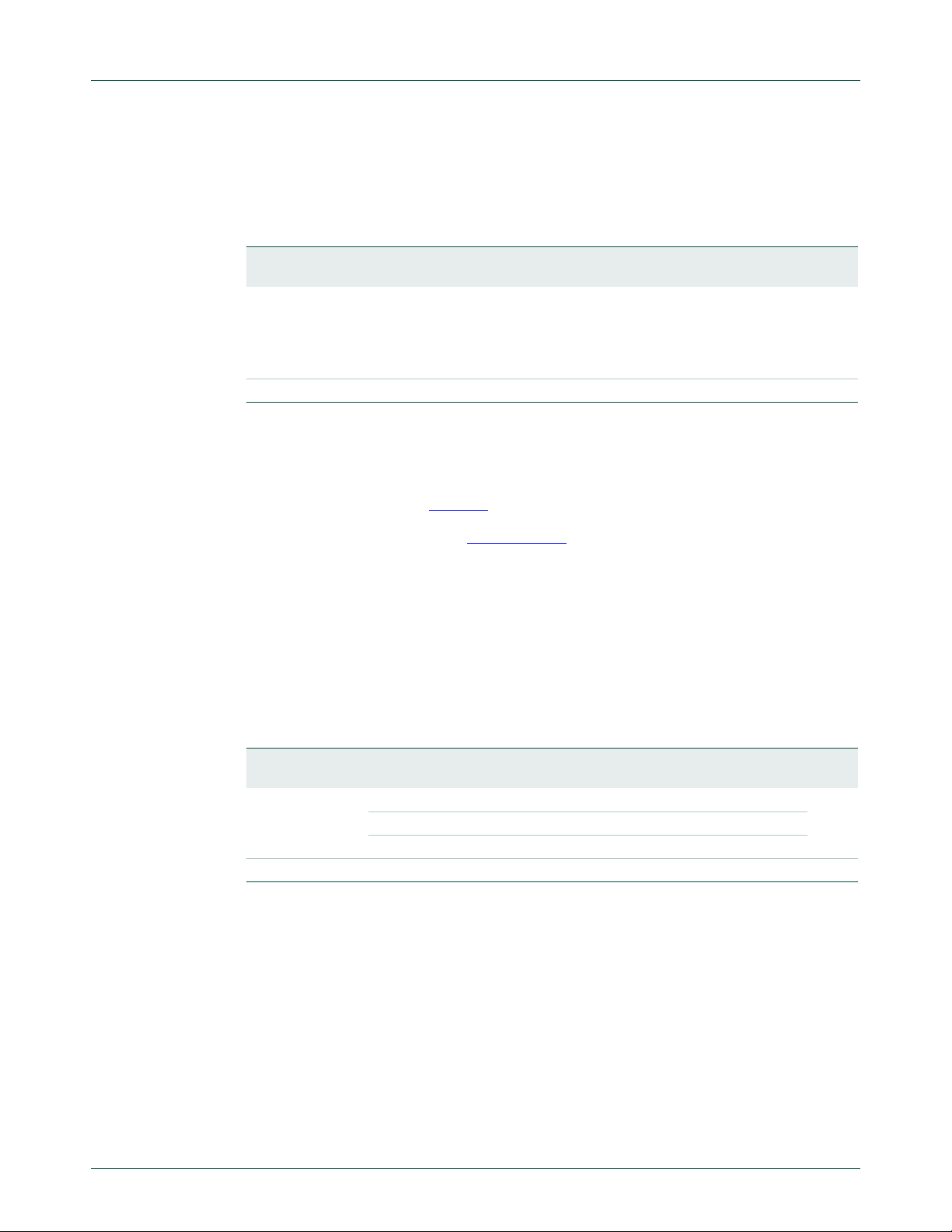

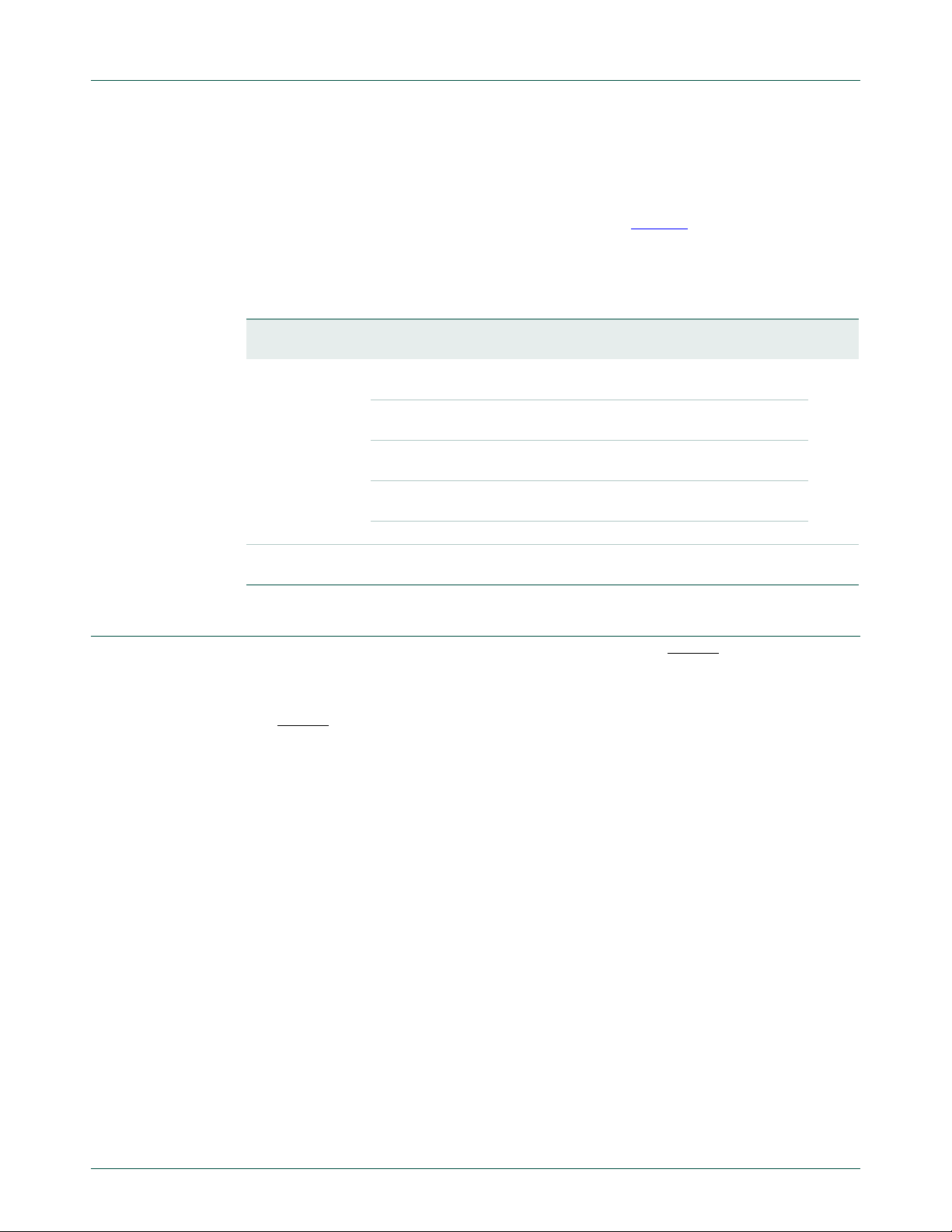

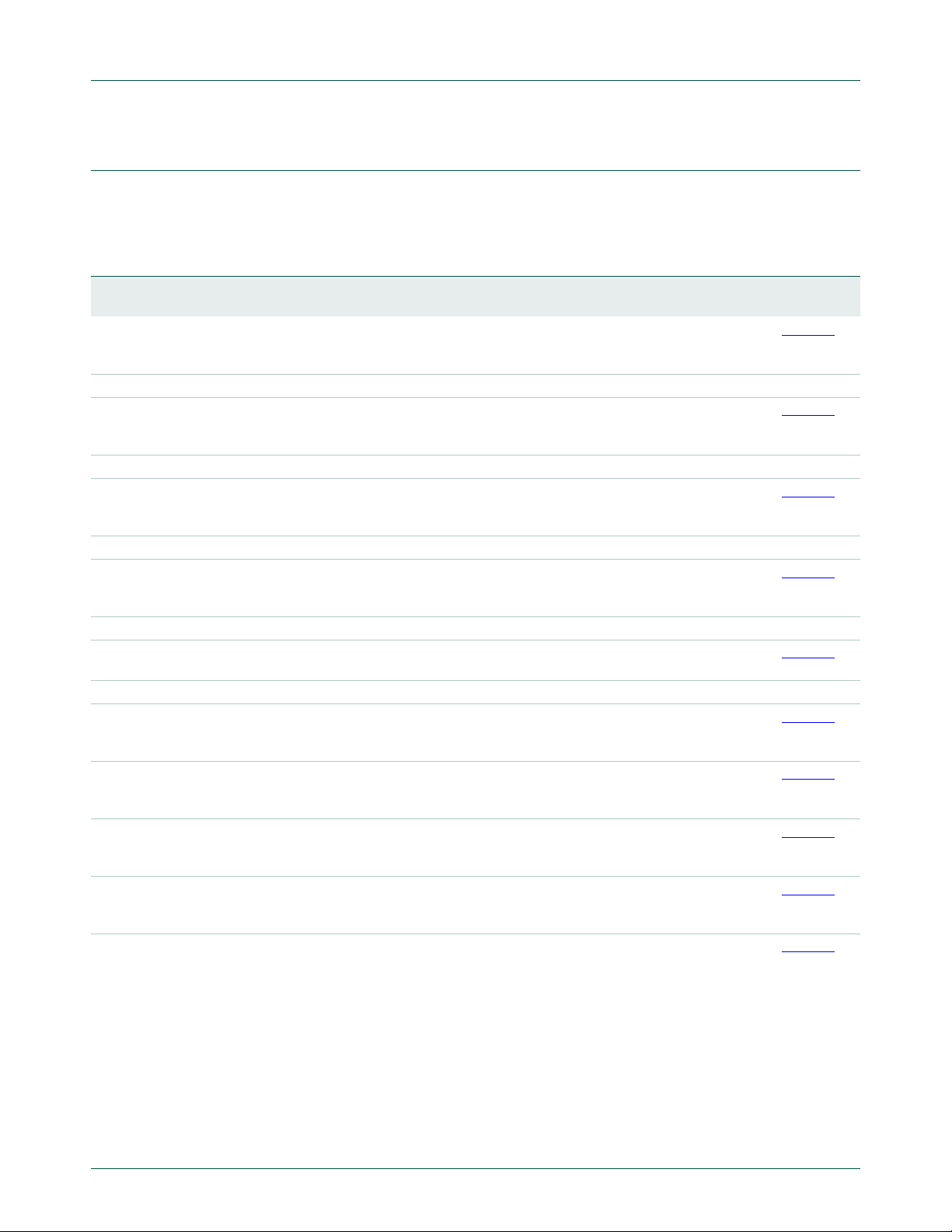

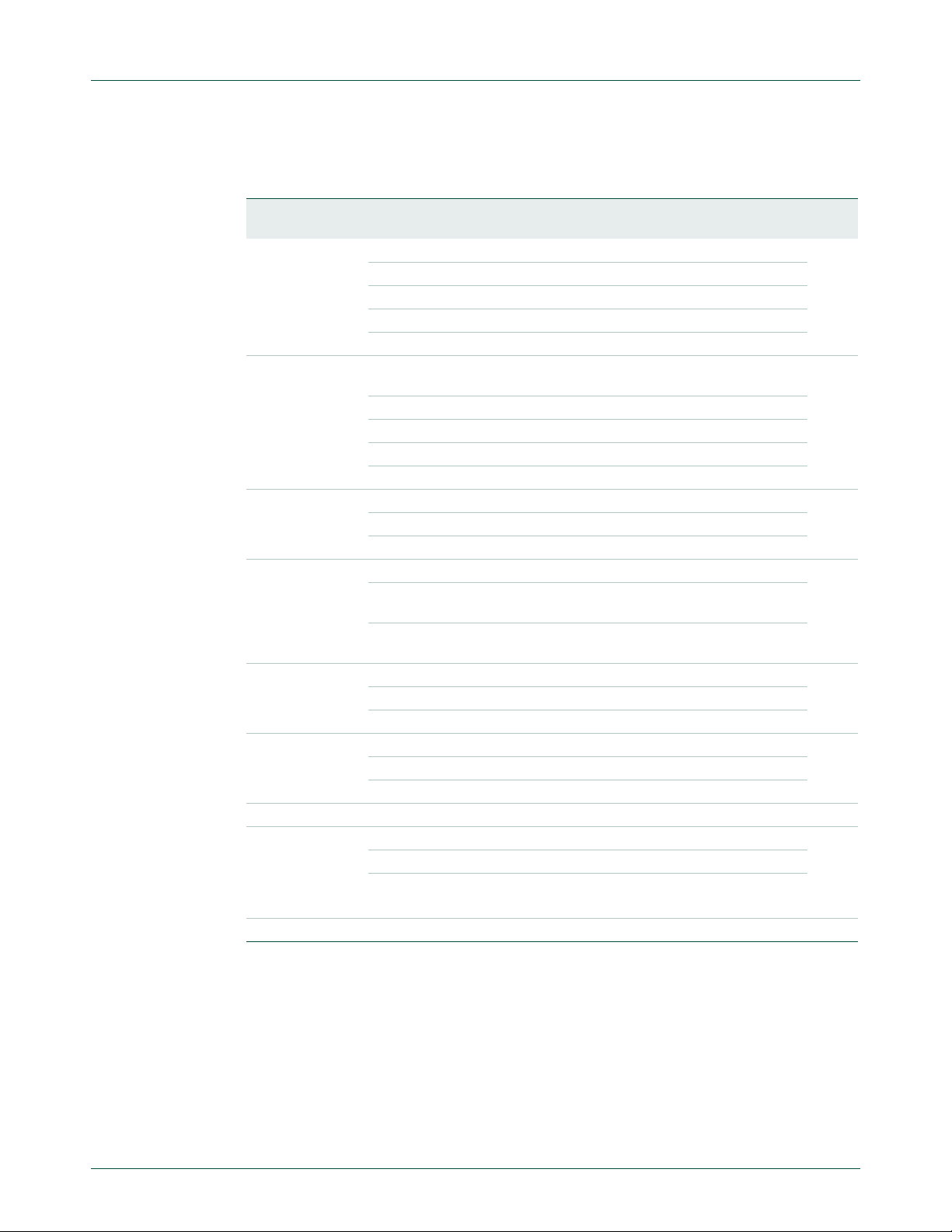

See Figure 7 for an overview of the LPC11U3x/2x/1x Clock Generation Unit (CGU).

The LPC11U3x/2x/1x include three independent oscillators. These are the system

oscillator, the Internal RC oscillator (IRC), and the W atchdog oscillator . Each oscillator can

be used for more than one purpose as required in a particular application.

direction

Pin description

pins from all available GPIO pins (see Table 40

).

Following reset, the LPC11U3x/2x/1x will operate from the Internal RC oscillator until

switched by software. This allows systems to operate without an external crystal and the

bootloader code to operate at a known frequency.

The SYSAHBCLKCTRL register gates the system clock to the various peripherals and

memories. USART and SSP have individual clock dividers to derive peripheral clocks

from the main clock.

UM10462 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2016. All rights reserved.

User manual Rev. 5.5 — 21 December 2016 19 of 523

Page 20

NXP Semiconductors

system oscillator

watchdog oscillator

IRC oscillator

USB PLL

USBPLLCLKSEL

(USB clock select)

SYSTEM CLOCK

DIVIDER

SYSAHBCLKCTRLn

(AHB clock enable)

CPU, system control,

PMU

memories,

peripheral clocks

SSP0 PERIPHERAL

CLOCK DIVIDER

SSP0

SSP1 PERIPHERAL

CLOCK DIVIDER

SSP1

USART PERIPHERAL

CLOCK DIVIDER

UART

WDT

CLKSEL

(WDT clock select)

USB 48 MHz CLOCK

DIVIDER

USB

USBUEN

(USB clock update enable)

watchdog oscillator

IRC oscillator

system oscillator

CLKOUT PIN CLOCK

DIVIDER

CLKOUT pin

CLKOUTUEN

(CLKOUT update enable)

002aaf892

system clock

SYSTEM PLL

IRC oscillator

system oscillator

IRC oscillator

watchdog oscillator

MAINCLKSEL

(main clock select)

SYSPLLCLKSEL

(system PLL clock select)

main clock

IRC oscillator

n

The main clock, and the clock outputs from the IRC, the system oscillator, and the

watchdog oscillator can be observed directly on the CLKOUT pin.

UM10462

Chapter 3: LPC11U3x/2x/1x System control block

Fig 7. LPC11U3x/2x/1x CGU block diagram

3.5 Register description

All system control block registers are on word address boundaries. Details of the registers

appear in the description of each function.

UM10462 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2016. All rights reserved.

User manual Rev. 5.5 — 21 December 2016 20 of 523

Page 21

NXP Semiconductors

In addition to the system control block registers described in Table 5, the flash access

timing register, which can be re-configured as part the system setup, is described in

Table 6

UM10462

Chapter 3: LPC11U3x/2x/1x System control block

. This register is not part of the system configuration block.

All address offsets not shown in Table 5

and Table 6 are reserved and should not be

written.

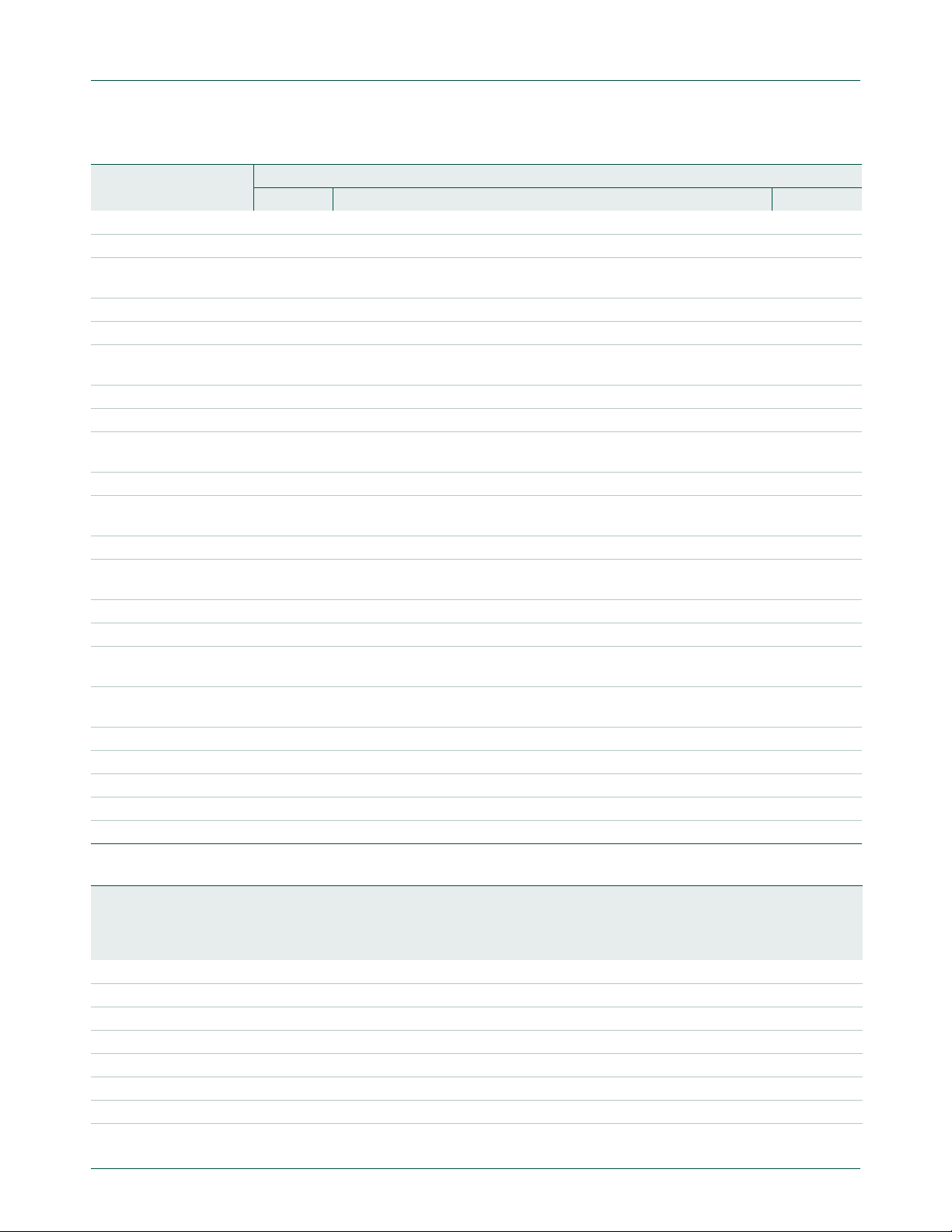

Table 5. Register overview: system control block (base address 0x4004 8000)

Name Access Offset Description Reset value Reset value

SYSMEMREMAP R/W 0x000 System memory remap 0x02 0x02 Table 7

PRESETCTRL R/W 0x004 Peripheral reset control 0 0 Table 8

SYSPLLCTRL R/W 0x008 System PLL control 0 0 Table 9

SYSPLLST AT R 0x00C System PLL status 0 0 Table 10

USBPLLCTRL R/W 0x010 USB PLL control 0 0 Table 11

USBPLLSTAT R 0x014 USB PLL status 0 0 Table 12

SYSOSCCTRL R/W 0x020 System oscillator control 0 0 Table 13

WDTOSCCTRL R/W 0x024 Watchdog oscillator control 0 0 Table 14

IRCCTRL R/W 0x028 IRC control 0x080 - Table 15

- - 0x02C Reserved - - SYSRSTSTA T R/W 0x030 System reset status register 0x3 0x3 Table 16

SYSPLLCLKSEL R/W 0x040 System PLL clock source select 0x1 0x1 Table 17

SYSPLLCLKUEN R/W 0x044 System PLL clock source update

USBPLLCLKSEL R/W 0x048 USB PLL clock source select 0 0 Table 19

USBPLLCLKUEN R/W 0x04C USB PLL clock source update enable 0 0 Table 20

MAINCLKSEL R/W 0x070 Main clock source select 0 0 Table 21

MAINCLKUEN R/W 0x074 Main clock source update enable 0x1 0x1 Table 22

SYSAHBCLKDIV R/W 0x078 System clock divider 0x1 0x1 Table 23

SYSAHBCLKCTRL R/W 0x080 System clock control 0x3F 0x0800485F Table 24

SSP0CLKDIV R/W 0x094 SSP0 clock divider 0 0x1 Table 25

UARTCLKDIV R/W 0x098 UART clock divider 0 0 Table 26

SSP1CLKDIV R/W 0x09C SSP1 clock divider 0 0 Table 27

- - 0x0A0 -

USBCLKSEL R/W 0x0C0 USB clock source select 0 0 Table 28

USBCLKUEN R/W 0x0C4 USB clock source update enable 0 0 Table 29

USBCLKDIV R/W 0x0C8 USB clock source divider 0 0x1 Table 30

- - 0x0CC Reserved - CLKOUTSEL R/W 0x0E0 CLKOUT clock source select 0 0 Table 31

CLKOUTUEN R/W 0x0E4 CLKOUT clock source update enable 0 0 Table 32

CLKOUTDIV R/W 0x0E8 CLKOUT clock divider 0 0 Table 33

PIOPORCAP0 R 0x100 POR captured PIO status 0 user dependent user

PIOPORCAP1 R 0x104 POR captured PIO status 1 user dependent user

Reference

after boot

0x1 0x1 Table 18

enable

Reserved - - -

0x0BC

Table 34

dependent

Table 35

dependent

UM10462 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2016. All rights reserved.

User manual Rev. 5.5 — 21 December 2016 21 of 523

Page 22

NXP Semiconductors

UM10462

Chapter 3: LPC11U3x/2x/1x System control block

Table 5. Register overview: system control block (base address 0x4004 8000) …continued

Name Access Offset Description Reset value Reset value

after boot

BODCTRL R/W 0x150 Brown-Out Detect 0 0 Table 36

SYSTCKCAL R/W 0x154 System tick counter calibration 0x0 0x4 Table 37

IRQLATENCY R/W 0x170 IRQ delay. Allows trade-off between

interrupt latency and determinism.

NMISRC R/W 0x174 NMI Source Control 0 0 Table 39

PINTSEL0 R/W 0x178 GPIO Pin Interrupt Select register 0 0 0 Table 40

PINTSEL1 R/W 0x17C GPIO Pin Interrupt Select register 1 0 0 Table 40

PINTSEL2 R/W 0x180 GPIO Pin Interrupt Select register 2 0 0 Table 40

PINTSEL3 R/W 0x184 GPIO Pin Interrupt Select register 3 0 0 Table 40

PINTSEL4 R/W 0x188 GPIO Pin Interrupt Select register 4 0 0 Table 40

PINTSEL5 R/W 0x18C GPIO Pin Interrupt Select register 5 0 0 Table 40

PINTSEL6 R/W 0x190 GPIO Pin Interrupt Select register 6 0 0 Table 40

PINTSEL7 R/W 0x194 GPIO Pin Interrupt Select register 7 0 0 Table 40

USBCLKCTRL R/W 0x198 USB clock control 0 0 Table 41

USBCLKST R 0x19C USB clock status 0x1 0x1 Table 42

STAR TERP0 R/W 0x204 Start logic 0 interrupt wake-up enable

register 0

STAR TERP1 R/W 0x214 Start logic 1 interrupt wake-up enable

register 1

PDSLEEPCFG R/W 0x230 Power-down states in deep-sleep

mode

PDAWAKECFG R/W 0x234 Power-down states for wake-up from

deep-sleep

PDRUNCFG R/W 0x238 Power configuration register 0xEDD0 0xEDF0 Table 47

DEVICE_ID R 0x3F4 Device ID part dependent Table 48

0x10 0x10 Table 38

00Table 43

00Table 44

0xFFFF 0xFFFF Table 45

0xEDF0 0xEDF0 Table 46

Reference

Table 6. Register overview: flash control block (base address 0x4003 C000)

Name Access Offset Description Reset value Reference

FLASHCFG R/W 0x010 Flash read access configuration - Table 49

3.5.1 System memory remap register

The system memory remap register selects whether the exception ve ctors are read from

boot ROM, flash, or SRAM. By default, the flash memory is mapped to address 0x0000

0000. When the MAP bits in the SYSM E MREMAP register are set to 0x0 or 0x1, the boot

ROM or RAM respectively are mapped to the bottom 512 bytes of the memory map

(addresses 0x0000 0000 to 0x0000 0200).

UM10462 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2016. All rights reserved.

User manual Rev. 5.5 — 21 December 2016 22 of 523

Page 23

NXP Semiconductors

Table 7. System memory remap register (SYSMEMREMAP, address 0x4004 8000) bit

Bit Symbol Value Description Reset

1:0 MAP System memory remap. Value 0x3 is reserved. 0x2

31:2 - - Reserved -

3.5.2 Peripheral reset control register

This register allows software to reset specific peripherals. A 0 in an assigned bit in this

register resets the specified peripheral. A 1 negates the reset and allows peripheral

operation.

UM10462

Chapter 3: LPC11U3x/2x/1x System control block

description

value

0x0 Boot Loader Mode. Interrupt vectors are re-mapped to Boot

ROM.

0x1 User RAM Mode. Interrupt vectors are re-mapped to Static

RAM.

0x2 User Flash Mode. Interrupt vectors are not re-mapped and

reside in Flash.

Remark: Before accessing the SSP and I2C peripherals, write a 1 to this register to

ensure that the reset signals to the SSP and I2C are de-asserted.

Table 8. Peripheral reset control register (PRESETCTRL, address 0x4004 8004) bit

description

Bit Symbol Value Description Reset

0 SSP0_RST_N SSP0 reset control 0

0 Resets the SSP0 peripheral.

1 SSP0 reset de-asserted.

1 I2C_RST_N I2C reset control 0

0 Resets the I2C peripheral.

1 I2C reset de-asserted.

2 SSP1_RST_N SSP1 reset control 0

0 Resets the SSP1 peripheral.

1 SSP1 reset de-asserted.

3 - Reserved 31:4 - - Reserved -

3.5.3 System PLL control register

This register connects and enables the system PLL and co nfigures the PLL m ultiplier and

divider values. The PLL accepts an input frequency from 10 MHz to 25 MHz from various

clock sources. The input frequency is multiplied to a higher frequency and then divided

down to provide the actual clock used by the CPU, peripherals, and memories. The PLL

can produce a clock up to the maximum allowed for the CPU.

value

UM10462 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2016. All rights reserved.

User manual Rev. 5.5 — 21 December 2016 23 of 523

Page 24

NXP Semiconductors

Table 9. Syste m PLL control register (SYSPLLCTRL, address 0x4004 8008) bit description

Bit Symbol Value Description Reset

4:0 MSEL Feedback divider value. The division value M is the

6:5 PSEL Post divider ratio P. The division ratio is 2 P. 0

31:7 - - Reserved. Do not write ones to reserved bits. -

3.5.4 System PLL status register

This register is a Read-only register and supplies the PLL lock status (see

Section 3.10.1

Table 10. System PLL status register (SYSPLLSTAT, address 0x4004 800C) bit description

Bit Symbol Value Description Reset

0 LOCK PLL lock status 0

31:1 - - Reserved -

UM10462

Chapter 3: LPC11U3x/2x/1x System control block

value

0

programmed MSEL value + 1.

00000: Division ratio M = 1

to

11111: Division ratio M = 32

0x0 P = 1

0x1 P = 2

0x2 P = 4

0x3 P = 8

).

value

0 PLL not locked

1 PLL locked

3.5.5 USB PLL control register

The USB PLL is identical to the system PLL and is used to provide a dedicated clock to

the USB block if available (see Section 3.1

This register connects and enables the USB PLL and configures the PLL multiplier and

divider values. The PLL accepts an input frequency from 10 MHz to 25 MHz from various

clock sources. The input frequency is multiplied up to a high frequency, then divided down

to provide the actual clock 48 MHz clock used by the USB subsystem.

Remark: The USB PLL must be connected to the system oscillator for correct USB

operation (see Table 19

UM10462 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2016. All rights reserved.

User manual Rev. 5.5 — 21 December 2016 24 of 523

).

).

Page 25

NXP Semiconductors

Table 11. USB PLL control register (USBPLLCTRL, address 0x4004 8010) bit

Bit Symbol Value Description Reset

4:0 MSEL Feedback divider value. The division value M is the

6:5 PSEL Post divider ratio P. The division ratio is 2 P. 0x00

31:7 - - Reserved. Do not write ones to reserved bits. 0x00

3.5.6 USB PLL status register

UM10462

Chapter 3: LPC11U3x/2x/1x System control block

description

value

0x000

programmed MSEL value + 1.

00000: Division ratio M = 1

to

11111: Division ratio M = 32

0x0 P = 1

0x1 P = 2

0x2 P = 4

0x3 P = 8

This register is a Read-only register and supplies the PLL lock status (see

Section 3.10.1

Table 12. USB PLL status register (USBPLLSTAT, ad dress 0x4004 8014) bit description

Bit Symbol Value Description Reset

0 LOCK PLL lock status 0x0

31:1 - - Reserved 0x00

).

0 PLL not locked

1 PLL locked

3.5.7 System oscillator control register

This register configures the frequency range for the system oscillator.

Table 13. System oscillator control register (SYSOSCCTRL, address 0x4004 8020) bit

description

Bit Symbol Value Description Reset

0 BYPASS Bypass system oscillator 0x0

0 Oscillator is not bypassed.

1 Bypass enabled. PLL input (sys_osc_clk) is fed

directly from the XTALIN pin bypassing the

oscillator. Use this mode when using an external

clock source instead of the crystal oscillator.

1 FREQRANGE Determines frequency range for Low-power

oscillator.

0 1 - 20 MHz frequency range.

1 15 - 25 MHz frequency range

31:2 - - Reserved 0x00

value

value

0x0

UM10462 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2016. All rights reserved.

User manual Rev. 5.5 — 21 December 2016 25 of 523

Page 26

NXP Semiconductors

3.5.8 Watchdog oscillator control register

This register configures the watchdog oscillator. The oscillator consists of an analog and a

digital part. The analog part contains the oscillator function and generates an analog clock

(Fclkana). With the digital part, the analog output clock (Fclkana) can be divided to the

required output clock frequency wdt_osc_clk. The analog output freque ncy (Fclkana) can

be adjusted with the FREQSEL bits between 600 kHz and 4.6 MHz. With the digital part

Fclkana will be divided (divider ratios = 2, 4,...,64) to wdt_osc_clk using the DIVSEL bits.

The output clock frequency of the watchdog oscillator can be calculated as

wdt_osc_clk = Fclkana/(2 (1 + DIVSEL)) = 9.4 kHz to 2.3 MHz (nominal values).

Remark: Any setting of the FREQSEL bits will yield a Fclkana value within 40% of the

listed frequency value. The watchdog oscillator is the clock source with the lowest power

consumption. If accurate timing is required, use the IRC or system oscillator.

Remark: The frequency of the watchdog oscillator is undefined after reset. The watchdog

oscillator frequency must be programmed by writing to the WDTOSCCTRL register before

using the watchdog oscillator.

Table 14. Watchdog oscillator control register (WDTOSCCTRL, address 0x4004 8024) bit

Bit Symbol Value Description Reset

4:0 DIVSEL Select divider for Fclkana.

8:5 FREQSEL Select watchdog oscillator analog output frequency

31:9 - - Reserved 0x00

UM10462

Chapter 3: LPC11U3x/2x/1x System control block

description

value

0

wdt_osc_clk = Fclkana/ (2 (1 + DIVSEL))

00000: 2 (1 + DIVSEL) = 2

00001: 2 (1 + DIVSEL) = 4

to

11111: 2 (1 + DIVSEL) = 64

0x00

(Fclkana).

0x1 0.6 MHz

0x2 1.05 MHz

0x3 1.4 MHz

0x4 1.75 MHz

0x5 2.1 MHz

0x6 2.4 MHz

0x7 2.7 MHz

0x8 3.0 MHz

0x9 3.25 MHz

0xA 3.5 MHz

0xB 3.75 MHz

0xC 4.0 MHz

0xD 4.2 MHz

0xE 4.4 MHz

0xF 4.6 MHz

UM10462 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2016. All rights reserved.

User manual Rev. 5.5 — 21 December 2016 26 of 523

Page 27

NXP Semiconductors

3.5.9 Internal resonant crystal control register

This register is used to trim the on-chip 12 MHz oscillator. The trim value is factory-preset

and written by the boot code on start-up.

Table 15. Internal resonant crystal control register (IRCCTRL, address 0x4004 8028) bit

Bit Symbol Description Reset value

7:0 TRIM Trim value 0x80 then flash will

31:8 - Reserved 0x00

3.5.10 System reset status register

If another reset signal - for example the external RESET pin - remains asserted after the

POR signal is negated, then its bit is set to detected. Write a one to clear the reset.

UM10462

Chapter 3: LPC11U3x/2x/1x System control block

description

reprogram

The reset value given in Table 16

Table 16. System reset status register (SYSRSTSTAT, address 0x4004 8030) bit description

Bit Symbol Value Description Reset

0 POR POR reset status 1

0 No POR detected

1 POR detected. Writing a one clears this reset.

1 EXTRST External reset status 1

0 No reset event detected.

1 Reset detected. Writing a one clears this reset.

2 WDT Status of the Watchdog reset 0

0 No WDT reset detected

1 WDT reset detected. Writing a one clears this reset.

3 BOD Status of the Brown-out detect reset 0

0 No BOD reset detected

1 BOD reset detected. Writing a one clears this reset.

4 SYSRST Status of the software system reset 0

0 No System reset detected

1 System reset detected. Writing a one clears this reset.

31:5 - - Reserved -

applies to the POR reset.

value

3.5.11 System PLL clock source select register

This register selects the clock source for the system PLL. The SYSPLLCLKUEN register

(see Section 3.5.12

UM10462 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2016. All rights reserved.

User manual Rev. 5.5 — 21 December 2016 27 of 523

) must be toggled from LOW to HIGH for the update to take effect.

Page 28

NXP Semiconductors

T able 17. System PLL clock source select register (SYSPLLCLKSEL, address 0x4004 8040)

Bit Symbol Value Description Reset

1:0 SEL System PLL clock source 1

31:2 - - Reserved -

UM10462

Chapter 3: LPC11U3x/2x/1x System control block

bit description

value

0x0 IRC

0x1 Crystal Oscillator (SYSOSC)

0x2 Reserved

0x3 Reserved

UM10462 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2016. All rights reserved.

User manual Rev. 5.5 — 21 December 2016 28 of 523

Page 29

NXP Semiconductors

3.5.12 System PLL clock source update register

This register updates the clock source of the system PLL with the new input clock after the

SYSPLLCLKSEL register has been written to. In order for the update to take effect, first

write a zero to the SYSPLLUEN register and then write a one to SYSPLLUEN.

Table 18. System PLL clock source update enable register (SYSPLLCLKUEN, address

Bit Symbol Value Description Reset value

0 ENA Enable system PLL clock source update 1

31:1 - - Reserved -

3.5.13 USB PLL clock source select register

This register selects the clock source for the dedicated USB PLL. The USBPLLCLKUEN

register (see Section 3.5.14

effect.

UM10462

Chapter 3: LPC11U3x/2x/1x System control block

0x4004 8044) bit description

0 No change

1 Update clock source

) must be toggled from LOW to HIGH for the update to take

Remark: When switching clock sources, both clocks must be running before the clock

source is updated in the USBPLLCLKUEN register. For USB operation, the clock source

must be switched from IRC to system oscillator with both the IRC and the system

oscillator running. After the switch, the IRC can be turned off.

T able 19. USB PLL clock source select register (USBPLLCLKSEL, address 0x4004 8048) bit

description

Bit Symbol Value Description Reset

1:0 SEL USB PLL clock source 0x00

0x0 IRC. The USB PLL clock source must be switched to system

oscillator for correct full-speed USB operation. The IRC is

suitable for low-speed USB operation.

0x1 System oscillator

0x2 Reserved

0x3 Reserved

31:2 - - Reserved 0x00

3.5.14 USB PLL clock source update enable register

This register updates the clock source of the USB PLL with the new input clock after the

USBPLLCLKSEL register has been written to. In order for the update to take effect at the

USB PLL input, first write a zero to the USBPLLUEN register and then write a one to

USBPLLUEN.

value

Remark: The system oscillator must be selected in the USBPLLCLKSEL register in order

to use the USB PLL, and this register must be toggled to update the USB PLL clock with

the system oscillator.

Remark: When switching clock sources, both clocks must be running before the clock

source is updated.

UM10462 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2016. All rights reserved.

User manual Rev. 5.5 — 21 December 2016 29 of 523

Page 30

NXP Semiconductors

T able 20. USB PLL clock source update enable register (USBPLLCLKUEN, address 0x4004

Bit Symbol Value Description Reset value

0 ENA Enable USB PLL clock source update 0x0

31:1 - - Reserved 0x00

3.5.15 Main clock source select register

This register selects the main system clock, which can be the system PLL (sys_pllclkout),

or the watchdog oscillator, or the IRC oscillator. The main system clock clocks the core,

the peripherals, and the memories.

UM10462

Chapter 3: LPC11U3x/2x/1x System control block

804C) bit description

0 No change

1 Update clock source

Bit 0 of the MAINCLKUEN register (see Section 3.5.16

the update to take effect.

Table 21. Main clock source select register (MAINCLKSEL, address 0x4004 8070) bit

description

Bit Symbol Value Description Reset value

1:0 SEL Clock source for main clock 0

0x0 IRC Oscillator

0x1 PLL input

0x2 Watchdog oscillator

0x3 PLL output

31:2 - - Reserved -

3.5.16 Main clock source update enable register

This register updates the clock source of the main clock with the new input clock after the

MAINCLKSEL register has been written to. In order for the update to take effect, first write

a zero to bit 0 of this register, then write a one.

Table 22. Main clock source update enable register (MAINCLKUEN, address 0x4004 8074)

bit description

Bit Symbol Value Description Reset value

0 ENA Enable main clock source update 1

0 No change

1 Update clock source

31:1 - - Reserved -

) must be toggled from 0 to 1 for

3.5.17 System clock divider register

This register controls how the main clock is divided to provide the system clock to the

core, memories, and the peripherals. The system clock can be shut down completely by

setting the DIV field to zero.

UM10462 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2016. All rights reserved.

User manual Rev. 5.5 — 21 December 2016 30 of 523

Page 31

NXP Semiconductors

Table 23. System clock divider register (SYSAHBCLKDIV, address 0x4004 8078) bit

Bit Symbol Description Reset

7:0 DIV System AHB clock divider values

31:8 - Reserved -

3.5.18 System clock control register

The SYSAHBCLKCTRL register enables the clocks to individual system and peripheral

blocks. The system clock (bit 0) provides the clock for the AHB, the APB br idge , th e ARM

Cortex-M0, the Syscon block, and the PMU. This clock cannot be disabled.

Table 24. System clock control register (SYSAHBCLKCTRL, address 0x4004 8080) bit

Bit Symbol Value Description Reset

0 SYS Enables the clock for the AHB, the APB bridge, the

1 ROM Enables clock for ROM. 1

2 RAM0 Enables clock for Main SRAM0. 1

3 FLASHREG Enables clock for flash register interface. 1

4 FLASHARRAY Enables clock for flash array access. 1

5 I2C Enables clock for I2C. 1

6 GPIO Enables clock for GPIO port registers. 0

7 CT16B0 Enables clock for 16-bit counter/timer 0. 0

UM10462

Chapter 3: LPC11U3x/2x/1x System control block

description

value

0x1

0: System clock disabled.

1: Divide by 1.

to

255: Divide by 255.

description

value

1

Cortex-M0 FCLK and HCLK, SysCon, and the PMU.

This bit is read only and always reads as 1.

0 Reserved

1 Enable

0 Disable

1 Enable

0 Disable

1 Enable

0 Disable

1 Enable

0 Disable

1 Enable

0 Disable

1 Enable

0 Disable

1 Enable

0 Disable

1 Enable

UM10462 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2016. All rights reserved.

User manual Rev. 5.5 — 21 December 2016 31 of 523

Page 32

NXP Semiconductors

Table 24. System clock control register (SYSAHBCLKCTRL, address 0x4004 8080) bit

Bit Symbol Value Description Reset

8 CT16B1 Enables clock for 16-bit counter/timer 1. 0

9 CT32B0 Enables clock for 32-bit counter/timer 0. 0

10 CT32B1 Enables clock for 32-bit counter/timer 1.

11 SSP0 Enables clock for SSP0. 0

12 USART Enables clock for UART.

13 ADC Enables clock for ADC. 0

14 USB Enables clock to the USB register interface. 0

15 WWDT Enables clock for WWDT. 0

16 IOCON Enables clock for I/O configuration block. 0

17 - Reserved 0

18 SSP1 Enables clock for SSP1. 0

19 PINT Enables clock to GPIO Pin interrupts register

22:20 - Reserved 23 GROUP0INT Enables clock to GPIO GROUP0 interrupt register

description

UM10462

Chapter 3: LPC11U3x/2x/1x System control block

…continued

value

0 Disable

1 Enable

0 Disable

1 Enable

0 Disable

1 Enable

0 Disable

1 Enable

0 Disable

1 Enable

0 Disable

1 Enable

0 Disable

1 Enable

0 Disable

1 Enable

0 Disable

1 Enable

0 Disable

1 Enable

0

interface.

0 Disable

1 Enable

0

interface.

0 Disable

1 Enable

UM10462 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2016. All rights reserved.

User manual Rev. 5.5 — 21 December 2016 32 of 523

Page 33

NXP Semiconductors

Table 24. System clock control register (SYSAHBCLKCTRL, address 0x4004 8080) bit

Bit Symbol Value Description Reset

24 GROUP1INT Enables clock to GPIO GROUP1 interrupt register

25 - - Reserved 26 RAM1 Enables SRAM1 block at address 0x2000 0000. See

27 USBRAM Enables USB SRAM block at address 0x2000 4000. 0

31:28 - - Reserved -

description

…continued

0 Disable

1 Enable

0 Disable

1 Enable

0 Disable

1 Enable

UM10462

Chapter 3: LPC11U3x/2x/1x System control block

interface.

Section 3.1

for availability of this bit.

value

0

0

3.5.19 SSP0 clock divider register

This register configures the SSP0 peripheral clock SPI0_PCLK. SPI0_PCLK can be shut

down by setting the DIV field to zero.

Table 25. SSP0 clock divider register (SSP0CLKDIV, address 0x4004 8094) bit description

Bit Symbol Description Reset

7:0 DIV SPI0_PCLK clock divider values.

0: System clock disabled.

1: Divide by 1.

to

255: Divide by 255.

31:8 - Reserved -

3.5.20 USART clock divider register

This register configures the USART peripheral clo ck UART_PCLK. The UAR T_PCLK can

be shut down by setting the DIV field to zero.

T able 26. USART clock divider register (UARTCLKDIV, address 0x4004 8098) bit description

Bit Symbol Description Reset

7:0 DIV UART_PCLK clock divider values

0: Disable UART_PCLK.

1: Divide by 1.

to

255: Divide by 255.

31:8 - Reserved -

value

0

value

0

UM10462 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2016. All rights reserved.

User manual Rev. 5.5 — 21 December 2016 33 of 523

Page 34

NXP Semiconductors

3.5.21 SSP1 clock divider register

This register configures the SSP1 peripheral clock SSP1_PCLK. The SSP1_PCLK can be

shut down by setting the DIV bits to 0x0.

Table 27. SPI1 clock divider register (SSP1CLKDIV, address 0x4004 809C) bit description

Bit Symbol Description Reset

7:0 DIV SSP1_PCLK clock divider values

31:8 - Reserved 0x00

3.5.22 USB clock source select register

This register selects the clock source for the USB usb_clk. The clock source can be either

the USB PLL output or the main clock, and the clock can be further divided by the

USBCLKDIV register (see Table 30

UM10462

Chapter 3: LPC11U3x/2x/1x System control block

value

0x00

0: Disable SSP1_PCLK.

1: Divide by 1.

to

255: Divide by 255.

) to obtain a 48 MHz clock.

The USBCLKUEN register (see Section 3.5.23

) must be toggled from LOW to HIGH for

the update to take effect.

Remark: When switching clock sources, both clocks must be running before the clock

source is updated. The default clock source for the USB controller is the USB PLL output.

For switching the clock source to the main clock, ensure that the system PLL and the USB

PLL are running to make both clock sources available for switching. The main clock must

be set to 48 MHz and configured with the main PLL and the system oscillator. After the

switch, the USB PLL can be turned off.

Table 28. USB clock source select register (USBCLKSEL, address 0x4004 80C0) bit

description

Bit Symbol Value Description Reset

1:0 SEL USB clock source. Values 0x2 and 0x3 are reserved. 0x00

0x0 USB PLL out

0x1 Main clock

31:2 - - Reserved 0x00

3.5.23 USB clock source update enable register

This register updates the clock source of the USB with the new input clock after the

USBCLKSEL register has been written to. In order for the update to take effect, first write

a zero to the USBCLKUEN register and then write a one to USBCLKUEN.

value

Remark: When switching clock sources, both clocks must be running before the clock

source is updated.

UM10462 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2016. All rights reserved.

User manual Rev. 5.5 — 21 December 2016 34 of 523

Page 35

NXP Semiconductors

T able 29. USB clock source update enable register (USBCLKUEN, address 0x4004 80C4) bit

Bit Symbol Value Description Reset value

0 ENA Enable USB clock source update 0x0

31:1 - - Reserved 0x00

3.5.24 USB clock divider register

This register allows the USB clock usb_clk to be divided to 48 MHz. The usb_clk can be

shut down by setting the DIV bits to 0x0.

Table 30. USB clock divider register (USBCLKDIV, address 0x4004 80C8) bit description

Bit Symbol Description Reset value

7:0 DIV USB clock divider values

31:8 - Reserved 0x00

UM10462

Chapter 3: LPC11U3x/2x/1x System control block

description

0 No change

1 Update clock source

0x01

0: Disable USB clock.

1: Divide by 1.

to

255: Divide by 255.

3.5.25 CLKOUT clock source select register

This register selects the signal visible on the CLKOUT pin. Any oscillator or the main clock

can be selected.

Bit 0 of the CLKOUTUEN register (see Section 3.5.26

) must be toggled from 0 to 1 for the

update to take effect.

Table 31. CLKOUT clock source select register (CLKOUTSEL, address 0x4004 80E0) bit

description

Bit Symbol Value Description Reset

1:0 SEL CLKOUT clock source 0

0x0 IRC oscillator

0x1 Crystal oscillator (SYSOSC)

0x2 LF oscillator (watchdog oscillator)

0x3 Main clock

31:2 - - Reserved 0

3.5.26 CLKOUT clock source update enable register

This register updates the clock source of the CLKOUT pin with the new clock after the

CLKOUTSEL register has been written to. In order for the update to t ake effect at the input

of the CLKOUT pin, first write a zero to bit 0 of this register, then write a one.

value

UM10462 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2016. All rights reserved.

User manual Rev. 5.5 — 21 December 2016 35 of 523

Page 36

NXP Semiconductors

Table 32. CLKOUT clock source update enable register (CLKOUTUEN, address 0x4004

Bit Symbol Value Description Reset value

0 ENA Enable CLKOUT clock source update 0

31:1 - - Reserved -

3.5.27 CLKOUT clock divider register

This register determines the divider value for the signal on the CLKOUT pin.

Table 33. CLKOUT clock divider registers (CLKOUTDIV, address 0x4004 80E8) bit

Bit Symbol Description Reset

7:0 DIV CLKOUT clock divider values

31:8 - Reserved -

UM10462

Chapter 3: LPC11U3x/2x/1x System control block

80E4) bit description

0 No change

1 Update clock source

description

value

0

0: Disable CLKOUT clock divider.

1: Divide by 1.

to

255: Divide by 255.

3.5.28 POR captured PIO status register 0

The PIOPORCAP0 register captures the state of GPIO port 0 at power-on-r eset. Each bit

represents the reset state of one GPIO pin. This register is a read- on ly status register.

Table 34. POR captured PIO status register 0 (PIOPORCAP0, address 0x4004 8100) bit

description

Bit Symbol Description Reset value

23:0 PIOSTAT State of PIO0_23 through PIO0_0 at power-on reset Implementation

31:24 - Reserved. -

3.5.29 POR captured PIO status register 1

The PIOPORCAP1 register captures the state of GPIO port 1 at power-on-r eset. Each bit

represents the reset state of one GPIO pin. This register is a read- on ly status register.

Table 35. POR captured PIO status register 1 (PIOPORCAP1, address 0x4004 8104) bit

description

Bit Symbol Description Reset value

31:0 PIOSTAT State of PIO1_31 through PIO1_0 at power-on reset Implementation

3.5.30 BOD control register

dependent

dependent

The BOD control register selects up to four separate threshold values for sending a BOD

interrupt to the NVIC and for forced reset. Reset and interrupt threshold values listed in

Table 36

UM10462 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2016. All rights reserved.

User manual Rev. 5.5 — 21 December 2016 36 of 523

are typical values.

Page 37

NXP Semiconductors

Both the BOD interrupt and the BOD reset, depending on the value of bit BODRSTENA in

this register, can wake-up the chip from Sl eep, Deep-sleep, and Power -down modes. See

Section 3.9

Table 36. BOD control register (BODCTRL, address 0x4004 8150) bit description

Bit Symbol Value Description Reset

1:0 BODRSTLEV BOD reset level 0

3:2 BODINTVAL BOD interrupt level 0

4 BODRSTENA BOD reset enable 0

31:5 - - Reserved 0x00

UM10462

Chapter 3: LPC11U3x/2x/1x System control block

.

value

0x0 Level 0: The reset assertion threshold voltage is 1.46 V; the