Page 1

UM10429

LPC1102 User manual

Rev. 1 — 20 October 2010 User manual

Document information

Info Content

Keywords ARM Cortex-M0, LPC1102, LPC1102UK

Abstract LPC1102 User manual

Page 2

NXP Semiconductors

UM10429

LPC1102 UM

Revision history

Rev Date Description

1 20101020 LPC1102 User manual

Contact information

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: salesaddresses@nxp.com

UM10429 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

User manual Rev. 1 — 20 October 2010 2 of 258

Page 3

1.1 Introduction

1.2 Features

UM10429

Chapter 1: LPC1102 Introductory information

Rev. 1 — 20 October 2010 User manual

The LPC1102 is an ARM Cortex-M0 based, low-cost 32-bit MCU, designed for 8/16-bit

microcontroller applications, offering performance, low power, simple instruction set and

memory addressing together with reduced code size compared to existing 8/16-bit

architectures.

The LPC1102 operates at CPU frequencies of up to 50 MHz.

The peripheral complement of the LPC1102 includes 32 kB of flash memory, 8 kB of data

memory, one RS-485/EIA-485 UART, one SPI interface with SSP features, four general

purpose counter/timers, a 10-bit ADC, and 11 general purpose I/O pins.

• System:

– ARM Cortex-M0 processor, running at frequencies of up to 50 MHz.

– ARM Cortex -M 0 bu ilt- in Ne ste d Vectored Interrupt Controller (NVIC).

– Serial Wire Debug.

– System tick timer.

• Memory:

– 32 kB on-chip flash programming memory.

– 8 kB SRAM.

– In-Application Programming (IAP) and In-System Programming (ISP) support via

on-chip bootloader software.

• Digital peripherals:

– 11 General Purpose I/O (GPIO) pins with configurable pull-up/pull-down resistors.

– GPIO pins can be used as edge and level sensitive interrupt sources.

– Four general purpose counter/timers with a total of one capture input and nine

match outputs.

– Programmable WatchDog Timer (WDT).

• Analog peripherals:

– 10-bit ADC with input multiplexing among five pins.

UM10429 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

User manual Rev. 1 — 20 October 2010 3 of 258

Page 4

NXP Semiconductors

• Serial interfaces:

• Clock generation:

• Power control:

• Unique device serial number for identification.

• Single 3.3 V power supply (1.8 V to 3.6 V).

• Available as WLCSP16 package.

UM10429

Chapter 1: LPC11 02 Introductory information

– UART with fractional baud rate generation, internal FIFO, and RS-485 support.

– One SPI controller with SSP features and with FIFO and multi-protocol capabilities.

– 12 MHz internal RC oscillator trimmed to 1% accuracy that can optionally be used

as a system clock.

– Programmable watchdog oscillator with a frequency range of 7.8 kHz to 1.8 MHz.

– PLL allows CPU operation up to the maximum CPU rate without the need for a

high-frequency crystal. May be run from an external clock or the internal RC

oscillator.

– Clock output function with divider that can reflect the external clock, IRC clo ck,

CPU clock, and the Watchdog clock.

– Integrated PMU (Power Management Unit) to minimize power consumption dur ing

Sleep and Deep-sleep modes.

– Power profiles residing in boot ROM allowing to optimize performance and

minimize power consumption for any give n application th rough one simple fu nction

call.

– Two reduced power modes: Sleep and Deep-sleep modes.

– Processor wake-up from Deep-sleep mode via a dedicated start logic using up to

six of the functional pins.

– Power-On Reset (POR).

– Brownout detect with four separate thresholds for interrupt and forced reset.

1.3 Ordering information

Table 1. Ordering information

Type number Package

LPC1102UK WLCSP16 wafer level chip-size package; 16 bumps; 2.17 × 2.32 × 0.6 mm -

UM10429 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

User manual Rev. 1 — 20 October 2010 4 of 258

Name Description Version

Table 2. Ordering options

Type number Flash Total

SRAM

LPC1102UK 32 kB 8 kB 1 - 1 5 WLCSP16

UART I2C/

Fm+

SPI ADC

channels

Package

Page 5

NXP Semiconductors

SRAM

8 kB

ARM

CORTEX-M0

TEST/DEBUG

INTERFACE

FLASH

32 kB

HIGH-SPEED

GPIO

AHB TO APB

BRIDGE

CLOCK

GENERATION,

POWER CONTROL,

SYSTEM

FUNCTIONS

XTALIN

RESET

clocks and

controls

SWD

LPC1102

002aaf524

slave

slave

slave slave

ROM

slave

AHB-LITE BUS

GPIO port

PIO0/1

IRC

POR

SPI

10-bit ADC

UART

32-bit COUNTER/TIMER 0

WDT

IOCONFIG

CT32B0_MAT[3,1,0]

AD[4:0]

RXD

TXD

SYSTEM CONTROL

PMU

32-bit COUNTER/TIMER 1

CT32B1_MAT[2:0]

CT32B1_CAP0

16-bit COUNTER/TIMER 1

16-bit COUNTER/TIMER 0

CT16B0_MAT[2:0]

SCK, MISO,

MOSI

system bus

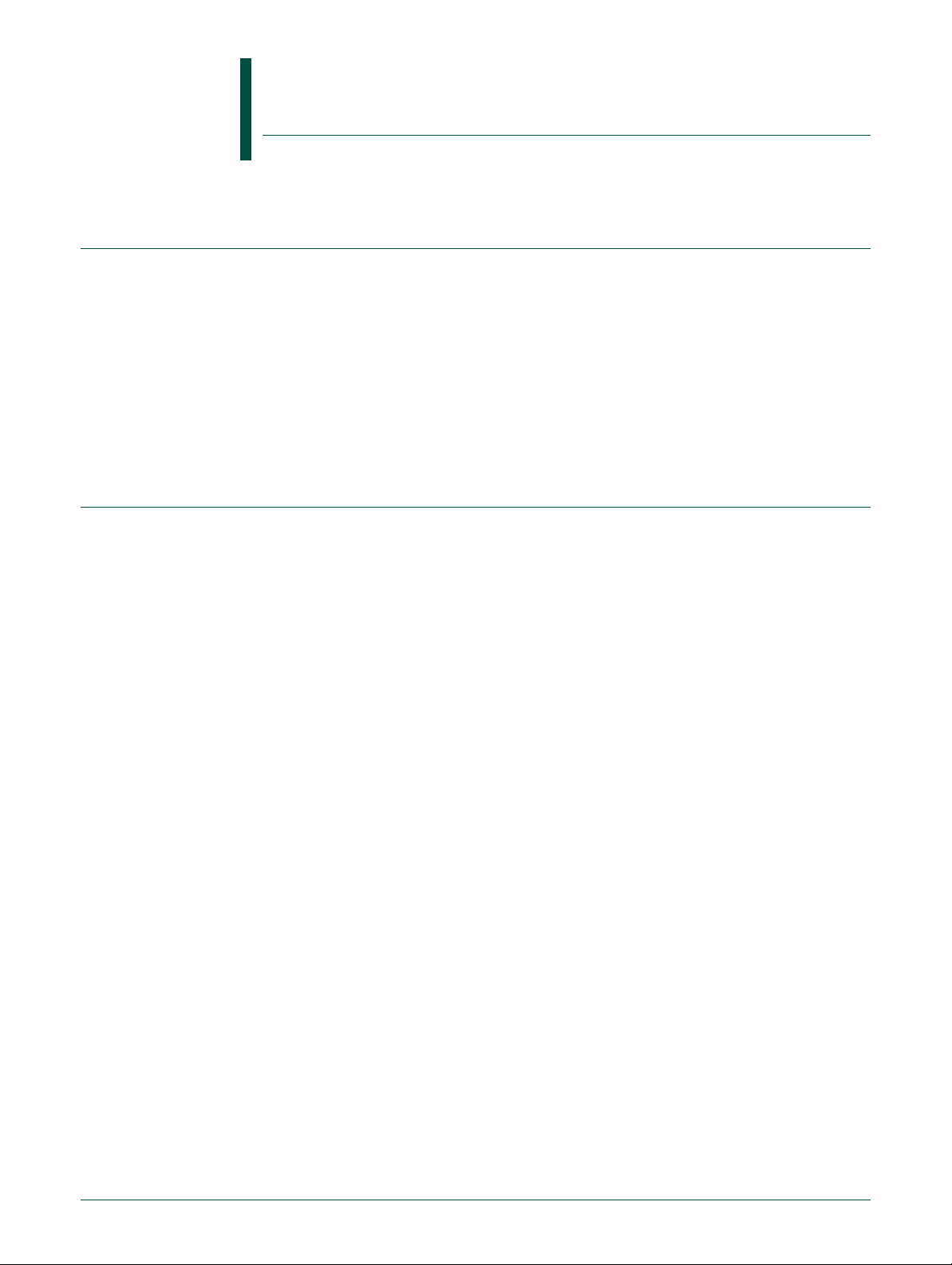

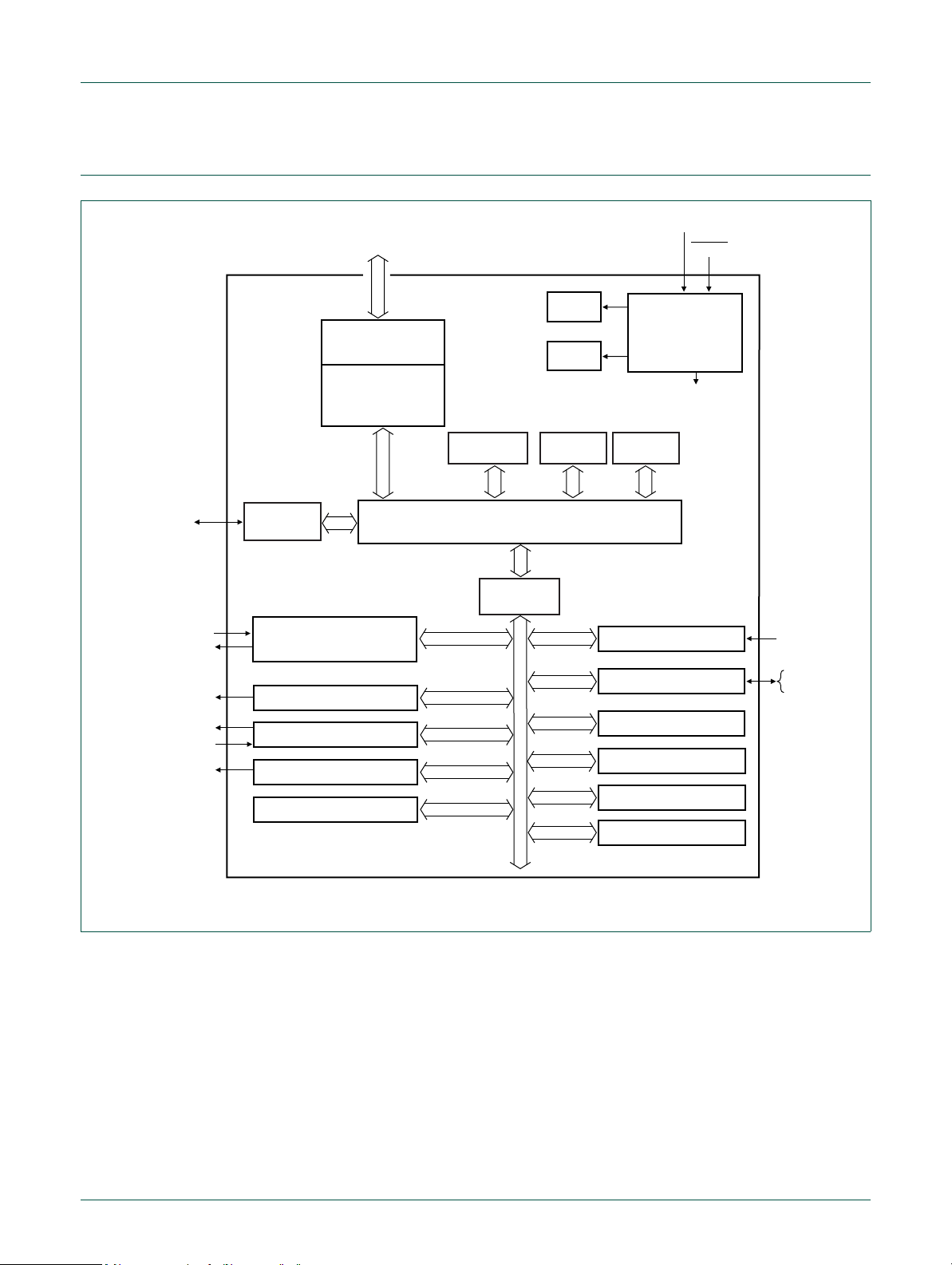

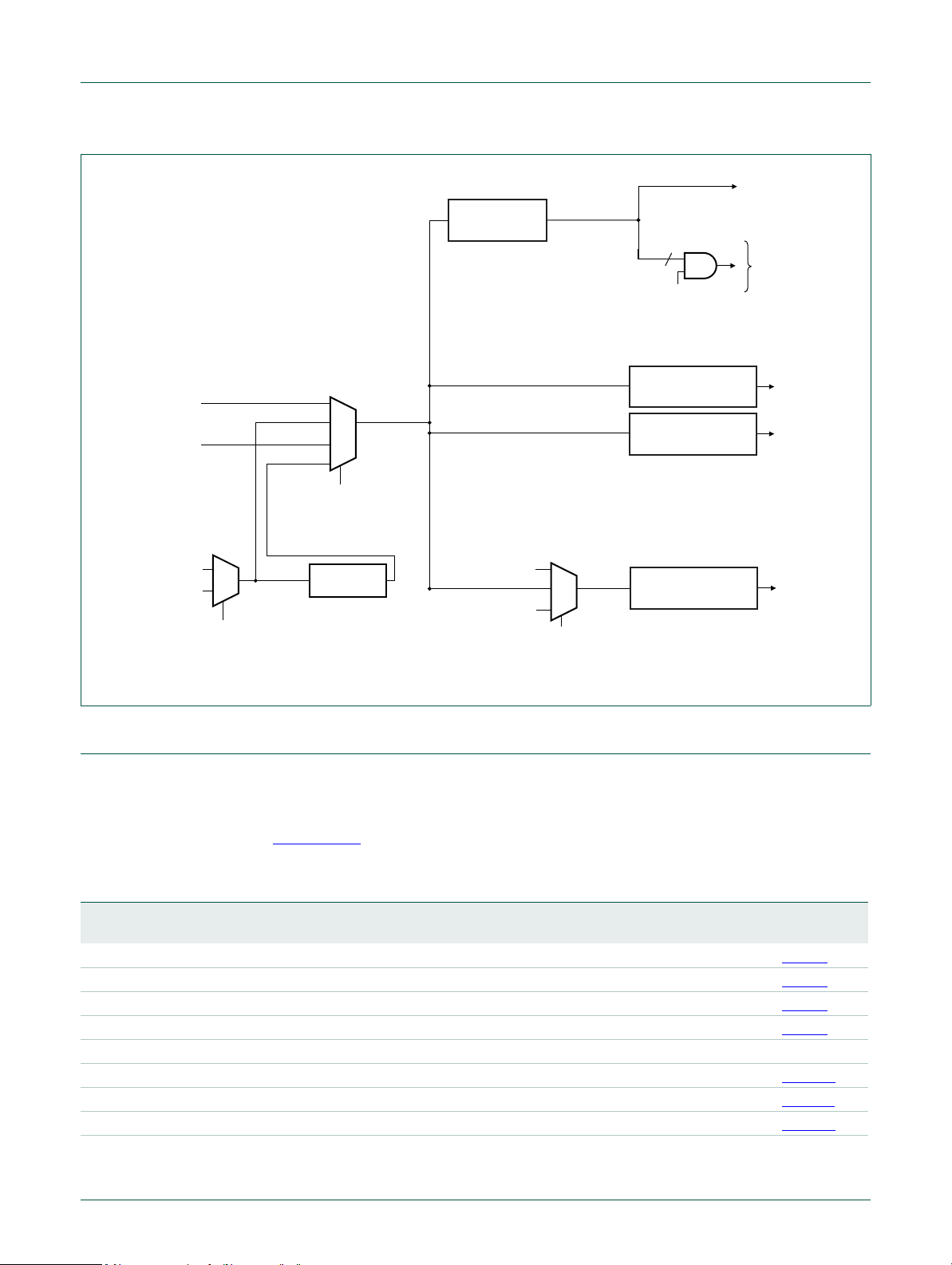

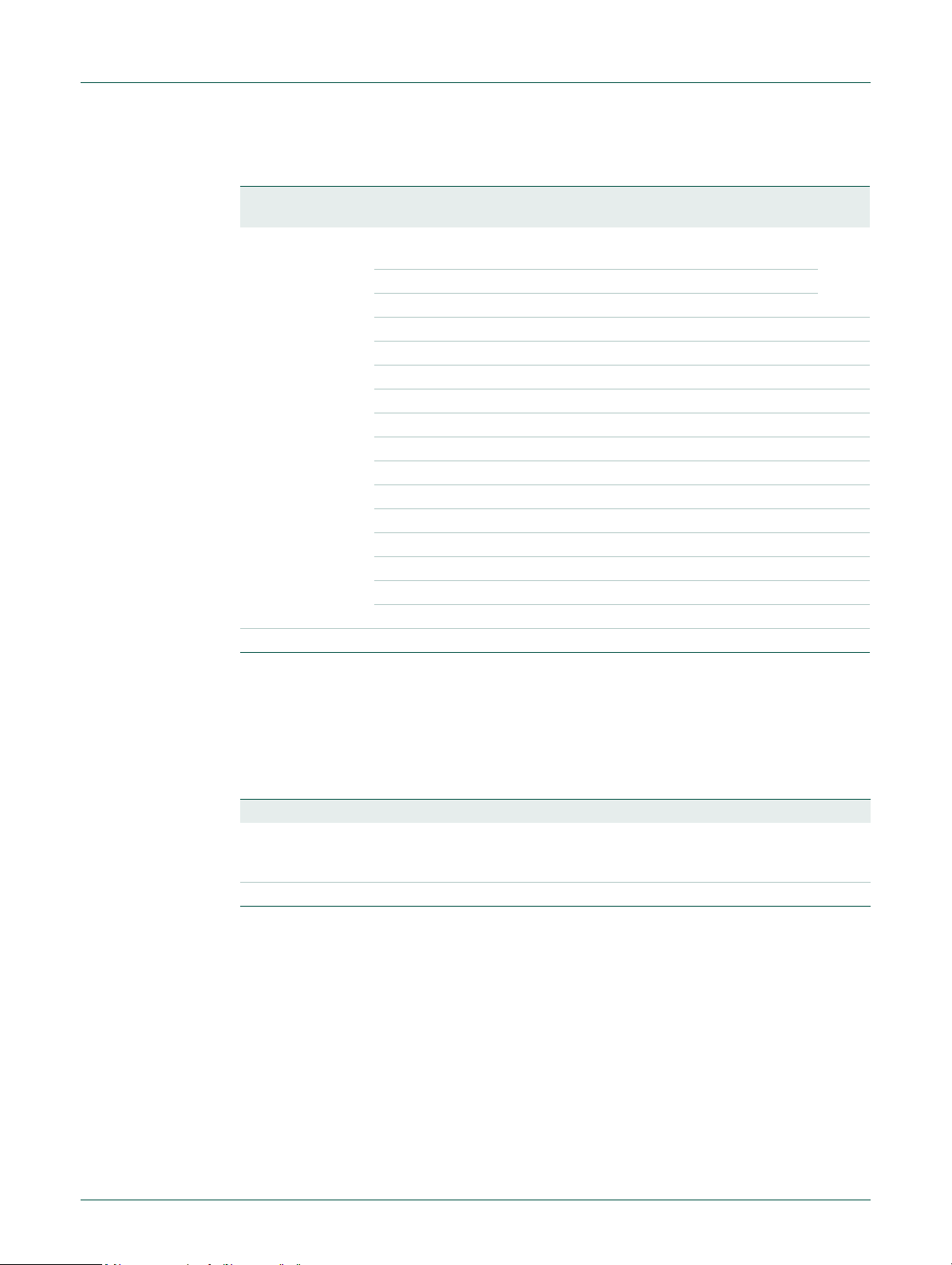

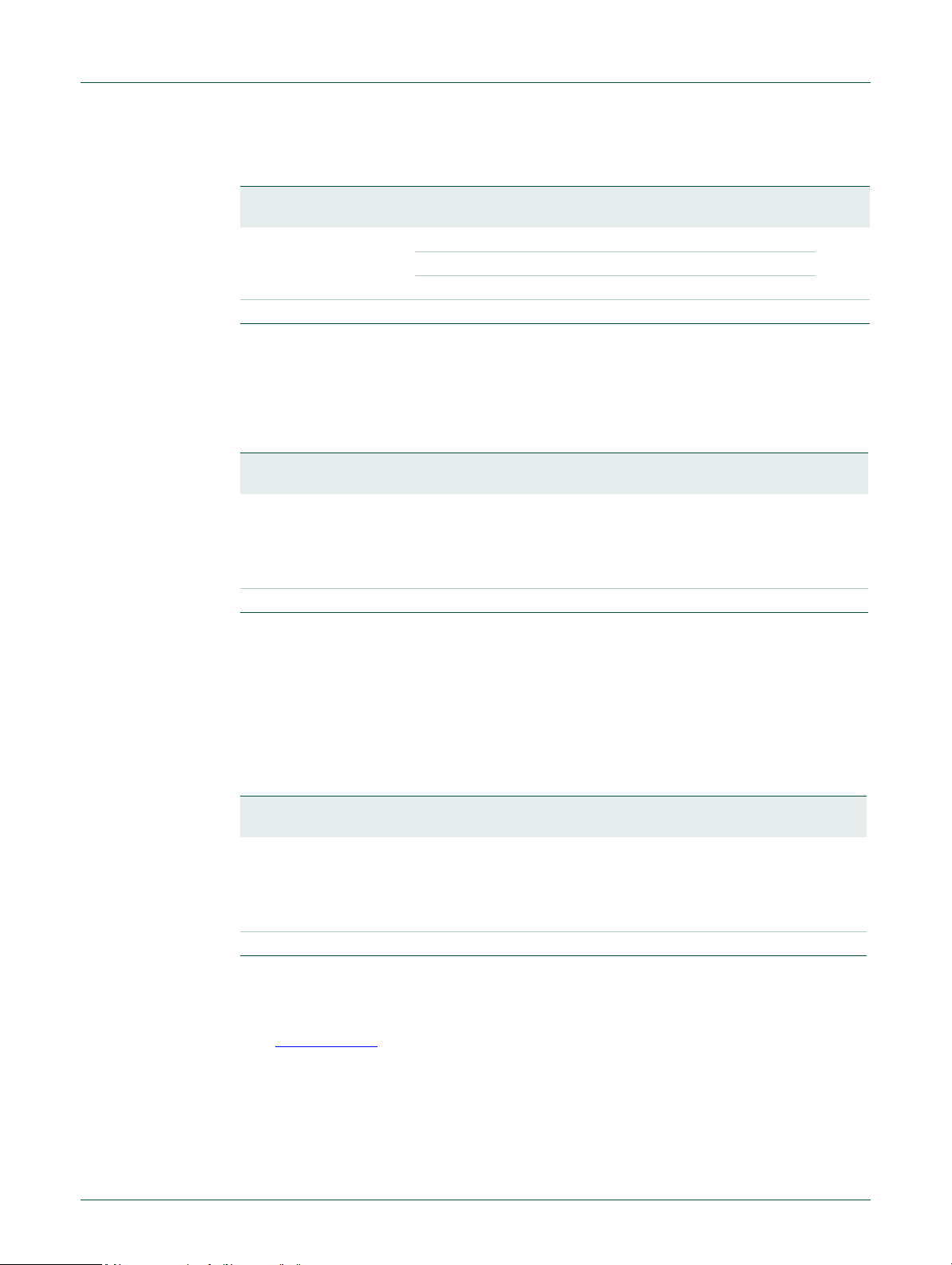

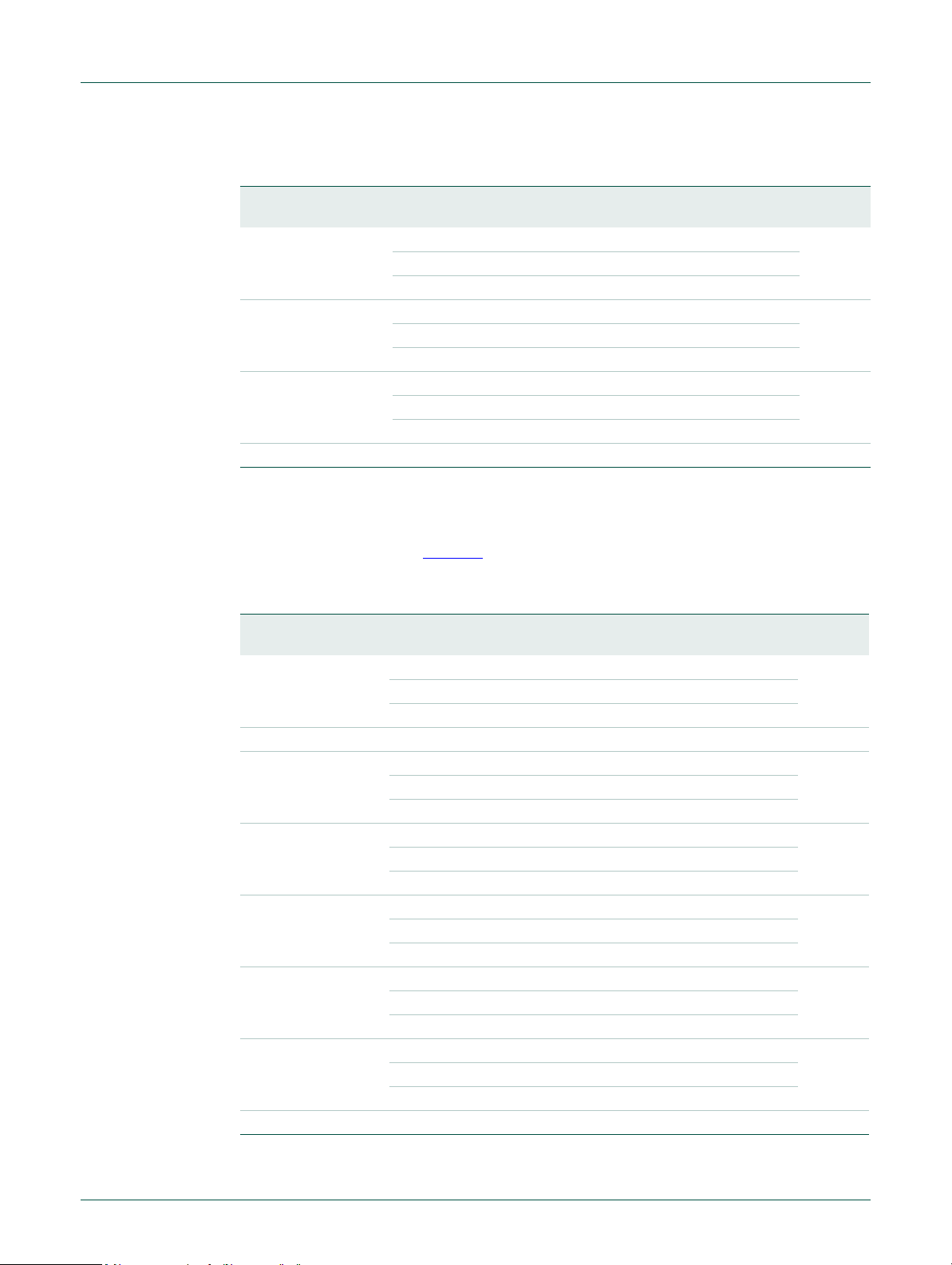

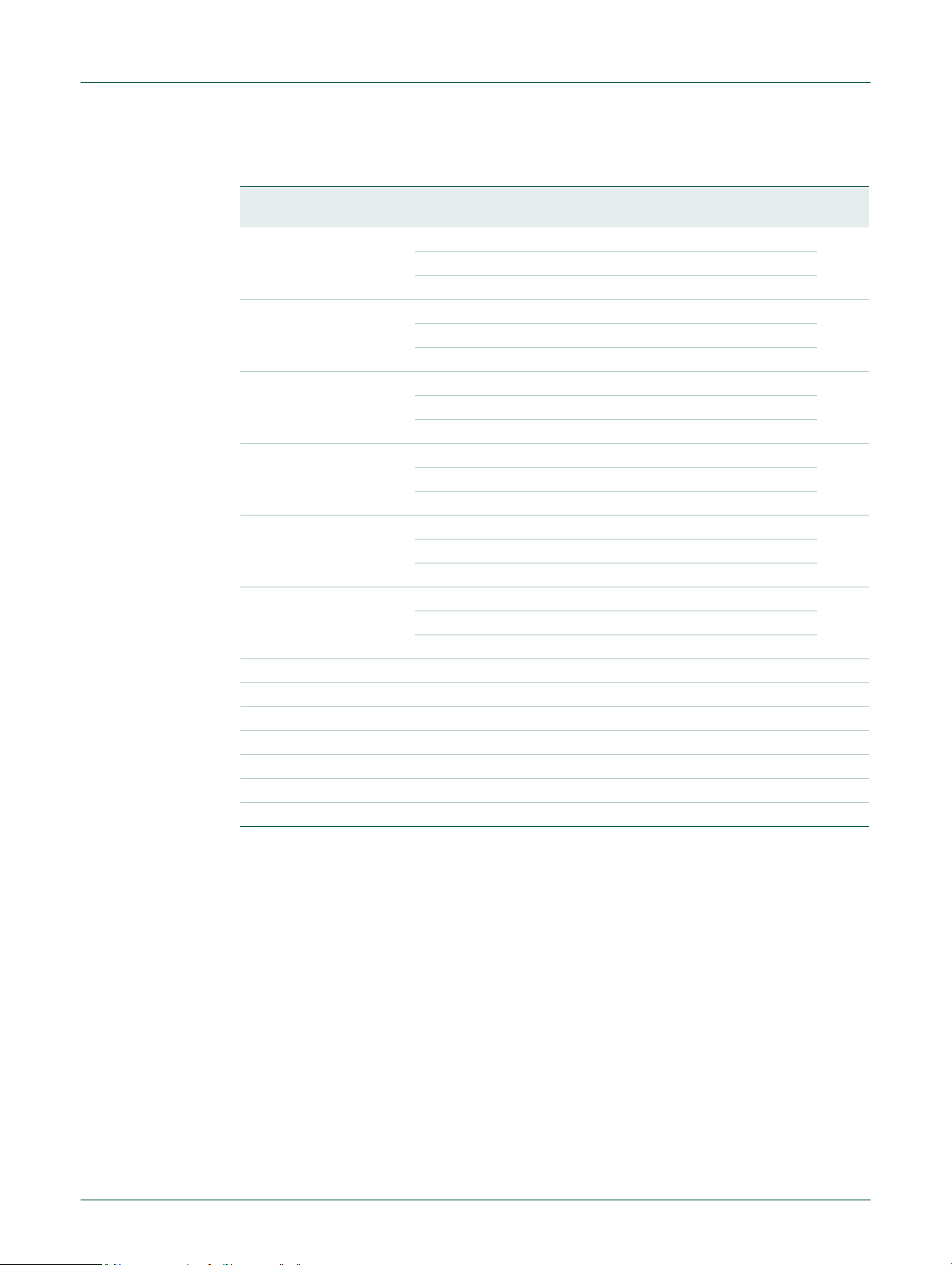

1.4 Block diagram

UM10429

Chapter 1: LPC11 02 Introductory information

Fig 1. LPC1102 Block diagram

UM10429 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

User manual Rev. 1 — 20 October 2010 5 of 258

Page 6

NXP Semiconductors

1.5 ARM Cortex-M0 processor

The ARM Cortex-M0 processor is described in detail in Section 19.2 “About the

Cortex-M0 processor and core peripherals”. For the LPC1102, the ARM Cortex-M0

processor core is configured as follows:

• System options:

– The Nested Vectored Interrupt Controller (NVIC) is includ ed and su pport s up to 32

interrupts.

– The system tick timer is included.

• Debug options: Serial Wire Debug is included with two watchpoints and four

breakpoints.

UM10429

Chapter 1: LPC11 02 Introductory information

UM10429 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

User manual Rev. 1 — 20 October 2010 6 of 258

Page 7

UM10429

Chapter 2: LPC1102 Memory mapping

Rev. 1 — 20 October 2010 User manual

2.1 How to read this chapter

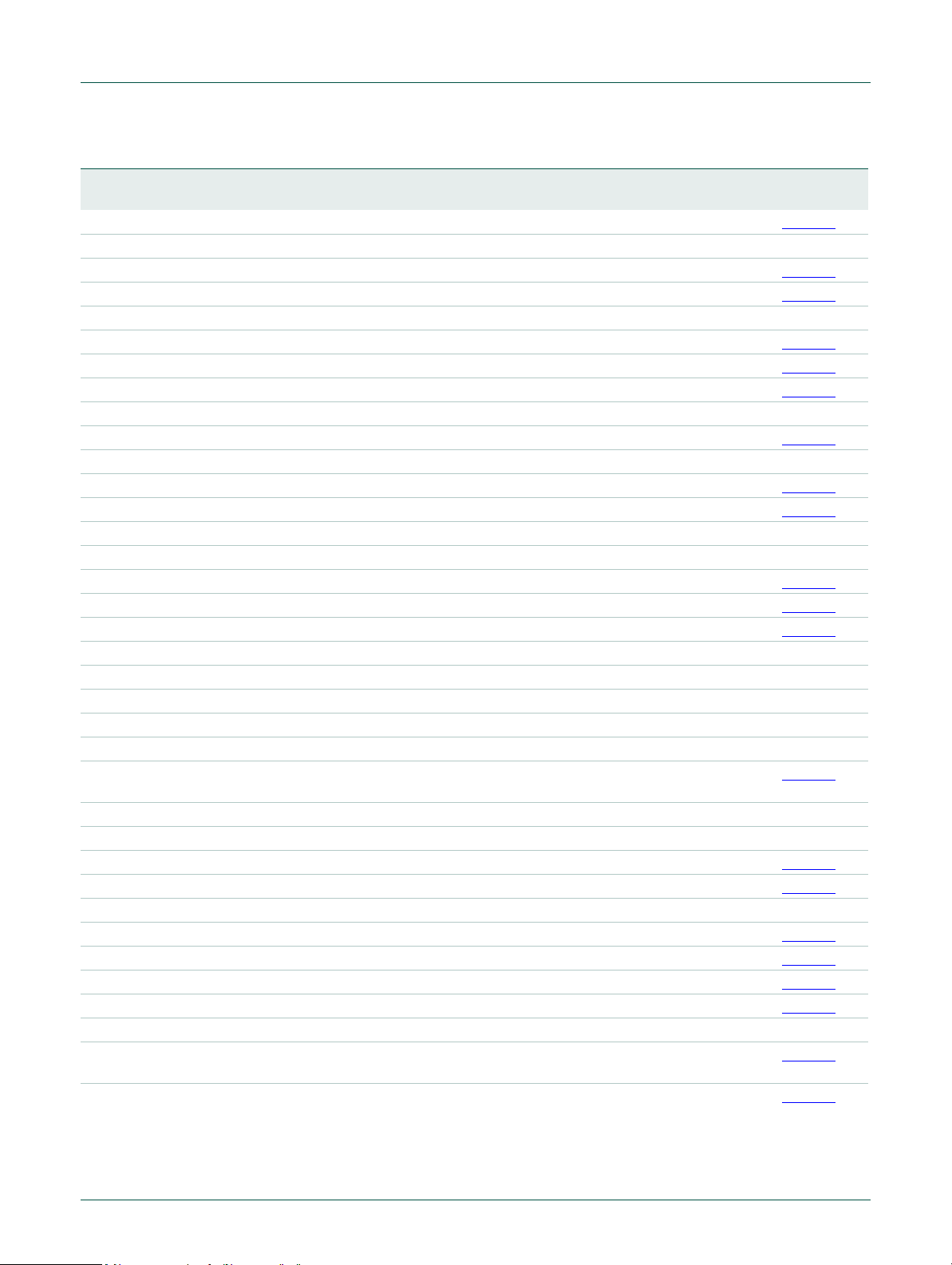

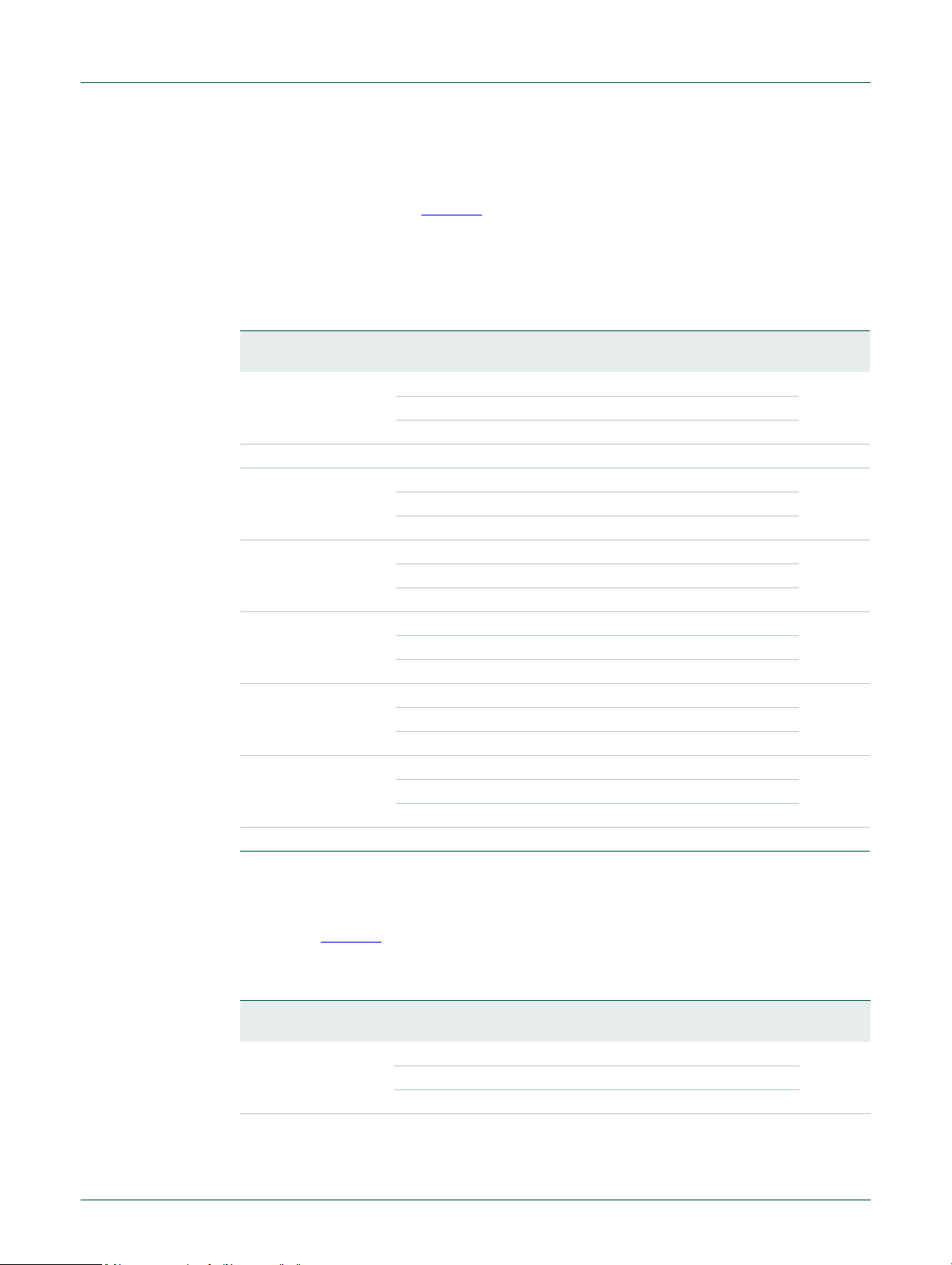

Table 3 shows the memory configuration for the LPC1102 part.

Table 3. LPC1102 memory configuration

Part Flash SRAM

Suffix

LPC1102 32 kB 8 kB

2.2 Memory map

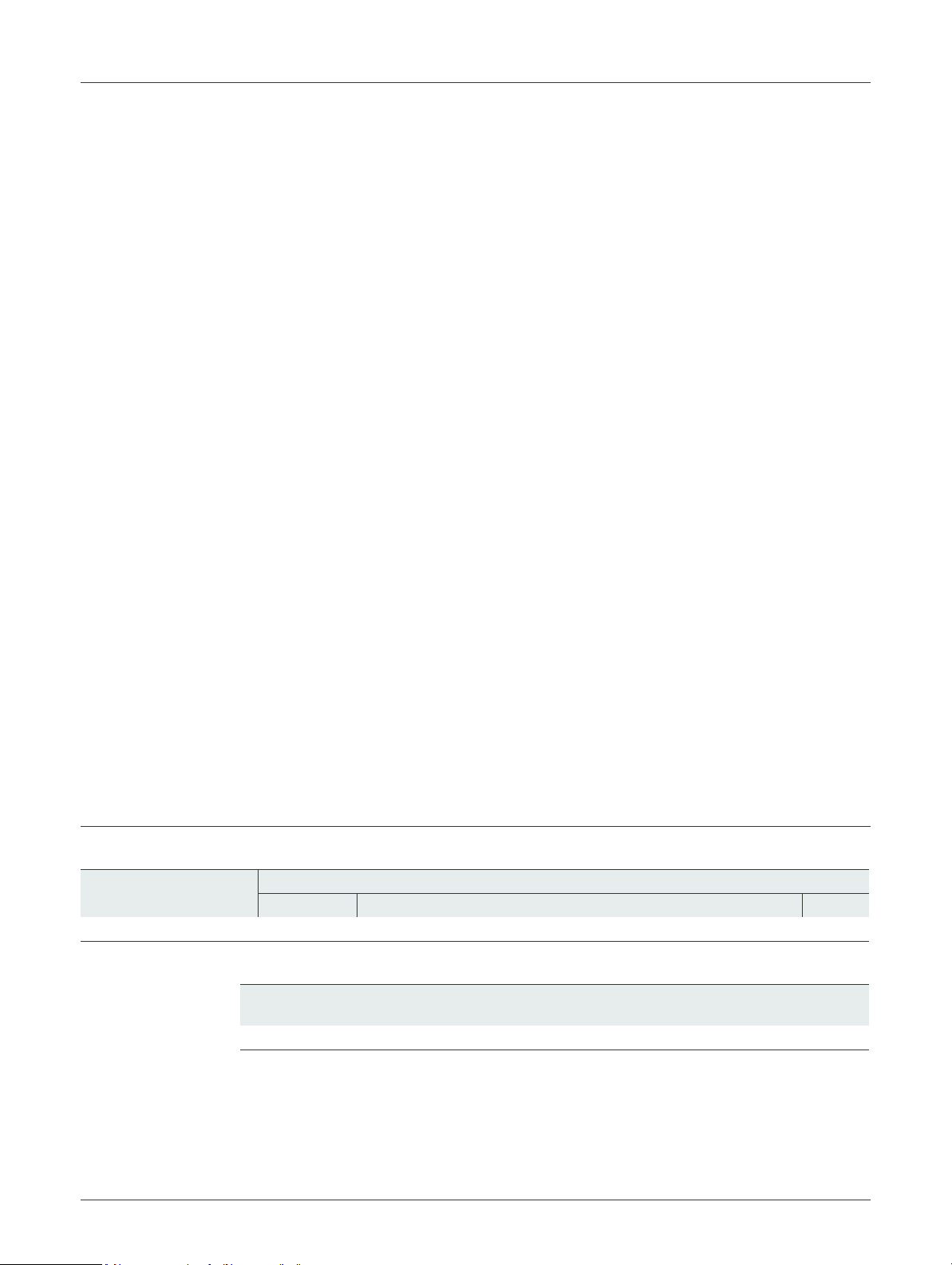

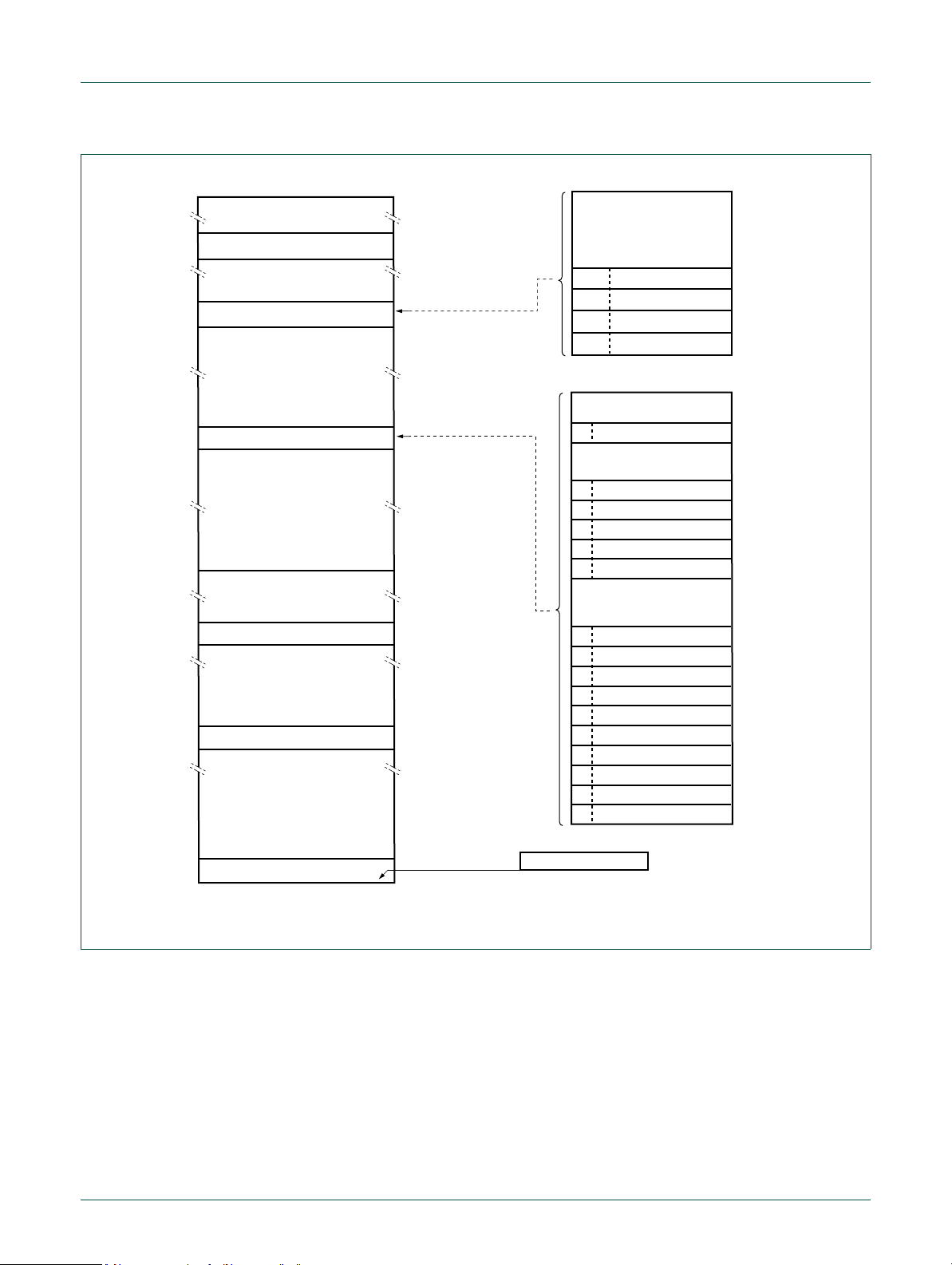

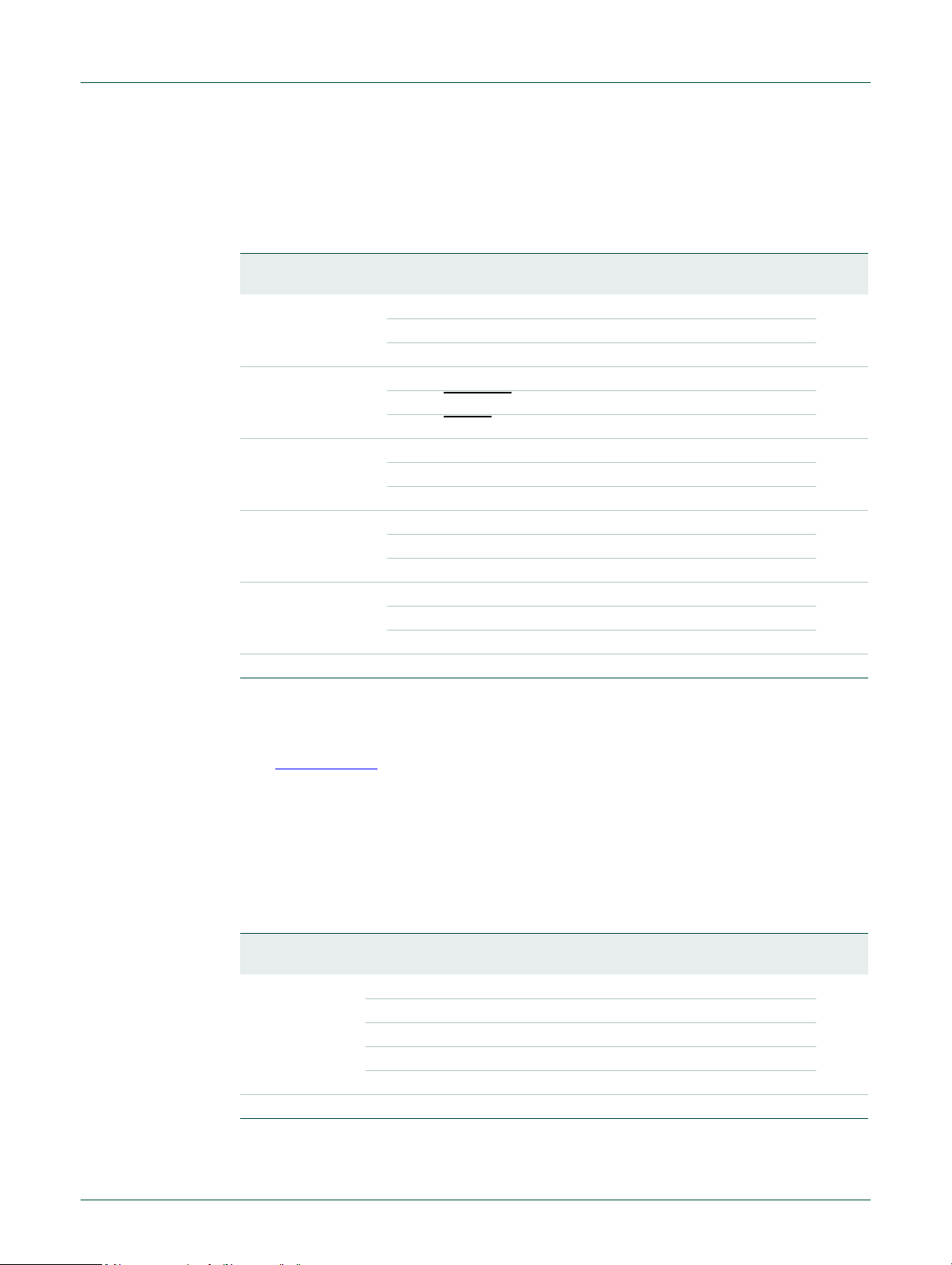

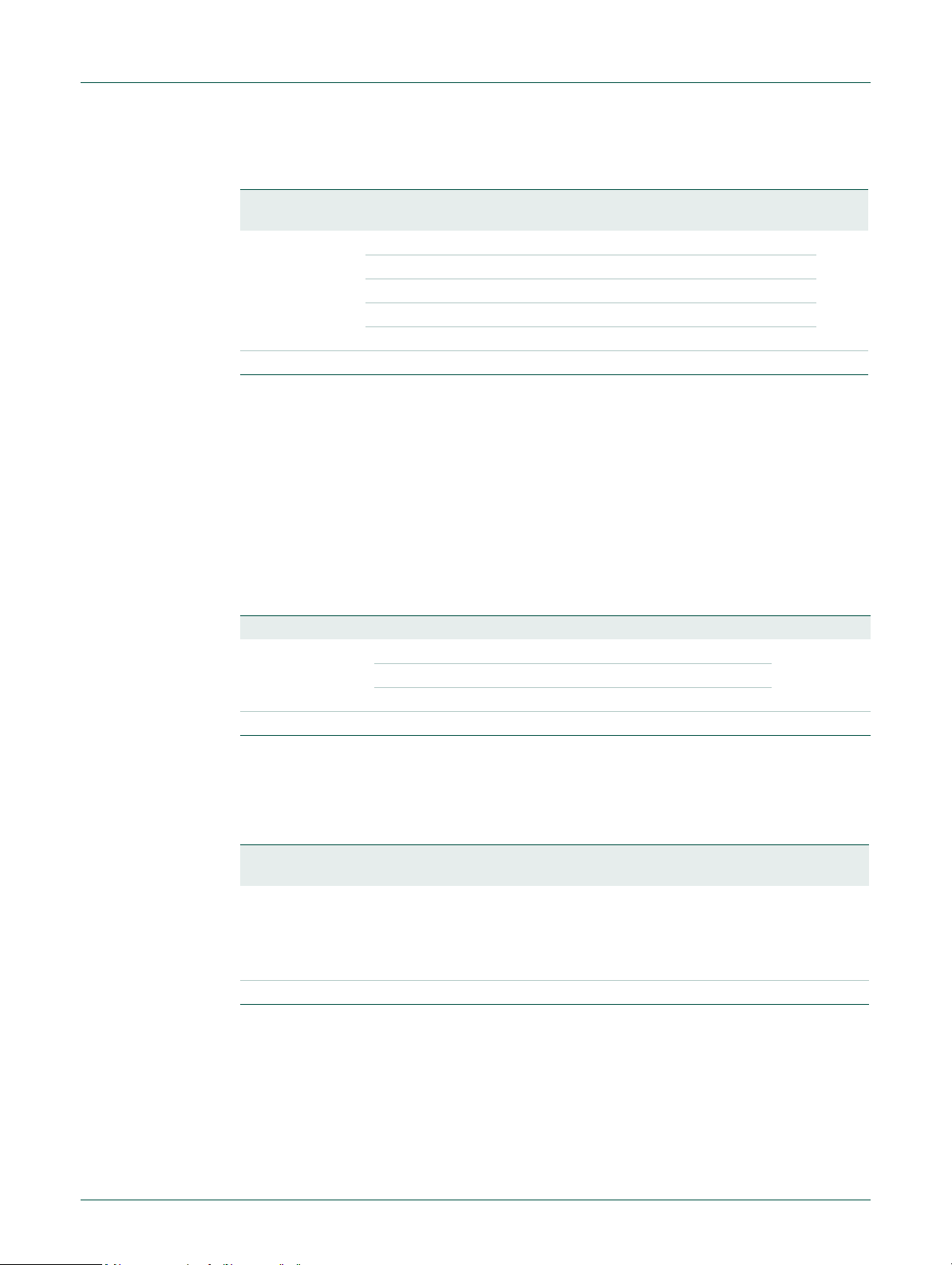

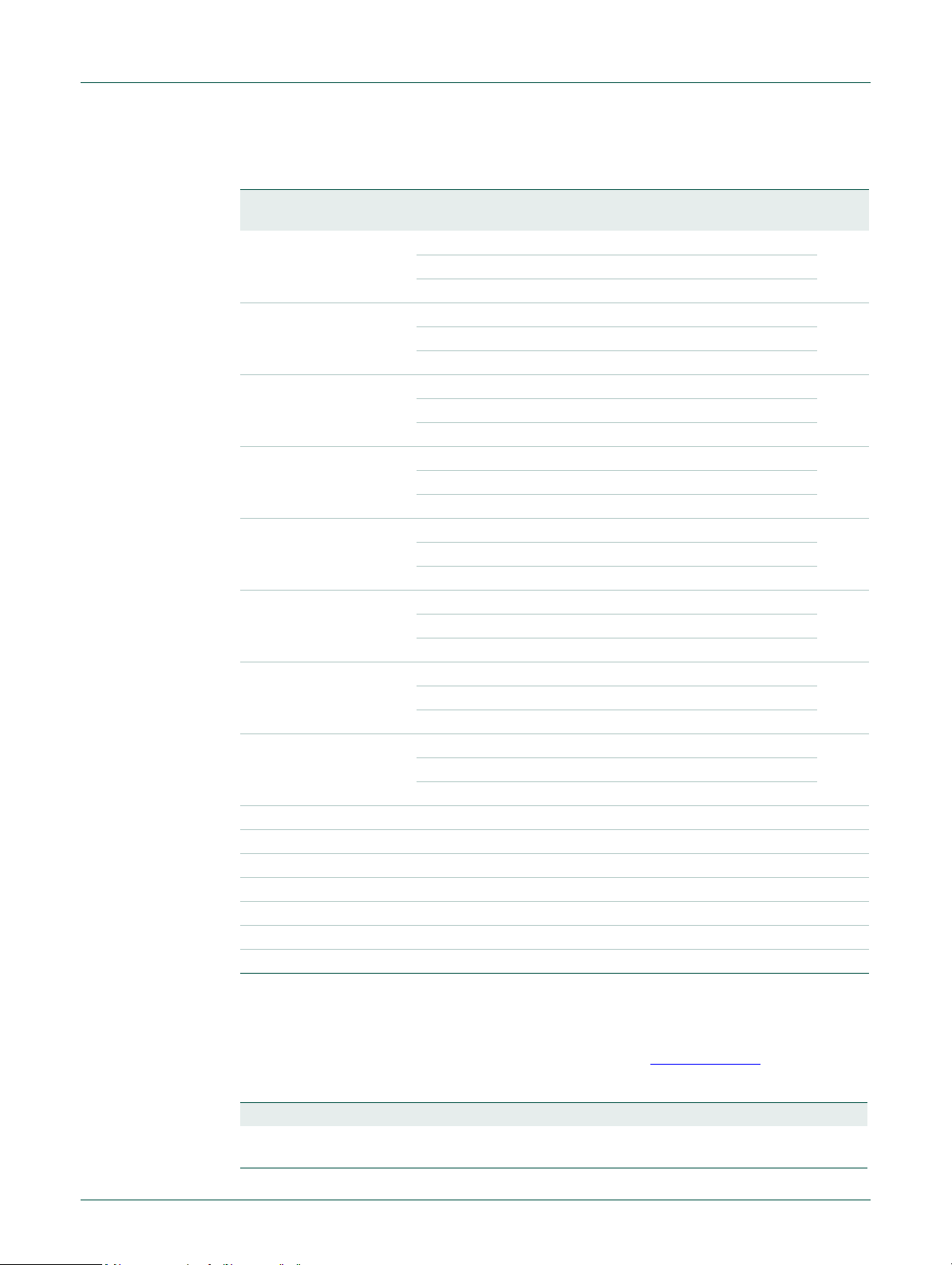

Figure 2 shows the memory and peripheral address space of the LPC1102.

The AHB peripheral area is 2 MB in size and is divided to allow for up to 128 peripherals.

On the LPC1102, the GPIO ports are the only AHB peripherals. The APB peripheral area

is 512 kB in size and is divided to allow for up to 32 peripherals. Each peripheral of either

type is allocated 16 kB of space. This allows simplifying the address decoding for each

peripheral.

All peripheral register addresses are 32-bit word aligned regardless of their size. An

implication of this is that word and half-word registers must be accessed all at once. For

example, it is not possible to read or write the upper byte of a word register separately.

UM10429 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

User manual Rev. 1 — 20 October 2010 7 of 258

Page 8

NXP Semiconductors

0x5000 0000

0x5001 0000

0x5002 0000

0x5020 0000

AHB peripherals

127 - 16 reserved

GPIO PIO1

7-4

0x5003 0000

0x5004 0000

reserved

reserved

11-8

15-12

GPIO PIO0

3-0

APB peripherals

0x4000 4000

0x4000 8000

0x4000 C000

0x4001 0000

0x4001 8000

0x4002 0000

0x4002 8000

0x4003 8000

0x4003 C000

0x4004 0000

0x4004 4000

0x4004 8000

0x4004 C000

0x4005 8000

0x4005 C000

0x4008 0000

0x4002 4000

0x4001 C000

0x4001 4000

0x4000 0000

WDT

32-bit counter/timer 0

32-bit counter/timer 1

ADC

UART

PMU

reserved

13 - 10 reserved

reserved

reserved

21 - 19 reserved

31 - 23 reserved

0

1

2

3

4

5

6

7

8

9

16

15

14

17

18

reserved

reserved

reserved

0x0000 0000

0 GB

0.5 GB

4 GB

1 GB

0x1000 2000

0x1FFF 0000

0x1FFF 4000

0x2000 0000

0x4000 0000

0x4008 0000

0x5000 0000

0x5020 0000

0xFFFF FFFF

reserved

reserved

reserved

APB peripherals

AHB peripherals

8 kB SRAM

0x1000 0000

LPC1102

0x0000 8000

32 kB on-chip flash

16 kB boot ROM

0x0000 0000

0x0000 00C0

active interrupt vectors

002aaf526

reserved

SPI

16-bit counter/timer 1

16-bit counter/timer 0

IOCONFIG

system control

22

reserved

flash controller

0xE000 0000

0xE010 0000

private peripheral bus

UM10429

Chapter 2: LPC1102 Memory mapping

Fig 2. LPC1102 memory map

UM10429 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

User manual Rev. 1 — 20 October 2010 8 of 258

Page 9

UM10429

Chapter 3: LPC1102 System configuration

Rev. 1 — 20 October 2010 User manual

3.1 How to read this chapter

This chapter applies to part LPC1102.

3.2 Introduction

The system configuration block controls oscillators, start logic, and clock generation of the

LPC1102. Also included in this block are registers for setting the priority for AHB access

and a register for remapping flash, SRAM, and ROM memory areas.

3.3 Pin description

Table 4 shows pins that are associated with system con tr o l bloc k func tio ns .

Table 4. Pin summary

Pin name Pin direction Pin description

PIO0_0; PIO0_8 to PIO0_11 I Start logic wake-up pins port 0

PIO1_0 I Start logic wake-up pin port 1

3.4 Clocking and power control

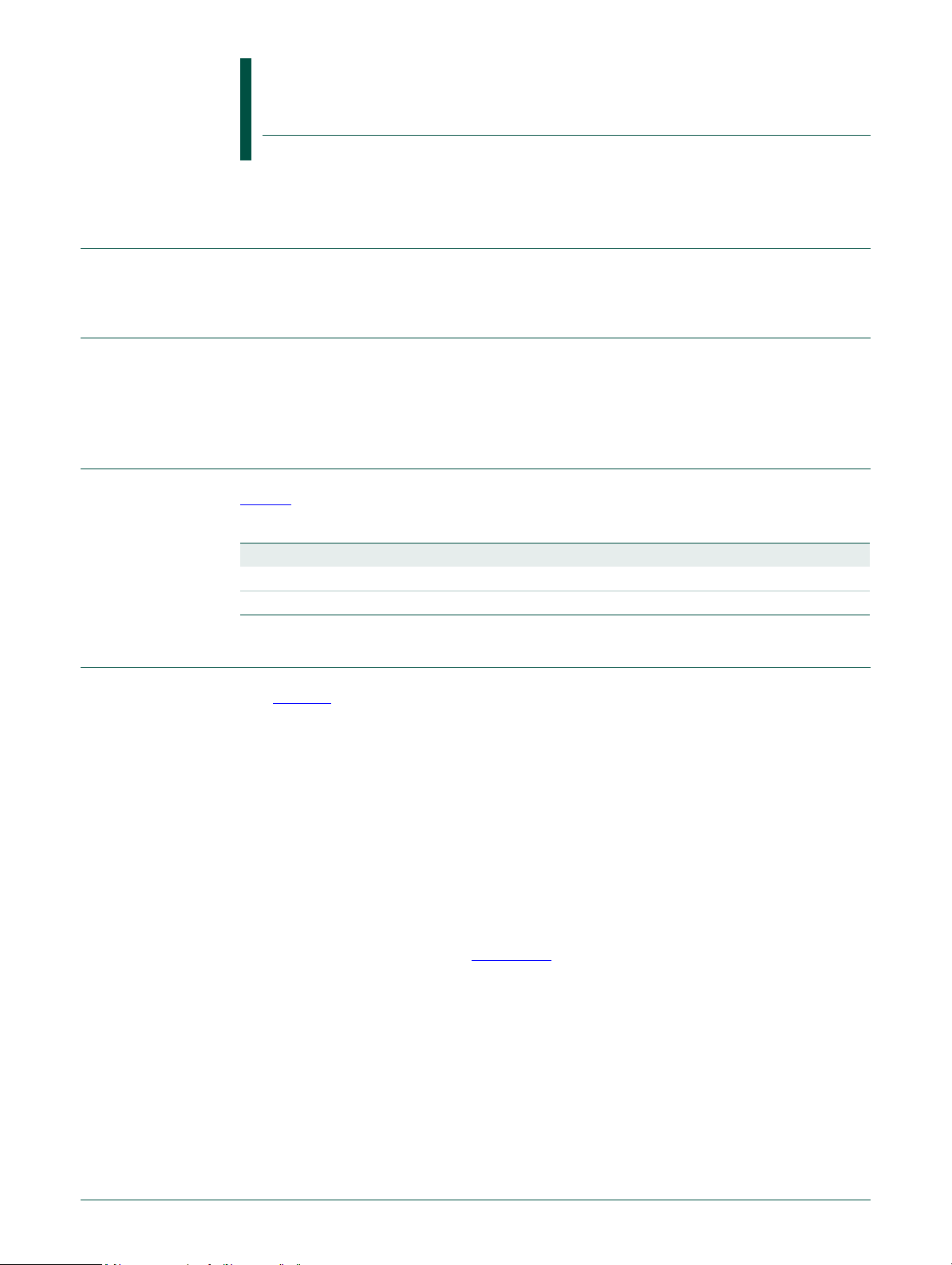

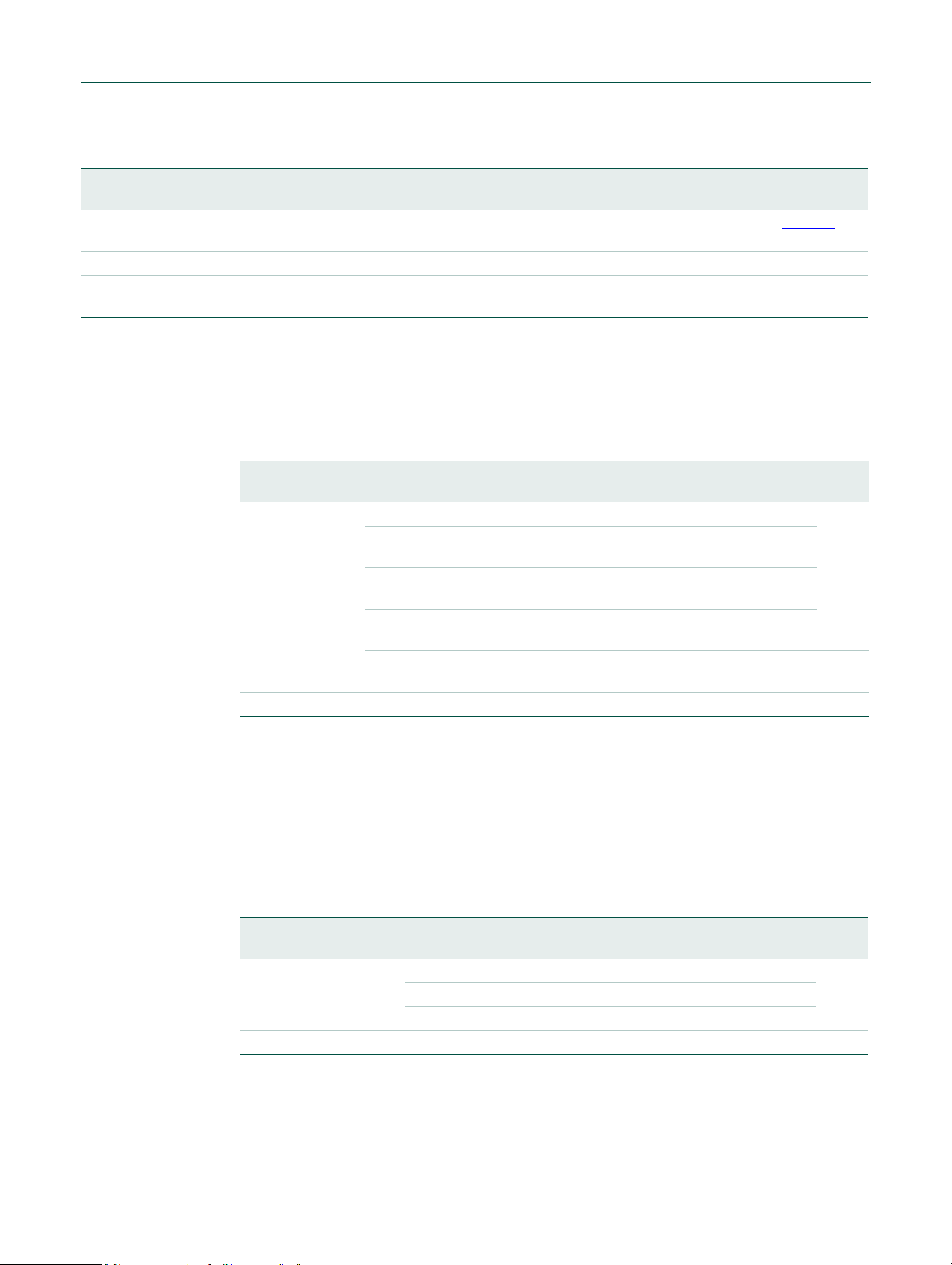

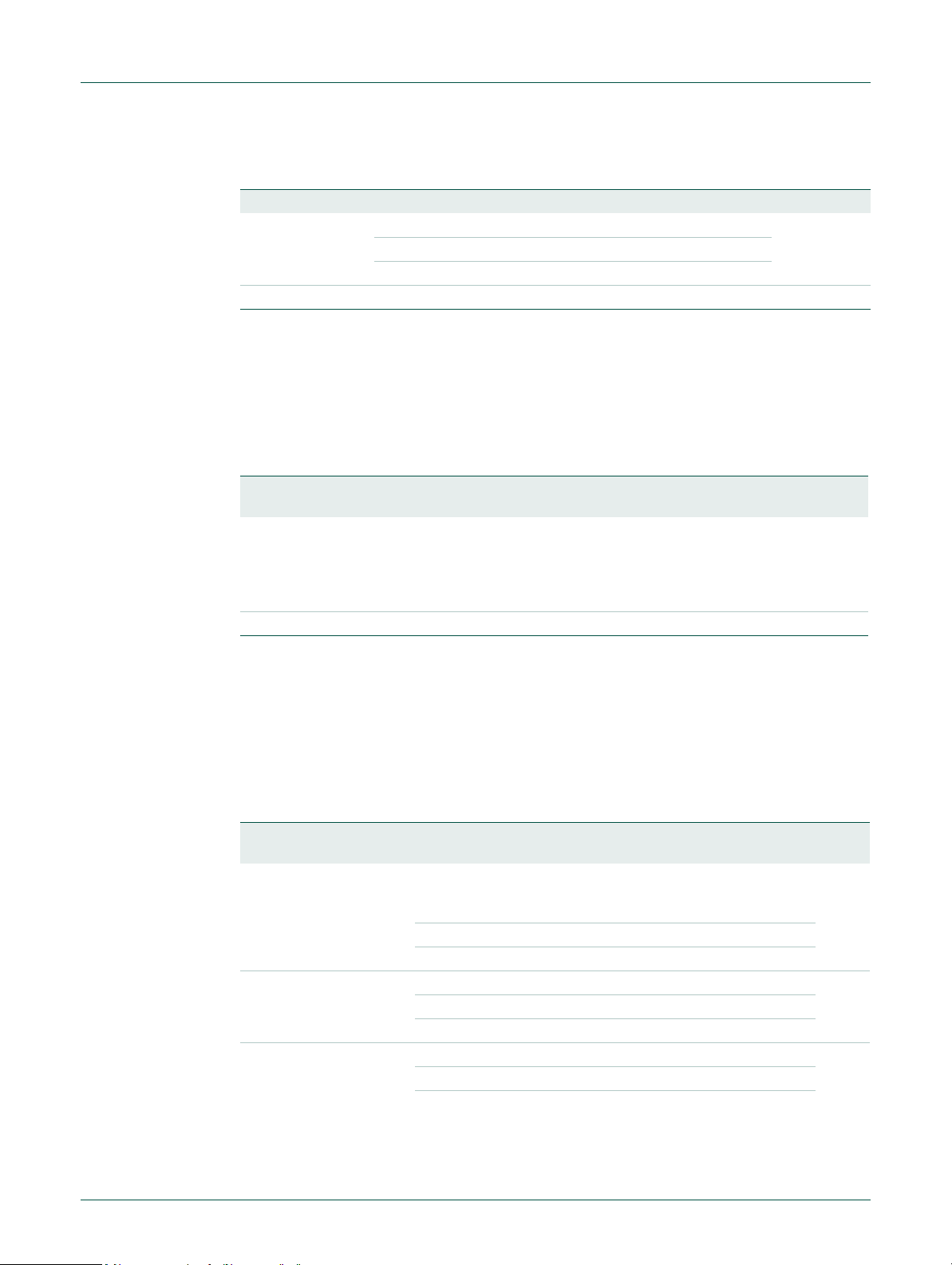

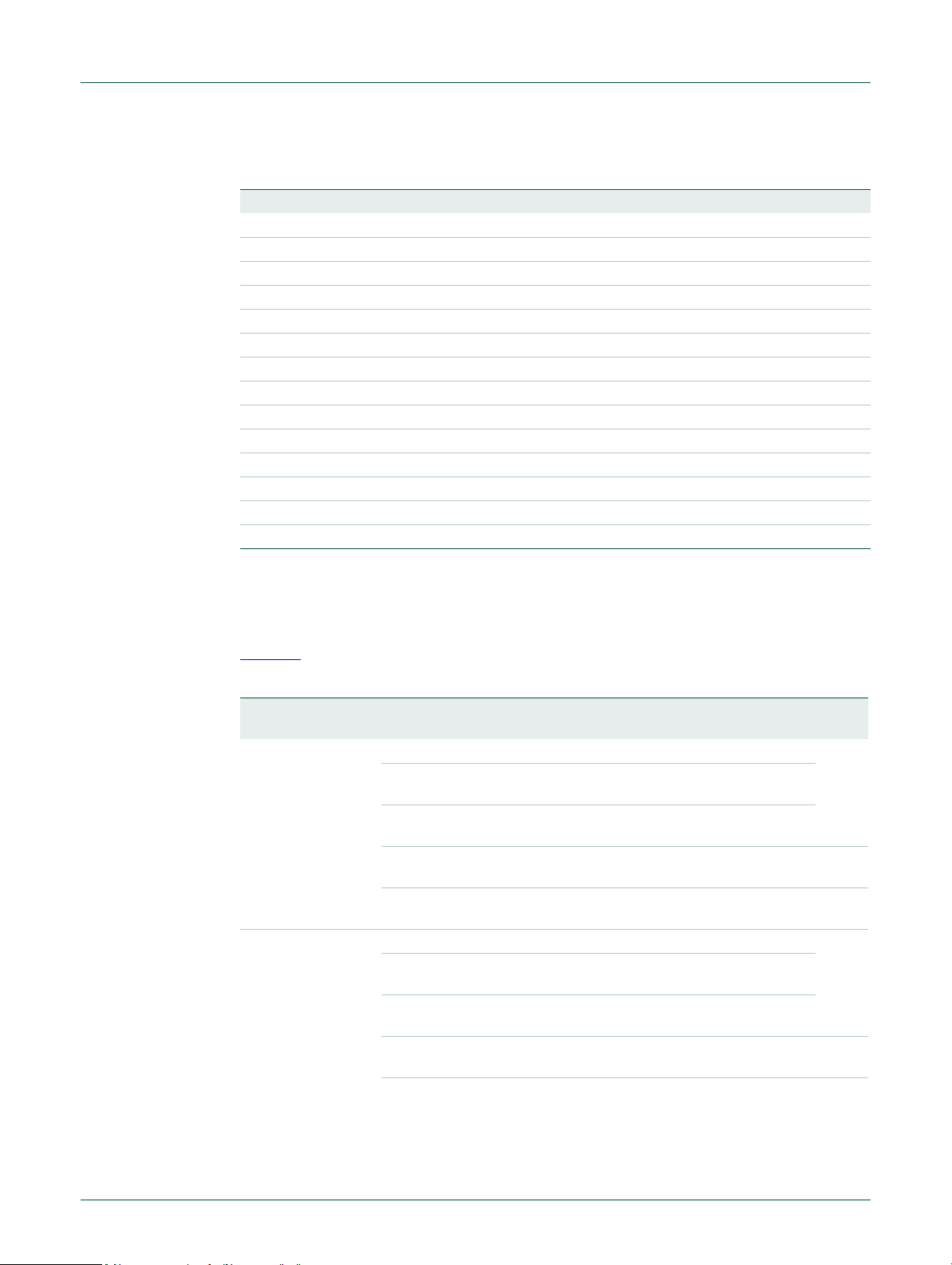

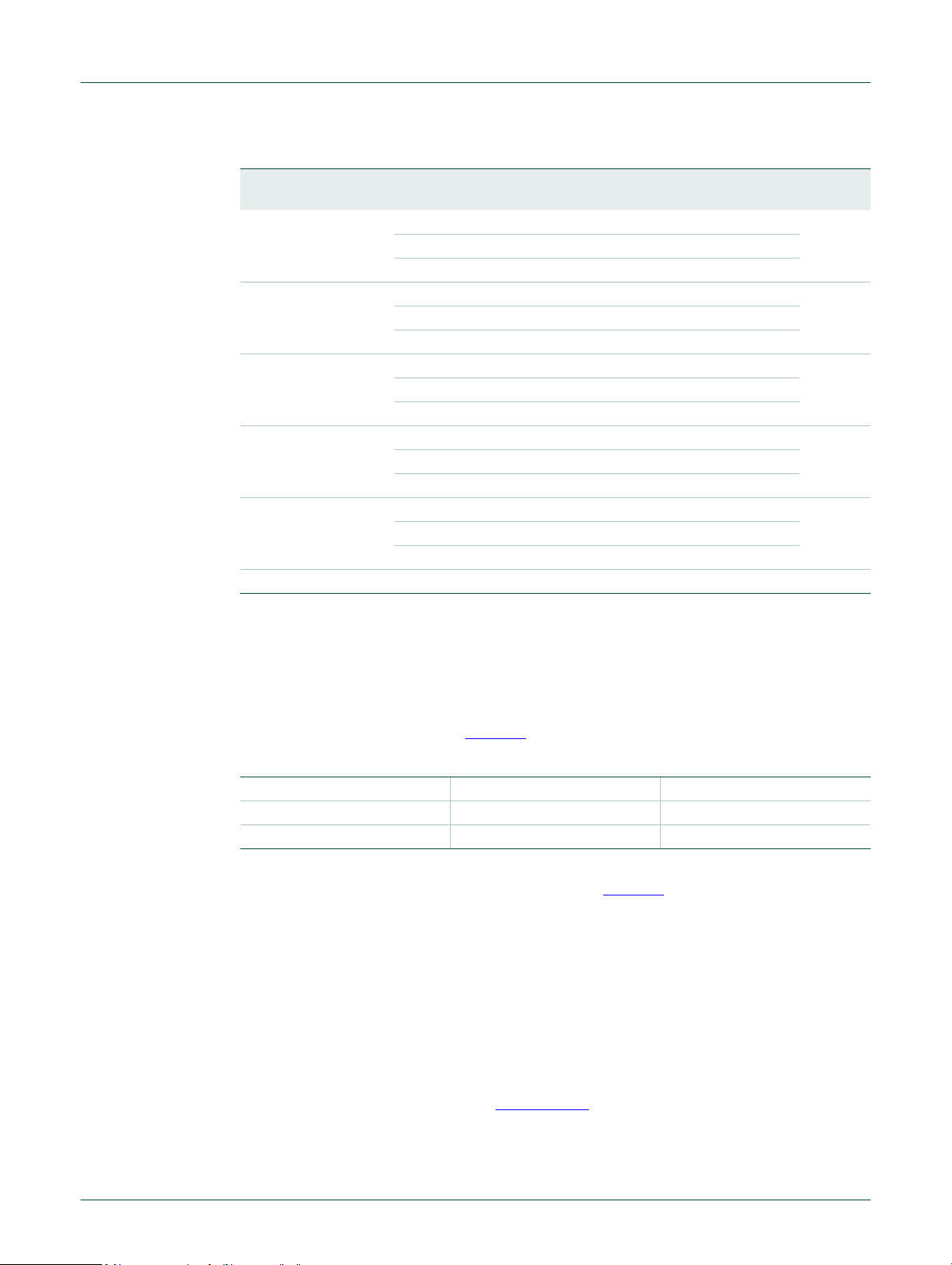

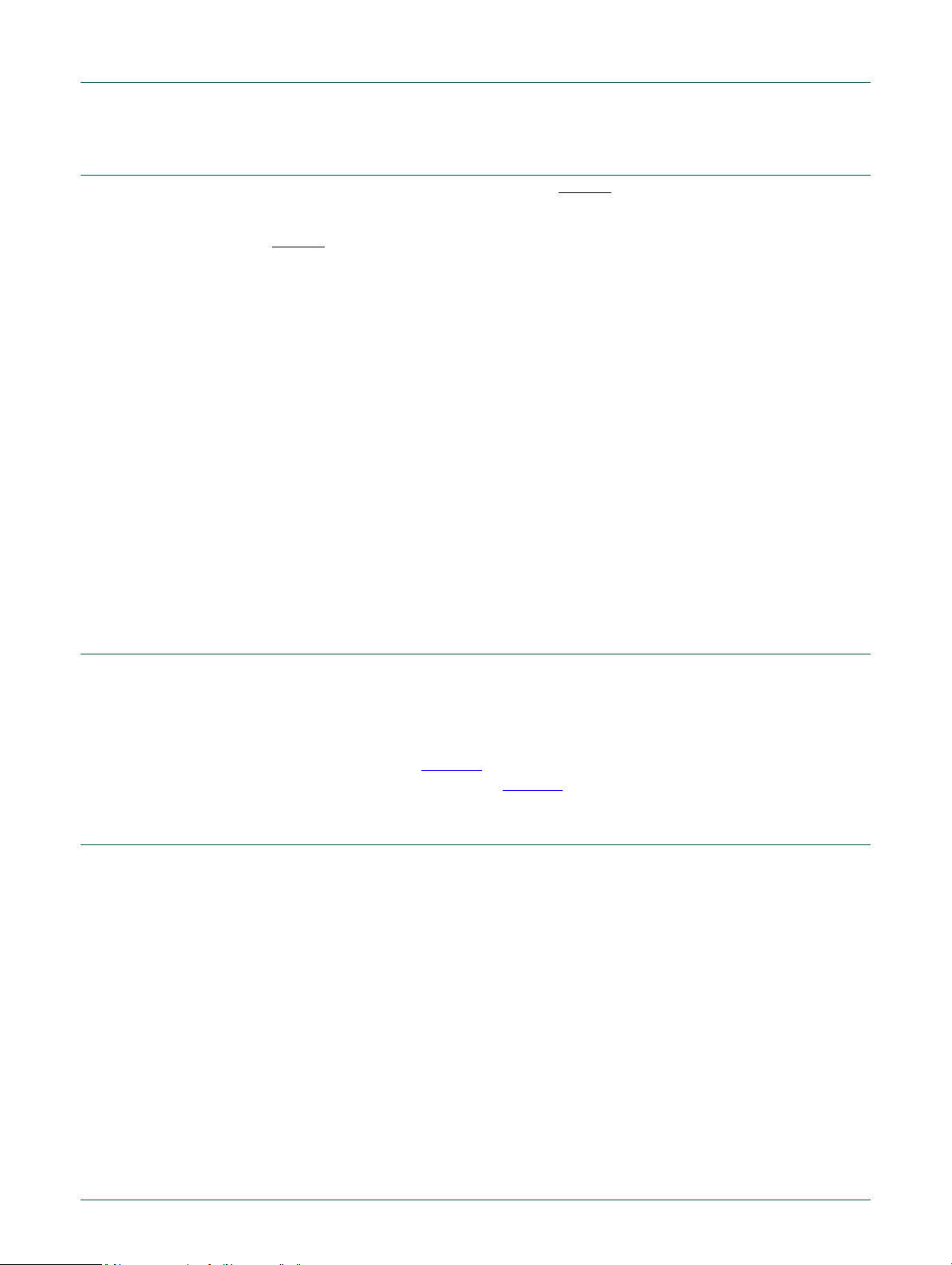

See Figure 3 for an overview of the LPC1102 Clock Generation Unit (CGU).

The LPC1102 include three independent oscillators. These are the system oscillator, the

Internal RC oscillator (IRC), and the watchdog oscillator. Each oscillator can be used for

more than one purpose as required in a particular application.

Following reset, the LPC1102 will operate from the Internal RC oscillator until switched by

software. This allows systems to operate without any external crystal and the bootloader

code to operate at a known frequency.

The SYSAHBCLKCTRL register gates the system clock to the various peripherals and

memories. UART, the WDT, and SPI0 have individual clock dividers to derive peripheral

clocks from the main clock.

For details on power control see Section 3.8

.

UM10429 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

User manual Rev. 1 — 20 October 2010 9 of 258

Page 10

NXP Semiconductors

SYSTEM PLL

IRC oscillator

system oscillator

watchdog oscillator

IRC oscillator

watchdog oscillator

MAINCLKSEL

(main clock select)

SYSPLLCLKSEL

(system PLL clock select)

SYSTEM CLOCK

DIVIDER

AHB clock 0

(system)

AHBCLKCTRL[1:18]

SPI0 PERIPHERAL

CLOCK DIVIDER

SPI0_PCLK

UART PERIPHERAL

CLOCK DIVIDER

UART_PCLK

WDT CLOCK

DIVIDER

WDT_PCLK

WDTUEN

(WDT clock update enable)

main clock

system clock

IRC oscillator

AHB clocks

1 to 18

(memories

and peripherals)

18

sys_pllclkout

sys_pllclkin

UM10429

Chapter 3: LPC1102 System configuration

3.5 Register description

Table 5. Register overview: system control block (base address 0x4004 8000)

UM10429 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

User manual Rev. 1 — 20 October 2010 10 of 258

Fig 3. LPC1102 CGU block diagram

All registers, regardless of size, are on word address boundaries. Details of the registers

appear in the description of each function.

See Section 3.11

for the flash access timing register, which can be re-configured as part

the system setup. This register is not part of the system configuration block.

Name Access Address offset Description Reset

Reference

value

SYSMEMREMAP R/W 0x000 System memory remap 0x002 Table 6

PRESETCTRL R/W 0x004 Peripheral reset control 0x000 Table 7

SYSPLLCTRL R/W 0x008 System PLL control 0x000 Table 8

SYSPLLSTAT R 0x00C System PLL status 0x000 Table 9

- - 0x010 - 0x01C Reserved - -

SYSOSCCTRL R/W 0x020 System oscillator control 0x000 Table 10

WDTOSCCTRL R/W 0x024 Watchdog oscillator control 0x000 Table 11

IRCCTRL R/W 0x028 IRC control 0x080 Table 12

- - 0x02C Reserved - -

Page 11

NXP Semiconductors

UM10429

Chapter 3: LPC1102 System configuration

Table 5. Register overview: system control block (base address 0x4004 8000) …continued

Name Access Address offset Description Reset

value

SYSRSTST AT R 0x030 System reset status register 0x000 Table 13

- - 0x034 - 0x03C Reserved - -

SYSPLLCLKSEL R/W 0x040 System PLL clock source select 0x000 Table 14

SYSPLLCLKUEN R/W 0x044 System PLL clock source update enable 0x000 Table 15

- - 0x048 - 0x06C Reserved - -

MAINCLKSEL R/W 0x070 Main clock source select 0x000 Table 16

MAINCLKUEN R/W 0x074 Main clock source update enable 0x000 Table 17

SYSAHBCLKDIV R/W 0x078 System AHB clock divider 0x001 Table 18

- - 0x07C Reserved - -

SYSAHBCLKCTRL R/W 0x080 System AHB clock control 0x85F Table 19

- - 0x084 - 0x090 Reserved - -

SSP0CLKDIV R/W 0x094 SPI0 clock divder 0x000 Table 20

UARTCLKDIV R/W 0x098 UART clock divder 0x000 Table 21

- - 0x09C Reserved - -

- - 0x0A0-0x0CC Reserved - -

WDTCLKSEL R/W 0x0D0 WDT clock source select 0x000 Table 22

WDTCLKUEN R/W 0x0D4 WDT clock source update enable 0x000 Table 23

WDTCLKDIV R/W 0x0D8 WDT clock divider 0x000 Table 24

- - 0x0DC Reserved - -

- - 0x0E0 Reserved - -

- - 0x0E4 Reserved - -

- - 0x0E8 Reserved - -

- - 0x0EC - 0x0FC Reserved PIOPORCAP0 R 0x100 POR captured PIO status 0 user

dependent

- - 0x104 Reserved - -

- R 0x108 - 0x14C Reserved - -

BODCTRL R/W 0x150 BOD control 0x000 Table 26

SYSTCKCAL R/W 0x154 System tick counter calibration 0x004 Table 27

- - 0x158 - 0x1FC Reserved - -

STARTAPRP0 R/W 0x200 Start logic edge control register 0 Table 28

STARTERP0 R/W 0x204 Start logic signal enable register 0 Table 29

STARTRSRP0CLR W 0x208 Start logic reset register 0 n/a Table 30

STARTSRP0 R 0x20C Start logic status register 0 n/a Table 31

- - 0x210 - 0x22C Reserved - -

PDSLEEPCFG R/W 0x230 Power-down states in Deep-sleep mode 0x0000

0000

PDAWAKECFG R/W 0x234 Power-down states after wake-up from

Deep-sleep mode

0x0000

EDF0

Reference

-

Table 25

Table 33

Table 34

UM10429 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

User manual Rev. 1 — 20 October 2010 11 of 258

Page 12

NXP Semiconductors

UM10429

Chapter 3: LPC1102 System configuration

Table 5. Register overview: system control block (base address 0x4004 8000) …continued

Name Access Address offset Description Reset

value

PDRUNCFG R/W 0x238 Power-down configuration register 0x0000

EDF0

- - 0x23C - 0x3F0 Reserved - -

DEVICE_ID R 0x3F4 Device ID part

dependent

3.5.1 System memory remap register

The system memory remap register selects whether the ARM interrupt vectors are read

from the boot ROM, the flash, or the SRAM.

Table 6. System memory remap register (SYSMEMREMAP, address 0x4004 8000) bit

description

Bit Symbol Value Description Reset

1:0 MAP System memory remap 10

0x0 Boot Loader Mode. Interrupt vectors are re-mapped to Boot

ROM.

0x1 User RAM Mode. Interrupt vectors are re-mapped to Static

RAM.

0x2 User Flash Mode. Interrupt vectors are not re-mapped and

reside in Flash.

0x3 User Flash Mode. Interrupt vectors are not re-mapped and

reside in Flash.

31:2 - - Reserved 0x00

Reference

Table 35

Table 36

value

3.5.2 Peripheral reset control register

This register allows software to reset the SPI peripheral. Writing a 0 to the SSP0_RST_N

bit resets the SPI0 peripheral. Writing a 1 de-asserts the reset.

Remark: Before accessing the SPI peripheral, write a 1 to this register to ensure that the

reset signal to the SPI is de-asserted.

Table 7. Peripher al reset control register (PRESETCTRL, address 0x4004 8004) bit

description

Bit Symbol Value Description Reset

value

0 SSP0_RST_N SPI0 reset control 0

0 Resets the SPI0 periphe ral.

1 SPI0 reset de-asserted.

31:1 - - Reserved 0x00

UM10429 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

User manual Rev. 1 — 20 October 2010 12 of 258

Page 13

NXP Semiconductors

3.5.3 System PLL control register

This register connects and enables the system PLL a nd configur es the PLL multiplie r and

divider values. The PLL accepts an input frequency from 10 MHz to 25 MHz from various

clock sources. The input frequency is multiplied up to a high frequency, then divided down

to provide the actual clock used by the CPU, peripherals, and memories. The PLL can

produce a clock up to the maximum allowed for the CPU.

Table 8. Syste m PLL control register (SYSPLLCTRL, address 0x4004 8008) bit description

Bit Symbol Value Description Reset

4:0 MSEL Feedback divider value. The division value M is the

6:5 PSEL Post divider ratio P. The division ratio is 2 × P. 0x00

31:7 - - Reserved. Do not write ones to reserved bits. 0x0

UM10429

Chapter 3: LPC1102 System configuration

value

0x000

programmed MSEL value + 1.

00000: Division ratio M = 1

to

11111: Division ration M = 32

0x0 P = 1

0x1 P = 2

0x2 P = 4

0x3 P = 8

3.5.4 System PLL status register

This register is a Read-only register and supplies the PLL lock status (see

Section 3.10.1

Table 9. Syste m PLL status register (SYSPLLSTAT, address 0x4004 800C) bit description

Bit Symbol Value Description Reset

0 LOCK PLL lock status 0x0

31:1 - - Reserved 0x00

).

0 PLL not locked

1 PLL locked

3.5.5 System oscillator control register

This register configures the frequency range for the system oscillator.

Table 10. System oscillator control register (SYSOSCCTRL, address 0x4004 8020) bit

description

Bit Symbol Value Description Reset

0 BYPASS Bypass system oscillator 0x0

0 Oscillator is not bypassed.

1 Bypass enabled. PLL input (sys_osc_clk) is fed

directly from the XTALIN pin.

value

value

UM10429 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

User manual Rev. 1 — 20 October 2010 13 of 258

Page 14

NXP Semiconductors

Table 10. System oscillator control register (SYSOSCCTRL, address 0x4004 8020) bit

Bit Symbol Value Description Reset

1 FREQRANGE Determines frequency range for Low-power

31:2 - - Reserved 0x00

3.5.6 Watchdog oscillator control register

This register configures the watchdog oscillator. The oscillator consists of an analog and a

digital part. The analog part contains the oscillator function and generates an analog clock

(Fclkana). With the digital part, the analog output clock (Fclkana) can be divided to the

required output clock frequency wdt_osc_clk. The analog output frequency (Fclkan a) can

be adjusted with the FREQSEL bits between 500 kHz and 3.4 MHz. With the digital part

Fclkana will be divided (divider ratios = 2, 4,...,64) to wdt_osc_clk using the DIVSEL bits.

UM10429

Chapter 3: LPC1102 System configuration

description

value

0x0

oscillator.

0 1 - 20 MHz frequen cy range.

1 15 - 25 MHz freque ncy range

The output clock frequency of the watchdog oscillator can be calculated as

wdt_osc_clk =

⁄

(2 × (1 + DIVSEL))

= 7.8 kHz to 1.7 MHz (nominal values).

Fclkana

Remark: Any setting of the FREQSEL bits will yield a Fclkana value within ±40% of the

listed frequency value. The watchdog oscillator is the clock source with the lowest power

consumption. If accurate timing is required, use the IRC or system oscillator.

Remark: The frequency of the watchdog oscillator is undefined after reset. The watchdog

oscillator frequency must be programmed by writing to the WDTOSCCTRL register before

using the watchdog oscillator.

Table 11. Watchdog oscillator control register (WDTOSCCTRL, address 0x4004 8024) bit

description

Bit Symbol Value Description Reset

value

4:0 DIVSEL Select divider for Fclkana.

wdt_osc_clk = Fclkana/ (2 × (1 + DIVSEL))

00000: 2 × (1 + DIVSEL) = 2

00001: 2 × (1 + DIVSEL) = 4

to

11111: 2 × (1 + DIVSEL) = 64

0x00

UM10429 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

User manual Rev. 1 — 20 October 2010 14 of 258

Page 15

NXP Semiconductors

Table 11. Watchdog oscillator control register (WDTOSCCTRL, address 0x4004 8024) bit

Bit Symbol Value Description Reset

8:5 FREQSEL Select watchdog oscillator analog output frequency

31:9 - - Reserved 0x00

description

0x1 0.5 MHz

0x2 0.8 MHz

0x3 1.1 MHz

0x4 1.4 MHz

0x5 1.6 MHz

0x6 1.8 MHz

0x7 2.0 MHz

0x8 2.2 MHz

0x9 2.4 MHz

0xA 2.6 MHz

0xB 2.7 MHz

0xC 2.9 MHz

0xD 3.1 MHz

0xE 3.2 MHz

0xF 3.4 MHz

UM10429

Chapter 3: LPC1102 System configuration

…continued

value

0x00

(Fclkana).

3.5.7 Internal resonant crystal control register

This register is used to trim the on-chip 12 MHz oscillator. The trim value is factory-preset

and written by the boot code on start-up.

Table 12. Internal resonant crystal control register (IRCCTRL, address 0x4004 8028) bit

description

Bit Symbol Value Description Reset value

7:0 TRIM Trim value 0x1000 0000,

31:9 - - Reserved 0x00

then flash will

reprogram

UM10429 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

User manual Rev. 1 — 20 October 2010 15 of 258

Page 16

NXP Semiconductors

3.5.8 System reset status register

if another reset signal - for example EXTRST - remains asserted after the POR signal is

negated, then its bit is set to detected.

Table 13. System reset status register (SYSRSTSTAT, address 0x4004 8030) bit description

Bit Symbol Value Description Reset

0 POR POR reset status 0x0

1 EXTRST 0x0

2 WDT Status of the Watchdog reset 0x0

3 BOD Status of the Brown-out detect reset 0x0

4 SYSRST Status of the software system reset 0x0

31:5 - - Reserved 0x00

Chapter 3: LPC1102 System configuration

0 no POR detected

1 POR detected

0 no RESET

1 RESET

0 no WDT reset de tected

1 WDT reset detected

0 no BOD reset detected

1 BOD reset detected

0 no System reset detected

1 System reset detected

event detected

detected

UM10429

value

3.5.9 System PLL clock source select register

This register selects the clock source for the system PLL. The SYSPLLCLKUEN register

(see Section 3.5.10

Remark: When switching clock sources, both clocks must be running before the clock

source is updated.

Remark: When using the C_CAN controller with baudrates above 100 kbit/s, the system

oscillator must be selected.

T able 14. System PLL clock source select register (SYSPLLCLKSEL, address 0x4004 8040)

bit description

Bit Symbol Value Description Reset

1:0 SEL System PLL clock source 0x00

31:2 - - Reserved 0x00

) must be toggled from LOW to HIGH for the update to take effect.

0x0 IRC oscillator

0x1 System oscillator

0x2 Reserved

0x3 Reserved

value

UM10429 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

User manual Rev. 1 — 20 October 2010 16 of 258

Page 17

NXP Semiconductors

3.5.10 System PLL clock source update enable register

This register updates the clock source of the system PLL with the new input clock after the

SYSPLLCLKSEL register has been written to. In order for the update to take effect, first

write a zero to the SYSPLLUEN register and then write a one to SYSPLLUEN.

Remark: When switching clock sources, both clocks must be running before the clock

source is updated.

Table 15. System PLL clock source update enable register (SYSPLLUEN, address 0x4004

Bit Symbol Value Description Reset value

0 ENA Enable system PLL clock source update 0x0

31:1 - - Reserved 0x00

3.5.11 Main clock source select register

This register selects the main system clock which can be either any input to the system

PLL, the output from the system PLL (sys_pllclkout), or the watchdog or IRC oscillators

directly. The main system clock clocks the core, the peripherals, and the memories.

UM10429

Chapter 3: LPC1102 System configuration

8044) bit description

0 No change

1 Update clock source

The MAINCLKUEN register (see Section 3.5.12

) must be toggled from LOW to HIGH for

the update to take effect.

Remark: When switching clock sources, both clocks must be running before the clock

source is updated.

Remark: When using the C_CAN controller with baudrates above 100 kbit/s, the system

oscillator must be selected.

Table 16. Main clock source select register (MAINCLKSEL, address 0x4004 8070) bit

description

Bit Symbol Value Description Reset value

1:0 SEL Clock source for main clock 0x00

0x0 IRC oscillator

0x1 Input clock to system PLL

0x2 WDT oscillator

0x3 System PLL clock out

31:2 - - Reserved 0x00

3.5.12 Main clock source update enable register

This register updates the clock source of the main clock with the new input clock after the

MAINCLKSEL register has been written to. In order for the update to take effect, first write

a zero to the MAINCLKUEN register and then write a one to MAINCLKUEN.

Remark: When switching clock sources, both clocks must be running before the clock

source is updated.

UM10429 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

User manual Rev. 1 — 20 October 2010 17 of 258

Page 18

NXP Semiconductors

Table 17. Main clock source update enable register (MAINCLKUEN, address 0x4004 8074)

Bit Symbol Value Description Reset value

0 ENA Enable main clock source update 0x0

31:1 - - Reserved 0x00

3.5.13 System AHB clock divider register

This register divides the main clock to provide the system clock to the core, memories,

and the peripherals. The system clock can be shut down completely by setting the DIV

bits to 0x0.

Table 18. System AHB clock divider register (SYSAHBCLKDIV, address 0x4004 8078) bit

Bit Symbol Description Reset

7:0 DIV System AHB clock divider values

31:8 - Reserved 0x00

UM10429

Chapter 3: LPC1102 System configuration

bit description

0 No change

1 Update clock source

description

value

0x01

0: System clock disabled.

1: Divide by 1.

to

255: Divide by 255.

3.5.14 System AHB clock control register

The AHBCLKCTRL register enables the clocks to individual system and peripheral blocks.

The system clock (sys_ahb_clk[0], bit 0 in the AHBCLKCTRL register) provides the clock

for the AHB to APB bridge, the AHB matrix, the ARM Cortex- M 0, the Syscon block, and

the PMU. This clock cannot be disabled.

Table 19. System AHB clock control register (SYSAHBCLKCTRL , ad dress 0x4004 8080) bit

description

Bit Symbol Value Description Reset

0 SYS Enables clock for AHB to APB bridge, to the AHB

matrix, to the Cortex-M0 FCLK and HCLK, to the

SysCon, and to the PMU. This bit is read only.

0 Reserved

1 Enable

1 ROM Enables clock for ROM. 1

0 Disable

1 Enable

2 RAM Enables clock for RAM. 1

0 Disable

1 Enable

value

1

UM10429 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

User manual Rev. 1 — 20 October 2010 18 of 258

Page 19

NXP Semiconductors

Table 19. System AHB clock control register (SYSAHBCLKCTRL , ad dress 0x4004 8080) bit

Bit Symbol Value Description Reset

3 FLASHREG Enables clock for flash register interface. 1

4 FLASHARRAY Enables clock for flash array access. 1

5- Reserved. 0

6 GPIO Enables clock for GPIO. 1

7 CT16B0 Enables clock for 16-bit counter/timer 0. 0

8 CT16B1 Enables clock for 16-bit counter/timer 1. 0

9 CT32B0 Enables clock for 32-bit counter/timer 0. 0

10 CT32B1 Enables clock for 32-bit counter/timer 1. 0

11 SSP0 Enables clock for SPI0. 1

12 UART Enables clock for UART. Note that the UART pins

13 ADC Enables clock for ADC. 0

14 - Reserved 0

15 WDT Enables clock for WDT. 0

description

UM10429

Chapter 3: LPC1102 System configuration

…continued

value

0 Disabled

1 Enabled

0 Disabled

1 Enabled

0 Disable

1 Enable

0 Disable

1 Enable

0 Disable

1 Enable

0 Disable

1 Enable

0 Disable

1 Enable

0 Disable

1 Enable

0

must be configured in the IOCON block before the

UART clock can be enabled.

0 Disable

1 Enable

0 Disable

1 Enable

0 Disable

1 Enable

UM10429 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

User manual Rev. 1 — 20 October 2010 19 of 258

Page 20

NXP Semiconductors

Table 19. System AHB clock control register (SYSAHBCLKCTRL , ad dress 0x4004 8080) bit

Bit Symbol Value Description Reset

16 IOCON Enables clock for I/O configuration block. 0

31:17 - - Reserved 0x00

3.5.15 SPI0 clock divider register

This register configures the SPI0 peripheral clock SPI0_PCLK. The SPI0_PCLK can be

shut down by setting the DIV bits to 0x0.

Table 20. SPI0 clock divider register (SSP0CLKDIV, address 0x4004 8094) bit description

Bit Symbol Description Reset

7:0 DIV SPI0_PCLK clock divider values

31:8 - Reserved 0x00

description

0: Disable SPI0_PCLK.

1: Divide by 1.

to

255: Divide by 255.

UM10429

Chapter 3: LPC1102 System configuration

…continued

value

0 Disable

1 Enable

value

0x00

3.5.16 UART clock divider register

This register configures the UART peripheral clock UART_PCLK. The UART_PCLK can

be shut down by setting the DIV bits to 0x0.

Remark: Note that the UART pins must be configured in the IOCON block before the

UART clock can be enabled.

Table 21. UART clock divider register (UARTCLKDIV, address 0x4004 8098) bit description

Bit Symbol Description Reset

7:0 DIV U ART_PCLK clock divider values

0: Disable UART_PCLK.

1: Divide by 1.

to

255: Divide by 255.

31:8 - Reserved 0x00

3.5.17 WDT clock source select register

This register selects the clock source for the watchdog timer. The WDTCLKUEN register

(see Section 3.5.18

Remark: When switching clock sources, both clocks must be running before the clock

source is updated.

) must be toggled from LOW to HIGH for the update to take effect.

value

0x00

UM10429 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

User manual Rev. 1 — 20 October 2010 20 of 258

Page 21

NXP Semiconductors

Table 22. WDT clock source select register (WDTCLKSEL, address 0x4004 80D0) bit

Bit Symbol Value Description Reset

1:0 SEL WDT clock source 0x00

31:2 - - Reserved 0x00

3.5.18 WDT clock source update enable register

This register updates the clock source of the watchdog timer with the new input clock a fter

the WDTCLKSEL register has been written to. In order for the update to take effect at the

input of the watchdog timer, first write a zero to the WDTCLKUEN register and then write

a one to WDTCLKUEN.

UM10429

Chapter 3: LPC1102 System configuration

description

value

0x0 IRC oscillator

0x1 Main clock

0x2 Watchdog oscillator

0x3 Reserved

Remark: When switching clock sources, both clocks must be running before the clock

source is updated.

Table 23. WDT clock source update enable register (WDTCLKUEN, address 0x4004 80D4)

bit description

Bit Symbol Value Description Reset value

0 ENA Enable WDT clock source update 0x0

0 No change

1 Update clock source

31:1 - - Reserved 0x00

3.5.19 WDT clock divider register

This register determines the divider values for the watchdog clock wdt_clk.

Table 24. WDT clock divider register (WDTCLKDIV, address 0x4004 80D8) bit description

Bit Symbol Description Reset

7:0 DIV W DT clock divider values

0: Disable WDT_PCLK.

1: Divide by 1.

to

255: Divide by 255.

31:8 - Reserved 0x00

value

0x00

3.5.20 POR captured PIO status register 0

The PIOPORCAP0 register captures the state (HIGH or LOW) of the PIO pins of ports 0,1,

and 2 (pins PIO2_0 to PIO2_7) at power-on-reset. Each bit represents the reset state of

one GPIO pin. This register is a read-only status register.

UM10429 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

User manual Rev. 1 — 20 October 2010 21 of 258

Page 22

NXP Semiconductors

Table 25. POR captured PIO status registers 0 (PIOPORCAP0, address 0x4004 8100) bit

Bit Symbol Description Reset value

0 CAPPIO0_0 Raw reset status input PIO0_0 User implementation dependent

7:1 - Reserved. 8 CAPPIO0_8 Raw reset status input PIO0_8 User implementation dependent

9 CAPPIO0_9 Raw reset status input PIO0_9 User implementation dependent

10 CAPPIO0_10 Raw reset status input PIO0_10 User implementation dependent

1 1 CAPPIO0_11 Raw reset status input PIO0_11 User implementation dependent

12 CAPPIO1_0 Raw reset status input PIO1_0 User implementation dependent

13 CAPPIO1_1 Raw reset status input PIO1_1 User implementation dependent

14 CAPPIO1_2 Raw reset status input PIO1_2 User implementation dependent

15 CAPPIO1_3 Raw reset status input PIO1_3 User implementation dependent

17:16 - Reserved. 18 CAPPIO1_6 Raw reset status input PIO1_6 User implementation dependent

19 CAPPIO1_7 Raw reset status input PIO1_7 User implementation dependent

31:20 - Reserved. -

UM10429

Chapter 3: LPC1102 System configuration

description

3.5.21 BOD control register

The BOD control register selects four separate threshold values for sending a BOD

interrupt to the NVIC and for forced reset. Reset and interrupt threshold values listed in

Table 26

Table 26. BOD control register (BODCTRL, address 0x400 4 8150) bit description

Bit Symbol Value Description Reset

1:0 BODRSTLEV BOD reset level 00

3:2 BODINTVAL BOD interrupt level 00

are typical values.

0x0 Level 0: The reset assertion threshold voltage is 1.46 V; the

0x1 Level 1: The reset assertion threshold voltage is 2.06 V; the

0x2 Level 2: The reset assertion threshold voltage is 2.35 V; the

0x3 Level 3: The reset assertion threshold voltage is 2.63 V; the

0x0 Level 0: The interrupt assertion threshold voltage is 1.65 V;

0x1 Level 1:The interrupt assertion threshold voltage is 2.22 V;

0x2 Level 2: The interrupt assertion threshold voltage is 2.52 V;

0x3 Level 3: The interrupt assertion threshold voltage is 2.80 V;

value

reset de-assertion threshold voltage is 1.63 V.

reset de-assertion threshold voltage is 2.15 V.

reset de-assertion threshold voltage is 2.43 V.

reset de-assertion threshold voltage is 2.71 V.

the interrupt de-assertion threshold voltage is 1.80 V.

the interrupt de-assertion threshold voltage is 2.35 V.

the interrupt de-assertion threshold voltage is 2.66 V.

the interrupt de-assertion threshold voltage is 2.90 V.

UM10429 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

User manual Rev. 1 — 20 October 2010 22 of 258

Page 23

NXP Semiconductors

Table 26. BOD control register (BODCTRL, address 0x400 4 8150) bit description

Bit Symbol Value Description Reset

4 BODRSTENA BOD reset enable 0

31:5 - - Reserved 0x00

3.5.22 System tick counter calibration register

This register determines the value of the SYST_CALIB register (see Table 138).

Table 27. System tick timer calibration register (SYSTCKCAL, address 0x4004 8154) bit

Bit Symbol Value Description Reset

25:0 CAL System tick timer calibration value 0x04

31:26 - - Reserved 0x00

UM10429

Chapter 3: LPC1102 System configuration

value

0 Disable reset function.

1 Enable reset function.

description

value

3.5.23 Start logic edge control register 0

The STARTAPRP0 register controls the start logic input s of ports 0 (PIO0_0 to PIO0_11)

and 1 (PIO1_0). This register selects a falling or rising edge on the corresponding PIO

input to produce a falling or rising clock edge, respectively, for the start logic (see

Section 3.9.2

Every bit in the STARTAPRP0 register controls one port input and is connected to one

wake-up interrupt in the NVIC. Bit 0 in the STARTAPRP0 register corresponds to interrupt

0, bit 1 to interrupt 1, etc. (see Table 44

Remark: Each interrupt connected to a start log ic input must be enabled in the NVIC if the

corresponding PIO pin is used to wake up the chip from Deep-sleep mode.

Table 28. Start logic edge control register 0 (STARTAPRP0, address 0x4004 8200) bit

Bit Symbol Value Description Reset

0 APRPIO0_0 Edge select for start logic input PIO0_0 0x0

7:1 - - Reserved 0x0

8 APRPIO0_8 Edge select for start logic input PIO0_8 0x0

9 APRPIO0_9 Edge select for start logic input PIO0_9 0x0

).

), up to a total of 13 interrupts.

description

0 Falling edge

1 Rising edge

0 Falling edge

1 Rising edge

0 Falling edge

1 Rising edge

value

UM10429 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

User manual Rev. 1 — 20 October 2010 23 of 258

Page 24

NXP Semiconductors

Table 28. Start logic edge control register 0 (STARTAPRP0, address 0x4004 8200) bit

Bit Symbol Value Description Reset

10 APRPIO0_10 Edge select for start logic input PIO0_10 0x0

11 APRPIO0_11 Edge select for start logic input PIO0_11 0x0

12 APRPIO1_0 Edge select for start logic input PIO1_0. 0x0

31:13 - - Reserved 0x0

3.5.24 Start logic signal enable register 0

description

UM10429

Chapter 3: LPC1102 System configuration

…continued

value

0 Falling edge

1 Rising edge

0 Falling edge

1 Rising edge

0 Falling edge

1 Rising edge

This ST ARTERP0 reg ister enables or disables the st art signal bits in the st art logic. The bit

assignment is identical to Table 28

Table 29. Start logic signal enable register 0 (STARTERP0, address 0x4004 8204) bit

description

Bit Symbol Value Description Reset

0 ERPIO0_0 Enable start signal for start logic input PIO0_0 0 x 0

0 Disabled

1 Enabled

7:1 - Reserved 0x0

8 ERPIO0_8 Enable start signal for start logic input PIO0_8 0 x 0

0 Disabled

1 Enabled

9 ERPIO0_9 Enable start signal for start logic input PIO0_9 0 x 0

0 Disabled

1 Enabled

10 ERPIO0_10 Enable start signal for start logic input PIO0_10 0x0

0 Disabled

1 Enabled

11 ERPIO0_11 Enable start signal for start logic input PIO0_11 0x0

0 Disabled

1 Enabled

12 ERPIO1_0 Enable start signal for start logic input PIO1_0 0x0

0 Disabled

1 Enabled

31:13 - Reserved 0x0

.

value

UM10429 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

User manual Rev. 1 — 20 October 2010 24 of 258

Page 25

NXP Semiconductors

3.5.25 Start logic reset register 0

Writing a one to a bit in the STARTRSRP0CLR register resets the start logic state. The bit

assignment is identical to Table 28

clock edge for registering a start signal. This clock edge (falling or rising) sets the interrupt

for waking up from Deep-sleep mode. Therefore, the sta rt-up logic st ates must be cleared

before being used.

Table 30. Start logic reset register 0 (STARTRSRP0CLR, address 0x4004 8208) bit

Bit Symbol Value Description Reset

0 RSRPIO0_0 Start signal reset for start logic input PIO0_0 n/a

7:1 - - Reserved n/a

8 RSRPIO0_8 Start signal reset for start logic input PIO0_8 n/a

9 RSRPIO0_9 Start signal reset for start logic input PIO0_9 n/a

10 RSRPIO0_10 Start signal reset for start logic input PIO0_10 n/a

11 RSRPIO0_11 Start signal reset for start logic input PIO0_11 n/a

12 RSRPIO1_0 Start signal reset for start logic input PIO1_0 n/a

31:13 - - Reserved n/a

UM10429

Chapter 3: LPC1102 System configuration

. The start-up logic uses the input signals to generate a

description

value

01 Write: reset start signal

01 Write: reset start signal

01 Write: reset start signal

01 Write: reset start signal

01 Write: reset start signal

01 Write: reset start signal

3.5.26 Start logic status register 0

This register reflects the status of the enabled start signal bits. The bit assignment is

identical to Table 28

or not a wake-up signal has been received for a given pin.

Table 31. Start logic status register 0 (START SRP0, add ress 0x4004 820C) bit description

Bit Symbol Value Description Reset

0 SRPIO0_0 Start signal status for start logic input 0PIO0_0 n/a

7:1 - - Reserved n/a

UM10429 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

User manual Rev. 1 — 20 October 2010 25 of 258

. Each bit (if enabled) reflects the state of the start logic, i.e. whether

value

0 No start signal received

1 Start signal pending

Page 26

NXP Semiconductors

UM10429

Chapter 3: LPC1102 System configuration

Table 31. Start logic status register 0 (START SRP0, add ress 0x4004 820C) bit description

Bit Symbol Value Description Reset

value

8 SRPIO0_8 Start signal status for start logic input PIO0_8 n/a

0 No start signal received

1 Start signal pending

9 SRPIO0_9 Start signal status for start logic input PIO0_9 n/a

0 No start signal received

1 Start signal pending

10 SRPIO0_10 Start signal status for start logic input PIO0_10 n/a

0 No start signal received

1 Start signal pending

11 SRPIO0_11 Start signal status for start logic input PIO0_11 n/a

0 No start signal received

1 Start signal pending

12 SRPIO1_0 Start signal status for start logic input PIO1_0 n/a

0 No start signal received

1 Start signal pending

31:13 - - Reserved n/a

3.5.27 Deep-sleep mode configuration register

This register controls the behavior of the WatchDog (WD) oscillator and the BOD circuit

when the device enters Deep-sleep mode.

This register must be initialized at least once before entering Deep-sleep mode with

one of the four values shown in Table 32

Table 32. Allowed values for PDSLEEPCFG register

Configuration WD oscillator on WD oscillator off

BOD on PDSLEEPCFG = 0x0000 18B7 PDSLEEPCFG = 0x0000 18F7

BOD off PDSLEEPCFG = 0x0000 18BF PDSLEEPCFG = 0x0000 18FF

:

Remark: Failure to initialize and program this register correctly may result in undefined

behavior of the microcontroller. The values listed in Table 32

for PDSLEEPCFG register.

To select the appropriate power configuration for Deep-sleep mode, consider the

following:

• BOD: Leaving the BOD circuit enabled will protect the part from a low voltage event

occurring while the part is in Deep-sleep mode. However, the BOD circuit causes an

additional current drain in Deep-sleep mode.

• WD oscillator: The watchdog oscillator can be left running in Deep-sleep mode to

provide a clock for the watchdog timer or a general purpose timer if they are needed

for timing a wake-up event (see Section 3.9.3

oscillator analog output frequency must be set to its lowest value (bits FREQSEL in

for details). In this case, the watchdog

are the only values allowed

UM10429 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

User manual Rev. 1 — 20 October 2010 26 of 258

Page 27

NXP Semiconductors

Remark: Reserved bits in this register must always be written as indicated. This register

must be initialized correctly before entering Deep-sleep mode.

Table 33. Deep-sleep configuration register (PDSLEEPCFG, address 0x4004 8230) bit

Bit Symbol Value Description Reset

2:0 - Reserved. Always write these bits as 111. 0

3 BOD_PD BOD power-down control in Deep-sleep mode, see

5:4 - Reserved. Always write these bits as 11. 0

6 WDTOSC_PD Watchdog oscillator power control in Deep-sleep

7- Reserved. Always write this bit as 1. 0

10:8 - Reserved. Always write these bits as 000. 0

12:11 - Reserved. Always write these bits as 11. 0

31:13 - Reserved 0

UM10429

Chapter 3: LPC1102 System configuration

the WDTOSCCTRL = 0001, see Table 11) and all peripheral clocks other than the

timer clock must be disabled in the SYSAHBCLKCTRL register (see Table 19

entering Deep-sleep mode.

The watchdog oscillator, if running, contributes an additional current drain in

Deep-sleep mode.

description

Table 32

0 Powered

1 Powered down

mode, see Table 32

0 Powered

1 Powered down

.

.

) before

value

0

0

3.5.28 Wake-up configuration register

The bits in this register determine the state the chip enters when it is waking up from

Deep-sleep mode.

By default, the IRC and flash memory are powered and running and the BOD circuit is

enabled when the chip wakes up from Deep-sleep mode.

Remark: Reserved bits must be always written as indicated.

Table 34. Wake-up configuration register (PDAWAKECFG, address 0x4004 8234) bit

description

Bit Symbol Value Description Reset

value

0 IRCOUT_PD IRC oscillator output wake-up configuration 0

0 Powered

1 Pow ered down

1 IRC_PD IRC oscillator power-down wake-up configuration 0

0 Powered

1 Pow ered down

UM10429 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

User manual Rev. 1 — 20 October 2010 27 of 258

Page 28

NXP Semiconductors

Table 34. Wake-up configuration register (PDAWAKECFG, address 0x4004 8234) bit

Bit Symbol Value Description Reset

2 FLASH_PD Flash wake-up configuration 0

3 BOD_PD BOD wake-up configuration 0

4 ADC_PD ADC wake-up configuration 1

5 SYSOSC_PD System oscillator wake-up configuration 1

6 WDTOSC_PD Watchdog oscillator wake-up configuration 1

7 SYSPLL_PD System PLL wake-up configuration 1

8 - Reserved. Always write this bit as 1. 1

9 - Reserved. Always write this bit as 0. 0

10 - Reserved. Always write this bit as 1. 1

1 1 - Reserved. Always write this bit as 1. 1

12 - Reserved. Always write this bit as 0. 0

15:13 - Reserved. Always write these bits as 111. 111

31:16 - - Reserved -

description

UM10429

Chapter 3: LPC1102 System configuration

…continued

value

0 Powered

1 Pow ered down

0 Powered

1 Pow ered down

0 Powered

1 Pow ered down

0 Powered

1 Pow ered down

0 Powered

1 Pow ered down

0 Powered

1 Pow ered down

3.5.29 Power-down configuration register

The bits in the PDRUNCFG register control the power to the various analog blocks. This

register can be written to at any time while the chip is running, and a write will take effect

immediately with the exception of the power-down signal to the IRC.

To avoid glitches when powering down the IRC, the IRC clock is automatically switched off

at a clean point. Therefore, for the IRC a delay is possible before the power-down state

takes effect.

By default, the IRC and flash memory are powered and running and the BOD circuit is

enabled.

Remark: Reserved bits must be always written as indicated.

UM10429 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

User manual Rev. 1 — 20 October 2010 28 of 258

Page 29

NXP Semiconductors

Table 35. Power-down configuration register (PDRUNCFG, address 0x4004 8238) bit

Bit Symbol Value Description Reset

0 IRCOUT_PD IRC oscillator output power-down 0

1 IRC_PD IRC oscillator power-down 0

2 FLASH_PD Flash power-down 0

3 BOD_PD BOD power-down 0

4 ADC_PD ADC power-down 1

5 SYSOSC_PD System oscillator power-down 1

6 WDTOSC_PD Watchdog oscillator power-down 1

7 SYSPLL_PD System PLL power-down 1

8 - Reserved. Always write this bit as 1. 1

9 - Reserved. Always write this bit as 0. 0

10 - Reserved. Always write this bit as 1. 1

11 - Reserved. Always write this bit as 1. 1

12 - Reserved. Always write this bit as 0. 0

15:13 - Reserved. Always write these bits as 111. 111

31:16 - - Reserved -

UM10429

Chapter 3: LPC1102 System configuration

description

value

0 Powered

1 Powered down

0 Powered

1 Powered down

0 Powered

1 Powered down

0 Powered

1 Powered down

0 Powered

1 Powered down

0 Powered

1 Powered down

0 Powered

1 Powered down

0 Powered

1 Powered down

3.5.30 Device ID register

This device ID register is a read-only register and contains the part ID for each LPC1102

part. This register is also read by the ISP/IAP commands (Section 19.5.11

Table 36. Device ID register (DEVICE_ID, address 0x4004 83F4) bit d escription

Bit Symbol Description Reset value

31:0 DEVICEID Part ID numbers for LPC1102 parts

LPC1102 = 0x2500 102B

UM10429 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

User manual Rev. 1 — 20 October 2010 29 of 258

).

part-dependent

Page 30

NXP Semiconductors

3.6 Reset

Reset has four sources on the LPC1102: the RESET pin, Watchdog Reset, Power-On

Reset (POR), and Brown Out Detect (BOD). In addition, there is a software reset.

UM10429

Chapter 3: LPC1102 System configuration

The RESET

the operating voltage attains a usable level, starts the IRC causing reset to remain

asserted until the external Reset is de-asserted, the oscillator is running, and the flash

controller has completed its initialization.

On the assertion of a reset source external to the Cortex-M0 CPU (POR, BOD reset,

External reset, and Watchdog reset), the following processes are initiated:

1. The IRC starts up. After the IRC-start-up time (maximum of 6 μs on power-up), the

IRC provides a stable clock output.

2. The boot code in the ROM starts. The boot code per forms the boot tasks and may

jump to the flash.

3. The flash is powered up. This takes approximately 100 μs. Then the flash initialization

sequence is started, which takes about 250 cycles.

When the internal Reset is removed, the processor begins executing at address 0, which

is initially the Reset vector mapped from the boot block. At that point, all of the processor

and peripheral registers have been initialized to predetermined values.

3.7 Brown-out detection

The LPC1 10 2 includes four levels for m onitoring th e volta ge on the VDD pin. If this voltage

falls below one of the four selected levels, the BOD asserts an interrupt signal to the

NVIC. This signal can be enabled for interrupt in the Interr upt Enable Register in the NVIC

in order to cause a CPU interrupt; if not, software can monitor the signal by reading the

NVIC status register (see Table 44

cause a forced reset of the chip (see Table 26

pin is a Schmitt trigger input pin. Assertion of chip Reset by any source, once

). An additional four threshold levels can be selected to

).

3.8 Power management

The LPC1102 support a variety of power control features. In Active mode, when the chip

is running, power and clocks to selected peripherals can be optimized for power

consumption. In addition, there are three special modes of processor power reduction:

Sleep mode and Deep-sleep mode mode.

Remark: The Debug mode is not supported in Sleep or Deep-sleep mode.

3.8.1 Active mode

In Active mode, the ARM Cortex-M0 core and memories are clocked by the syste m clock,

and peripherals are clocked by the system clock or a dedicated peripheral clock.

The chip is in Active mode after reset and the default power configuration is determined

by the reset values of the PDRUNCFG and SYSAHBCLKCTRL registers. The power

configuration can be changed during run time.

UM10429 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

User manual Rev. 1 — 20 October 2010 30 of 258

Page 31

NXP Semiconductors

3.8.1.1 Power configuration in Active mode

Power consumption in Active mode is determined by the following configuration choices:

• The SYSAHBCLKCTRL register controls which memories and peripherals are

• The power to various analog blocks (PLL, oscillators, the ADC, the BOD circuit, and

• The clock source for the system clock can be selected from the IRC (default), the

• The system clock frequency can be selected by the SYSPLLCTRL (Table 8) and the

• Selected peripherals (UART, SPI0, WDT) use individual peripheral clocks with their

3.8.2 Sleep mode

UM10429

Chapter 3: LPC1102 System configuration

running (Table 19

the flash block) can be controlled at any time individually through the PDRUNCFG

register (Table 35

system oscillator, or the watchdog oscillator (see Figure 3

SYSAHBCLKDIV register (Table 18

own clock dividers. The peripheral clocks can be shut down through the

corresponding clock divider registers.

).

).

and related registers).

).

In Sleep mode, the system clock to the ARM Cortex-M0 core is stopped, an d execution o f

instructions is suspended until either a reset or an enabled interrupt occurs.

Peripheral functions, if selected to be clocked in the SYSAHBCLKCTRL regi ster, continue

operation during Sleep mode and may generate interrupts to cause the processor to

resume execution. Sleep mode eliminates dynamic power used by the processor itself,

memory systems and their related controllers, and internal buses. The processor sta te

and registers, peripheral registers, and int er na l SRAM va lue s ar e ma in tained, and th e

logic levels of the pins remain static.

3.8.2.1 Power configuration in Sleep mode

Power consumption in Sleep mode is configured by the same settings as in Active mode:

• The clock remains running.

• The system clock frequency remains the same as in Active mode, but the processor is

not clocked.

• Analog and digital peripherals are selected as in Active mode.

3.8.2.2 Programming Sleep mode

The following steps must be performed to enter Sleep mode:

1. The DPDEN bit in the PCON register must be set to zero (Table 41

2. The SLEEPDEEP bit in the ARM Cortex-M0 SCR register must be set to zero, see

(Table 225

3. Use the ARM Cortex-M0 Wait-For-Interrupt (WFI) instruction.

).

).

UM10429 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

User manual Rev. 1 — 20 October 2010 31 of 258

Page 32

NXP Semiconductors

3.8.2.3 Wake-up from Sleep mode

Sleep mode is exited automatically when an interrupt enabled by the NVIC arrives at the

processor or a reset occurs. After wake-up due to an in te rr upt, the micr ocontr olle r returns

to its original power configuration defined by the contents of the PDRUNCFG and the

SYSAHBCLKDIV registers. If a reset occurs, the microcontroller enters the default

configuration in Active mode.

3.8.3 Deep-sleep mode

In Deep-sleep mode, the system clock to the processor is disabled as in Sleep mode. All

analog blocks are powered down, except for the BOD circuit and the watchdog oscillator,

which must be selected or deselected during Deep-sleep mode in the PDSLEEPCFG

register.

Deep-sleep mode eliminates all power used by the flash and analog peripherals and all

dynamic power used by the processor itself, memory systems and their related

controllers, and internal buses. The processor state and registers, peripheral registers,

and internal SRAM values are maintained, and the logic levels of the pins remain static.

UM10429

Chapter 3: LPC1102 System configuration

3.8.3.1 Power configuration in Deep-sleep mode

Power consumption in Deep-sleep mode is determined by the Deep-sleep power

configuration setting in the PDSLEEPCFG (Table 33

• The only clock source available in Deep-sleep mode is the watchdog oscillator. The

watchdog oscillator can be left running in Deep-sleep mode if required for

timer-controlled wake-up (see Section 3.9.3

system oscillator) and the system PLL are shut down. The watchdog oscillator analog

output frequency must be set to the lowest value of its analog clock output (bits

FREQSEL in the WDTOSCCTRL = 0001, see Table 11

• The BOD circuit can be left running in Deep-slee p mode if r equir ed b y th e a pplication .

• If the watchdog oscillator is running in Deep-sleep mode, only the watchdog timer or

one of the general-purpose timers should be enabled in SYSAHBCLKCTRL register

to minimize power consumption.

3.8.3.2 Programming Deep-sleep mode

The following steps must be performed to enter Deep-sleep mode:

1. The DPDEN bit in the PCON register must be set to zero (Table 41

2. Select the power configuration in Deep-sleep mode in the PDSLEEPCFG (Table 33

register.

a. If a timer-controlled wake-up is needed, ensure that the watchdog oscillator is

powered in the PDRUNCFG register and switch the clock source to WD oscillator

in the MAINCLKSEL register (Table 16

b. If no timer-controlled wake-up is needed and the watchdog oscillator is shut down,

ensure that the IRC is powered in the PDRUNCFG register and switch the clock

source to IRC in the MAINCLKSEL register (Table 16

system clock is shut down glitch-free.

3. Select the power configuration after wake-up in the PDAWAKECFG (Table 34

register.

).

) register:

). All other clock sources (the IRC and

).

).

)

). This ensures that the

)

UM10429 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

User manual Rev. 1 — 20 October 2010 32 of 258

Page 33

NXP Semiconductors

4. If an external pin is used for wake-up, enable and clear the wake-up pin in the start

5. In the SYSAHBCLKCTRL register (Table 19

6. Write one to the SLEEPDEEP bit in the ARM Cortex-M0 SCR register (Table 225

7. Use the ARM WFI instruction.

3.8.3.3 Wake-up from Deep-sleep mode

The microcontroller can wake up from Deep-sleep mode in the following ways:

• Signal on an external pin. For this purpose, pins PIO0_0, PIO0_8 to PIO0_11, and

• Input signal to the start logic created by a match event on one of the g ene ral pur po se

• Reset from the BOD circuit. In this case, the BOD circuit must be enabled in the

• Reset from the watchdog timer. In this case, the watchdog oscillator must be running

• A reset signal from the external RESET pin.

UM10429

Chapter 3: LPC1102 System configuration

logic registers (Table 28

counter/timer or WDT if needed.

PIO1_0 can be enabled as inputs to the start logic. The start logic does not require

any clocks and generates the interrupt if enabled in the NVIC to wake up from

Deep-sleep mode.

timer external match outputs. The pin holding the timer match function must be

enabled as start logic input in the NVIC, the corresponding timer must be enabled in

the SYSAHBCLKCTRL register, and the watchdog oscillator must be running in

Deep-sleep mode (for details see Section 3.9.3

PDSLEEPCFG register, and the BOD reset must be enabled in the BODCTRL

register (Table 26

in Deep-sleep mode (see PDSLEEPCFG register), and the WDT must be enabled in

the SYSAHBCLKCTRL register.

to Table 31), and enable the start logic interrupt in the NVIC.

), disable all peripherals except

).

).

).

Remark: If the watchdog oscillator is running in Deep-sleep mode, its frequency

determines the wake-up time causing the wake-up time to be longer than waking up with

the IRC.

3.9 Deep-sleep mode details

3.9.1 IRC oscillator

The IRC is the only oscillator on the LPC1102 that can always shut down glitch-free.

Therefore it is recommended that the user switches the clock source to IRC before the

chip enters Deep-sleep mode.

3.9.2 Start logic

The Deep-sleep mode is exited when the start logic indicates an interrupt to the ARM

core. The port pins PIO0_0 to PIO0_11 and PIO1_1 are connected to the start logic and

serve as wake-up pins. The user must program the start logic registers for each input to

set the appropriate edge polarity for the corresponding wake-up event. Furthermore, the

interrupts corresponding to each input must be enabled in the NVIC (see Section 3.5.23

UM10429 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

User manual Rev. 1 — 20 October 2010 33 of 258

).

Page 34

NXP Semiconductors

The start logic does not require a clock to run because it uses the input signals on the

enabled pins to generate a clock edge when enabled. Therefore, the start logic signals

should be cleared (see Table 30

The start logic can also be used in Active mode to provide a vectored interrupt using the

LPC1102’s input pins.

3.9.3 Using the general purpose counter/timers to create a self-wake-up event

If enabled in Deep-sleep mode through the SYSAHBCLKCFG register, the counter/timers

can count clock cycles of the watchdog oscillator and create a match event when the

number of cycles equals a preset match value. The match event causes the

corresponding match output pin to go HIGH, LOW, or toggle. The state of the match

output pin is also monitored by the start logic and can trigger a wake- up interrupt if that pin

is enabled in the NVIC and the start logic trigger is configured accordingly in the start lo gic

edge control register (see Table 28

The following steps must be performed to configure the counter/timer and create a timed

Deep-sleep self-wake-up event:

UM10429

Chapter 3: LPC1102 System configuration

) before use.

).

1. Configure the port pin as match output in the IOCONFIG block. Select from pins

PIO0_8 to PIO0_11, which are inputs to the start logic and also hold a match output

function.

2. In the corresponding counter/timer, set the match value, and configure the match

output for the selected pin.

3. Select the watchdog oscillator to run in Deep-sleep mode in the PDSLEEPCFG

register.

4. Switch the clock source to the watchdog oscillator in the MAINCLKSEL register

(Table 16

5. Enable the pin, configure its edge detect function, and reset the start logic in the start

logic registers (Table 28

6. Disable all other peripherals in the SYSAHBCLKCTRL register.

7. Ensure that the DPDEN bit in the PCON register is set to zero (Table 41

8. Write one to the SLEEPDEEP bit in the ARM Cortex-M0 SCR register (Table 225

9. Start the counter/timer.

10. Use the ARM WFI instruction to enter Deep-sleep mode.

) and ensure the watchdog oscillator is powered in the PDRUNCFG register.

to Table 31), and enable the interrupt in the NVIC.

3.10 System PLL functional description

The LPC1102 uses the system PLL to create the clocks for the core and peripherals.

).

).

UM10429 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

User manual Rev. 1 — 20 October 2010 34 of 258

Page 35

NXP Semiconductors

LOCK

DETECT

PFD

FCLKOUT

pd

analog section

pd

cd

/M

/2P

cd

PSEL<1:0>

pd

2

MSEL<4:0>

5

irc_osc_clk

sys_osc_clk

SYSPLLCLKSEL

FCLKIN

FCCO

LOCK

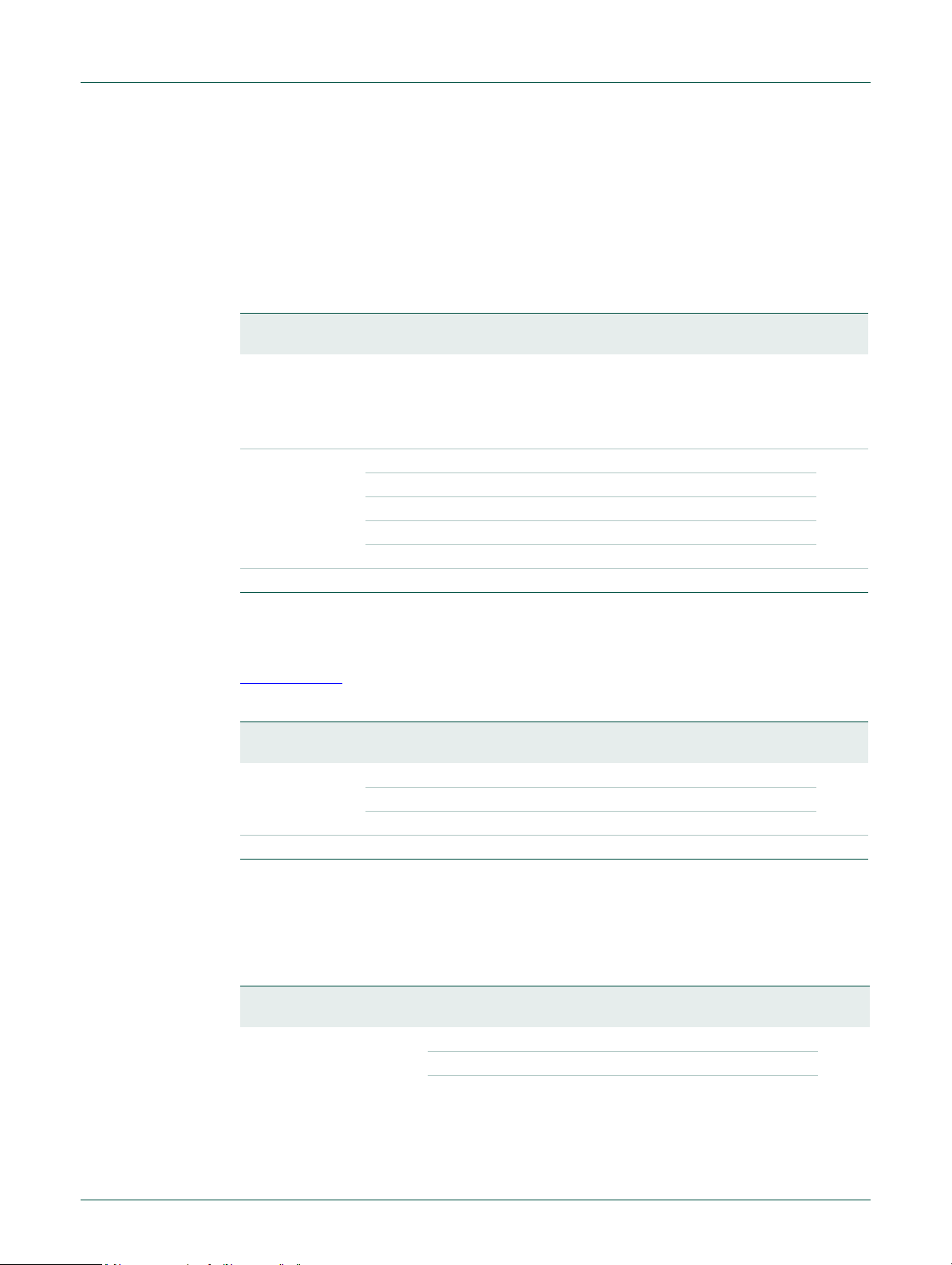

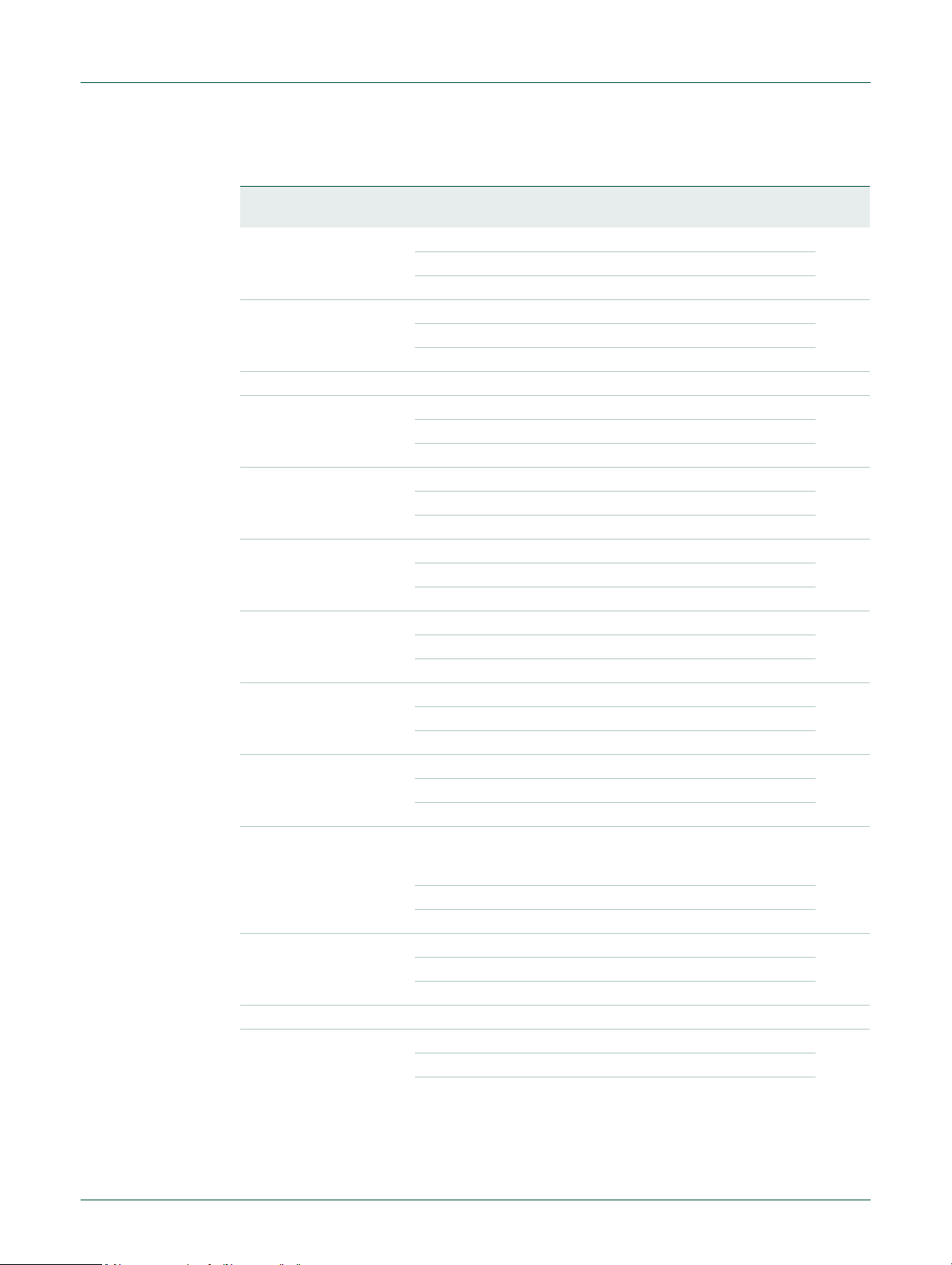

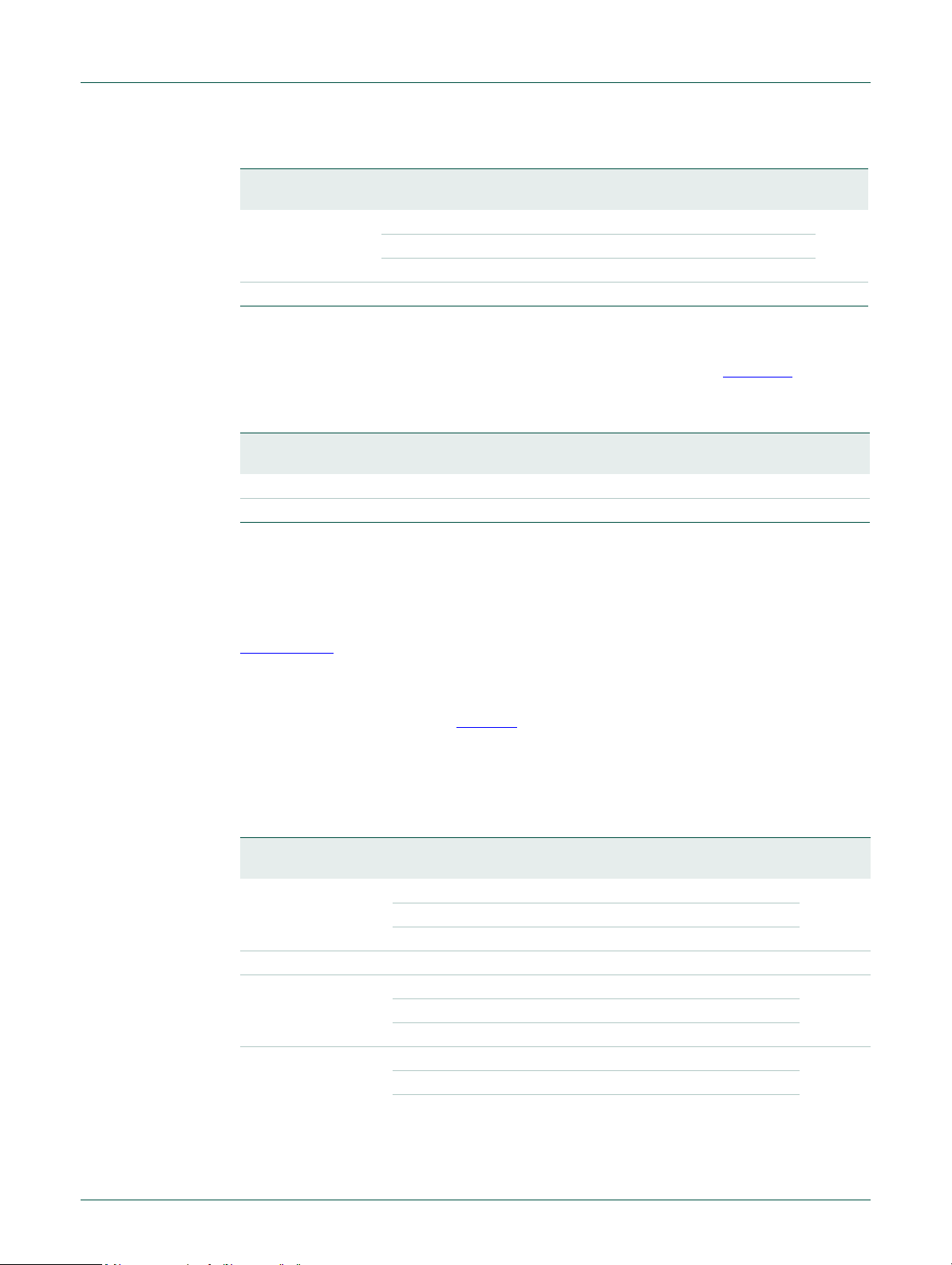

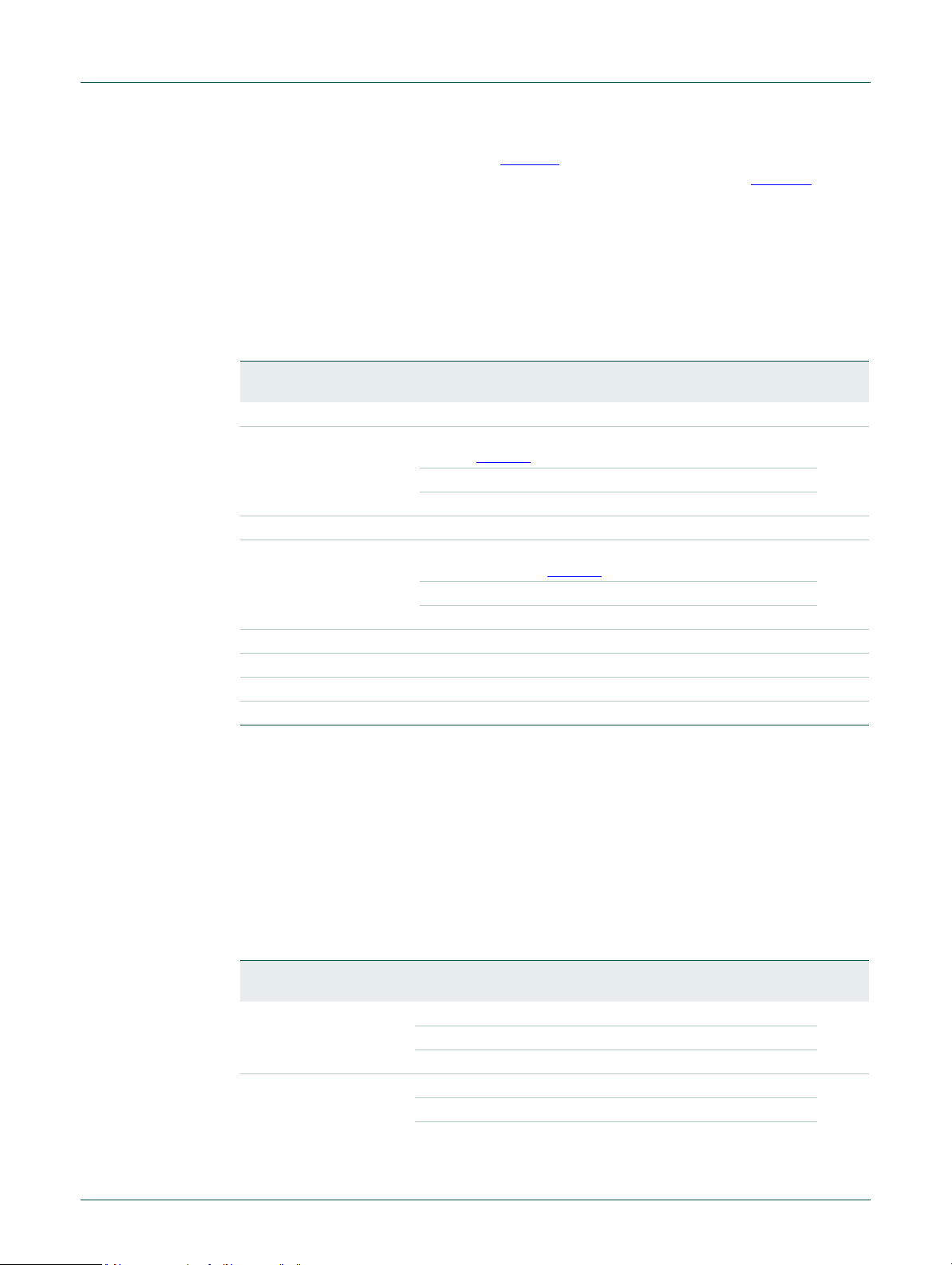

Fig 4. System PLL block diagram

UM10429

Chapter 3: LPC1102 System configuration

The block diagram of this PLL is shown in Figure 4. The input frequency range is 10 MHz

to 25 MHz. The input clock is fed directly to the Phase-Fr eque n cy Det ector (PFD). This

block compares the phase and frequency of its inputs, and generates a control signal

when phase and/ or frequency do not match. The loop filter filters these control signals

and drives the current controlled oscillator (CCO), which generates the main clock and

optionally two additional phases. The CCO frequency range is 156 MHz to

320 MHz.These clocks are either divided by 2×P by the programmable post divider to

create the output clock(s), or are sent directly to the output(s). The main output clock is

then divided by M by the programmable feedback divider to generate the feedback clock.

The output signal of the phase-frequency detector is a lso monitored by the lock detector,

to signal when the PLL has locked on to the input clock.

Remark: The divider values for P and M must be selected so that the PLL output clock

frequency FCLKOUT is lower than 100 MHz.

3.10.1 Lock detector

The lock detector measures the phase difference between the rising edges of the input

and feedback clocks. Only when this difference is smaller than the so called “lock

criterion” for more than eight consecutive input clock periods, the lock output switches

from low to high. A single too large phase difference immediately resets the counter and

causes the lock signal to drop (if it was high). Requiring eig h t phas e measurements in a

row to be below a certain figure ensures that the lock detector will not indicate lock until

both the phase and frequency of the input and feedback clocks are very well aligned. This

effectively prevents false lock indications, and thus ensures a glitch free lock signal.

3.10.2 Power-down control

To reduce the power consumption when the PLL clock is not needed, a Power-down

mode has been incorporated. This mode is enabled by setting the SYSPLL_PD bits to one

in the Power-down configuration register (Table 35

reference will be turned off, the oscillator and the phase-frequency detector will be

UM10429 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

User manual Rev. 1 — 20 October 2010 35 of 258

). In this mode, the internal current

Page 36

NXP Semiconductors

FCLKOUT M FCLKIN× FCCO()2P×()⁄==

stopped and the dividers will enter a reset state. While in Power-down mode, the lock

output will be low to indicate that the PLL is not in lock. When the Power-down mode is

terminated by setting the SYSPLL_PD bits to zero, the PLL will resume its normal

operation and will make the lock signal high once it has regained lock on the input clock.

3.10.3 Divider ratio programming

Post divider

The division ratio of the post divider is controlled by the PSEL bits. The division ratio is two

times the value of P selected by PSEL bits as shown in Table 8

output clock with a 50% duty cycle.

Feedback divider

The feedback divider’s division ratio is controlled by the MSEL bits. The division ratio

between the PLL ’s outp ut clock and the input clock is the decim al value on MSEL bits p lus

one, as specified in Table 8

Changing the divider values

Changing the divider ratio while the PLL is running is not recommended. As there is no

way to synchronize the change of the MSEL and PSEL values with the dividers, the risk

exists that the counter will read in an undefined value, which could lead to unwanted

spikes or drops in the frequency of the output clock. The recommended way of changing

between divider settings is to power down the PLL, ad just the divider settings and then le t

the PLL start up again.

UM10429

Chapter 3: LPC1102 System configuration

. This guarantees an

.

3.10.4 Frequency selection

The PLL frequency equations use the following parameters (also see Figure 3):

Table 37. PLL frequency parameters

Parameter System PLL

FCLKIN Frequency of sys_pllclkin (input clock to the system PLL) from the

SYSPLLCLKSEL multiplexer (see Section 3.5.9

FCCO Frequency of the Current Controlled Osci llator (CCO); 156 to 320 MHz.

FCLKOUT Frequency of sys_pllclkout

P System PLL post divider ratio; PSEL bits in SYSPLLCTRL (see Section 3.5.3

M System PLL feedback divider register; MSEL bits in SYSPLLCTRL (see

Section 3.5.3

3.10.4.1 Normal mode

In normal mode the post divider is enabled, giving a 50% duty cycle clock with the

following frequency relations:

To select the appropriate values for M and P, it is recommended to follow these steps:

).

).

).

(1)

UM10429 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

User manual Rev. 1 — 20 October 2010 36 of 258

Page 37

NXP Semiconductors

1. Specify the input clock frequency FCLKIN.

2. Calculate M to obtain the desired output frequency FCLKOUT with

3. Find a value so that FCCO = 2 × P × FCLKOUT.

4. Verify that all fr equencies and divider values conform to the limits specified in Table 8

5. Ensure that FCLKOUT < 100 MHz.

UM10429

Chapter 3: LPC1102 System configuration

M = FCLKOUT / FCLKIN.

.

Table 38

shows how to configure the PLL for a 12 MHz crystal oscillator using the

SYSPLLCTRL register (Table 8

system clock divider SYSAHBCLKDIV is set to one (see Table 18

T able 38. PLL configuration examples

PLL input

clock

sys_pllclkin

(FCLKIN)

12 MHz 48 MHz 00011 4 01 2 192 MHz

12 MHz 36 MHz 00010 3 10 4 288 MHz

12 MHz 24 MHz 00001 2 10 4 192 MHz

3.10.4.2 Power-down mode

In this mode, the internal current reference will be turned off, the oscillator and the

phase-frequency detector will be stopped and the dividers will enter a reset state. While in

Power-down mode, the lock output will be low, to indicate that the PLL is not in lock. When

the Power-down mode is terminated by setting the SYSPLL_PD bit to zero in the

Power-down configuration register (Table 35

and will make the lock signal HIGH once it has regained lock on the input clock.

3.11 Flash memory access

Main clock

(FCLKOUT)

). The main clock is equivalent to the system clock if the

).

MSEL bits

Table 8

M divider

value

PSEL bits

Table 8

P divider

value

FCCO

frequency

), the PLL will resume its normal operation

Depending on the system clock frequency, access to the flash memory can be configured

with various access times by writing to the FLASHCFG register at address 0x4003 C010.

This register is part of the flash configuration block (see Figure 2

).

Remark: Improper setting of this register may result in incorrect operation of th e LPC1102

flash memory.

UM10429 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

User manual Rev. 1 — 20 October 2010 37 of 258

Page 38

NXP Semiconductors

Table 39. Flash configuration register (FLASHCFG, address 0x4003 C010) bit description

Bit Symbol Value Description Reset

1:0 FLASHTIM Flash memory access time. FLASHTIM +1 is equal to the

31:2 - - Reserved. User software must not change the value of

UM10429

Chapter 3: LPC1102 System configuration

value

10

number of system clocks used for flash access.

0x0 1 system clock flash access time (for system clock

frequencies of up to 20 MHz).

0x1 2 system clocks flash access time (for system clock

frequencies of up to 40 MHz).

0x2 3 system clocks flash access time (for system clock

frequencies of up to 50 MHz).

0x3 Reserved.

<tbd>

these bits. Bits 31:2 must be written back exactly as read.

UM10429 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

User manual Rev. 1 — 20 October 2010 38 of 258

Page 39

UM10429

Chapter 4: LPC1102 PMU (Power Management Unit)

Rev. 1 — 20 October 2010 User manual

4.1 Introduction

The PMU allows access to the power mode status.

4.2 Register description

Table 40. Register overview: PMU (base address 0x4003 8000)

Name Access Address

PCON R/W 0x000 Power control register 0x0

4.2.1 Power control register

The power control register provides the flags for active or Sleep/Deep- sleep modes.

Table 41. Power control register (PCON, address 0x4003 8000) bit description

Bit Symbol Value Description Reset

0 - Reserved. This bit must always be written as 0. 0x0

1 - Reserved. This bit must always be written as 0. 0

7:2 - Reserved. These bits must always be written as 0. 0x0

8 SLEEPFLAG Sleep mode flag 0

11:9 - Reserved. These bits must always be written as 0. 0x0

1 1 - Reserved. This bit must always be written as 0. 0x0

31:12 - Reserved. Do not write ones to this bit. 0x0

Description Reset

offset

0 Read: No powe r-down mode entered. LPC1102 is in

Active mode.