Page 1

CBT3126

Quad FET bus switch

Rev. 02 — 23 October 2008 Product data sheet

1. General description

The CBT3126 is a quadruple FET bus switch features independent line switches. Each

switch is disabled when the associated Output Enable (OE) input is LOW.

The CBT3126 is characterized for operation from −40 °Cto+85°C.

2. Features

n Standard ’126-type pinout

n Multiple package options

n 5 Ω switch connection between two ports

n TTL-compatible input levels

n Minimal propagation delay through the switch

n Latch-up protection exceeds 500 mA per JEDEC standard JESD78 class II level A

n ESD protection:

u HBM JESD22-A114E exceeds 2000 V

u MM JESD22-A115-A exceeds 200 V

u CDM JESD22-C101C exceeds 1000 V

n Specified from −40 °Cto+85°C

3. Ordering information

Table 1. Ordering information

Type number Temperature range Package

Name Description Version

CBT3126D −40 °Cto+85°C SO14 plastic small outline package; 14 leads;

body width 3.9 mm

CBT3126DB −40 °Cto+85°C SSOP14 plastic shrink small outline package; 14 leads;

body width 5.3 mm

SOT108-1

SOT337-1

Page 2

NXP Semiconductors

CBT3126

Quad FET bus switch

Table 1. Ordering information

…continued

Type number Temperature range Package

Name Description Version

CBT3126DS −40 °Cto+85°C SSOP16

[1]

plastic shrink small outline package; 16 leads;

body width 3.9 mm; leadpitch 0.635 mm

CBT3126PW −40 °Cto+85°C TSSOP14 plastic thin shrink small outline package; 14 leads;

body width 4.4 mm

[1] Also known as QSOP16.

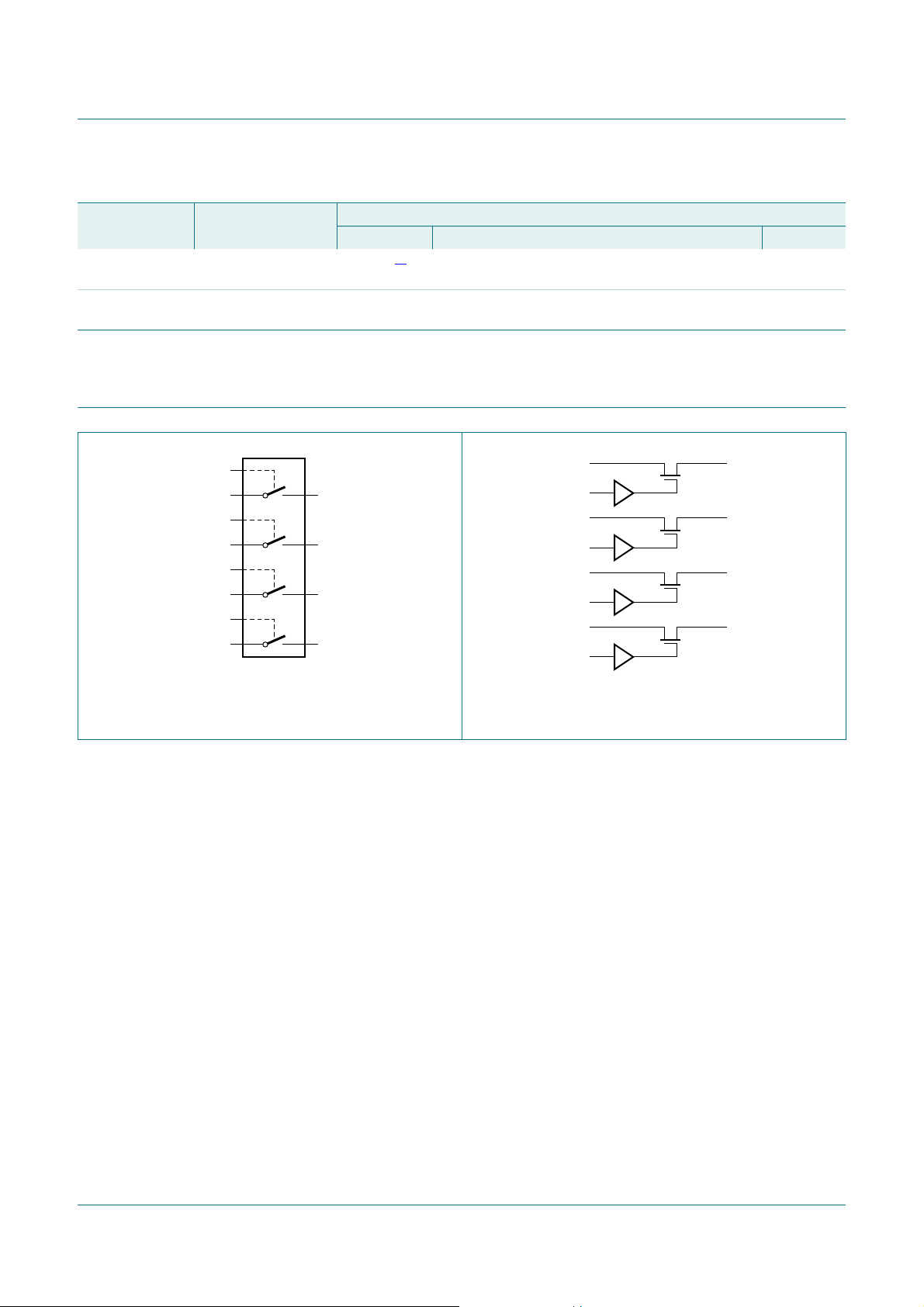

4. Functional diagram

23

1OE

1A 1B

2OE

2A 2B

3OE

3A 3B

4OE

4A 4B

001aaj023

1A

1

1OE

56

2A

4

2OE

98

3A

10

3OE

12 11

4A

13

4OE

001aaj024

SOT519-1

SOT402-1

1B

2B

3B

4B

Pin numbers are for the 14 pin packages.

Fig 1. Logic symbol Fig 2. Logic diagram

CBT3126_2 © NXP B.V. 2008. All rights reserved.

Product data sheet Rev. 02 — 23 October 2008 2 of 15

Page 3

NXP Semiconductors

5. Pinning information

5.1 Pinning

CBT3126

1

1OE V

2

1A 4OE

3

1B 4A

4

2OE 4B

5

2A 3OE

6

2B 3A

7

GND 3B

001aaj025

CBT3126

Quad FET bus switch

CBT3126

1

n.c. V

14

CC

13

12

11

10

9

8

2

1OE 4OE

3

1A 4A

4

1B 4B

5

2OE 3OE

6

2A 3A

7

2B 3B

8

GND n.c.

001aaj026

16

CC

15

14

13

12

11

10

9

Fig 3. Pin configuration SOT108-1 (SO14), SOT337-4

Fig 4. Pin configuration SOT519-1 (SSOP16)

(SSOP14) and SOT402-1 (TSSOP14)

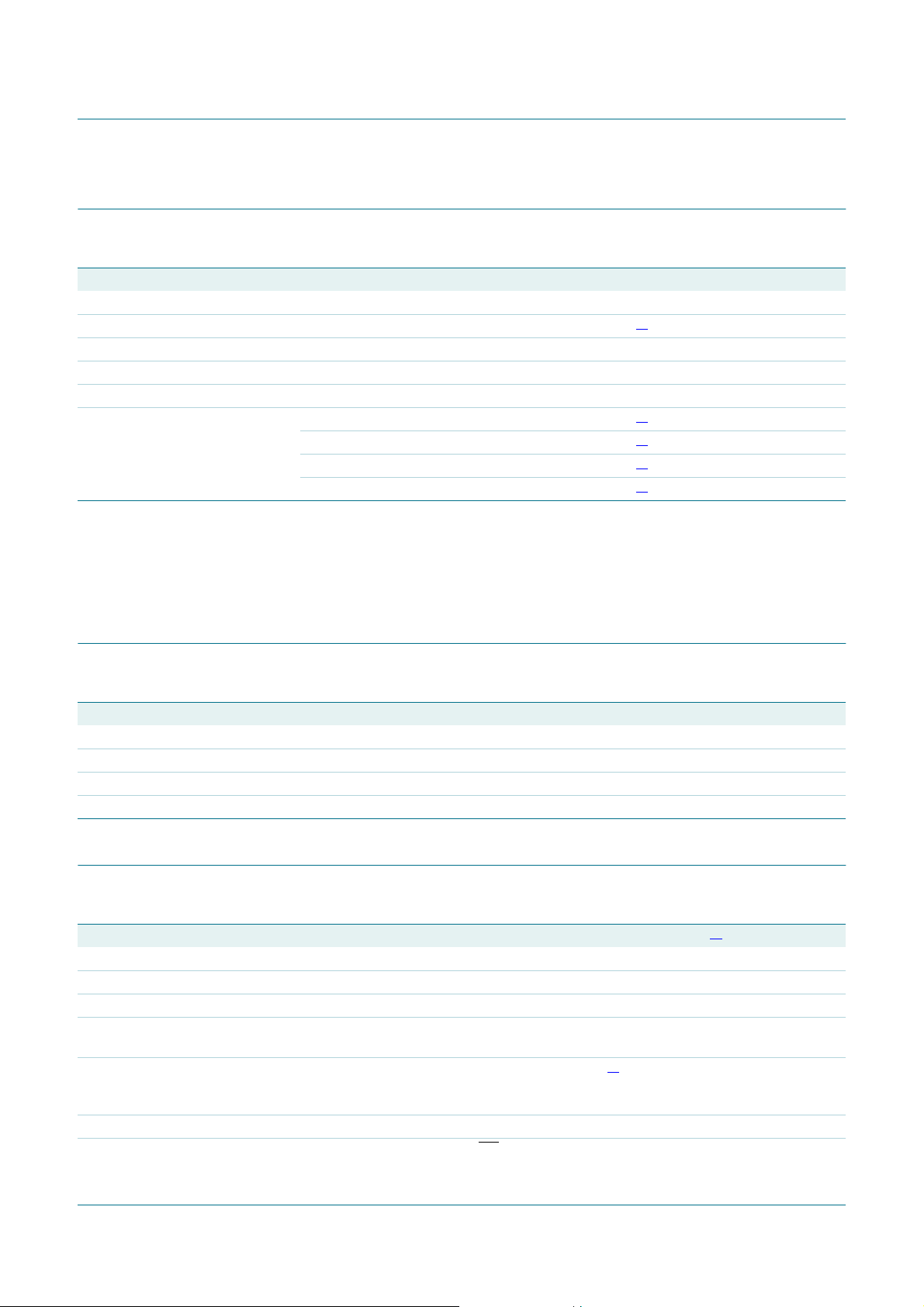

5.2 Pin description

Table 2. Pin description

Symbol Pin SOT108-1 SOT337-4

Pin SOT519-1 Description

and SOT402-1

1OE to 4OE 1, 4, 10, 13 2, 5, 12, 15 output enable input

1A to 4A, 2, 5, 9, 12 3, 6, 11, 14 A input/output

1B to 4B 3, 6, 8, 11 4, 7, 10, 13 B output/input

GND 7 8 ground (0 V)

V

CC

14 16 positive supply voltage

n.c. - 1, 9 not connected

6. Functional description

Table 3. Function selection

H = HIGH voltage level; L = LOW voltage level.

Inputs Switch

nOE

L nA to nB disconnected

H nA to nB connected

CBT3126_2 © NXP B.V. 2008. All rights reserved.

Product data sheet Rev. 02 — 23 October 2008 3 of 15

Page 4

NXP Semiconductors

CBT3126

Quad FET bus switch

7. Limiting values

Table 4. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

Symbol Parameter Conditions Min Max Unit

V

CC

V

I

I

CC

I

IK

T

stg

P

tot

[1] The input and output negative voltage ratings may be exceeded if the input and output clamp current ratings are observed.

[2] The package thermal impedance is calculated from JESD51-7.

[3] For SO14 package; P

[4] For SSOP14, SSOP16 and TSSOP14 packages; P

supply voltage −0.5 +7.0 V

input voltage

[1]

−0.5 +7.0 V

supply current continuous current through each VCC or GND pin - 128 mA

input clamping current VI<0V −50 - mA

storage temperature −65 +150 °C

total power dissipation T

derates linearly with 8 mW/K above 70 °C.

tot

= −40 °C to +125 °C

amb

SO14 package

SSOP14 and SSOP16 package

TSSOP14 package

derates linearly with 5.5 mW/K above 70 °C.

tot

[2]

[3]

- 500 mW

[4]

- 500 mW

[4]

- 500 mW

8. Recommended operating conditions

Table 5. Operating conditions

All unused control inputs of the device must be held at VCC or GND to ensure proper device operation.

Symbol Parameter Conditions Min Max Unit

V

CC

V

IH

V

IL

T

amb

supply voltage 4.5 5.5 V

HIGH-level input voltage 2.0 - V

LOW-level input voltage - 0.8 V

ambient temperature operating in free-air −40 +85 °C

9. Static characteristics

Table 6. Static characteristics

T

=−40°C to +85°C.

amb

Symbol Parameter Conditions Min Typ

V

V

I

I

∆I

C

C

I

CC

IK

pass

CC

I

io(off)

input clamping voltage VCC= 4.5 V; II= −18 mA - - −1.2 V

pass voltage VI=VCC= 5.0 V; IO= −100 µA - 3.8 - V

input leakage current VCC= 5.5 V; VI= GND or 5.5 V - - ±1 µA

supply current VCC= 5.5 V; IO= 0 mA;

V

I=VCC

or GND

additional supply current control pins; per input;

V

= 5.5 V; one input at 3.4 V,

CC

other inputs at V

or GND

CC

--3µA

[2]

- - 2.5 mA

input capacitance control pins; VI= 3 V or 0 V - 1.7 - pF

off-state input/output capacitance VO=3V or 0V;OE = V

CC

- 3.4 - pF

[1]

Max Unit

CBT3126_2 © NXP B.V. 2008. All rights reserved.

Product data sheet Rev. 02 — 23 October 2008 4 of 15

Page 5

NXP Semiconductors

CBT3126

Quad FET bus switch

Table 6. Static characteristics

T

=−40°C to +85°C.

amb

Symbol Parameter Conditions Min Typ

R

ON

ON resistance VCC= 4.0 V

…continued

[1]

Max Unit

[3]

VI= 2.4 V; II= 15 mA - 16 22 Ω

= 4.5 V

V

CC

=0V; II=64mA - 5 7 Ω

V

I

=0V; II=30mA - 5 7 Ω

V

I

= 2.4 V; II= 15 mA - 10 15 Ω

V

I

[1] All typical values are measured at VCC=5V; T

amb

=25°C.

[2] This is the increase in supply current for each input that is at the specified TTL voltage level rather than VCC or GND.

[3] Measured by the voltage drop between the A and the B terminals at the indicated current through the switch. ON resistance is

determined by the lowest voltage of the two (A or B) terminals.

10. Dynamic characteristics

Table 7. Dynamic characteristics

T

=−40°C to +85°C; VCC= 4.5 V to 5.5 V; for test circuit see Figure 7.

amb

Symbol Parameter Conditions Min Max Unit

t

pd

t

en

t

dis

propagation delay nA to nB or nB to nA; see Figure 5

enable time OE to nA or nB; see Figure 6

disable time OE to nA or nB; see Figure 6

[1][2]

- 0.25 ns

[2]

1.6 4.5 ns

[2]

1.0 5.4 ns

[1] This parameter is warranted but not production tested. The propagation delay is based on the RC time constant of the typical ON

resistance of the switch and a load capacitance, when driven by an ideal voltage source (zero output impedance).

[2] t

t

t

PLH

PZL

PLZ

and t

and t

and t

are the same as tpd;

PHL

are the same as ten;

PZH

are the same as t

PHZ

.

dis

11. AC waveforms

V

I

input

0 V

V

OH

output

V

OL

V

M

t

PHL

V

M

Measurement points are given in Table 8.

VOL and VOH are typical voltage output levels that occur with the output load.

Fig 5. The input (nA, nB) to output (nB, nA) propagation delay times

V

M

t

PLH

V

M

001aai367

CBT3126_2 © NXP B.V. 2008. All rights reserved.

Product data sheet Rev. 02 — 23 October 2008 5 of 15

Page 6

NXP Semiconductors

nOE input

output

LOW-to-OFF

OFF-to-LOW

output

HIGH-to-OFF

OFF-to-HIGH

Measurement points are given in Table 8.

VOL and VOH are typical voltage output levels that occur with the output load.

Fig 6. Enable and disable times

GND

V

CC

V

OL

V

OH

GND

CBT3126

Quad FET bus switch

V

I

V

M

t

PLZ

t

PHZ

switch

enabled

V

X

V

Y

disabled

switch

t

PZL

t

PZH

V

M

V

M

switch

enabled

001aaj027

Table 8. Measurement points

Input Output

V

M

V

M

V

X

V

Y

1.5 V 1.5 V VOL + 0.3 V VOH− 0.3 V

CBT3126_2 © NXP B.V. 2008. All rights reserved.

Product data sheet Rev. 02 — 23 October 2008 6 of 15

Page 7

NXP Semiconductors

12. Test information

negative

pulse

0 V

positive

pulse

0 V

CBT3126

Quad FET bus switch

t

V

CC

DUT

W

V

M

t

r

t

f

V

M

t

W

V

EXT

R

V

O

C

L

R

L

L

V

I

90 %

V

M

10 %

t

f

t

10 %

r

90 %

V

M

V

I

R

T

V

I

G

001aae331

Test data is given in Table 9.

Definitions for test circuit:

RL = Load resistance.

CL = Load capacitance including jig and probe capacitance.

RT = Termination resistance should be equal to the output impedance Zo of the pulse generator.

V

= External voltage for measuring switching times.

EXT

Fig 7. Test circuit for measuring switching times

Table 9. Test data

Supply voltage Input Load V

V

CC

V

I

tr, t

f

C

L

R

L

t

EXT

PLH

, t

PHL

t

PLZ

, t

PZL

t

PHZ

4.5 V to 5.5 V GND to 3.0 V ≤ 2.5 ns 50 pF 500 Ω open 7.0 V open

, t

PZH

CBT3126_2 © NXP B.V. 2008. All rights reserved.

Product data sheet Rev. 02 — 23 October 2008 7 of 15

Page 8

NXP Semiconductors

13. Package outline

CBT3126

Quad FET bus switch

SO16: plastic small outline package; 16 leads; body width 3.9 mm

D

c

y

Z

16

pin 1 index

1

e

9

8

w M

b

p

SOT109-1

E

H

E

A

2

A

1

detail X

A

X

v M

A

Q

(A )

L

p

L

A

3

θ

0 2.5 5 mm

scale

DIMENSIONS (inch dimensions are derived from the original mm dimensions)

mm

OUTLINE

VERSION

SOT109-1

A

max.

1.75

0.069

A1A2A

0.25

1.45

0.10

1.25

0.010

0.057

0.004

0.049

IEC JEDEC JEITA

076E07 MS-012

0.25

0.01

b

3

p

0.49

0.25

0.36

0.19

0.0100

0.019

0.0075

0.014

UNIT

inches

Note

1. Plastic or metal protrusions of 0.15 mm (0.006 inch) maximum per side are not included.

(1)E(1) (1)

cD

10.0

9.8

0.39

0.38

REFERENCES

eHELLpQZywv θ

4.0

3.8

0.16

0.15

1.27

0.05

6.2

5.8

0.244

0.228

1.05

0.041

1.0

0.4

0.039

0.016

0.7

0.25

0.6

0.028

0.01 0.004

0.020

EUROPEAN

PROJECTION

0.25 0.1

0.01

0.7

0.3

0.028

0.012

ISSUE DATE

99-12-27

03-02-19

o

8

o

0

Fig 8. Package outline SOT109-1 (SO16)

CBT3126_2 © NXP B.V. 2008. All rights reserved.

Product data sheet Rev. 02 — 23 October 2008 8 of 15

Page 9

NXP Semiconductors

CBT3126

Quad FET bus switch

SSOP16: plastic shrink small outline package; 16 leads; body width 5.3 mm

D

c

y

Z

16

pin 1 index

9

A

2

A

E

H

E

1

SOT338-1

A

X

v M

A

Q

(A )

L

p

L

A

3

θ

1

e

DIMENSIONS (mm are the original dimensions)

mm

OUTLINE

VERSION

SOT338-1

A

max.

2

0.21

0.05

b

p

3

1.80

1.65

IEC JEDEC JEITA

0.25

0.38

0.25

UNIT A1A2A

Note

1. Plastic or metal protrusions of 0.25 mm maximum per side are not included.

8

b

p

cD

0.20

6.4

0.09

6.0

REFERENCES

MO-150

w M

0 2.5 5 mm

scale

(1)E(1)

eHELLpQZywv θ

5.4

5.2

7.9

0.65 1.25

7.6

1.03

0.63

detail X

0.9

0.7

0.130.2 0.1

EUROPEAN

PROJECTION

(1)

1.00

0.55

ISSUE DATE

99-12-27

03-02-19

o

8

o

0

Fig 9. Package outline SOT338-1 (SSOP16)

CBT3126_2 © NXP B.V. 2008. All rights reserved.

Product data sheet Rev. 02 — 23 October 2008 9 of 15

Page 10

NXP Semiconductors

CBT3126

Quad FET bus switch

SSOP16: plastic shrink small outline package; 16 leads; body width 3.9 mm; lead pitch 0.635 mm

D

c

y

Z

16

1

e

9

A

2

A

1

8

w M

b

p

E

H

E

detail X

A

X

v M

(A )

L

p

L

A

3

θ

SOT519-1

A

0 2.5 5 mm

scale

DIMENSIONS (mm are the original dimensions)

mm

OUTLINE

VERSION

SOT519-1

A

max.

1.73

0.25

0.10

p

1.55

1.40

IEC JEDEC JEITA

0.25

0.31

0.20

0.25

0.18

UNIT A1A2A3b

Note

1. Plastic or metal protrusions of 0.2 mm maximum per side are not included.

(1)E(1)

cD

5.0

4.8

REFERENCES

eHELL

4.0

3.8

6.2

0.635 1

5.8

0.89

0.41

(1)

p

0.180.2 0.09

EUROPEAN

PROJECTION

Zywv θ

0.18

0.05

ISSUE DATE

99-05-04

03-02-18

o

8

o

0

Fig 10. Package outline SOT519-1 (SSOP16)

CBT3126_2 © NXP B.V. 2008. All rights reserved.

Product data sheet Rev. 02 — 23 October 2008 10 of 15

Page 11

NXP Semiconductors

CBT3126

Quad FET bus switch

TSSOP16: plastic thin shrink small outline package; 16 leads; body width 4.4 mm

D

c

y

Z

16

pin 1 index

9

A

2

18

w M

b

e

p

A

1

E

H

E

L

detail X

SOT403-1

A

X

v M

A

Q

(A )

3

A

θ

L

p

0 2.5 5 mm

scale

DIMENSIONS (mm are the original dimensions)

UNIT A1A2A

Notes

1. Plastic or metal protrusions of 0.15 mm maximum per side are not included.

2. Plastic interlead protrusions of 0.25 mm maximum per side are not included.

A

max.

0.15

mm

1.1

OUTLINE

VERSION

SOT403-1 MO-153

0.05

0.95

0.80

IEC JEDEC JEITA

0.25

b

3

p

0.30

0.19

(1)E(2) (1)

cD

0.2

5.1

0.1

4.9

REFERENCES

eHELLpQZywv θ

4.5

4.3

0.65

6.6

6.2

0.75

0.50

0.4

0.3

EUROPEAN

PROJECTION

0.13 0.10.21

0.40

0.06

ISSUE DATE

99-12-27

03-02-18

o

8

o

0

Fig 11. Package outline SOT403-1 (TSSOP16)

CBT3126_2 © NXP B.V. 2008. All rights reserved.

Product data sheet Rev. 02 — 23 October 2008 11 of 15

Page 12

NXP Semiconductors

CBT3126

Quad FET bus switch

DHVQFN16: plastic dual in-line compatible thermal enhanced very thin quad flat package; no leads;

16 terminals; body 2.5 x 3.5 x 0.85 mm

A

D

B

A

A

E

1

SOT763-1

c

terminal 1

index area

terminal 1

index area

L

1

E

h

16

DIMENSIONS (mm are the original dimensions)

Note

1. Plastic or metal protrusions of 0.075 mm maximum per side are not included.

(1)

A

UNIT

mm

OUTLINE

VERSION

SOT763-1 MO-241 - - -- - -

max.

A

0.05

0.00

1

e

27

15

c

b

0.30

0.2

0.18

IEC JEDEC JEITA

e

1

b

10

D

h

0 2.5 5 mm

D

2.15

1.85

h

(1)

E

E

h

2.6

1.15

2.4

0.85

REFERENCES

D

(1)

3.6

3.4

v

w

8

e

9

scale

0.51

2.5

detail X

C

y

X

ISSUE DATE

02-10-17

03-01-27

w

0.1v0.05

y

1

C

ye

0.05 0.1

y

1

EUROPEAN

PROJECTION

M

ACCB

M

e

L

1

0.5

0.3

Fig 12. Package outline SOT763-1 (DHVQFN16)

CBT3126_2 © NXP B.V. 2008. All rights reserved.

Product data sheet Rev. 02 — 23 October 2008 12 of 15

Page 13

NXP Semiconductors

CBT3126

Quad FET bus switch

14. Abbreviations

Table 10. Abbreviations

Acronym Description

CDM Charged Device Model

ESD ElectroStatic Discharge

HBM Human Body Model

MM Machine Model

TTL Transistor-Transistor Logic

15. Revision history

Table 11. Revision history

Document ID Release date Data sheet status Change notice Supersedes

CBT3126_2 20081023 Product data sheet - CBT3126_1

Modifications:

CBT3126_1 20011212 Product data sheet - -

• Theformat of this data sheet has been redesigned to comply with the newidentityguidelinesof

NXP Semiconductors.

• Legal texts have been adapted to the new company name where appropriate.

• Table 4 “Limiting values” P

• Section 10 “Dynamic characteristics” t

added.

tot

value updated.

dis

CBT3126_2 © NXP B.V. 2008. All rights reserved.

Product data sheet Rev. 02 — 23 October 2008 13 of 15

Page 14

NXP Semiconductors

16. Legal information

16.1 Data sheet status

CBT3126

Quad FET bus switch

Document status

Objective [short] data sheet Development This document contains data from the objective specification for product development.

Preliminary [short] data sheet Qualification This document contains data from the preliminary specification.

Product [short] data sheet Production This document contains the product specification.

[1] Please consult the most recently issued document before initiating or completing a design.

[2] The term ‘short data sheet’ is explained in section “Definitions”.

[3] The productstatus ofdevice(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status

information is available on the Internet at URL

[1][2]

Product status

16.2 Definitions

Draft — The document is a draft version only. The content is still under

internal review and subject to formal approval, which may result in

modifications or additions. NXP Semiconductors does not give any

representations or warranties as to the accuracy or completeness of

information included herein and shall have no liability for the consequences of

use of such information.

Short data sheet — A short data sheet is an extract from a full data sheet

with the same product type number(s) and title. A short data sheet is intended

for quick reference only and should not be relied upon to contain detailed and

full information. For detailed and full information see the relevant full data

sheet, which is available on request via the local NXP Semiconductors sales

office. In case of any inconsistency or conflict with the short data sheet, the

full data sheet shall prevail.

16.3 Disclaimers

General — Information in this document is believed to be accurate and

reliable. However, NXP Semiconductors does not give any representations or

warranties, expressed or implied, as to the accuracy or completeness of such

information and shall have no liability for the consequences of use of such

information.

Right to make changes — NXP Semiconductors reserves the right to make

changes to information published in this document, including without

limitation specifications and product descriptions, at any time and without

notice. This document supersedes and replaces all information supplied prior

to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed,

authorized or warranted to be suitable for use in medical, military, aircraft,

space or life support equipment, nor in applications where failure or

[3]

http://www.nxp.com.

Definition

malfunction of an NXP Semiconductors product can reasonably be expected

to result in personal injury, death or severe property or environmental

damage. NXP Semiconductors accepts no liability for inclusion and/or use of

NXP Semiconductors products in such equipment or applications and

therefore such inclusion and/or use is at the customer’s own risk.

Applications — Applications that are described herein for any of these

products are for illustrative purposes only. NXP Semiconductors makes no

representation or warranty that such applications will be suitable for the

specified use without further testing or modification.

Limiting values — Stress above one or more limiting values (as defined in

the Absolute Maximum Ratings System of IEC 60134) may cause permanent

damage to the device. Limiting values are stress ratings only and operation of

the device at these or any other conditions above those given in the

Characteristics sections of this document is not implied. Exposure to limiting

values for extended periods may affect device reliability.

Terms and conditions of sale — NXP Semiconductors products are sold

subject to the general terms and conditions of commercial sale, as published

at

http://www.nxp.com/profile/terms, including those pertaining to warranty,

intellectual property rights infringement and limitation of liability, unless

explicitly otherwise agreed to in writing by NXP Semiconductors. In case of

any inconsistency or conflict between information in this document and such

terms and conditions, the latter will prevail.

No offer to sell or license — Nothing in this document may be interpreted

or construed as an offer to sell products that is open for acceptance or the

grant, conveyanceor implication of any license under any copyrights, patents

or other industrial or intellectual property rights.

16.4 Trademarks

Notice: All referenced brands,product names, service names and trademarks

are the property of their respective owners.

17. Contact information

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: salesaddresses@nxp.com

CBT3126_2 © NXP B.V. 2008. All rights reserved.

Product data sheet Rev. 02 — 23 October 2008 14 of 15

Page 15

NXP Semiconductors

18. Contents

1 General description. . . . . . . . . . . . . . . . . . . . . . 1

2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

3 Ordering information. . . . . . . . . . . . . . . . . . . . . 1

4 Functional diagram . . . . . . . . . . . . . . . . . . . . . . 2

5 Pinning information. . . . . . . . . . . . . . . . . . . . . . 3

5.1 Pinning . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

5.2 Pin description . . . . . . . . . . . . . . . . . . . . . . . . . 3

6 Functional description . . . . . . . . . . . . . . . . . . . 3

7 Limiting values. . . . . . . . . . . . . . . . . . . . . . . . . . 4

8 Recommended operating conditions. . . . . . . . 4

9 Static characteristics. . . . . . . . . . . . . . . . . . . . . 4

10 Dynamic characteristics . . . . . . . . . . . . . . . . . . 5

11 AC waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . 5

12 Test information. . . . . . . . . . . . . . . . . . . . . . . . . 7

13 Package outline . . . . . . . . . . . . . . . . . . . . . . . . . 8

14 Abbreviations. . . . . . . . . . . . . . . . . . . . . . . . . . 13

15 Revision history. . . . . . . . . . . . . . . . . . . . . . . . 13

16 Legal information. . . . . . . . . . . . . . . . . . . . . . . 14

16.1 Data sheet status . . . . . . . . . . . . . . . . . . . . . . 14

16.2 Definitions. . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

16.3 Disclaimers. . . . . . . . . . . . . . . . . . . . . . . . . . . 14

16.4 Trademarks. . . . . . . . . . . . . . . . . . . . . . . . . . . 14

17 Contact information. . . . . . . . . . . . . . . . . . . . . 14

18 Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

CBT3126

Quad FET bus switch

Please be aware that important notices concerning this document and the product(s)

described herein, have been included in section ‘Legal information’.

© NXP B.V. 2008. All rights reserved.

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: salesaddresses@nxp.com

Date of release: 23 October 2008

Document identifier: CBT3126_2

Loading...

Loading...