Page 1

现货库存、技术资料、百科信息、热点资讯,精彩尽在鼎好!

TDA18271HD

Silicon Tuner IC

Rev. 03 — 11 September 2008 Product data sheet

1. General description

The TDA18271HD is a Silicon Tuner IC designed mainly for terrestrial analog and digital

TV reception. The TDA18271HD integrates the overall tuning function, including

selectivity.

The TDA18271HD is compatible with all analog and digital TV standards and delivers a

low IF signal to a demodulator (for analog TV) and/or channel decoder (for digital TV).

This specification is based on software version 3.4.

2. Features

n Fully integrated RF tracking filters for unwanted signal suppression

n Fully integrated IF selectivity (no need for external SAW filters)

n Worldwide multistandard terrestrial (all analog and digital worldwide terrestrial

n Integrated loop-through and slave tuner output for straightforward multi-silicon tuner

n Fully integrated oscillators with no external components

n Alignment free

n Integrated wide-band gain control

n Single 3.3 V power supply

n Low power consumption

n Crystal oscillator output buffer (16 MHz) for single crystal applications

n I2C-bus interface compatible with 3.3 V and 5 V microcontrollers

n Three Standby modes

n RoHS packaging

3. Applications

3.1 Target applications

n Hybrid (analog and digital TV) for PCTV, DVD-R and TV applications

n Application optimization is described in application notes

standards supported)

application

AN602,AN604

and

AN605

Page 2

NXP Semiconductors

3.2 Key benefits

n The TDA18271HD is a Silicon Tuner targeting digital and analog TV applications. The

aim is to match the performance of conventional Can tuners while reducing the sizeof

the tuner function. Additionally, the following benefits are provided:

u Easy on-board integration

u Easy dual tuner configuration

u Drastic size reduction of the tuner function and power consumption

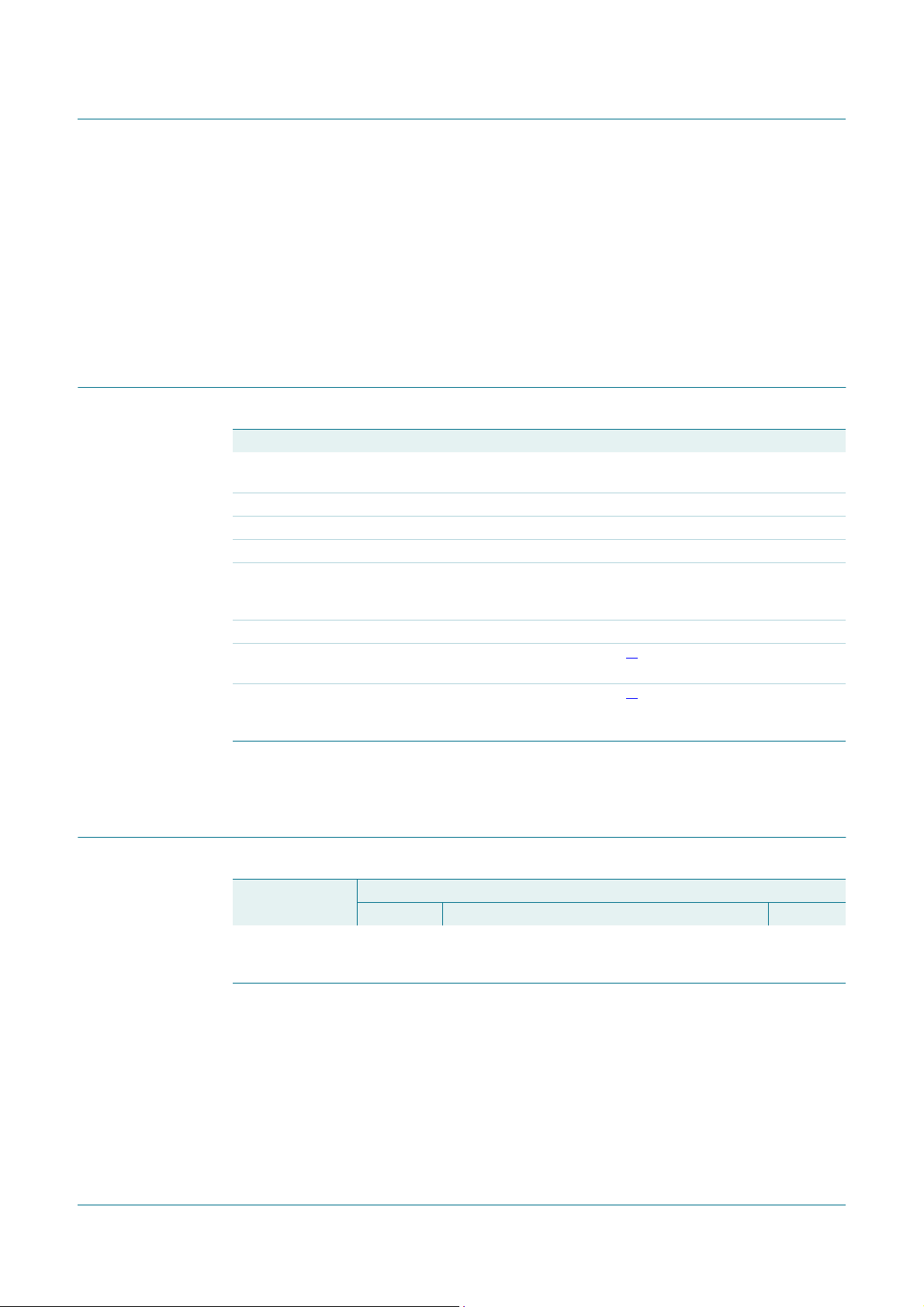

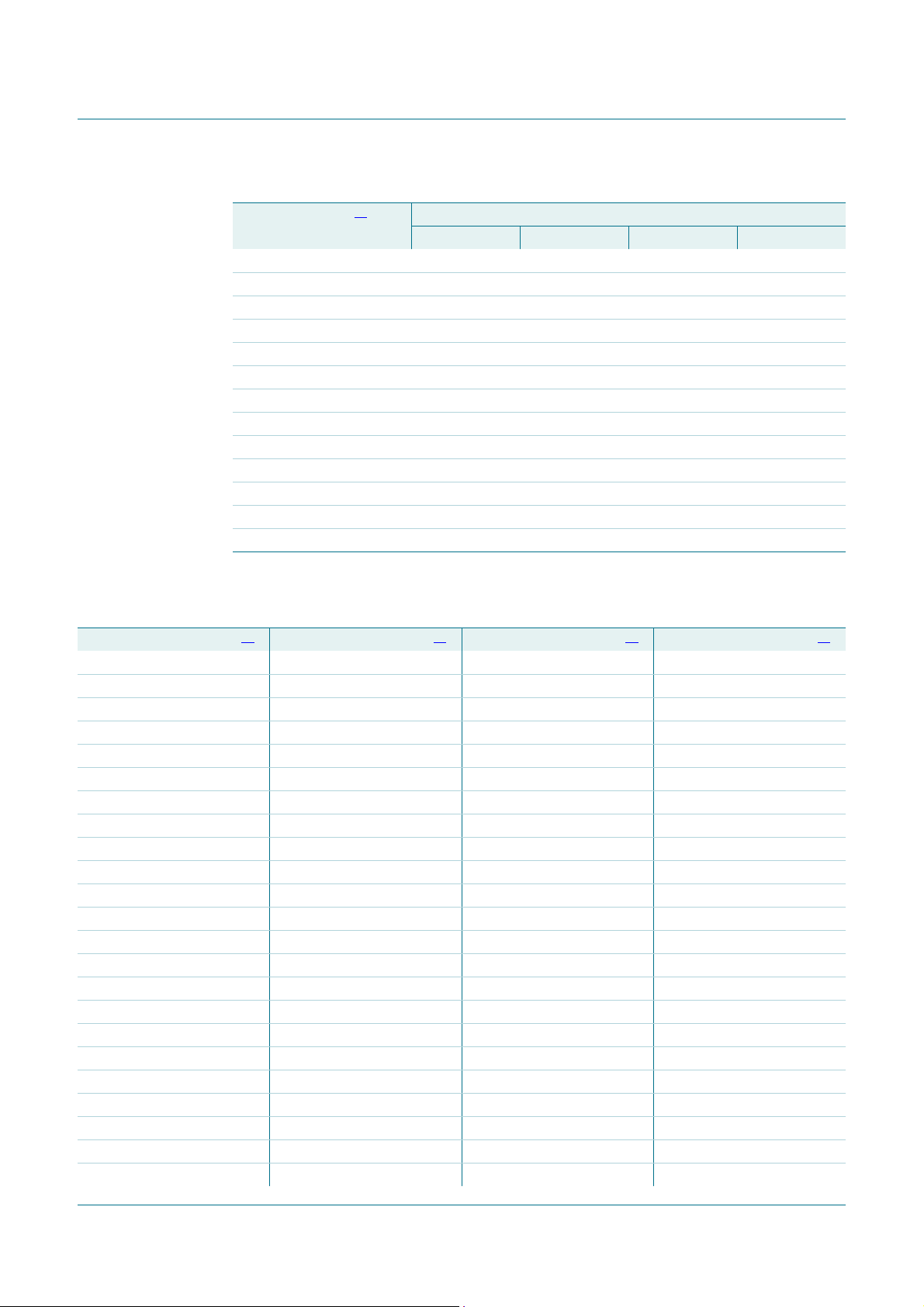

4. Quick reference data

Table 1. Quick reference data

Symbol Parameter Conditions Min Typ Max Unit

f

RF(STO)

NF

ϕ

n

P power dissipation - 780 - mW

V

i(max)

α

image

S

dig

S

a

RF frequency on pin

STO

tuner noise figure maximum gain - 5.5 - dB

tun

phase noise 1 kHz and 10 kHz - −89 - dBc/Hz

maximum input voltage 1dBgain compression,

image rejection - 65 - dB

digital sensitivity DVB-T (64 QAM2⁄3);

analog sensitivity 50 dB video SNR

TDA18271HD

Silicon Tuner IC

slave tuner output 45 - 864 MHz

- 103 - dBµV

oneanalog TVsignalat

RF input (−5 dBm)

[1]

BER = 2.10

weighted 22 dBµV

(color loss)

−4

- −82 - dBm

[2]

-58-dBµV

[1] Measured with TDA10048HN channel decoder.

[2] Measured with TDA8295 IF modulator.

5. Ordering information

Table 2. Ordering information

Type number Package

Name Description Version

TDA18271HD/C2 HLQFN64R plastic thermal enhanced low profile quad flat

package; no leads; 64 terminals; resin based;

body 9 × 9 × 1.6 mm

TDA18271HD_3 © NXP B.V. 2008. All rights reserved.

Product data sheet Rev. 03 — 11 September 2008 2 of 69

SOT903-1

Page 3

NXP Semiconductors

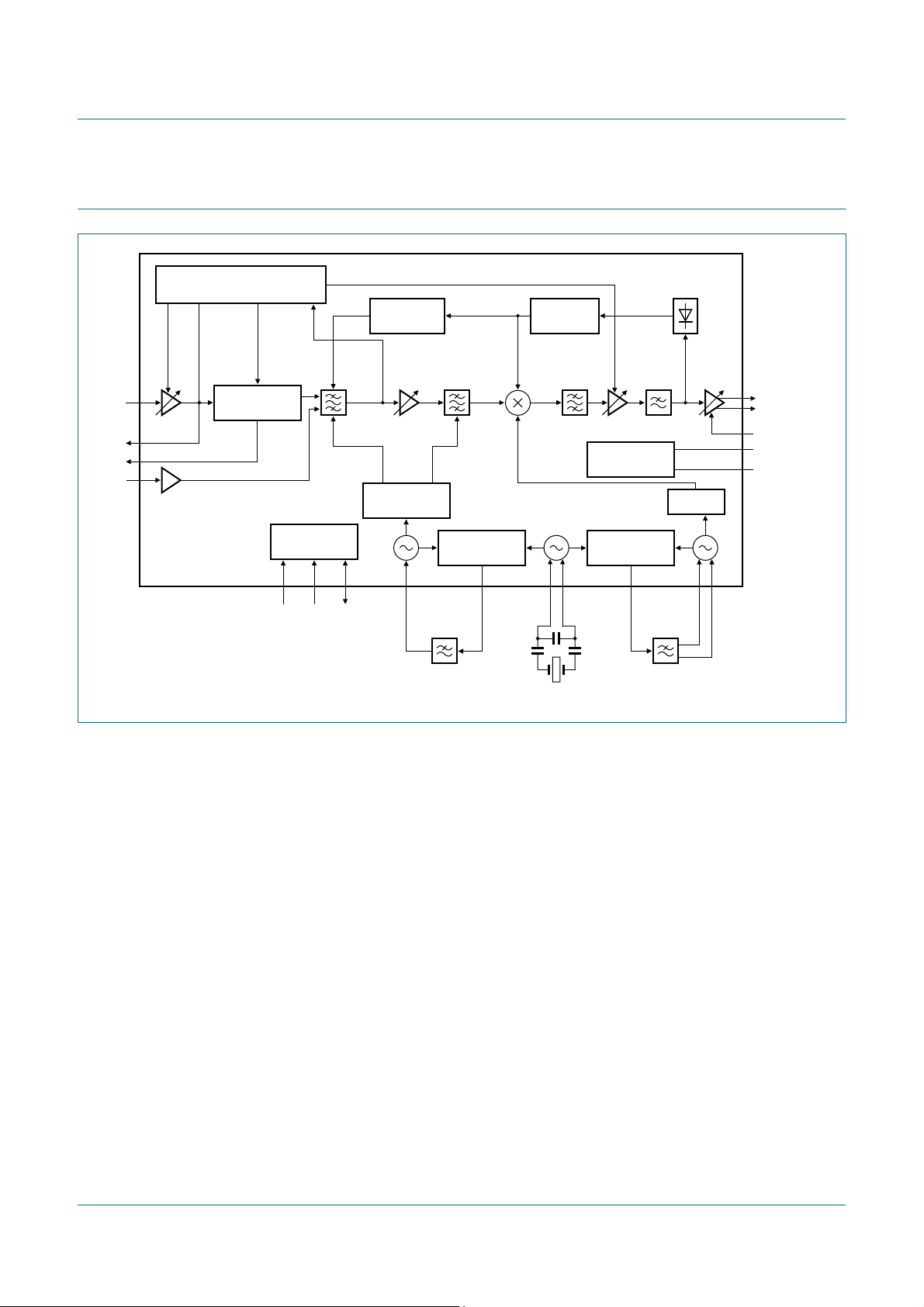

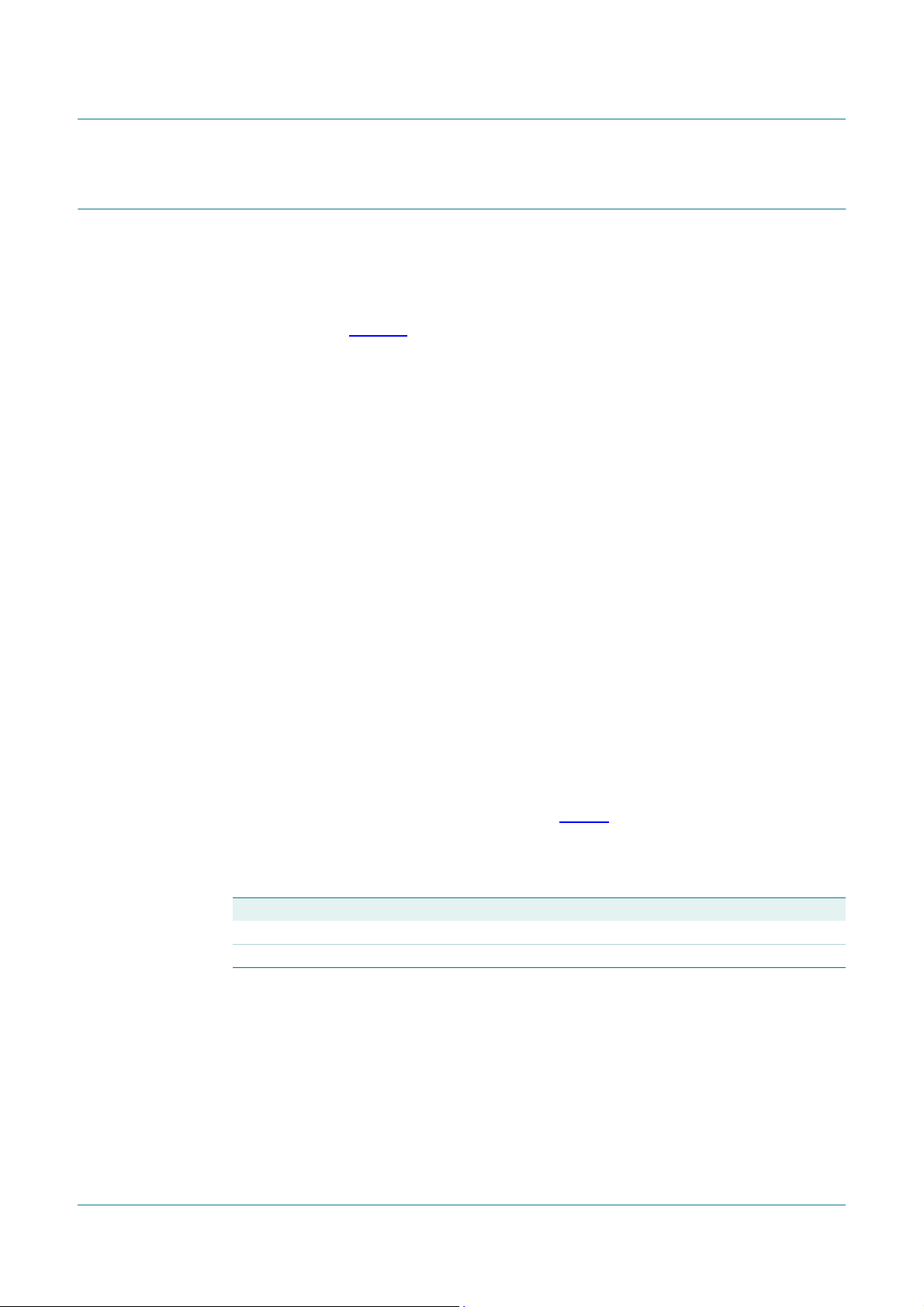

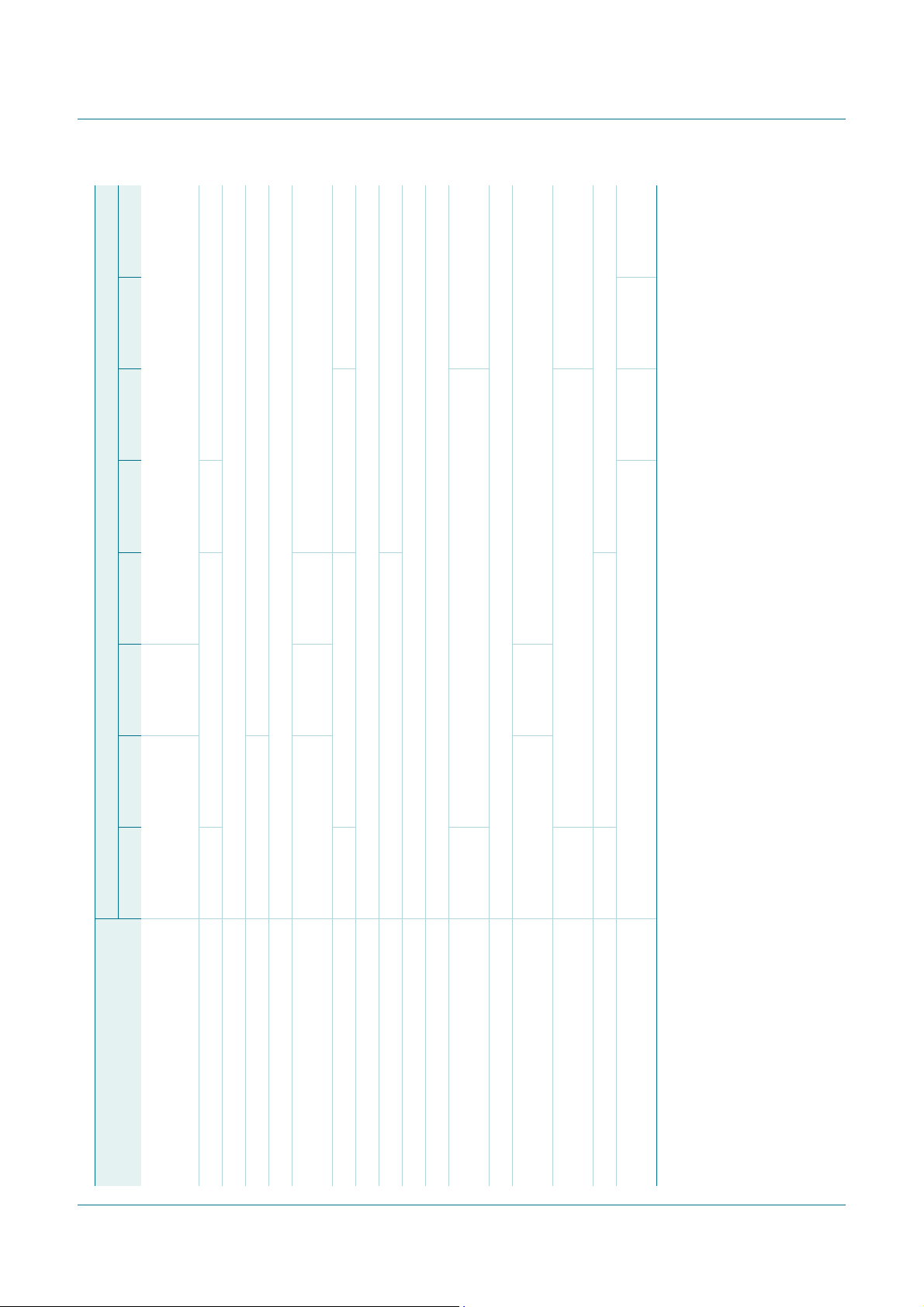

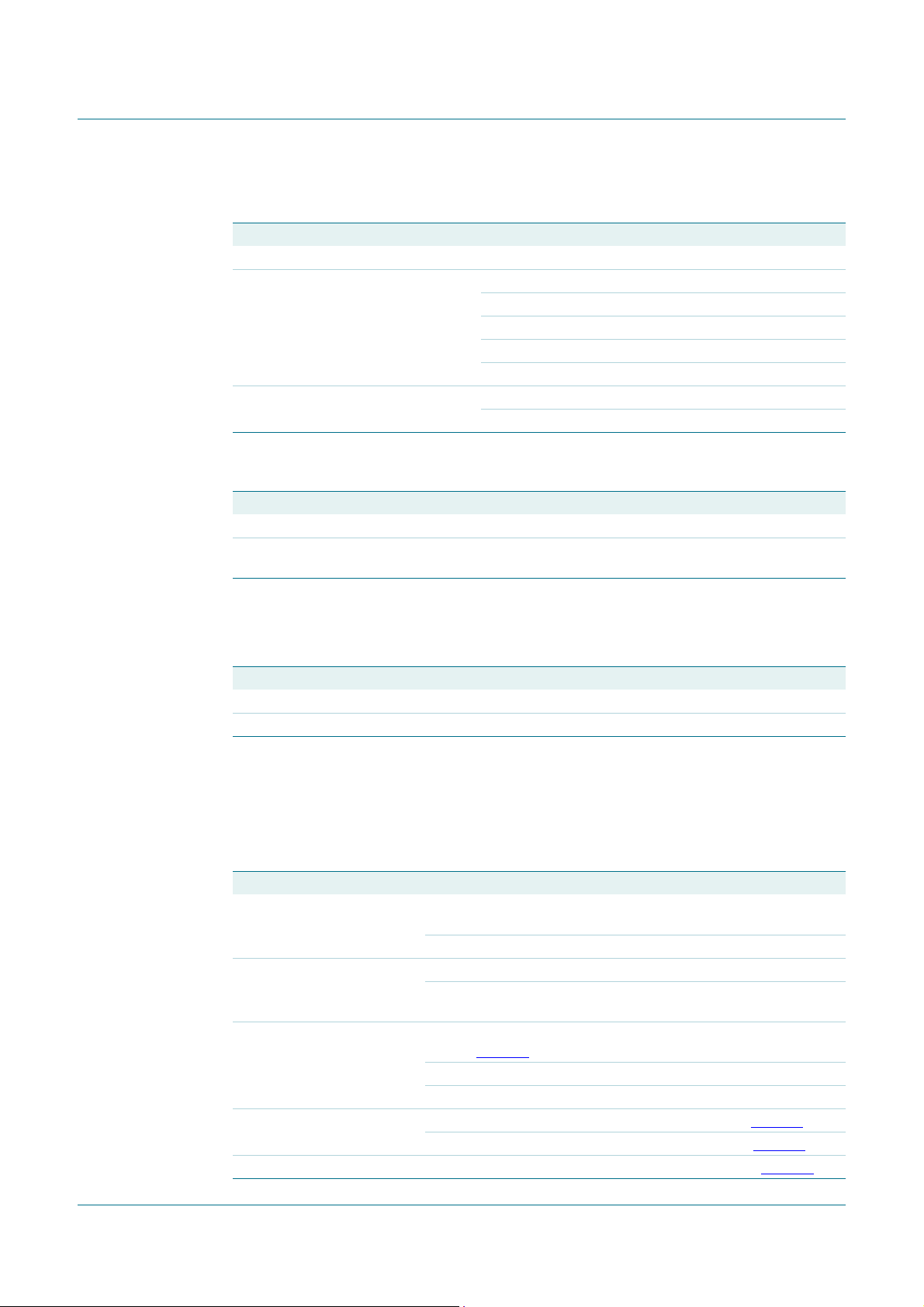

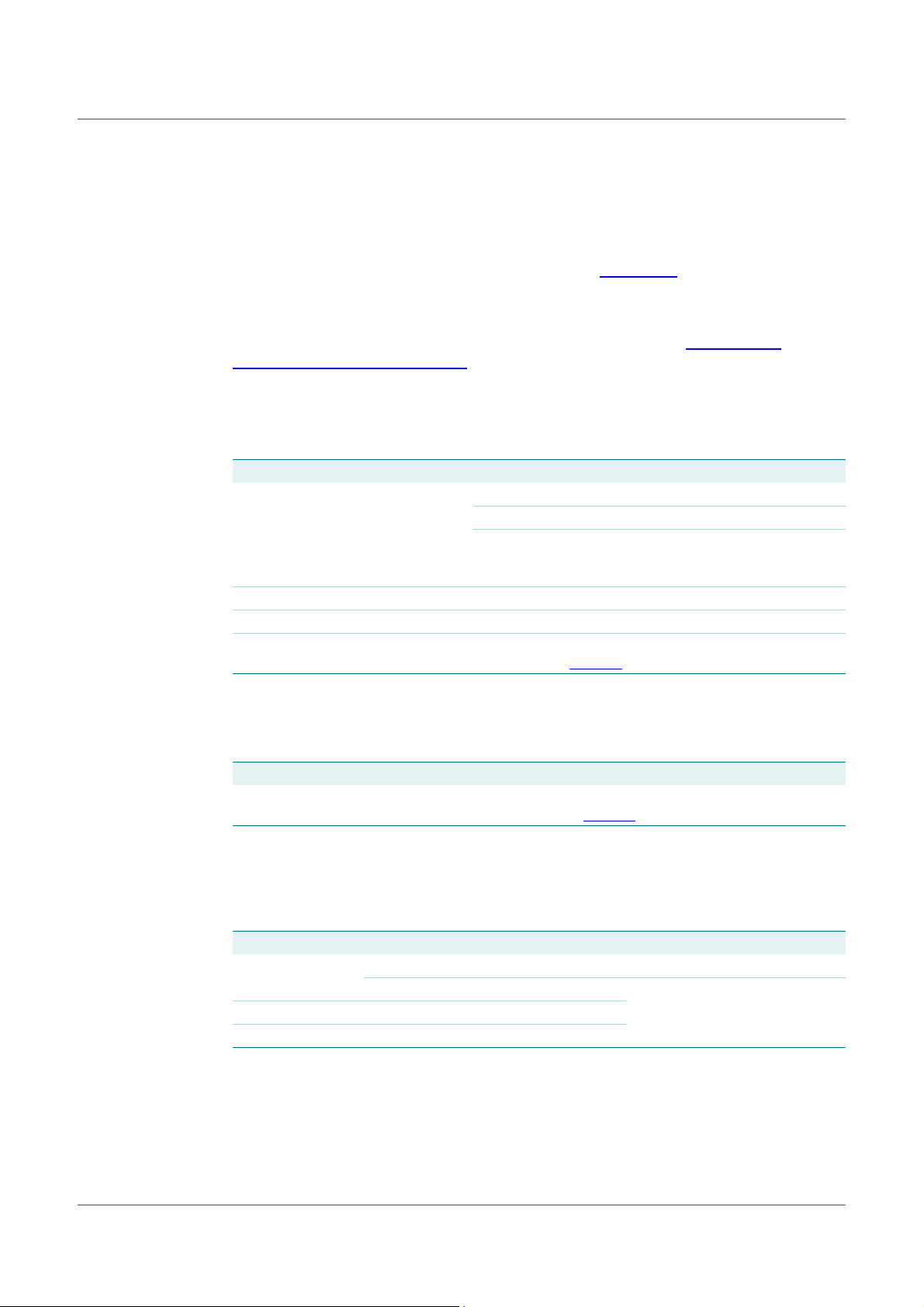

6. Block diagram

AGC CONTROL

DC-to-DC

CONVERTER

TDA18271HD

Silicon Tuner IC

DIGITAL

CIRCUITRY

LNA

RF_IN

STO

LT

FM_IN

10

15

13

8

AGC1

ATTENUATORS

Fig 1. Block diagram

AGC2

TDA18271HD

CONTROL

INTERFACE

32 39 35 34 26 2227 24 21

LC

tracking

filters

38

SCLAS SDA

polyphase

RF

AGC

TEST SIGNAL

GENERATOR

VT_CAL CP_CAL

RF

filter

CALIBRATION

SYNTHESIZER

mixer

XTALP

IF

polyphase

filter

AGC

DUAL TUNER

PROTOCOL

crystal

oscillator

MAIN

SYNTHESIZER

XTALN VT_FINE

IF

low-pass

filter

CP_LO

AGC

DIVIDER

IF

45

IFOUTN

IFOUTP

46

47

V_IFAGC

28

FREEZE

19

MASTERSYNC

VCO

VT_COARSE

001aag453

TDA18271HD_3 © NXP B.V. 2008. All rights reserved.

Product data sheet Rev. 03 — 11 September 2008 3 of 69

Page 4

NXP Semiconductors

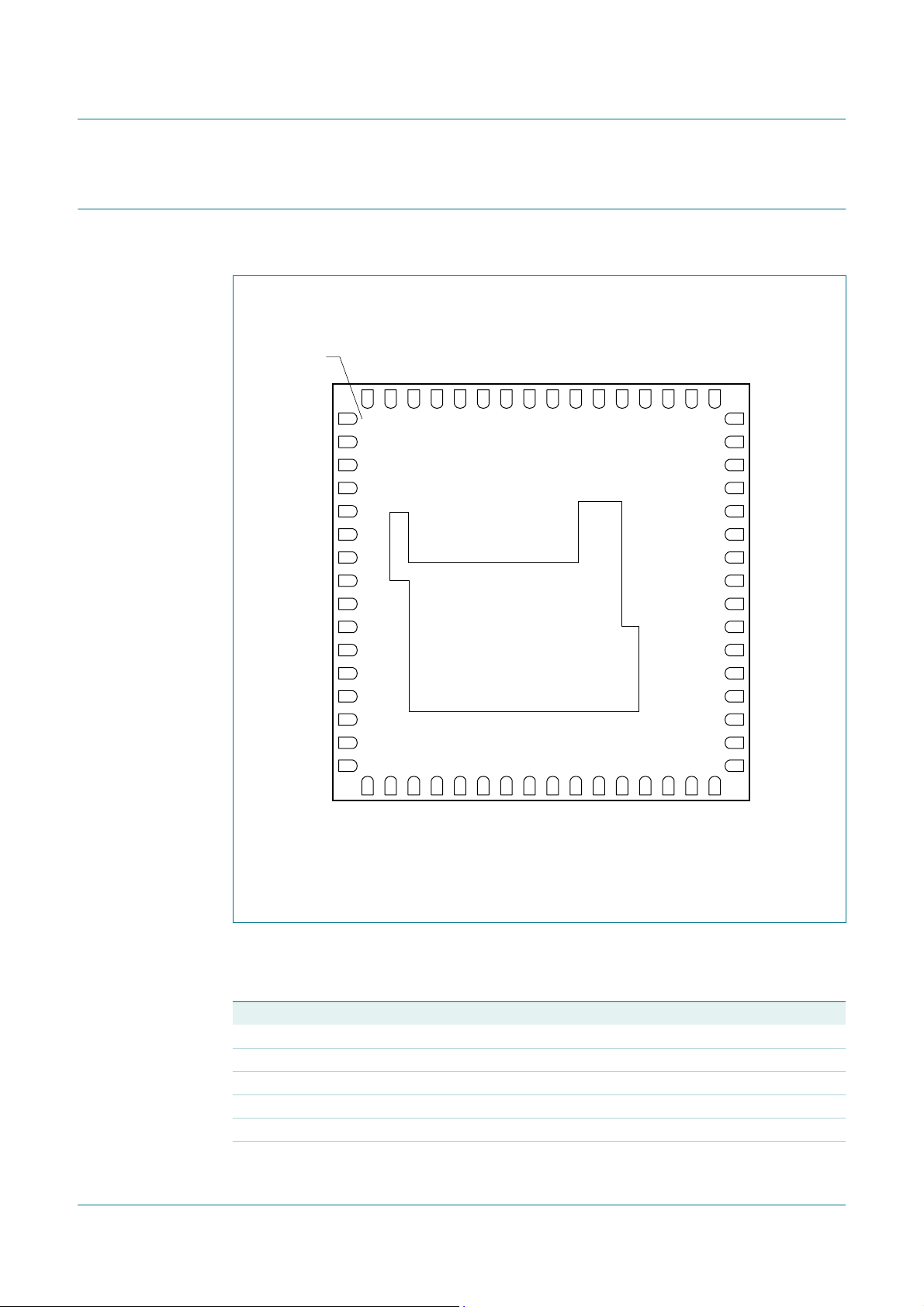

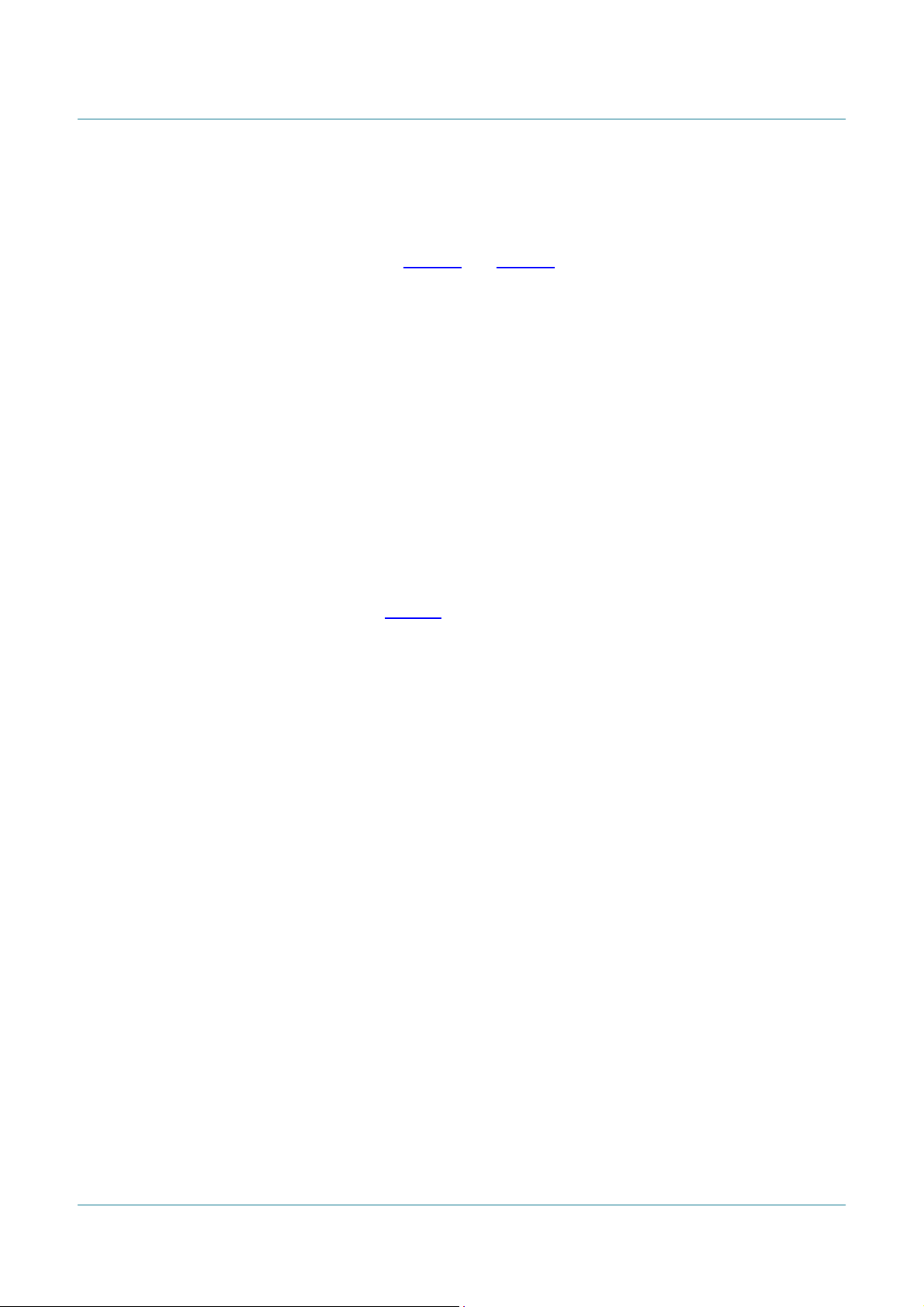

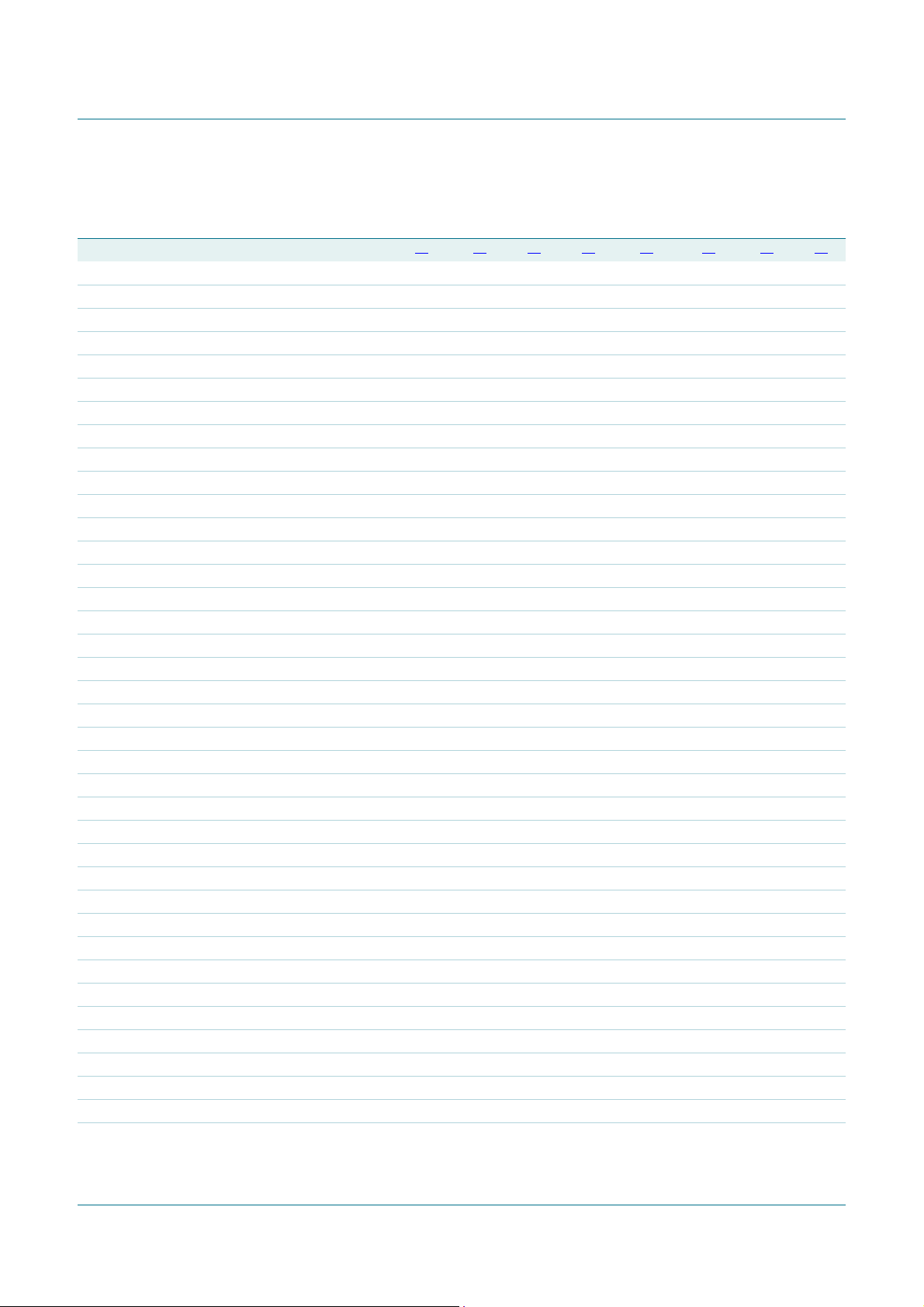

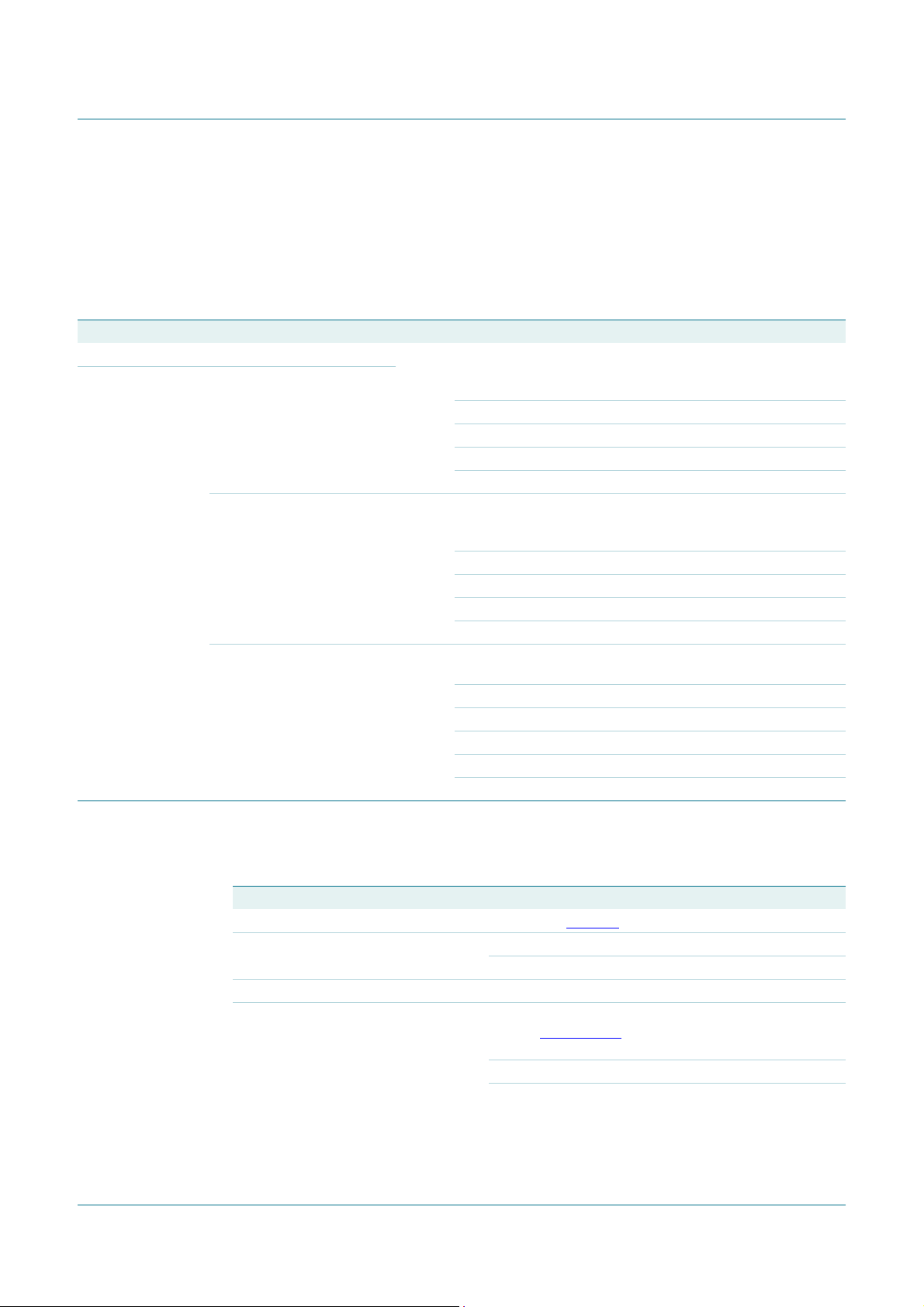

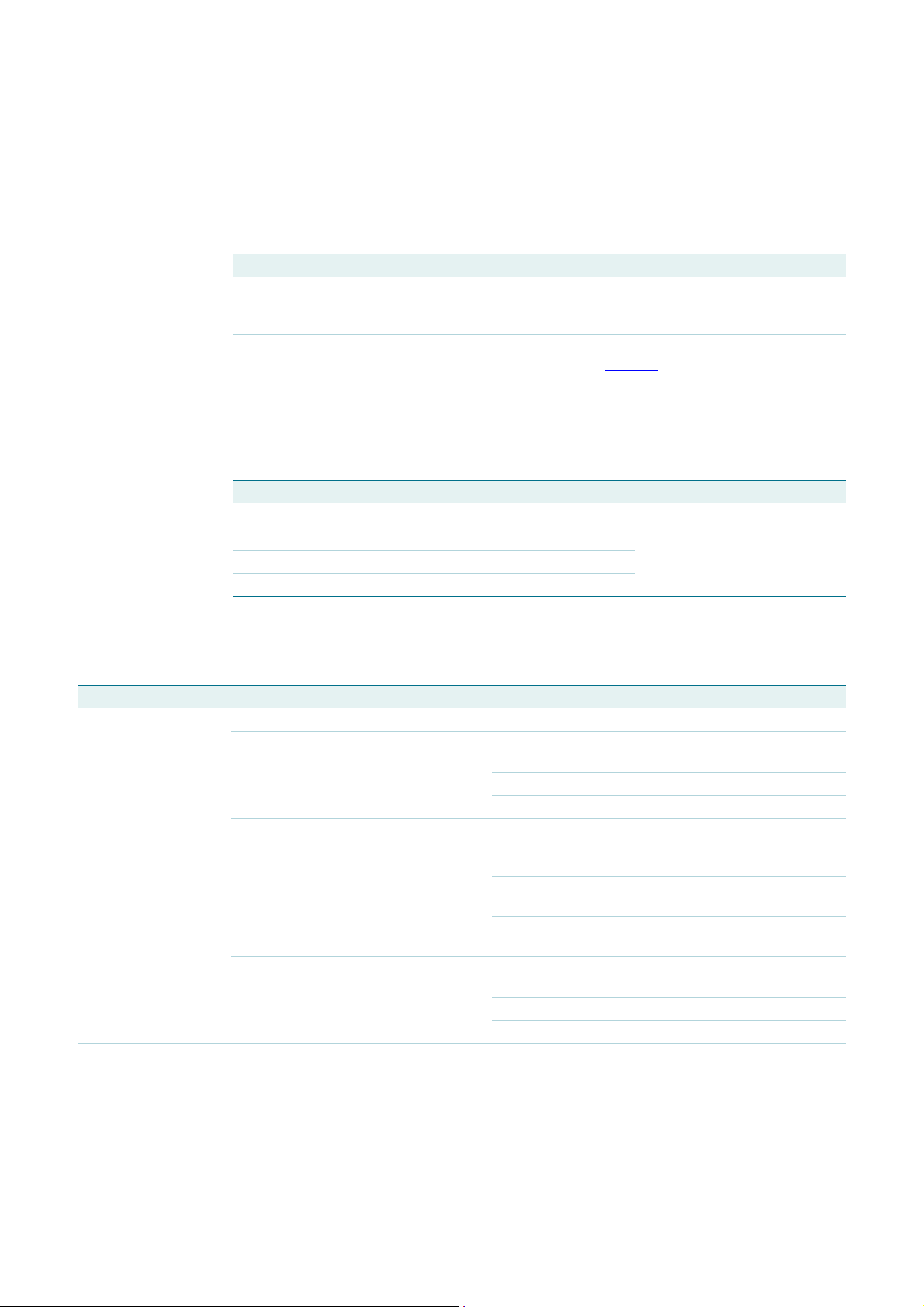

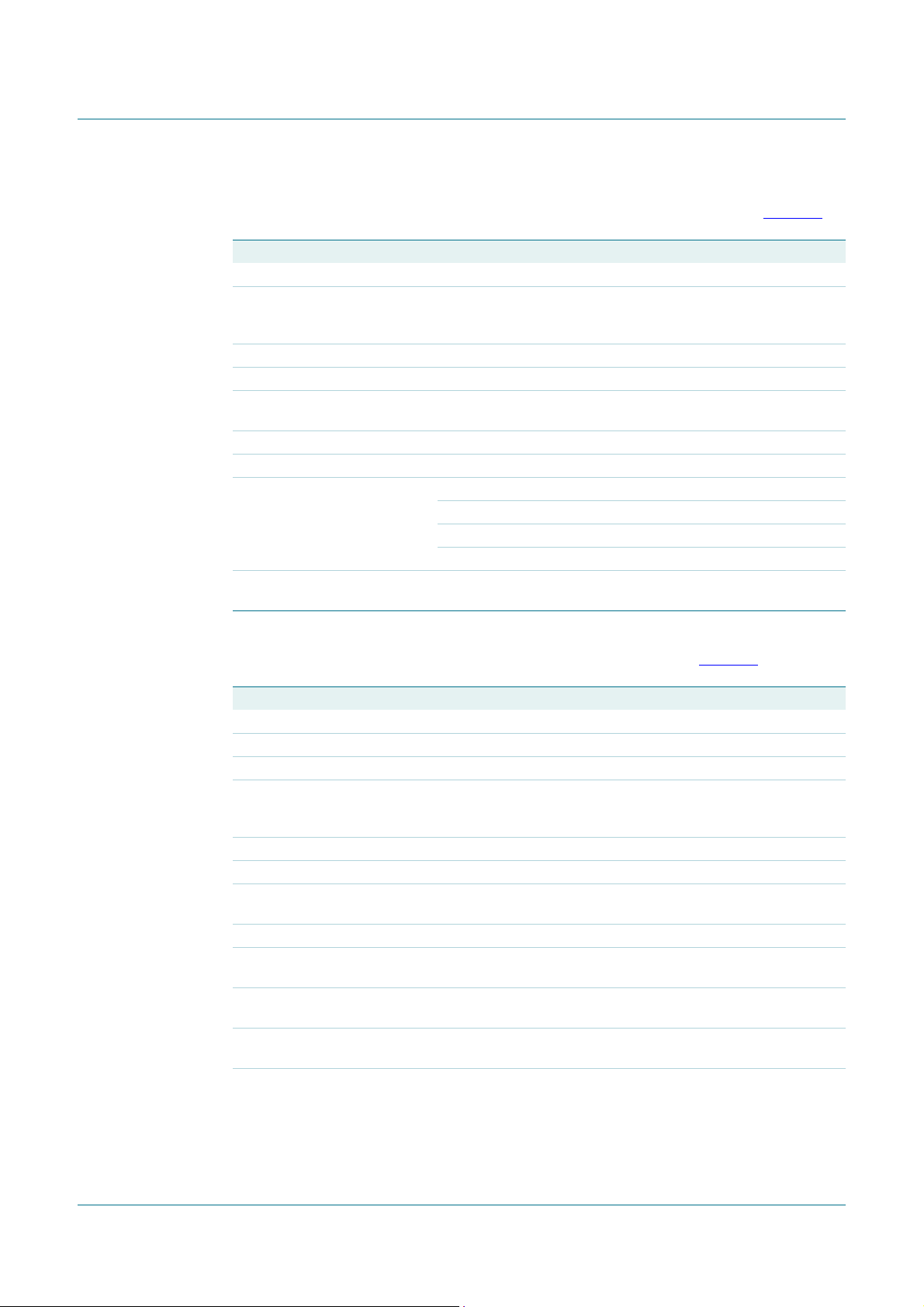

7. Pinning information

7.1 Pinning

terminal 1

index area

GND

GND

GND

GND

GND

GND

GND

FM_IN

VCC

RF_IN

GND

CAPRFAGC

GND

STO

VCC

LT

TDA18271HD

Silicon Tuner IC

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

CAPREGFILTRF

VSYNC

GND

GND

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

TDA18271HD

23

24

25

26

27

28

29

30

48

GND

47

V_IFAGC

46

IFOUTP

45

IFOUTN

44

VCC

43

GND

42

CAPREG28

41

GND

40

CAPREG18

39

SDA

38

SCL

37

GND

36

GND

35

VT_CAL

34

CP_CAL

33

VCC

31

32

XTOUTP

XTOUTN

AS

001aag454

VCC

CAPREGVCO

MASTERSYNC

VT_FINE

Transparent top view

VT_COARSE

CAPFILTVCO

GND

GND

CP_LO

XTALP

XTALN

FREEZE

XTOUT_MS

Fig 2. Pin configuration

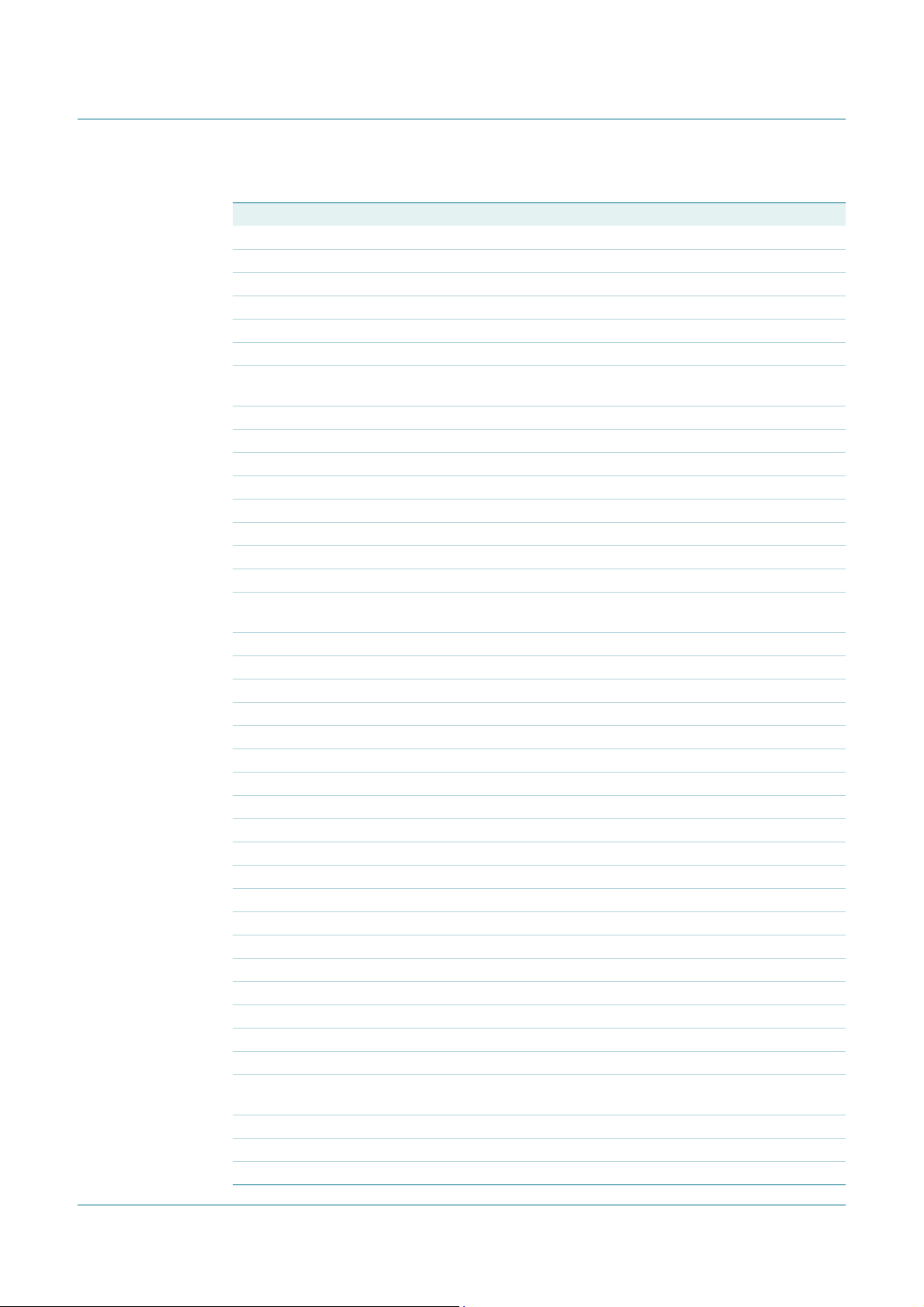

7.2 Pin description

Table 3. Pin description

Symbol Pin Description

GND 1 to 7 ground

FM_IN 8 unbalanced FM input

VCC 9 3.3 V supply voltage

RF_IN 10 unbalanced RF (TV) input

GND 11 ground

CAPRFAGC 12 RF AGC filtering

TDA18271HD_3 © NXP B.V. 2008. All rights reserved.

Product data sheet Rev. 03 — 11 September 2008 4 of 69

Page 5

NXP Semiconductors

TDA18271HD

Silicon Tuner IC

Table 3. Pin description

Symbol Pin Description

LT 13 loop-through output

GND 14 ground

STO 15 slave tuner output

VCC 16 3.3 V supply voltage

CAPREGVCO 17 VCO supply decoupling

VCC 18 3.3 V supply voltage

MASTERSYNC 19 synchronization signalfor dual tuner applications; leaveopen for

CAPFILTVCO 20 VCO reference decoupling

VT_COARSE 21 LO tuning voltage input

VT_FINE 22 LO tuning voltage input

GND 23 ground

CP_LO 24 charge pump of the local synthesizer

GND 25 ground

XTALP 26 crystal oscillator input

XTALN 27 crystal oscillator input

FREEZE 28 synchronization signal for multi tuner applications; leave open

XTOUT_MS 29 XTOUT mode and master/slave selection

XTOUTP 30 crystal oscillator output buffer

XTOUTN 31 crystal oscillator output buffer

AS 32 I

VCC 33 3.3 V supply voltage

CP_CAL 34 charge pump of the calibration synthesizer

VT_CAL 35 tuning voltage of the calibration synthesizer

GND 36, 37 ground

SCL 38 I

SDA 39 I

CAPREG18 40 internal regulator decoupling

GND 41 ground

CAPREG28 42 internal regulator decoupling

GND 43 ground

VCC 44 3.3 V supply voltage

IFOUTN 45 IF output

IFOUTP 46 IF output

V_IFAGC 47 IF gain control input

GND 48 to 50 ground

VSYNC 51 verticalsynchronization input for analogapplications; connectto

CAPREGFILTRF 52 internal regulator decoupling

GND 53 to 64 ground

GND exposed die ground

TDA18271HD_3 © NXP B.V. 2008. All rights reserved.

Product data sheet Rev. 03 — 11 September 2008 5 of 69

…continued

single tuner applications

for single tuner applications

2

C-bus address selection input

2

C-bus clock input

2

C-bus data input/output

ground for digital applications

Page 6

NXP Semiconductors

8. Functional description

The RF input signal is driven to a low-noise amplifier. It is then band-pass filtered,

amplified and fedto the image rejection mixer. The mixerdownconverts the RF signal to a

low IF depending on the channel bandwidth.

Standard IF filters are implemented for 1.5 MHz, 6 MHz, 7 MHz and 8 MHz channel

bandwidths; see Table 43.

The Silicon Tuner can be used either as TV receiver or FM radio receiver.

The TDA18271HD requires a single 16 MHz crystal for clock generation. When bit

XTOUT_ON = 1, a clock signal is available on pins XTOUTP and XTOUTN to drive a

second tuner, achannel decoder oran IF demodulator (TDA8295) for analogTV reception

and FM radio.

Remark: Most recent video decoders from NXP Semiconductors include a low IF

demodulation function.

8.1 TV and FM reception

TDA18271HD

Silicon Tuner IC

The Silicon Tuner can be used in two modes, selectable via the I2C-bus:

• TV reception: the RF signal must be connected to pin RF_IN

• FM reception: the RF signal must be connected to pin FM_IN or RF_IN

The RF_IN input pin can also be used for FM reception at the cost of software

modification. The FM_IN input pin can only receive signals in the FM frequency range.

8.2 Master and slave operation

The TDA18271HD allows easy dual-tuner configuration.

Each individual tuner has to be set either to Master mode or Slave mode by applying a

specific DC voltage to the XTOUT_MS pin; see Table 4. This will decide whether the

crystal oscillator part is used as negative impedance connected to the crystal part or as a

current buffer.

Table 4. Master/slave selection

Voltage on pin XTOUT_MS Tuner type Crystal oscillator function

0 V to 0.1V

0.4V

In dual tuner applications:

to 0.6V

CC

CC

CC

master negative impedance presented to the crystal

slave current input buffer

• The first tuner is set to Master mode

• The second tuner has to be set to Slave mode

In single tuner applications:

• The tuner must be set to Master mode

TDA18271HD_3 © NXP B.V. 2008. All rights reserved.

Product data sheet Rev. 03 — 11 September 2008 6 of 69

Page 7

NXP Semiconductors

8.3 Tuner outputs

The tuner provides a slave tuner output (pin STO) and a loop-through output (pin LT).

These outputs are used to transmit the antenna signal to other tuners. Each output has its

own characteristics (see Table 58 and Table 59).

8.3.1 Loop-through output

The gain between the antenna connector and the loop-through pin (pin LT) equals 0 dB.

This pin can be connected to any consumer electronic equipment.

8.3.2 Slave tuner output

In dual tuner applications the slave tuner output (pin STO) must be connected to the RF

input of the slave tuner TDA18271HD.

The gain between the antenna connector and the slave tuner output can change

according to the input level. The slave tuner will automatically compensate for the gain

change, using the MASTERSYNC and FREEZE signals.

8.4 Crystal input mode

TDA18271HD

Silicon Tuner IC

The TDA18271HD requires a 16 MHz crystal reference. The chosen crystal must

withstand at least 100 µW drive level andan additional shunt capacitor witha typical value

of 5.6 pF as shown in Figure 1 is also needed. The quartz references for which the

performances are guaranteed are:

• NDK NX5032

• Siward SX-5032

• TXC 9C series

• Chungho Elcom HC49S profile

Clock reference:

• In Master mode, the clock reference must be provided bya 16 MHz crystal connected

between pins XTALP and XTALN of the master tuner

• In Slave mode, the clock reference must be provided by pins XTOUTP and XTOUTN

of the tuner in Master mode to pins XTALP and XTALN of the tuner in Slave mode

8.5 Crystal output mode

Pins XTOUTP and XTOUTN deliver a symmetrical sine waveform to drive the channel

decoder and/or IF demodulator. The load on these outputs should be made similar to

ensure optimum performances. If only one crystal output is used, the unused output

should be loaded by an equivalent capacitance.

TDA18271HD_3 © NXP B.V. 2008. All rights reserved.

Product data sheet Rev. 03 — 11 September 2008 7 of 69

Page 8

NXP Semiconductors

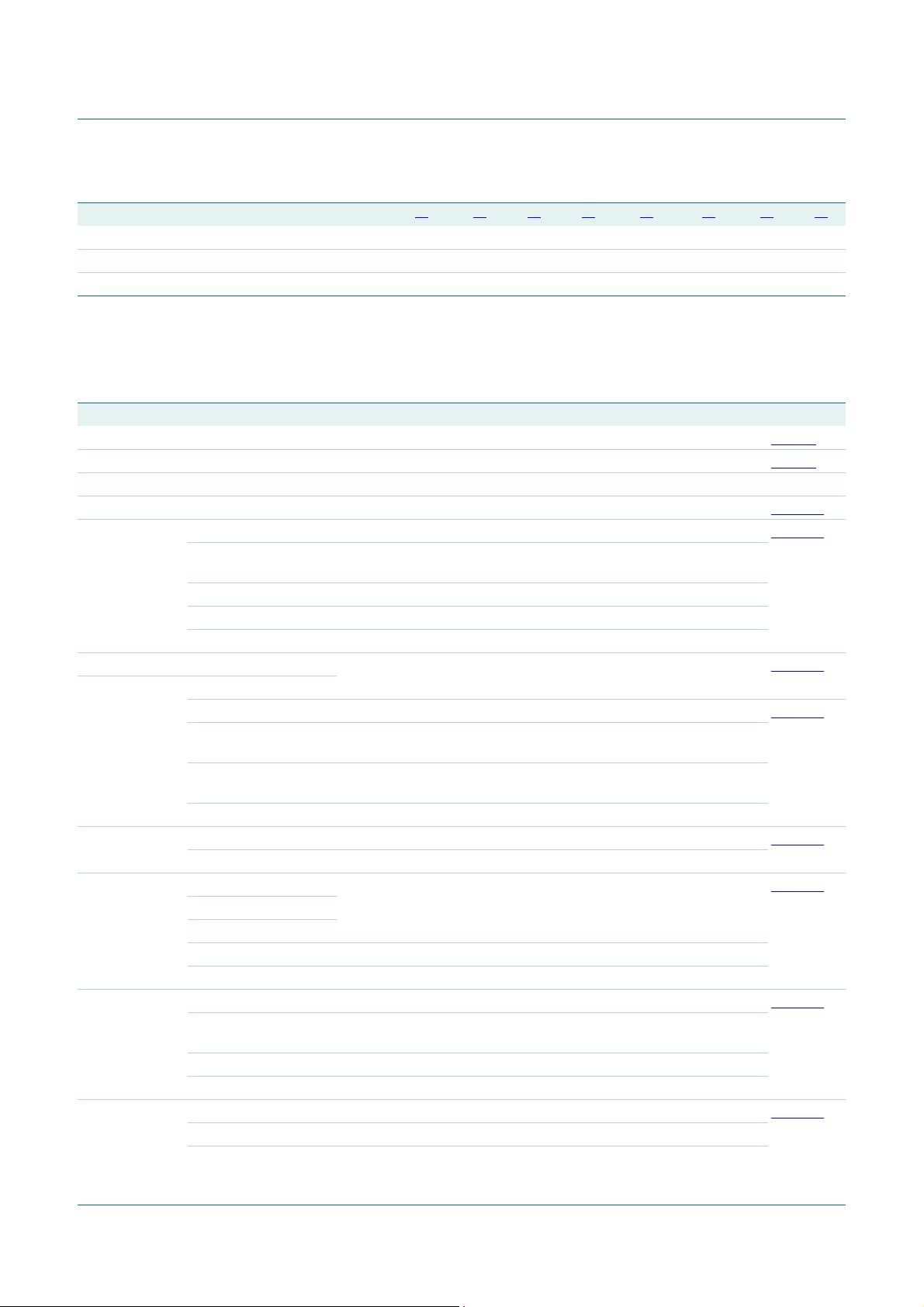

9. Control interface

9.1 I2C-bus format, Write/Read mode

Remark: The I2C-bus read in the TDA18271HD must read the entire I2C-bus map, with

required subaddress 00h. The number of bytes read is 16, or 39 in extended register

mode; see Table 7. Reading write-only bits can return values that are different from the

programmed values.

TDA18271HD

Silicon Tuner IC

TDA18271HD_3 © NXP B.V. 2008. All rights reserved.

Product data sheet Rev. 03 — 11 September 2008 8 of 69

Page 9

NXP Semiconductors

TDA18271HD

Silicon Tuner IC

AGC1_

FIRSTN

AGC1_

ALWAYS_

MASTERN

Bit

FORLON

0 RF_CAL_OK IR_CAL_OK BP_FILTER[2:0]

IR_GSTEP[2:0] 0 IR_MEAS[2:0]

DIS_

LEVEL

POWER_

7 6 5 4 3 2 1 0

LEVEL[8]

_REG

EB4[4:0]

SRCE

Sub

address

name

C-bus format

xxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxx x x x xxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxx xx xx

xxxxx xxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxx xxxxxx xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxx x x

2

xxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxx xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxx

xxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxxx xxx

Address byte 1 - - 11000 MA[1:0] R/W

Address byte 2 - - 0 0 AD[5:0]

ID byte ID 00h 1 ID[6:0]

Thermo byte TM 01h POR LOCK TM_RANGE TM_ON TM_D[3:0]

Power level byte PL 02h POWER_LEVEL[7:0]

Name Byte

Table 5. I

TDA18271HD_3 © NXP B.V. 2008. All rights reserved.

Product data sheet Rev. 03 — 11 September 2008 9 of 69

Easy prog byte 1 EP1 03h POWER_

Easy prog byte 2 EP2 04h RF_BAND[2:0] GAIN_TAPER[4:0]

Easy prog byte 3 EP3 05h SM SM_LT SM_XT AGCK_MODE[1:0] STD[2:0]

Easy prog byte 4 EP4 06h FM_RFN XTOUT_ON 1 IF_LEVEL[2:0] CAL_MODE[1:0]

Easy prog byte 5 EP5 07h EXTENDED

Cal post-divider byte CPD 08h CAL_POST_DIV[7:0]

Cal divider byte 1 CD1 09h 0 CAL_DIV[22:16]

MPD 0Ch IF_NOTCH MAIN_POST_DIV[6:0]

Cal divider byte 2 CD2 0Ah CAL_DIV[15:8]

Cal divider byte 3 CD3 0Bh CAL_DIV[7:0]

Main post-divider

byte

Main divider byte 1 MD1 0Dh 0 MAIN_DIV[22:16]

Main divider byte 2 MD2 0Eh MAIN_DIV[15:8]

Main divider byte 3 MD3 0Fh MAIN_DIV[7:0]

Extended byte 1 EB1 10h EB1[7:3] CALVCO_

Extended byte 2 EB2 11h EB2[7:0]

Extended byte 3 EB3 12h EB3[7:0]

Extended byte 4 EB4 13h EB4[7:6] LO_FORCE

Extended byte 5 EB5 14h EB5[7:0]

Extended byte 6 EB6 15h EB6[7:0]

Page 10

NXP Semiconductors

TDA18271HD

Silicon Tuner IC

LP_FC EB23[0]

EB12[3:0]

Bit

7 6 5 4 3 2 1 0

EB7[4:0]

SRCE

FORCE

DET

PD_AGC2_

DET

EB20[4:0]

EB18[6:2] AGC1_GAIN[1:0]

LOCK

FC2_EN

EB21[6:2] AGC2_GAIN[1:0]

LOOP_OFF

Sub

address

…continued

name

C-bus format

xxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxx x x x xxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxx xx xx

xxxxx xxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxx xxxxxx xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxx x x

2

xxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxx xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxx

xxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxxx xxx

Extended byte 13 EB13 1Ch EB13[7] RFC_K[2:0] RFC_M[1:0] EB13[1:0]

Extended byte 14 EB14 1Dh RFC_CPROG[7:0]

Extended byte 15 EB15 1Eh EB15[7:4] EB15[3:0]

Extended byte 16 EB16 1Fh EB16[7:0]

Extended byte 17 EB17 20h EB17[7:0]

Extended byte 18 EB18 21h AGC1_

Extended byte 19 EB19 22h EB19[7:0]

Name Byte

Table 5. I

TDA18271HD_3 © NXP B.V. 2008. All rights reserved.

Product data sheet Rev. 03 — 11 September 2008 10 of 69

Extended byte 7 EB7 16h EB7[7:6] CAL_

Extended byte 8 EB8 17h CID_ALARM EB8[6:4] EB8[3] EB8[2:0]

Extended byte 9 EB9 18h EB9[7:0]

Extended byte 10 EB10 19h EB10[7:6] CID_GAIN[5:0]

Extended byte 11 EB11 1Ah EB11[7:0]

Extended byte 12 EB12 1Bh EB12[7:6] PD_AGC1_

Extended byte 20 EB20 23h EB20[7:6] FORCE_

LOOP_OFF

Extended byte 21 EB21 24h AGC2_

Extended byte 22 EB22 25h EB22[7] RF_TOP[2:0] IF_TOP[3:0]

Extended byte 23 EB23 26h EB23[7:3] FORCELP_

Page 11

NXP Semiconductors

TDA18271HD

Silicon Tuner IC

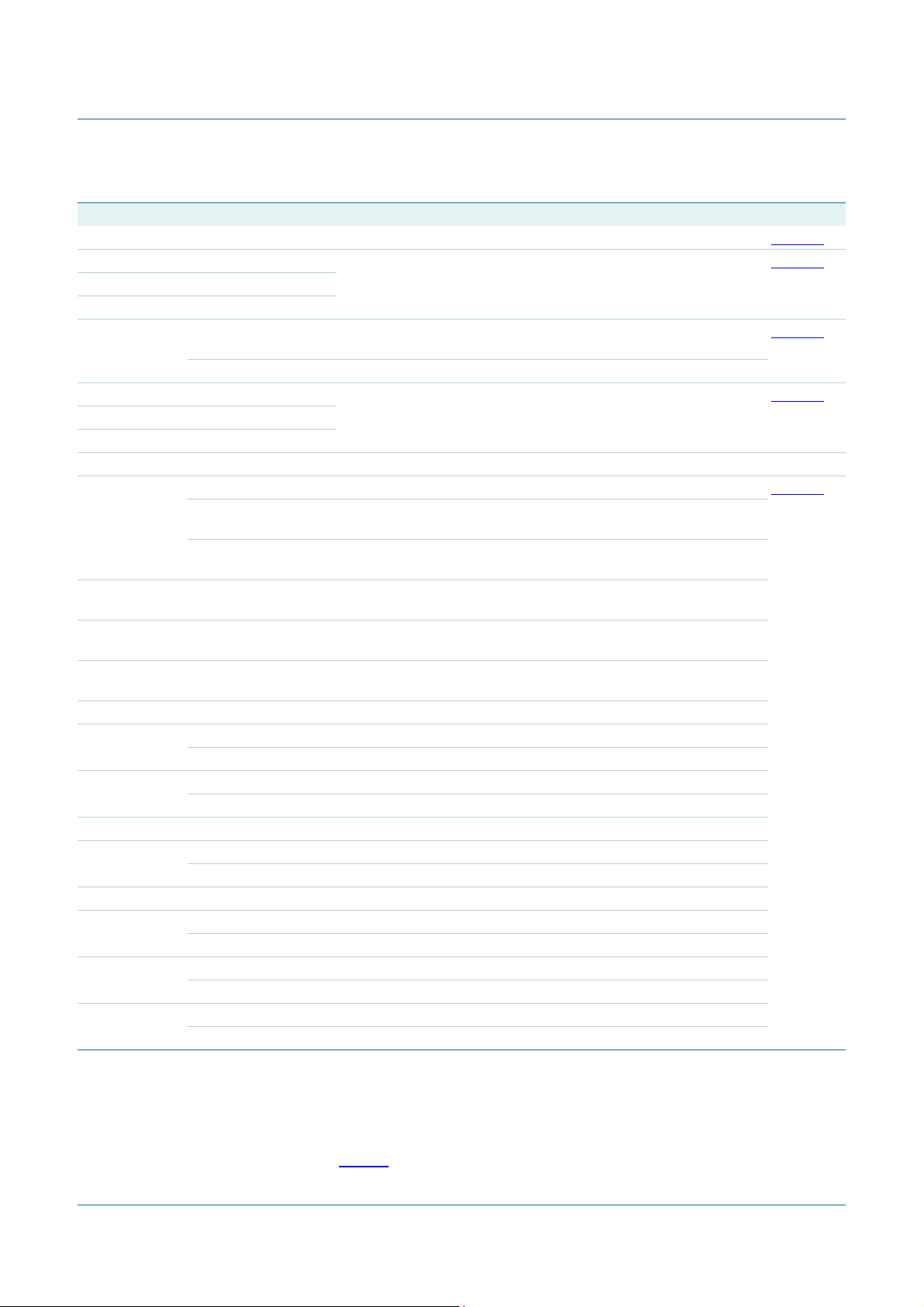

9.2 I2C-bus at power-on reset

Table 6. I2C-bus at power-on reset

Name Byte Subaddress 7

[1]

Address byte 1 - - 1 1 0 0 0 MA[1] MA[0] X

Address byte 2 - - X X AD[5] AD[4] AD[3] AD[2] AD[1] AD[0]

ID byte ID 00h 1 0 0 0 0 1 0 0

Thermo byte TM 01h 1 0 0 0 X X X X

Power level byte PL 02h X X X X X X X X

Easy prog byte 1 EP1 03h X 1 0 0 0 1 1 0

Easy prog byte 2 EP2 04h 1 1 0 1 1 1 1 1

Easy prog byte 3 EP3 05h 1 0 0 1 0 0 1 0

Easy prog byte 4 EP4 06h 0 1 1 0 0 0 0 0

Easy prog byte 5 EP5 07h 0 0 1 1 0 0 0 0

Cal post-divider byte CPD 08h 0 0 0 0 0 0 0 0

Cal divider byte 1 CD1 09h 0 0 0 0 0 0 0 0

Cal divider byte 2 CD2 0Ah 0 0 0 0 0 0 0 0

Cal divider byte 3 CD3 0Bh 0 0 0 0 0 0 0 0

Main post-divider byte MPD 0Ch 0 0 0 0 0 0 0 0

Main divider byte 1 MD1 0Dh 0 0 0 0 0 0 0 0

Main divider byte 2 MD2 0Eh 0 0 0 0 0 0 0 0

Main divider byte 3 MD3 0Fh 0 0 0 0 0 0 0 0

Extended byte 1 EB1 10h 1 1 1 1 1 1 1 1

Extended byte 2 EB2 11h 0 0 0 0 0 0 0 1

Extended byte 3 EB3 12h 1 0 0 0 0 1 0 0

Extended byte 4 EB4 13h 0 1 0 0 0 0 0 1

Extended byte 5 EB5 14h 0 0 0 0 0 0 0 1

Extended byte 6 EB6 15h 1 0 0 0 0 1 0 0

Extended byte 7 EB7 16h 0 1 0 0 1 0 0 0

Extended byte 8 EB8 17h 0 1 1 1 X 1 0 1

Extended byte 9 EB9 18h 0 0 0 0 0 0 0 0

Extended byte 10 EB10 19h X X X X X X X X

Extended byte 11 EB11 1Ah 1 0 0 0 0 1 1 0

Extended byte 12 EB12 1Bh 0 0 0 0 0 1 1 1

Extended byte 13 EB13 1Ch 1 1 0 0 0 0 1 0

Extended byte 14 EB14 1Dh 0 0 0 0 0 0 0 0

Extended byte 15 EB15 1Eh 1 0 0 0 X X X X

Extended byte 16 EB16 1Fh 0 0 0 X X X 0 0

Extended byte 17 EB17 20h 0 0 0 X X X X X

Extended byte 18 EB18 21h 0 0 0 0 0 0 0 0

Extended byte 19 EB19 22h 0 0 0 X X X 0 0

Extended byte 20 EB20 23h 1 0 0 X X X X X

[1]

6

[1]

5

[1]

4

[1]

3

[1]

2

[1]

1

[1]

0

TDA18271HD_3 © NXP B.V. 2008. All rights reserved.

Product data sheet Rev. 03 — 11 September 2008 11 of 69

Page 12

NXP Semiconductors

TDA18271HD

Silicon Tuner IC

2

Table 6. I

C-bus at power-on reset

Name Byte Subaddress 7

…continued

[1]

[1]

6

[1]

5

[1]

4

[1]

3

[1]

2

[1]

1

[1]

0

Extended byte 21 EB21 24h 0 0 1 1 0 0 1 1

Extended byte 22 EB22 25h 0 1 0 0 1 0 0 0

Extended byte 23 EB23 26h 1 0 1 1 0 0 0 0

[1] X indicates a bit not changed on reset.

9.3 Description of symbols used in I2C-bus format table

Table 7. I2C-bus register bits explanation

Address Byte Symbol Description Reference

MA[1:0] programmable address bits

AD[5:0] programmable address bits of the first programming byte

Data bytes

00h ID ID[6:0] chip identification number

01h TM POR Power-On Reset bit

LOCK indicates that the main synthesizer is locked to the programmed

frequency

TM_RANGE range selection bit for the internal die sensor

TM_ON enables die temperature measurement

TM_D[3:0] data from die temperature measurement (read only)

02h PL POWER_LEVEL[7:0] Power level indicator value (read only)

03h EP1 POWER_LEVEL[8]

DIS_POWER_LEVEL disables the power-on level function

RF_CAL_OK indicates that the RF tracking filter calibration procedure has been

successful

IR_CAL_OK indicates that the complete image rejection calibration procedure

has been successful

BP_FILTER[2:0] RF band-pass filter selection

04h EP2 RF_BAND[2:0] RF tracking filter band selection

GAIN_TAPER[4:0] gain taper value

05h EP3 SM Sleep mode, Standby modes

SM_LT

SM_XT

AGCK_MODE[1:0] defines the standard

STD[2:0] defines the standard

06h EP4 FM_RFN selects which input is fed to RF filter

XTOUT_ON providesthe 16 MHz crystal referenceon the XTOUTPand XTOUTN

pins

IF_LEVEL[2:0] IF output level selection

CAL_MODE[1:0] calibration mode selection

07h EP5 EXTENDED_REG enables the extended register addressing

IR_GSTEP[2:0] gain step for image rejection calibration

IR_MEAS[2:0] image rejection measurement frequency range

Table 8

Table 9

Table 10

Table 11

Table 12

Table 13

Table 14

Table 15

Table 18

Table 19

TDA18271HD_3 © NXP B.V. 2008. All rights reserved.

Product data sheet Rev. 03 — 11 September 2008 12 of 69

Page 13

NXP Semiconductors

TDA18271HD

Silicon Tuner IC

2

Table 7. I

Address Byte Symbol Description Reference

08h CPD CAL_POST_DIV[7:0] calibration synthesizer post-divider Table 20

09h CD1 CAL_DIV[22:16] calibration synthesizer main divider bits

0Ah CD2 CAL_DIV[15:8]

0Bh CD3 CAL_DIV[7:0]

0Ch MPD IF_NOTCH adds a DC notch in IF for a better adjacent channels rejection;

0Dh MD1 MAIN_DIV[22:16] LO synthesizer main divider bits

0Eh MD2 MAIN_DIV[15:8]

0Fh MD3 MAIN_DIV[7:0]

Extended bytes

10h EB1 CALVCO_FORLON determines which VCO is used during Normal mode operations

13h EB4 LO_FORCESRCE forces the main PLL charge pump to source current to the main PLL

16h EB7 CAL_FORCESRCE forces the calibration PLL charge pump to source current to the

17h EB8 CID_ALARM indicates that signal sensed by the power detector used during

19h EB10 CID_GAIN[5:0] calibration power detector output

1Bh EB12 PD_AGC1_DET power-down of AGC1 detector

1Ch EB13 RFC_K[2:0] parameter used during the RF tracking filter calibration

1Dh EB14 RFC_CPROG[7:0] tuning word of the RF tracking filters

21h EB18 AGC1_LOOP_OFF turns off the AGC1 loop

23h EB20 FORCE_LOCK forces the internal PLLs lock indicator to logic 1

24h EB21 AGC2_LOOP_OFF turns off the AGC2 loop

25h EB22 RF_TOP[2:0] Take-Over Point (TOP) of the RF AGC, detection in RF

26h EB23 FORCELP_FC2_EN FM filter selection

C-bus register bits explanation

MAIN_POST_DIV[6:0] LO synthesizer post-divider bits

AGC1_ALWAYS_

MASTERN

AGC1_FIRSTN determines which AGC (1 or 2) will be detected when detectors 1

PD_AGC2_DET power-down of AGC2 detector

RFC_M[1:0] parameter used during the RF tracking filter calibration

AGC1_GAIN[1:0] AGC1 gain

AGC2_GAIN[1:0] AGC2 gain

IF_TOP[3:0] TOP of the RF AGC, detection in IF

LP_FC

…continued

Table 21

Table 22

depends on standards

Table 23

Table 24

enables AGC1 normal operation whatever the tuner type (master or

slave)

and 2 are up

loop filter

calibration PLL loop filter

calibrations is out of range

9.3.1 I2C-bus address selection

The programmable module address bits MA[1:0] allow up to four tuners to be addressed

in one system. Bits MA1 and MA0 are programmed by a specific voltage (VAS) applied to

pin AS. The relationship between the status of bits MA[1:0] and the voltage applied to pin

AS is shown in Table 8.

TDA18271HD_3 © NXP B.V. 2008. All rights reserved.

Product data sheet Rev. 03 — 11 September 2008 13 of 69

Page 14

NXP Semiconductors

Table 8. Address byte 1 bit description

Legend: * power-on reset value.

Bit Symbol Access Value Description

7 to 3 - R/W 1 1000* must be set to 1 1000

2 to 1 MA[1:0] R/W programmable address bits

0 R/W R/W 0 write mode

Table 9. Address byte 2 bit description

Legend: * power-on reset value.

Bit Symbol Access Value Description

7 to 6 - R/W 00 must be set to 00

5 to 0 AD[5:0] R/W - programmable address bits of the first

TDA18271HD

Silicon Tuner IC

00 V

01 VAS = 0.2 × VCCto 0.3 × V

10 VAS = 0.4 × VCCto 0.6 × V

11 VAS = 0.9 × VCCto V

1 read mode

= 0 V to 0.1 × V

AS

programming byte

CC

CC

CC

CC

9.3.2 Description of chip ID byte

Table 10. ID - identification byte (subaddress 00h) bit description

Legend: * power-on reset value.

Bit Symbol Access Value Description

7 - R 1* must be 1

6 to 0 ID[6:0] R 000 0100* TDA18271HD/C2 identification number

9.3.3 Description of temperature sensor byte

The temperature sensor is not available in Device-off mode,as it requires a 16 MHz clock

to operate.

Table 11. TM - Thermo byte (subaddress 01h) bit description

Legend: * power-on reset value.

Bit Symbol Access Value Description

7 POR R 1* power supply falls below the power-on reset level and is

reset after a read operation ending with a stop condition

0 power supply is above the power-on reset level

6 LOCK R 1 main synthesizer is locked to the programmed frequency

0* main synthesizer is not locked to the programmed

frequency

5 TM_RANGE R/W temperature rangeselection for the internal die sensor (see

Table 52)

192°C to 122 °C

0* 60 °C to 90 °C

4 TM_ON R/W 1 enables die temperature measurement (see

0* disables die temperature measurement (see

3 to 0 TM_D[3:0] R XXXX data from die temperature measurement (see

Table 52)

Table 52)

Table 52)

TDA18271HD_3 © NXP B.V. 2008. All rights reserved.

Product data sheet Rev. 03 — 11 September 2008 14 of 69

Page 15

NXP Semiconductors

TDA18271HD

Silicon Tuner IC

9.3.4 Description of power level byte (read mode)

There are 9 power level bits sent in power level bytes 2 and 3. They indicate the

composite voltage gain of the LNA, the loaded attenuator voltage gains, and the level at

the input of the RF AGC.

Table 12. PL - Power level (address 02h and 03h) bit description

Legend: * power-on reset value.

Address Register Bit Symbol Access Value Description

03h EP1 7 POWER_LEVEL[8] R AGC2 gain, attenuator voltage gain including load,

02h PL 7 POWER_LEVEL[7]

00 −15 dB

01 −12 dB

10 −9 dB

11 −6 dB

6 to 5 POWER_LEVEL[6:5] R AGC1 gain, LNA voltage gain, the LNA voltage gain

00 6 dB

01 9 dB

10 12 dB

11 15 dB

4 to 0 POWER_LEVEL[4:0] R sensed level at the input of the RF AGC, detector

0 0000 103 dBµV (RMS value)

0 0001 102 dBµV (RMS value)

... ...

1 1110 73 dBµV (RMS value)

1 1111 72 dBµV (RMS value)

the attenuatorload is 50 Ω (allowsthe maximumgain

of −6 dB)

assumes a 75 Ω source impedance and a lowoutput

impedance

slope is −1 dB/step

9.3.5 Description of Easy prog byte 1

Table 13. EP1 - Easy prog byte 1 (subaddress 03h) bit description

Legend: * power-on reset value.

Bit Symbol Access Value Description

7 POWER_LEVEL[8] R see

6 DIS_POWER_LEVEL R/W 1* power level disabled

0 power level enabled

5 - R/W 0* must be set to 0

4 RF_CAL_OK R/W RF tracking filter calibration procedure (see

1 successful

0* not successful

TDA18271HD_3 © NXP B.V. 2008. All rights reserved.

Product data sheet Rev. 03 — 11 September 2008 15 of 69

Table 12

Section 9.4.9); updated each time the procedure

is started

Page 16

NXP Semiconductors

TDA18271HD

Silicon Tuner IC

Table 13. EP1 - Easy prog byte 1 (subaddress 03h) bit description

Legend: * power-on reset value.

Bit Symbol Access Value Description

3 IR_CAL_OK R/W complete image rejection calibration procedure

2 to 0 BP_FILTER[2:0] R/W 110* RF band-pass filter selection (see

9.3.6 Description of Easy prog byte 2

Table 14. EP2 - Easy prog byte 2 (subaddress 04h) bit description

Legend: * power-on reset value.

Bit Symbol Access Value Description

7 to 5 RF_BAND[2:0] R/W 110* RF tracking filter band selection (see

4 to 0 GAIN_TAPER[4:0] R/W gain taper value (see

9.3.7 Description of Easy prog byte 3

The TDA18271HDhas three different Standbymodes. Two Standby modes are dedicated

to special applicationdemands; the third Standby modeis called ‘device-off’. It represents

the smallest achievable power consumption.

(see

Section 9.4.4); can only be reset with POR

1 successful

0* not successful

Table 49)

1 1111* minimum attenuation

0 0000 maximum attenuation

…continued

Table 44)

Table 45)

Table 15. EP3 - Easy prog byte 3 (subaddress 05h) bit description

Legend: * power-on reset value.

Bit Symbol Access Value Description

7 to 5 SM, SM_LT,

SM_XT

4 to 3 AGCK_MODE[1:0] R/W 10010* defines the standard

2 to 0 STD[2:0] R/W description of standards (see

Table 16. Power modes

Bit Circuit Mode

SM SM_LT SM_XT Loop-

000ononon Normal mode

100ononon Standby mode with crystal

1 1 0 off off on Standby mode with only crystal

1 1 1 off off off Device-off mode

[1] In all modes, the I2C-bus interface remains active. All other bit settings are invalid.

R/W 100 Power modes

through

Slavetuner

output

Crystal

oscillator

Table 16

Table 43)

[1]

oscillator, slave-tuner output and

loop-through output on

oscillator and its output buffer on

TDA18271HD_3 © NXP B.V. 2008. All rights reserved.

Product data sheet Rev. 03 — 11 September 2008 16 of 69

Page 17

NXP Semiconductors

Table 17. AGC modes

Standard AGC_MODE[1:0]

FM radio 1 1 internal

Analog TV standards 0 1 VSYNC

Digital TV standards 1 1 internal

[1] Depending on the programmedAGC_MODE, AGC1 can be synchronous with either VSYNC or an internal

9.3.8 Description of Easy prog byte 4

Table 18. EP4 - Easy prog byte 4 (subaddress 06h) bit description

Legend: * power-on reset value.

Bit Symbol Access Value Description

7 FM_RFN R/W selection which input is fed to RF filter

6 XTOUT_ON R/W 1* 16 MHz on pins XTOUT

5 - R/W 1* must be set to logic 1

4 to 2 IF_LEVEL[2:0] R/W IF output level selection and attenuation with regard to

1 to 0 CAL_MODE[1:0] R/W calibration mode selection

TDA18271HD

Silicon Tuner IC

EP3[4:3]

16 MHz signal; for analog reception, when no synchronization signal is available for VSYNC pin, the

internal reference may be used.

[1]

1 FM input (RF LNA on; FM LNA on)

0* RF input (RF LNA on; FM LNA off)

0 not 16 MHz on pins XTOUT

2 V (p-p)

000* 2 V (p-p); 0 dB

001 1.25 V (p-p); 4 dB

010 1 V (p-p); 6 dB

011 0.8 V (p-p); 8 dB

100 not used

101 not used

110 0.6 V (p-p); 10.4 dB

111 0.5 V (p-p); 12 dB

00* no calibration (Normal mode)

01 Power detection mode

10 image rejection calibration (IRCAL) mode

11 RF tracking filter calibration (RFCAL) mode

Reference signal

All calibrations require a precise set of sequential operations, therefore it is mandatory to

follow the flowcharts described in Section 9.4.

The TDA18271HD has two calibration modes: one for the image rejection calibration and

one for the RF tracking filter calibration.

The image rejection calibration optimizes tunable parameters inside the mixer using a set

of internal measurements to ensure a 65 dB typical value of image rejection. The internal

signal used during this phase is generated by the PLL calibration (CAL PLL).

TDA18271HD_3 © NXP B.V. 2008. All rights reserved.

Product data sheet Rev. 03 — 11 September 2008 17 of 69

Page 18

NXP Semiconductors

The RF tracking filters central frequency can be adjusted with the tuning word

RFC_CPROG. The RF tracking filter calibration (RFCAL) uses an internal tone at the

input of the tracking filters (generated by CAL PLL) and finds the RFC_CPROG that

corresponds to the maximum transmitted power.The RFCAL is just a small part of a more

complex algorithm fully described in the flowcharts in Section 9.4.

The Power detection mode is a Normal mode in which the detector used for the

calibrations is switched ON. This special mode enables power sensing at the input of the

TDA18271HD and makes the power scan algorithm possible (see Section 9.4.8

“Flowchart TDA18271PowerScan”).

9.3.9 Description of Easy prog byte 5

Table 19. EP5 - Easy prog byte 5 (subaddress 07h) bit description

Legend: * power-on reset value.

Bit Symbol Access Value Description

7 EXTENDED_REG R/W enables extended register addressing

6 to 4 IR_GSTEP[2:0] R/W 011* gain step for image rejection calibration

3 - R/W 0* must be set to logic 0

2 to 0 IR_MEAS[2:0] R/W 000* image rejection measurement frequency range

TDA18271HD

Silicon Tuner IC

1 extended register (10h to 26h)

0* limited register (00h to 0Fh); only 1 byte can

be programmed after address 0Fh within 1

transmission

Table 53)

(see

9.3.10 Description of Cal post-divider byte

Table 20. CPD - Cal post-divider byte (subaddress 08h) bit description

Legend: * power-on reset value.

Bit Symbol Access Value Description

7 to 0 CAL_POST_DIV[7:0] R/W 00h* calibration synthesizer post-divider (see

9.3.11 Description of Cal divider bytes 1, 2 and 3

Table 21. CD1, CD2 and CD3 - Cal divider bytes 1, 2 and 3 (address 09h, 0Ah and 0Bh) bit

description

Legend: * power-on reset value.

Address Register Bit Symbol Access Value Description

09h CD1 7 - R/W 0* must be set to 0

6 to 0 CAL_DIV[22:16] R/W 00h* calibration synthesizer main

0Ah CD2 7 to 0 CAL_DIV[15:8] R/W 00h*

0Bh CD3 7 to 0 CAL_DIV[7:0] R/W 00h*

Table 48)

divider bits

TDA18271HD_3 © NXP B.V. 2008. All rights reserved.

Product data sheet Rev. 03 — 11 September 2008 18 of 69

Page 19

NXP Semiconductors

9.3.12 Description of Main post-divider byte

Table 22. MPD - Main post-divider byte (subaddress 0Ch) bit description

Legend: * power-on reset value.

Bit Symbol Access Value Description

7 IF_NOTCH R/W 0* adds a DC notch in IF for better

6 to 0 MAIN_POST_DIV[6:0] R/W 000 LO synthesizer post-divider; see

9.3.13 Description of Main divider bytes 1, 2 and 3

Table 23. MD1, MD2 and MD3 - Main divider bytes 1, 2 and 3 (address 0Dh, 0Eh and 0Fh) bit

Legend: * power-on reset value.

Address Register Bit Symbol Access Value Description

0Dh MD1 7 - R/W 0* must be set to 0

0Eh MD2 7 to 0 MAIN_DIV[15:8] R/W 00h*

0Fh MD3 7 to 0 MAIN_DIV[7:0] R/W 00h*

description

6 to 0 MAIN_DIV[22:16] R/W 00h* LO synthesizer main divider bits

TDA18271HD

Silicon Tuner IC

adjacent channels rejection; depends

on standards; see

Table 47

Table 43

9.3.14 Description of Extended bytes 1 to 23

Table 24. EB1 to EB23 - Extended bytes 1 to 23 (address 10h to 26h) bit description

Legend: * power-on reset value.

Address Register Bit Symbol Access Value Description

10h EB1 7 to 3 EB1[7:3] R 1 1111* extended byte 1

2 CALVCO_FORLON R determines VCO used during Normal

mode operations

1* LO VCO is used

0 CAL VCO is used

1 AGC1_ALWAYS_

MASTERN

0 AGC1_FIRSTN R determines whichAGCwill be updated

11h EB2 7 to 0 EB2[7:0] R/W 0000 0001* extended byte 2

12h EB3 7 to 0 EB3[7:0] R/W 1000 0100* extended byte 3

R enables AGC1 normal operation

whatever the tuner type (master or

slave)

1* normal operation for the master;

6 dB fixed for the slave

0 normaloperation for boththe master

and the slave

when detectors 1 and 2 are active

1* AGC1 and AGC2 both updated

0 AGC1 has priority on AGC2

TDA18271HD_3 © NXP B.V. 2008. All rights reserved.

Product data sheet Rev. 03 — 11 September 2008 19 of 69

Page 20

NXP Semiconductors

TDA18271HD

Silicon Tuner IC

Table 24. EB1 to EB23 - Extended bytes 1 to 23 (address 10h to 26h) bit description

…continued

Legend: * power-on reset value.

Address Register Bit Symbol Access Value Description

13h EB4 7 to 6 EB4[7:6] R/W 01* extended byte 4

5 LO_FORCESRCE R/W 1 forces the main PLL charge pump to

source current to the main PLL loop

filter

0* no force

4 to 0 EB4[4:0] R/W 0 0001* extended byte 4

14h EB5 7 to 0 EB5[7:0] R/W 0000 0001* extended byte 5

15h EB6 7 to 0 EB6[7:0] R/W 1000 0100* extended byte 6

16h EB7 7 and 6 EB7[7:6] R/W 01* extended byte 7

5 CAL_FORCESRCE R/W 1 forces the CAL PLL charge pump to

source current to the CAL PLL loop

filter

0* no force

4 to 0 EB7[4:0] R/W 0 1000* extended byte 7

17h EB8 7 CID_ALARM R signal sensed by the power detector

used during calibrations

1 out of range

0* in range

6 to 4 EB8[6:4] R/W 111 0101* extended byte 8

3 EB8[3] R

2 to 0 EB8[2:0] R/W

18h EB9 7 to 0 EB9[7:0] W 0000 0000* extended byte 9

19h EB10 7 and 6 EB10[7:6] R 00* extended byte 10

5 to 0 CID_GAIN[5:0] R - calibration power detector output

1Ah EB11 7 to 0 EB11[7:0] R/W 1000 0110* extended byte 11

1Bh EB12 7 and 6 EB12[7:6] R 00* extended byte 12

5 PD_AGC1_DET R/W AGC1 detector

1 power down

0* no power down

4 PD_AGC2_DET R/W AGC2 detector

1 power down

0* no power down

3 to 0 EB12[3:0] R/W 0111* extended byte 12

1Ch EB13 7 EB13[7] R/W 1* extended byte 13

6 to 4 RFC_K[2:0] R/W 100* parameters used during the RF

3 and 2 RFC_M[1:0] R/W 00*

1 to 0 EB13[1:0] R/W 10* extended byte 13

1Dh EB14 7 to 0 RFC_CPROG[7:0] R/W 0000 0000* tuning word of the RF tracking filters

1Eh EB15 7 to 4 EB15[7:4] R/W 1000 XXXX* extended byte 15

3 to 0 EB15[3:0] R

1Fh EB16 7 to 0 EB16[7:0] W 000X XX00* extended byte 16

tracking filter calibration (see

Table 46)

TDA18271HD_3 © NXP B.V. 2008. All rights reserved.

Product data sheet Rev. 03 — 11 September 2008 20 of 69

Page 21

NXP Semiconductors

TDA18271HD

Silicon Tuner IC

Table 24. EB1 to EB23 - Extended bytes 1 to 23 (address 10h to 26h) bit description

…continued

Legend: * power-on reset value.

Address Register Bit Symbol Access Value Description

20h EB17 7 to 0 EB17[7:0] W 000X XXXX* extended byte 17

21h EB18 7 AGC1_LOOP_OFF R/W turns the AGC1 loop

1 off

0* on

6 to 2 EB18[6:2] R/W 00000* extended byte 18

1 and 0 AGC1_GAIN[1:0] R/W AGC1 gain

00* 6 dB

01 9 dB

10 12 dB

11 15 dB

22h EB19 7 to 0 EB19[7:0] W 000X XX00* extended byte 19

23h EB20 7 and 6 EB20[7:6] W 10* extended byte 20

5 FORCE_LOCK W forces the internal lock indicator

1 forced to logic 1

0* not forced

4 to 0 EB20[4:0] W X XXXX* extended byte 20

24h EB21 7 AGC2_LOOP_OFF R/W turns the AGC2 loop

1 off

0* on

6 to 2 EB21[6:2] R/W 00000* extended byte 21

1 and 0 AGC2_GAIN[1:0] R/W AGC2 gain

00* −15 dB

01 −12 dB

10 −9 dB

11 −6 dB

25h EB22 7 EB22[7] R 0* extended byte 22

6 to 4 RF_TOP[2:0] R/W 100* Take-Over Point of the RF AGC,

detection in RF

3 to 0 IF_TOP[3:0] R/W 1000* Take-Over Point of the RF AGC,

detection in IF

26h EB23 7 to 3 EB23[7:3] R/W 1 0110* extended byte 23

2 FORCELP_

FC2_EN

1 LP_FC R/W 0*

0 EB23[0] R/W 0* extended byte 23

R/W 0* FM filter selection; see

Table 26

Table 25 and

TDA18271HD_3 © NXP B.V. 2008. All rights reserved.

Product data sheet Rev. 03 — 11 September 2008 21 of 69

Page 22

NXP Semiconductors

Table 25. Low-pass cut-off frequency when using RF_IN input

RF input FORCELP_FC2_EN LP_FC STD[1:0] Cut-off frequency (MHz)

RF_IN 1 1 XX 1.5

Table 26. Low-pass cut-off frequency when using FM_IN input

RF input FORCELP_FC2_EN LP_FC STD[1:0] Cut-off frequency (MHz)

FM_IN 1 0 00 6

TDA18271HD

Silicon Tuner IC

0 X 00 6

0 X 01 7

0 X 10 8

0 X 11 9

1 0 01 7

1 0 10 8

1 0 11 9

1 1 XX 1.5

9.4 I2C-bus programming flowcharts

The following flowcharts describe how to:

• Initialize the TDA18271HD

• Launch the calibrations

• Go to Normal mode

The image rejection calibration and RF trackingfilter calibration must be launched exactly

as described in the flowchart, otherwise bad calibration or even blocking of the

TDA18211HD can result making it impossible to communicate via the I2C-bus.

Proper internal initialization requires switching to Normal mode using a single I2C-bus

sequence from subaddresses 03h to 0Fh.

9.4.1 Flowchart explanation

This section provides instructions for reading the flowcharts.

TDA18271HD_3 © NXP B.V. 2008. All rights reserved.

Product data sheet Rev. 03 — 11 September 2008 22 of 69

Page 23

NXP Semiconductors

MS

TDA18271HD

Silicon Tuner IC

master or slave

2

C-bus write

for I

actions registers to update

initialization phase

in the software

internal table

Internal table I2C-bus

IR_GSTEP = 2h

I2C_XTOUT_ASYM = 1

PD_AGC1_DET = 1

IR_GSTEP = 2h,

I2C_XTOUT_ASYM = 1,

PD_AGC1_DET = 1

- EP5

- EP1...CD2

- EP1...EP2,

tuner registers

update

EP5

EB12

EB13

-

EB12

EB13

MD3

001aag935

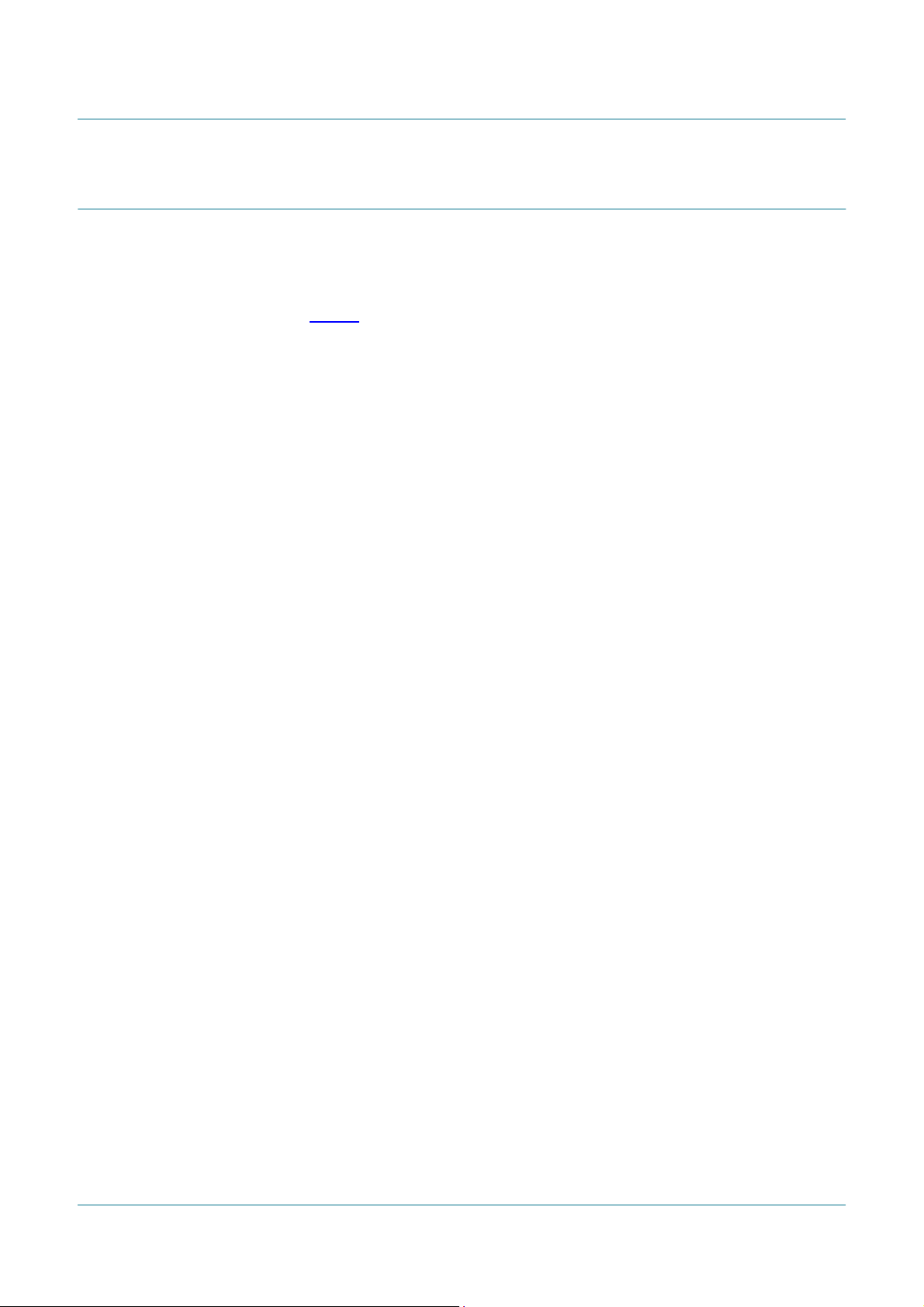

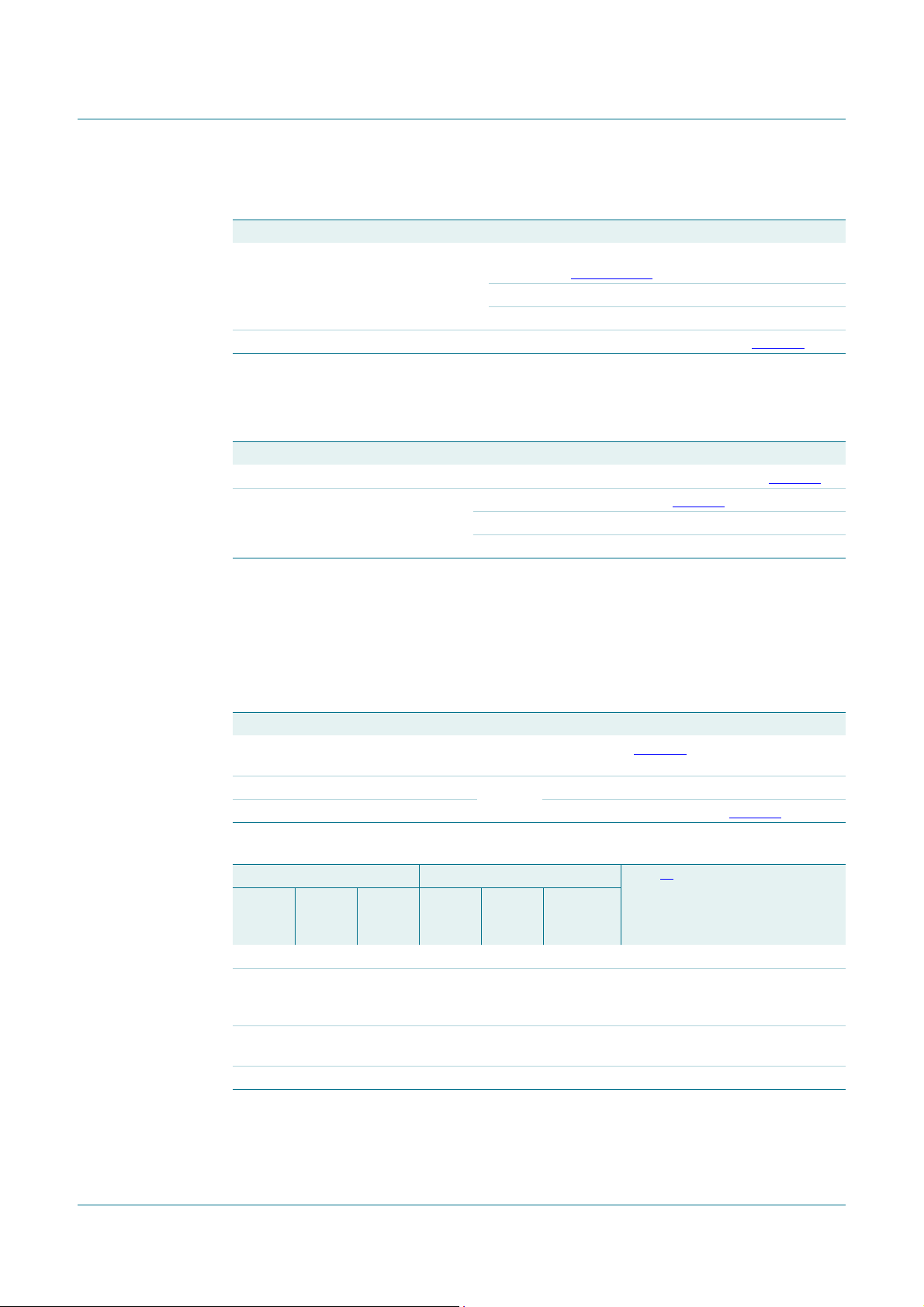

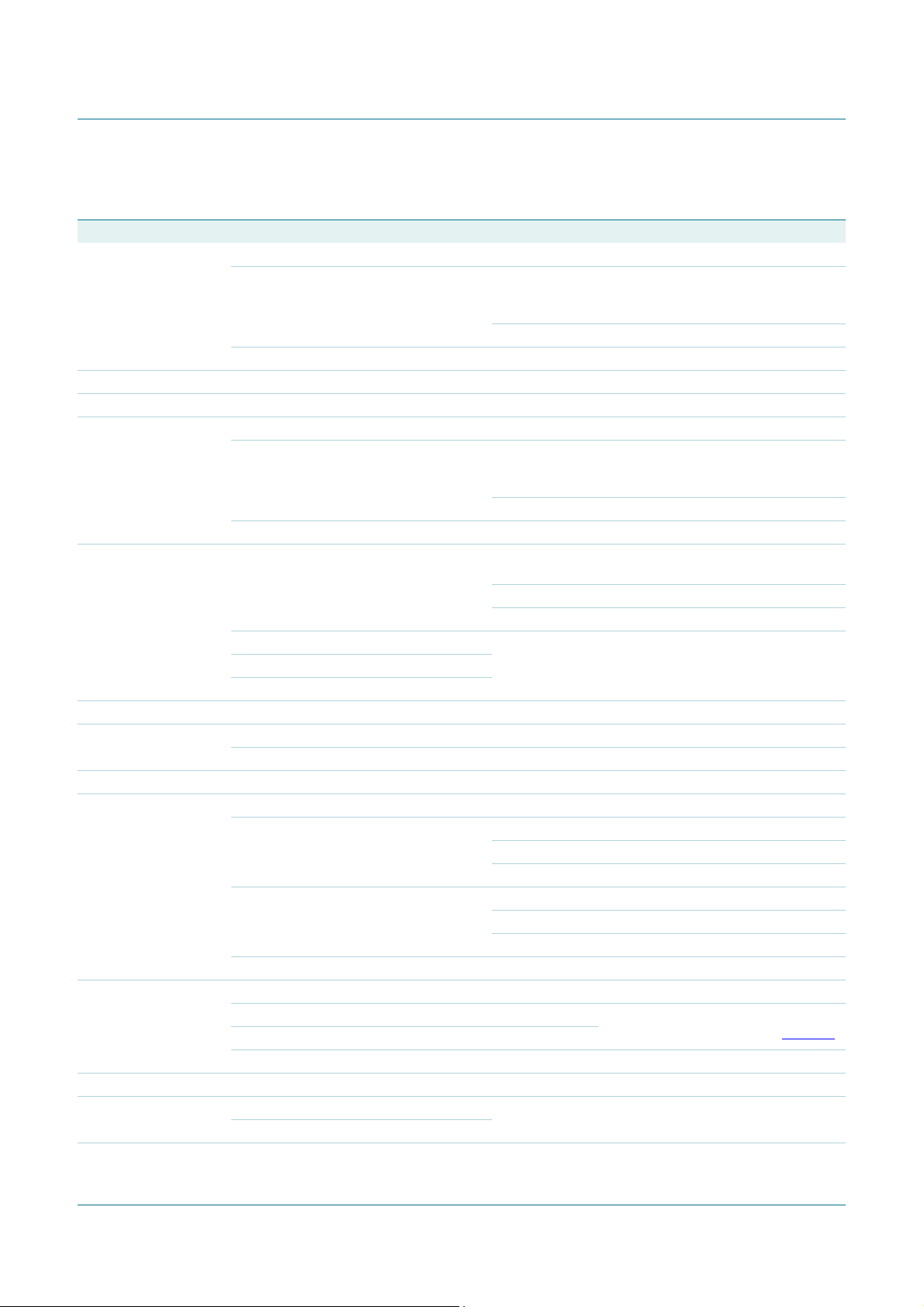

Fig 3. Programming sequence

1. I2C-bus write:

– IR_GSTEP is updated, no immediate I2C-bus write

– I2C_XTOUT_ASYM is updated followed by an I2C-bus write of byte EP5

– PD_AGC1_DET is updated followed by an I2C-bus write of byte EB12

– I2C-bus write of byte EB13 with current value of the software internal register of

byte EB13

I2C-bus read:

– Subaddressing is not supported in read mode

– The mandatory I2C-bus read access procedures to the TDA18271HD are

described in Section 9.4.16 “Flowchart TDA18271Read” and Section 9.4.17

“Flowchart TDA18271ReadExtended”

2. Update at the same time is indicated by separation with commas:

IR_GSTEP, I2C_XTOUT_ASYM and PD_AGC1_DET are updated, no I2C-bus

registers updated

3. I2C-bus registers update bytes EP5, EB12 and EB13

4. Bytes EP1 to CD2 are written in a single I2C-bus sequence

Example:

Start C0 03 EP1 EP2 EP3 EP4 EP5 CPD CD1 CD2 Stop

5. Bytes EP1, EP2 and MD3 are written in as many I2C-bus sequences as needed

Example:

Start C0 03 EP1 EP2 Stop

Start C0 0F MD3 Stop

TDA18271HD_3 © NXP B.V. 2008. All rights reserved.

Product data sheet Rev. 03 — 11 September 2008 23 of 69

Page 24

NXP Semiconductors

TDA18271HD

Silicon Tuner IC

X

X

X

X

X

X

X

X

stored or already calculated data

input variable

result of an operation

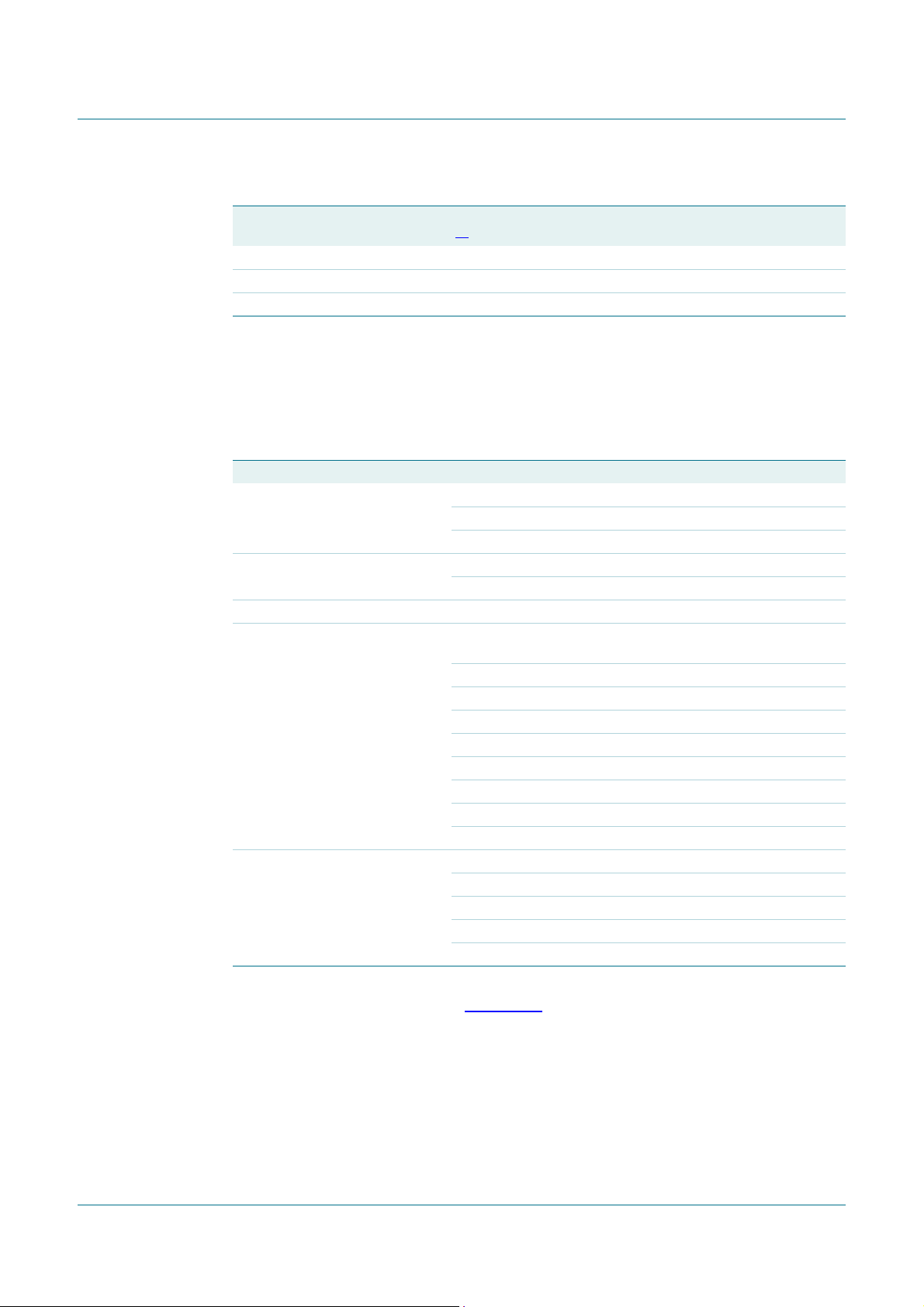

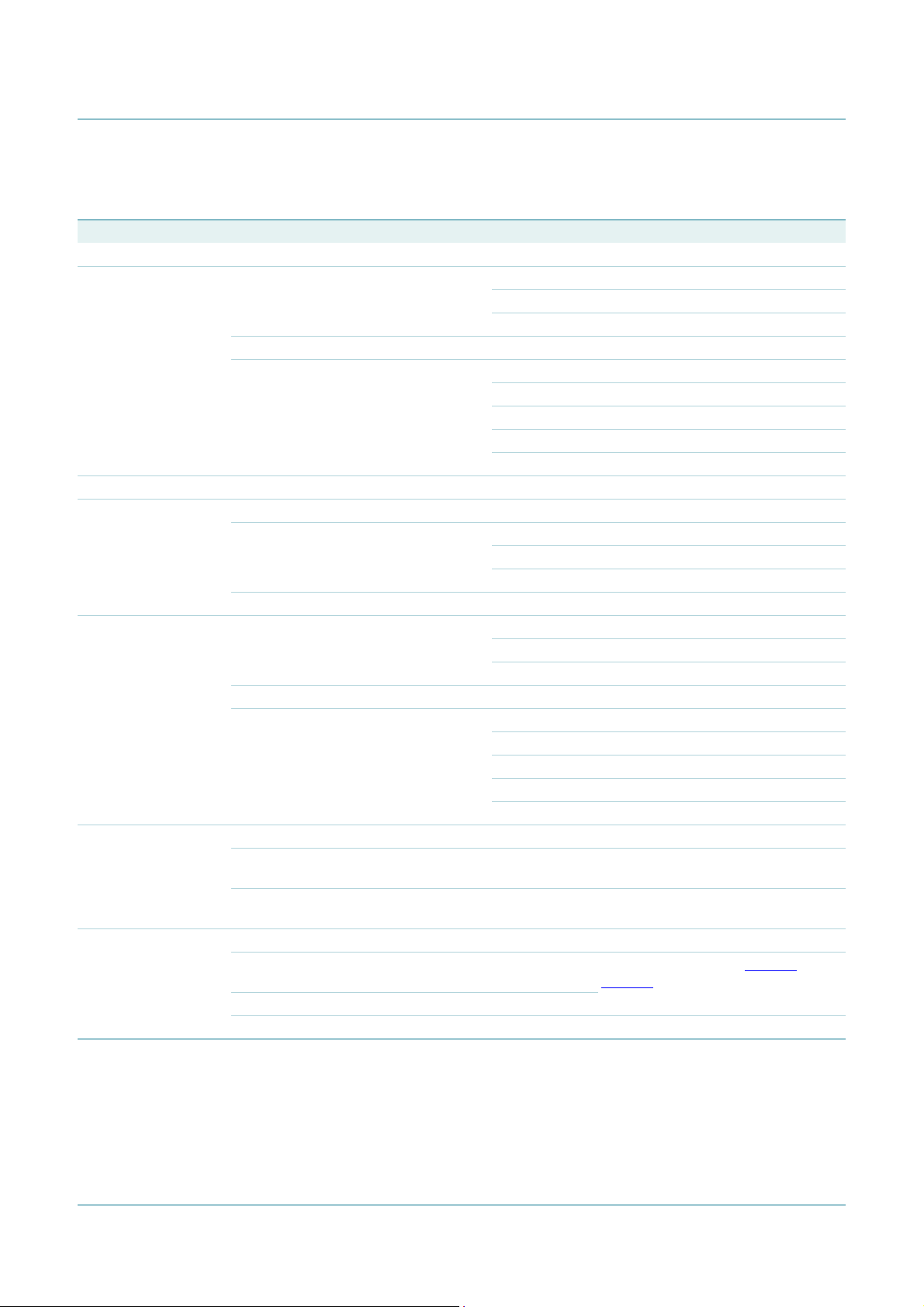

output variable

Fig 4. Blocks used in the flowcharts

I2C-bus initialization sequence

Call TDA18271FixedContentsI2Cupdate

MS_init

Calibrate the RF tracking filters

call TDA18271CalcRFFilterCurve

Back to POR

Call TDA18271MSPOR

Master/slave variable MS_init is input for each of the three procedures.

Fig 5. Variable used in multiple procedures

001aag722

001aah042

xx_in

XY_map

yy_outFind yy = f(xx) in XY_map

001aag822

xx is a list of values stored in the first column of the map XY_map.

yy is a list of values stored in column in XY_map

yy_out is the particular value of yy to find row n. xx(n − 1) < xx_in ≤ xx(n)

a. General description to find a value in a table

650 MHz

KM_map

Finding the row of RFC_K: 350000 < 650000 ≤ 720000. Result n = 1. The value of RFC_K is then

3; see Table 46

Find RFC_K = f

KM_map

RF(max)

in

RFC_K

001aag723

b. Example to find the value RFC_K corresponding to fRF= 650 MHz in the KM_map

Fig 6. Finding a value in a table

Units: In the flowcharts, hexadecimal values end with “h”, decimal values with “d”.

TDA18271HD_3 © NXP B.V. 2008. All rights reserved.

Product data sheet Rev. 03 — 11 September 2008 24 of 69

Page 25

NXP Semiconductors

9.4.2 Flowchart TDA18271SetRf_dual

The initialization phase has to be launched before any SetRf.

Table 27. TDA18271SetRf_dual

Function Description Reference

Description protocol top view for a dual tuner application

Input RF_freq, Standard (from microcontroller), MS (from microcontroller)

Table Output -

[1] MS = 1: master is selected for the channel configuration; MS = 0: slave is selected for the channel

configuration.

Start

TDA18271SetRf_dual

Yes

init_done = 1

TDA18271HD

Silicon Tuner IC

[1]

Master and slave initialization

Call TDA18271InitCal

TMVALUE_RFCAL

RF_freq

MS

Standard

RF_freq

MS

Set the RF tracking filters

Call TDA18271RFTrackingFiltersCorrection

Set the tuner to the wanted channel

Call TDA18271ChannelConfiguration

Fig 7. Flowchart TDA18271SetRf_dual

9.4.3 Flowchart TDA18271InitCal

Table 28. TDA18271InitCal

Function Description Reference

Description systematic initializations for master and slave

tuners

Input MS_init

Table Output TMVALUE_RFCAL, init_done

No

End

TDA18271SetRf_dual

TMVALUE_RFCAL

init_done

001aah043

TDA18271HD_3 © NXP B.V. 2008. All rights reserved.

Product data sheet Rev. 03 — 11 September 2008 25 of 69

Page 26

NXP Semiconductors

TDA18271HD

Silicon Tuner IC

Start

TDA18271InitCal

MS_init

MS_init

MS_init = 1

Master initialization

2

C-bus initialization sequence

I

Call TDA18271FixedContentsI2Cupdate

Calibrate the RF tracking filters

Call TDA18271CalcRFFilterCurve

Back to POR

Call TDA18271MSPOR

MS_init = 0

Slave initialization

2

C-bus initialization sequence

I

Call TDA18271FixedContentsI2Cupdate

Calibrate the RF tracking filters

Call TDA18271CalcRFFilterCurve

Back to POR

Call TDA18271MSPOR

init_done = true

MS_init

TMVALUE_RFCAL

MS_init

init_done

End

TDA18271InitCal

001aah044

Fig 8. Flowchart TDA18271InitCal

9.4.4 Flowchart TDA18271FixedContentsI2Cupdate

Table 29. TDA18271FixedContentsI2Cupdate

Function Description Reference

Description update and write the TDA18271HD registers

sequential update of AGC1 and AGC2

image calibration algorithm

Input MS

Table Output -

The register contents are not described in detail as this procedure is not to be modified.

TDA18271HD_3 © NXP B.V. 2008. All rights reserved.

Product data sheet Rev. 03 — 11 September 2008 26 of 69

Page 27

NXP Semiconductors

TDA18271HD

Silicon Tuner IC

TDA18271FixedContentsI2Cupdate

Start

Actions

Internal table update with

correct values

Tuner registers update

AGC1 gain setup EB17 = 00h

MS

Internal table

TM = 08h

PL = 80h

EP1 = C6h

EP2 = DFh

EP3 = 16h

EP4 = 60h

EP5 = 80h

CPD = 80h

CD1 = 00h

CD2 = 00h

CD3 = 00h

MPD = 00h

MD1 = 00h

MD2 = 00h

MD3 = 00h

EB1 = FCh

EB2 = 01h

EB3 = 84h

EB4 = 41h

EB5 = 01h

EB6 = 84h

EB7 = 40h

EB8 = 07h

EB9 = 00h

EB10 = 00h

EB11 = 96h

EB12 = 33h

EB13 = C1h

EB14 = 00h

EB15 = 8Fh

EB16 = 00h

EB17 = 00h

EB18 = 8Ch

EB19 = 00h

EB20 = 20h

EB21 = B3h

EB22 = 48h

EB23 = B0h

- TM...EB23

EB17 = 03h

EB17 = 43h

EB17 = 4Ch

I2C-bus

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

EB17

EB17

EB17

EB17

IRCAL low band

initialization

Tuner registers update

MAIN PLL CP source on

Wait 1 ms

MAIN PLL CP source off EB4 = 41h EB4

Wait 5 ms - PLL locking

Launch detector

Wait 5 ms - measurement

CAL PLL update EP5 = 85h

Tuner registers update

Wait 5 ms - PLL locking

Launch optimization algorithm Wait 30 ms - optimization

IRCAL mid band

initialization

Tuner registers update - EP3...MD3

Wait 5 ms - PLL locking

Launch detector

Wait 5 ms - measurement

CAL PLL update EP5 = 86h

Tuner registers update

Wait 5 ms - PLL locking

Launch optimization algorithm Wait 30 ms - optimization

EP3 = 1Fh

EP4 = 66h

EP5 = 81h

CPD = CCh

CD1 = 6Ch

CD2 = 00h

CD3 = 00h

MPD = CDh

MD1 = 77h

MD2 = 08h

MD3 = 00h

- EP3...MD3

EB4 = 61h EB4

-

CPD = CBh

CD1 = 66h

CD2 = 70h

EP5 = 82h

CPD = A8h

CD2 = 00h

MPD = A9h

MD1 = 73h

MD2 = 1Ah

-

CPD = A8h

CD1 = 66h

CD2 = A0h

- EP3...CD3

-

-

-

-

-

-

-

-

-

-

-

EP1

-

-

-

-

- EP3...CD3

EP2

-

-

-

-

-

-

EP1

-

-

-

-

EP2

IRCAL high band

initialization

Tuner registers update - EP3...MD3

Wait 5 ms - PLL locking

Launch detector

Wait 5 ms - measurement

CAL PLL update EP5 = 87h

Tuner registers update

Wait 5 ms - PLL locking

Launch optimization algorithm Wait 30 ms - optimization

TDA18271FixedContentsI2Cupdate

End

EP5 = 83h

CPD = 98h

CD1 = 65h

CD2 = 00h

MPD = 99h

MD1 = 71h

MD2 = CDh

-

CD1 = 65h

CD2 = 50h

- EP3...CD3

-

-

-

-

-

-

-

EP1

-

-

-

EP2

EP4Back to normal mode EP4 = 64h

EP1Synchronization -

001aah045

Fig 9. Flowchart TDA18271FixedContentsI2Cupdate

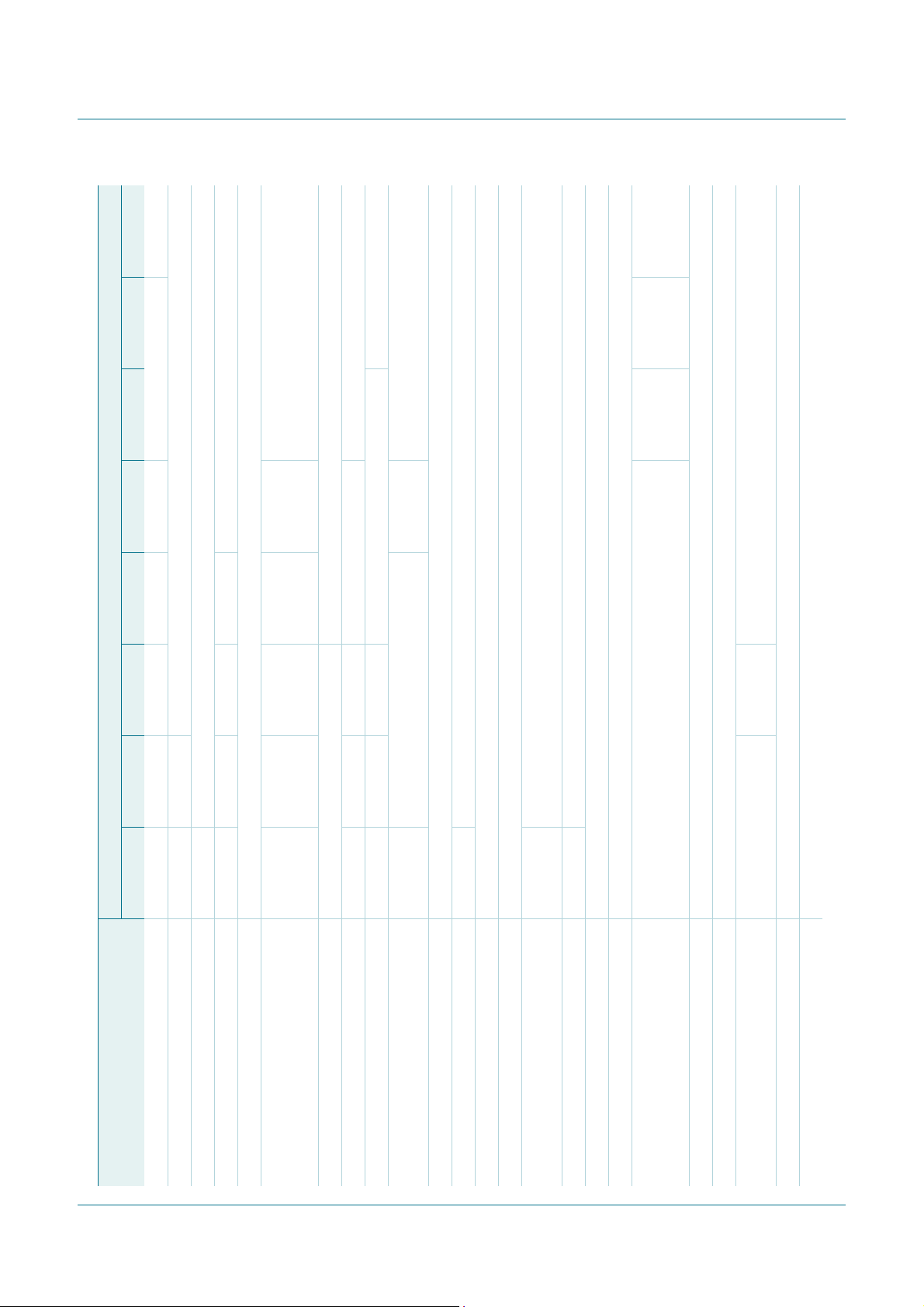

9.4.5 Flowchart TDA18271CalcRFFilterCurve

Table 30. TDA18271CalcRFFilterCurve

Function Description Reference

Description calculate the RF filter curve coefficients

Input RF1_default, RF2_default, RF3_default, MS

Table RF_BAND_map

Output TMVALUE_RFCAL

TDA18271HD_3 © NXP B.V. 2008. All rights reserved.

Product data sheet Rev. 03 — 11 September 2008 27 of 69

Table 45 “RF_BAND_map”

Page 28

NXP Semiconductors

TDA18271HD

Silicon Tuner IC

MS

f

RF(max)

f

RF(max)

f

RF(max)

f

RF(max)

TDA18271CalcRFFilterCurve

Wait 200 ms for die temperature stabilization

PowerScan Initialization

Call TDA18271Po werScanInit

f

= 47900 kHz

RF(max)

RF_Band 0 filters calibration

Call TDA18271RFTrackingFiltersInit

f

= 61100 kHz

RF(max)

RF_Band 1 filters calibration

Call TDA18271RFTrackingFiltersInit

f

= 152600 kHz

RF(max)

RF_Band 2 filters calibration

Call TDA18271RFTrackingFiltersInit

f

= 164700 kHz

RF(max)

RF_Band 3 filters calibration

Call TDA18271RFTrackingFiltersInit

Start

f

RF(max)

RF1_0, RF_A1_0,

RF_B1_0

f

RF(max)

RF1_1, RF_A1_1,

RF_B1_1

f

RF(max)

RF1_2, RF_B1_2,

RF2_2, RF_A1_2

f

RF(max)

RF1_3, RF_A1_3,

RF_B1_3

f

= 203500 kHz

RF(max)

f

RF(max)

f

RF(max)

f

RF(max)

Variable RF_max is used for frequency f

RF_Band 4 filters calibration

Call TDA18271RFTrackingFiltersInit

f

= 457800 kHz

RF(max)

RF_Band 5 filters calibration

Call TDA18271RFTrackingFiltersInit

f

= 865000 kHz

RF(max)

RF_Band 6 filters calibration

Call TDA18271RFTrackingFiltersInit

Read die current temperature

Call TDA18271ThermometerRead

TDA18271CalcRFFilterCurve

RF(max)

Fig 10. Flowchart TDA18271CalcRFFilterCurve

f

RF(max)

RF1_4, RF_A1_4,

RF_B1_4

f

RF(max)

RF1_5, RF_B1_5, RF2_5, RF_A1_5,

RF3_5, RF_A2_5, RF_B2_5

f

RF(max)

RF1_6, RF_B1_6, RF2_6, RF_A1_6,

RF3_6, RF_A2_6, RF_B2_6

TMVALUE_RFCAL

End

001aah046

.

TDA18271HD_3 © NXP B.V. 2008. All rights reserved.

Product data sheet Rev. 03 — 11 September 2008 28 of 69

Page 29

NXP Semiconductors

9.4.6 Flowchart TDA18271RFTrackingFiltersInit

Table 31. TDA18271RFTrackingFiltersInit

Function Description Reference

Description calculate the RF filter curve coefficients used

Input f

Table RF_CAL_map (Cprog_table = f (frequency))

Output RF1, RF2, RF3, RF_A1, RF_B1, RF_A2,

bcal is a boolean output from TDA18271PowerScan:

bcal = 1 (true): enables the calibration of the RF tracking filters

bcal = 0 (false): no calibration is performed, default values for RFC_CPROG are used

for their approximation

, MS

RF(max)

RF_B2

TDA18271HD

Silicon Tuner IC

Table 51 “RF_CAL_map”

TDA18271HD_3 © NXP B.V. 2008. All rights reserved.

Product data sheet Rev. 03 — 11 September 2008 29 of 69

Page 30

NXP Semiconductors

RF1_default

MS

MS

RF1

Start

TDA18271RFTrackingFiltersInit

RF_A1 = 0, RF_B1 = 0, RF_A2 = 0, RF_B2 = 0

Find RF1_default, RF2_default, RF3_default = f

Look for optimized calibration frequency

Call TDA18271PowerScan

bcal = 1

Yes

Find Cprog_cal1 to track RF1

Call TDA18271CalibrateRF

in RF_Band_map

RF(max)

No

TDA18271HD

Silicon Tuner IC

RF1_default,

RF2_default,

RF3_default

RF1

bcal

RF1

Cprog_cal1

RF1

RF_CAL_map

RF1

Cprog_cal1

Cprog_table1

RF2_default

MS

MS

RF2

RF2

RF_CAL_map

Cprog_table2

RF1

RF2

Cprog_cal1

Cprog_cal2

Cprog_table1

Cprog_table2

RF3_default

MS

MS

RF3

Find Cprog_table = f

Cprog_cal1 = Cprog_table1

RF_B1 = Cprog_cal1 − Cprog_table1

Look for optimized calibration frequency

Call TDA18271PowerScan

Find Cprog_cal2 to track RF2

Call TDA18271CalibrateRF

Find Cprog_table = f

Cprog_cal2 = Cprog_table2

RF_A1 = (Cprog_cal2 − Cprog_table2 − Cprog_cal1 + Cprog_table1) /

(RF2 − RF1)

Look for optimized calibration frequency

Call TDA18271PowerScan

Find Cprog_cal3 to track RF3

Call TDA18271CalibrateRF

RF(max)

RF(max)

in RF_CAL_map

bcal = 0

Yes

RF2_default = 0

No

bcal = 1

Yes

in RF_CAL_map

bcal = 0

Yes

RF3_default = 0

No

bcal = 1

Yes

No

Yes

No

No

Yes

No

Cprog_table1

Cprog_cal1Cprog_table1

RF_B1

RF_A1

TDA18271 RFTrackingFiltersInit

TDA18271 RFTrackingFiltersInit

End

bcal

RF2

RF2

Cprog_cal2

Cprog_table2

Cprog_cal2

RF_A1

End

bcal

RF3

RF3

Cprog_cal3

RF3

RF_CAL_map

RF2

RF3

Cprog_cal2

Cprog_cal3

Cprog_table2

Cprog_table3

Find Cprog_table = f

Cprog_cal3 = Cprog_table3

RF_A2 = (Cprog_cal3 − Cprog_table3 − Cprog_cal2 + Cprog_table2)/(RF3 − RF2)

RF_B2 = Cprog_cal2 − Cprog_table2

in RF_CAL_map

RF(max)

bcal = 0

Yes

End

TDA18271RFTrackingFiltersInit

No

Cprog_table3

Cprog_cal3Cprog_table3

RF_A2

RF_B2

001aah047

Fig 11. Flowchart TDA18271RFTrackingFiltersInit

TDA18271HD_3 © NXP B.V. 2008. All rights reserved.

Product data sheet Rev. 03 — 11 September 2008 30 of 69

Page 31

NXP Semiconductors

9.4.7 Flowchart TDA18271PowerScanInit

Table 32. TDA18271PowerScanInit

Function Description Reference

Description fixed settings of the TDA18271PowerScan

Input MS

Table Output -

Frequency unit during the algorithm in kHz.

Variable count homogeneous to kHz.

TDA18271HD

Silicon Tuner IC

TDA18271PowerScanInit

Start

Actions

Set standard mode to digital mode

Set AGC1_GAIN to 6 dB

Set AGC2_GAIN to −15 dB

End

TDA18271PowerScanInit

Fig 12. Flowchart TDA18271PowerScanInit

9.4.8 Flowchart TDA18271PowerScan

Table 33. TDA18271PowerScan

Function Description Reference

Description find an interference-free calibration frequency

Input freq_input, MS

Table RF_BAND_map, RF_CAL_map,

CID_Target_map

Output bcal, freq_output

Internal table I2C-bus

STD = 12,

IF_LEVEL = 0

CAL_MODE = 0

- EP3...EP4Tuner registers update

AGC1_GAIN = 0

AGC2_GAIN = 0

FORCELP_FC2_EN = 1,

LP_FC = 1

- EB21...EB23Tuner register update

-

EB18

-

-1.5 MHz low-pass filter

Table 45 “RF_BAND_map”

Table 51 “RF_CAL_map”

Table 54 “CID_Target_map”

MS

001aah048

TDA18271HD_3 © NXP B.V. 2008. All rights reserved.

Product data sheet Rev. 03 — 11 September 2008 31 of 69

Page 32

NXP Semiconductors

TDA18271HD

Silicon Tuner IC

RF_BAND_map

RF_CAL_map

CID_Target_map

MS

freq_input

freq_MAINPLL

freq_input

sgn

count

freq_input

freq_MAINPLL

Start

TDA18271PowerScan

Actions

Find RF_BAND = f

Find Cprog_table = f

Find GAIN_TAPER = f

Find CID_Target count_limit = f

CID_Target_map

freq_MAINPLL = freq_input = 1 MHz

Downconvert freq_input to 1 MHz

Call TDA18271CalcMAINPLL

Wait 5 ms - PLL locking

Detection mode

Launch power detection measurement

Read power detection information

Call TDA18271ReadExtended

Algorithm Initialization

sgn = 1

freq_output = freq_input

bcal = 0

count = 0

wait = false

No

freq_MAINPLL = freq_input + (sgn × count) + 1 MHz

Downconvert updated freq_input to 1 MHz

Call TDA18271CalcMAINPLL

Wait 100 µs - PLL locking

in RF_BAND_map (MS)

RF(max)

in RF_CAL_map

RF(max)

in GAIN_TAPER_map

RF(max)

RF(max)

CID_GAIN < CID_Target

Yes

No

wait = true

Internal table I2C-bus

RF_BAND = RF_BAND

RFC_Cprog = Cprog_table

in

Yes

Wait 5 ms - PLL locking

wait = false

GAIN_TAPER = GAIN_TAPER

CID_Target = CID_Target

count_limit = count_limit

- EP2, EB14Tuner register update

CAL_MODE = 1

-

-

EP4

EP2

MS

CID_Target

count_limit

freq_MAINPLL

CID_GAIN

sgn

freq_output

bcal

count

wait

freq_MAINPLL

wait

Launch power detection measurement - EP2

Read power detection information

count

freq_MAINPLL

Call TDA18271ReadExtended

count = count + 200

No

count > count_limit

No

sgn = − sgn

count = 200

wait = true

CID_GAIN ≥ CID_Target

bcal = 1

freq_output = freq_MAINPLL − 1 MHz

Yes

End

TDA18271PowerScan

sgn > 0

No

Yes

Yes

bcal

freq_output

Fig 13. Flowchart TDA18271PowerScan

freq_input

bcal = 0

freq_output = freq_input

End

TDA18271PowerScan

bcal

freq_output

CID_GAIN

count

sgn

count

wait

001aah049

TDA18271HD_3 © NXP B.V. 2008. All rights reserved.

Product data sheet Rev. 03 — 11 September 2008 32 of 69

Page 33

NXP Semiconductors

9.4.9 Flowchart TDA18271CalibrateRF

Table 34. TDA18271RFCalibrateRF

Function Description Reference

Description finds the Cprog for which freq_input is the

Input freq_input, MS

Table BP_FILTER_map, KM_map and

Output RFC_CPROG

central frequency of the RF tracking filters

GAIN_TAPER_map

TDA18271HD

Silicon Tuner IC

Table 44 “BP_FILTER_map”

Table 46 “KM_map”

Table 49 “GAIN_TAPER_map”

TDA18271HD_3 © NXP B.V. 2008. All rights reserved.

Product data sheet Rev. 03 — 11 September 2008 33 of 69

Page 34

NXP Semiconductors

TDA18271HD

Silicon Tuner IC

BP_FILTER_map

KM_map

GAIN_TAPER_map

freq_input

MS

freq_input

freq_input + 1 MHz

Start TDA18271CalibrateRF

Actions

Normal mode

Switch OFF AGC1

Set AGC1_GAIN to 15 dB

Frequency dependent parameters update

Find BP_FILTER = f

Find GAIN_TAPER = f

Find RF_BAND = f

Find RFC_K, RFC_M = f

MAIN PLL charge pump source

CAL PLL charge pump source

Force DC-DC converter to 0 V

Disable PLLs lock

RF tracking filters calibration mode

Set the internal calibration signal

Call TDA18271CalcCALPLL

Downconvert the calibration signal to 1 MHz

Call TDA18271CalcMAINPLL

Wait 5 ms

Internal synchronization EP2, EP1, EP2, EP1

in BP_FILTER_map

RF(max)

in GAIN_TAPER_map

RF(max)

in RF_BAND_map (MS)

RF(max)

RF(max)

in KM_map

Internal table I2C-bus

CAL_MODE = 0

SM_LT = 1

AGC1_GAIN = 3h

BP_FILTER = BP_FILTER

GAIN_TAPER = GAIN_TAPER

RF_BAND = RF_BAND

RFC_K = RFC_K, RFC_M = RFC_M

- EP1 … EP3, EB13Tuner registers update

LO_FORCESRCE = 1

CAL_FORCESRCE = 1

RFC_CPROG = 0

FORCE_LOCK = 0

CAL_MODE = 3h

- EP4 … EP5Tuner registers update

MS

EP4

EB18

-

-

-

-

EB4

EB7

EB14

EB20

-

Normal operation for the MAIN PLL charge pump

Normal operation for the CAL PLL charge pump

Wait 10 ms - PLLs locking

Launch the RF Tracking filters calibration FORCE_LOCK = 1

Wait 60 ms - calibration ongoing

Normal mode

Switch ON AGC1

Set AGC1_GAIN to 6 dB

Tuner registers update

Synchronization

Get the calibration result

Call TDA18271ReadExtended

End TDA18271CalibrateRF

Fig 14. Flowchart TDA18271CalibrateRF

LO_FORCESRCE = 0

CAL_FORCESRCE = 0

CAL_MODE = 0

SM_LT = 0

AGC1_GAIN = 0

- EP3 ... EP4

- EP1

EB4

EB7

EB20

-

EB18

RFC_CPROG

001aah050

TDA18271HD_3 © NXP B.V. 2008. All rights reserved.

Product data sheet Rev. 03 — 11 September 2008 34 of 69

Page 35

NXP Semiconductors

9.4.10 Flowchart TDA18271MSPOR

Table 35. TDA18271MSPOR

Function Description Reference

Description master or slave tuner goes to Power-On Reset

Input MS

Table Output -

TDA18271HD

Silicon Tuner IC

(POR) mode

Start

TDA18271MSPOR

Actions

Power Up Detector 1

Turn AGC1 loop ON

Set AGC1_GAIN to 6 dB

Set AGC2_GAIN to −6 dB

POR mode

1.5 MHz low-pass filter disabled

End

TDA18271MSPOR

Internal table I2C-bus

PD_AGC1_DET = 0

AGC1_LOOP_OFF = 0

AGC1_GAIN = 0

AGC2_GAIN = 3h

SM = 1, SM_LT = 0,

SM_XT = 0

FORCELP_FC2_EN = 0,

LP_FC = 0

Fig 15. Flowchart TDA18271MSPOR

9.4.11 Flowchart TDA18271RFTrackingFiltersCorrection

Table 36. TDA18271RFTrackingFiltersCorrection

Function Description Reference

Description find the Cprog corresponding to the

programmed central frequency

freq_input

Input freq_input, TMVALUE_RFCAL, MS

Table RF_BAND_map,

RF_CAL_DC_OVER_DT_map,

RF_CAL_map

Output -

Table 45 “RF_BAND_map”

Table 50 “RF_CAL_DC_OVER_DT_map”

Table 51 “RF_CAL_map”

MS

EB12

EB18

-

EP3

EB21 ... EB23

001aah051

TDA18271HD_3 © NXP B.V. 2008. All rights reserved.

Product data sheet Rev. 03 — 11 September 2008 35 of 69

Page 36

NXP Semiconductors

TDA18271HD

Silicon Tuner IC

RF_CAL_map

RF_BAND_map

freq_input

MS

RF_A2

RF2

RF_B2

Cprog_table

freq_input

Start TDA18271RFT rackingFiltersCorrection

Action

Power-up TDA18271 SM = 0, SM_LT = 0,

Read current die temperature

Call TDA18271ThermometerRead

Frequency dependent parameters update

Find RFC_CPROG = f

Find RF1, RF2, RF3, RF_A1, RF_A2, RF_B1, RF_B2 = f

in RF_BAND_map (MS)

No

Capprox =

RF_A2 × (freq_input − RF2) +

RF_B2 + Cprog_table

in RF_CAL_map, Cprog_table = RFC_Cprog

RF(max)

Capprox

RF3 = 0 or

freq_input < RF2

RF_A1

RF1

RF_B1

Cprog_table

freq_input

RF(max)

Yes

Internal table I2C-bus

Capprox =

RF_A1 × (freq_input − RF1) +

RF_B1 + Cprog_table

SM_XT = 0

MS

EP3

TMVALUE_CURRENT

Cprog_table

RF1

RF2

RF3

RF_A1

RF_A2

RF_B1

RF_B2

Capprox

No No

in RF_CAL_DC_OVER_DT_map dCoverdT

RF_CAL_DC_OVER_DT_map

freq_input

dCoverdT

TMVALUE_CURRENT

TMVALUE_RFCAL

Capprox

RFCAL_TCOMP

Capprox < 0 Capprox > 255

Yes Yes

Find dCoverdT = f

Calculate temperature compensation

RFCAL_TCOMP = dCoverdT × (TMVALUE_CURRENT − TMVALUE_RFCAL)

Calculate final Cprog

Cprog = Capprox + RFCAL_TCOMP

RF(max)

End TDA18271RFTrackingFiltersCorrection

Fig 16. Flowchart TDA18271RFtrackingFiltersCorrection

Capprox = 255Capprox = 0

RFCAL_TCOMP

RFC_Cprog = Cprog EB14

001aah052

TDA18271HD_3 © NXP B.V. 2008. All rights reserved.

Product data sheet Rev. 03 — 11 September 2008 36 of 69

Page 37

NXP Semiconductors

9.4.12 Flowchart TDA18271ChannelConfiguration

Table 37. TDA18271ChannelConfiguration

Function Description Reference

Description tunes the tuner according to the

Input freq_input, MS, Standard

Table STANDARD_DESCRIPTION_map,

Output -

channel and broadcast configuration

BP_FILTER_map, RF_BAND_map,

CAL_PLL_map,

GAIN_TAPER_map, IR_MEAS_map

TDA18271HD

Silicon Tuner IC

Table 43 “STANDARD_DESCRIPTION_map”

Table 44 “BP_FILTER_map”

Table 45 “RF_BAND_map”

Table 48 “CAL_PLL_map”

Table 49 “GAIN_TAPER_map”

Table 53 “IR_MEAS_map”

TDA18271HD_3 © NXP B.V. 2008. All rights reserved.

Product data sheet Rev. 03 — 11 September 2008 37 of 69

Page 38

NXP Semiconductors

IF_freq

MS

C-bus

2

----EB22--

TDA18271HD

Silicon Tuner IC

-

-

MPD = CAL_POST_DIV & 7Fh MPD

in

LO(max)

EB7

EB7

CAL_FORCESRCE = 1

CAL_FORCESRCE = 0

001aah053

Start TDA18271ChannelConfiguration

from STANDARD_DESCRIPTION_map according to Standard

STD = STD from STANDARD_DESCRIPTION_map according to Standard value

STD[2] = 0

CAL_MODE = 0

IF_LEVEL = IF_LEVEL

IF_NOTCH = IF_NOTCH

EB22 = EB22

IF_FREQ = IF_FREQ

Actions Internal table I

Standard mode update

Update TV broadcast parameters

Switch RFAGC to high speed mode

Normal mode

Update IF output level

Update IF notch frequency

Update extended byte 22

Update IF center frequency

FM_RFn = FM_RFn

Update FM_RFn

IR_MEAS = IR_MEAS

BP_FILTER = BP_FILTER

RF_BAND = RF_BAND

GAIN_TAPER = GAIN_TAPER

CALVCO_FORLON = MS

AGC1_ALWAYS_MASTERN = 0

AGC1_FIRSTN = 0

in GAIN_TAPER_map

in BP_FILTER_map

in RF_BAND_map (MS)

in IR_MEAS_map

RF(max)

RF(max)

RF(max)

RF(max)

Update frequency dependent parameters

Find IR_MEAS = f

Disable power level indicator DIS_POWER_LEVEL = 1 -

Find RF_BAND = f

Find BP_FILTER = f

Dual Tuner and AGC1 extra configurations managing

Find GAIN_TAPER = f

MAIN VCO when Master, CAL VCO when Slave

AGC1 always active

AGC1 has priority on AGC2

- EB1

Yes

Tuner registers update

freq_pll = freq_input + IF_freq

No

MS = 1

Tune to wanted channel frequency

Call TDA18271CalcMAINPLL

Find CAL_POST_DIV = f

CAL PLL charge pump source

Wait 1 ms

Tuner registers update - TM ... EP5

CAL_PLL_map

freq_pll

CAL_PLL_map

freq_pll

- TM ... EP5

Tune to wanted channel frequency

Call TDA18271CalcMAINPLL

Tuner registers update

Normal operation for the CAL PLL

EB4

EB4

LO_FORCESRCE = 1

LO_FORCESRCE = 0

MAIN PLL charge pump source

Wait 1 ms

Normal operation for the MAIN PLL

Switch RFAGC to normal speed mode STD[2] = not (FM_RFn) EP3

Wait 20 ms

Switch RFAGC to normal speed mode STD[2] = not (FM_RFn) EP3

Wait 20 ms

End TDA18271ChannelConfiguration

End TDA18271ChannelConfiguration

xxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxx x x x xxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxx xx xx

xxxxx xxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxx xxxxxx xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxx x x

xxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxx xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxx

xxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxxx xxx

IR_MEAS_map

BP_FILTER_map

RF_BAND_map

GAIN_TAPER_map

freq_input

Standard

STANDARD_DESCRIPTION_

map

MS

MS

freq_input

IF_freq

freq_pll

Fig 17. Flowchart TDA18271ChannelConfiguration

TDA18271HD_3 © NXP B.V. 2008. All rights reserved.

Product data sheet Rev. 03 — 11 September 2008 38 of 69

Page 39

NXP Semiconductors

9.4.13 Flowchart TDA18271CalcMAINPLL

MPD, MD1, MD2 and MD3 are 8-bit registers. Arithmetical and logical operations

performed on these registers are handled as binary operations. Dividing is right shifting

and multiplying is left shifting.

Table 38. TDA18271CalcMAINPLL

Function Description Reference

Description finds the correct values for the bytes MPD,

Input freq_input, MS

Table MAIN_PLL_map

Output -

MAIN_PLL_map

freq_input

MD1, MD2, MD3 and update the tuner registers

Start TDA18271CalcMAINPLL

Find MAIN_POST_DIV, Div = f

in MAIN_PLL_map

LO(max)

TDA18271HD

Silicon Tuner IC

Table 47 “MAIN_PLL_map”

MAIN_POST_DIV

Div

MS

MAIN_POST_DIV

Div

freq_input

MAIN_DIV

Update MPD byte

MAIN_DIV = (Div × freq_input × 27) / 125

Update MD1, MD2, MD3 bytes

Tuner registers update

End TDA18271CalcMAINPLL

Fig 18. Flowchart TDA18271CalcMAINPLL

9.4.14 Flowchart TDA18271CalcCALPLL

CPD, CD1, CD2 and CD3 are 8-bit registers. Arithmetical and logical operations

performed on these registers are handled as binary operations. Dividing is right shifting

and multiplying is left shifting.

Internal table

MPD = MAIN_POST_DIV & 7Fh

16

MD1 = (MAIN_DIV / 2

MD2 = (MAIN_DIV / 2

MD3 = MAIN_DIV

-

) & 7Fh

8

)

I2C-bus

-

MAIN_DIV

-

MPD … MD3

001aah054

TDA18271HD_3 © NXP B.V. 2008. All rights reserved.

Product data sheet Rev. 03 — 11 September 2008 39 of 69

Page 40

NXP Semiconductors

Table 39. TDA18271CalcCALPLL

Function Description Reference

Description finds the correct values forthe bytes CPD, CD1,

Input freq_input, MS

Table CAL_PLL_map

Output -

CAL_PLL_map

freq_input

CD2, CD3 and update the tuner registers

Start TDA18271CalcCALPLL

Find CAL_POST_DIV, Div = f

in CAL_PLL_map

LO(max)

TDA18271HD

Silicon Tuner IC

Table 48 “CAL_PLL_map”

CAL_POST_DIV

Div

MS

CAL_POST_DIV

Div

freq_input

CAL_DIV

Update CPD byte

CAL_DIV = (Div × freq_input × 27) / 125

Update CD1, CD2, CD3 bytes

Tuner registers update

End TDA18271CalcCALPLL

Fig 19. Flowchart TDA18271CalcCALPLL

9.4.15 Flowchart TDA18271ThermometerRead

Table 40. TDA18271ThermometerRead

Function Description Reference

Description turns the on-chip temperature sensor ON,

reads the current temperature on the die and

then turns the temperature sensor OFF

Input MS

Table THERMOMETER_map

Output TMVALUE (temperature in °C)

Internal table

CPD = CAL_POST_DIV

CD1 = (CAL_DIV / 2

CD2 = (CAL_DIV / 2

CD3 = CAL_DIV

-

16

8

Table 52 “THERMOMETER_map”

) & 7Fh

)

I2C-bus

-

CAL_DIV

-

CPD … CD3

001aah055

TDA18271HD_3 © NXP B.V. 2008. All rights reserved.

Product data sheet Rev. 03 — 11 September 2008 40 of 69

Page 41

NXP Semiconductors

TDA18271HD

Silicon Tuner IC

TDA18271ThermometerRead

Switch thermometer ON

Read thermometer information

Call TDA18271Read

No

(TM_D = 0) and (TM_RANGE = 1)

(TM_D = 8) and (TM_RANGE = 0)

Switch TM_RANGE

Wait 10 ms - temperature sensing

Read thermometer information

Call TDA18271Read

Start

or

Yes

Internal tableActions

TM_ON = 1

TM_RANGE = not (TM_RANGE)

MS

I2C-bus

TM

TM_RANGE

TM_D

TM

TM_RANGE

TM_D

TM_D

TM_RANGE

Find TMVALUE = f (TM_D, TM_RANGE) in

THERMOMETER_map

Switch thermometer OFF

Normal mode

End

TDA18271ThermometerRead

Fig 20. Flowchart TDA18271ThermometerRead

9.4.16 Flowchart TDA18271Read

Table 41. TDA18271Read

Function Description Reference

Description reads the first 16 bytes of the TDA18271HD

Input MS

Table Output an image of the tuner registers from TM to MD3

The internal software registers are never updated at any time during the read procedure

but are updated when the TDA18271Read is called.

The I2C-bus read in the TDA18271HD does not support subaddressing or variable length

sequences. The chip can only be read by performing read sequences TDA18271Read

(16 bytes) or TDA18271ReadExtended (39 bytes).

TM_ON = 0

CAL_MODE = 0

TMVALUE

TM

EP4

001aah056