A B

D

HGFEC

P65U V10

GP106 8GB/4GB GDDR5, 256b, 256Mx32/128MX32

1

Tall DVI-D + HDMI+ DP

TABLE OF CONTENTS

Page

2

3

4

Description

Table of Contents

1

Block Biagram

2

PCI Express

3

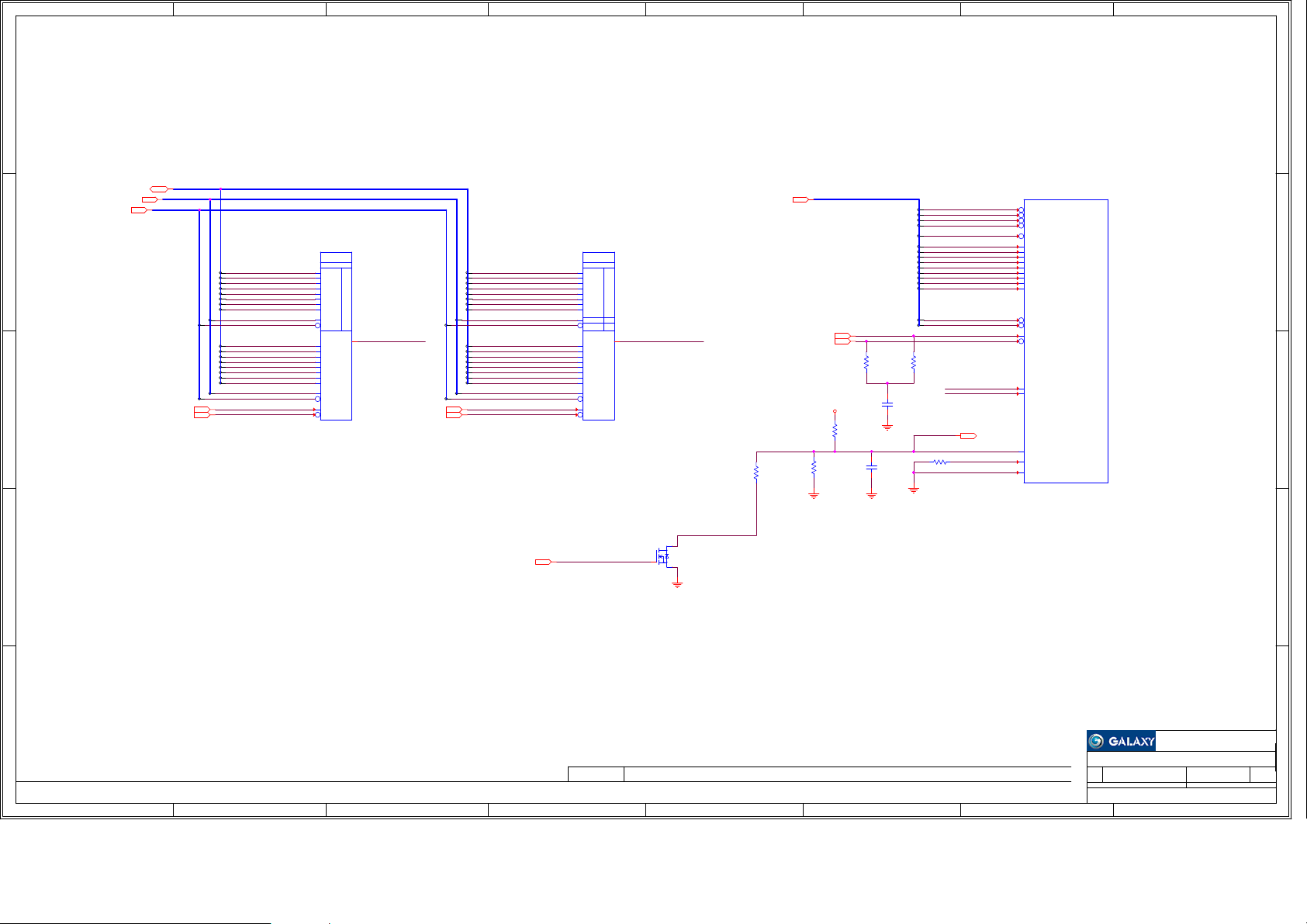

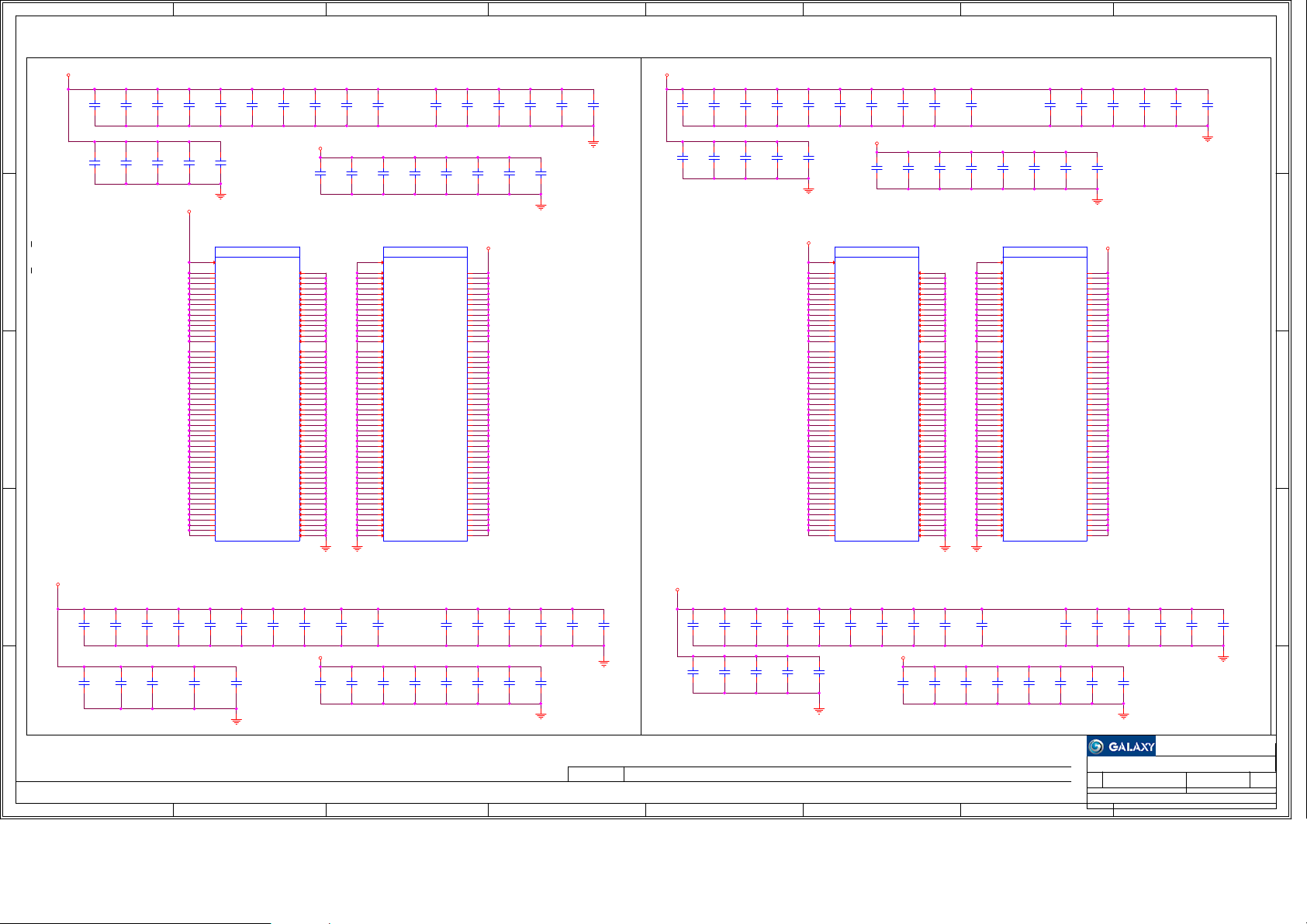

GPU FB_AB

4

MEMORY: FBA[31:0]

5

MEMORY: FBA[63:32]

6

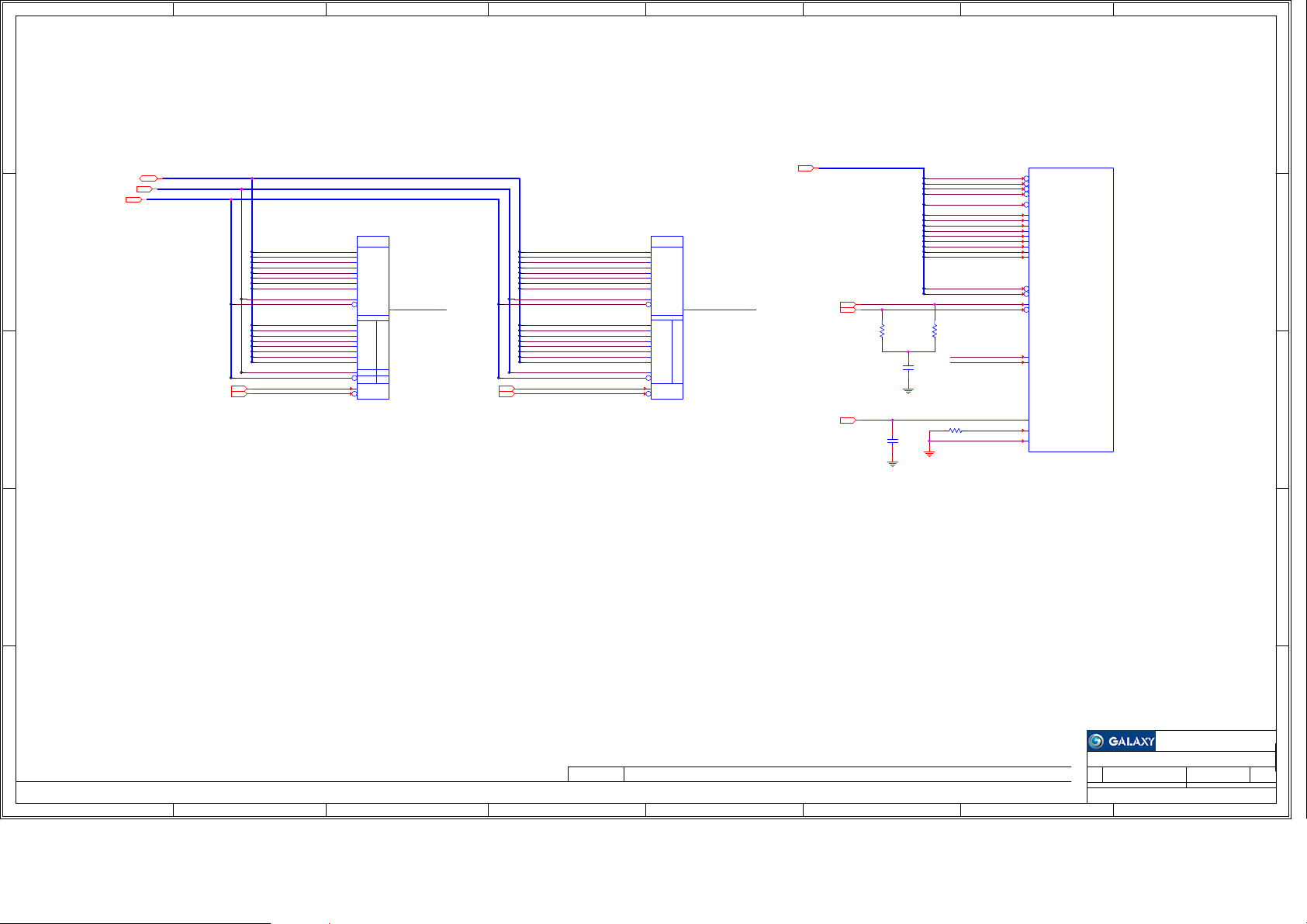

MEMORY: FBB[31:0]

7

MEMORY: FBB[63:32]

8

9

MEM FB_AB PWR

10

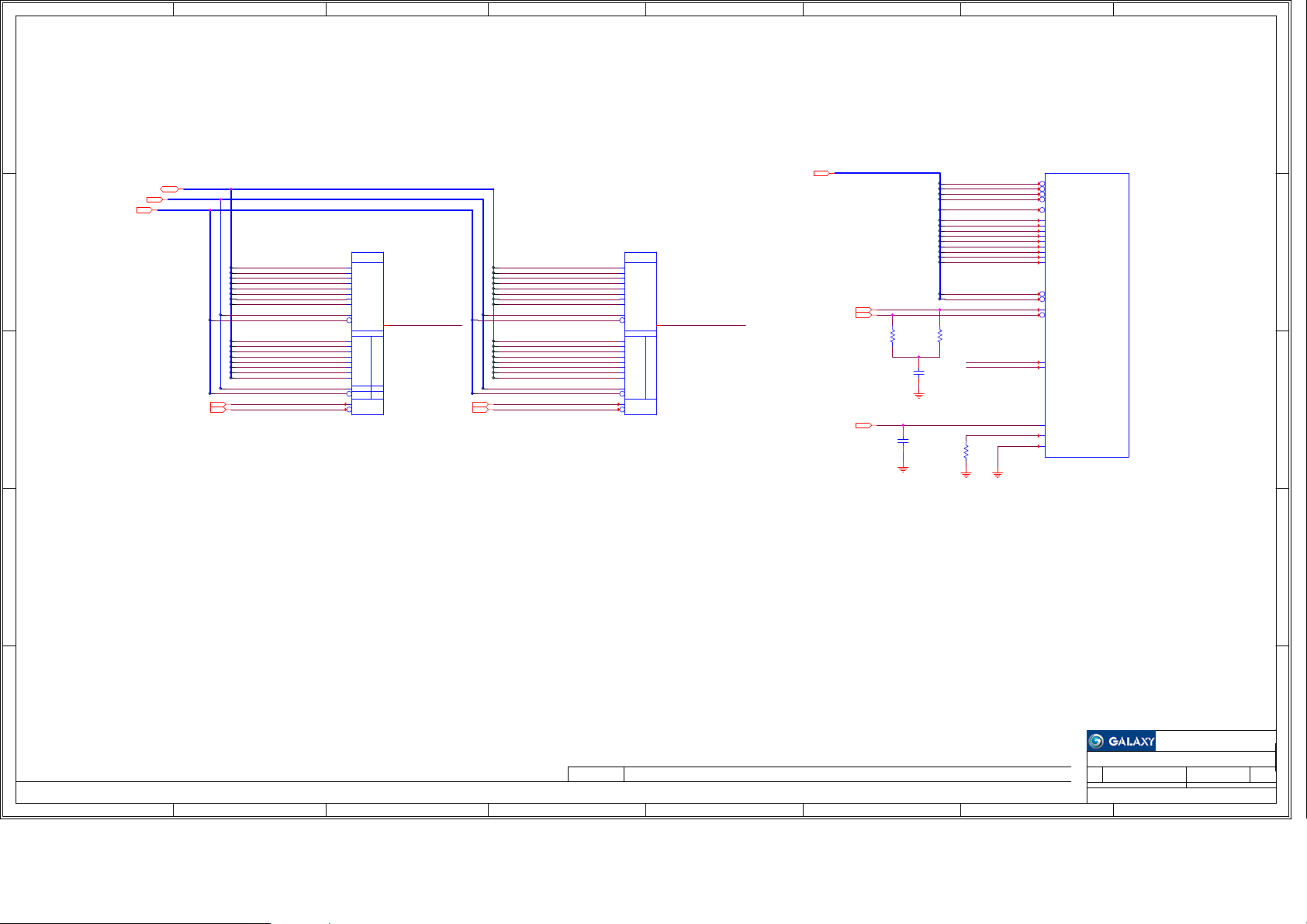

GPU FB_CD

MEMORY: FBC[31:0]

11

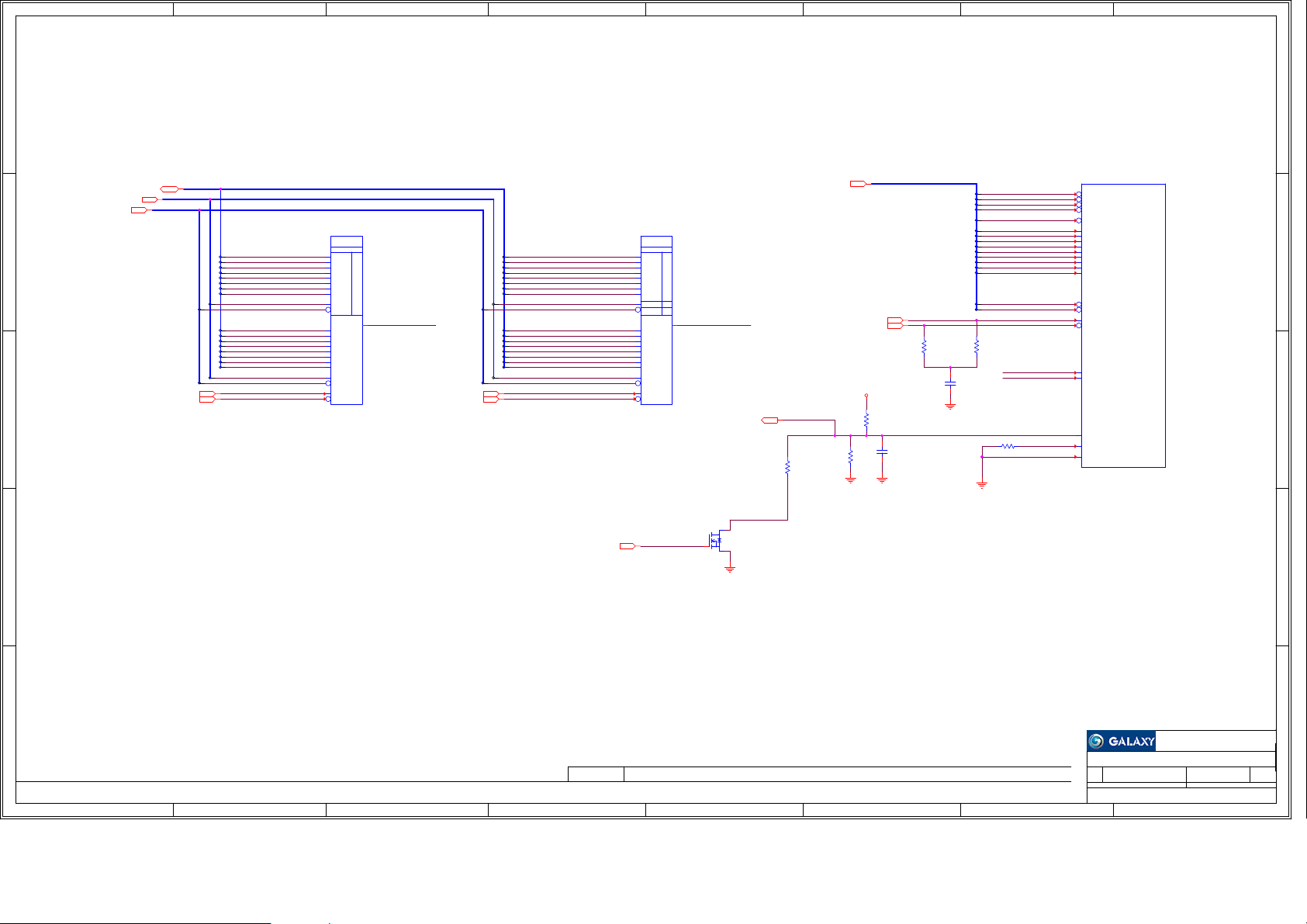

MEMORY: FBC[63:32]

12

13

MEMORY: FBD[31:0]

MEMORY: FBD[63:32]

14

MEM FB_CD PWR

15

GPU PWR & GND

16

GPU Decoupling

17

IFPAB DVI-D-DL

18

IFPE DP

19

IFPF DP

20

21

IFPC HDMI

22

IFPD DP

MIOA/B Interface and Frame Lock

23

24

MISC1: Fan, Thermal, JTAG, GPIO,STEREO

MISC2: ROM, XTAL,STRAPS

25

Page

Description

26

PS: 1V8_PLL, 1V8_AON

27

PS: 5V, PEX_VDD

28

PS: NV3V3, NV12V

29

PS: FBVDD

30

PS: NVVDD Controller

31

PS: NVVDD Phase 1,2 & 3

32

PS: NVVDD Rail Balance Login & Dynamic Phase

33

PS: Input, Filtering, and Monitoring

PS: 12V Power Steering,PSI Control & LED

34

35

PS: Shut Down and Sequencing

36

PS: GC6 MISC

37

MECH_SN EEPRON

1

2

3

4

5

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

A B D F H

ASSEMBLY

PAGE DETAIL

<ASSEMBLY_DESCRIPTION>

Table of Contents

5

Galaxy Microsystems (HK) Ltd.

Galaxy Microsystems (HK) Ltd.

Page Name:

Page Name:

Page Name:

Size Project Name: Rev

Size Project Name: Rev

Size Project Name: Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

PROPERTY NOTE: This document contains information confidential and

PROPERTY NOTE: This document contains information confidential and

PROPERTY NOTE: This document contains information confidential and

property to Galaxy Microsystems (HK) Ltd.

property to Galaxy Microsystems (HK) Ltd.

property to Galaxy Microsystems (HK) Ltd.

EC

G

Galaxy Microsystems (HK) Ltd.

Table of Contents

Table of Contents

Table of Contents

Design By:

Design By:

P65U

P65U

P65U

Design By:

Neston V10

Neston V10

Neston V10

of

of

of

137Friday, January 13, 2017

137Friday, January 13, 2017

137Friday, January 13, 2017

A B C D E F G H

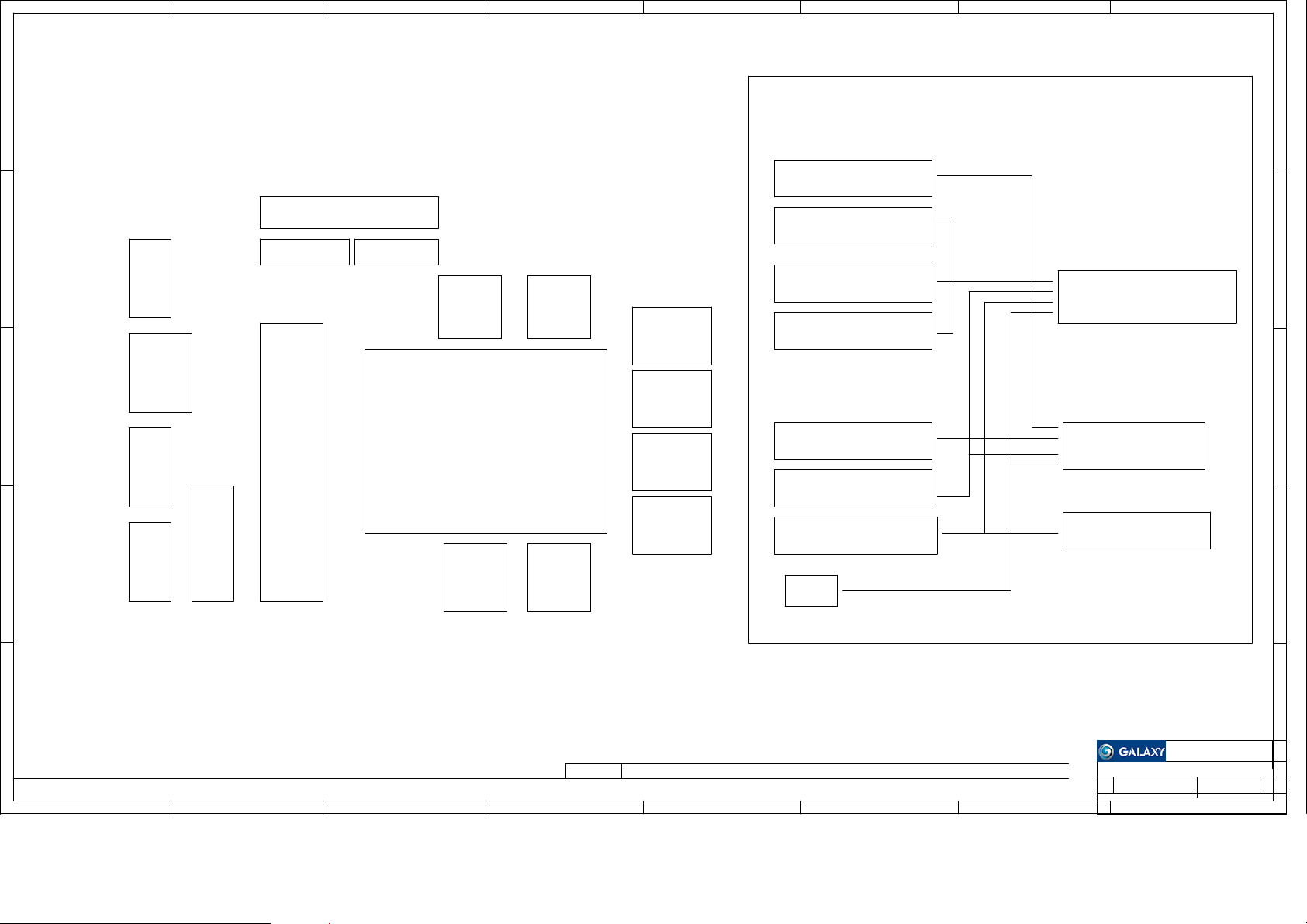

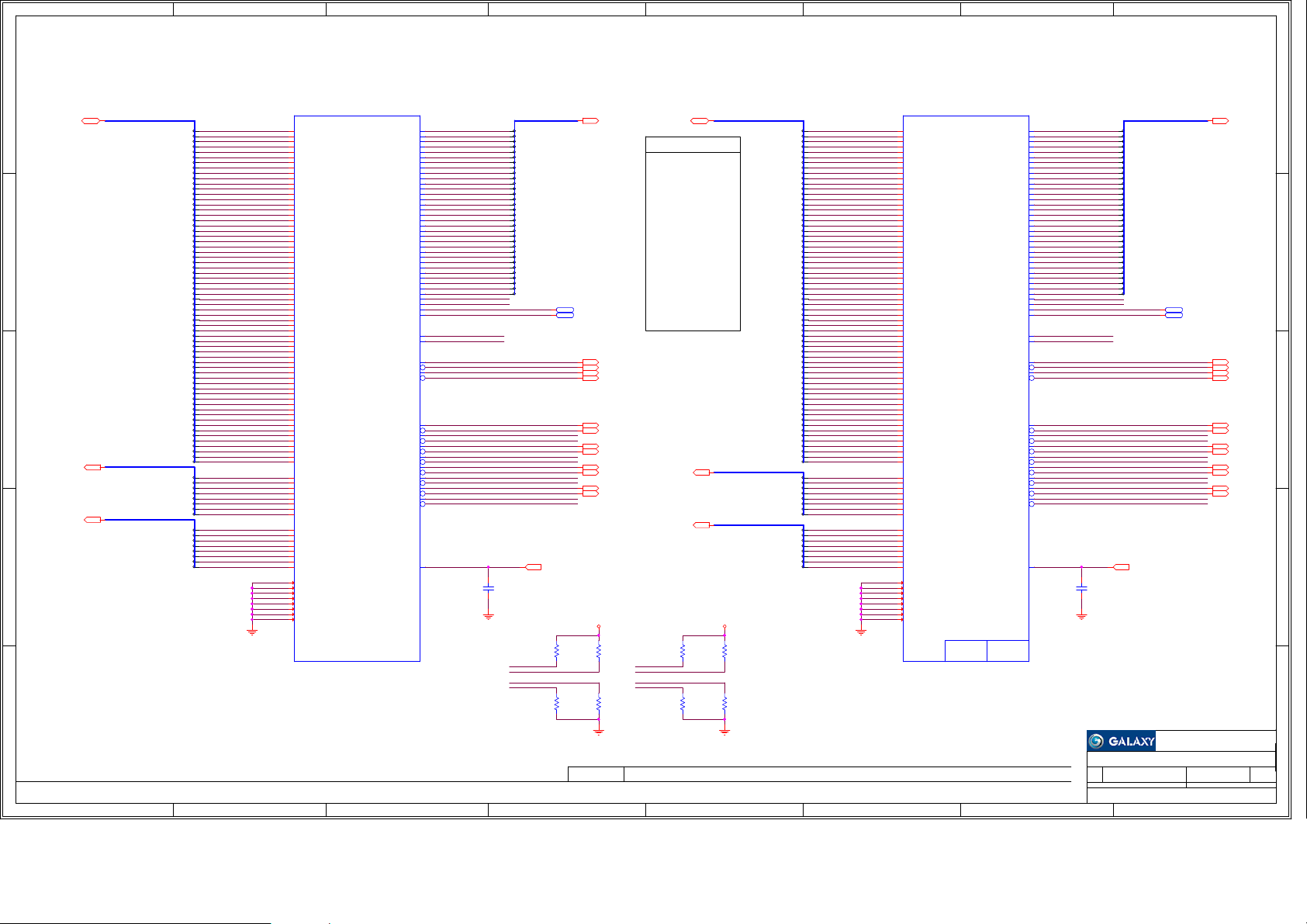

Page2: Block Diagram

1

1

Power Supply:

Power Supply

NVVDD-PH3_BAL

3-WAY SLI

2

FRAME LOCK

2-WAY SLI

DP

MEM DMEM

D

LO

HI

MEM

C

LO

QD:DP

HDMI/

3

MEM

C

HI

POWER SUPPLY

GP104/GP106

MEM

DPDP

MEM

4

DVI-I

MEM A AMEM

HI

LO

B

LO

B

HI

Power Supply

NVVDD-PH3

Power Supply

NVVDD-PH2

Power Supply

NVVDD-PH1

Power Supply

FBVDD/Q-PH1

Power Supply

5V Linear

PEX_VDD

Open_Vreg option

Fan

2

EXT_12V 2x3PWR 1

3

PEX_12V Finger

3V3 Finger

4

5

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

C E

ASSEMBLY

PAGE DETAIL

<ASSEMBLY_DESCRIPTION>

Block Biagram

5

Galaxy Microsystems (HK) Ltd.

Galaxy Microsystems (HK) Ltd.

Page Name:

Page Name:

Page Name:

Size Project Name: Rev

Size Project Name: Rev

Size Project Name: Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

PROPERTY NOTE: This document contains information confidential and

PROPERTY NOTE: This document contains information confidential and

FDBA

G

PROPERTY NOTE: This document contains information confidential and

property to Galaxy Microsystems (HK) Ltd.

property to Galaxy Microsystems (HK) Ltd.

property to Galaxy Microsystems (HK) Ltd.

Galaxy Microsystems (HK) Ltd.

Block Biagram

Block Biagram

Block Biagram

Design By:

Design By:

P65U

P65U

P65U

Design By:

H

Neston V10

Neston V10

Neston V10

237Friday, January 13, 2017

237Friday, January 13, 2017

237Friday, January 13, 2017

of

of

of

A B C D E F G H

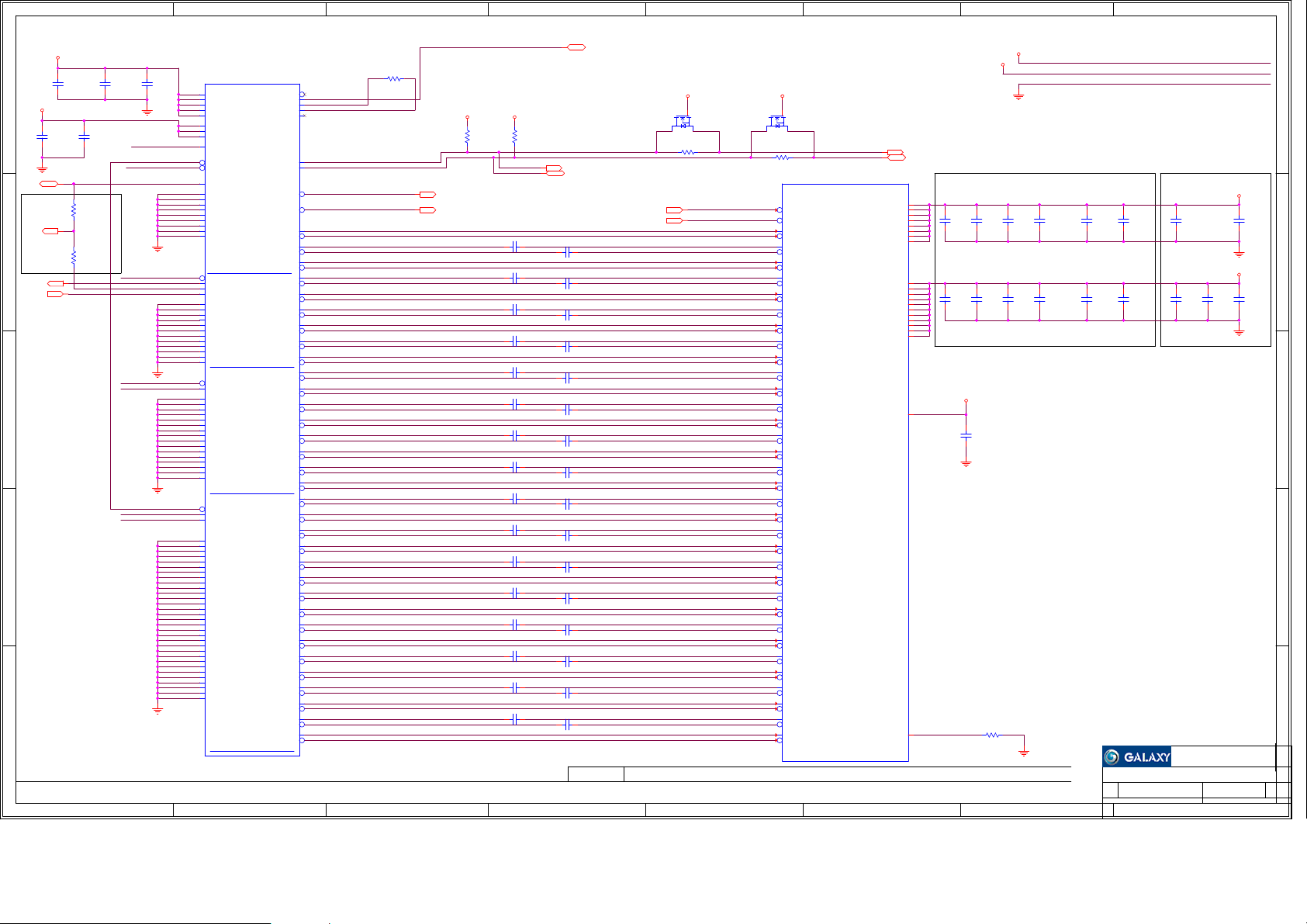

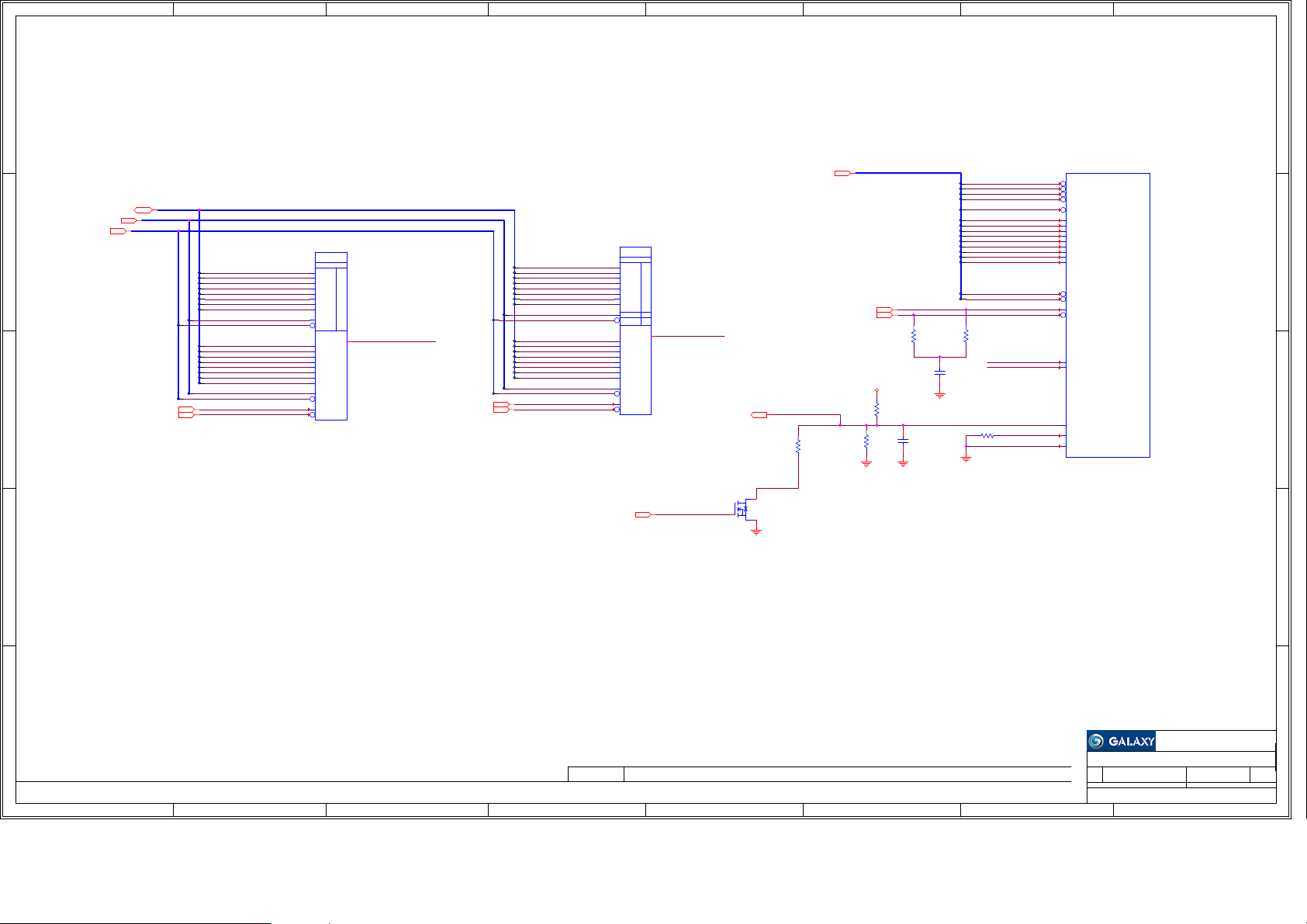

Page3: PCI Express

12V

C978

C979

10uF

16V

20%

3V3

GND

BI

STUFF FOR

TESLA ONLY

OUT

UNSTUFF FOR

DT/QUADRO

C88

4.7uF

6.3V

20%

X5R

0603

COMMON

OUT

IN

X6S

0805LP

COMMON

R892

0ohm/NC

0.05 ohm

0402

DNI

POWER_BRAKE*

R894

0ohm/NC

0.05 ohm

0402

DNI

C970

0.1uF

16V

10%

X7R

0402

COMMON

1

2

4.7uF

16V

10%

X5R

0603

COMMON

SNN_3V3AUX

SNN_PE_PRSNT2_A

PEX_CONN_B12

SNN_PE_PRSNT2_B

GPU_EVENT_CONN_R

RSVD4_POWER_BRAKE

GC6_FB_EN_CONN_A32

SNN_PE_PRSNT2_C

SNN_PE_RSVD6

C980

0.1uF

16V

10%

X7R

0402

COMMON

GND

GND

GND

3

GND

PEX_PRSNT*

SNN_PE_RSVD7

SNN_PE_RSVD8

4

5

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

GND

CN1

CON_X16

COMMON

@electro_mechanic.con_pci_express(sym_1):page3_i662

B1

+12V

B2

+12V

A2

+12V

A3

+12V

B3

+12V/RSVD

B8

+3V3

A9

+3V3

A10

+3V3

B10

+3V3AUX

A1

PRSNT1

B17

PRSNT2

B12

RSVD

B4

GND

A4

GND

B7

GND

A12

GND

B13

GND

A15

GND

B16

GND

B18

GND

A18

GND

B31

PRSNT2

A19

RSVD

B30

RSVD

A32

RSVD

A20

GND

B21

GND

B22

GND

A23

GND

A24

GND

B25

GND

B26

GND

A27

GND

A28

GND

B29

GND

A31

GND

B32

GND

B48

PRSNT2

A33

RSVD

A34

GND

B35

GND

B36

GND

A37

GND

A38

GND

B39

GND

B40

GND

A41

GND

A42

GND

B43

GND

B44

GND

A45

GND

A46

GND

B47

GND

B49

GND

A49

GND

B81

PRSNT2

A50

RSVD

B82

RSVD

A51

GND

B52

GND

B53

GND

A54

GND

A55

GND

B56

GND

B57

GND

A58

GND

A59

GND

B60

GND

B61

GND

A62

GND

A63

GND

B64

GND

B65

GND

A66

GND

A67

GND

B68

GND

B69

GND

A70

GND

A71

GND

B72

GND

B73

GND

A74

GND

A75

GND

B76

GND

B77

GND

A78

GND

A79

GND

B80

GND

A82

GND

PCIE_16X

END OF X1

END OF X4

END OF X8

END OF X16

TRST* JTAG1

TCLK JTAG2

TDI JTAG3

TDO JTAG4

TMS JTAG5

SMCLK

SMDAT

PERST

REFCLK

REFCLK

PERP0

PERN0

PETP0

PETN0

PERP1

PERN1

PETP1

PETN1

PERP2

PERN2

PETP2

PETN2

PERP3

PERN3

PETP3

PETN3

PERP4

PERN4

PETP4

PETN4

PERP5

PERN5

PETP5

PETN5

PERP6

PERN6

PETP6

PETN6

PERP7

PERN7

PETP7

PETN7

PERP8

PERN8

PETP8

PETN8

PERP9

PERN9

PETP9

PETN9

PERP10

PERN10

PETP10

PETN10

PERP11

PERN11

PETP11

PETN11

PERP12

PERN12

PETP12

PETN12

PERP13

PERN13

PETP13

PETN13

PERP14

PERN14

PETP14

PETN14

PERP15

PERN15

PETP15

PETN15

WAKE

R767

0ohm

0402

COMMON

B9

A5

A6

PEX_TDO

A7

A8

PEX_SMCLK

B5

PEX_SMDAT

B6

PEX_WAKE*

B11

PEX_RST* PEX_RST_BUF*

A11

PEX_REFCLK

A13

PEX_REFCLK*

A14

PEX_TXX0

A16

PEX_TXX0*

A17

PEX_RX0

B14

PEX_RX0*

B15

PEX_TXX1

A21

PEX_TXX1*

A22

PEX_RX1

B19

PEX_RX1*

B20

PEX_TXX2

A25

PEX_TXX2*

A26

PEX_RX2

B23

PEX_RX2*

B24

PEX_TXX3

A29

PEX_TXX3*

A30

PEX_RX3

B27

PEX_RX3*

B28

PEX_TXX4

A35

PEX_TXX4*

A36

PEX_RX4

B33

PEX_RX4*

B34

PEX_TXX5

A39

PEX_TXX5*

A40

PEX_RX5

B37

PEX_RX5*

B38

PEX_TXX6

A43

PEX_TXX6*

A44

PEX_RX6

B41

PEX_RX6*

B42

PEX_TXX7

A47

PEX_TXX7*

A48

PEX_RX7

B45

PEX_RX7*

B46

PEX_TXX8

A52

PEX_TXX8*

A53

PEX_RX8

B50

PEX_RX8*

B51

PEX_TXX9

A56

PEX_TXX9*

A57

PEX_RX9

B54

PEX_RX9*

B55

PEX_TXX10

A60

PEX_TXX10*

A61

PEX_RX10

B58

PEX_RX10*

B59

PEX_TXX11

A64

PEX_TXX11*

A65

PEX_RX11

B62

PEX_RX11*

B63

PEX_TXX12

A68

PEX_TXX12*

A69

PEX_RX12

B66

PEX_RX12*

B67

PEX_TXX13

A72

PEX_TXX13*

A73

PEX_RX13

B70

PEX_RX13*

B71

PEX_TXX14

A76

PEX_TXX14*

A77

PEX_RX14

B74

PEX_RX14*

B75

PEX_TXX15

A80

PEX_TXX15*

A81

PEX_RX15

B78

PEX_RX15*

B79

0.05 ohm

PEX_REFCLK

PEX_REFCLK

PEX_RX0

PEX_RX0

PEX_RX1

PEX_RX1

PEX_RX2

PEX_RX2

PEX_RX3

PEX_RX3

PEX_RX4

PEX_RX4

PEX_RX5

PEX_RX5

PEX_RX6

PEX_RX6

PEX_RX7

PEX_RX7

PEX_RX8

PEX_RX8

PEX_RX9

PEX_RX9

PEX_RX10

PEX_RX10

PEX_RX11

PEX_RX11

PEX_RX12

PEX_RX12

PEX_RX13

PEX_RX13

PEX_RX14

PEX_RX14

PEX_RX15

PEX_RX15

OUT

OUT

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

3V3 3V3

R754

47k

5 %

0402

COMMON

C E

PEX_TCLK

R755

47k

5 %

0402

COMMON

OUT

BI

{36}

{36}

C946 0.22uF

X5R

C944 0.22uF

X5R

C942

X5R

C939

X5R

C937

X5R

C935

X5R

C932

X5R

C922

X5R

C919

X5R

C900

X5R

C913

X5R

C902

C898 0.22uF

C895

C891 0.22uF

C887

C0402

C0402

C0402

C0402

C0402

C0402

C0402

C0402

C0402

C0402

C0402

C0402

C0402

C0402

C0402

C0402

6.3V 10%

6.3V 10%

0.22uF

6.3V

0.22uF

6.3V 10%

0.22uF

6.3V 10%

0.22uF

6.3V

0.22uF

0.22uF

6.3V 10%

0.22uF

6.3V

0.22uF

0.22uF

6.3V

X5R

6.3V

X5R

0.22uF

6.3V

X5R

6.3V

X5R

0.22uF

6.3V

X5R

0.22uF

C945

0.22uF

6.3V

X5R

C0402

C943

0.22uF

6.3V 10%

X5R

C0402

C940

0.22uF

10%

6.3V

X5R

C0402

C938 0.22uF

6.3V 10%

X5R

C0402

C936 0.22uF

6.3V

X5R

C0402

C934

0.22uF

10%

6.3V 10%

X5R

C0402

C923 0.22uF

10%6.3V

X5R

C0402

C921

0.22uF

10%6.3V

6.3V

X5R

C0402

C918 0.22uF

X5R

C0402

C896

0.22uF

10%

6.3V

X5R

C0402

C912 0.22uF

10%6.3V

6.3V 10%

X5R

C0402

C901

0.22uF

10%

6.3V

X5R

C0402

C897

0.22uF

6.3V

10%

X5R

C0402

C892 0.22uF

10%

6.3V 10%

X5R

C0402

C888

0.22uF

6.3V 10%

10%

X5R

C0402

C886 0.22uF

10%

X5R

C0402

BI

10%

10%

10%

10%6.3V

10%

10%6.3V

10%

10%

10%

10%6.3V

ASSEMBLY

PAGE DETAIL

{36}

{36}

PEX_TX0

PEX_TX0*

PEX_TX1

PEX_TX1*

PEX_TX2

PEX_TX2*

PEX_TX3

PEX_TX3*

PEX_TX4

PEX_TX4*

PEX_TX5

PEX_TX5*

PEX_TX6

PEX_TX6*

PEX_TX7

PEX_TX7*

PEX_TX8

PEX_TX8*

PEX_TX9

PEX_TX9*

PEX_TX10

PEX_TX10*

PEX_TX11

PEX_TX11*

PEX_TX12

PEX_TX12*

PEX_TX13

PEX_TX13*

PEX_TX14

PEX_TX14*

PEX_TX15

PEX_TX15*

{36}

D

3

Q_FET_N_ENH/NC

R756

IN

IN

<ASSEMBLY_DESCRIPTION>

PCI Express

3.3V

NV3V3

5

G

Q524B

@discrete.q_fet_n_enh(sym_7):page3_i968

SOT363

COMMON

S

4

0ohm/NC

DNI0402

0.05 ohm

GPU_PEX_CLKREQ*

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

D

6

Q_FET_N_ENH/NC

R758

0402

BK26

BL26

BM26

BM27

BG26

BH26

BL27

BK27

BF26

BE26

BK29

BL29

BF27

BG27

BM29

BM30

BG29

BH29

BL30

BK30

BF29

BE29

BK32

BL32

BF30

BG30

BM32

BM33

BG32

BH32

BL33

BK33

BF32

BE32

BK35

BL35

BF33

BG33

BM35

BM36

BG35

BH35

BL36

BK36

BF35

BE35

BK38

BL38

BF36

BG36

BM38

BM39

BG38

BH38

BL39

BK39

BF38

BE38

BK41

BL41

BF39

BG39

BM41

BM42

BH41

BG41

BL42

BK42

3.3V

NV3V3

2

G

Q524A

@discrete.q_fet_n_enh(sym_7):page3_i970

SOT363

COMMON

S

1

0ohm/NC

0.05 ohm

DNI

G1A

BGA2152

COMMON

1/23 PCI_EXPRESS

PEX_RST

PEX_CLKREQ

PEX_REFCLK

PEX_REFCLK

PEX_TX0

PEX_TX0

PEX_RX0

PEX_RX0

PEX_TX1

PEX_TX1

PEX_RX1

PEX_RX1

PEX_TX2

PEX_TX2

PEX_RX2

PEX_RX2

PEX_TX3

PEX_TX3

PEX_RX3

PEX_RX3

PEX_TX4

PEX_TX4

PEX_RX4

PEX_RX4

PEX_TX5

PEX_TX5

PEX_RX5

PEX_RX5

PEX_TX6

PEX_TX6

PEX_RX6

PEX_RX6

PEX_TX7

PEX_TX7

PEX_RX7

PEX_RX7

PEX_TX8

PEX_TX8

PEX_RX8

PEX_RX8

PEX_TX9

PEX_TX9

PEX_RX9

PEX_RX9

PEX_TX10

PEX_TX10

PEX_RX10

PEX_RX10

PEX_TX11

PEX_TX11

PEX_RX11

PEX_RX11

PEX_TX12

PEX_TX12

PEX_RX12

PEX_RX12

PEX_TX13

PEX_TX13

PEX_RX13

PEX_RX13

PEX_TX14

PEX_TX14

PEX_RX14

PEX_RX14

PEX_TX15

PEX_TX15

PEX_RX15

PEX_RX15

I2CS_SCL

I2CS_SDA

OUT

BI

PEX_DVDD

PEX_DVDD

PEX_DVDD

PEX_DVDD

PEX_DVDD

PEX_DVDD

PEX_DVDD

PEX_DVDD

PEX_HVDD

PEX_HVDD

PEX_HVDD

PEX_HVDD

PEX_HVDD

PEX_HVDD

PEX_HVDD

PEX_HVDD

PEX_HVDD

PEX_HVDD

PEX_HVDD

PEX_PLL_HVDD

PEX_TERMP

FDBA

BB33

BB35

BB36

BC33

BC35

BC36

BD33

BD36

BB26

BB27

BB29

BB32

BC26

BC27

BC29

BC30

BC32

BD27

BD30

BB30

BL44

PEX_TERMP

{24}

{24}

Place under GPU

C831

1uF

6.3V

10%

X6S

0402

COMMON

C825

1uF

6.3V

10%

X6S

0402

COMMON

1V8

GND

C854

0.1uF

16V

10%

X7R

0402

COMMON

C855

1uF

6.3V

10%

X6S

0402

COMMON

C826

1uF

6.3V

10%

X6S

0402

COMMON

12V

NET

12V

3V3

3V3

GND

GND

C856

C830

1uF

1uF

6.3V

6.3V

10%

10%

X6S

X6S

0402

0402

COMMON

COMMON

C827

C773

1uF

1uF

6.3V

6.3V

10%

10%

X6S

X6S

0402

0402

COMMON

COMMON

C142

4.7uF

6.3V

20%

X6S

0603

COMMON

C815

4.7uF

6.3V

20%

X6S

0603

COMMON

VOLTAGE

12V

C910

4.7uF

6.3V

20%

X6S

0603

COMMON

C803

4.7uF

6.3V

20%

X6S

0603

COMMON

5.5A 0.406

3.0A 0.400

8.5A0V 0.400

Place between

GPU and PS

C884

10uF

6.3V

10%

X7R

0805

COMMON

C893

C841

10uF

10uF

6.3V

6.3V

10%

10%

X7R

X7R

0805

0805

COMMON

COMMON

MIN_WIDTHMAX_CURRENT

PEX_VDD

GND

1V8

GND

C890

10uF

6.3V

10%

X7R

0805

COMMON

C813

22uF

6.3V

20%

X6S

0805LP

COMMON

1

2

3

4

R659

2.49k

COMMON0402

1 %

GND

G

Page Name:

Page Name:

Page Name:

Size Project Name: Rev

Size Project Name: Rev

Size Project Name: Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

PROPERTY NOTE: This document contains information confidential and

PROPERTY NOTE: This document contains information confidential and

PROPERTY NOTE: This document contains information confidential and

property to Galaxy Microsystems (HK) Ltd.

property to Galaxy Microsystems (HK) Ltd.

property to Galaxy Microsystems (HK) Ltd.

Galaxy Microsystems (HK) Ltd.

Galaxy Microsystems (HK) Ltd.

Galaxy Microsystems (HK) Ltd.

PCI Express

PCI Express

PCI Express

Design By:

Design By:

P65U

P65U

P65U

Design By:

H

Neston V10

Neston V10

Neston V10

5

337Friday, January 13, 2017

337Friday, January 13, 2017

337Friday, January 13, 2017

A B C D E F G H

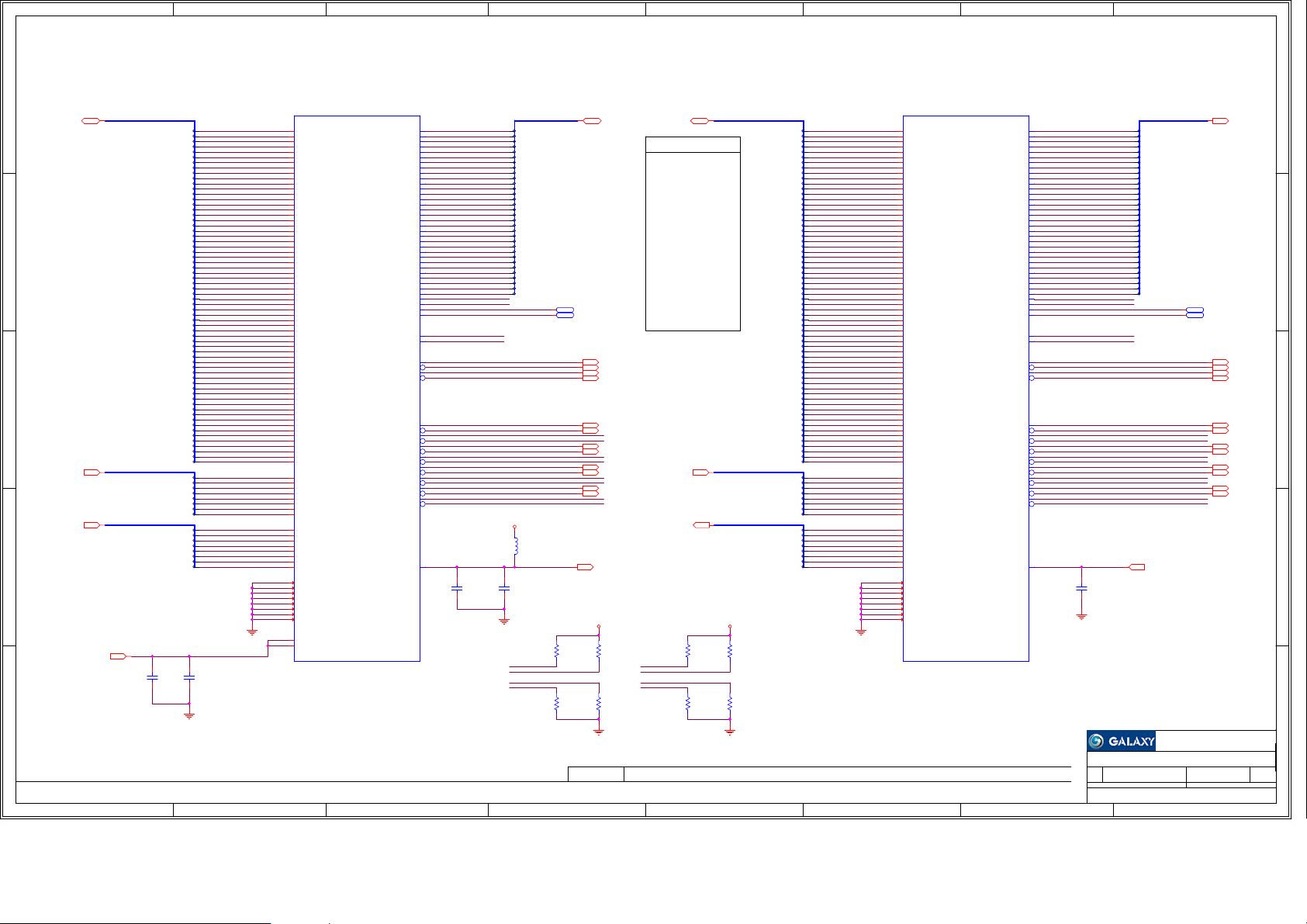

Page4: MEMORY: GPU Partition A/B

1

FB_DATA

{5,6}

2

3

{5,6}

{5,6}

4

FBA_D[63..0]

BI

FB_DBI

FBA_DBI[7..0]

IN

FB_EDC

FBA_EDC[7..0]

IN

FBA_D0

0

FBA_D1

1

FBA_D2

2

FBA_D3

3

FBA_D4

4

FBA_D5

5

FBA_D6

6

FBA_D7

7

FBA_D8

8

FBA_D9

9

FBA_D10

10

FBA_D11

11

FBA_D12

12

FBA_D13

13

FBA_D14

14

FBA_D15

15

FBA_D16

16

FBA_D17

17

FBA_D18

18

FBA_D19

19

FBA_D20

20

FBA_D21

21

FBA_D22

22

FBA_D23

23

FBA_D24

24

FBA_D25

25

FBA_D26

26

FBA_D27

27

FBA_D28

28

FBA_D29

29

FBA_D30

30

FBA_D31

31

FBA_D32

32

FBA_D33

33

FBA_D34

34

FBA_D35

35

FBA_D36

36

FBA_D37

37

FBA_D38

38

FBA_D39

39

FBA_D40

40

FBA_D41

41

FBA_D42

42

FBA_D43

43

FBA_D44

44

FBA_D45

45

FBA_D46

46

FBA_D47

47

FBA_D48

48

FBA_D49

49

FBA_D50

50

FBA_D51

51

FBA_D52

52

FBA_D53

53

FBA_D54

54

FBA_D55

55

FBA_D56

56

FBA_D57

57

FBA_D58

58

FBA_D59

59

FBA_D60

60

FBA_D61

61

FBA_D62

62

FBA_D63

63

FBA_DBI0

0

FBA_DBI1

1

FBA_DBI2

2

FBA_DBI3

3

FBA_DBI4

4

FBA_DBI5

5

FBA_DBI6

6

FBA_DBI7

7

FBA_EDC0

0

FBA_EDC1

1

FBA_EDC2

2

FBA_EDC3

3

FBA_EDC4

4

FBA_EDC5

5

FBA_EDC6

6

FBA_EDC7

7

GND

{4,10}

5

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

1V8_FB_PLL

IN

C775

0.1uF

16V

10%

X7R

0402

COMMON

C649

0.1uF

16V

10%

X7R

0402

COMMON

GND

AG48

AG49

AD47

AD49

AD48

AC46

AC47

AA47

AA46

AA45

AW51

BA52

AW50

BA51

BA50

BB50

BA49

AW49

AV48

AV51

AV52

AV49

AK49

AM47

AM46

AN48

AN49

AM44

AM45

AN45

AN46

AR48

AN47

AR47

AR46

AG47

AC48

BB51

AV50

AM48

U51

U48

U50

U49

R51

R50

R47

U46

V46

Y45

Y47

Y46

V50

V47

U52

V51

AJ44

AJ45

AF46

AF47

AF48

Y44

AT49

AT47

AT48

AT46

AJ48

AJ46

AJ47

U47

Y48

AR49

R48

V48

AF44

AA48

BB52

AT50

AK48

AR51

W47

W49

W51

W6

W8

Y14

Y15

Y16

AF42

L29

G1B

BGA2152

COMMON

2/23 FBA

FBA_D0

FBA_D1

FBA_D2

FBA_D3

FBA_D4

FBA_D5

FBA_D6

FBA_D7

FBA_D8

FBA_D9

FBA_D10

FBA_D11

FBA_D12

FBA_D13

FBA_D14

FBA_D15

FBA_D16

FBA_D17

FBA_D18

FBA_D19

FBA_D20

FBA_D21

FBA_D22

FBA_D23

FBA_D24

FBA_D25

FBA_D26

FBA_D27

FBA_D28

FBA_D29

FBA_D30

FBA_D31

FBA_D32

FBA_D33

FBA_D34

FBA_D35

FBA_D36

FBA_D37

FBA_D38

FBA_D39

FBA_D40

FBA_D41

FBA_D42

FBA_D43

FBA_D44

FBA_D45

FBA_D46

FBA_D47

FBA_D48

FBA_D49

FBA_D50

FBA_D51

FBA_D52

FBA_D53

FBA_D54

FBA_D55

FBA_D56

FBA_D57

FBA_D58

FBA_D59

FBA_D60

FBA_D61

FBA_D62

FBA_D63

FBA_DQM0

FBA_DQM1

FBA_DQM2

FBA_DQM3

FBA_DQM4

FBA_DQM5

FBA_DQM6

FBA_DQM7

FBA_DQS_WP0

FBA_DQS_WP1

FBA_DQS_WP2

FBA_DQS_WP3

FBA_DQS_WP4

FBA_DQS_WP5

FBA_DQS_WP6

FBA_DQS_WP7

GND

GND

GND

GND

GND

GND

GND

GND

FB_REFPLL_AVDD0

FB_REFPLL_AVDD1

FB_CMD

FBA_CMD0

FBA_CMD1

FBA_CMD2

FBA_CMD3

FBA_CMD4

FBA_CMD5

FBA_CMD6

FBA_CMD7

FBA_CMD8

FBA_CMD9

FBA_CMD10

FBA_CMD11

FBA_CMD12

FBA_CMD13

FBA_CMD14

FBA_CMD15

FBA_CMD16

FBA_CMD17

FBA_CMD18

FBA_CMD19

FBA_CMD20

FBA_CMD21

FBA_CMD22

FBA_CMD23

FBA_CMD24

FBA_CMD25

FBA_CMD26

FBA_CMD27

FBA_CMD28

FBA_CMD29

FBA_CMD30

FBA_CMD31

FBA_CMD32

FBA_CMD33

FBA_CMD34

FBA_CMD35

FBA_DBG_RFU1

FBA_DBG_RFU2

FBA_CLK0

FBA_CLK0

FBA_CLK1

FBA_CLK1

FBA_WCK01

FBA_WCK01

FBA_WCKB01

FBA_WCKB01

FBA_WCK23

FBA_WCK23

FBA_WCKB23

FBA_WCKB23

FBA_WCK45

FBA_WCK45

FBA_WCKB45

FBA_WCKB45

FBA_WCK67

FBA_WCK67

FBA_WCKB67

FBA_WCKB67

Y51

Y52

Y49

AA52

AA51

AA50

AC50

AC51

AC52

AC49

AD52

AD51

AD50

AF50

AF51

AF52

AN50

AN51

AN52

AM49

AM52

AM51

AM50

AK50

AK51

AK52

AJ49

AJ52

AJ51

AJ50

AG50

AG51

AG52

AF49

Y50

AR50

AA44

AN44

AG45

AG46

AK46

AK45

U45

U44

V45

V44

AC45

AC44

AD46

AD45

AV47

AV46

AW48

AW47

AR45

AR44

AT45

AT44

FBA_CMD0

FBA_CMD1

FBA_CMD2

FBA_CMD3

FBA_CMD4

FBA_CMD5

FBA_CMD6

FBA_CMD7

FBA_CMD8

FBA_CMD9

FBA_CMD10

FBA_CMD11

FBA_CMD12

FBA_CMD13

FBA_CMD14

FBA_CMD15

FBA_CMD16

FBA_CMD17

FBA_CMD18

FBA_CMD19

FBA_CMD20

FBA_CMD21

FBA_CMD22

FBA_CMD23

FBA_CMD24

FBA_CMD25

FBA_CMD26

FBA_CMD27

FBA_CMD28

FBA_CMD29

FBA_CMD30

FBA_CMD31

SNN_FBA_CMD<32>

SNN_FBA_CMD<33>

FBA_DEBUG0

FBA_DEBUG1

SNN_FBA_DBG_RFU1

SNN_FBA_DBG_RFU2

FBA_CLK0

FBA_CLK0*

FBA_CLK1

FBA_CLK1*

FBA_WCK01

FBA_WCK01*

SNN_FBA_WCKB01

SNN_FBA_WCKB01*

FBA_WCK23

FBA_WCK23*

SNN_FBA_WCKB23

SNN_FBA_WCKB23*

FBA_WCK45

FBA_WCK45*

SNN_FBA_WCKB45

SNN_FBA_WCKB45*

FBA_WCK67

FBA_WCK67*

SNN_FBA_WCKB67

SNN_FBA_WCKB67*

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

50OHM_NETCLASS1

50OHM_NETCLASS1

FBA_CMD[31..0]

FB_CLK

FB_CLK

FB_CLK

FB_CLK

FB_WCK

FB_WCK

FB_WCK

FB_WCK

FB_WCK

FB_WCK

FB_WCK

FB_WCK

FB_WCK

FB_WCK

FB_WCK

FB_WCK

FB_WCK

FB_WCK

FB_WCK

FB_WCK

1V8

LB502

30ohm

COMMON

BEAD_0603

FBA_PLL_AVDD

AN42

C645

0.1uF

16V

10%

X7R

0402

COMMON

1V8_FB_PLL 1V8_FB_PLL

C903

22uF

6.3V

20%

X6S

0805LP

COMMON

GND

R602

10k

5 %

0402

FBA_CMD1

FBA_CMD17

FBA_CMD2

FBA_CMD18

COMMON

R644

10k

5 %

0402

COMMON

C E

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

ASSEMBLY

PAGE DETAIL

BI

FBVDD

GND

R645

10k

5 %

0402

COMMON

R601

10k

5 %

0402

COMMON

{7,8}

{5,6}

GDDR5 CMD Mapping

CMD 0..31

CMD0

CMD1

CMD2

CMD3

CMD4

CMD5

CMD6

CMD7

CMD8

CMD9

CMD10

CMD11

CMD12

CMD13

CMD14

CMD15

CMD16

CMD17

CMD18

CMD19

CMD20

CMD21

CMD22

CMD23

CMD24

CMD25

CMD26

CMD27

CMD28

CMD29

CMD30

CMD31

{5}

{5}

{6}

{6}

{5}

{5}

{5}

{5}

{6}

{6}

{7,8}

{6}

{6}

{7,8}

{4,10}

FBB_CMD1

FBB_CMD17

FBB_CMD2

FBB_CMD18

<ASSEMBLY_DESCRIPTION>

GPU FB_AB

CAS*

CKE*

RST*

RAS*

A1_A9

A0_A10

A12_RFU

ABI*

A6_A11

A7_A8

WE*

A5_BA1

A4_BA2

A2_BA0

A3_BA3

CS*

BI

IN

OUT

R568

10k

5 %

0402

COMMON

R581

10k

5 %

0402

COMMON

32..63

CAS*

CKE*

RST*

RAS*

A1_A9

A0_A10

A12_RFU

ABI*

A6_A11

A7_A8

WE*

A5_BA1

A4_BA2

A2_BA0

A3_BA3

CS*

FB_DATA

FBB_D[63..0]

FB_DBI

FBB_DBI[7..0]

FB_EDC

FBB_EDC[7..0]

FBVDD

R570

10k

5 %

0402

COMMON

R580

10k

5 %

0402

COMMON

GND

G1C

BGA2152

COMMON

FBB_D0

0

FBB_D1

1

FBB_D2

2

FBB_D3

3

FBB_D4

4

FBB_D5

5

FBB_D6

6

FBB_D7

7

FBB_D8

8

FBB_D9

9

FBB_D10

10

FBB_D11

11

FBB_D12

12

FBB_D13

13

FBB_D14

14

FBB_D15

15

FBB_D16

16

FBB_D17

17

FBB_D18

18

FBB_D19

19

FBB_D20

20

FBB_D21

21

FBB_D22

22

FBB_D23

23

FBB_D24

24

FBB_D25

25

FBB_D26

26

FBB_D27

27

FBB_D28

28

FBB_D29

29

FBB_D30

30

FBB_D31

31

FBB_D32

32

FBB_D33

33

FBB_D34

34

FBB_D35

35

FBB_D36

36

FBB_D37

37

FBB_D38

38

FBB_D39

39

FBB_D40

40

FBB_D41

41

FBB_D42

42

FBB_D43

43

FBB_D44

44

FBB_D45

45

FBB_D46

46

FBB_D47

47

FBB_D48

48

FBB_D49

49

FBB_D50

50

FBB_D51

51

FBB_D52

52

FBB_D53

53

FBB_D54

54

FBB_D55

55

FBB_D56

56

FBB_D57

57

FBB_D58

58

FBB_D59

59

FBB_D60

60

FBB_D61

61

FBB_D62

62

FBB_D63

63

FBB_DBI0

0

FBB_DBI1

1

FBB_DBI2

2

FBB_DBI3

3

FBB_DBI4

4

FBB_DBI5

5

FBB_DBI6

6

FBB_DBI7

7

FBB_EDC0

0

FBB_EDC1

1

FBB_EDC2

2

FBB_EDC3

3

FBB_EDC4

4

FBB_EDC5

5

FBB_EDC6

6

FBB_EDC7

7

H32

D32

A33

B32

E32

G32

J30

F32

H36

G36

J36

F36

F33

D33

J32

G33

E45

D45

F45

G45

D42

E42

F42

H41

E41

F39

E39

D39

F38

E38

D36

E36

M50

P48

M51

M49

P47

P52

R46

P46

L50

L51

L52

L49

M46

L47

M48

M47

D48

C50

C48

C49

E49

E50

F49

F48

F50

D52

J50

H48

H51

J51

H49

H52

C32

E33

E44

G39

P49

L48

D50

H50

B33

E35

G44

H38

P50

J48

D51

F51

Y17

Y18

Y19

Y20

Y21

Y22

Y23

Y24

3/23 FBB

FBB_D0

FBB_D1

FBB_D2

FBB_D3

FBB_D4

FBB_D5

FBB_D6

FBB_D7

FBB_D8

FBB_D9

FBB_D10

FBB_D11

FBB_D12

FBB_D13

FBB_D14

FBB_D15

FBB_D16

FBB_D17

FBB_D18

FBB_D19

FBB_D20

FBB_D21

FBB_D22

FBB_D23

FBB_D24

FBB_D25

FBB_D26

FBB_D27

FBB_D28

FBB_D29

FBB_D30

FBB_D31

FBB_D32

FBB_D33

FBB_D34

FBB_D35

FBB_D36

FBB_D37

FBB_D38

FBB_D39

FBB_D40

FBB_D41

FBB_D42

FBB_D43

FBB_D44

FBB_D45

FBB_D46

FBB_D47

FBB_D48

FBB_D49

FBB_D50

FBB_D51

FBB_D52

FBB_D53

FBB_D54

FBB_D55

FBB_D56

FBB_D57

FBB_D58

FBB_D59

FBB_D60

FBB_D61

FBB_D62

FBB_D63

FBB_DQM0

FBB_DQM1

FBB_DQM2

FBB_DQM3

FBB_DQM4

FBB_DQM5

FBB_DQM6

FBB_DQM7

FBB_DQS_WP0

FBB_DQS_WP1

FBB_DQS_WP2

FBB_DQS_WP3

FBB_DQS_WP4

FBB_DQS_WP5

FBB_DQS_WP6

FBB_DQS_WP7

GND

GND

GND

GND

GND

GND

GND

GND

FBB_CMD0

FBB_CMD1

FBB_CMD2

FBB_CMD3

FBB_CMD4

FBB_CMD5

FBB_CMD6

FBB_CMD7

FBB_CMD8

FBB_CMD9

FBB_CMD10

FBB_CMD11

FBB_CMD12

FBB_CMD13

FBB_CMD14

FBB_CMD15

FBB_CMD16

FBB_CMD17

FBB_CMD18

FBB_CMD19

FBB_CMD20

FBB_CMD21

FBB_CMD22

FBB_CMD23

FBB_CMD24

FBB_CMD25

FBB_CMD26

FBB_CMD27

FBB_CMD28

FBB_CMD29

FBB_CMD30

FBB_CMD31

FBB_CMD32

FBB_CMD33

FBB_CMD34

FBB_CMD35

FBB_DBG_RFU1

FBB_DBG_RFU2

FBB_CLK0

FBB_CLK0

FBB_CLK1

FBB_CLK1

FBB_WCK01

FBB_WCK01

FBB_WCKB01

FBB_WCKB01

FBB_WCK23

FBB_WCK23

FBB_WCKB23

FBB_WCKB23

FBB_WCK45

FBB_WCK45

FBB_WCKB45

FBB_WCKB45

FBB_WCK67

FBB_WCK67

FBB_WCKB67

FBB_WCKB67

FBB_PLL_AVDD

B35

A35

D35

A36

B36

C36

C38

B38

A38

D38

A39

B39

C39

C41

B41

A41

B49

A49

A48

D47

A47

B47

C47

C45

B45

A45

D44

A44

B44

C44

C42

B42

A42

D41

C35

B50

J35

J41

H42

G42

F47

E47

J33

H33

G35

H35

J39

H39

F41

G41

L46

L45

M44

M45

H47

H46

J47

J46

L38

FBB_CMD0

FBB_CMD1

FBB_CMD2

FBB_CMD3

FBB_CMD4

FBB_CMD5

FBB_CMD6

FBB_CMD7

FBB_CMD8

FBB_CMD9

FBB_CMD10

FBB_CMD11

FBB_CMD12

FBB_CMD13

FBB_CMD14

FBB_CMD15

FBB_CMD16

FBB_CMD17

FBB_CMD18

FBB_CMD19

FBB_CMD20

FBB_CMD21

FBB_CMD22

FBB_CMD23

FBB_CMD24

FBB_CMD25

FBB_CMD26

FBB_CMD27

FBB_CMD28

FBB_CMD29

FBB_CMD30

FBB_CMD31

SNN_FBB_CMD<32>

SNN_FBB_CMD<33>

FBB_DEBUG0

FBB_DEBUG1

SNN_FBB_DBG_RFU1

SNN_FBB_DBG_RFU2

FBB_CLK0

FBB_CLK0*

FBB_CLK1

FBB_CLK1*

FBB_WCK01

FBB_WCK01*

SNN_FBB_WCKB01

SNN_FBB_WCKB01*

FBB_WCK23

FBB_WCK23*

SNN_FBB_WCKB23

SNN_FBB_WCKB23*

FBB_WCK45

FBB_WCK45*

SNN_FBB_WCKB45

SNN_FBB_WCKB45*

FBB_WCK67

FBB_WCK67*

SNN_FBB_WCKB67

SNN_FBB_WCKB67*

GND

C652

0.1uF

16V

10%

X7R

0402

COMMON

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

50OHM_NETCLASS1

50OHM_NETCLASS1

IN

FB_CMD

FBB_CMD[31..0]

FB_CLK

FB_CLK

FB_CLK

FB_CLK

FB_WCK

FB_WCK

FB_WCK

FB_WCK

FB_WCK

FB_WCK

FB_WCK

FB_WCK

FB_WCK

FB_WCK

FB_WCK

FB_WCK

FB_WCK

FB_WCK

FB_WCK

FB_WCK

OUT

TP501TP508

TP504TP510

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

{4,10}

1

{7,8}

2

{7}

{7}

{8}

{8}

3

{7}

{7}

{7}

{7}

{8}

{8}

{8}

{8}

4

GND

5

Galaxy Microsystems (HK) Ltd.

Galaxy Microsystems (HK) Ltd.

Page Name:

Page Name:

Page Name:

Size Project Name: Rev

Size Project Name: Rev

Size Project Name: Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

PROPERTY NOTE: This document contains information confidential and

PROPERTY NOTE: This document contains information confidential and

PROPERTY NOTE: This document contains information confidential and

property to Galaxy Microsystems (HK) Ltd.

property to Galaxy Microsystems (HK) Ltd.

FDBA

G

property to Galaxy Microsystems (HK) Ltd.

Galaxy Microsystems (HK) Ltd.

GPU FB_AB

GPU FB_AB

GPU FB_AB

Design By:

Design By:

P65U

P65U

P65U

Design By:

Neston V10

Neston V10

Neston V10

H

of

of

of

437Friday, January 13, 2017

437Friday, January 13, 2017

437Friday, January 13, 2017

A B C D E F G H

Page5: FRAME BUFFER PARTITION A [31:0]

1

FBA_D[31..0]

BI

{4,6}

{4,6}

FBA_EDC[7..0]

IN

FBA_DBI[7..0]

IN

{4}

2

FBA_D0

0

FBA_D1

1

FBA_D2

2

FBA_D3

3

FBA_D4

4

FBA_D5

5

FBA_D6

6

FBA_D7

7

FBA_EDC0

0

FBA_DBI0

0

FBA_D8

8

FBA_D9

9

FBA_D10

10

FBA_D11

11

FBA_D12

12

FBA_D13

13

FBA_D14

14

FBA_D15

15

FBA_EDC1

1

FBA_DBI1

1

3

{4}

{4}

FBA_WCK01

IN

FBA_WCK01*

IN

4

FB_DATA

FB_EDC

FB_EDC

M3D

@memory.u_mem_sd_ddr5_x32(sym_2):page5_i297

BGA170_MIRR

COMMON

MIRRORED

x16x32

V4

DQ0

NC

V2

DQ1

NC

T4

DQ2

NC

T2

DQ3

NC

N4

DQ4

NC

N2

DQ5

NC

M4

DQ6

NC

M2

DQ7

NC

R2

EDC0

NC

P2

DBI0

NC

VREFD

V11

DQ8

V13

DQ9

T11

DQ10

T13

DQ11

N11

DQ12

N13

DQ13

M11

DQ14

M13

DQ15

R13

EDC1

P13

DBI1

P4

WCK01

P5

WCK01

M3A

@memory.u_mem_sd_ddr5_x32(sym_4):page5_i337

BGA170_MIRR

COMMON

MIRRORED

FBA_D16

16

FBA_D17

17

FBA_D18

18

FBA_D19

19

FBA_D20

20

FBA_D21

21

FBA_D22

22

FBA_D23

23

FBA_EDC2

2

FBA_DBI2

SNN_FBA_VREFD_M3_0 SNN_FBA_VREFD_M3_1

V10

{4}

{4}

2

FBA_D24

24

FBA_D25

25

FBA_D26

26

FBA_D27

27

FBA_D28

28

FBA_D29

29

FBA_D30

30

FBA_D31

31

FBA_EDC3

3

FBA_DBI3

3

FBA_WCK23

IN

FBA_WCK23*

IN

{7,11,24}

x32 x16

A11

DQ16

NC

A13

DQ17

NC

B11

DQ18

NC

B13

DQ19

NC

E11

DQ20

NC

E13

DQ21

NC

F11

DQ22

NC

F13

DQ23

NC

C13

EDC2

GND

D13

DBI2

NC

A10

VREFD

A4

DQ24

A2

DQ25

B4

DQ26

B2

DQ27

E4

DQ28

E2

DQ29

F4

DQ30

F2

DQ31

C2

EDC3

D2

DBI3

D4

WCK23

D5

WCK23

GPIO10_FBVREF_SEL

IN

3

D

Q26

@discrete.q_fet_n_enh(sym_2):page5_i135

SOT23_1G1D1S

G

1

COMMON

S

2

1G1D1S

0.300

FBA_VREFC_Q

50V

0.22A

3500mohm@10V / 3500mohm@4.5V / 3500mohm@2.5V

0.22A

0.35W

20V

R120

931ohm

1 %

0402

COMMON

FB_CMD

FBA_CMD[31..0]

R121

1.33k

1 %

0402

COMMON

{4,6}

FBA_CLK0

IN

FBA_CLK0*

IN

R613

40.2ohm

1 %

0402

COMMON

FBA_CLK0_RC

FBVDD

R122

549ohm

1 %

GND

0402

COMMON

COMMON

0.300

C156

820pF

50V

10%

X7R

0402

GND

C756

10nF

16V

10%

X7R

0402

COMMON

GND

FBA_CMD3

3

FBA_CMD0

0

FBA_CMD10

10

FBA_CMD15

15

FBA_CMD7

7

FBA_CMD5

5

FBA_CMD4

4

FBA_CMD13

13

FBA_CMD14

14

FBA_CMD12

12

FBA_CMD11

11

FBA_CMD8

8

FBA_CMD9

9

FBA_CMD6

6

FBA_CMD2

2

FBA_CMD1

1

R612

40.2ohm

1 %

0402

COMMON

FBA_VREFC

R614 121ohm

0402

1 %

COMMON

SNN_FBA_RFU1_M1

SNN_FBA_RFU2_M1

OUT

FBA_ZQ0

IN

{4}

{4}

GND

M3B

@memory.u_mem_sd_ddr5_x32(sym_5):page5_i342

BGA170_MIRR

COMMON

L3

RAS

G3

CAS

G12

WE

L12

CS

J4

ABI

K4

A0_A10

K5

A1_A9

K11

A2_BA0

K10

A3_BA3

H11

A4_BA2

H10

A5_BA1

H5

A6_A11

H4

A7_A8

J5

RFU_A12

J2

RESET

J3

CKE

J12

CLK

J11

CLK

A5

NC_RFU_A5

V5

NC_RFU_V5

{6}

J14

VREFC

J13

ZQ

J10

SEN

1

2

3

4

GND

5

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

C E

ASSEMBLY

PAGE DETAIL

<ASSEMBLY_DESCRIPTION>

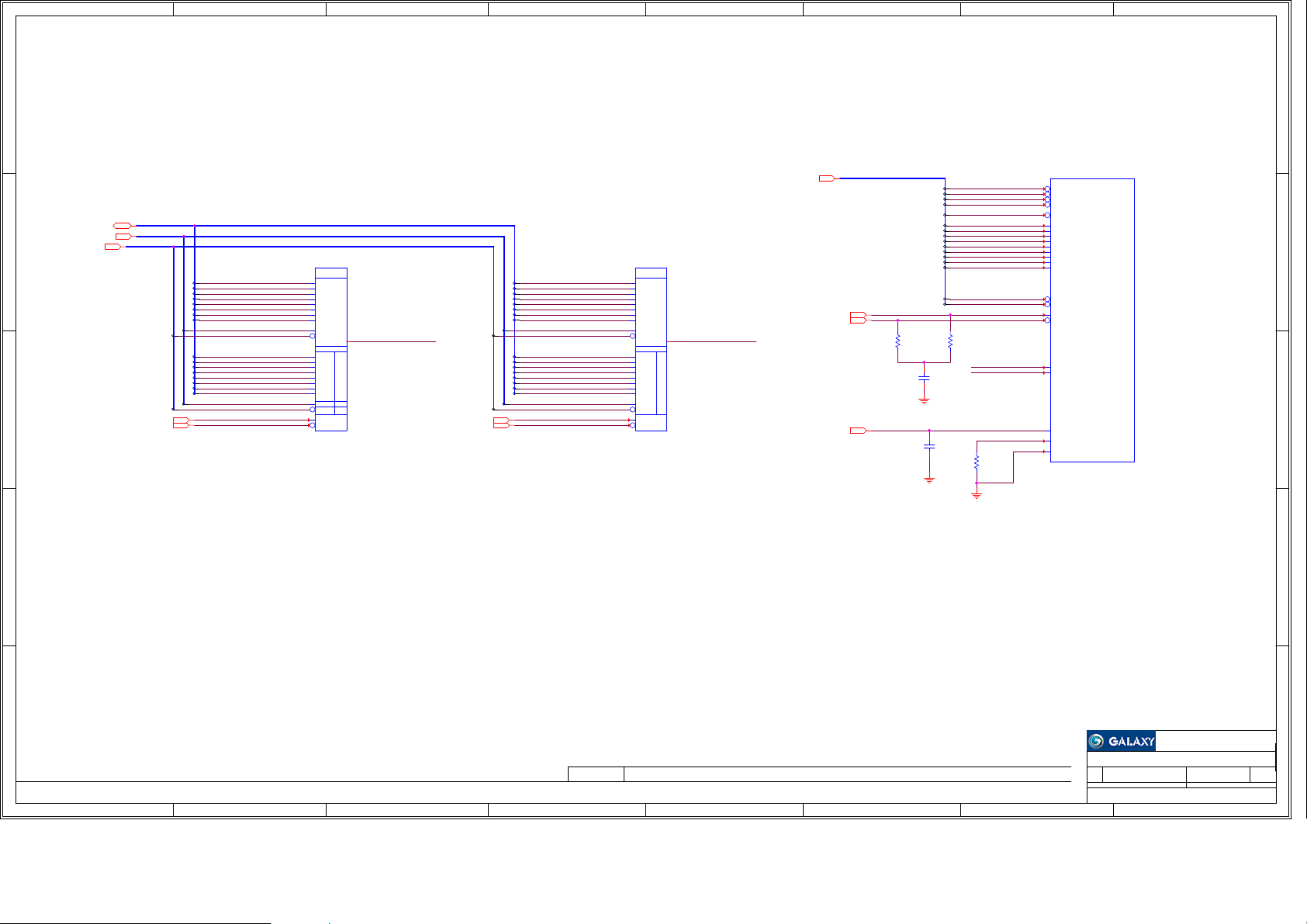

MEMORY: FBA[31:0]

5

Galaxy Microsystems (HK) Ltd.

Galaxy Microsystems (HK) Ltd.

Page Name:

Page Name:

Page Name:

Size Project Name: Rev

Size Project Name: Rev

Size Project Name: Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

PROPERTY NOTE: This document contains information confidential and

PROPERTY NOTE: This document contains information confidential and

PROPERTY NOTE: This document contains information confidential and

property to Galaxy Microsystems (HK) Ltd.

property to Galaxy Microsystems (HK) Ltd.

FDBA

G

property to Galaxy Microsystems (HK) Ltd.

Galaxy Microsystems (HK) Ltd.

MEMORY: FBA[31:0]

MEMORY: FBA[31:0]

MEMORY: FBA[31:0]

Design By:

Design By:

P65U

P65U

P65U

Design By:

Neston V10

Neston V10

Neston V10

H

of

of

of

537Friday, January 13, 2017

537Friday, January 13, 2017

537Friday, January 13, 2017

A B C D E F G H

Page6: FRAME BUFFER PARTITION A [63:32]

1

M1B

@memory.u_mem_sd_ddr5_x32(sym_5):page6_i154

FBA_CMD[31..0]

FBA_D[63..32]

BI

{4,5}

{4,5}

FBA_EDC[7..0]

IN

FBA_DBI[7..0]

IN

{4}

2

32

33

34

35

36

37

38

39

4

4

40

41

42

43

44

45

46

47

5

3

{4}

{4}

5

IN

IN

FBA_D32

FBA_D33

FBA_D34

FBA_D35

FBA_D36

FBA_D37

FBA_D38

FBA_D39

FBA_EDC4

FBA_DBI4

FBA_D40

FBA_D41

FBA_D42

FBA_D43

FBA_D44

FBA_D45

FBA_D46

FBA_D47

FBA_EDC5

FBA_DBI5

FBA_WCK45

FBA_WCK45*

FB_DATA

FB_EDC

FB_DBI

M1D

@memory.u_mem_sd_ddr5_x32(sym_1):page6_i152

BGA170

COMMON

NORMAL

A4

DQ0

A2

DQ1

B4

DQ2

B2

DQ3

E4

DQ4

E2

DQ5

F4

DQ6

F2

DQ7

C2

EDC0

D2

DBI0

VREFD

x16

x32

A11

DQ8

NC

A13

DQ9

NC

B11

DQ10

NC

B13

DQ11

NC

E11

DQ12

NC

E13

DQ13

NC

F11

DQ14

NC

F13

DQ15

NC

C13

EDC1

GND

D13

DBI1

NC

D4

WCK01

D5

WCK01

M1A

@memory.u_mem_sd_ddr5_x32(sym_3):page6_i153

BGA170

COMMON

FBA_D48

48

FBA_D49

49

FBA_D50

50

FBA_D51

51

FBA_D52

52

FBA_D53

53

FBA_D54

54

FBA_D55

55

FBA_EDC6

6

FBA_DBI6

SNN_FBA_VREFD_M1_0 SNN_FBA_VREFD_M1_1

A10

{4}

{4}

6

FBA_D56

56

FBA_D57

57

FBA_D58

58

FBA_D59

59

FBA_D60

60

FBA_D61

61

FBA_D62

62

FBA_D63

63

FBA_EDC7

7

FBA_DBI7

7

FBA_WCK67

IN

FBA_WCK67*

IN

NORMAL

V11

DQ16

V13

DQ17

T11

DQ18

T13

DQ19

N11

DQ20

N13

DQ21

M11

DQ22

M13

DQ23

R13

EDC2

P13

DBI2

V10

VREFD

x16

x32

V4

DQ24

NC

V2

DQ25

NC

T4

DQ26

NC

T2

DQ27

NC

N4

DQ28

NC

N2

DQ29

NC

M4

DQ30

NC

M2

DQ31

NC

R2

EDC3

NC

P2

DBI3

NC

P4

WCK23

P5

WCK23

IN

{4}

{4}

{5}

FB_CMD

{4,5}

FBA_CLK1

IN

FBA_CLK1*

IN

R619

40.2ohm

1 %

0402

COMMON

FBA_CLK1_RC

GND

FBA_VREFC

IN

C147

820pF

50V

10%

X7R

0402

COMMON

GND

C777

10nF

16V

10%

X7R

0402

COMMON

19

16

26

31

23

21

20

29

30

28

27

24

25

22

18

17

R618

40.2ohm

1 %

0402

COMMON

FBA_CMD19

FBA_CMD16

FBA_CMD26

FBA_CMD31

FBA_CMD23

FBA_CMD21

FBA_CMD20

FBA_CMD29

FBA_CMD30

FBA_CMD28

FBA_CMD27

FBA_CMD24

FBA_CMD25

FBA_CMD22

FBA_CMD18

FBA_CMD17

SNN_FBA_RFU1_M3

SNN_FBA_RFU2_M3

FBA_ZQ2

R620

121ohm

1 %

0402

COMMON

GND GND

BGA170

COMMON

G3

RAS

L3

CAS

L12

WE

G12

CS

J4

ABI

H4

A0_A10

H5

A1_A9

H11

A2_BA0

H10

A3_BA3

K11

A4_BA2

K10

A5_BA1

K5

A6_A11

K4

A7_A8

J5

RFU_A12

J2

RESET

J3

CKE

J12

CLK

J11

CLK

A5

NC_RFU_A5

V5

NC_RFU_V5

0.300

J14

VREFC

J13

ZQ

J10

SEN

1

2

3

4

5

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

C E

ASSEMBLY

PAGE DETAIL

<ASSEMBLY_DESCRIPTION>

MEMORY: FBA[63:32]

4

5

Galaxy Microsystems (HK) Ltd.

Galaxy Microsystems (HK) Ltd.

Page Name:

Page Name:

Page Name:

Size Project Name: Rev

Size Project Name: Rev

Size Project Name: Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

PROPERTY NOTE: This document contains information confidential and

PROPERTY NOTE: This document contains information confidential and

PROPERTY NOTE: This document contains information confidential and

property to Galaxy Microsystems (HK) Ltd.

property to Galaxy Microsystems (HK) Ltd.

FDBA

G

property to Galaxy Microsystems (HK) Ltd.

Galaxy Microsystems (HK) Ltd.

MEMORY: FBA[63:32]

MEMORY: FBA[63:32]

MEMORY: FBA[63:32]

Design By:

Design By:

P65U

P65U

P65U

Design By:

Neston V10

Neston V10

Neston V10

H

of

of

of

637Friday, January 13, 2017

637Friday, January 13, 2017

637Friday, January 13, 2017

A B C D E F G H

Page7: FRAME BUFFER PARTITION B [31:0]

1

M7B

@memory.u_mem_sd_ddr5_x32(sym_5):page7_i1383

FBB_ZQ0

BGA170_MIRR

COMMON

L3

RAS

G3

CAS

G12

WE

L12

CS

J4

ABI

K4

A0_A10

K5

A1_A9

K11

A2_BA0

K10

A3_BA3

H11

A4_BA2

H10

A5_BA1

H5

A6_A11

H4

A7_A8

J5

RFU_A12

J2

RESET

J3

CKE

J12

CLK

J11

CLK

A5

NC_RFU_A5

V5

NC_RFU_V5

J14

VREFC

J13

ZQ

J10

SEN

FBB_CMD[31..0]

FBB_D[31..0]

BI

{4,8}

{4,8}

FBB_EDC[7..0]

IN

FBB_DBI[7..0]

IN

2

0

{4}

3

{4}

1

IN

IN

4

FB_DATA

{4}

FB_EDC

FB_DBI

0

FBB_D0

1

FBB_D1

2

FBB_D2

3

FBB_D3

4

FBB_D4

5

FBB_D5

6

FBB_D6

7

FBB_D7

FBB_EDC0

0

FBB_DBI0

FBB_D8

8

FBB_D9

9

FBB_D10

10

FBB_D11

11

FBB_D12

12

FBB_D13

13

FBB_D14

14

FBB_D15

15

FBB_EDC1

1

FBB_DBI1

FBB_WCK01

FBB_WCK01*

M7D

@memory.u_mem_sd_ddr5_x32(sym_2):page7_i1321

BGA170_MIRR

COMMON

MIRRORED

x16x32

V4

DQ0

NC

V2

DQ1

NC

T4

DQ2

NC

T2

DQ3

NC

N4

DQ4

NC

N2

DQ5

NC

M4

DQ6

NC

M2

DQ7

NC

R2

EDC0

NC

P2

DBI0

NC

VREFD

V11

DQ8

V13

DQ9

T11

DQ10

T13

DQ11

N11

DQ12

N13

DQ13

M11

DQ14

M13

DQ15

R13

EDC1

P13

DBI1

P4

WCK01

P5

WCK01

M7A

@memory.u_mem_sd_ddr5_x32(sym_4):page7_i1378

BGA170_MIRR

COMMON

MIRRORED

FBB_D16

16

FBB_D17

17

FBB_D18

18

FBB_D19

19

FBB_D20

20

FBB_D21

21

FBB_D22

22

FBB_D23

23

FBB_EDC2

2

FBB_DBI2

SNN_FBB_VREFD_M7_0 SNN_FBB_VREFD_M7_1

V10

{4}

{4}

2

FBB_D24

24

FBB_D25

25

FBB_D26

26

FBB_D27

27

FBB_D28

28

FBB_D29

29

FBB_D30

30

FBB_D31

31

FBB_EDC3

3

FBB_DBI3

3

FBB_WCK23

IN

FBB_WCK23*

IN

{5,11,24}

A11

A13

B11

B13

E11

E13

F11

F13

C13

D13

A4

A2

B4

B2

E4

E2

F4

F2

C2

D2

D4

D5

IN

x32 x16

DQ16

NC

DQ17

NC

DQ18

NC

DQ19

NC

DQ20

NC

DQ21

NC

DQ22

NC

DQ23

NC

EDC2

GND

DBI2

NC

VREFD

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

EDC3

DBI3

WCK23

WCK23

GPIO10_FBVREF_SEL

A10

3

D

Q33

@discrete.q_fet_n_enh(sym_2):page7_i1237

SOT23_1G1D1S

G

1

COMMON

S

2

1G1D1S

FBB_VREFC_Q

FBB_VREFC

OUT

R135

931ohm

1 %

0402

COMMON

0.300

50V

0.22A

3500mohm@10V / 3500mohm@4.5V / 3500mohm@2.5V

0.22A

0.35W

20V

GND

IN

{4}

{4}

{8}

IN

IN

FBVDD

R136

549ohm

1 %

0402

COMMON

C195

820pF

R134

1.33k

50V

10%

1 %

X7R

0402

0402

COMMON

COMMON

GND

GND

{4,8}

FBB_CLK0

FBB_CLK0*

FB_CMD

R587

40.2ohm

1 %

0402

COMMON

FBB_CLK0_RC

FBB_CMD3

3

FBB_CMD0

0

FBB_CMD10

10

FBB_CMD15

15

FBB_CMD7

7

FBB_CMD5

5

FBB_CMD4

4

FBB_CMD13

13

FBB_CMD14

14

FBB_CMD12

12

FBB_CMD11

11

FBB_CMD8

8

FBB_CMD9

9

FBB_CMD6

6

FBB_CMD2

2

FBB_CMD1

1

R591

40.2ohm

1 %

0402

COMMON

C563

10nF

16V

10%

X7R

0402

COMMON

GND

0.300

SNN_FBB_RFU1_M1

SNN_FBB_RFU2_M1

R569

121ohm

COMMON

0402

1 %

GND

1

2

3

4

5

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

C E

ASSEMBLY

PAGE DETAIL

<ASSEMBLY_DESCRIPTION>

MEMORY: FBB[31:0]

5

Galaxy Microsystems (HK) Ltd.

Galaxy Microsystems (HK) Ltd.

Page Name:

Page Name:

Page Name:

Size Project Name: Rev

Size Project Name: Rev

Size Project Name: Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

PROPERTY NOTE: This document contains information confidential and

PROPERTY NOTE: This document contains information confidential and

PROPERTY NOTE: This document contains information confidential and

property to Galaxy Microsystems (HK) Ltd.

property to Galaxy Microsystems (HK) Ltd.

FDBA

G

property to Galaxy Microsystems (HK) Ltd.

Galaxy Microsystems (HK) Ltd.

MEMORY: FBB[31:0]

MEMORY: FBB[31:0]

MEMORY: FBB[31:0]

Design By:

Design By:

P65U

P65U

P65U

Design By:

Neston V10

Neston V10

Neston V10

H

of

of

of

737Friday, January 13, 2017

737Friday, January 13, 2017

737Friday, January 13, 2017

A B C D E F G H

Page8: FRAME BUFFER PARTITION B [63:32]

1

M8B

@memory.u_mem_sd_ddr5_x32(sym_5):page8_i155

FBB_ZQ2

BGA170

COMMON

G3

RAS

L3

CAS

L12

WE

G12

CS

J4

ABI

H4

A0_A10

H5

A1_A9

H11

A2_BA0

H10

A3_BA3

K11

A4_BA2

K10

A5_BA1

K5

A6_A11

K4

A7_A8

J5

RFU_A12

J2

RESET

J3

CKE

J12

CLK

J11

CLK

A5

NC_RFU_A5

V5

NC_RFU_V5

J14

VREFC

J13

ZQ

J10

SEN

FBB_CMD[31..0]

FBB_D[63..32]

FBB_EDC[7..0]

{4}

{4,7}

{4,7}

BI

IN

FBB_DBI[7..0]

IN

2

FB_DATA

FB_EDC

FB_DBI

M8D

@memory.u_mem_sd_ddr5_x32(sym_1):page8_i157

BGA170

COMMON

32

FBB_D32

33

FBB_D33

34

FBB_D34

35

FBB_D35

36

FBB_D36

37

FBB_D37

38

FBB_D38

39

FBB_D39

FBB_EDC4

4

FBB_DBI4

4

FBB_D40

40

FBB_D41

41

FBB_D42

42

FBB_D43

43

FBB_D44

44

FBB_D45

45

FBB_D46

46

FBB_D47

47

FBB_EDC5

5

FBB_DBI5

5

FBB_WCK45

FBB_WCK45*

{4}

{4}

IN

IN

NORMAL

A4

DQ0

A2

DQ1

B4

DQ2

B2

DQ3

E4

DQ4

E2

DQ5

F4

DQ6

F2

DQ7

C2

EDC0

D2

DBI0

SNN_FBB_VREFD_M8_0 SNN_FBB_VREFD_M8_1

A10

VREFD

x16

x32

A11

DQ8

NC

A13

DQ9

NC

B11

DQ10

NC

B13

DQ11

NC

E11

DQ12

NC

E13

DQ13

NC

F11

DQ14

NC

F13

DQ15

NC

C13

EDC1

GND

D13

DBI1

NC

D4

WCK01

D5

WCK01

FBB_D48

48

FBB_D49

49

FBB_D50

50

FBB_D51

51

FBB_D52

52

FBB_D53

53

FBB_D54

54

FBB_D55

55

FBB_EDC6

6

FBB_DBI6

6

FBB_D56

56

FBB_D57

57

FBB_D58

58

FBB_D59

59

FBB_D60

60

FBB_D61

61

FBB_D62

62

FBB_D63

63

FBB_EDC7

7

FBB_DBI7

7

FBB_WCK67

FBB_WCK67*

{4}

{4}

IN

IN

M8A

@memory.u_mem_sd_ddr5_x32(sym_3):page8_i156

BGA170

COMMON

NORMAL

V11

DQ16

V13

DQ17

T11

DQ18

T13

DQ19

N11

DQ20

N13

DQ21

M11

DQ22

M13

DQ23

R13

EDC2

P13

DBI2

VREFD

x16

x32

V4

DQ24

NC

V2

DQ25

NC

T4

DQ26

NC

T2

DQ27

NC

N4

DQ28

NC

N2

DQ29

NC

M4

DQ30

NC

M2

DQ31

NC

R2

EDC3

NC

P2

DBI3

NC

P4

WCK23

P5

WCK23

V10

IN

{4}

{4}

3

FB_CMD

{4,7}

FBB_CLK1

IN

FBB_CLK1*

IN

R585

40.2ohm

1 %

0402

COMMON

FBB_CLK1_RC

FBB_VREFC

IN

GND

C197

820pF

50V

10%

X7R

0402

COMMON

FBB_CMD19

19

FBB_CMD16

16

FBB_CMD26

26

FBB_CMD31

31

FBB_CMD23

23

FBB_CMD21

21

FBB_CMD20

20

FBB_CMD29

29

FBB_CMD30

30

FBB_CMD28

28

FBB_CMD27

27

FBB_CMD24

24

FBB_CMD25

25

FBB_CMD22

22

FBB_CMD18

18

FBB_CMD17

17

R589

40.2ohm

1 %

0402

COMMON

SNN_FBB_RFU1_M3

C561

SNN_FBB_RFU2_M3

10nF

16V

10%

X7R

0402

COMMON

GND

{7}

R576

121ohm

0402

COMMON

1 %

GND

1

2

3

4

5

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

C E

ASSEMBLY

PAGE DETAIL

<ASSEMBLY_DESCRIPTION>

MEMORY: FBB[63:32]

4

5

Galaxy Microsystems (HK) Ltd.

Galaxy Microsystems (HK) Ltd.

Page Name:

Page Name:

Page Name:

Size Project Name: Rev

Size Project Name: Rev

Size Project Name: Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

PROPERTY NOTE: This document contains information confidential and

PROPERTY NOTE: This document contains information confidential and

PROPERTY NOTE: This document contains information confidential and

property to Galaxy Microsystems (HK) Ltd.

property to Galaxy Microsystems (HK) Ltd.

FDBA

G

property to Galaxy Microsystems (HK) Ltd.

Galaxy Microsystems (HK) Ltd.

MEMORY: FBB[63:32]

MEMORY: FBB[63:32]

MEMORY: FBB[63:32]

Design By:

Design By:

P65U

P65U

P65U

Design By:

Neston V10

Neston V10

Neston V10

H

of

of

of

837Friday, January 13, 2017

837Friday, January 13, 2017

837Friday, January 13, 2017

A B C D E F G H

Page9: FRAME BUFFER PARTITION A/B DECOUPLING

FBVDD

DECOUPLING AROUND FBA MEMORIES (DQ0-DQ31)

C154

C153

C157

C177

1

C155

1uF

1uF

1uF

6.3V

6.3V

10%

10%

X6S

X6S

0402

0402

COMMON

COMMON

0402

0402

C168

C729

22uF

22uF

4V

4V

20%

20%

X6S

X6S

0603W

0603W

COMMON

COMMON

0603

0603

1uF

6.3V

6.3V

10%

10%

X6S

X6S

0402

0402

COMMON

COMMON

0402

0402

C703

C659

22uF

22uF

4V

4V

20%

20%

X6S

X6S

0603W

0603W

COMMON

COMMON

0603

0603

FBVDD

2

3

SOE*/MF_VDD

J1

C10

VDD

C5

VDD

D11

VDD

G1

VDD

G11

VDD

G14

VDD

G4

VDD

L1

VDD

L11

VDD

L14

VDD

L4

VDD

P11

VDD

R10

VDD

R5

VDD

B1

VDDQ

B12

VDDQ

B14

VDDQ

B3

VDDQ

D1

VDDQ

D12

VDDQ

D14

VDDQ

D3

VDDQ

E10

VDDQ

E5

VDDQ

F1

VDDQ

F12

VDDQ

F14

VDDQ

F3

VDDQ

G13

VDDQ

G2

VDDQ

H12

VDDQ

H3

VDDQ

K12

VDDQ

K3

VDDQ

L13

VDDQ

L2

VDDQ

M1

VDDQ

M12

VDDQ

M14

VDDQ

M3

VDDQ

N10

VDDQ

N5

VDDQ

P1

VDDQ

P12

VDDQ

P14

VDDQ

P3

VDDQ

T1

VDDQ

T12

VDDQ

T14

VDDQ

T3

VDDQ

4

1uF

6.3V

10%

X6S

0402

COMMON

0402

0402

C631

22uF

4V

20%

X6S

0603W

COMMON

0603

GND

add 1k to VDD

BGA_0170_P080_140X120

C176

C740

1uF

6.3V

10%

X6S

0402

COMMON

@memory.u_mem_sd_ddr5_x32(sym_7):page9_i984

BGA170_MIRR

Mirrored

C705

1uF

1uF

6.3V

6.3V

10%

10%

X6S

X6S

0402

0402

COMMON

COMMON

0402

0402

FBVDD

0402

M3C

COMMON

B10

VSS

B5

VSS

D10

VSS

G10

VSS

G5

VSS

H1

VSS

H14

VSS

K1

VSS

K14

VSS

L10

VSS

L5

VSS

P10

VSS

T10

VSS

T5

VSS

A1

VSSQ

A12

VSSQ

A14

VSSQ

A3

VSSQ

C1

VSSQ

C11

VSSQ

C12

VSSQ

C14

VSSQ

C3

VSSQ

C4

VSSQ

E1

VSSQ

E12

VSSQ

E14

VSSQ

E3

VSSQ

F10

VSSQ

F5

VSSQ

H13

VSSQ

H2

VSSQ

K13

VSSQ

K2

VSSQ

M10

VSSQ

M5

VSSQ

N1

VSSQ

N12

VSSQ

N14

VSSQ

N3

VSSQ

R1

VSSQ

R11

VSSQ

R12

VSSQ

R14

VSSQ

R3

VSSQ

R4

VSSQ

V1

VSSQ

V12

VSSQ

V14

VSSQ

V3

VSSQ

GND GND

C693

1uF

6.3V

10%

X6S

0402

COMMON

C694

1uF

6.3V

10%

X6S

0402

COMMON

0402

0402

C741

1uF

6.3V

10%

X6S

0402

COMMON

0402

C664

C663

1uF

1uF

6.3V

6.3V

10%

10%

X6S

X6S

0402

0402

COMMON

COMMON

0402

M1C

@memory.u_mem_sd_ddr5_x32(sym_6):page9_i1290

BGA170

COMMON

J1

MF_VSS/SOE*

add 1k to VSS

B10

VSS

B5

VSS

D10

VSS

G10

VSS

G5

VSS

H1

VSS

H14

VSS

K1

VSS

K14

VSS

L10

VSS

L5

VSS

P10

VSS

T10

VSS

T5

VSS

A1

VSSQ

A12

VSSQ

A14

VSSQ

A3

VSSQ

C1

VSSQ

C11

VSSQ

C12

VSSQ

C14

VSSQ

C3

VSSQ

C4

VSSQ

E1

VSSQ

E12

VSSQ

E14

VSSQ

E3

VSSQ

F10

VSSQ

F5

VSSQ

H13

VSSQ

H2

VSSQ

K13

VSSQ

K2

VSSQ

M10

VSSQ

M5

VSSQ

N1

VSSQ

N12

VSSQ

N14

VSSQ

N3

VSSQ

R1

VSSQ

R11

VSSQ

R12

VSSQ

R14

VSSQ

R3

VSSQ

R4

VSSQ

V1

VSSQ

V12

VSSQ

V14

VSSQ

V3

VSSQ

BGA_0170_P080_140X120

0402

Normal

C658

1uF

6.3V

10%

X6S

0402

COMMON

C175

C178

10uF

10uF

4V

4V

20%

20%

X6S

X6S

0603

0603

COMMON

COMMON

0603

0603

C626

C629

1uF

1uF

6.3V

6.3V

10%

10%

X6S

X6S

0402

0402

COMMON

COMMON

0402

0402

FBVDD

C10

VDD

C5

VDD

D11

VDD

G1

VDD

G11

VDD

G14

VDD

G4

VDD

L1

VDD

L11

VDD

L14

VDD

L4

VDD

P11

VDD

R10

VDD

R5

VDD

B1

VDDQ

B12

VDDQ

B14

VDDQ

B3

VDDQ

D1

VDDQ

D12

VDDQ

D14

VDDQ

D3

VDDQ

E10

VDDQ

E5

VDDQ

F1

VDDQ

F12

VDDQ

F14

VDDQ

F3

VDDQ

G13

VDDQ

G2

VDDQ

H12

VDDQ

H3

VDDQ

K12

VDDQ

K3

VDDQ

L13

VDDQ

L2

VDDQ

M1

VDDQ

M12

VDDQ

M14

VDDQ

M3

VDDQ

N10

VDDQ

N5

VDDQ

P1

VDDQ

P12

VDDQ

P14

VDDQ

P3

VDDQ

T1

VDDQ