NSC LMC7221AIN, LMC7221AIMX, LMC7221AIM5X, LMC7221AIM5, LMC7221AIM Datasheet

...

LMC7221

Tiny CMOS Comparator with Rail-To-Rail Input and Open

Drain Output

General Description

The LM7221 is a micropower CMOS comparator available in

the space saving SOT23-5 package. This makes this comparator ideal for space and weight critical designs. The

LMC7221 is also available in the SO-8 package. The

LMC7221 is supplied in two offset voltage grades, 5 mV and

15 mV.

The open drain output can be pulled up with a resistor to a

voltage which can be higher or lower than the supply

voltage—this makes the part useful for mixed voltage systems.

For a tiny comparator with a push-pull output, please see the

LMC7211 datasheet.

Features

n Tiny SOT 23-5 package saves space

n Package is less than 1.43 mm thick

n Guaranteed specs at 2.7V, 5V, 15V supplies

n Typical supply current 7 µA at 5V

n Response time of 4 µs at 5V

n LMC7221— open drain output

n Input common-mode range beyond V− and V+

n Low input current

Applications

n Mixed voltage battery powered products

n Notebooks and PDAs

n PCMCIA cards

n Mobile communications

n Alarm and security circuits

n Driving low current LEDs

n Direct sensor interface

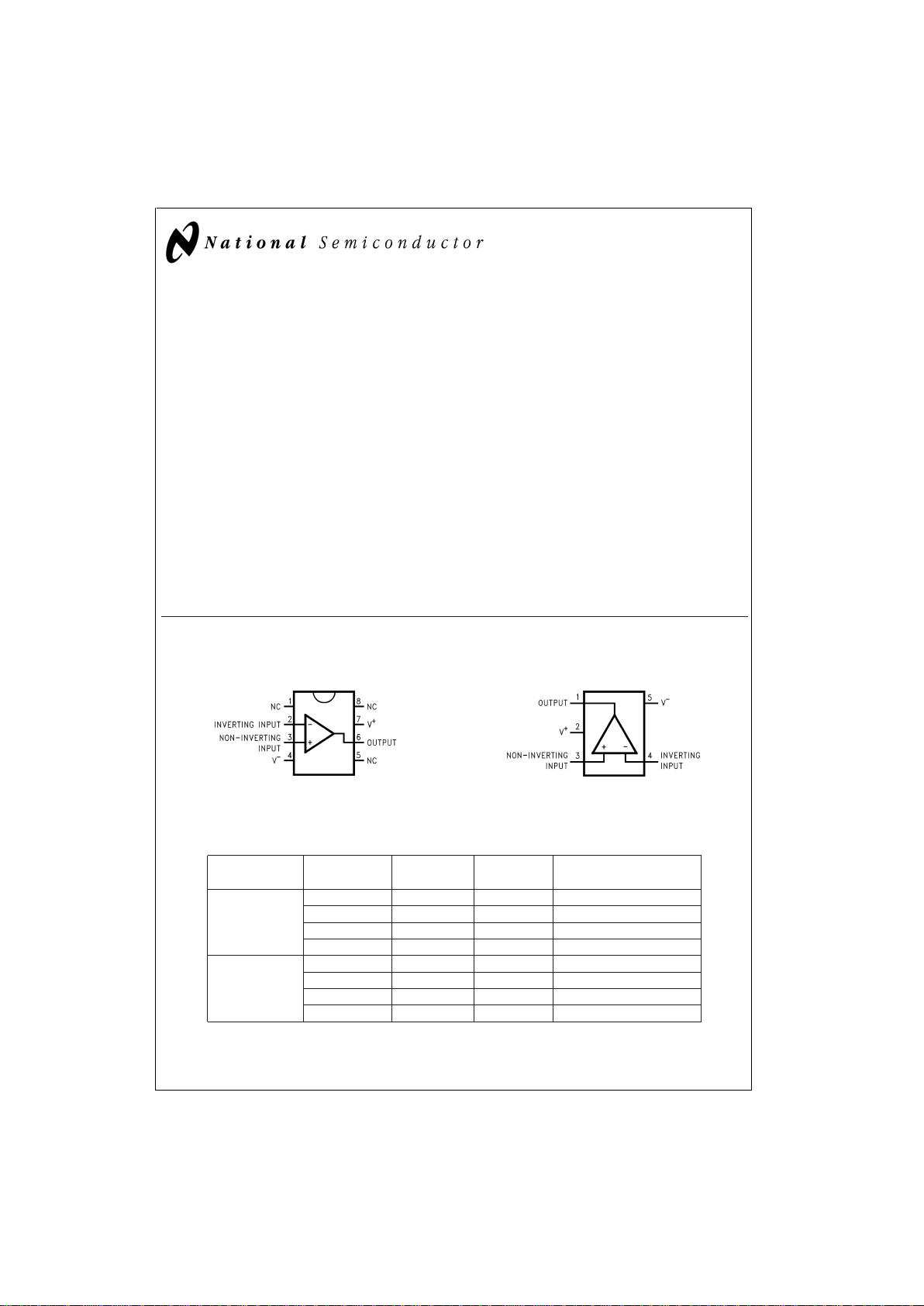

Connection Diagrams

Ordering Information

Package Ordering NSC Drawing Package Transport Media

Information Number Marking

8-Pin SO-8

LMC7221AIM M08A LMC7221AIM Rails

LMC7221AIMX M08A LMC7221AIM 2.5k Units Tape and Reel

LMC7221BIM M08A LMC7221BIM Rails

LMC7221BIMX M08A LMC7221BIM 2.5k Units Tape and Reel

5-Pin SOT 23-5

LMC7221AIM5 MA05A C01A 1k Units Tape and Reel

LMC7221AIM5X MA05A C01A 3k Units Tape and Reel

LMC7221BIM5 MA05A C01B 1k Units Tape and Reel

LMC7221BIM5X MA05A C01B 3k Units Tape and Reel

8–Pin SO-8

DS012346-1

Top View

5-Pin SOT23-5

DS012346-2

Top View

September 1999

LMC7221 Tiny CMOS Comparator with Rail-To-Rail Input and Open Drain Output

© 1999 National Semiconductor Corporation DS012346 www.national.com

Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required,

please contact the National Semiconductor Sales Office/

Distributors for availability and specifications.

ESD Tolerance (Note 2) 2 kV

Differential Input Voltage (V

CC

) +0.3V to (−VCC)−0.3V

Voltage at Input (V

CC

) + 0.3V to (−VCC)−0.3V

Voltage at Output Pin 15V

Supply Voltage (V

+–V−

) 16V

Current at Input Pin

(Note 7)

±

5mA

Current at Output Pin

(Notes 3, 8)

±

30 mA

Current at Power Supply Pin 40 mA

Lead Temperature

(soldering, 10 sec.) 260˚C

Storage Temperature Range −65˚C to +150˚C

Junction Temperature

(Note 4) 150˚C

Operating Ratings (Note 1)

Supply Voltage 2.7 ≤ V

CC

≤ 15V

Junction Temperature Range

LMC7221AI, LMC7221BI −40˚C ≤ T

J

≤ +85˚C

Thermal Resistance (θ

JA

)

SO-8 Package,

8-Pin Surface Mount 180˚C/W

M05A Package,

5-Pin Surface Mount 325˚C/W

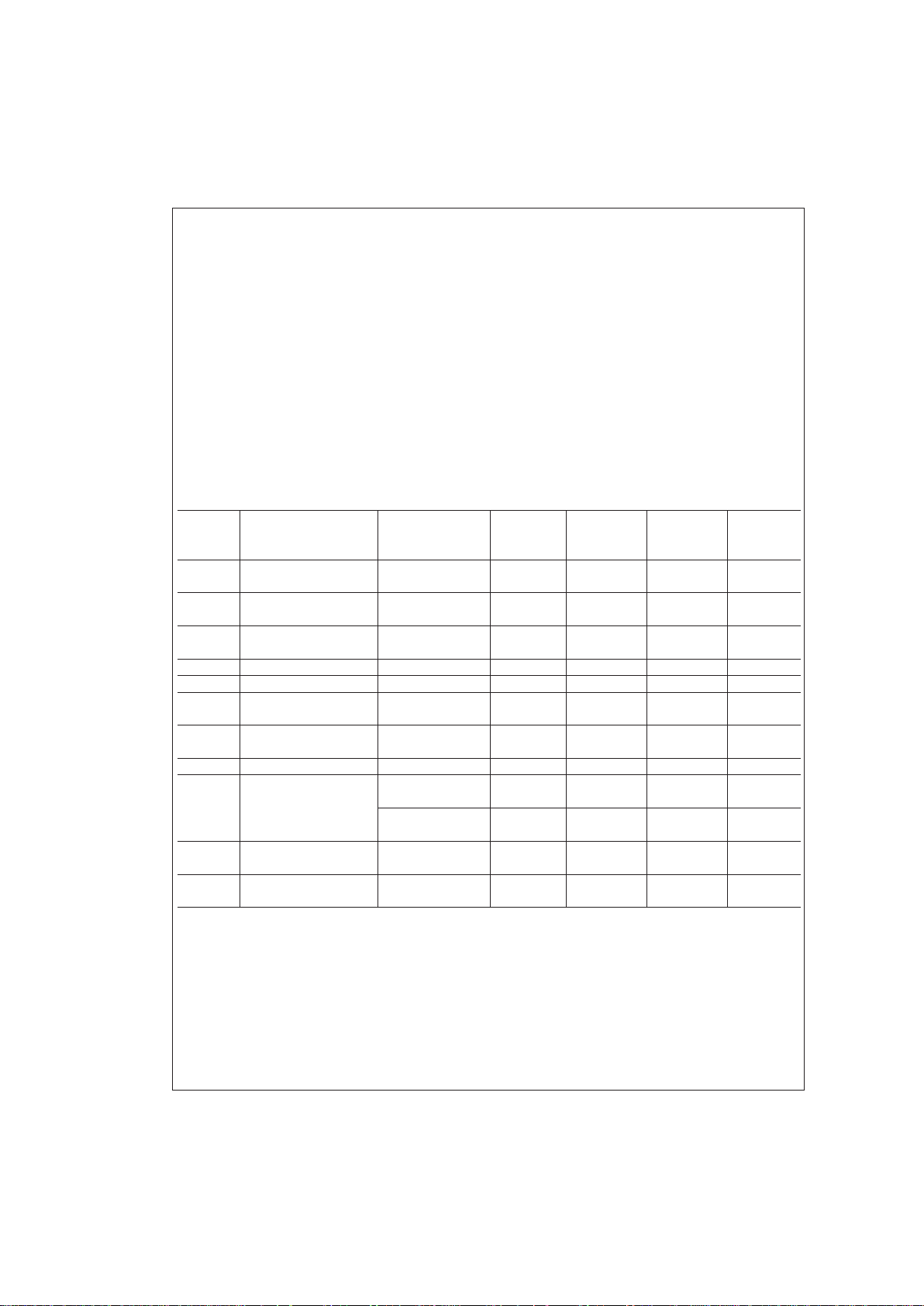

2.7V Electrical Characteristics

Unless otherwise specified, all limits guaranteed for T

J

=

25˚C, V

+

=

2.7V, V

−

=

0V, V

CM

=

V

O

=

V+/2. Boldface limits apply

at the temperature extremes

Typ LMC7221AI LMC7221BI

Symbol Parameter Conditions (Note 5) Limit Limit Units

(Note 6) (Note 6)

V

OS

Input Offset Voltage 3 5 15 mV

818max

TCV

OS

Input Offset Voltage 1.0 µV/˚C

Temperature Drift

Input Offset Voltage (Note 10) 3.3 µV/Month

Average Drift

I

B

Input Current 0.04 pA

I

OS

Input Offset Current 0.02 pA

CMRR Common Mode 0V ≤ V

CM

≤ 2.7V 75 dB

Rejection Ratio

PSRR Power Supply 2.7V ≤ V

+

≤ 15V 80 dB

Rejection Ratio

A

V

Voltage Gain 100 dB

CMVR Input Common-Mode CMRR

>

55 dB 3.0 2.9 2.9 V

Voltage Range 2.7 2.7 min

CMRR

>

55 dB −0.3 −0.2 −0.2 V

0.0 0.0 max

V

OL

Output Voltage Low I

load

=

2.5 mA 0.2 0.3 0.3 V

0.4 0.4 max

I

S

Supply Current V

OUT

=

low 7 12 12 µA

14 14 max

www.national.com 2

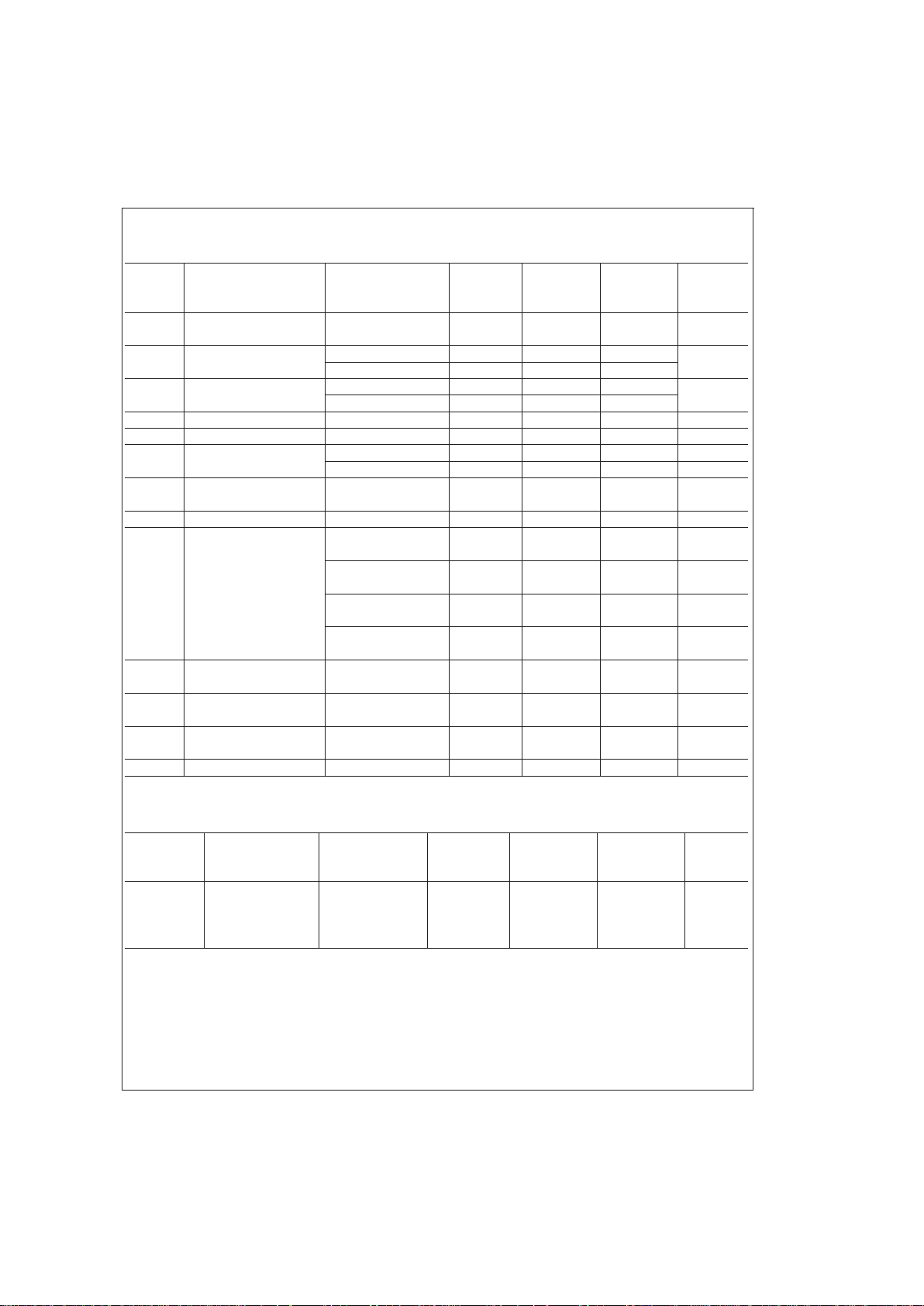

5.0V and 15.0V Electrical Characteristics

Unless otherwise specified, all limits guaranteed for T

J

=

25˚C, V

+

=

5.0V and 15V, V

−

=

0V, V

CM

=

V

O

=

V

+

/2. Boldface lim-

its apply at the temperature extremes

Typ LMC7221AI LMC7221BI

Symbol Parameter Conditions (Note 5) Limit Limit Units

(Note 6) (Note 6)

V

OS

Input Offset Voltage 3 5 15 mV

818max

TCV

OS

Input Offset Voltage V

+

=

5V 1.0 µV/˚C

Temperature Drift V

+

=

15V 4.0

Input Offset Voltage V

+

=

5V (Note 10) 3.3 µV/Month

Average Drift V

+

=

15V (Note 10) 4.0

I

B

Input Current 0.04 pA

I

OS

Input Offset Current 0.02 pA

CMRR Common Mode V+=5.0V 75 dB

Rejection Ration V+=15.0V 82 dB

PSRR Power Supply 5V ≤ V

+

≤ 10V 80 dB

Rejection Ratio

A

V

Voltage Gain 100 dB

CMVR Input Common-Mode V+=5.0V 5.3 5.2 5.2 V

Voltage Range CMRR

>

55 dB 5.0 5.0 min

V+=5.0V −0.3 −0.2 −0.2 V

CMRR

>

55 dB 0.0 0.0 max

V+=15.0V 15.3 15.2 15.2 V

CMRR

>

55 dB 15.0 15.0 min

V+=15.0V −0.3 −0.2 −0.2 V

CMRR

>

55 dB 0.0 0.0 max

V

OL

Output Voltage Low V+=5V 0.2 0.40 0.40 mV

I

load

=

5mA 0.55 0.55 max

V+=15V 0.2 0.40 0.40 mV

I

load

=

5mA 0.55 0.55 max

I

S

Supply Current V

OUT

=

Low 7 14 14 µA

18 18 max

I

SC

Short Circuit Current Sinking (Note 8) 45 mA

Leakage Characteristics

T

J

=

25˚C

Typ LMC7221AI LMC7221BI

Symbol Parameter Conditions (Note 5) Limit Limit Units

(Note 6) (Note 6)

I

LEAKAGE

Output Leakage V+=2.7V

Current V

IN

(+)=0.5V 0.1 500 500 nA

V

IN

(−)=0V

V

OUT

=

15V

www.national.com3

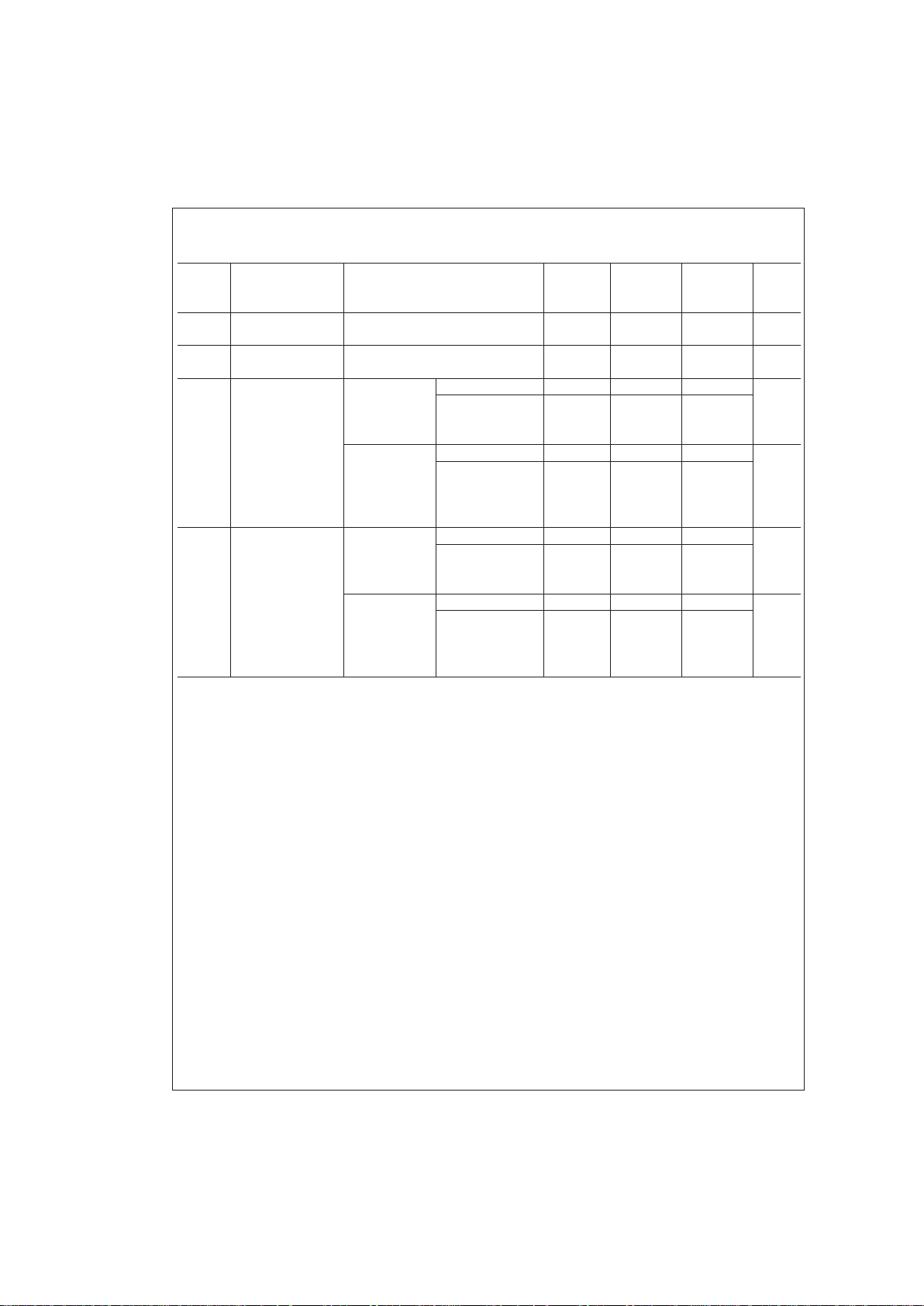

AC Electrical Characteristics

Unless otherwise specified, all limits guaranteed for T

J

=

25˚C, V

+

=

5V, V

−

=

0V, V

CM

=

V

O

=

V

+

/2. Boldface limits apply at

the temperature extreme

Typ LMC7221AI LMC7221BI

Symbol Parameter Conditions (Note 5) Limit Limit Units

(Note 6) (Note 6)

t

rise

Rise Time f=10 kHz, C

L

=

50 pF, (Note 9) 0.3 µs

Overdrive=10 mV, 5 kΩ Pullup

t

fall

Fall Time f=10 kHz, C

L

=

50 pF, (Note 9) 0.3 µs

Overdrive=10 mV, 5 kΩ Pullup

t

PHL

Propagation Delay f=10 kHz, 10 mV 10 µs

(High to Low) C

L

=

50 pF, 100 mV 4

(Note 11) 5 kΩ Pullup

(Note 9)

V+=2.7V, 10 mV 10 µs

f=10 kHz,

C

L

=

50 pF, 100 mV 4

5kΩPullup

(Note 9)

t

PLH

Propagation Delay f=10 kHz, 10 mV 6 µs

(Low to High) C

L

=

50 pF, 100 mV 4

(Note 11) 5 kΩ Pullup

(Note 9)

V+=2.7V, 10 mV 7 µs

f=10 kHz,

C

L

=

50 pF, 100 mV 4

5kΩPullup

(Note 9)

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but specific performance is not guaranteed. For guaranteed specifications and the test conditions, see the Electrical Characteristics.

Note 2: Human body model, 1.5 kΩ in series with 100 pF.

Note 3: Applies to both single-supply and split-supply operation. Continuous short circuit operation at elevated ambient temperature can result in exceeding the

maximum allowed junction temperature of 150˚C. Output currents in excess of

±

30 mA may adversely affect reliability.

Note 4: The maximum power dissipation is a function of T

J(max)

, θJA, and TA. The maximum allowable power dissipation at any ambient temperature is

Note 5: P

D

=

(T

J(max)−TA

)/θJA. All numbers apply for packages soldered directly into a PC board.

Note 6: Typical values represent the most likely parametric norm.

Note 7: All limits are guaranteed by testing or statistical analysis.

Note 8: Limiting input pin current is only necessary for input voltages which exceed the absolute maximum input voltage rating.

Note 9: Do not short circuit the output to V+ when V+ is greater than 12V or reliability will be adversely affected.

Note 10: C

L

includes the probe and test jig capacitance.

Note 11: Input offset voltage average drift is calculated by dividing the accelerated operating life V

OS

drift by the equivalent operational time. This represents worst

case input conditions and includes the first 30 days of drift.

Note 12: Input step voltage for propagation delay measurement is 2V.

www.national.com 4

Loading...

Loading...