NSC LM9833CCVJD Datasheet

LM9833 48-Bit Color, 1200dpi USB Image Scanner

General Description

The LM9833 is a complete USB image scanner system on a single IC. The LM9833 provides all the functions (image sen sor

control, illumination control, analog front end, pixel processing

function image data buffer/DRAM controller, microstepping

motor controller, and USB interface) necessary to crea te a high

performance color scann er. The LM9833 scans imag es in 48 bit

color/16 bit gray, and has output data formats for 48 and 24bit

color/16 and 8 bit gray. The LM9833 su pp orts sensors with pixel

counts of up to 16384 pixels x 3 colors (1200 dpi x 13.6 inches).

The LM9833’s low operating and suspend mode supply currents

allow design of USB bus- powe re d scan ne rs. T he only a dditional

active components required are an external 4Mbit or 16Mbit

DRAM for data bufferi ng and power transistors fo r the stepper

motor.

Applications

•

Color Flatbed Document Scanners

•

Color Sheetfed Document Scanners

Key Specifications

•

Analog to Digital Converter Resolution 16 Bits

•

Maximum Pixel Conversion Rate 6MHz

•

A4 Color 150dpi scan time <10 seconds

•

A4 Color 300dpi scan time <40 seconds

•

A4 Color 600dpi scan time <160 seconds

•

Supply Voltage

- LM9833 +4.75V to +5.25V

- LM9833 DRAM I/O +2.85 to +5.25V

•

Maximum Operating Current Consumption 136mA

•

Maximum Suspend Current Consumption 175µA

Features

• 16 bit ADC digitizes at up to 6Mpixels/s (2M RGB pixels/sec).

• Digital Pixel Processing provid es 1200, 800, 600, 400, 300,

200, 150, and 100dpi horizontal resolution from a 1200dpi

sensor and 600, 400, 300, 200, 150, 100, 75, and 50dpi

horizontal resolution from a 600dpi sensor.

• Provides 50-2400dpi vertical resolution in 1 dpi increments.

• Pixel rate error correction for gain (shading) and offset errors.

• Supports 4 or 16Mbit external DRAMs.

• Multiple CCD clocking rates allows matching of CCD clock to

scan resolution and pixel depth for maximum scan speed.

• Stepper motor control ti ghtly coupled with imag e data buffer

management to maximize data transfer efficiency.

• PWM stepper motor current control allows microsteppi ng for

the price of fullstepping.

• USB interface f or Plug and P lay o peration on U SB-equipp ed

computers.

• Serial EEPROM option for custom Vendor and Product IDs.

• Support for USB bus-powered operation.

• Pixel depths of 1, 2, or 4 bits are packed into bytes for faster

scans of line art and low pixel depth images.

• Supports 3 channel CCDs and 1 channel CIS sensors.

• 3 (R, G, and B) 12-bit, u ser-programmable gam ma cor rect ion

tables.

• Compatible with a wide range of color linear CCDs and

Contact Image Sensors (CIS).

• Operates with 48MHz external crystal.

• Internal bandgap voltage reference.

• 100 pin TQFP package

LM9833 48-Bit Color 1200dpi USB Image Scanner

October 2001

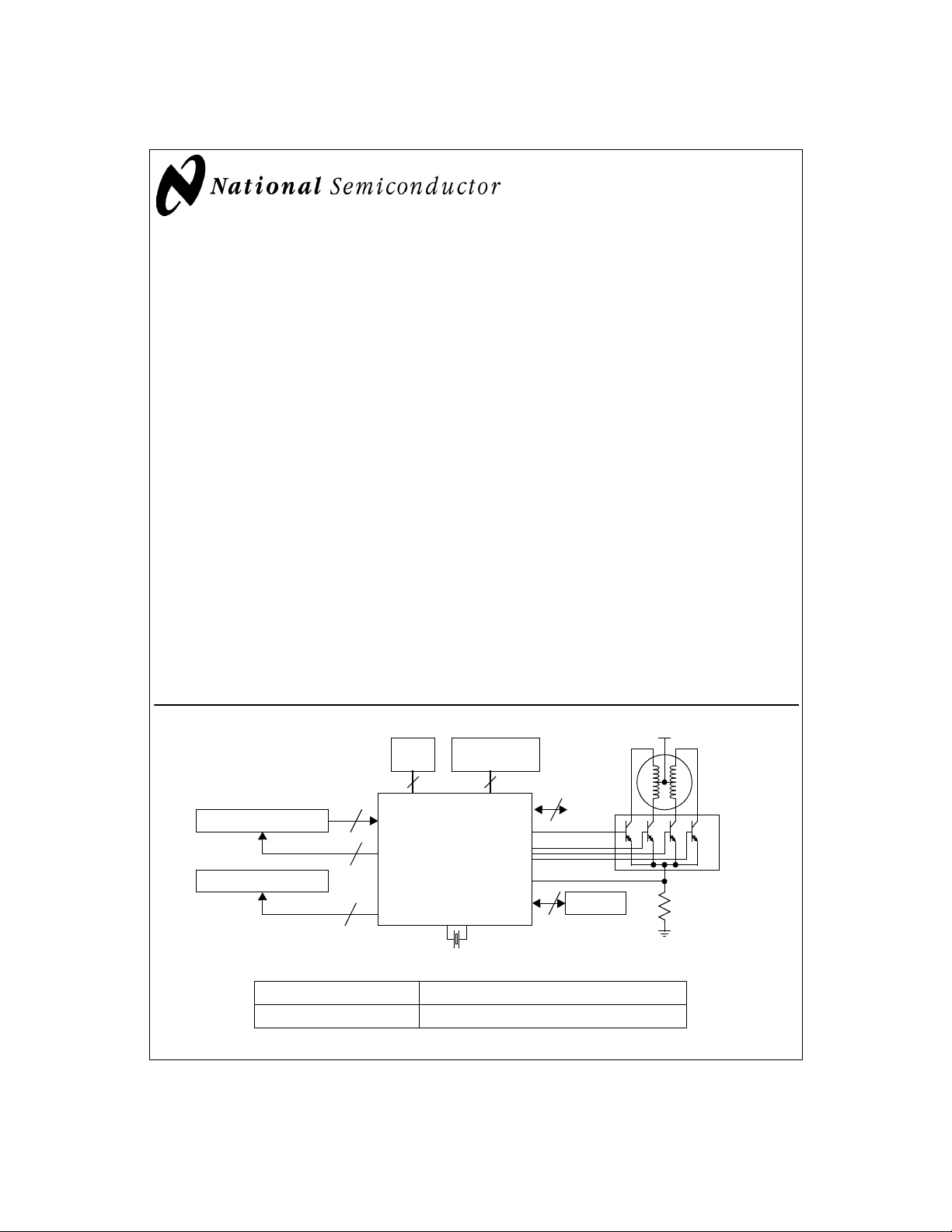

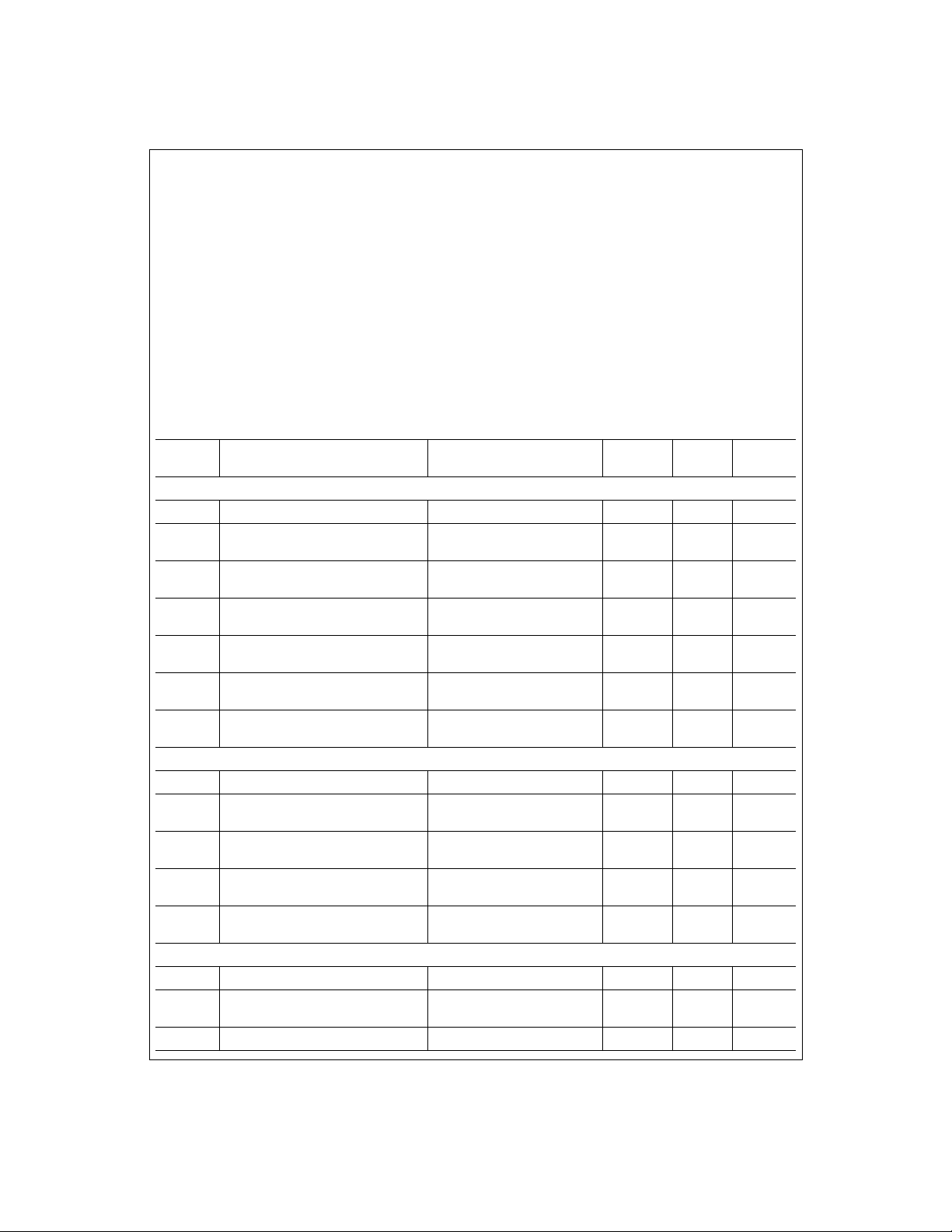

LM9833 Scanner System Block Diagram

USB

Port

2

2-6

1-3

1-3

LM9833CCVJD

CCD/CIS

Illumination

Ordering Information

Commercial (0°C ≤ TA ≤ +70°C) Package

LM9833CCVJ D VJD100A 100 Pin Thin Quad Flatpac

©2000 National Semiconductor Corporation

Serial

EEPROM

2

8MISC

I/O

30

DRAM

48MHz Crystal

1 www.national.com

+12V

Stepper

Motor

Power

Transistors

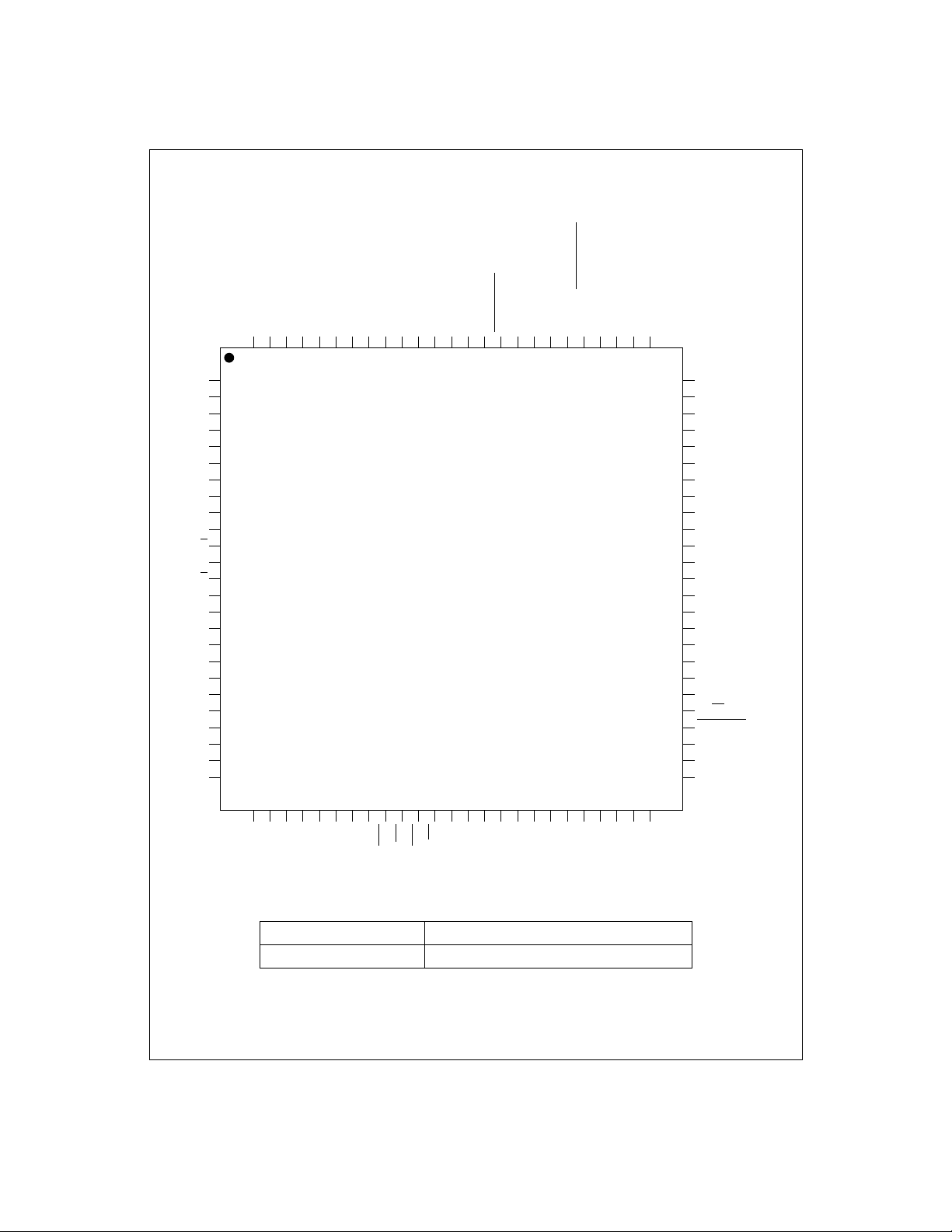

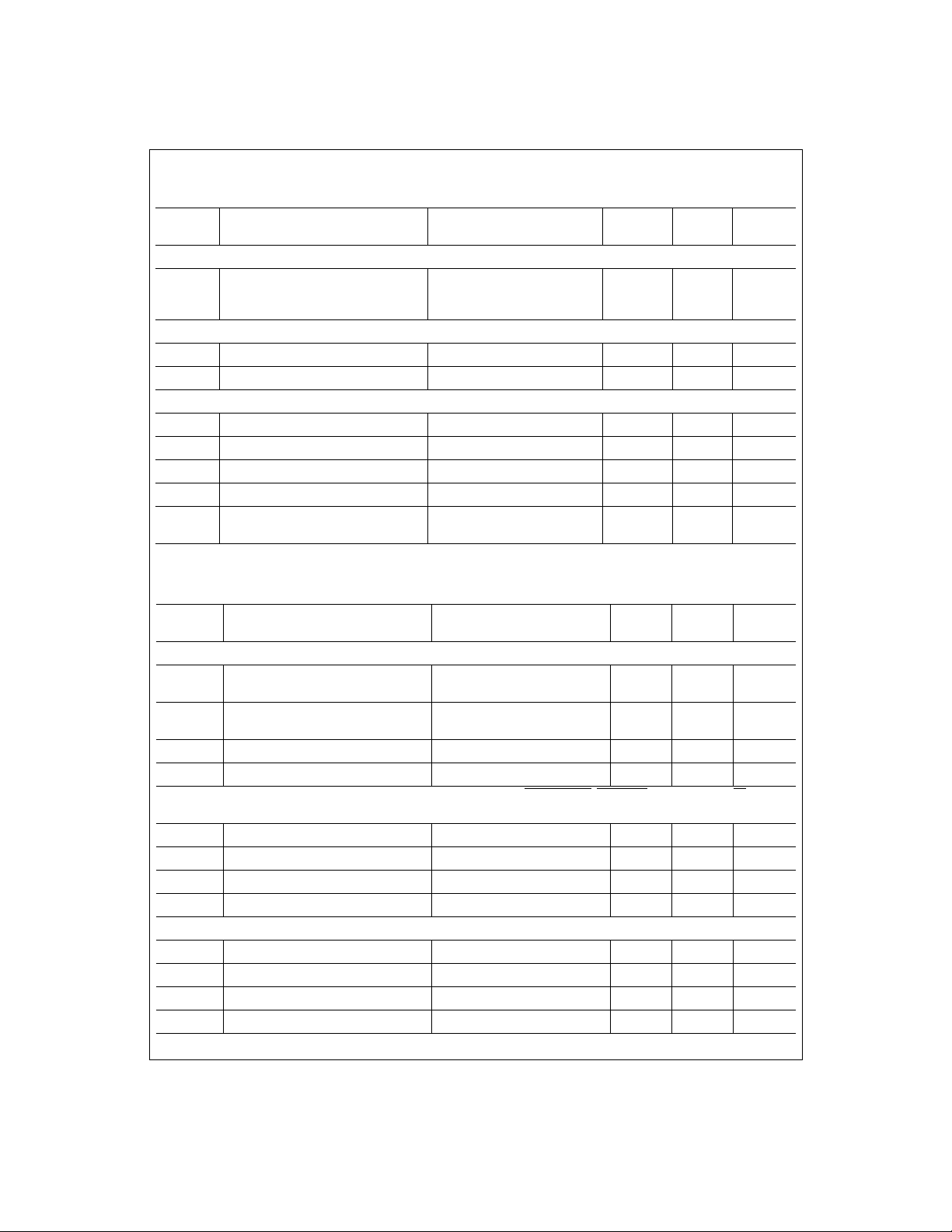

Connection Diagram

LM9833

V

BANDGAP

V

REF LO

V

REF MID

V

REF HI

AGND

V

DGND

OS

OS

OS

D0

D15

DRAM

D1

D14

D2

D13

D3

D12

D4

D11

AGND VADGND VDTEST SENSEGND SENSEA SENSEB NC CMODE RESET NC NC DGND VDBUS POWR D+ D- V

REGULATOR

DGND ACTIVE/SUSPENDED CP2 CP1 RS ø2

100999897969594939291908988878685848382818079787776

1

2

3

R

4

5

G

6

7

B

8

V

9

A

A

10

A

11

B

12

B

13

14

LM9833CCVJD

15

16

17

18

19

20

21

22

23

24

25

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

ø1

TR2

TR1

MISC I/O 6

MISC I/O 5

MISC I/O 4

DGND

V

MISC I/O 3

MISC I/O 2

MISC I/O 1

D

PAPER SENSE 1

PAPER SENSE 2

V

D

DGND

LAMP

B

LAMP

G

LAMP

R

DGND

V

D

24/48

CRYSTAL/EXT CLK

CRYSTAL IN

CRYSTAL OUT

SCL

26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50

D5

D6

D9

D10

Ordering Information

Commercial (0°C ≤ TA ≤ +70°C) Package

LM9833CCVJD VJD100A 100 Pin Thin Quad Flatpac

DRAM

V

D7

DGND

D8

A9A8A0A7A1

RD

WR

RAS

CAS

A6A2A5A3A4

DRAM

DGND

V

SDA

2 www.national.com

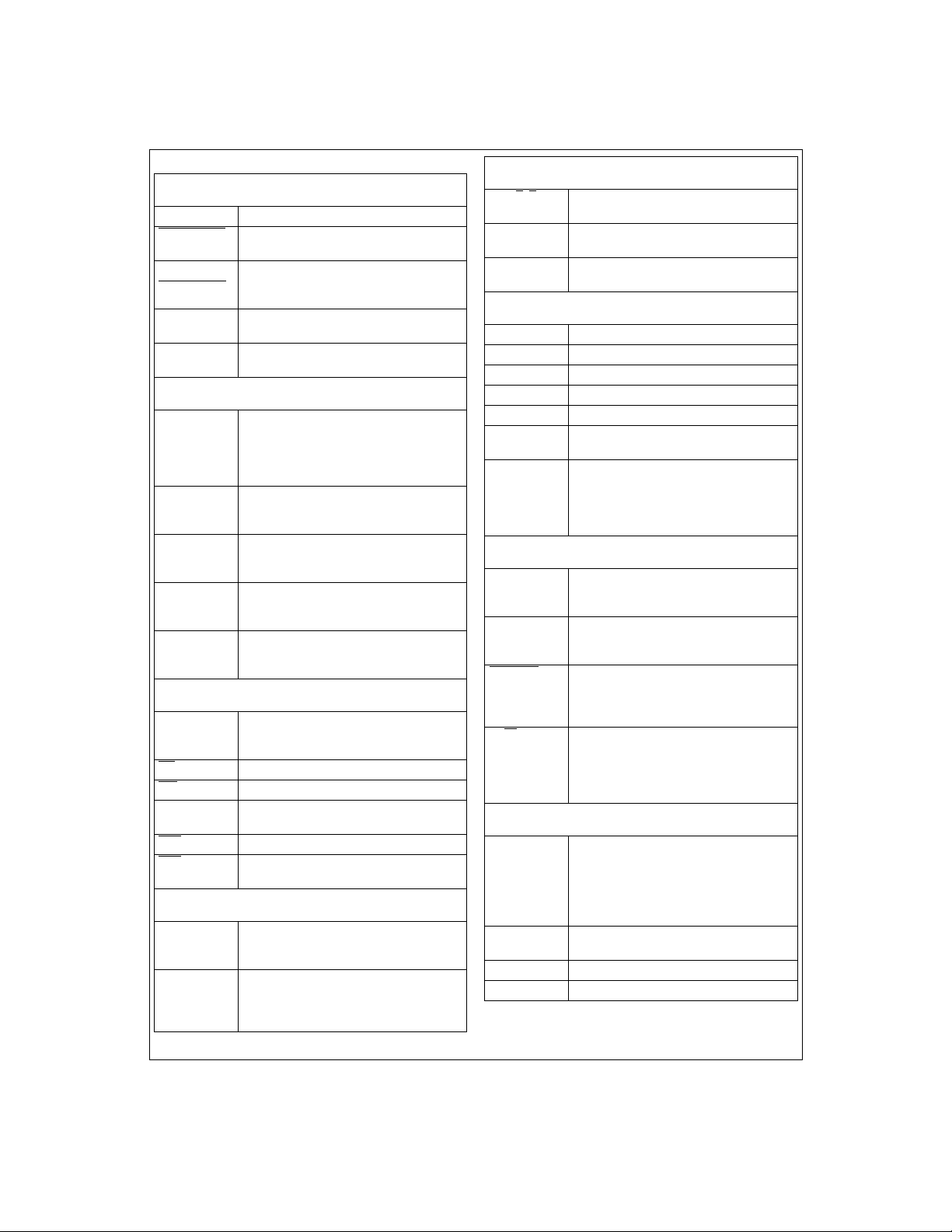

Pin Descriptions

USB Interface

D+, D- Digital I/O. USB Interface signals

BUS POWER

ACTIVE/

SUSPENDED

SDA Digital I/O. Serial Data to/from external

SCL Digital Output. Serial Clock Output to externa l

Digital Input. Tie low for bus powered systems, tie high for external power.

Digital Output. Low in Suspend mode. High in

operational mode. Used to control external

regulators, other components.

EEPROM.

EEPROM.

Analog

OSR,

OS

,

G

OS

B

V

REF LO

V

REF MID

V

REF HI

V

BANDGAP

Analog Inputs. The se inpu ts (for Re d, Green ,

and Blue) should be tied to the sensor ’s output signal through DC bloc king capacitors. If

unused, tie to ground through DC blocking

capacitors.

Analog Output/Input . Bypass to AGND with a

0.047µF monolithic capacitor. Do not put a

DC load on this pin.

Analog Output/Input . Bypass to AGND with a

0.047µF monolithic capacitor. Do not put a

DC load on this pin.

Analog Output/Input . Bypass to AGND with a

0.047µF monolithic capacitor. Do not put a

DC load on this pin.

Analog Output. Bypass to AGND with a

0.047µF monolithic capacitor. Do not put a

DC load on this pin.

DRAM

D0 (LSB) -D15

(MSB)

RD

WR

A0-A9 Digital Outputs. Addre ss pins for up to 1M x

RAS

CAS

Digital Inputs/Outp uts. This is the 16 bit data

path between the external DRAM and the

LM9833.

Digital Output. Read signal to external DRAM.

Digital Output. Write signal to external DRAM.

16 external DRAM.

Digital Output. Row Address Strobe signal.

Digital Output. Column Address Strobe sig-

nal.

Scanner Support I/O

PAPER

SENSE 1-2

MISC I/O 1-6 Digital Inputs/Outputs. Programmable, used

Digital Inputs. P rogrammable, u sed for sensing home position, paper, front panel

switches, etc.

for front panel switches, status LEDs, etc. A t

power-on and in Susp end Mode, MISC I/Os

1-3 are inputs and MISC I/Os 4-6 are outputs.

Stepper Motor

A, B, A, B Digital Outputs. Pulses to stepper motor drive

SENSE

A

SENSE

B

SENSE

GND

circuitry.

,

Analog Inputs. Current sensing for stepper

motor’s PWM current control.

Analog Input. Ground sen se input for stepper

motor’s PWM current control.

Sensor Control

ø1 Digital Output. CCD/CIS clock signal phase 1.

ø2 Digital Output. CCD/CIS clock signal phase 2.

RS Digital Output. Reset pulse for the CCD/CIS.

CP1 Digital Output. Clamp pulse for the CCD/CIS.

CP2 Digital Output. Clamp pulse for the CCD/CIS.

TR1, TR2 Digital Outputs. Transfer pulses for the

,

LAMP

R

LAMP

,

G

LAMP

B

CCD/CIS.

Digital Outputs. Us ed to control R, G, and B

LEDs of single output CIS, as well as brightness of CCFL. The CDS signal can be se en

on LAMP

7).

in a test mode (see registe r 5E, bi t

B

Master Clock Generation

CRYSTAL IN Digital Input. Used with CRYSTAL OUT and

CRYSTAL

OUT

CRYSTAL

EXT CLOCK

24/48

an external 48MHz crystal to form a crystal

oscillator.

Digital Output. Used with CRYST AL IN and an

external 48MHz crystal to form a crystal oscillator.

/

Digital Input. Tie to DGND for operati on with

an external crystal. Pull up to V

CRYSTAL OUT with an external TTL or

CMOS clock source.

Digital Input. Tie to DGND for operation with a

48MHz crystal or exter nal clo ck. P ull up to V

for operation with a 2 4M H z crystal o r e xter na l

clock. NOTE: Operation at 24MHz is not guaranteed - always use a 48MHz crystal.

to drive

D

Miscellaneous

V

REGULATOR

RESET Digital input. Take high to force device into

TEST Analog Output.

CMODE Digital Input. Test mode, always tie high.

Digital Output. This is the regu late d 3.3 V supply (generated from V

transceiver. It should be us ed as th e termina l

voltage for the 1.5k D+ pullup resistor, and

bypassed to DGND with a 0.047µF monolithic

capacitor.

Power On Reset state, low to exit reset state.

) that powers the USB

D

LM9833

D

3 www.national.com

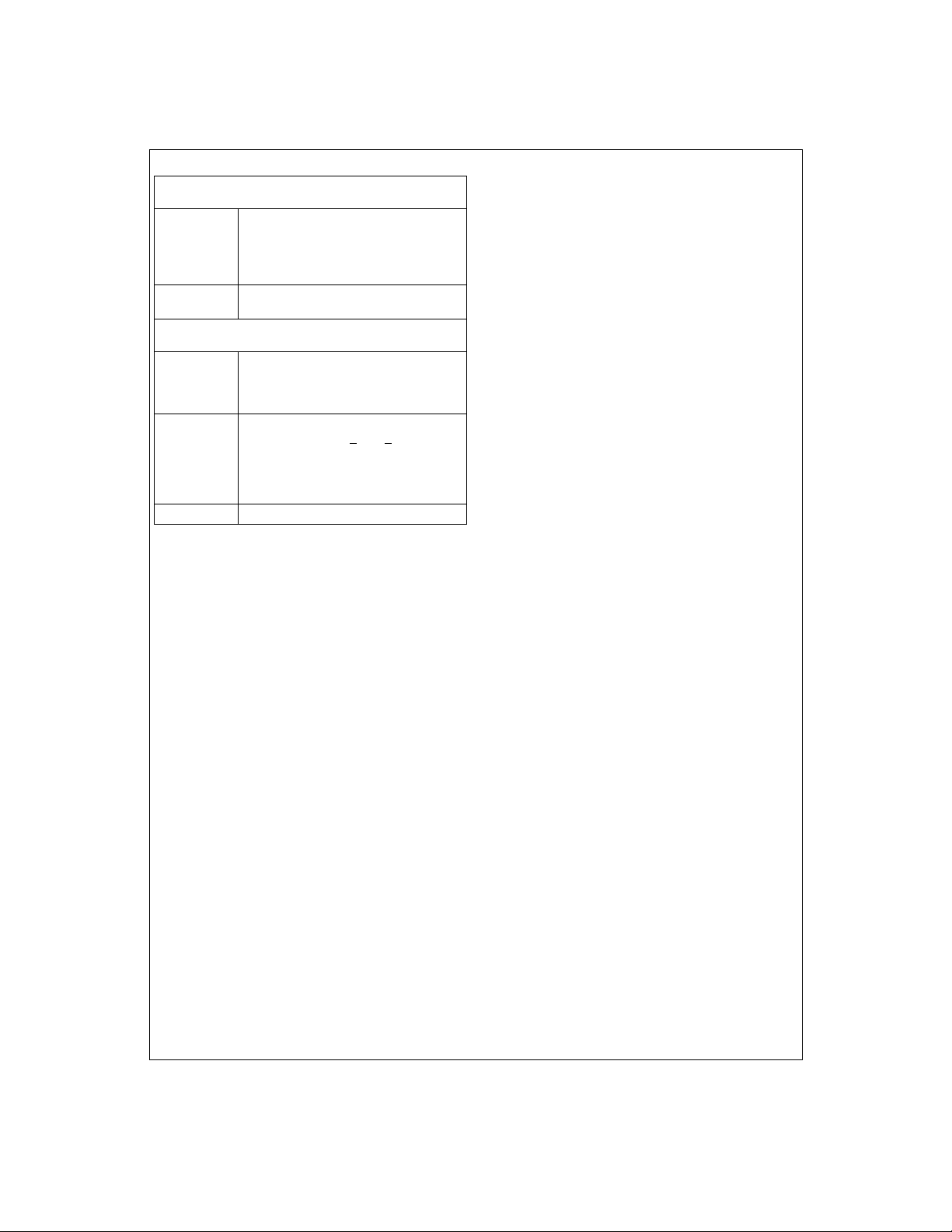

Pin Descriptions

Analog Power Supplies (4 pins)

LM9833

VA (2) This is the positive supply pin for the analog

AGND (2) This is the ground retu rn for the analog sup-

supply. It should be connected to a voltage

source of +5V and bypassed to AGND with a

0.1µF monolithic capacitor in parallel with a

10µF tantalum capacitor.

ply.

(Continued)

Digital Power Supplies (17 pins)

VD (5) This is the positive su pply pin for the digital

V

(3) This is the positiv e supply pin for the digital

DRAM

DGND (9) This is the ground return for V

supply. It should be connected to a voltage

source of +5V and bypassed to DGND with a

0.1µF monolithic capacitor.

supply for the LM9833’s external DRAM I/O. It

also powers th e A, B , A

outputs. It should be conne cted to a 3 or 5V

supply and bypassed to the closest DGND pin

with a 0.1µF monolithic capacitor.

, and B stepper motor

and V

D

DRAM

.

4 www.national.com

LM9833

DRAM

(Notes 1 & 2)

)

+

+0.3V

Operating Ratings

Operating Temperature Range T

LM9833CCVJD 0°C≤T

V

Supply Voltage +4.75V to +5.25V

A

V

Supply Voltage +4.75V to +5.25V

D

V

Supply Voltage +2.85V ≤ V

DRAM

|V

| ≤ 100mV

A-VD

Input Voltage Range -0.05V to V

Absolute Maximum Ratings

Positive Supply Voltage (V+=VA=VD=V

With Respect to GND=AGND=DGND 6.5V

Voltage On Any Input or Output Pin -0.3V to V

Input Current at any pin (Note 3) ±25mA

Package Input Current (Note 3) ±50mA

Package Dissipation at T

ESD Susceptibility (Note 5)

Human Body Model 2000 V

= 25°C (Note 4)

A

Machine Model 250 V

Soldering Information

Infrared, 10 seconds (Note 6) 235°C

Storage Temperature -65°C to +150°

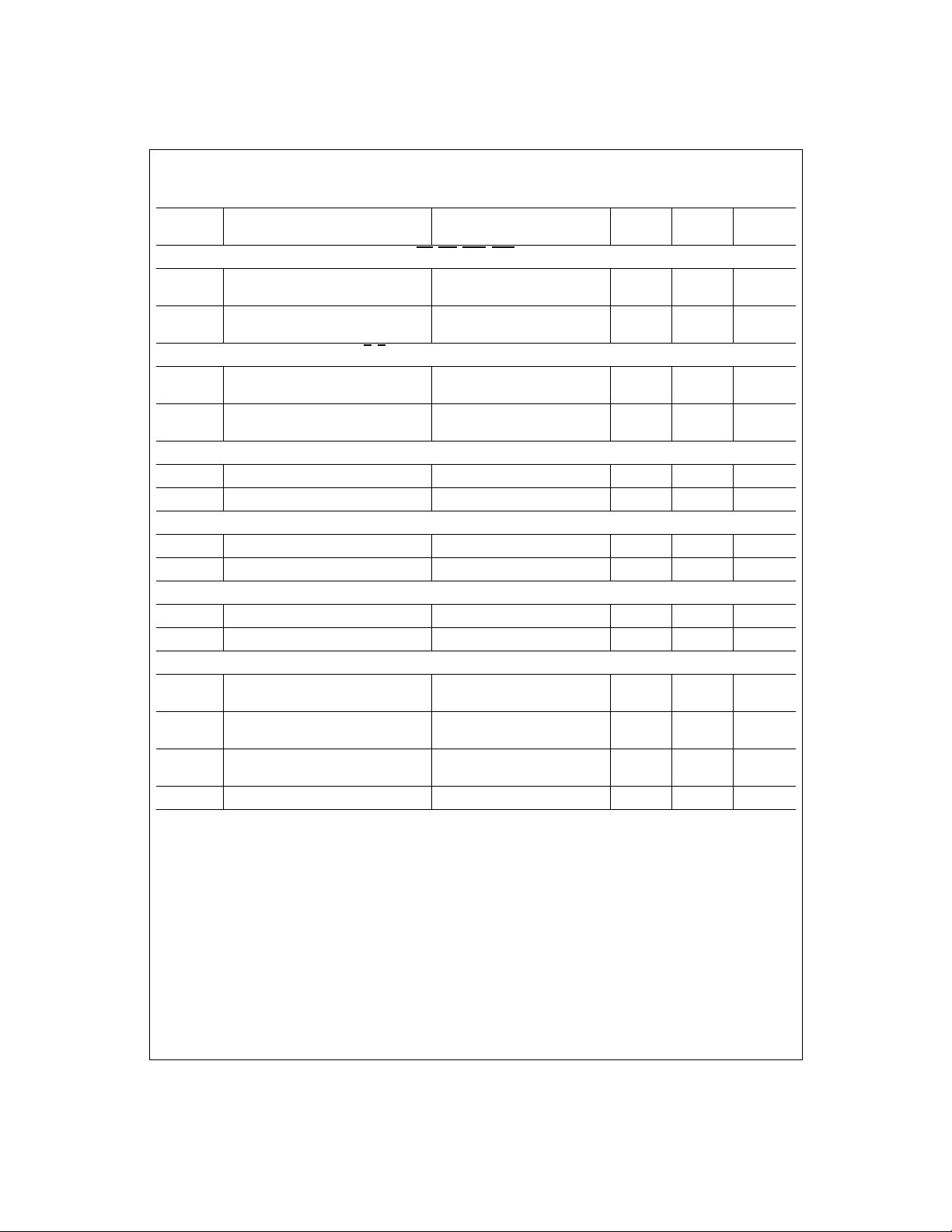

Electrical Characteristics

The following specifications apply for AGND=DGND=0V, VA=VD=V

100%, unless otherwise noted. Boldface limits apply for T

A=TJ=TMIN

Symbol Parameter Conditions

Full Channel Characteristics (in units of 12 bit LSBs unless otherwise noted)

Resolution with No Missing Codes 16 12 bits (min)

DNL

INL

V

OS1

V

OS2

V

OS3

Differential Non-Linear ity

(Note 14)

Integral Non-Lineari ty Error

(Notes 11 & 14)

Analog Channel Gain Constant

C

(ADC Codes/V), referred to 16 bi ts.

Pre-Boost Analog Channel Offset Error 26

Pre-PGA Analog Channel Offset Error -30

Post-PGA Analog Channel Offset Error -26

Bias Current = 80%,

V

DRAM

Bias Current = 80%,

V

DRAM

Includes voltage reference

variation, gain setting = 1

Coarse Color Balance PGA Characteristics (Configuration Registers 3B, 3C, and 3D)

Monotonicity 5 bits (min)

(Minimum PGA Gain) PGA Setting = 0 0.93

G

0

(Maximum PGA Gain) PGA Setting = 31 3.00

G

31

x3 Boost Gain

x3 Boost Setting On

(bit B5 of Gain Register is set)

Gain Error at any gain (Note 13) 0.3

Static Offset DAC Characteristics (Configuration Registers 38, 39, and 3A)

Monotonicity 6 bits (min)

Offset DAC LSB size PGA gain = 1 9

Offset DAC Adjustment Range PGA gain = 1 ±278 ±256 mV (min)

DRAM

=3.3V

=3.3V

=+5.0VDC, f

to T

CRYSTAL IN

; all other limits TA=TJ=25°C. (Notes 8, 9, & 10)

MAX

(Notes 1 & 2)

MIN≤TA≤TMAX

≤+70°C

A

≤ V

DRAM

+100mV

D

+

+ 0.05V

= 48MHz, Analog Bias Current =

Typical

(Note 9)

-0.45

+0.75

-2.3

+1.7

32768

2.94

Limits

(Note 10)

-0.9

+2.4

-8.5

+7.5

29648

37200

-34

+76

-80

+31

-75

+26

0.90

0.96

2.95

3.10

2.85

3.04

-0.6

+0.9

6

12

Units

(Limits)

LSB (min)

LSB (max)

LSB (min)

LSB (max)

LSB (min)

LSB (max)

mV (min)

mV (max)

mV (min)

mV (max)

mV (min)

mV (max)

V/V (min)

V/V (max)

V/V (min)

V/V (max)

V/V (min)

V/V (max)

% (min)

% (max)

mV (min)

mV (max)

5 www.national.com

Electrical Characteristics

The following specifications apply for AGND=DGND=0V, V

100%, unless otherwise noted. Boldface limits apply for T

LM9833

(Continued)

A=VD=VDRAM

A=TJ=TMIN

=+5.0VDC, f

to T

CRYSTAL IN

; all other limits TA=TJ=25°C. (Notes 8, 9, & 10)

MAX

Symbol Parameter Conditions

CCD/CIS Source Requiremen ts for Full Spec ified Accura cy and Dynamic Range (Note 12)

V

CCDPEAK

Sensor’s Maximum Outp ut Sig nal

Amplitude before LM9833 Analog Front

End Saturation

Gain = 0.933

Gain = 3.0

Gain = 9.0

Analog Input Characteristics

Average OS

OS

R

, OSG, OSB Input Current CDS Enabled, OS = 3.5V

R

, OSG, OSB Input Current CDS Disabled, OS = 3.5V

DC

DC

Internal Voltage Reference Characteristics

V

BANDGAP

V

REF LO

V

REF MID

V

REF HI

V

REGULA-

TOR

Voltage Reference Output Voltage 1.23 V

Negative Reference Output Voltage V

Midpoint Reference Output Voltage VA/2.0 V

Positive Reference Output Voltage

USB I/O Voltage Regulator 3.3 V

DC and Logic Electrical Characteristics

The following specifications apply for AGND=DGND=0V, VA=VD=V

f

CRYSTAL IN

= 48MHz. Boldface limits apply for TA=TJ=T

MIN

to T

Symbol Parameter Conditions

Digital Input Characteristics for D0-D15 (DRAM Interface)

V

V

V

C

Logical “1” Input Voltage

IN(1)

Logical “0” Input Voltage

IN(0)

Input Leakage Current ±0.1 µA

I

IN

Input Capacitance 5 pF

IN

V

V

V

DRAM

DRAM

DRAM

DRAM

Digital Input Characteristics for PAPER SENSE 1-2, MISC I/O 1-6, SDA, BUS POWER

CMODE

V

V

C

Logical “1” Input Voltage VD=5.25V 2.0 V (min)

IN(1)

Logical “0” Input Voltage VD=4.75V 0.8 V (ma x)

IN(0)

Input Leakage Current ±0.1 µA

I

IN

Input Capacitance 5 pF

IN

Digital Input Characteristics for D+, D-

V

V

C

Logical “1” Input Voltage VD=5.25V 2.0 V (min)

IN(1)

Logical “0” Input Voltage VD=4.75V 0.8 V (ma x)

IN(0)

Input Leakage Current ±0.1 µA

I

IN

Input Capacitance 5 pF

IN

=+5.0VDC unless otherwise noted,

DRAM

; all other limits TA=TJ=25°C. (Notes 8, 9, & 10)

MAX

=5.25V

=3.6V

=4.75V

=2.85V

= 48MHz, Analog Bias Current =

Typical

(Note 9)

1.9

0.6

0.19

Limits

(Note 10)

Units

(Limits)

V

V

V

±3 nA

±26 ±30 µA (max)

-1.0 V

REF MID

V

+1.0 V

REF MID

Typical

(Note 9)

Limits

(Note 10)

2.0

2.0

0.8

0.8

Units

(Limits)

V (min)

V (min)

V (max)

V (max)

, CRYSTAL/EXT CLOCK, 24/48, RESET,

6 www.national.com

A=VD=VDRAM

to T

MIN

MAX

(Continued)

=+5.0VDC unless otherwise noted,

; all other limits TA=TJ=25°C. (Notes 8, 9, & 10)

DC and Logic Electrical Characteristics

The following specifications apply for AGND=DGND=0V, V

f

CRYSTAL IN

= 48MHz. Boldface limits apply for TA=TJ=T

Symbol Parameter Conditions

Digital Output Characteristics for D0-D15, A0-A9, RD

V

OUT(1)

V

OUT(0)

Digital Output Characteristics for A, B, A

V

OUT(1)

V

OUT(0)

Logical “1” Output Voltage

Logical “0” Output Voltage

, B

Logical “1” Output Voltage

Logical “0” Output Voltage

, WR, RAS, CAS (DRAM Interface)

V

V

V

V

V

V

V

V

DRAM

DRAM

DRAM

DRAM

DRAM

DRAM

DRAM

DRAM

=4.75V, I

=2.85V, I

=4.75V, I

=2.85V, I

=4.75V, I

=2.85V, I

=4.75V, I

=2.85V, I

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

=-4mA

=-4mA

=4mA

=4mA

=-10mA

=-10mA

=4mA

=4mA

Digital Output Characteristics for MISC I/O 1-6, TR1, TR2, ø1, ø2, RS, CP1, CP2, LAMP

V

V

OUT(1)

OUT(0)

Logical “1” Output Voltage VD=4.75V, I

Logical “0” Output Voltage VD=4.75V, I

=-4mA 2.4 V (min)

OUT

=4mA 0.4 V (ma x)

OUT

Digital Output Characteristics for D+, D-

V

V

OUT(1)

OUT(0)

Logical “1” Output Voltage VD=4.75V, I

Logical “0” Output Voltage VD=4.75V, I

=-1mA 2.4 V (min)

OUT

=3mA 0.4 V (ma x)

OUT

CRYSTAL IN, CRYSTAL OUT Characteristics

XTAL

XTAL

CRYSTAL OUT Bias Level (Offset) 0.8 V

OUT DC

CRYSTAL OUT Amplitude f

OUT AC

= 48MHz 0.8 V

CRYSTAL

Power Supply Characteristics (Note 14)

I

A

I

D

I

DRAM

I

SUSPEND

Analog Supply Current

(V

pins)

A

Digital Supply Current

(V

pins)

D

DRAM Supply Current

(V

pins)

DRAM

Total Suspend Current (IA+ID+I

DRAM

Operating (Bias Current = 80%) 65 91 mA (max)

Operating (Bias Current = 80%) 35 41 mA (max)

Operating, V

Operating, V

DRAM

DRAM

= 5V

= 3V

)19175 µA (max)

Typical

(Note 9)

, LAMPG, LAMP

R

2

1

Limits

(Note 10)

2.4

2.4

0.4

0.4

2.4

2.4

0.4

0.4

B

8

5

LM9833

Units

(Limits)

V (min)

V (min)

V (max)

V (max)

V (min)

V (min)

V (max)

V (max)

P-P

mA (max)

mA (max)

7 www.national.com

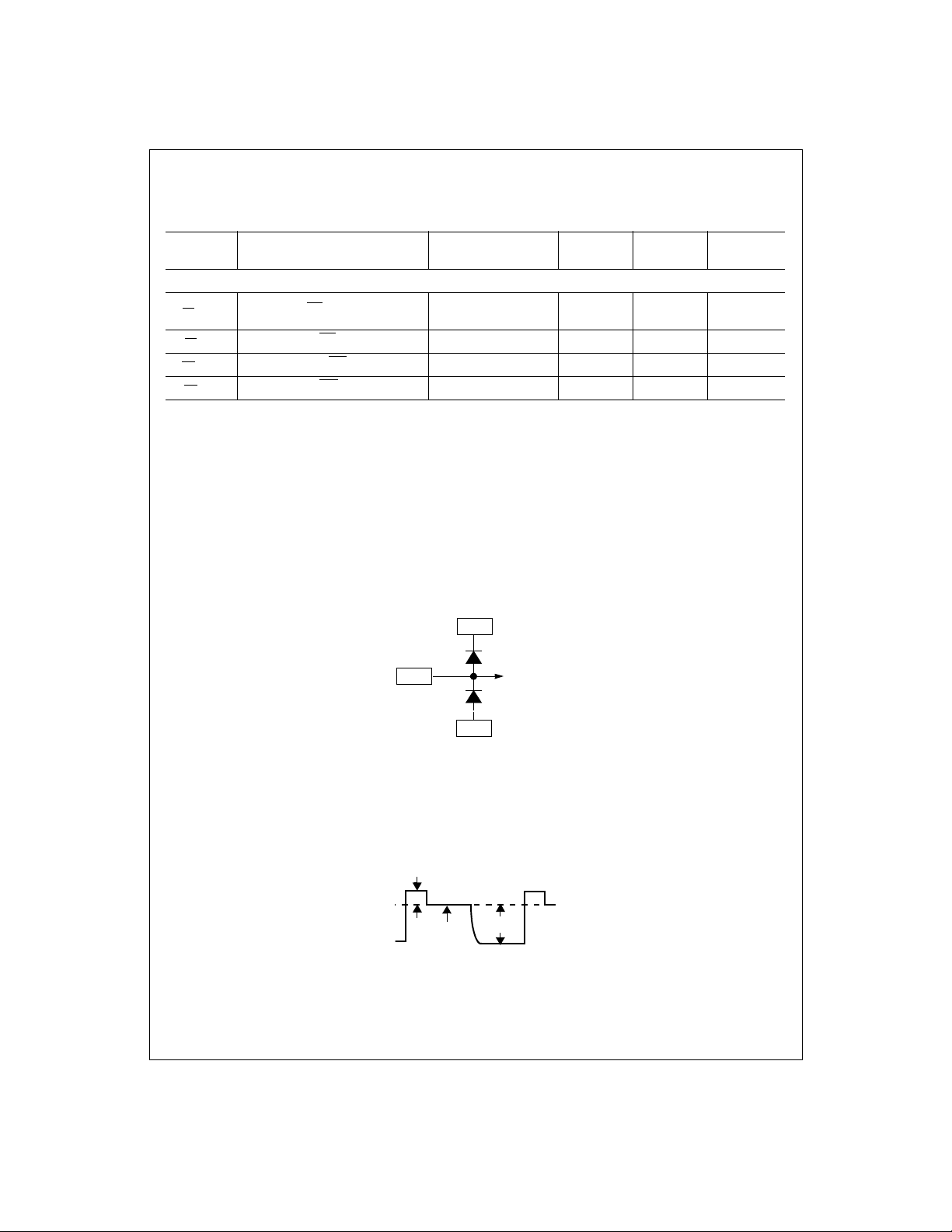

AC Electrical Characteristics

The following specifications apply for AGND=DGND=0V, VA=VD=V

LM9833

f

CRYSTAL IN

C

= 48MHz, MCLK DIVIDER = 1.0 (unless otherwise noted), f

(databus loading) = 20pF/pin. Boldface limits apply for TA=TJ=T

L

Symbol Parameter Conditions

DRAM Timing (Figure 1)

=5.0V

V

t

RD SETUP

t

RD HOLD

t

WR SETUP

t

WR HOLD

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional ,

but do not guara nt ee specific perform ance limits. For g uaranteed specifications and test conditions, see the Electrical Chara cteristics. The gua ranteed specificat ions apply

only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions.

Note 2: All voltages are measured with respect to GND =AGND=DGND = 0V, unless otherw is e specified.

Note 3: When the input voltage (V

maximum package input current rating limits the number of pins that can simultaneously safely exceed the power supplies with an input current of 25mA to two.

Note 4: The maximum power dissipation must be derated at elevated temperatures and is dictated by T

able power dissipation at any temperature is P

.

is 53°C/W

Note 5: Human body model, 100pF capacitor disch arged through a 1.5 k Ω resistor. Machine model, 200pF capacitor discharged through a 0Ω resistor.

Note 6: See AN-450 “Surface Mounting Methods and Their Effect on Product Reliability” or the section titled “Surface Mount” found in any National Semiconductor Linear

Data Book for other m et hods of soldering su rf ac e mount devices.

Note 7: Two diodes clamp the OS analog inputs to

impedance of the sensor, prevents damage to th e LM9833 from tra ns ients during power-up.

Data valid to RD rising edge

Data valid after RD rising edge 0 ns (min)

Data valid before WR falling edge 5 ns (min)

Data valid after WR rising edge 10 ns (min)

) at any pin exceeds the power supplies (VIN<GND or VIN>VA or VD), the current at that pin should be limited to 25mA. The 50mA

IN

= (TJmax - TA) / ΘJA. TJmax = 150°C for this device. The typical thermal resistance (ΘJA) of this part when board mounted

D

AGND

and VA as shown below. This input protection, in combination with the external clamp capacitor and the output

V

DRAM

DRAM

=3.3V

VA

=+5.0VDC unless otherwise noted,

DRAM

MIN

MCLK

to T

= f

CRYSTAL IN

MAX

/MCLK DIVIDER, f

; all other limits TA=TJ=25°C. (Notes 8, 9, & 10)

Typical

(Note 9)

max, ΘJA and the ambient temperature, TA. The maximum allow-

J

Limits

(Note 10)

26

35

ADC CLK

= f

MCLK

Units

(Limits)

ns (min)

ns (min)

/8,

OS Input

To Internal

Circuitry

AGND

Note 8: For best performance, it is required that all supply pins be powered from the same power supply with separate bypass capacitors at each supply pin.

Note 9: Typicals are at T

Note 10: Tested limits are guaranteed to National's AOQL (Average Outgoing Quality Level).

Note 11: Integral linearity error is defined as the deviation of the analog value, expressed in LSBs, from the straight line that best fits the actual transfer function o f the ADC.

Note 12: V

a white (full scale) image wi th r es pect to the reference level, V

correctable range of pixel-to-pixel V

LM9833 can correct for using its internal PGA.

Note 13: PGA Gain Error is the maximum difference between the measured gain for any PGA code and the ideal gain calculated by using the formula

Gain

Note 14: DNL, INL, and Pow er Supply Current are s pecified at the 80% Bi as Current Setting (R egister 9). This is the ma ximum recomme nded Bias Curren t setting , and

gives the best analog performance as we ll as lower power consu m pt ion for USB-bus powered applications.

is defined as the CCD OS voltage for the reference pe ri od foll o wing the r eset feedthrough pulse. V

REF

V

G0X

--- -

PGA

V

=25°C, f

J=TA

WHITE

PGA code

-------------- ------------ -+=XG

where .

32

= 48MHz, and repre s ent most likely parametric norm.

CRYSTAL IN

is defined as the peak positive deviation above V

. V

REF

variation is defined as the maximum variation in V

–()

31G0

RFT

CCD Output Signal

V

RFT

V

REF

32

------=

31

V

is defined as the peak CCD pixel output voltage for

WHITE

of the reset feedthrough pulse. The maximum

(due to PRNU, light source intensity variation, optics, etc.) that the

WHITE

WHITE

REF

8 www.national.com

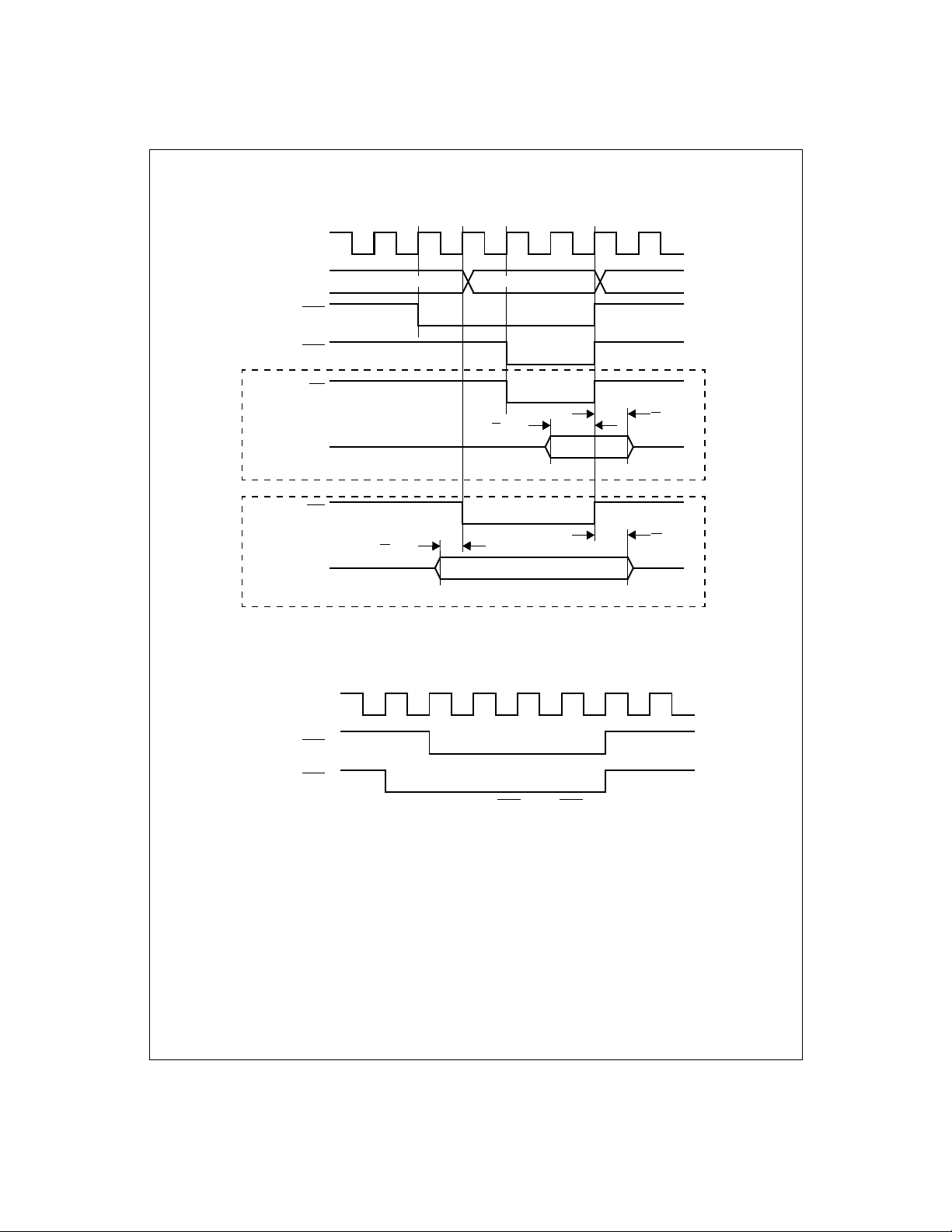

Timi ng Diagra ms

LM9833

48MHz Internal Clock

(t

= 20.83ns)

PERIOD

A0-A9 Row Address

RAS

CAS

RD

Read Operation

WR

Write Operation

01234560

n

Column Address

t

RD SETUP

n

Row Address

t

RD HOLD

n+1

DataD0-D15

t

t

WR SETUP

WR HOLD

DataD0-D15

Figure 1: DRAM Read and Write

48MHz Internal Clock

(t

= 20.83ns)

PERIOD

RAS

CAS

01234560

Figure 2: DRAM Refresh (CAS

before RAS)

9 www.national.com

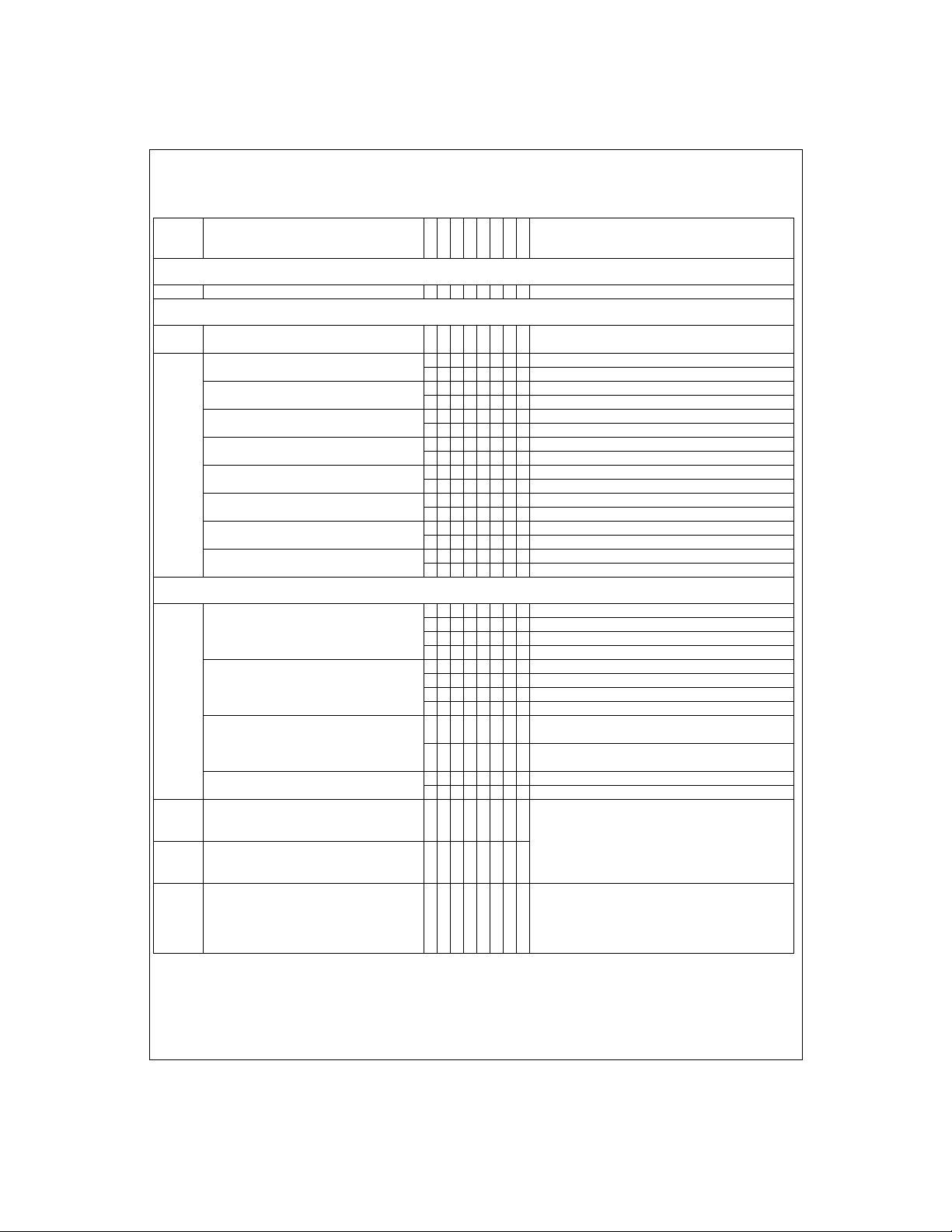

Register Listing

Registers in bold boxes are reset to that value on power-up. All register addresses are in hexadecimal. All other numbers are

LM9833

decimal unless otherwise noted.

Address Function

IMAGE BUFFER (READ ONLY)

00 Pixel (Image) Data nnnnnnnnOne byte of image data.

STATUS REGISTERS (READ ONLY)

01 Image Data Available In Buffer nnnnnnnn

PAPER SENSE 1 State

read clears bit if edge sensitive input.

PAPER SENSE 2 State

read clears bit if edge sensitive input.

MISC I/O 1 State

read clears bit if edge sensitive input.

MISC I/O 2 State

read clears bit if edge sensitive input.

02

MISC I/O 3 State

read clears bit if edge sensitive input.

MISC I/O 4 State

read clears bit if edge sensitive input.

MISC I/O 5 State

read clears bit if edge sensitive input.

MISC I/O 6 State

read clears bit if edge sensitive input.

DATAPORT REGISTERS

DataPort T arget

DataPort T arget Color

03

Pause (Read Only)

This bit indicates whether or not the scanner

is currently paused due to a buffer full

condition.

DRAM Test

04 DataPort Address - MSB

05 DataPort Address - LSB aaaaaaaa

06 DataPort nnnnnnnn

D7D6D5D4D3D2D1D

0False

1True

0False

1True

0False

1True

0False

1True

0Normal State

1 The scanner is currently in the pause/reverse cycle.

0 Normal Operation

1 DRAM Test mode

R

/Waaaaaa

0

n*2 (256k x 16 DRAM) or n*8 (1M x 16 DRAM)

kilobytes of image data is available

0False

1True

0False

1True

0False

1True

0False

1True

0 0 Offset Coefficient Data

0 1 Gain Coefficient Data

1 0 Gamma Lookup Table

11N/A

00 Red

01 Green

10 Blue

11 N/A

Address of location to be read/written to.

a = 0 to 4095 for gamma tables,

0 to 16383 for Offset and Gain Coefficient Data

Addresses greater than these are illegal.

Bit D6 of register 4 indicates whether next operation

will be a Read (D6=1) or a Write (D6=0).

Data to be read from or written to the address of the

currently selected Dataport Target. The DataPort

Address is automatically incremented whenever one

(gamma data) or two (Gain/Offset Data) bytes are

read from or written to this register.

Value

10 www.national.com

MCLK

(Continued)

/8

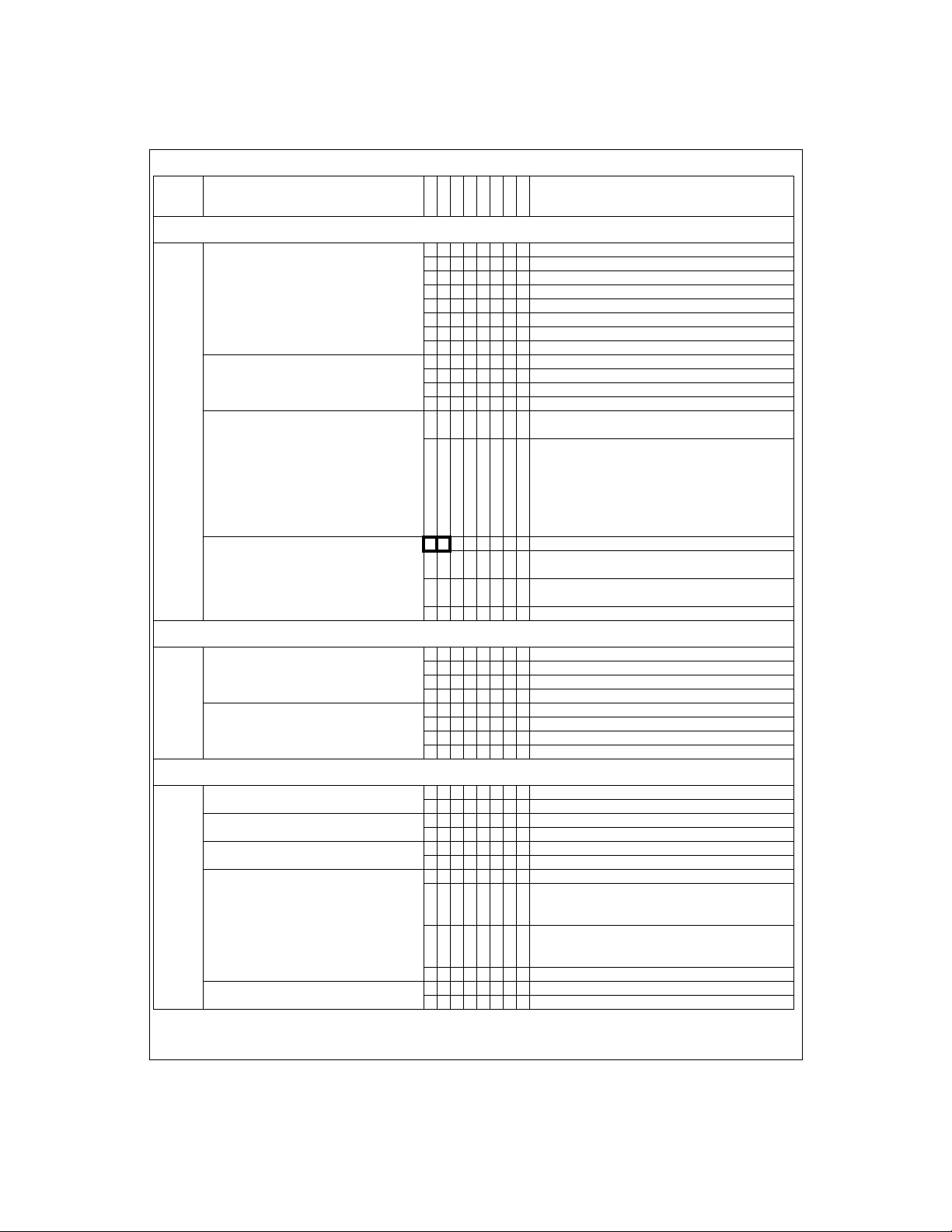

Register Listing

Address Function

COMMAND REGISTER

Command Register

This register is used to start and end a scan.

It is also used to home the sensor in a

flatbed scanner or eject the image in a

sheetfed scanner. Note: Always make sure

the Command Reg i st er i s in the idle s tat e

(=0) before issuing a new command.

07

Standby

When this bit is set the entire chip enters a

low power state.

Warning: A Standby command will stop

DRAM refresh.

Soft Reset

Write a 1 then a 0 to reset the LM9833’s

state machines.

Warning: A Reset will stop DRAM refresh.

MASTER CLOCK DIVIDER

MCLK Divider

This register sets the master clock frequency

for the entire scanner.

08

f

= 48MHz/MCLK_Divider

MCLK

f

= f

ADC

D7D6D5D4D3D2D1D

0 Normal Operation.

1 Low Power Standby Mode.

0 Normal Operation.

1

000000÷1.0

000001÷1.5

000110÷4

aaaaaa÷ ((aaaaaa/2)+1)

111110÷32.0

111111÷32.5

0

Idle - Stops motor (A, B, A

000

completes current line of data (if scanning).

Note: CCD/CIS clocks continue clocking.

High Speed Forward - Moves motor forward at a

001

speed determined by the Fast Feed Step Size

(registers 48 and 49).

High Speed Reverse - Moves motor backward at a

010

speed determined by the Fast Feed Step Size

(registers 48 and 49).

Start Scan - Resets the LM9833’s data pointers and

011

starts an image scan.

Programmed High Speed Forward - Moves motor

forward at a speed determined by the Fast Feed Step

101

Size (registers 48 and 49) for the number of lines

programmed in registers 4A and 4B.

Programmed High Speed Reverse - Moves motor

backward at a speed determined by the Fast Feed

110

Step Size (registers 48 and 49) for the number of lines

programmed in registers 4A and 4B.

Resets the LM9833. See section 10.2 Soft Reset for

instructions on using this bit.

LM9833

Value

, B = 0),

11 www.national.com

Register Listing

Address Function

LM9833

HORIZONTAL RESOLUTION AND DATAMODE SETTINGS

Horizontal DPI Divider

This register determines the horizontal

resolution of the scan.

Scan resolution = Optical resolution divided

by the Horizontal_DPI_Divider.

Pixel Packing

This register determines how many bits in

each byte of data are transmitted to the host

when DataMode = 0

DataMode

09

When DataMode = 0, the pixel data is fully

processed, going through the Offset,

Shading, Horizontal DPI Adjust, Gamma,

and Pixel Packing blocks.

When DataMode = 1, 16 bit da ta is ext racte d

following the Shading Multiplier stage.

Gamma and any other post processing must

be done by th e host.

Analog Bias Current (Percent of Nominal)

The recommended setting is 80% for best

performance. Lower settings will reduce

power consumption further but may degrade

ADC INL and DNL performance.

TURBO AND PREVIEW MODE SETTINGS

Turbo/Preview Mode Select

0A

Turbo/Preview Mode Speed

SENSOR CONFIGURATION

Input Signal Polarity

CDS On/Off

Standard/Even-Odd Sensor

0B

CIS TR1 Timing Mode

Fake Optical Black Pixels

(for Dyna-type CIS sensors)

(Continued)

D7D6D5D4D3D2D1D

0 0 1 bit/pixel (1 bit grayscale/3 bit color)

0 1 2 bits/pixel (2 bit grayscale/6 bit color)

1 0 4 bits/pixel (4 bit grayscale/12 bit color)

1 1 8 bits/pixel (8 bit grayscale/24 bit color)

0

1

0 0 100% (analog supply current = ~81mA)

0 1 80% (analog supply current = ~65mA)

1 0 70% (analog supply current = ~57mA)

1 1 50% (analog supply current = ~41mA)

0 0 Off - use standard CCD Timing

01

10

11 N/A

0 Off: Normal operation

1 On: RS pulse held high for entire Optical Black period

0

000÷1

001÷1.5

010÷2

011÷3

100÷4

101÷6

110÷8

111÷12

1, 2, 4, or 8 bit image data,

as determined by the Pixel Size setting.

16 bit image data - sent in 2 bytes, MSB first:

15 14 13 12 11 10 09 08 - 07 06 05 04 03 02 01 00

0 0 Normal Operation

0 1 Preview Mode (for CCD Sensors)

1 0 Turbo Mode (for CIS Sensors)

11 N/A

00 x2

0 1 x3 (3 Channel Pixel Rate Mode Only)

1 0 x4 (3 Channel Pixel Rate Mode Only)

1 1 x6 (3 Channel Pixel Rate Mode Only)

0 Negative (Most CCD Sensors and Toshiba CIS)

1 Positive (Most CIS Sensors)

0 CDS Off

1 CDS On

0 Standard (1 pixels per Ø period)

1 Even/Odd (2 pixels per Ø period)

CIS TR1 Timing Mode 1:

TR1 pulse = exactly one Ø clock,

starting at rising edge of Ø1

CIS TR1 Timing Mode 2:

TR1 pulse = exactly one Ø clock,

TR1 centered around Ø1 high.

Value

12 www.national.com

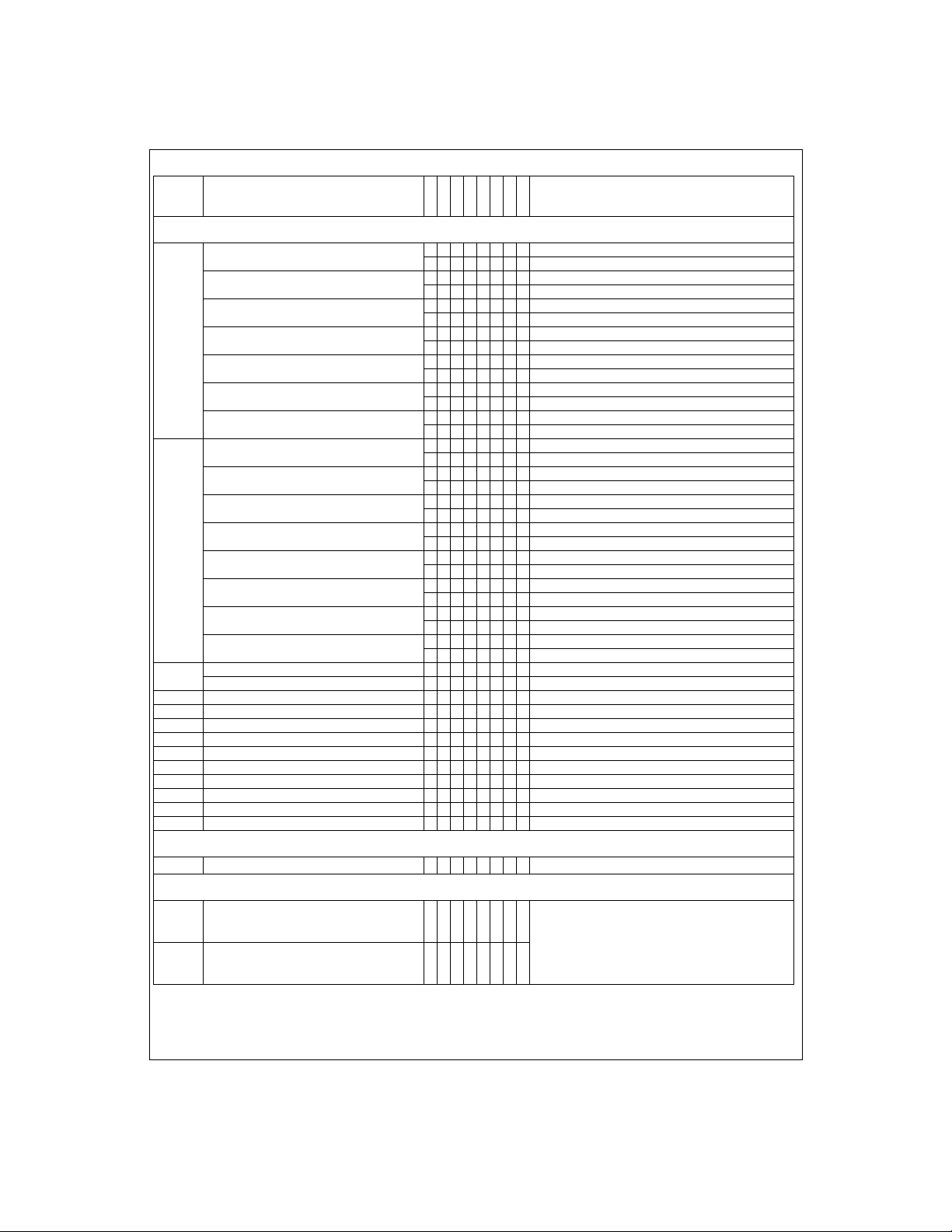

Register Listing

Address Function

SENSOR CONTROL SETTINGS

Ø1 Polarity

Ø2 Polarity

RS Polarity

0C

CP1 Polarity

CP2 Polarity

TR1 Polarity

TR2 Polarity

Ø1 Active/Off

Ø2 Active/Off

RS Active/Off

CP1 Active/Off

0D

CP2 Active/Off

TR1 Active/Off

TR2 Active/Off

Number of TR Pulses

TR Pulse Duration nnnnn+1 pixel periods (1-16)

0E

TR-Ø1 Guardband Duration n n n n n pixel periods (0-15)

0F Optical Black Clamp Start nnnnn

10 Optical Black Clamp End nnnnn

11 Reset Pulse Start nnnnn

12 Reset Pulse Stop nnnnn

13 CP1 Pulse Start nnnnn

14 CP1 Pulse Stop nnnnn

15 CP2 Pulse Start nnnnn

16 CP2 Pulse Stop nnnnn

17 Reference Sample Position nnnnn

18 Signal Sample Position nnnnn

INTEGRATION TIME ADJUST

19 Integration Time Adjustment Function nnnnnnn

STEPPER PHASE CORRECTION

1A TR to Stepper Phase Correction - MSB nnnnnn

1B TR to Stepper Phase Correction - LSB nnnnnnnn

(Continued)

D7D6D5D4D3D2D1D

0 Positive

1 Negative

0 Positive

1 Negative

0 Positive

1 Negative

0 Positive

1 Negative

0Off

1Active

0Off

1Active

0Off

1Active

0Off

1Active

01 TR Pulse

12 TR Pulses

0

0 Positive

1 Negative

0 Positive

1 Negative

0 Positive

1 Negative

0Off

1Active

0Off

1Active

0Off

1Active

pixel rate: n=0-23, line rate: n=0-7 MCLKs from Ø1 edge

pixel rate: n=0-23, line rate: n=0-7 MCLKs from Ø1 edge

pixel rate: n=0-23, line rate: n=0-7 MCLKs from Ø1 edge

pixel rate: n=0-23, line rate: n=0-7 MCLKs from Ø1 edge

pixel rate: n=0-23, line rate: n=0-7 MCLKs from Ø1 edge

pixel rate: n=0-23, line rate: n=0-7 MCLKs from Ø1 edge

pixel rate: n=0-23, line rate: n=0-7 MCLKs from Ø1 edge

pixel rate: n=0-23, line rate: n=0-7 MCLKs from Ø1 edge

pixel rate: n=0-23, line rate: n=0-7 MCLKs from Ø1 edge

pixel rate: n=0-23, line rate: n=0-7 MCLKs from Ø1 edge

t

= n*t

READOUT

First step of scan occurs n pixels (1 - 16383) after first

TR pulse. This register can be used to set the phase

between the TR pulses and the stepper motor pulses.

NOTE: a setting of n = 0 creates the maximum delay

(16384) pixels, which will increase scan time. If this

function is not used, this register should be set to 1.

Value

, n = 1 to 127. n=0 turns off function.

INT

LM9833

13 www.national.com

Loading...

Loading...