NSC LM9820CCWMX Datasheet

October 2000

LM9810/LM9820

10/12-Bit Image Sensor Processor Analog Front End

LM9810/20 10/12-Bit Image Sensor Processor Analog Front End

General Description

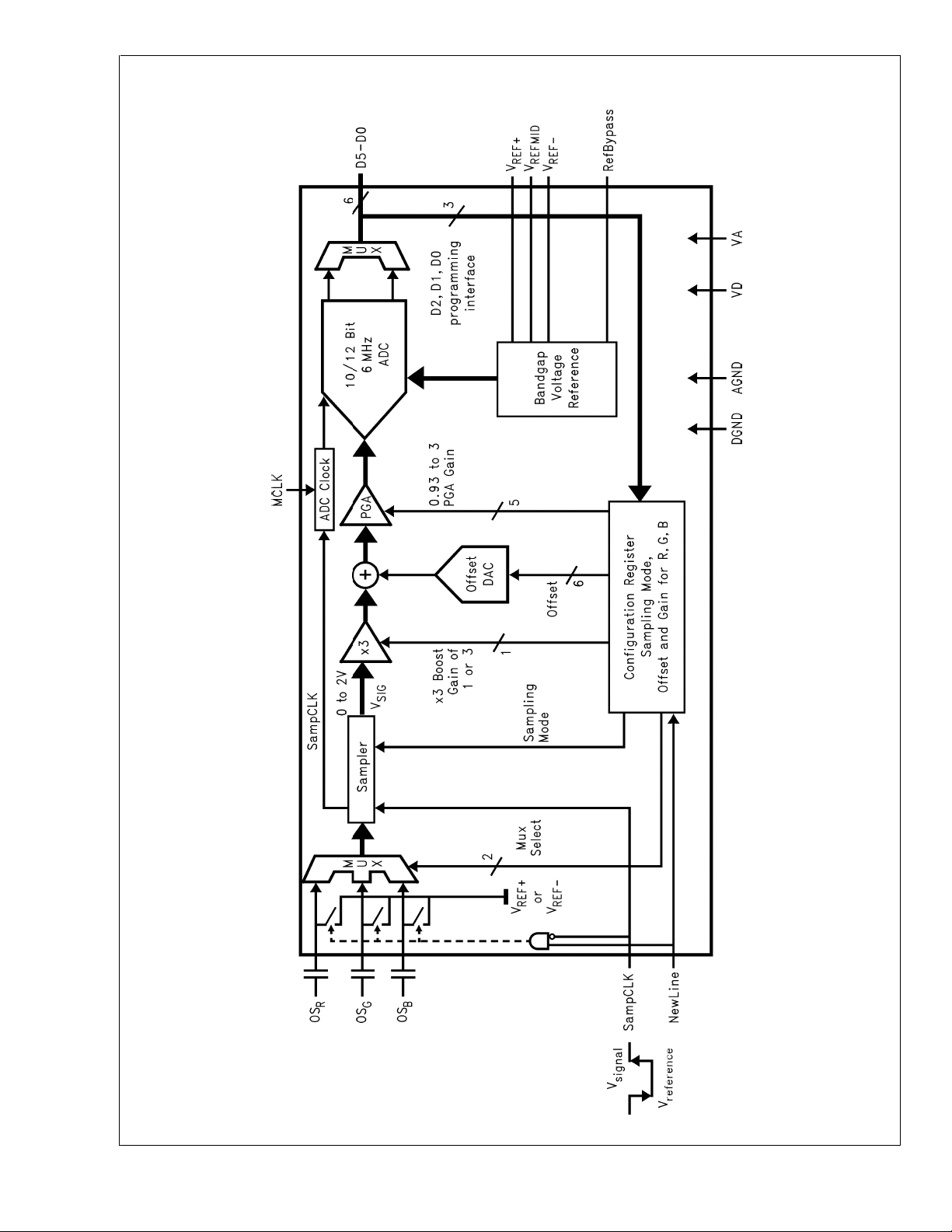

The LM9810 and LM9820 are high performance Analog

Front Ends (AFEs) for image sensor processing systems.

The LM9810/20 performs all the analog and mixed signal

functions (correlated double sampling, color specific gain

and offset correction, and analog to digital conversion) necessary todigitizethe output of a wide variety of CIS and CCD

sensors. The LM9810 has a 10-bit 6 MHz ADC, and the

LM9820 has a 12-bit 6 MHz ADC. The LM9810 and LM9820

are pin-for-pin and functionally compatible.

Key Specifications

n Output Data Resolution 10/12 Bits

n Pixel Conversion Rate 6 MHz

n Supply Voltage 5V

n Power Dissipation 300 mW

±

5%

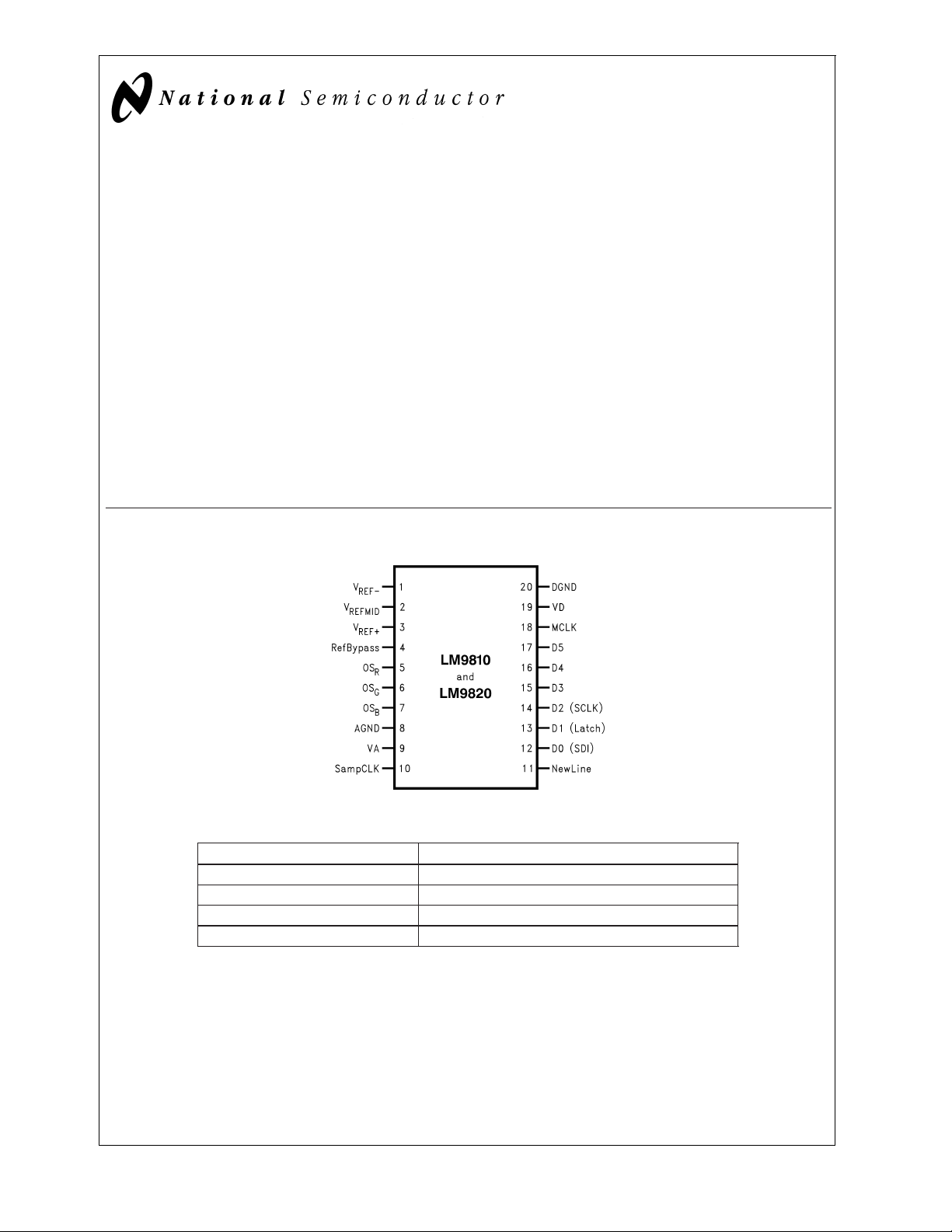

Connection Diagram

Features

n 6 million pixels/s conversion rate

n Digitally programmed gain and offset for red, green and

blue pixels

n Correlated Double Sampling for lowest noise

n TTL/CMOS input/output compatible

Applications

n Color Flatbed Document Scanners

n Color Sheetfed Scanners

n Multifunction Imaging Products

n Digital Copiers

n General Purpose Linear CCD Imaging

DS100943-69

Ordering Information

Commercial (0˚C ≤ TA≤ +70˚C) Package

LM9810CCWM 20-Pin Wide SOIC

LM9810CCWMX 20-Pin Wide SOIC, Tape and Reel

LM9820CCWM 20-Pin Wide SOIC

LM9820CCWMX 20-Pin Wide SOIC, Tape and Reel

© 2000 National Semiconductor Corporation DS100943 www.national.com

Block Diagram

LM9810/20

DS100943-70

www.national.com 2

LM9810/20

Absolute Maximum Ratings (Notes 1, 2)

Positive Supply Voltage (V

with Respect to

GND = AGND = DGND 6.5V

Voltage on any Input or Output Pin 0.3V to V

Input Current at any Pin (Note 3)

Package Input Current (Note 3)

Package Dissipation at T

ESD Susceptibility (Note 5)

Human Body Model 2000V

+

=VA=VD)

+

±

25 mA

±

50 mA

= 25˚C (Note 4)

A

+0.3V

Operating Ratings (Notes 1, 2)

Operating Temperature

Range T

Supply Voltage +4.75V to +5.25V

V

A

Supply Voltage +4.75V to +5.25V

V

D

| ≤ 100 mV

|V

A–VD

,OSG,OS

OS

R

B

Input Voltage Range −0.05V to VA+ 0.05V

NewLine, SampCLK, D0-D2, MCLK

Input Voltage Range −0.05V to V

= 0˚C ≤ TA≤ T

MIN

MAX

+ 0.05V

D

+70˚C

Soldering Information (Note 6)

Infrared, 10 seconds 300˚C

Storage Temperature −65˚C to +150˚C

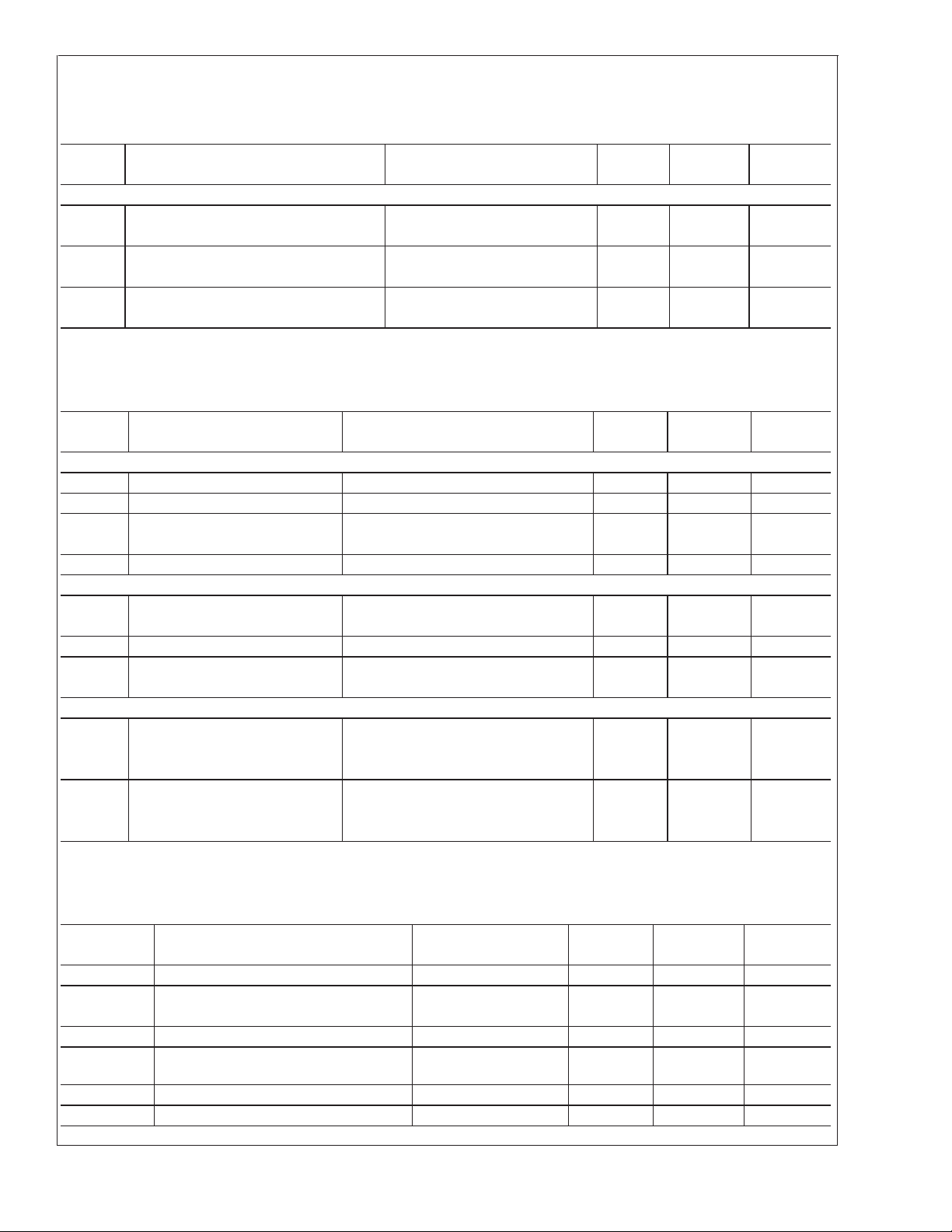

Electrical Characteristics

The following specifications apply for AGND = DGND = 0V, VA=VD= +5.0VDC,f

apply for TA=TJ=T

MIN

to T

; all other limits TA=TJ= 25˚C. (Notes 7, 8, 12)

MAX

Symbol Parameter Conditions Typical Limits Units

CCD/CIS SOURCE REQUIREMENTS FOR FULL SPECIFIED ACCURACY AND DYNAMIC RANGE (Note 12)

V

OS PEAK

Sensor’s Maximum Peak Differential Gain = 0.933 2.1 V

Signal Range Gain = 3.0 0.65 V

Gain = 9.0 0.21 V

ANALOG INPUT CHARACTERISTICS

OS

,OSG,OSBInput Capacitance 5 pF

R

OS

,OSG,OSBInput Leakage Measured with OS = 3.5 V

R

DC

Current CDS disabled, selected OS Input

CDS disabled, unselected OS Input 10 nA

COARSE COLOR BALANCE PGA CHARACTERISTICS

Monotonicity 5 bits (min)

G

(Minimum PGA Gain) PGA Setting = 0 0.93 .90 V/V (min)

0

G

(Maximum PGA Gain) PGA Setting = 31 3.0 2.96 V/V (min)

31

x3 Boost Gain x3 Boost Setting On 3.0 2.93 V/V (min)

(bit B5 of Gain Register is set) 3.05 V/V (max)

Gain Error at any Gain (Note 13)

INTERNAL REFERENCE CHARACTERISTICS

V

REFMID

V

REF+

V

REF

∆V

REF

Mid Supply Output Voltage 2.5 V

Positive Reference Output Voltage 3.5 V

Negative Reference Output Voltage 1.5 V

Differential Reference Voltage 2.0 V

V

REF+-VREF-

= 24 MHz, RS=25Ω.Boldface limits

MCLK

(Note 9) (Note 10) (Limits)

20 25 µA (max)

.96 V/V (max)

3.15 V/V (max)

±

0.4 1.67 % (max)

LM9810 Electrical Characteristics

The following specifications apply for AGND = DGND = 0V, VA=VD= +5.0VDC,f

apply for TA=TJ=T

(Notes 7, 8, 12)

MIN

to T

; all other limits TA=TJ= 25˚C. All LSB limits are in units of the LM9810’s 10-bit ADC.

MAX

Symbol Parameter Conditions Typical Limits Units

ADC CHARACTERISTICS

Resolution with No Missing Codes 10 bits (min)

INL Integral Non-Linearity Error (Note 11)

= 24 MHz, RS=25Ω.Boldface limits

MCLK

(Note 9) (Note 10) (Limits)

±

0.35

±

1.5 LSB (max)

www.national.com3

LM9810 Electrical Characteristics (Continued)

The following specifications apply for AGND = DGND = 0V, VA=VD= +5.0VDC,f

apply for TA=TJ=T

LM9810/20

(Notes 7, 8, 12)

MIN

to T

; all other limits TA=TJ= 25˚C. All LSB limits are in units of the LM9810’s 10-bit ADC.

MAX

Symbol Parameter Conditions Typical Limits Units

ADC CHARACTERISTICS

DNL Differential Non-Linearity

FULL CHANNEL LINEARITY (Note 14)

INL Integral Non-Linearity Error (Note 11)

DNL Differential Non-Linearity

STATIC OFFSET DAC CHARACTERISTICS

Monotonicity 6 bits (min)

Offset DAC LSB Size PGA Gain = 1 5 3.4 LSB (min)

Offset DAC Adjustment Range PGA Gain = 1

SYSTEM CHARACTERISTICS (SEE SECTION 1.7.1, INTERNAL OFFSETS)

C Analog Channel Gain Constant Includes Voltage Reference 502 468 LSB (min)

(ADC Codes/V) Variation, Gain Setting = 1 532 LSB (max)

V

OS1

Pre-Boost Analog Channel Offset Error, 4.4 -7.2 LSB (min)

CCD Mode +15.7 LSB (max)

V

OS1

Pre-Boost Analog Channel Offset Error, 4.5 -6.5 LSB (min)

CIS Mode +15.2 LSB (max)

V

OS2

V

OS3

Pre-PGA Analog Channel Offset Error -10 -28 LSB (min)

Post-PGA Analog Channel Offset Error -11 -30.6 LSB (min)

= 24 MHz, RS=25Ω.Boldface limits

MCLK

(Note 9) (Note 10) (Limits)

±

0.25

±

0.9 LSB

±

0.40 LSB

±

1.0 LSB (max)

6.4 LSB(max)

±

150

±

140 LSB (min)

+5.3 LSB (max)

+7.3 LSB (max)

LM9820 Electrical Characteristics

The following specifications apply for AGND = DGND = 0V, VA=VD= +5.0VDC,f

apply for TA=TJ=T

(Notes 7, 8, 12)

MIN

to T

; all other limits TA=TJ= 25˚C. All LSB limits are in units of the LM9810’s 12-bit ADC.

MAX

Symbol Parameter Conditions Typical Limits Units

ADC CHARACTERISTICS

Resolution with No Missing Codes 12 bits (min)

INL Integral Non-Linearity Error (Note 11)

DNL Differential Non-Linearity

FULL CHANNEL LINEARITY (Note 14)

INL Integral Non-Linearity Error (Note 11)

DNL Differential Non-Linearity

STATIC OFFSET DAC CHARACTERISTICS

Monotonicity 6 bits (min)

Offset DAC LSB Size PGA Gain = 1 20 14 LSB (min)

Offset DAC Adjustment Range PGA Gain = 1

SYSTEM CHARACTERISTICS (SEE SECTION 1.7.1, INTERNAL OFFSETS)

C Analog Channel Gain Constant Includes Voltage Reference 2008 1873 LSB (min)

(ADC Codes/V) Variation, Gain Setting = 1 2129 LSB (max)

V

OS1

Pre-Boost Analog Channel Offset Error, 17.6 -32.1 LSB (min)

CCD Mode +68.9 LSB (max)

= 24 MHz, RS=25Ω.Boldface limits

MCLK

(Note 9) (Note 10) (Limits)

±

1.1

±

0.6 +1.75 LSB (max)

±

4.0 LSB (max)

-1.0

±

3.4 LSB

±

0.65 LSB

26 LSB(max)

±

590

±

575 LSB (min)

www.national.com 4

LM9820 Electrical Characteristics (Continued)

The following specifications apply for AGND = DGND = 0V, VA=VD= +5.0VDC,f

apply for TA=TJ=T

(Notes 7, 8, 12)

MIN

to T

; all other limits TA=TJ= 25˚C. All LSB limits are in units of the LM9810’s 12-bit ADC.

MAX

Symbol Parameter Conditions Typical Limits Units

SYSTEM CHARACTERISTICS (SEE SECTION 1.7.1, INTERNAL OFFSETS)

V

OS1

Pre-Boost Analog Channel Offset Error, 18 -22.2 LSB (min)

CIS Mode +57 LSB (max)

V

OS2

V

OS3

Pre-PGA Analog Channel Offset Error -40 -94.3 LSB (min)

Post-PGA Analog Channel Offset Error -44 -121 LSB (min)

= 24 MHz, RS=25Ω.Boldface limits

MCLK

(Note 9) (Note 10) (Limits)

+16.4 LSB (max)

+28 LSB (max)

DC and Logic Electrical Characteristics

The following specifications apply for AGND = DGND = 0V, VA=VD= +5.0VDC,f

apply for TA=TJ=T

MIN

to T

; all other limits TA=TJ= 25˚C. (Notes 7, 8)

MAX

Symbol Parameter Conditions Typical Limits Units

D0–D2, MCLK, NewLine, SampCLK DIGITAL INPUT CHARACTERISTICS

V

IN(1)

V

IN(0)

I

IN

C

IN

Logical “1” Input Voltage VD= 5.25V 2.0 V (max)

Logical “0” Input Voltage VD= 4.75V 0.8 V (min)

Input Leakage Current VIN=V

D

V

= DGND −0.1 µA (max)

IN

Input Capacitance 5 pF

D0–D5, DIGITAL OUTPUT CHARACTERISTICS

V

V

I

OUT

OUT(1)

OUT(0)

Logical “1” Output Voltage VD= 4.75V, I

V

= 4.75V, I

D

Logical “0” Output Voltage VD= 5.25V, I

TRI-STATE®Output Current V

(D0–D5 only) V

= DGND 0.1 µA

OUT

OUT=VD

= −360 µA 2.4 V (min)

OUT

= −10 µA 4.4 V (min)

OUT

= 1.6 mA 0.4 V (max)

OUT

POWER SUPPLY CHARACTERISTICS

I

A

Analog Supply Current Operating 45 57 mA (max)

Standby with Input Clocks Stopped 0.8 0.9 mA (max)

Standby with Input Clocks Running 3.0 mA

I

D

Digital Supply Current (Note 15) Operating 220 320 µA (max)

Standby with Input Clocks Stopped 110 200 µA (max)

Standby with Input Clocks Running 220 µA

= 24 MHz, Rs=25Ω.Boldface limits

MCLK

(Note 9) (Note 10) (Limits)

0.1 µA (max)

−0.1 µA

LM9810/20

AC Electrical Characteristics

The following specifications apply for AGND = DGND = 0V, VA=VD= +5.0VDC,f

tr=tf= 5 ns, Rs=25Ω.Boldface limits apply for TA=TJ=T

MIN

to T

; all other limits TA=TJ= 25˚C. (Notes 7, 8)

MAX

Symbol Parameter Conditions Typical Limits Units

f

MCLK

Maximum MCLK Frequency 24 MHz (min)

MCLK Duty Cycle 40

t

MCLK

t

SCNL

MCLK Period 41 ns (min)

SampCLK Falling Edge before NewLine

Falling Edge

t

SampCLK

t

SampLo

SampCLK Period 4 t

Low Time for SampCLK 50 ns (min)

MCLK

= 24 MHz, t

MCLK

= 1/f

MCLK

(Note 9) (Note 10) (Limits)

60

3 t

,

MCLK

MCLK

www.national.com5

(min)

(max)

(min)

(min)

AC Electrical Characteristics (Continued)

The following specifications apply for AGND = DGND = 0V, VA=VD= +5.0VDC,f

tr=tf= 5 ns, Rs=25Ω.Boldface limits apply for TA=TJ=T

LM9810/20

Symbol Parameter Conditions Typical Limits Units

t

SampHi

t

SampSU

High Time for SampCLK 50 ns (min)

SampCLK Falling Edge before Rising

MIN

to T

; all other limits TA=TJ= 25˚C. (Notes 7, 8)

MAX

Edge of MCLK

t

DDO

Falling Edge of MCLK before New Valid

Data

t

HDO

Hold Time of Current Data from Falling

edge of MCLK

f

SCLK

t

DSU

D2(SCLK) Serial Clock Period 1 t

Input Data Setup Time before

D2(SCLK) Rising Edge

t

DH

Input Data Hold Time after

D2(SCLK) Rising Edge

t

SCLKLA

D2(SCLK) Rising Edge after Bit B0

before D1(Latch) Rising Edge

t

LASCLK

D1(Latch) Rising Edge before next

D2(SCLK) Rising Edge

t

LA

t

LANL

High Time for D1(Latch) 3 t

D1(Latch) Rising Edge before 3 t

NewLine Falling Edge (min)

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is

functional, but do not guarantee specific performance limits. For guaranteed specifications and test conditions, see the Electrical Characteristics. The guaranteed

specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test

conditions.

Note 2: All voltages are measured with respect to GND = AGND = DGND = 0V, unless otherwise specified.

Note 3: When the input voltage (V

50 mA maximum package input current rating limits the number of pins that can simultaneously safely exceed the power supplies with an input current of 25mAto

two.

Note 4: The maximum power dissipation must be derated at elevated temperatures and is dictated by T

allowable power dissipation at any temperature is P

mounted is 84˚C/W for the M20 SOIC package.

Note 5: Human body model, 100 pF capacitor discharged through a 1.5 kΩ resistor.

Note 6: SeeAN450 “Surface Mounting Methods and Their Effect on Product Reliability” or the section titled “Surface Mount” found in any National Semiconductor

Linear Data Book for other methods of soldering surface mount devices.

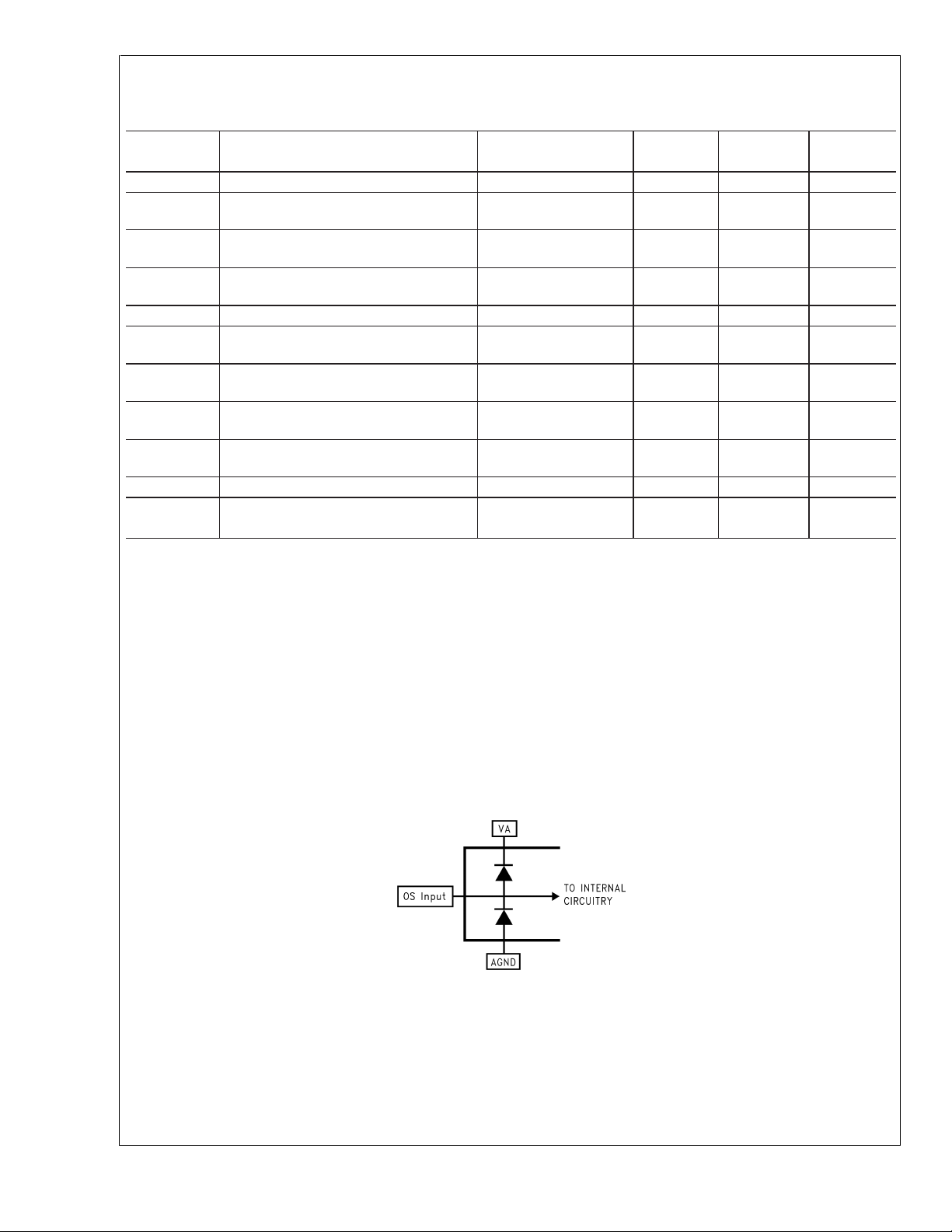

Note 7: Two diodes clamp the OS analog inputs to AGND and V

output impedance of the sensor, prevents damage to the LM9810/20 from transients during power-up.

) at any pin exceeds the power supplies (V

IN

D

=(T

)/θJA.T

Jmax–TA

as shown below. This input protection, in combination with the external clamp capacitor and the

A

<

GND or VINVAor VD), the current at that pin should be limited to 25 mA. The

IN

= 150˚C for this device. The typical thermal resistance (θJA) of this part when board

Jmax

MCLK

= 24 MHz, t

MCLK

= 1/f

MCLK

,

(Note 9) (Note 10) (Limits)

4 ns (min)

40 ns (max)

15 ns (min)

0 ns (min)

3 ns (min)

3 ns (min)

3 ns (min)

, θJAand the ambient temperature, TA. The maximum

Jmax

MCLK

MCLK

SampCLK

(min)

(min)

DS100943-71

Note 8: To guarantee accuracy, it is required that V

Note 9: Typicals are at T

Note 10: Tested limits are guaranteed to National’s AOQL (Average Outgoing Quality Level).

Note 11: Integral non-linearity error is defined as the deviation of the analog value, expressed in LSBs, from the straight line that best fits the actual transfer function

of the ADC.

Note 12: V

voltage for a white (full scale) image with respect to the reference level, V

pulse. The maximum correctable range of pixel-to-pixel V

variation, optics, etc.) that the LM9810/20 can correct for using its internal PGA.

is defined as the CCD OS voltage for the reference period following the reset feedthrough pulse. V

REF

J=TA

= 25˚C, f

MCLK

and VDbe connected together to the same power supply with separate bypass capacitors at each supply pin.

A

= 24 MHz, and represent most likely parametric norm.

is defined as the peak CCD pixel output

REF.VRFT

variation is defined as the maximum variation in V

WHITE

is defined as the peak positive deviation above V

WHITE

(due to PRNU, light source intensity

WHITE

of the reset feedthrough

REF

www.national.com 6

Loading...

Loading...