NSC LM5070, LM5070SDX-80 Datasheet

LM5070

Integrated Power Over Ethernet PD Interface and PWM

Controller

General Description

The LM5070 power interface port and pulse width modulation (PWM) controller provides a complete integrated solution for Powered Devices (PD) that connect into Power over

Ethernet (PoE) systems. The LM5070 integrates an 80V,

400mA line connection switch and associated control for a

fully IEEE 802.3af compliant interface with a full featured

current mode pulse width modulator dc-dc converter. All

power sequencing requirements between the controller interface and switch mode power supply (SMPS) are integrated into the IC. Two options are available providing either

an 80% maximum duty cycle limit with slope compensation

(on the –80 suffix) device or a 50% maximum duty cycle limit

and no slope compensation on the (– 50 suffix) device.

Features

n Fully Compliant 802.3af Power Interface Port

n 80V, 1Ω, 400 mA Internal MOSFET

n Programmable Inrush Current Limit

n Detection Resistor Disconnect Function

n Programmable Classification Current

n Programmable Under-voltage Lockout with

Programmable Hysteresis

n Thermal Shutdown Protection

n Current Mode Pulse Width Modulator

n Supports both Isolated and Non-Isolated Applications

n Error Amplifier and Reference for Non-Isolated

Applications

n Programmable Oscillator Frequency

n Programmable Soft-start

n 80% Maximum Duty Cycle Limiter, Slope Compensation

(-80 device)

n 50% Maximum Duty Cycle Limiter, No Slope

Compensation (-50 device)

n 800 mA Peak Gate Driver

Packages

n TSSOP-16

n LLP-16 (5 mmx5mm)

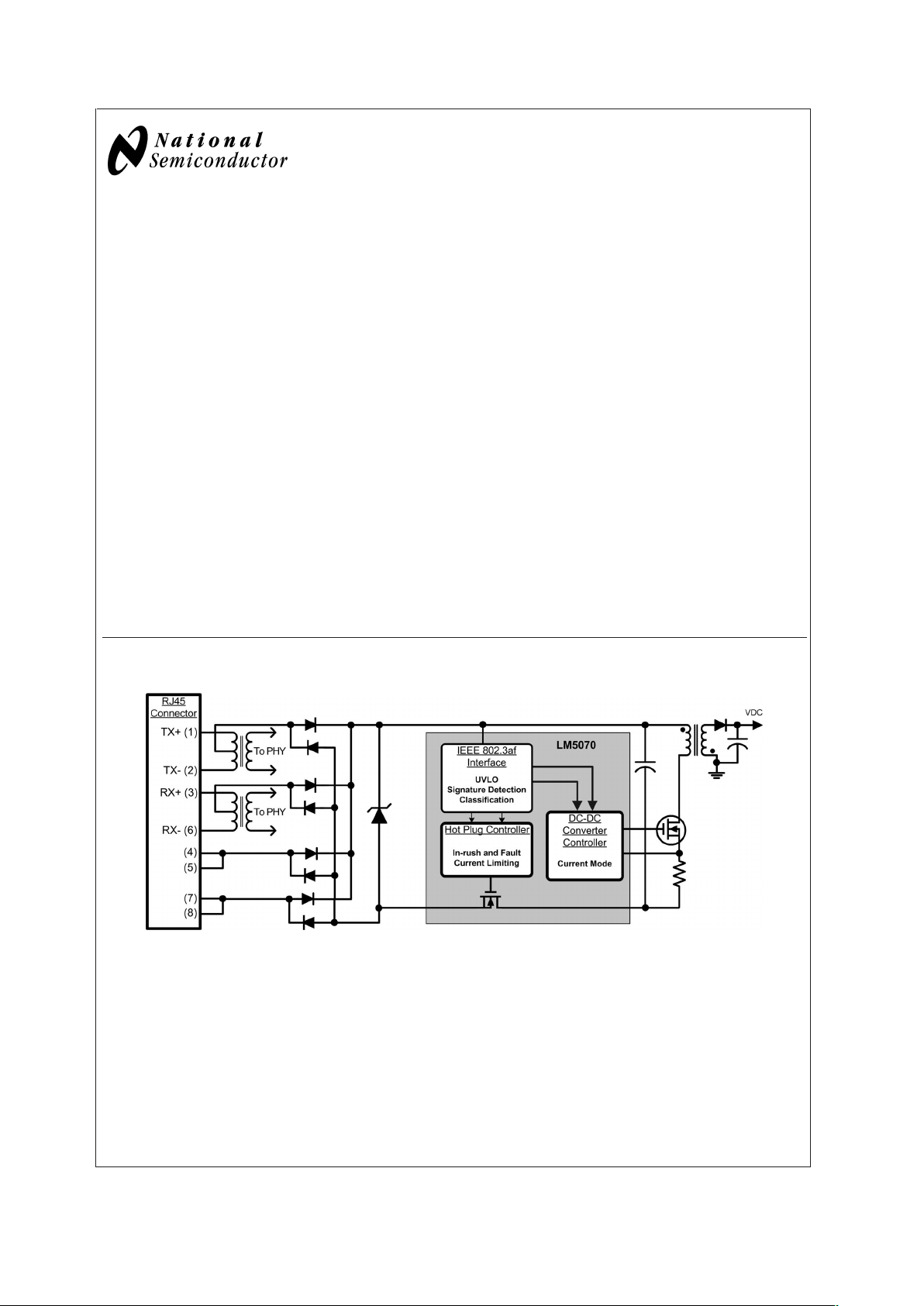

Block Diagrams

20120001

April 2006

LM5070 Integrated Power Over Ethernet PD Interface and PWM Controller

© 2006 National Semiconductor Corporation DS201200 www.national.com

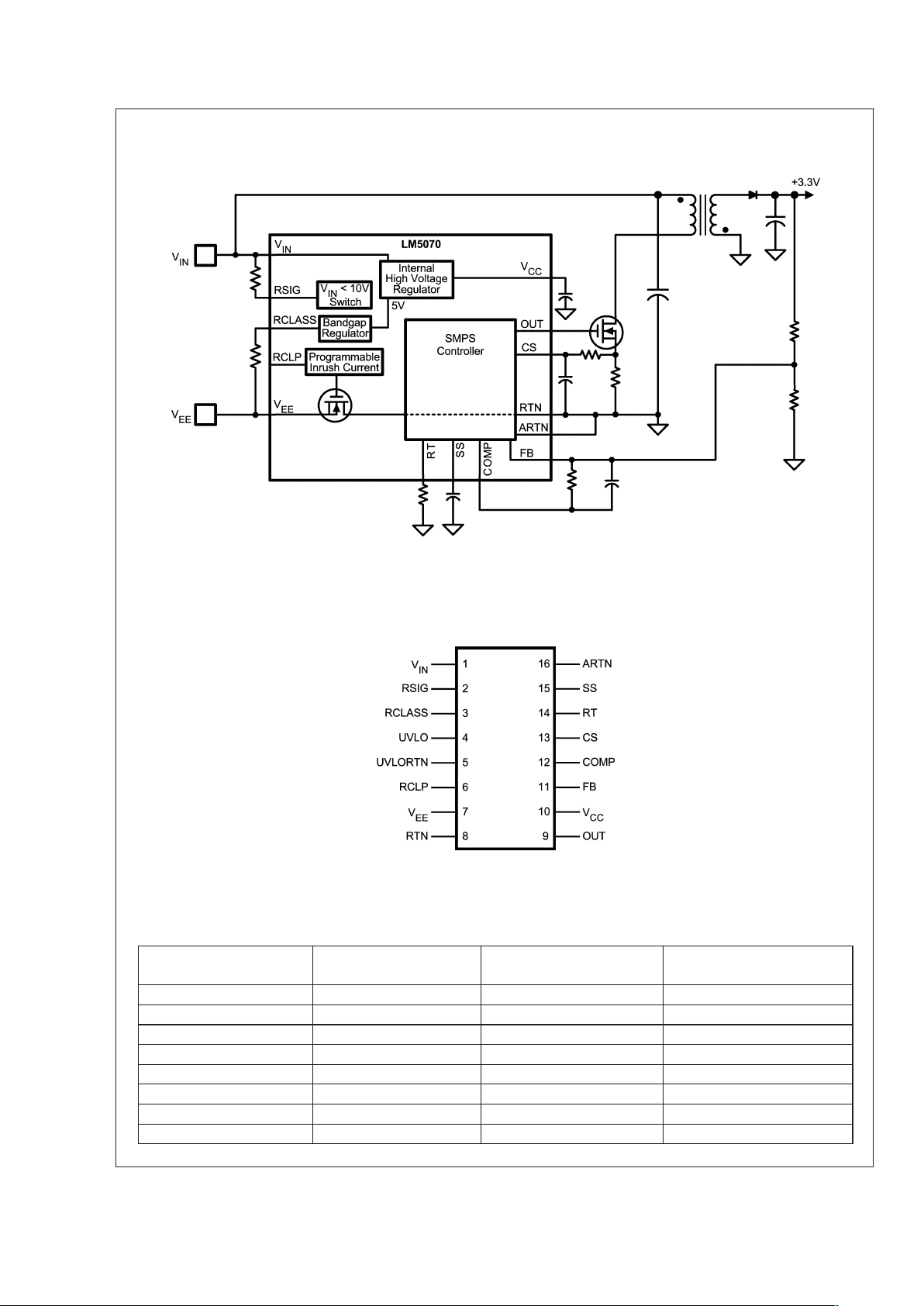

Block Diagrams (Continued)

Connection Diagram

20120003

16 Lead TSSOP, LLP

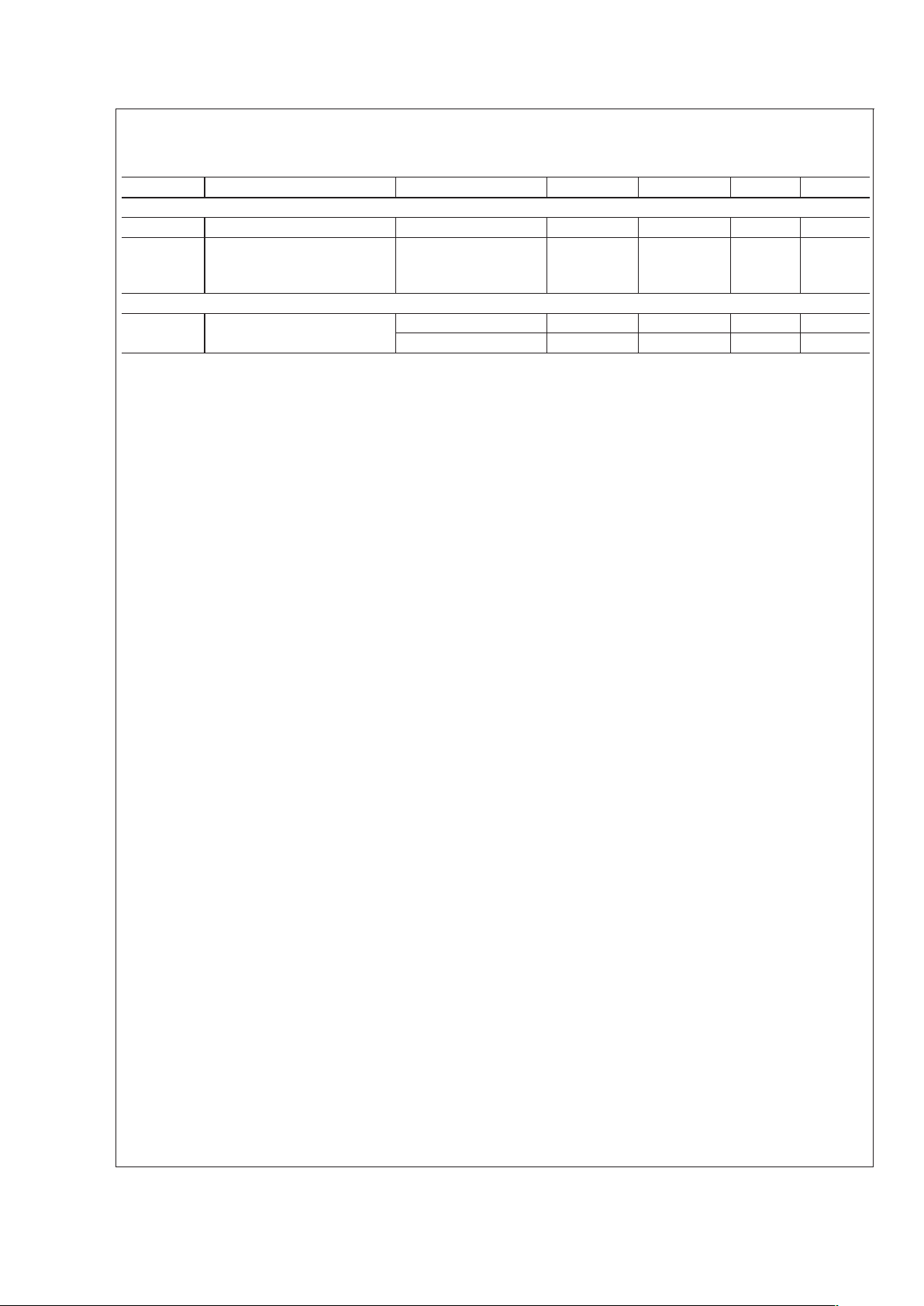

Ordering Information

Order Number Description

NSC Package Type /

Drawing Supplied As

LM5070MTC-50 50% Duty Cycle Limit TSSOP-16/MTC-16 92 units per rail

LM5070MTCX-50 50% Duty Cycle Limit TSSOP-16/MTC-16 2500 units on tape and reel

LM5070SD-50 50% Duty Cycle Limit LLP-16/SDA-16 1000 units on tape and reel

LM5070SDX-50 50% Duty Cycle Limit LLP-16/SDA-16 4500 units on tape and reel

LM5070MTC-80 80% Duty Cycle Limit TSSOP-16/MTC-16 92 units per rail

LM5070MTCX-80 80% Duty Cycle Limit TSSOP-16/MTC-16 2500 units on tape and reel

LM5070SD-80 80% Duty Cycle Limit LLP-16/SDA-16 1000 units on tape and reel

LM5070SDX-80 80% Duty Cycle Limit LLP-16/SDA-16 4500 units on tape and reel

20120002

FIGURE 1. Simplified Block Diagram

LM5070

www.national.com 2

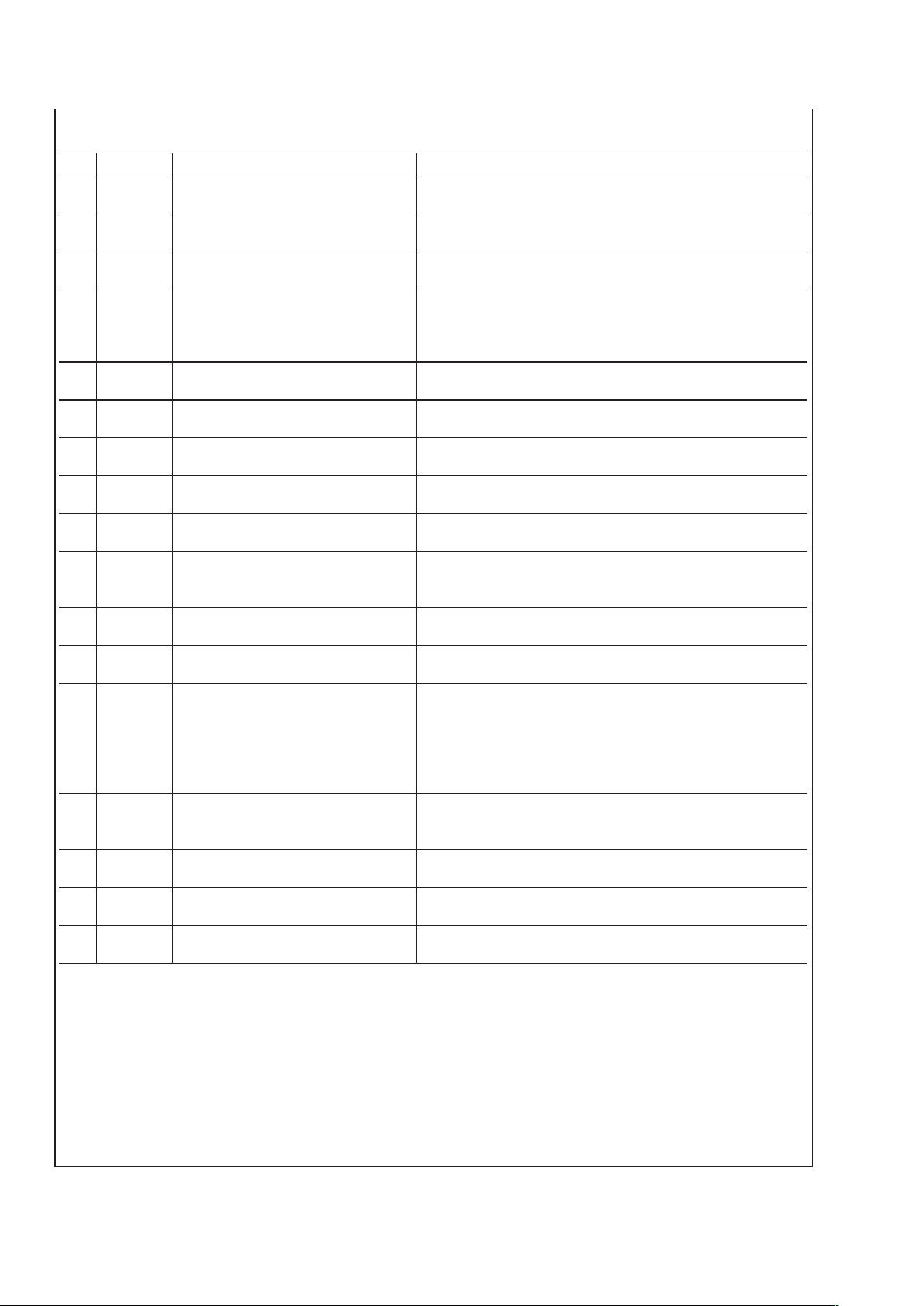

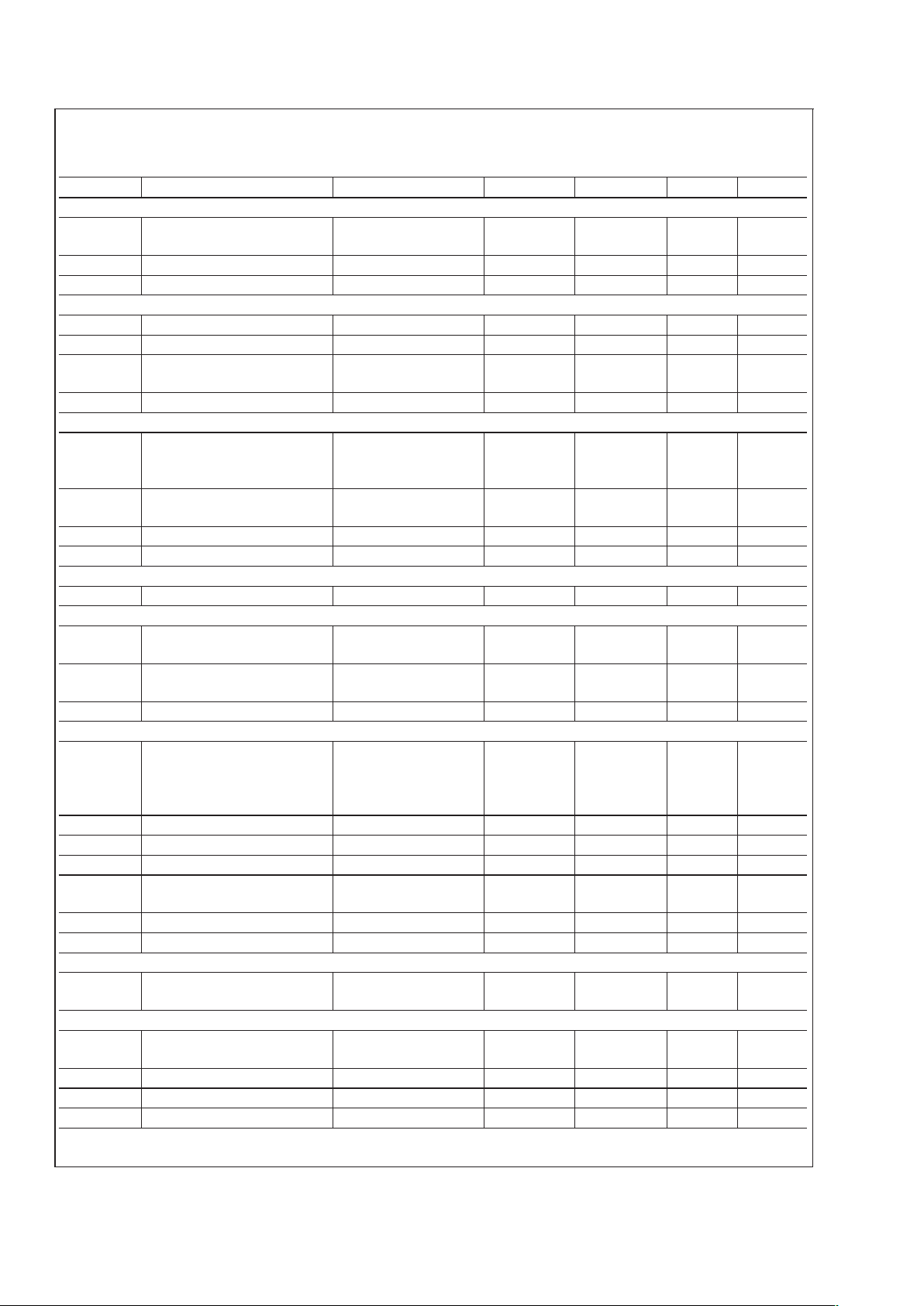

Pin Descriptions

Pin Name Description Application Information

1V

IN

System high potential input. The diode “OR” of several lines entering the PD, it is the more

positive input potential.

2 RSIG Signature resistor pin. Connect a 25kΩ signature resistor from V

IN

to this pin for signature

detection.

3 RCLASS Classification resistor pin. Connect the classification programming resistor from this pin to

V

EE

.

4 UVLO Line under-voltage lockout. An external resistor divider from V

IN

to UVLORTN programs the

shutdown levels with a 2.00V threshold at the UVLO pin.

Hysteresis is set by a switched internal 10uA current source that

forces additional current into the resistor divider.

5 UVLORTN Return for the external UVLO resistors. Connect the bottom resistor of the resistor divider between the

UVLO pin and this pin.

6 RCLP Current limit programming pin. Programs the inrush current limit for the device. If left open, the

inrush current limit will default to 400mA max.

7V

EE

System low potential input. Diode “OR’d” to the RJ45 connector and PSE’s – 48V supply, it is

the more negative input potential.

8 RTN System return for the PWM converter. The drain of the internal current limiting power MOSFET which

connects V

EE

to the return path of the dc-dc converter.

9 OUT Output of the PWM controller. DC-DC converter gate driver output with 800mA peak sink current

capability.

10 V

CC

Output of the internal high voltage series

pass regulator. Regulated output voltage

is nominally 7.8V.

When the auxiliary transformer winding (if used) raises the voltage

on this pin above the regulation set point, the internal series pass

regulator will shutdown, reducing the controller power dissipation.

11 FB Feedback signal. Inverting input of the internal error amplifier. The non-inverting

input is internally connected to a 1.25V reference.

12 COMP The output of the error amplifier and

input to the Pulse Width Modulator.

COMP pull-up is provided by an internal 5K resistor which may be

used to bias an opto-coupler transistor.

13 CS Current sense input. Current sense input for current mode control and over-current

protection. Current limiting is accomplished using a dedicated

current sense comparator. If the CS pin voltage exceeds 0.5V the

OUT pin switches low for cycle-by-cycle current limiting. CS is held

low for 50ns after OUT switches high to blank leading edge current

spikes.

14 RT / SYNC Oscillator timing resistor pin and

synchronization input.

An external resistor connected from RT to ARTN sets the oscillator

frequency. This pin will also accept narrow ac-coupled

synchronization pulses from an external clock.

15 SS Soft-start input. An external capacitor and an internal 10uA current source set the

soft-start ramp rate.

16 ARTN Analog PWM supply return. RTN for sensitive analog circuitry including the SMPS current limit

amplifier.

— EP Exposed PAD, underside of the LLP

package option.

Internally bonded to the die substrate. Connect to V

EE

potential for

low thermal impedance.

LM5070

www.national.com3

Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required,

please contact the National Semiconductor Sales Office/

Distributors for availability and specifications.

V

IN

,RTN to V

EE

-0.3V to 80V

RSIG to V

IN

-12V to 0V

UVLO to V

EE

-0.3V to 57V

UVLORTN -0.3V to 13V

RCLASS, RCLP to V

EE

-0.3V to 7V

ARTN to RTN -0.3V to 0.3V

V

CC

, OUT to ARTN -0.3V to 16V

All other inputs to ARTN -0.3V to 7V

ESD Rating

Human Body Model 2000V

Storage Temperature -65˚C to +150˚C

Junction Temperature 150˚C

Lead Temperature (Note 2)

Wave (4 seconds)

Infrared (10 seconds)

Vapor Phase (75 seconds)

260˚C

240˚C

219˚C

Operating Ratings

VINvoltage 1.8V to 75V

External voltage applied to V

CC

8.1V to 15V

Operating Junction Temperature -40˚C to +125˚C

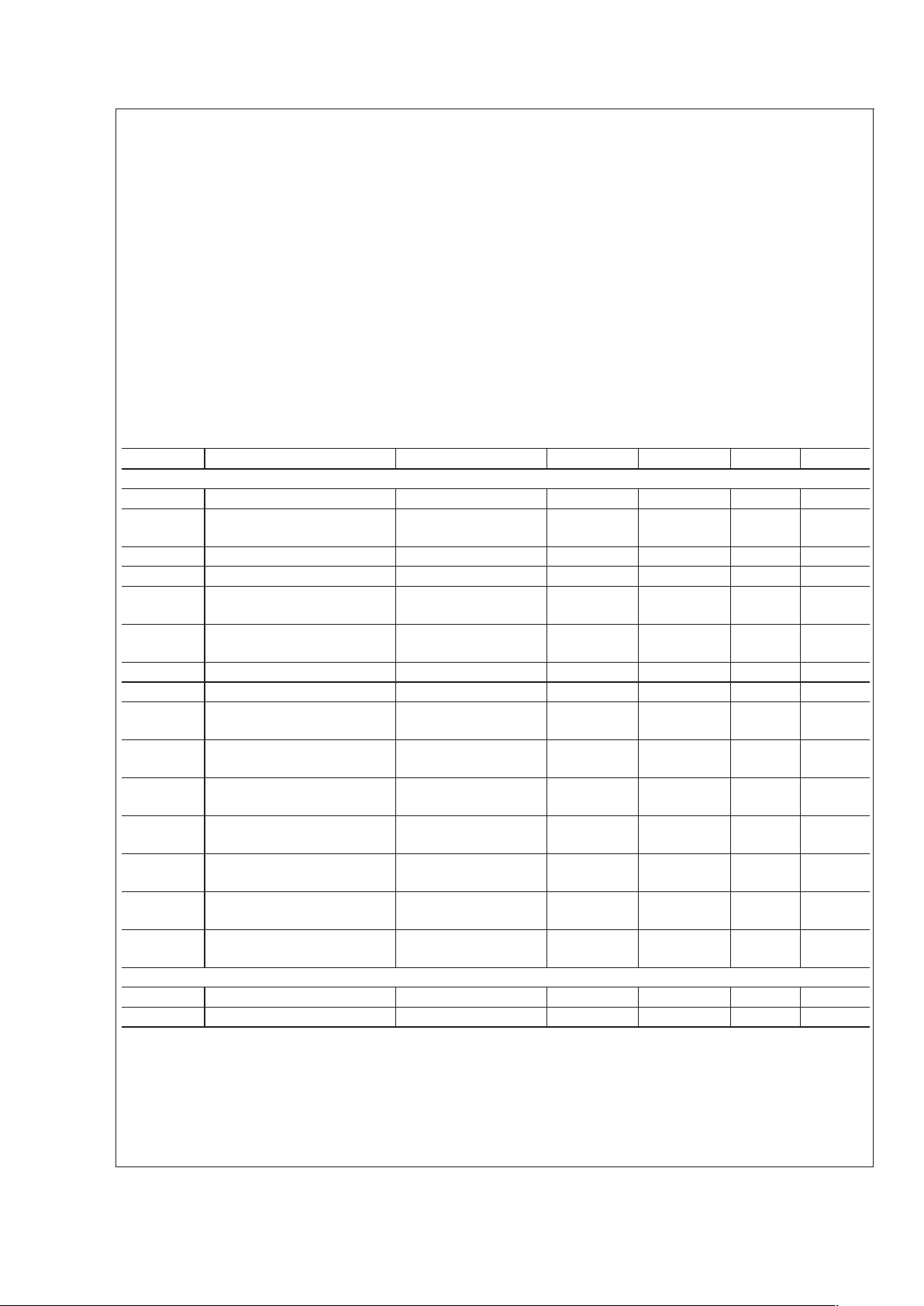

Electrical Characteristics (Note 3)

Specifications in standard type face are for TJ= +25˚C and those in boldface type apply over the full operating junction temperature range. Unless otherwise specified: V

IN

= 48V, VCC= 10V, RT = 30.3kΩ.

Symbol Parameter Conditions Min Typ Max Units

Powered Interface

IOS Offset Current V

IN

<

10.0V 10 uA

VCLSS(ON) Signature Resistor Disable /

Classification Current Turn On

V

IN

with respect to V

EE

10.0 11.5 12.5 V

VCLSS(OFF) Classification Current Turn Off VINwith respect to V

EE

20.5 22.0 23.0 V

Classification Voltage With respect to V

EE

1.43 1.5 1.57 V

ICLASS Supply Current During

Classification

V

IN

=17V 0.5 1.0 mA

IDC Supply Current During Normal

Operation

OUT floating 1 1.9 mA

UVLO Pin Reference Voltage V

IN

>

12V 1.95 2.00 2.05 V

UVLO Hysteresis Current V

IN

>

UVLO 8.0 10 11.5 uA

Softstart Release RTN falling with respect

to V

EE

1.2 1.45 1.7 V

Softstart Release Hysteresis RTN rising with respect

to V

EE

0.8 1.1 1.3 V

RDS(ON) PowerFET Resistance I = 350mA,

V

IN

= 48V

1 2.2 Ω

ILEAK SMPS Bias Current V

EE

= 0V, VIN= RTN =

57V

100 uA

ILIM Default Current Limit V

EE

= 0V, RTN = 3.0V,

Temp = 0˚C to 85˚C

350 390 420 mA

ILIM Default Current Limit V

EE

= 0V, RTN = 3.0V,

Temp = -40˚C to 125˚C

325 390 420 mA

Current Limit Programming

Accuracy

VEE= 0V, RTN = 3.0V,

RCLP = 80.6kΩ

-20 +20 %

Startup Regulator

VccReg V

CC

Regulation Open ckt 7.5 7.8 8.1 V

V

CC

Current Limit (Note 4) 15 20 mA

LM5070

www.national.com 4

Electrical Characteristics (Note 3) (Continued)

Specifications in standard type face are for TJ= +25˚C and those in boldface type apply over the full operating junction temperature range. Unless otherwise specified: V

IN

= 48V, VCC= 10V, RT = 30.3kΩ.

Symbol Parameter Conditions Min Typ Max Units

V

CC

Supply

V

CC

UVLO (Rising) VccReg –

300mV

VccReg –

100mV

V

CC

UVLO (Falling) 5.9 6.25 6.6 V

Supply Current (Icc) Cload = 0 1.5 3 mA

Error Amplifier

GBW Gain Bandwidth 4 MHz

DC Gain 75 dB

Input Voltage FB = COMP 1.219

1.212

1.281

1.288

V

COMP Sink Capability FB=1.5V COMP=1V 5 20 mA

Current Limit

ILIM Delay to Output CS step from 0 to 0.6V,

time to onset of OUT

transition (90%)

20 ns

Cycle by Cycle Current Limit

Threshold Voltage

0.44 0.5 0.56 V

Leading Edge Blanking Time 55 ns

CS Sink Impedance (clocked) 25 55 Ω

Softstart

Softstart Current Source 7 10 13 uA

Oscillator(Note 5)

Frequency1

(RT = 30.3K)

175 200 225 KHz

Frequency2

(RT = 10.5K)

505 580 665 KHz

Sync threshold 3.1 3.8 V

PWM Comparator

Delay to Output COMP set to 2V

CS stepped 0 to 0.4V,

time to onset of OUT

transition low

25 ns

Min Duty Cycle COMP=0V 0 %

Max Duty Cycle (-80 Device) 80 %

Max Duty Cycle (-50 Device) 50 %

COMP to PWM Comparator

Gain

0.33

COMP Open Circuit Voltage 4.5 5.4 6.3 V

COMP Short Circuit Current COMP= 0V 0.6 1.1 1.5 mA

Slope Compensation

Slope Comp Amplitude

(LM5070-80 Device Only)

Delta increase at PWM

Comparator to CS

105 mV

Output Section

Output High Saturation I

out

= 50mA,

V

CC-VOUT

0.25 0.75 V

Output Low Saturation I

out

= 100mA 0.25 0.75 V

Rise time Cload = 1nF 15 ns

Fall time Cload = 1nF 15 ns

LM5070

www.national.com5

Electrical Characteristics (Note 3) (Continued)

Specifications in standard type face are for TJ= +25˚C and those in boldface type apply over the full operating junction temperature range. Unless otherwise specified: V

IN

= 48V, VCC= 10V, RT = 30.3kΩ.

Symbol Parameter Conditions Min Typ Max Units

Thermal Shutdown

Tsd Thermal Shutdown Temp. 165 ˚C

Thermal

Shutdown

Hysteresis

25 ˚C

Thermal Resistance

θ

JA

Junction to Ambient MTC Package 125 ˚C/W

SDA Package 32 ˚C/W

Note 1: Absolute Maximum Ratings are limits beyond which damage to the device may occur. Operating Ratings are conditions under which operation of the device

is intended to be functional. For guaranteed specifications and test conditions, see the Electrical Characteristics. The absolute maximum rating ofV

IN

, RTN to V

EE

is derated to (-0.3V to 76V) at -40˚C.

Note 2: For detailed information on soldering plastic TSSOP and LLP package, refer to the Packaging Databook available from National Semiconductor.

Note 3: Min and Max limits are 100% production tested at 25 ˚C. Limits over the operating temperature range are guaranteed through correlation using Statistical

Quality Control (SQC) methods. Limits are used to calculate National’s Average Outgoing Quality Level (AOQL).

Note 4: Device thermal limitations may limit usable range.

Note 5: Specification applies to the oscillator frequency. The operational frequency of the LM5070-50 devices is divided by two.

LM5070

www.national.com 6

Loading...

Loading...