TL/H/6750

LM1893/LM2893 Carrier-Current Transceiver

April 1995

LM1893/LM2893 Carrier-Current Transceiver

²

General Description

Carrier-current systems use the power mains to transfer information between remote locations. This bipolar carriercurrent chip performs as a power line interface for half-duplex (bi-directional) communication of serial bit streams of

virtually any coding. In transmission, a sinusoidal carrier is

FSK modulated and impressed on most any power line via a

rugged on-chip driver. In reception, a PLL-based demodulator and impulse noise filter combine to give maximum range.

A complete system may consist of the LM1893, a COPS

TM

controller, and discrete components.

Features

Y

Noise resistant FSK modulation

Y

User-selected impulse noise filtering

Y

Up to 4.8 kBaud data transmission rate

Y

Strings of 0’s or 1’s in data allowed

Y

Sinusoidal line drive for low RFI

Y

Output power easily boosted 10-fold

Y

50 to 300 kHz carrier frequency choice

Y

TTL and MOS compatible digital levels

Y

Regulated voltage to power logic

Y

Drives all conventional power lines

Applications

Y

Energy management systems

Y

Home convenience control

Y

Inter-office communication

Y

Appliance control

Y

Fire alarm systems

Y

Security systems

Y

Telemetry

Y

Computer terminal interface

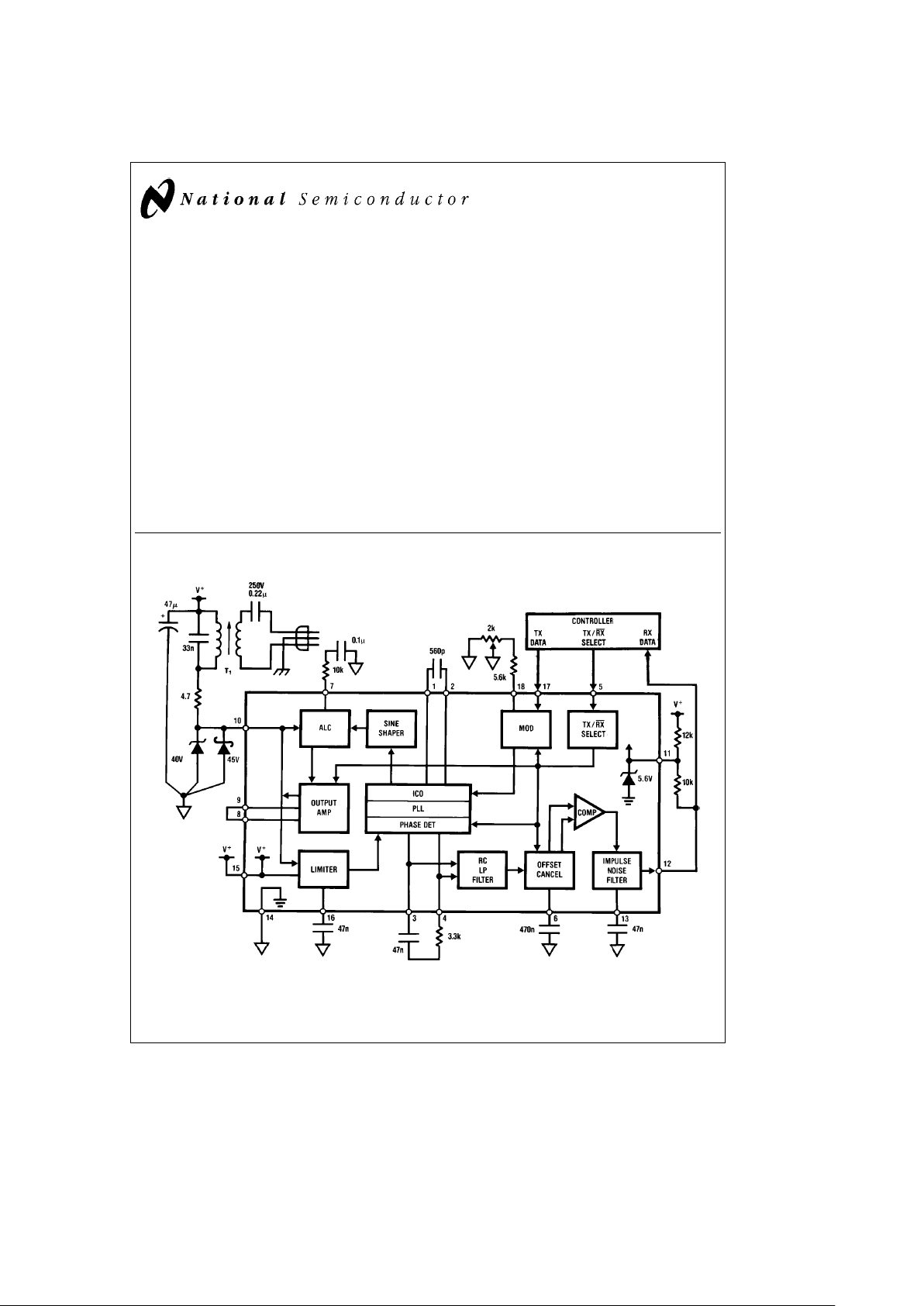

Typical Application

TL/H/6750– 1

FIGURE 1. Block diagram of carrierÐcurrent chip with a complement of discrete components making a complete

F

O

e

125 kHz, f

DATA

e

360 Baud transceiver. Use caution with this circuitÐdangerous line voltage is present.

BI-LINETMand COPSTMare trademarks of National Semiconductor Corp.

²

Carrier-Current Transceivers are also called Power Line Carrier (PLC) transceivers.

C

1995 National Semiconductor Corporation RRD-B30M115/Printed in U. S. A.

Absolute Maximum Ratings

If Military/Aerospace specified devices are required,

please contact the National Semiconductor Sales

Office/Distributors for availability and specifications.

Supply voltage 30 V

Voltage on pin 12 55 V

Voltage on pin 10 (Note 1) 41 V

Voltage on pins 5 and 17 40 V

5.6 V DC zener current 100 mA

Junction temperature: transmit mode 150

§

C

receive mode 125

§

C

Electro-Static Discharge (120 pF, 1500X) 1KV

Maximum continuous dissipation, T

A

e

25§C,

plastic DIP N (Note 2): transmit mode 1.66 W

receive mode 1.33 W

Operating ambient temp. range

b

40 to 85§C

Storage temperature range

b

65 to 150§C

Lead temp., soldering, 7 seconds 260

§

C

Note:

Absolute maximum ratings indicate limits beyond

which damage to the device may occur. Electrical specifications are not ensured when operating the device above

guaranteed limits but below absolute maximum limits, but

there will be no device degradation.

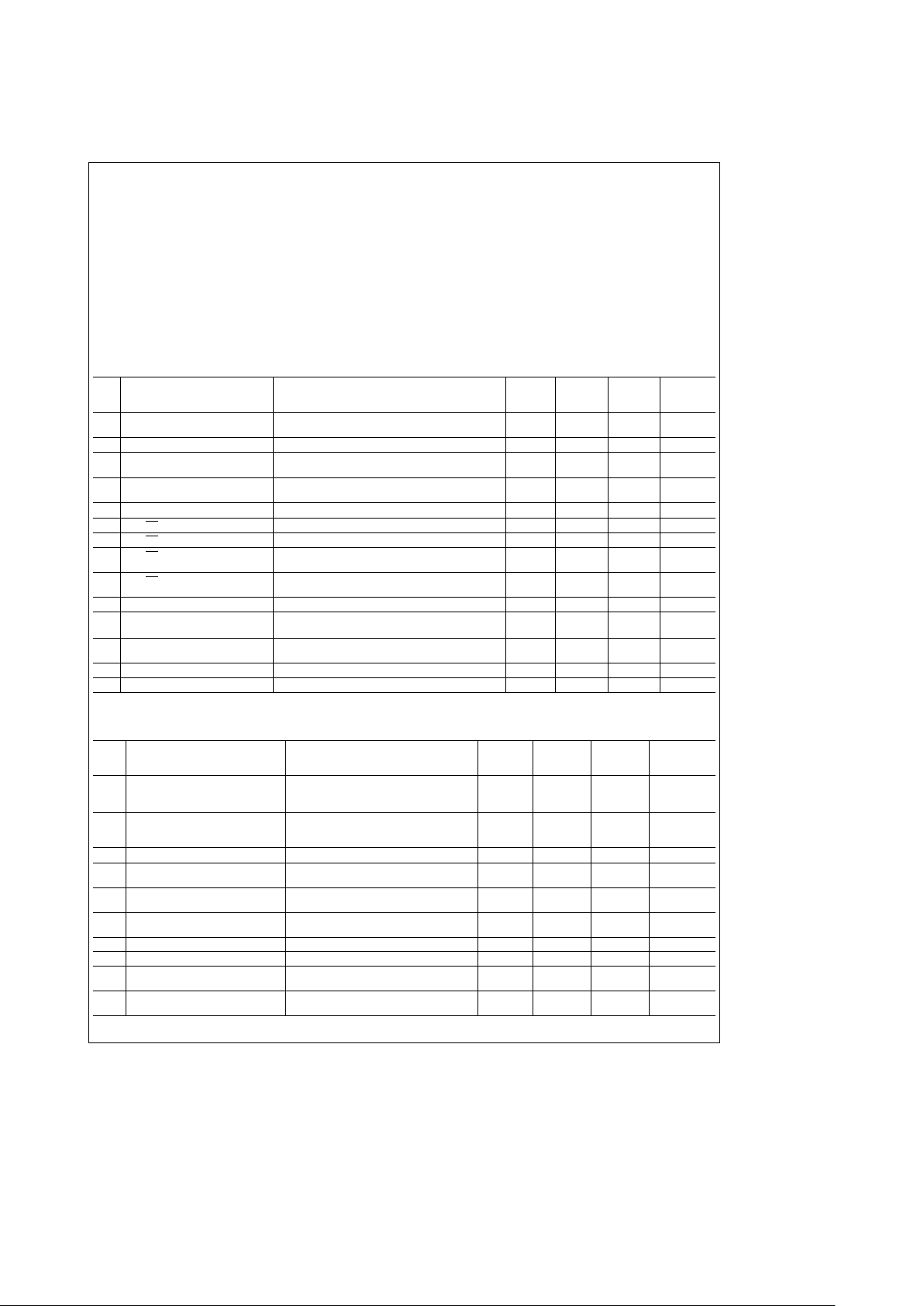

General Electrical Characteristics

(Note 3). The test conditions are: V

a

e

18V and F

O

e

125 kHz, unless otherwise noted.

Test Design

Limit

Ý

Parameter Conditions Typical Limit Limit

Units

(Note 4) (Note 5)

1 5.6 V Zener voltage, V

Z

Pin 11, I

Z

e

2 mA 5.6 5.2 V min.

5.9 V max.

2 5.6 V Zener resistance, R

Z

Pin 11, R

Z

e

(V

Z

@

10 mAbV

Z

@

1 mA)/(10 mAb1 mA) 5 X

3 Carrier I/O peak survivable Pin 10, discharge 1 mF cap. charged to V

OT

80 60 V max.

transient voltage, V

OT

thruk1X

4 Carrier I/O clamp voltage, V

OC

Pin 10, I

OC

e

10 mA, RX mode 44 41 V min.

2N2222 diode pin 8 to 9 50 V max.

5 Carrier I/O clamp resistance, R10Pin 10, I

OC

e

10 mA 20 X

6 TX/RX low input voltage, V

IL

Pin 5 1.8 0.8 V max.

7 TX/RX high input voltage, V

IH

Pin 5 (Note 9) 2.2 2.8 V min.

8 TX/RX low input current, I

IL

Pin 5 at 0.8 V

b

2

b

20 mA min.

1 mA max.

9 TX/RX high input current, I

IH

Pin5at40V

b

1 0 mA min.

10

b

4

10 mA max.

10 RXbTX switch-over time, T

RT

Time to develop 63% of full current drive thru pin 10 10 ms

11 TXbRX switch-over time, T

TR

1 bit time, T

B

e

1/(2F

DATA

). Time TTRis user 2 bit

controlled with C

M

, see Apps. Info.

12 ICO initial accuracy of F

O

TX mode, R

O

e

6.65 kX,C

O

e

560 pF 125 113 kHz min.

F

0

e

(F

1

a

F2)/2 137 kHz max.

13 ICO temperature coefficient of FOTX or RX mode, (F

OMAX

b

F

OMIN

)/(T

JMAX

b

T

JMIN

)

b

100 PPM/§C

14 Temperature drift of F

O

TX or RX mode,b40sT

J

s

T

JMAX

g

2.0

g

5.0 % max.

Transmitter Electrical Characteristics (Note 3). The test conditions are: V

a

e

18 V and F

O

e

125 kHz

unless otherwise noted. The transmit center frequency is F

O

, FSK low is F1, and FSK high is F2.

Test Design

Limit

Ý

Parameter Conditions Typical Limit Limit

Units

(Note 4) (Note 5)

15 Supply voltage, Va, range Meets test 17 spec. at T

J

e

25§C and: 13 14 15 V min.

l

(F

1

[

14V

]

b

F

1

[

18V])/F

1

[

18V

]

l

k

0.01 40 24 23 V max.

l

(F

1

[

24V

]

b

F

1

[

18V])/F

1

[

18V

]

l

k

0.01

16 Total supply current, I

QT

Pin 15. Pin 12 high. IQTis IQthrough 52 79 mA max.

pin 15 and the average current I

ODC

of the

Carrier I/O through pin 10

17 Carrier I/O output current, I

O

100X load on pin 10 70 45 mApp min.

18 Carrier I/O lower swing limit, V

ALC

Pin 10. Set internally be ALC. 4.7 4.0 V min.

2N2222 diode pin 8 to 9 5.7 V max.

19 THD of IO(Note 6) Q of 10 tank driving 10X line 0.6 5.0 % max.

100X load, no tank 5.5 9 % max.

20 FSK deviation, F

2

b

F

1

(F

2

b

F1)/([F

2

a

F

1

]

/2) 4.4 3.7 % min.

5.2 % max.

21 Data In. low input voltage, V

IL

Pin 17 1.7 0.8 V max.

22 Data In. high input voltage, V

IH

Pin 17 (Note 9) 2.1 2.8 V min.

23 Data In. low input current, I

IL

Pin 17 at 0.8 V

b

1

b

10 mA min.

1 mA max.

24 Data In. high input current, I

IH

Pin 17 at 40 V

b

1 0 mA min.

10

b

4

10 mA max.

2

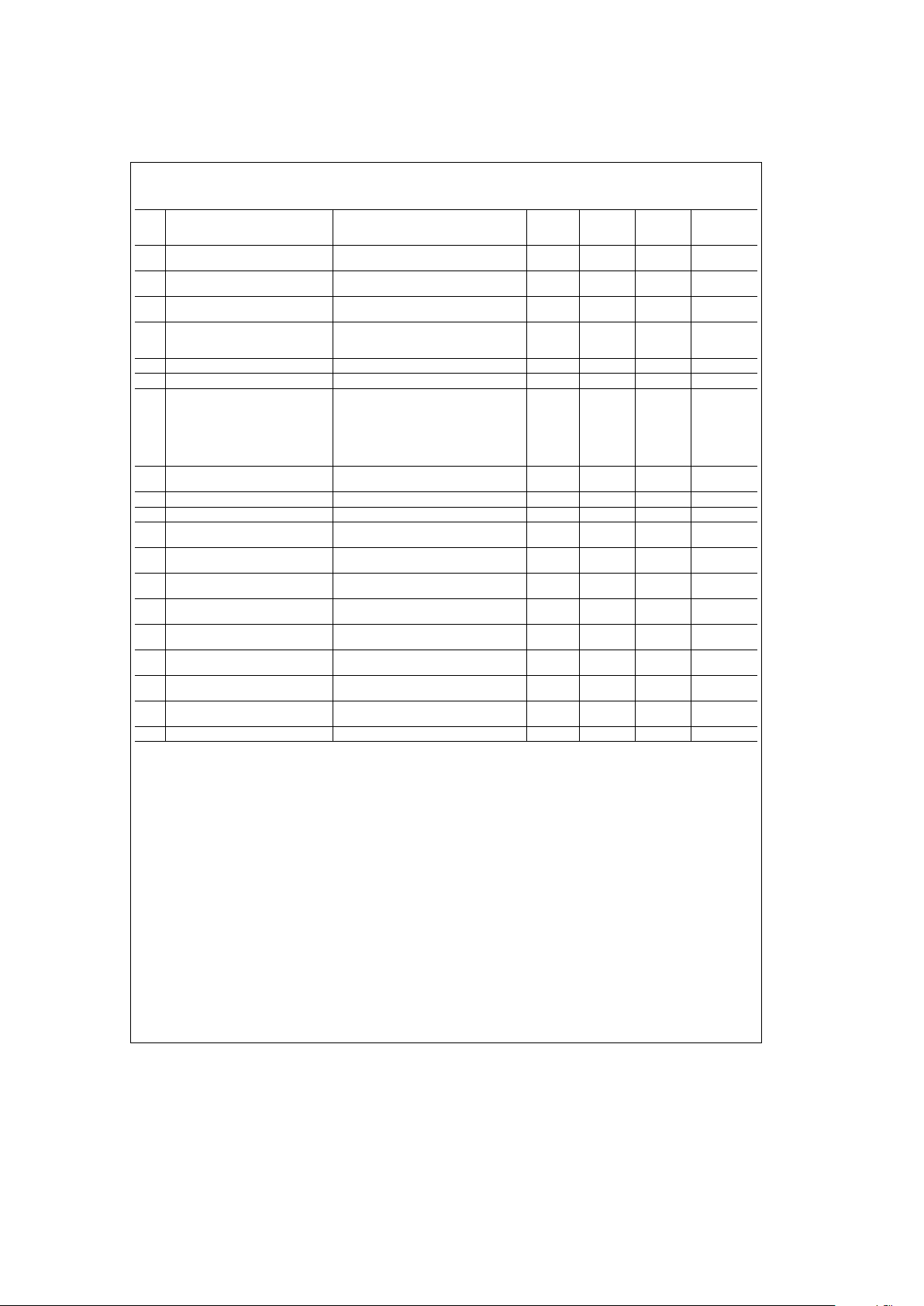

Receiver Electrical Characteristics (Note 3). The test conditions are: V

a

e

18 V, F

O

e

125 kHz,g2.2%

deviation FSK, F

DATA

e

2.4 kHz, V

IN

e

100 mVpp, in the receive mode, unless otherwise noted.

Test Design

Limit

Ý

Parameter Conditions Typical Limit Limit

Units

(Note 4) (Note 5)

25 Supply voltage, Va, range Functional receiver (Note 7) 12 13 13.5 V min.

37 30 28 V max.

26 Supply current, I

QT

IQTis pin 15 (Va) plus pin 10 11 5 mA min.

(Carrier I/O) current. 2.4 kX Pin 13 to GND. 14 mA max.

27 Carrier I/O input resistance, R

10

Pin 10 19.5 14 kX min.

30 kX max.

28 Max. data rate, F

MD

Functional receiver (Note 7), C

F

e

100 pF, 10 4.8 2.4 kBaud

R

F

e

0X, no tank,

2.4 kHz

e

4.8 kBaud

29 PLL capture range, F

C

C

F

e

100 pF, R

F

e

0 X

g

40

g

15

g

10 % min.

30 PLL lock range, F

L

C

F

e

100 pF, R

F

e

0 X

g

45

g

15 % min.

31 Receiver input sensitivity, S

IN

For a functional receiver (Note 8)

Referred to chip side (pin 10) 1.8 10 12 mV

RMS

of the line-coupling XFMR: F

O

e

50 kHz 2.0 mV

RMS

F

O

e

300 kHz 1.4 mV

RMS

Referred to line side of XFMR: 0.26 mV

RMS

(assuming a 7.07:1 XFMR) F

O

e

50 kHz 0.29 mV

RMS

F

O

e

300 kHz 0.20 mV

RMS

32 Tolerable input dc voltage offset Pin 10 lower than pin 15 by V

INDC

2 0.1 V max.

range, V

INDC

33 Data Out. breakdown voltage Pin 12, leakage Is20 mA 70 55 V min.

34 Data Out. low output, V

OL

Pin 12, sat. voltage at I

OL

e

2 mA 0.15 0.4 V max.

35 Impulse noise filter current, I

I

Pin 13 charge and discharge current

g

55

g

45 mA min.

g

85 mA max.

36 Offset hold cap. bias voltage, V

CM

Pin 6 2.0 1.3 V min.

3.5 V max.

37 Offset hold capacitor max. drive Pin 6. V(pin 3)bV(pin 4)

e

g

250 mV

g

55

g

25 mA min.

current, I

MCM

g

80 mA max.

38 Offset hold bias current, I

OHB

Pin 6, TX mode. Bias pin 6 as it self-

b

0.5

b

20

b

40 nA min.

biased during test 31. 40 nA max.

39 Phase comparator current, I

PC

Bias pins 3 and 4 at 8.5 V 100 50 mA min.

I

PC

e

I(pin 3)aI(pin 4), TX mode 200 mA max.

40 Phase detector output resistance, Pins 3 and 4. 10 6 kX min.

R

PD

R

PD

e

(V@100mAbV@50mA)/(50mA) 18 kX max.

41 Phase detector demodulated output Pin 3 to 4, measured after filtering 100 60 mVpp min.

voltage, V

PD

out the 2FOcomponent 180 mVpp max.

42 Fast offset cancel voltage ‘‘window’’ V

PIN3

b

V

PIN4

e

g

V

WINDOW

a

DC offset 0.95 0.70 V/V min.

-to-V

PD

ratio, VW/V

PD

Drive forg1 mA pin 6 current 1.20 V/V max.

43 Power supply rejection, PSRR C

L

e

0.1 mF. PSRReCMRR. 120 Hz 80 dB min.

Note 1: More accurately, the maximum voltage allowed on pin 10 is VOC, and VOCranges from 41 to 50V. Also, transients may reach above 60V; see the transient

peak voltage characteristic curve.

Note 2: The maximum power dissipation rating should be derated for device operation above 25

§

C to insure that the junction temperature remains below the

maximum rating. Use a i

JA

of 75§C/W for the N package using a socket in still air (which is the worst case). Consult the Application Information section for more

detail.

Note 3: The boldface values apply over the full junction temperature range for the specified supply voltage range. All other numbers apply at T

A

e

T

J

e

25§C. Pin

numbers refer to LM1893. LM2893 tested by shorting Carrier In to Carrier Out and testing it as an LM1893.

Note 4: Guaranteed and 100% production tested.

Note 5: Guaranteed (but not 100% production tested) over the temperature and supply voltage ranges. These limits are not used to calculate outgoing quality

levels.

Note 6: Total harmonic distortion is measured using THD

e

[

I

RMS

(all components at or above 2FO)]/[I

RMS

(fundamental)].

Note 7: Receiver function is defined as the error-free passage of 1 cycle of 50% duty-cycle 2.4 kHz square-wave data (2 sequential 208 mS bits), with the first bit

being a ‘‘1.’’ All of the data transitions (edges) must fall within

g

10% (g20.8 ms) of their noise-free positions. RX time delay is minimized by using no impulse noise

filter cap. C

I

for this test.

Note 8: During the sensitivity check, note 7 requirements are followed with these exceptions: (1) data rate F

DATA

e

1.2 kHz, (2) all of the data transitions must fall

within

g

20% (g41.6 ms) of their noise-free positions, and (3), a time-domain filter capacitor (CI) is used. The time delay of CIis (/2 bit, or 208 ms. (CIis

approximately 6200 pF).

Note 9: For TTL compatibility use a pull-up resistor to increase min. V

OH

to above 2.8 V.

3

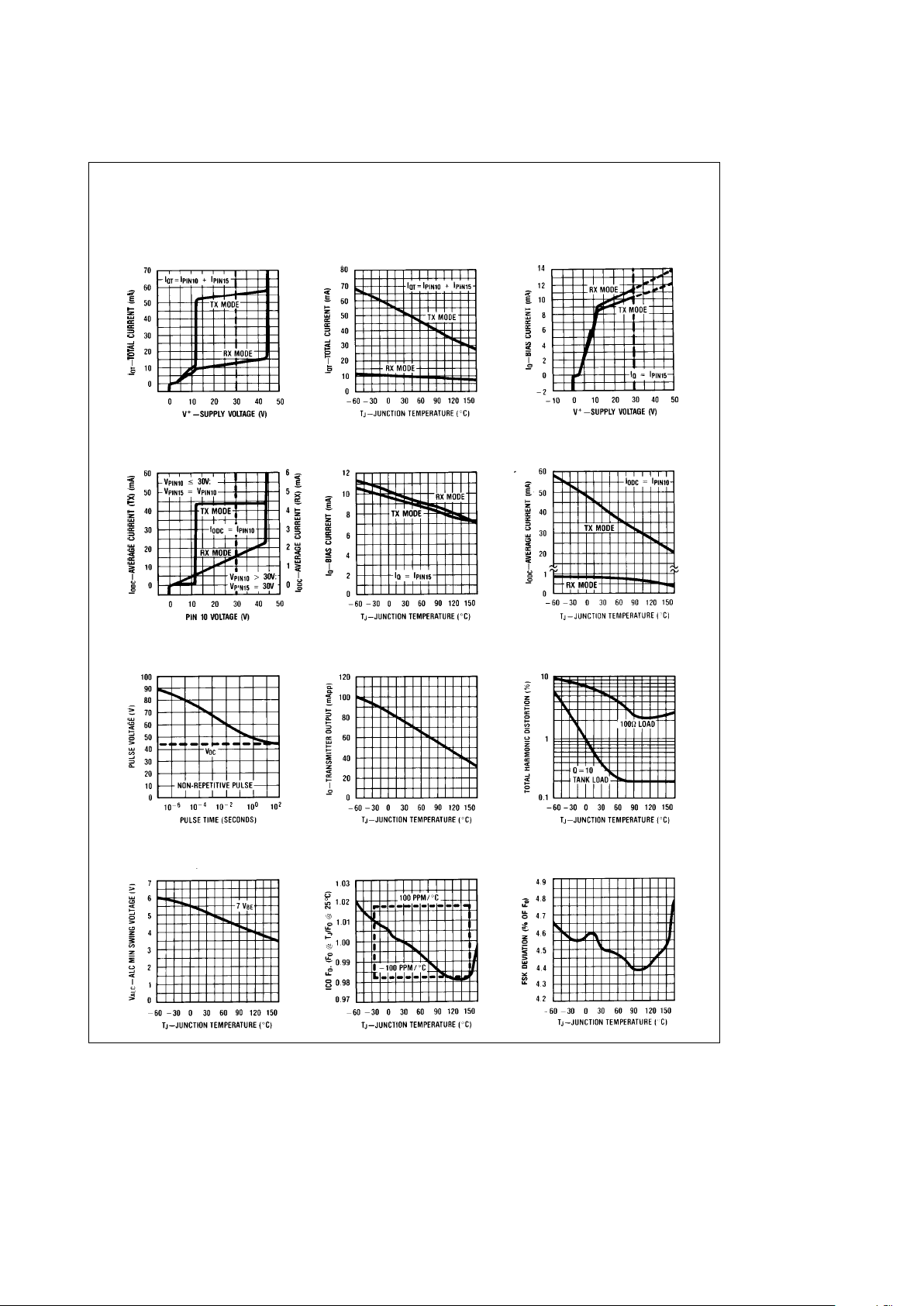

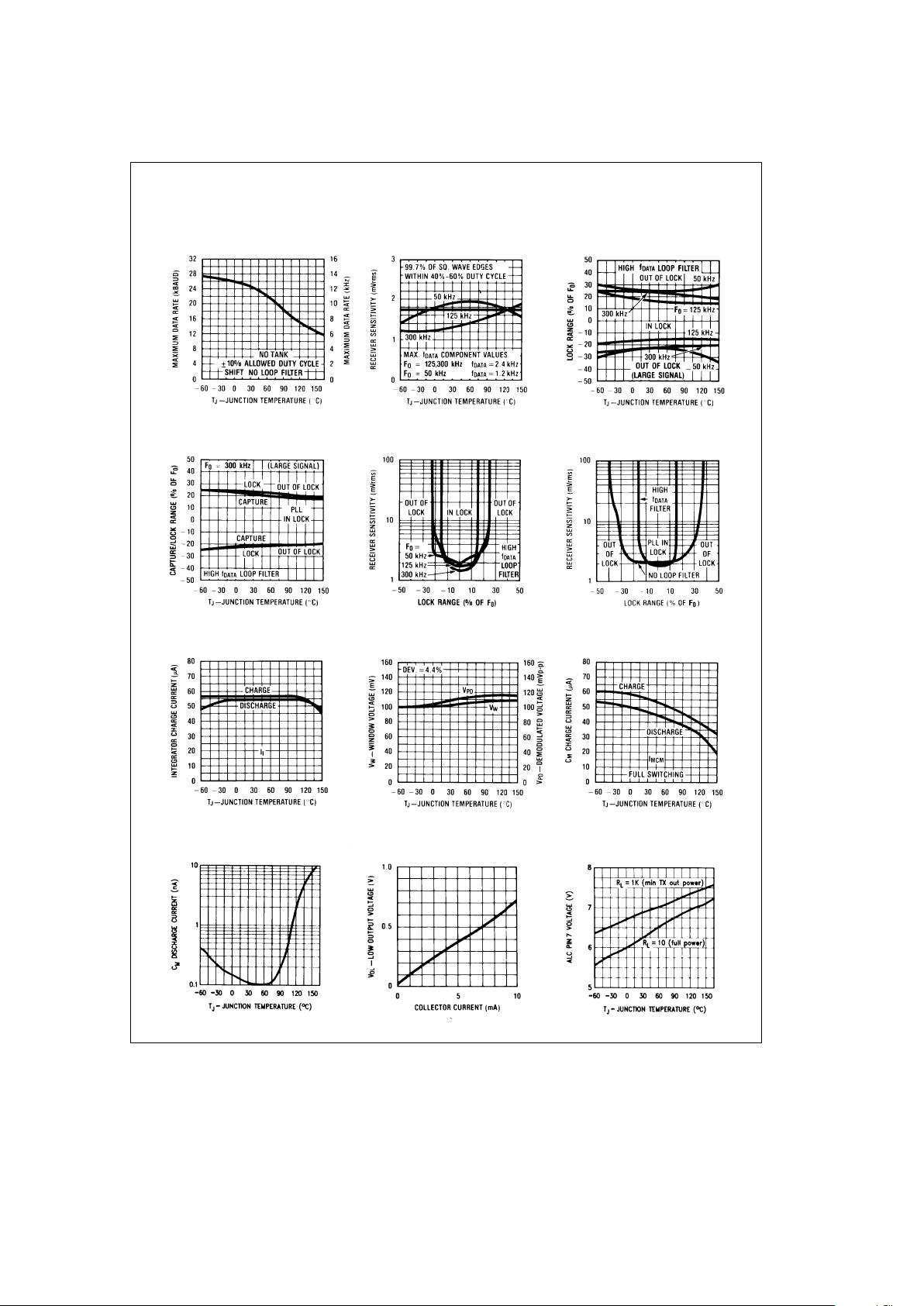

Typical Performance Characteristics (V

a

e

18V, F

O

e

125 kHz, circuit of

Figure 1

, pin numbers for

LM1893)

Total Current Consumption,

I

QT

, vs Supply Voltage

Total Current Consumption,

IQT, vs Junction Temperature

Chip Bias Current,

iQ, vs Supply Voltage

Chip Bias Current, I

Q

,

vs Junction Tempurature

Output Stage DC Current,

I

ODC

, vs Output Voltage

Output Stage DC Current,

I

ODC

,vs

Junction Temperature

Transient Voltage Survival

vs Pulse Time

Transmitter AC Output Current

vs Junction Temperature

Transmitter Sinusoid THD

vs Junction Temperature

ALC Voltage vs

Junction Temperature

ICO Frequency vs

Junction Temperature

Transmitter FSK Deviation

vs Junction Temperature

TL/H/6750– 38

4

Typical Performance Characteristics (Continued)

Maximum Data Rate vs

Junction Temperature

Receiver Sensitivity vs

Junction Temperature

PLL Lock Range vs

Junction Temperature and F

O

PLL Capture & Lock Range vs

Junction Temperature

Receiver Sensitivity vs

PLL Lock Range and F

O

Receiver Sensitivity vs

PLL Lock Range and Loop Filter

Impulse Noise Filter

Current vs Junction

Temperature

Phase Detector Output

Voltage vs Junction

Temperature

Offset Hold Cap. Charge

Currents vs Junction

Temperature

Offset Hold Cap. Bias Current vs

Junction Temperature

Data Out. Low Voltage vs

Pull Down Current

Pin 7 Bias Voltage vs

Junction Temperature

TL/H/6750– 39

5

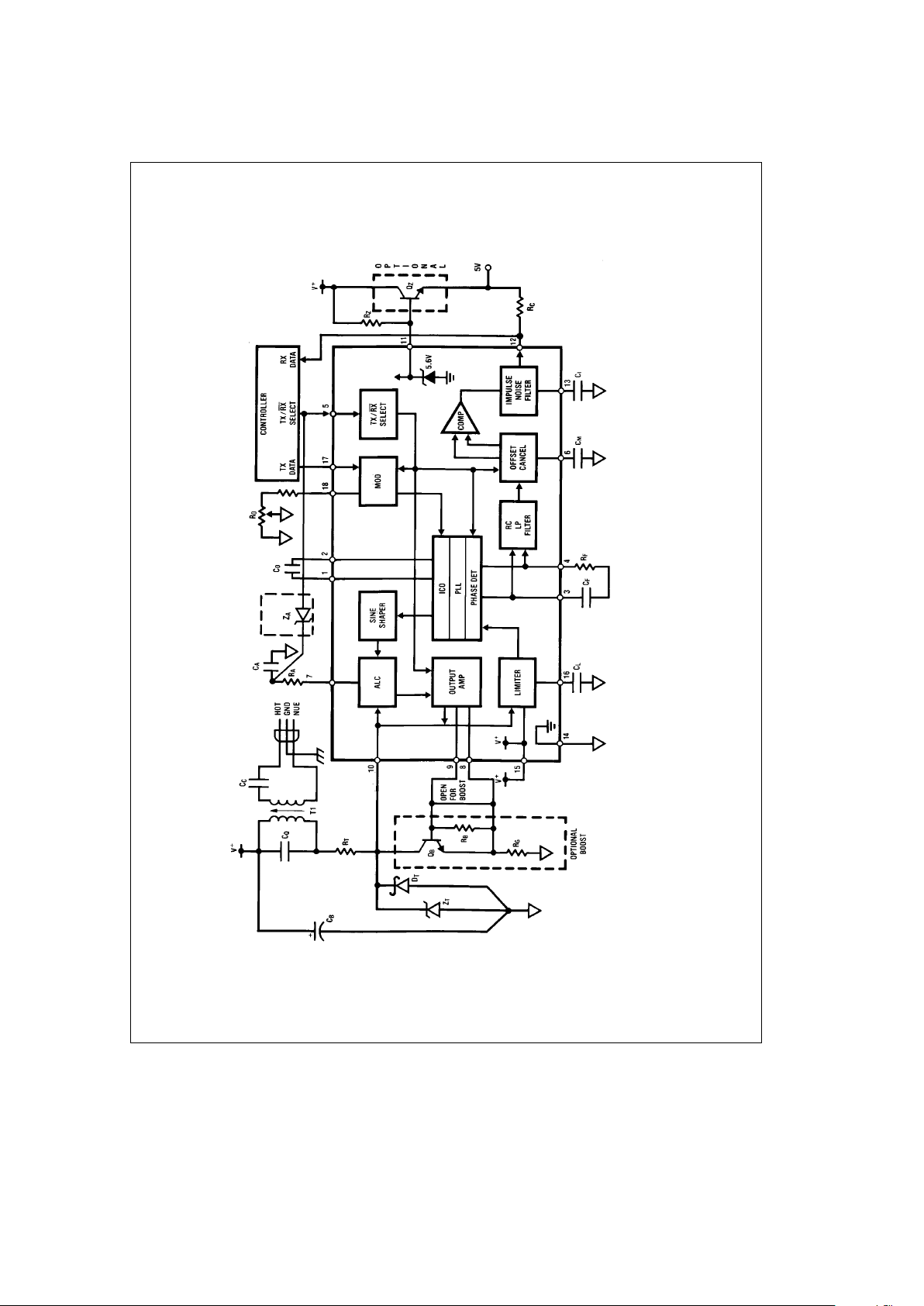

Application Information*

THE DATA PATH

The BI-LINETMchip serves as a power line interface in the

carrier-current transceiver (CCT) system of

Figure 3.Figure

4

shows the interface circuit now discussed. The controller

may select either the transmit (TX) or receive (RX) mode.

Serial data from the controller is used to generate a FSKmodulated 50 to 300 kHz carrier on the line in the TX mode.

In the RX mode line signal passes through the coupling

transformer into the PLL-based receiver. The recreated serial bit stream drives the controller.

With the IC in the TX mode (pin 5 a logic high), baseband

data to 5 kHz drive the modulator’s Data In pin to generate

a switched 0.978I/1.022I control current to drive the low TC,

triangle-wave, current-controlled oscillator to

g

2.2% deviation. The tri-wave passes through a differential attenuator

and sine shaper which deliver a current sinusoid through an

automatic level control (ALC) circuit to the gain of 200 current output amplifier. Drive current from the Carrier I/O develops a voltage swing on T

1

’s (

Figure 4

) resonant tank

proportional to line impedance, then passes through the

step-down transformer and coupling capacitor C

C

onto the

line. Progressively smaller line impedances cause reduced

signal swing, but never clipping-thus avoiding potential radio

frequency interference. When large line impedances threaten to allow excessive output swing on pin 10, the ALC

shunts current away from the output amplifier, holding the

voltage swing constant and within the amp’s compliance

limit. The amplifier is stable with a load of any magnitude or

phase angle.

In the RX mode (pin 5 a logic low), the TX sections on the

chip are disabled. Carrier signal, broad-band noise, transient

spikes, and power line component impinge of the receiver’s

input highpass filter, made up of C

C

and T1, and the tank

bandpass filter. In-band carrier signal, band-limited noise,

heavily attenuated line frequency component, and attenuated transient energy pass through to produce voltage swing

on the tank, swinging about the positive supply to drive the

Carrier I/O receiver input. The balanced Norton-input limiter

amplifier removes DC offsets, attenuates line frequency,

performs as a bandpass filter, and limits the signal to drive

the PLL phase detector differentially. The differential demodulated output signal from the phase detector, containing AC and DC data signal, noise, system DC offsets, and a

large twice-the-carrier-frequency component, passes

through a 3-stage RC lowpass filter to drive the offset cancel circuit differentially. The offset cancelling circuit works

by insuring that the (fixed)

g

50 mV signal delivered to the

data squaring (‘‘slicing’’) comparator is centered around the

0 mV comparator switch point. Whenever the comparator

signal plus DC offset and noise moves outside the carefully

matched

g

50 mV voltage ‘‘window’’ of the offset cancel

circuit, it adjusts its DC correction voltage in series with the

differential signal to force the signal back into the window.

While the signal is within the

g

50 mV window, the DC offset

is stored on capacitor C

M

. By grace of the highly non-linear

offset hold capacitor charging during offset cancelling, the

DC cancellation is done much more quickly than with an AC

coupling capacitor normally used in place of the offset cancel circuit. Since impulse noise spikes normally ring the signal symmetrically around 0 V, the fully bilateral offset cancel

topology affords excellent noise rejection. The switched current output of the comparator drives the impulse noise filter

integrator capacitor that rejects all data pulses of less than

the integrator charge time. Noise appears as duty-cycle jitter

at the open collector serial data output.

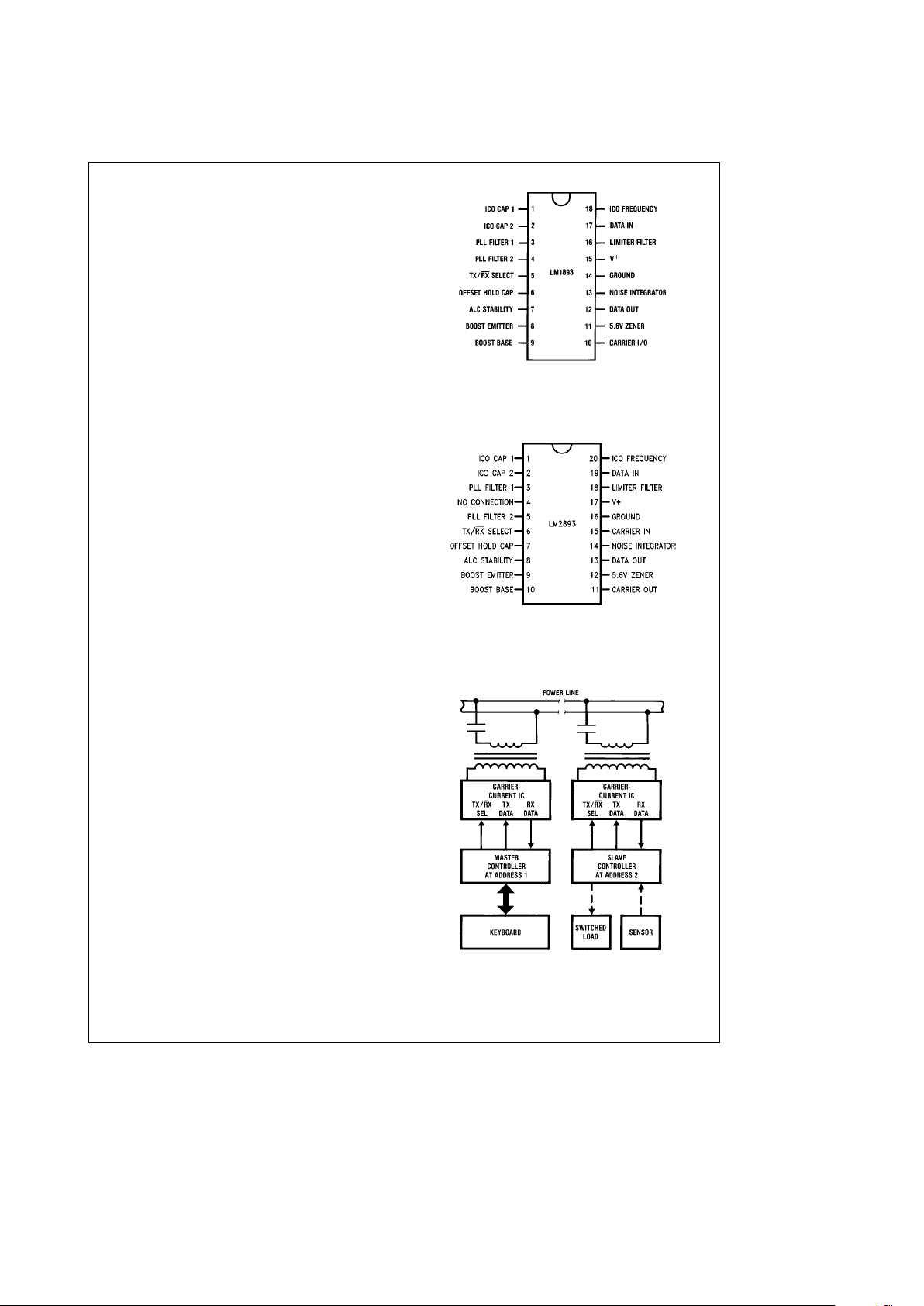

Dual-In-Line Package

TL/H/6750– 2

Top View

Order Number LM1893N

See NS Package Number N18A

Small Outline & Dual-In-Line Package

TL/H/6750– 41

Top View

Order Number LM2893M or LM2893N

See NS Package Number M20B or N20A

FIGURE 2. Connection Diagrams

TL/H/6750– 3

FIGURE 3. The block diagram of a carrier-current

system using the Bi-Line chip to interface digital

controllers via the power line

*Unless otherwise noted, all pin references refer to LM1893, but hold true

for equivalent LM2893 pin.

6

Application Information (Continued)

TL/H/6750– 4

FIGURE 4. Block diagram of a CCT system with the boost and 5V supply options shown in dashed boxes

7

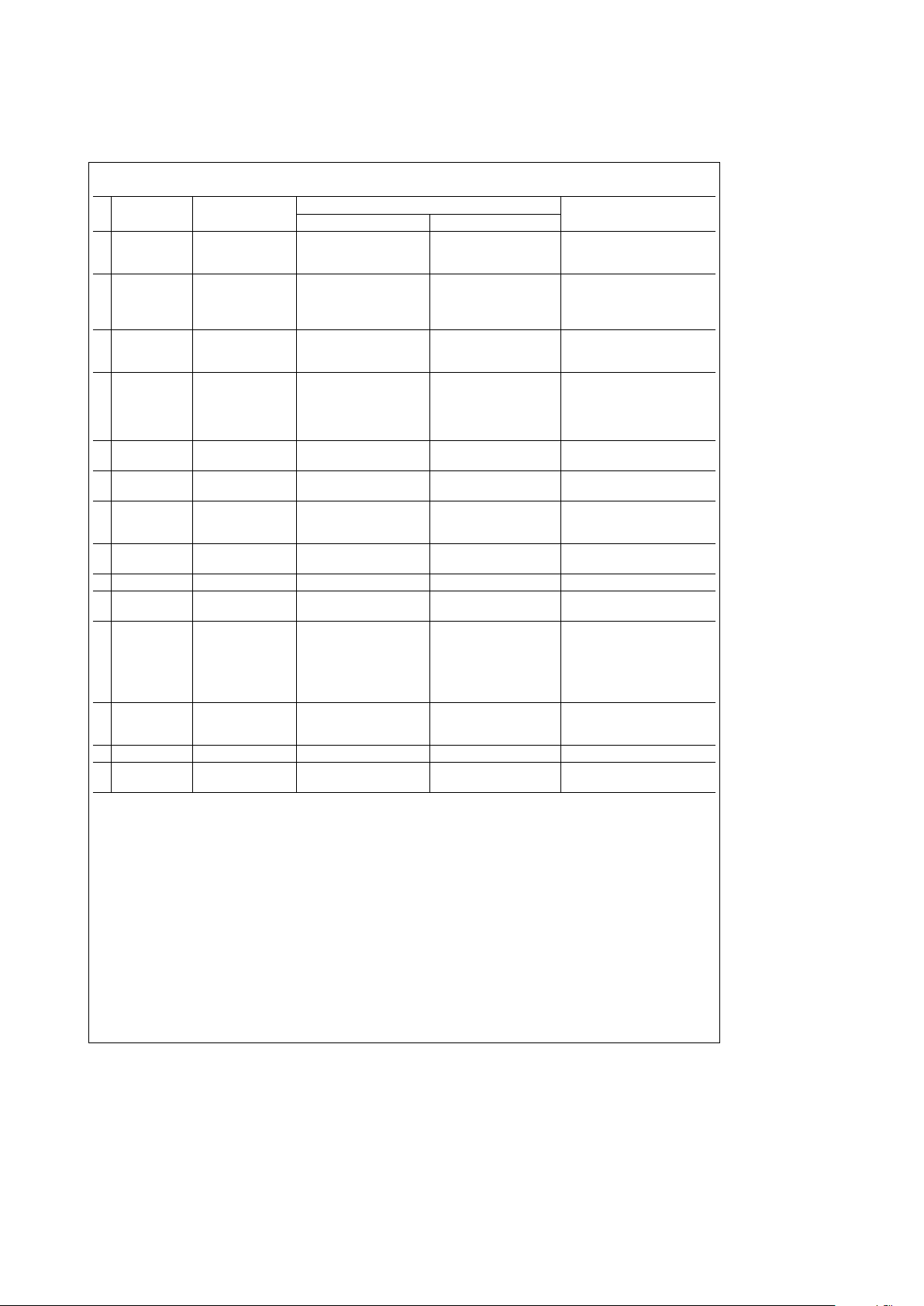

Application Information (Continued)

Ý

Recommended

Purpose

Effect of making the component value:

Notes

Value

Smaller Larger

CO560 pF Together, COand ROIncreases F

O

Decreases F

O

g

5% NPO ceramic. Use low TC

R

O

6.2 kX set ICO FO. Increases F

O

Decreases F

O

2 k pot and 5.6 k fixed R.

k

5.6 k not recommended.l7.6 k not recommended. Poor FOTC withk5.6kRO.

CF0.047 mF PLL loop filter pole Less noise immune, higher More noise immune, lower Depending on RFvalue and

f

DATA

, more PLL stability. f

DATA

, less PLL stability. FO, PLL unstable with large

RF3.3 kX PLL loop filter zero PLL less stable, allows PLL more stable, allows CF. See Apps. Info. C

F

less CF. Less ringing. more CF. More ringing. and RFvalues not critical.

CC0.22 mF Couples FOto line, Low TX line amplitude. Drives lower line Z.

t

250 V non-polar. Use 2C

C

CCand T1low-pass Less 60 Hz T1current. More 60 Hz T1current. on hot and neutral for max.

attenuates 60 Hz. Less stored charge. More stored charge. line isolation, safety.

CQ0.033 mF Tank matches line Z, Tank FOup or increase Tank FOdown or decrease 100 V nonpolar, low TC,g10%

bandpass filters, L of T

1

for constant FO. L of T1for constant FO. High large-signal Q needed.

T

1

Use isolates from line, Smaller L: higher FOor Larger L: lower FOor Optimize for low FOline

recommended and attenuates increase CC; decreased FOdecrease CC; increased FOpull with control of FOTC

XFMR transients. line pull. line pull. and Q.

CA0.1 mF ALC pole Noise spikes turn ALC off. Slower ALC response. RAoptional. ALC stable

R

A

10 kX ALC zero Less stable ALC. More stable ALC. for C

A

t

100 pF.

CL0.047 mF Limiter 50 kHz pole, Higher pole F, more 60 Hz Lower pole F, less 60 Hz Any reasonably low TC cap.

60 Hz rejection. reject. F

O

attenuation? reject, more noise BW. 300 pF guarantees stability.

CM0.47 mF Holds RX path VOSLess noise immune, shorter More noise immune, longer Low leakageg20% cap.

VOShold, faster VOSaqui- VOShold, slower VOSaqui- Scale with f

DATA

.

sition, shorter preamble. sition, longer preamble.

CI0.047 mF Rejects short pulses Less impulse reject, less More impulse reject, more CIcharge time (/2 bit nom.

like impulse noise. delay, more pulse jitter. delay, less pulse jitter. Must be

k

1 bit worst-case.

RC10 kX Open-col. pull-up Less available sink I. Less available source I. R

C

t

1.5 kX on 5.6 V

RZ12 kX 5.6 V Zener bias Larger shunt current, Smaller shunt current, 1kI

Z

k

30 mA recommended.

more chip dissipation. less V

a

current draw. (Chip power-up needs 5.6 V)

Z

T

t

44 V BV Transient clamp ZTfailure, higher series ZTcostly, lower series Recommend Zener rated

k

60 V peak R-excess peak V, Zener R gives enhanced fort500 W for 1 ms.

and chip damage, transient clamp,

less ruggedness. more ruggedness.

R

T

4.7 X Transient I limit Damage ZT, pull up Va. Excessive TX attenuation. Carbon comp. recommended.

D

T

t

44V BV Over-drive Clamp Failure on Transient Costly IRF 11DQ05 or 1N5819

RB180 X Base bleed Faster, lower THD IO. Inadequate turn-off speed. Boost optional. QBF(b3 dB)

Q

B

Power NPN Boost gain device Excessive TJand V

SAT

. More rugged, but costly. ofl200 MHz. R

B

l

24 Ohm.

RG1.1 X Current setting R More IO, need higher hfe. Less IO, lower min. hfe.I

O

e

70[(10aRG)/R

G

]

mApp.

C

B

t

47 mF Supply bypass Transients destroy chip. Less supply spike. Vanever over abs. max.

ZA5.1V Stop ALC charge Excess ALC ALC RX charging ZAoptional - 5.1V

in RX mode current flow not inhibited over T

J

g

20% low leakage type

FIGURE 5. A quick explanation of the external component function using the circuit of

Figure 4

. Values given are for V

a

e

18 V, F

O

e

125 kHz, f

DATA

e

360 Baud (180 Hz), using a 115 V 60 Hz power line

Component Selection

Assuming the circuit of

Figure 4

is used with something other than the nominal 125 kHz carrier frequency, 180 Hz data

rate, 18V supply voltage, etcetera, the component values

listed in

Figure 5

will need changing. This section will help

direct the CCT designer in finding the required component

values with emphasis placed on look-up tables and charts. It

is assumed that the designer has selected values for carrier

center frequency, F

O

; data rate, f

DATA

; supply voltage, Va;

power line voltage, V

L

; and power line frequency, FL.Ifone

or more of those parameters is not defined, one may read

the data sheet and make an educated guess.

Maxims to keep in mind, based on CCT electrical perform-

ance considerations only, are: 1) the higher the F

O

the better, 2) the lower the maximum data rate the better, and 3)

the more time and frequency filtering the better.

Use

Figure 5

as a quick reference to the external compo-

nent function.

THE TRANSMITTER

C

O

Central to chip operation is the low TC of FOemitter-coupled oscillator. With proper C

O

, the FOof the 2VBEamplitude triangle-wave oscillator output may vary from near DC

to above 300 kHz. While C

O

may have any value, COshould

8

Loading...

Loading...