NSC JM38510-30109BE, JD54LS109BFA Datasheet

TL/F/6368

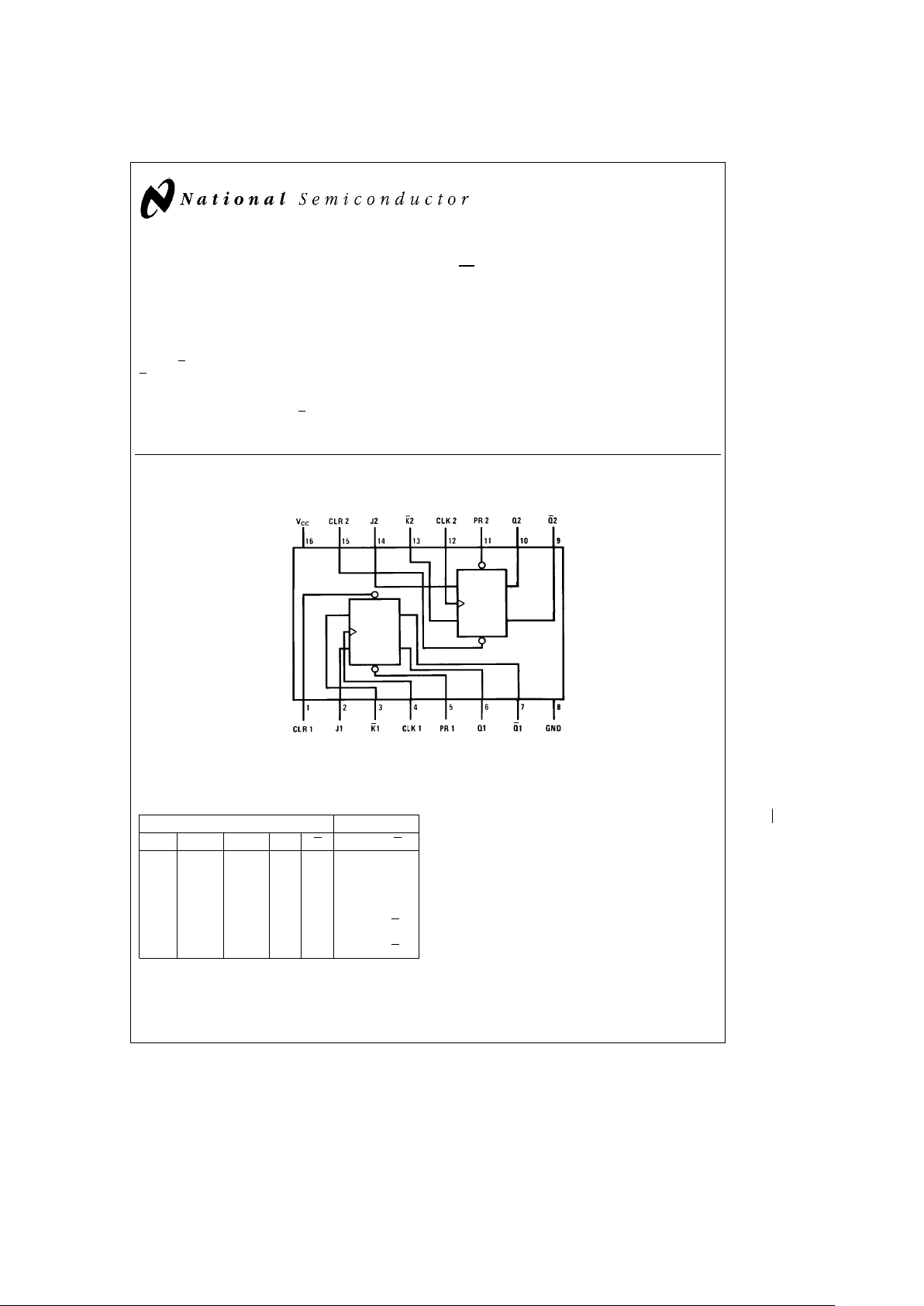

54LS109/DM54LS109A/DM74LS109A Dual Positive-Edge-Triggered J-K Flip-Flops

with Preset, Clear, and Complementary Outputs

June 1989

54LS109/DM54LS109A/DM74LS109A

Dual Positive-Edge-Triggered J-K

Flip-Flops

with Preset, Clear, and Complementary Outputs

General Description

This device contains two independent positive-edge-triggered J-K

flip-flops with complementary outputs. The J and

K

data is accepted by the flip-flop on the rising edge of the

clock pulse. The triggering occurs at a voltage level and is

not directly related to the transition time of the rising edge of

the clock. The data on the J and K

inputs may be changed

while the clock is high or low as long as setup and hold

times are not violated. A low logic level on the preset or

clear inputs will set or reset the outputs regardless of the

logic levels of the other inputs.

Features

Y

Alternate Military/Aerospace device (54LS109) is available. Contact a National Semiconductor Sales Office/

Distributor for specifications

Connection Diagram

Dual-In-Line Package

TL/F/6368– 1

Order Number 54LS109DMQB, 54LS109FMQB, DM54LS109AJ,

DM54LS109AW, DM74LS109AM or DM74LS109AN

See NS Package Number J16A, M16A, N16E or W16A

Function Table

Inputs Outputs

PR CLR CLK J K QQ

LH XXXHL

HL XXXLH

LL XXXH*H*

HH

u

LL L H

HH

u

H L Toggle

HH

u

LHQ0Q

0

HH

u

HH H L

HH LXXQ

0

Q

0

H

e

High Logic Level

L

e

Low Logic Level

X

e

Either Low or High Logic Level

u

e

Rising Edge of Pulse

*

e

This configuration is nonstable; that is, it will not persist when preset

and/or clear inputs return to their inactive (high) state.

Q

0

e

The output logic level of Q before the indicated input conditions were

established.

Toggle

e

Each output changes to the complement of its previous level on

each active transition of the clock pulse.

C

1995 National Semiconductor Corporation RRD-B30M105/Printed in U. S. A.

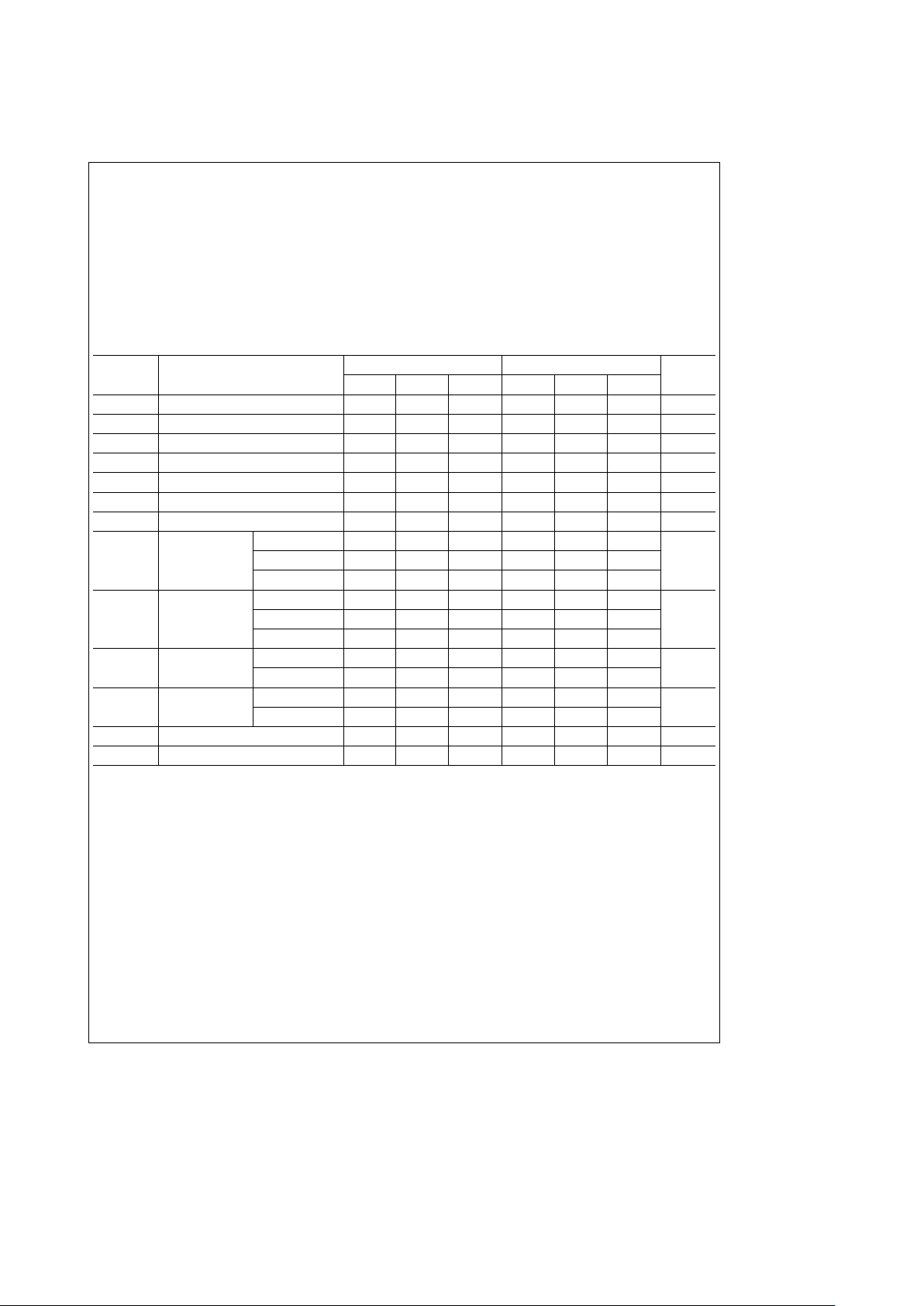

Absolute Maximum Ratings (Note)

If Military/Aerospace specified devices are required,

please contact the National Semiconductor Sales

Office/Distributors for availability and specifications.

Supply Voltage 7V

Input Voltage 7V

Operating Free Air Temperature Range

DM54LS and 54LS

b

55§Ctoa125§C

DM74LS 0

§

Ctoa70§C

Storage Temperature Range

b

65§Ctoa150§C

Note:

The ‘‘Absolute Maximum Ratings’’ are those values

beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The

parametric values defined in the ‘‘Electrical Characteristics’’

table are not guaranteed at the absolute maximum ratings.

The ‘‘Recommended Operating Conditions’’ table will define

the conditions for actual device operation.

Recommended Operating Conditions

Symbol Parameter

DM54LS109A DM74LS109A

Units

Min Nom Max Min Nom Max

V

CC

Supply Voltage 4.5 5 5.5 4.75 5 5.25 V

V

IH

High Level Input Voltage 2 2 V

V

IL

Low Level Input Voltage 0.7 0.8 V

I

OH

High Level Output Current

b

0.4

b

0.4 mA

I

OL

Low Level Output Current 4 8 mA

f

CLK

Clock Frequency (Note 2) 0 25 0 25 MHz

f

CLK

Clock Frequency (Note 3) 0 20 0 20 MHz

t

W

Pulse Width Clock High 18 18

(Note 2)

Preset Low 15 15 ns

Clear Low 15 15

t

W

Pulse Width Clock High 25 25

(Note 3)

Preset Low 20 20 ns

Clear Low 20 20

t

SU

Setup Time Data High 30

u

30

u

ns

(Notes1&2)

Data Low 20

u

20

u

t

SU

Setup Time Data High 35

u

35

u

ns

(Notes1&3)

Data Low 25

u

25

u

t

H

Hold Time (Note 4) 0

u

0

u

ns

T

A

Free Air Operating Temperature

b

55 125 0 70

§

C

Note 1: The symbol (u) indicates the rising edge of the clock pulse is used for reference.

Note 2: C

L

e

15 pF, R

L

e

2kX,T

A

e

25§C and V

CC

e

5V.

Note 3: C

L

e

50 pF, R

L

e

2kX,T

A

e

25§C and V

CC

e

5V.

Note 4: T

A

e

25§C and V

CC

e

5V.

2

Loading...

Loading...