NSC G1-300P-85-2.0, G1-300B-85-2.0, G1-266P-85-1.8, G1-266B-85-1.8, G1-233P-85-1.8 Datasheet

...

© 2000 National Semiconductor Corporation www.national.com

Geode™ GX1 Processor Series Low Power Integrated x86 Solution

General Description

The National Semiconductor®Geode™ GX1 processor

series is a line of integrated processors specifically

designed to power information appliances for entertainment, education, and business. Serving the needs of consumers and business professionals alike, it’s the perfect

solution for IA (information appliance) applications such as

thin clients, interactive set-top boxes, and personal internet

access devices.

The Geode GX1 processorseries is dividedintothreemain

categories as defined by the core operating voltage. Available with core voltages of 2.0V, 1.8V, and 1.6V, it offers

extremely low typical power consumption (1.2W, 1.0W, and

0.8W, respectively) leading to longer battery life and

enabling small form-factor, fanless designs. Typical power

consumption is defined as an average, measured running

Microsoft Windows at 80% Active Idle (Suspend-on-Halt)

with a display resolution of 800x600x8 bpp at 75 Hz.

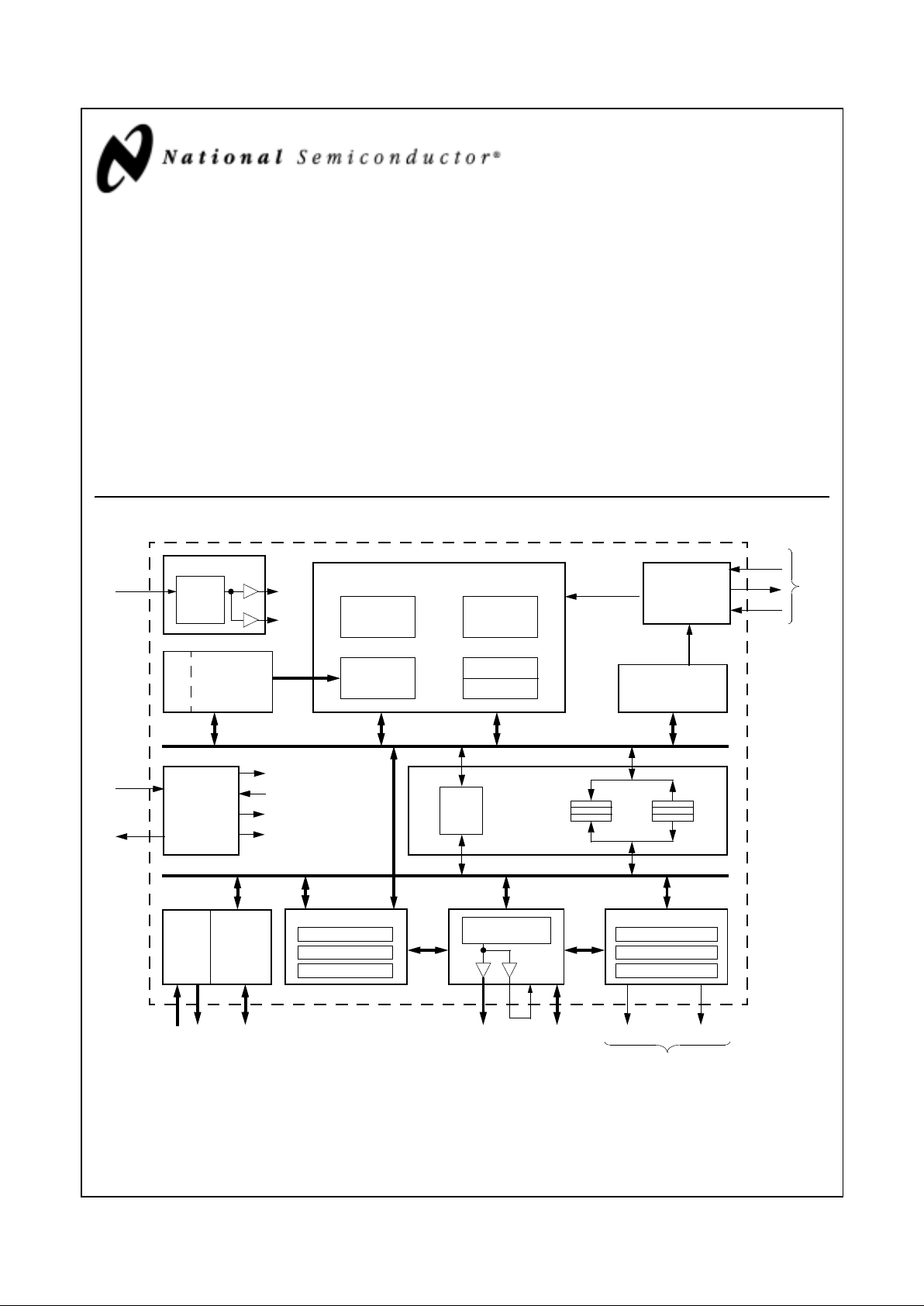

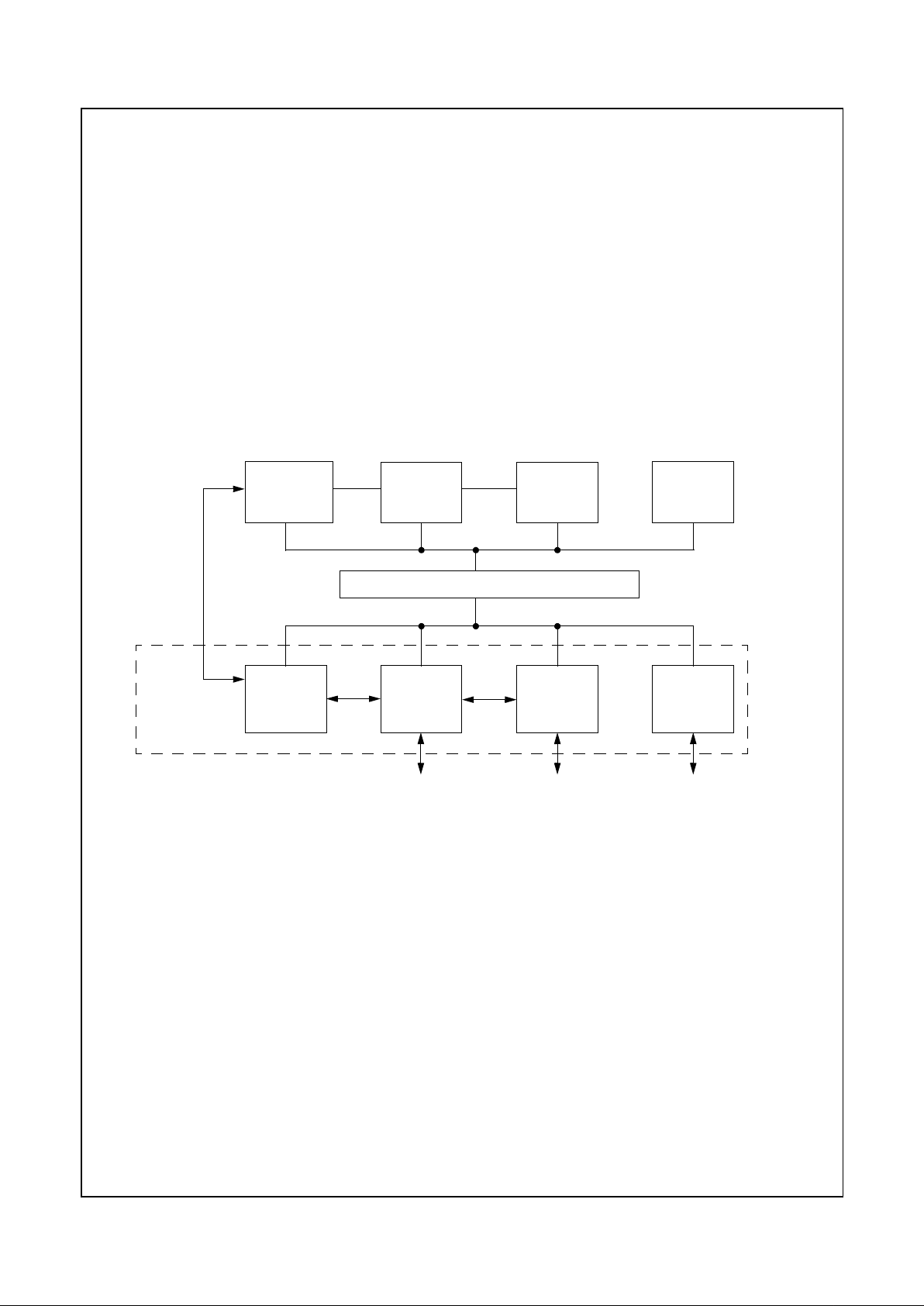

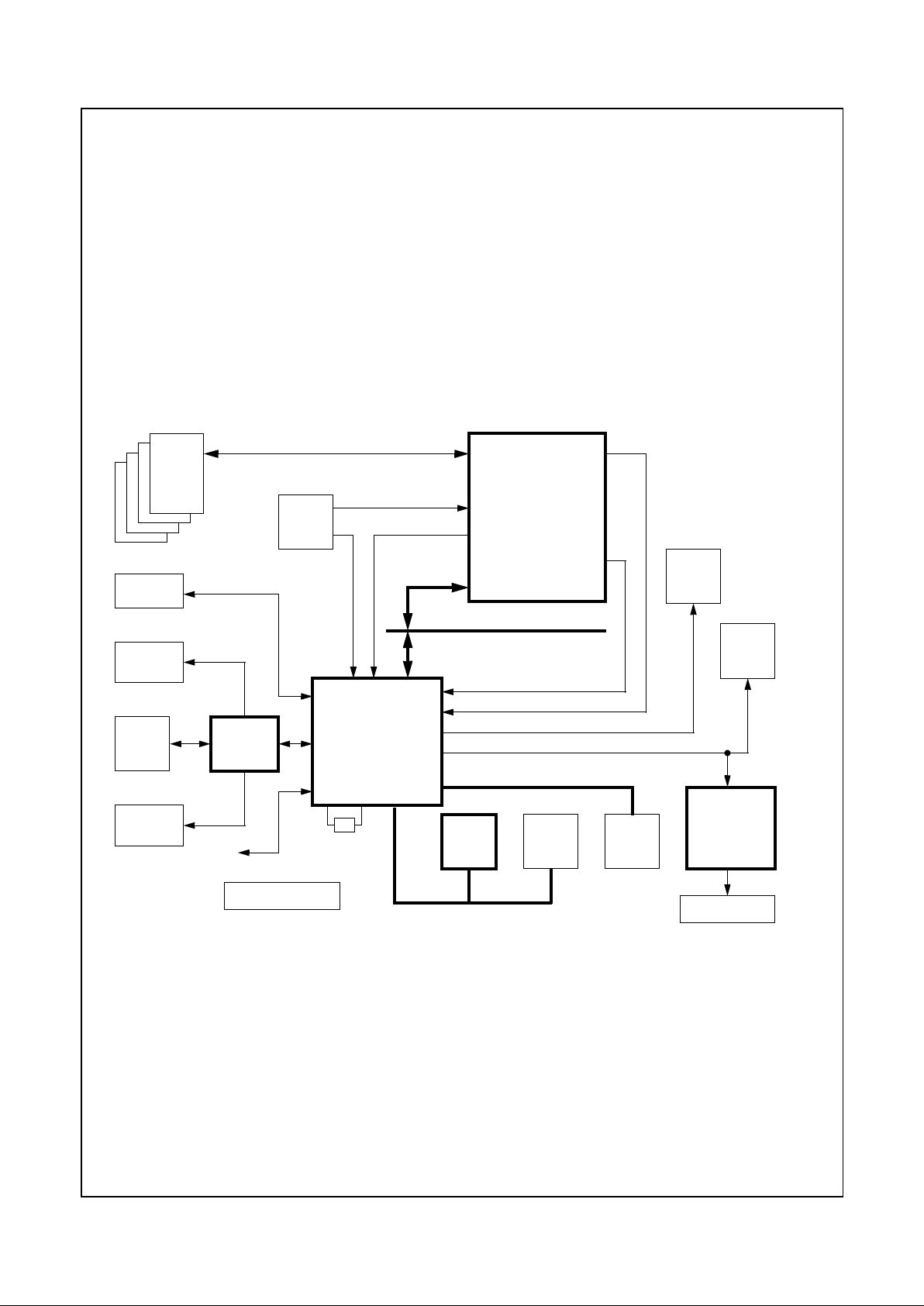

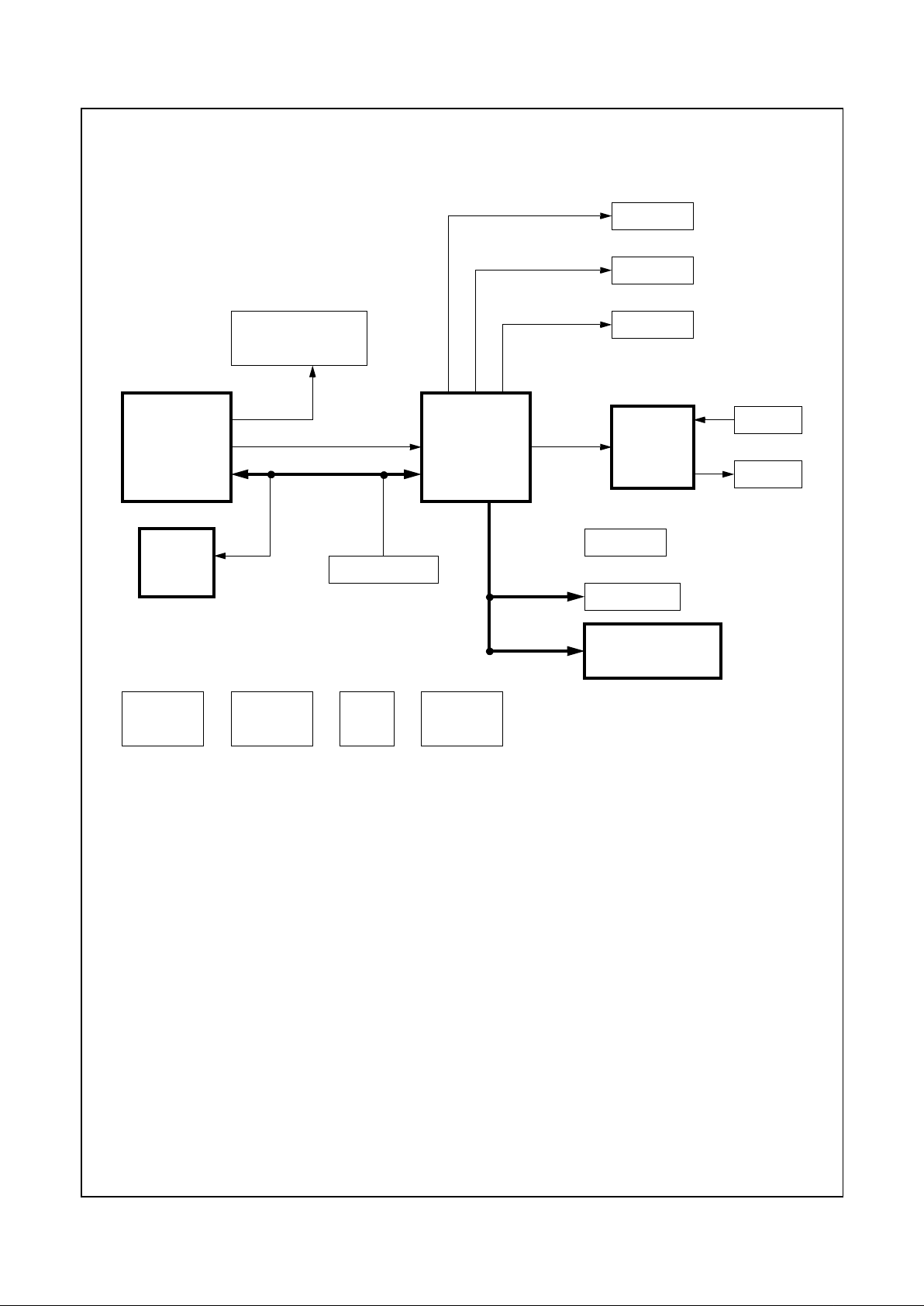

Geode™ GX1 Processor Internal Block Diagram

Interrupt

Floating Point

Clock Module

SYSCLK

Core

X-Bus

x86 Compatible Core

TLB

Instruction

16 KB

Unified L1

Cache

SYSCLK

X-Bus CLK

(128)

FP_Error

INT/NMI

X-Bus

Power

Management

Control

SUSP#

SUSPA#

Core Suspend

Core Acknowledge

X-Bus Suspend

X-Bus Acknowledge

X-Bus (32)

C-Bus (64)

Write

Read

Display Controller

Timing Generator

INTR

IRQ13

3

REQ/GNT

Pairs

PCI 4

SDRAM

Clocks

64-bit RGB YUV

Geode™ Graphics

Scratchpad

Arbiter

SMI#

Geode™ I/O Companio

Clocks

Clocks

Fetch

MMU

Load/Store

Integer

Unit

Unit

Control

Controller

Palette RAM

Compression Buffer

2D Accelerator

ROP Unit

BLT Engine

VGA

Buffers

Buffers

SDRAM

Bus

Arbiter

PCI Host

Controller

multiplied

by “A”

divide by “B”

Companion Interface

April 2000

Geode™ GX1 Processor Series

Low Power Integrated x86 Solution

National Semiconductor and V irtual System Architecture are registered trademarks of National Semiconductor Corporation.

Geode, WebPAD, and VSA, are trademarks of National Semiconductor Corporation.

For a complete listing of National Semiconductor trademarks, please visit www.national.com/trademarks.

www.national.com 2 Revision 1.0

Geode™ GX1 Processor Series

While the x86 core provides maximum compatibility with

the vast amount of Internet content available, the intelligent

integration of several other functions, such as audio and

graphics, offers a true system-levelmultimedia solution.

The Geode GX1 processor core is a proven x86 design

that offers competitive performance. It contains integer and

floating point execution units based on sixth-generation

technology. The integer core contains a single, five-stage

execution pipeline and offers advanced features such as

operand forwarding, branch target buffers, and extensive

write buffering. Accesses to the 16 KB write-back L1 cache

are dynamically reordered to eliminate pipeline stalls when

fetching operands.

In addition to the advanced CPU features, the GX1 processor integrates a host of functions typically implemented

with external components. A full function graphics accelerator contains a VGA (video graphics array) controller, bitBLT engine, and a ROP (raster operations) unit for

complete GUI (Graphical User Interface) acceleration

under most operating systems. A display controller contains additional video buffering to enable >30 fps MPEG1

playback and video overlay when used with a National

Semiconductor Geode I/O or graphics companion chip

(e.g., CS5530 or CS9211). Graphics and system memory

accesses are supported by a tightly coupled SDRAM controller which eliminates the need for an external L2 cache.

A PCI host controller supports up to three bus masters for

additional connectivity and multimedia capabilities.

The GX1 processor also incorporates Vir tual System

Architecture

®

(VSA™) technology. VSA technology

enables the XpressGRAPHICS and XpressAUDIO subsystems. Software handlers are available that provide full

compatibility for industry standard VGA and 16-bit audio

functions that are transparent at the operating system level.

Together the National Semiconductor I/O companion and

GX1 processor Geode devices provide a scalable, flexible,

low-power, system-level solution well suited for a wide

array of information appliances ranging from hand-held

personal information access devices to digital set-top

boxes and thin clients.

Features

General Features

Packaging:

— 352-Terminal Ball Grid Array (BGA) or

— 320-Pin Staggered Pin Grid Array (SPGA)

0.18-micron four layer metal CMOS process

Split rail design:

— Available 1.6V, 1.8V, or 2.0V core

— 3.3V I/O interface

Fully static design

Low Typical Power Consumption:

— 0.8W @ 1.6V/200 MHz

— 1.2W @ 2.0V/300 MHz

Note: Typical power consumption is defined as an aver-

age, measured running Windows at 80% Active

Idle (Suspend-on-Halt) with a display resolution of

800x600x8 bpp @ 75 Hz.

Speeds offered up to 300 MHz

Unified Memory Architecture

— Frame buffer and video memory reside in main

memory

— Minimizes PCB (Printed Circuit Board) area require-

ments

— Reduces system cost

Compatiblewith multiple Geode I/O companion devices

provided by National Semiconductor

32-Bit x86 Processor

Supports Intel’s MMX instruction set extension for the

acceleration of multimedia applications

16 KB unified L1 cache

Six-stage pipelined integer unit

Integrated Floating Point Unit (FPU)

Memory Management Unit (MMU) adheres to standard

paging mechanisms and optimizes code fetch performance:

— Load-store reordering gives priority to memory reads

— Memory-read bypassing eliminates unnecessary or

redundant memor y reads

Re-entrant System Management Mode (SMM)

enhanced for VSA technology

Revision 1.0 3 www.national.com

Geode™ GX1 Processor Series

Flexible Power Management

Supports a wide variety of standards:

— APM (Advanced PowerManagement) for Legacy

power management

— ACPI (Advanced Configuration and Power Interface)

for Windows power management

– Direct support forall standard processor (C0-C4)

states

— OnNOW design initiative compliant

Supports a wide variety of hardware and software

controlled modes:

— Active Idle (core-only stopped, display active)

— Standby (core and all integrated functions halted)

— Sleep (core and integrated functions halted and all

external clocks stopped)

— Suspend Modulation (automatic throttling of CPU

core via Geode I/O or graphics companion chip)

– Programmableduty cycle for optimal performance/

thermal balancing

— Several dedicated and programmable wake-up

events (via Geode I/O or graphics companion chip)

PCI Host Controller

Several arbitration schemes supported

Directlysupports up to three PCI bus masters,more with

external logic

Synchronous to CPU core

Allows external PCI master accesses to main memory

concurrent with CPU accesses to L1 cache

Virtual Systems Architecture Technology

Innovative architecture allowing OS independent (software) virtualization of hardware functions

Provides XpressGRAPHICS subsystem:

— High performance legacy VGA core compatibility

Note: The GUI acceleration is pure hardware.

Provides 16-bit XpressAUDIO subsystem:

— 16-bit stereo FM synthesis

—OPL3emulation

— Supports MPU-401 MIDIinterface

— Hardware assist provided v ia Geode I/O companion

chip

Additional hardware functions can be supported as

needed

2D Graphics Accelerator

Accelerates BitBLTs, line draw, text:

— Bresenham vector engine

Supports all 256 RasterOperations (ROPs)

Supports transparent BLTs and page flipping for

Microsoft’s DirectDraw

Runs at core clock frequency

Full VGA and VESA mode support

Special "driver level” instructions utilize internal

scratchpad for enhanced performance

Display Controller

Display Compression Technology (DCT) architecture

greatly reduces memory bandwidth consumption of

display refresh

Supports a separate video buffer and data path to

enable video acceleration in Geode I/O and graphics

companion chips

Internal palette RAM for gamma correction

Direct interface to GeodeI/O and graphics companion

chips for CRT and TFT flat panel support eliminates the

need for an external RAMDAC

Hardware cursor

Supports up to 1280x1024x8 bpp and 1024x768x16 bpp

XpressRAM

SDRAM interface tightly coupled to CPU coreand

graphics subsystem for maximum efficiency

64-Bit wide memory bus

Support for:

— Two 168-pin unbuffered DIMMs

— Up to 16 simultaneously open banks

— 16-byte reads (burst length of two)

— Up to 512MB total memory supported

Diverse Operating System Support

Microsoft’s Windows 2000, Windows 95, Windows 98,

and Windows NT in non PC applications; along with

Windows CE and Windows NTE

WindRiverSystem’s VxWorks

QNX Software Systems’ QNX

Linux

www.national.com 4 Revision 1.0

Geode™ GX1 Processor Series

Table of Contents

1.0 ArchitectureOverview..............................................10

1.1 INTEGERUNIT ............................................................11

1.2 FLOATINGPOINTUNIT .....................................................11

1.3 WRITE-BACKCACHEUNIT ..................................................11

1.4 MEMORYMANAGEMENTUNIT...............................................11

1.5 INTERNALBUSINTERFACEUNIT.............................................11

1.6 INTEGRATED FUNCTIONS . . . . ..............................................12

1.6.1 Graphics Accelerator . . . ..............................................12

1.6.2 DisplayController....................................................12

1.6.3 XpressRAMMemorySubsystem ........................................12

1.6.4 PCIController.......................................................12

1.7 GEODEGX1/CS5530SYSTEMDESIGNS .......................................13

1.7.1 ReferenceDesigns...................................................16

2.0 SignalDefinitions..................................................19

2.1 PINASSIGNMENTS ........................................................20

2.2 SIGNALDESCRIPTIONS ....................................................31

2.2.1 SystemInterfaceSignals ..............................................31

2.2.2 PCIInterfaceSignals .................................................33

2.2.3 MemoryControllerInterfaceSignals .....................................36

2.2.4 VideoInterfaceSignals ...............................................37

2.2.5 Power,Ground,andNoConnectSignals..................................39

2.2.6 InternalTestandMeasurementSignals...................................39

3.0 ProcessorProgramming............................................41

3.1 COREPROCESSORINITIALIZATION ..........................................41

3.2 INSTRUCTIONSETOVERVIEW...............................................42

3.2.1 LockPrefix .........................................................42

3.3 REGISTERSETS...........................................................43

3.3.1 ApplicationRegisterSet...............................................43

3.3.1.1 GeneralPurposeRegisters ............................................43

3.3.1.2 SegmentRegisters...................................................45

3.3.1.3 InstructionPointerRegister ............................................45

3.3.1.4 EFLAGSRegister....................................................46

3.3.2 SystemRegisterSet .................................................47

3.3.2.1 ControlRegisters....................................................48

3.3.2.2 ConfigurationRegisters...............................................50

3.3.2.3 DebugRegisters.....................................................55

3.3.2.4 TLBTestRegisters...................................................57

3.3.2.5 CacheTestRegisters.................................................59

3.3.3 ModelSpecificRegister ...............................................62

3.3.4 TimeStampCounter .................................................62

3.4 ADDRESSSPACES.........................................................63

3.4.1 I/OAddressSpace...................................................63

3.4.2 MemoryAddressSpace...............................................64

Revision 1.0 5 www.national.com

Geode™ GX1 Processor Series

Table of Contents (Continued)

3.5 OFFSET,SEGMENT,ANDPAGINGMECHANISMS ...............................64

3.5.1 Offset Mechanism . . . . . ..............................................64

3.5.2 SegmentMechanisms ................................................66

3.5.2.1 RealModeSegmentMechanism........................................66

3.5.2.2 Virtual8086ModeSegmentMechanism..................................66

3.5.2.3 SegmentMechanisminProtectedMode..................................67

3.5.2.4 SegmentSelectors...................................................67

3.5.3 Descriptors.........................................................70

3.5.3.1 GlobalandLocalDescriptorTableRegisters...............................70

3.5.3.2 SegmentDescriptors.................................................70

3.5.3.3 Task,Gate,Interrupt,andApplicationandSystemDescriptors.................71

3.5.4 PagingMechanism...................................................77

3.6 INTERRUPTSANDEXCEPTIONS .............................................79

3.6.1 Interrupts ..........................................................79

3.6.2 Exceptions .........................................................79

3.6.3 InterruptVectors.....................................................80

3.6.3.1 InterruptVectorAssignments...........................................80

3.6.3.2 InterruptDescriptorTable..............................................80

3.6.4 InterruptandExceptionPriorities........................................81

3.6.5 ExceptionsinRealMode ..............................................82

3.6.6 ErrorCodes ........................................................82

3.7 SYSTEMMANAGEMENTMODE ..............................................83

3.7.1 SMMOperation .....................................................84

3.7.2 SMI#Pin...........................................................85

3.7.3 SMMConfigurationRegisters ..........................................85

3.7.4 SMMMemorySpaceHeader...........................................85

3.7.5 SMMInstructions ....................................................87

3.7.6 SMMMemorySpace .................................................88

3.7.7 SMIGenerationforVirtualVGA .........................................88

3.7.8 SMMServiceRoutineExecution ........................................88

3.7.9 SMINesting ........................................................88

3.7.9.1 CPUStatesRelatedtoSMMandSuspendMode...........................90

3.8 HALTANDSHUTDOWN .....................................................91

3.9 PROTECTION .............................................................91

3.9.1 PrivilegeLevels .....................................................91

3.9.2 I/OPrivilegeLevels ..................................................91

3.9.3 PrivilegeLevelTransfers ..............................................92

3.9.3.1 Gates.............................................................92

3.9.4 InitializationandTransitiontoProtectedMode..............................93

3.10 VIRTUAL8086MODE .......................................................93

3.10.1 MemoryAddressing..................................................93

3.10.2 Protection ..........................................................93

3.10.3 Interrupt Handling . . . . . . ..............................................93

3.10.4 EnteringandLeavingVirtual8086Mode..................................93

3.11 FLOATINGPOINTUNITOPERATIONS .........................................94

3.11.1 FPURegisterSet ....................................................94

3.11.2 FPUTagWordRegister ...............................................94

3.11.3 FPUStatusRegister .................................................94

3.11.4 FPUModeControlRegister............................................94

www.national.com # Revision 1.0

Geode™ GX1 Processor Series

Table of Contents (Continued)

4.0 Integrated Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

4.1 INTEGRATED FUNCTIONS PROGRAMMING INTERFACE . . . . . . . . .................97

4.1.1 Graphics Control Register . . . . . . . . . . . . . . . ..............................97

4.1.2 ControlRegisters ....................................................99

4.1.3 Graphics Memory . . . . . . ..............................................99

4.1.4 ScratchpadRAM ...................................................100

4.1.4.1 InitializationofScratchpadRAM........................................100

4.1.4.2 ScratchpadRAMUtilization...........................................100

4.1.4.3 BLTBuffer.........................................................100

4.1.5 DisplayDriverInstructions ............................................102

4.1.6 CPU_READ/CPU_WRITEInstructions ..................................102

4.2 INTERNALBUSINTERFACEUNIT............................................103

4.2.1 FPUErrorSupport ..................................................103

4.2.2 A20MSupport .....................................................103

4.2.3 SMIGeneration ....................................................103

4.2.4 640KBto1MBRegion ..............................................103

4.2.5 InternalBusInterfaceUnitRegisters ....................................104

4.3 MEMORYCONTROLLER ...................................................107

4.3.1 MemoryArrayConfiguration ..........................................108

4.3.2 MemoryOrganizations...............................................109

4.3.3 SDRAMCommands.................................................110

4.3.3.1 SDRAMInitializationSequence........................................111

4.3.4 MemoryControllerRegisterDescription .................................112

4.3.5 AddressTranslation .................................................117

4.3.5.1 HighOrderInterleaving ..............................................117

4.3.5.2 AutoLowOrderInterleaving...........................................117

4.3.5.3 PhysicalAddresstoDRAMAddressConversion...........................117

4.3.6 MemoryCycles ....................................................120

4.3.7 SDRAMInterfaceClocking............................................123

4.4 GRAPHICSPIPELINE ......................................................125

4.4.1 BitBLT/VectorEngine ................................................125

4.4.2 Master/SlaveRegisters ..............................................126

4.4.3 PatternGeneration..................................................126

4.4.3.1 MonochromePatterns ...............................................127

4.4.3.2 DitherPatterns.....................................................127

4.4.3.3 ColorPatterns......................................................128

4.4.4 SourceExpansion ..................................................128

4.4.5 RasterOperations ..................................................128

4.4.6 Graphics Pipeline Register Descriptions . . . . .............................129

Revision 1.0 7 www.national.com

Geode™ GX1 Processor Series

Table of Contents (Continued)

4.5 DISPLAYCONTROLLER....................................................134

4.5.1 DisplayFIFO ......................................................135

4.5.2 CompressionTechnology.............................................135

4.5.3 HardwareCursor ...................................................136

4.5.4 DisplayTimingGenerator.............................................136

4.5.5 DitherandFrameRateModulation .....................................136

4.5.6 DisplayModes .....................................................136

4.5.7 Graphics Memory Map . . .............................................140

4.5.7.1 DCMemoryOrganizationRegisters.....................................140

4.5.7.2 FrameBufferandCompressionBufferOrganization........................140

4.5.7.3 VGADisplaySupport................................................141

4.5.8 DisplayControllerRegisters...........................................141

4.5.8.1 ConfigurationandStatusRegisters.....................................144

4.5.9 MemoryOrganizationRegisters........................................148

4.5.10 TimingRegisters ...................................................150

4.5.11 CursorPositionandMiscellaneousRegisters .............................153

4.5.12 PaletteAccessRegisters .............................................154

4.5.13 FIFODiagnosticRegisters ............................................155

4.5.14 CS5530DisplayControllerInterface ....................................156

4.5.14.1 CS5530VideoPortDataTransfer ......................................157

4.6 VIRTUALVGASUBSYSTEM.................................................158

4.6.1 TraditionalVGAHardware ............................................158

4.6.1.1 VGAMemoryOrganization............................................159

4.6.1.2 VGAFrontEnd.....................................................160

4.6.1.3 AddressMapping...................................................160

4.6.1.4 VideoRefresh......................................................160

4.6.1.5 VGAVideoBIOS ...................................................161

4.6.2 VirtualVGA .......................................................161

4.6.2.1 DatapathElements..................................................161

4.6.2.2 GX1VGAHardware.................................................162

4.6.2.3 SMIGeneration ....................................................162

4.6.2.4 VGARangeDetection ...............................................162

4.6.2.5 VGASequencer....................................................162

4.6.2.6 VGAWrite/ReadPath................................................162

4.6.2.7 VGAAddressGenerator..............................................162

4.6.2.8 VGAMemory ......................................................163

4.6.3 VGAConfigurationRegisters ..........................................163

4.6.4 VirtualVGARegisterDescriptions ......................................165

4.7 PCICONTROLLER ........................................................167

4.7.1 X-BusPCISlave....................................................167

4.7.2 X-BusPCIMaster ..................................................167

4.7.3 PCIArbiter ........................................................167

4.7.4 GeneratingConfigurationCycles .......................................167

4.7.5 GeneratingSpecialCycles............................................167

4.7.6 PCIConfigurationSpaceControlRegisters...............................168

4.7.7 PCIConfigurationSpaceRegisters .....................................169

4.7.8 PCICycles ........................................................174

4.7.8.1 PCIReadTransaction................................................174

4.7.8.2 PCIWriteTransaction................................................175

4.7.8.3 PCIArbitration .....................................................176

4.7.8.4 PCIHaltCommand..................................................176

www.national.com # Revision 1.0

Geode™ GX1 Processor Series

Table of Contents (Continued)

5.0 PowerManagement ...............................................177

5.1 POWERMANAGEMENTFEATURES ..........................................177

5.1.1 SystemManagementMode...........................................177

5.1.2 Suspend-on-Halt ...................................................177

5.1.3 CPUSuspend .....................................................177

5.1.3.1 SuspendModulationforThermalManagement............................178

5.1.3.2 SuspendModulationforPowerManagement..............................178

5.1.4 3VoltSuspend .....................................................178

5.1.5 GX1ProcessorSerialBus ............................................178

5.1.6 AdvancedPowerManagement(APM)Support ............................178

5.2 SUSPENDMODESANDBUSCYCLES ........................................179

5.2.1 TimingDiagramforSuspend-on-Halt....................................179

5.2.2 InitiatingSuspendwithSUSP# ........................................180

5.2.3 Stopping the Input Clock .............................................181

5.2.4 SerialPacketTransmission ...........................................181

5.3 POWERMANAGEMENTREGISTERS .........................................182

6.0 ElectricalSpecifications............................................185

6.1 PARTNUMBERS/PERFORMANCECHARACTERISTICS..........................185

6.2 ELECTRICALCONNECTIONS ...............................................186

6.2.1 Power/GroundConnectionsandDecoupling ..............................186

6.2.1.1 PowerPlanes......................................................186

6.2.2 NC-DesignatedPins.................................................188

6.2.3 Pull-UpandPull-DownResistors.......................................188

6.2.4 UnusedInputPins ..................................................188

6.3 ABSOLUTEMAXIMUMRATINGS.............................................189

6.4 RECOMMENDEDOPERATINGCONDITIONS...................................190

6.5 DCCHARACTERISTICS ....................................................191

6.5.1 Input/OutputDCCharacteristics .......................................191

6.5.2 DCCurrent........................................................191

6.5.2.1 DefinitionofCPUPowerStates........................................191

6.5.2.2 Definition and Measurement Techniques of CPU Current Parameters. . . . . . . . . . .191

6.5.2.3 Definitionof System Conditions for Measuring “On” Parameters. . . . . . . . . . . . . . . 192

6.5.2.4 DCCurrentMeasurements............................................193

6.6 I/O CURRENT DE-RATING CURVE . . . . . . . . . . . . . . .............................196

6.6.1 DisplayResolution ..................................................196

6.6.2 MemorySpeed.....................................................196

6.6.3 I/OCurrentDe-ratingCurve...........................................196

6.7 ACCHARACTERISTICS ....................................................197

7.0 PackageSpecifications............................................207

7.1 THERMALCHARACTERISTICS ..............................................207

7.1.1 HeatsinkConsiderations .............................................208

7.2 MECHANICALPACKAGEOUTLINES..........................................210

Revision 1.0 9 www.national.com

Geode™ GX1 Processor Series

Table of Contents (Continued)

8.0 InstructionSet....................................................213

8.1 GENERALINSTRUCTIONSETFORMAT.......................................213

8.1.1 Prefix(Optional) ...................................................214

8.1.2 Opcode...........................................................214

8.1.2.1 wField(OperandSize)...............................................214

8.1.2.2 dField(OperandDirection) ...........................................214

8.1.2.3 sField(ImmediateDataFieldSize).....................................215

8.1.2.4 eeeField(MOV-InstructionRegisterSelection)............................215

8.1.3 modandr/mByte(MemoryAddressing) .................................215

8.1.4 regField..........................................................216

8.1.4.1 sreg2Field(ES,CS,SS,DSRegisterSelection)...........................216

8.1.4.2 sreg3Field(FSandGSSegmentRegisterSelection).......................216

8.1.5 s-i-bByte(Scale,Indexing,Base) ......................................216

8.1.5.1 ssField(ScaleSelection).............................................216

8.1.5.2 indexField(IndexSelection) ..........................................217

8.1.5.3 BaseField(s-i-bPresent).............................................217

8.2 CPUIDINSTRUCTION......................................................218

8.2.1 Standard CPUID Levels . .............................................218

8.2.1.1 CPUIDInstructionwithEAX=00000000h...............................218

8.2.1.2 CPUIDInstructionwithEAX=00000001h...............................219

8.2.1.3 CPUIDInstructionwithEAX=00000002h...............................219

8.2.2 ExtendedCPUIDLevels..............................................220

8.2.2.1 CPUIDInstructionwithEAX=80000000h...............................220

8.2.2.2 CPUIDInstructionwithEAX=80000001h...............................220

8.2.2.3 CPUID Instruction with EAX = 8000 0002h, 80000003h, 8000 0004h . . . . . . . . . .221

8.2.2.4 CPUIDInstructionwithEAX=80000005h...............................221

8.3 PROCESSORCOREINSTRUCTIONSET ......................................222

8.3.1 Opcodes ..........................................................222

8.3.2 ClockCounts ......................................................222

8.3.3 Flags ............................................................222

8.4 FPUINSTRUCTIONSET....................................................234

8.5 MMXINSTRUCTIONSET ...................................................239

8.6 EXTENDEDMMXINSTRUCTIONSET.........................................244

Appendix A Support Documentation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 246

A.1 ORDERINFORMATION ....................................................246

A.2 DATABOOKREVISIONHISTORY ............................................246

www.national.com 10 Revision 1.0

Geode™ GX1 Processor Series

1.0 Architecture Overview

The Geode GX1 processor series represents the sixth generation of x 86-compatible 32-bit processors with sixth-generation features. The decoupled load/store unit allows

reordering of load/store traffic to achieve higher performance. Other features include single-cycle execution, single-cycle instruction decode, 16 KB write-back cache, and

clock rates up to 300MHz. These features are madepossible by theuse of advanced-process technologies and pipelining.

The GX1 processor has low power consumption at all clock

frequencies. Where additional power savings are required,

designers can make use of Suspend Mode, Stop Clock

capability, and SystemManagement Mode (SMM).

The GX1 processor is divided into major functional blocks

(as shown in Figure 1-1):

• Integer Unit

• Floating Point Unit (FPU)

• Write-Back Cache Unit

• Memory ManagementUnit (MMU)

• Internal Bus Interface Unit

• Integrated Functions

Instructions are executed in the integer unit and in the floating point unit. The cache unit stores the mostrecently used

data and instructions and providesfast access to this information for the integer and floating point units.

Figure 1-1. Internal Block Diagram

Write-Back

Unit

FPU

Internal Bus Interface Unit

Graphics Memory Display PCI

SDRAM Port CS5530

PCI Bus

Integer

Cache Unit

Integrated

Functions

MMU

(CRT/LCD TFT)

X-Bus

Pipeline Controller Controller Controller

C-Bus

Revision 1.0 11 www.national.com

Geode™ GX1 Processor Series

Architecture Overview (Continued)

1.1 INTEGER UNIT

The integer unit consists of:

• Instruction Buffer

• Instruction Fetch

• Instruction Decoder and Execution

The pipelined integer unit fetches, decodes, and executes

x86 instructions through the use of a five-stage integer

pipeline.

The instruction fetch pipeline stage generates, from the onchip cache, a continuous high-speed instruction stream for

use by the processor. Up to 128 bits of code are read during a single clock cycle.

Branch prediction logic within the prefetch unit generates a

predicted target address for unconditional or conditional

branch instructions. When a branch instruction is detected,

the instruction fetch stage starts loading instructions at the

predicted address within a single clock cycle. Up to 48

bytes of code are queued prior to the instruction decode

stage.

The instruction decode stage evaluates the code stream

provided by the instruction fetch stage and determines the

number of bytes in each instruction and the instruction

type. Instructions are processed and decoded at a maximum rate of one instruction per clock.

The address calculation function is pipelined and contains

two stages, AC1 and AC2. If the instruction refers to a

memory operand, AC1 calculates a linearmemory address

for the instruction.

The AC2 stage performs any required memory management functions, cache accesses, and register file

accesses. If a floating point instruction is detected by AC2,

the instruction is sent to the floating point unit for processing.

The execution stage, under control of microcode, executes

instructions using the operands provided by the address

calculation stage.

Write-back, the last stage of the integer unit, updates the

register file within theinteger unit or writes to the load/store

unit within the memory management unit.

1.2 FLOATING POINT UNIT

The floating point unit (FPU) interfaces to the integer unit

and the cache unit through a 64-bit bus. The FPU is x87instruction-set compatible and adheres to the IEEE-754

standard. Because almost all applications that contain FPU

instructions also contain integer instructions, the GX1 processor’s FPU achieves high performance by completing

integer and FPU operations in parallel.

FPU instructions are dispatched to the pipeline within the

integer unit. The address calculation stage of the pipeline

checks for memory management exceptions and accesses

memory operands for use by the FPU. Once the instructions and operands have been provided to the FPU, the

FPU completes instruction execution independently of the

integer unit.

1.3 WRITE-BACK CACHE UNIT

The 16 KB write-back unified (data/instruction) cache is

configured as four-way set associative. The cache stores

up to 16 KB of code and data in 1024 cache lines.

The GX1 processor provides the ability to allocate a portion

of the L1 cache as a scratchpad, which is used to accelerate the Virtual Systems Architecture technology algorithms

as well as for some graphics operations.

1.4 MEMORY MANAGEMENT UNIT

The memory management unit (MMU) translates the linear

address supplied by the integer unit into a physical address

to be used by the cache unit and the internal bus interface

unit. Memory management procedures are x86-compatible, adhering to standard paging mechanisms.

The M MU also contains a load/store unit that is responsible

for scheduling cache and external memory accesses. The

load/store unit incorporates two performance-enhancing

features:

• Load-store reordering that gives memory reads

required by the integer unit a priority over writes to

external memory .

• Memory-read bypassing that eliminates unnecessary

memory reads by using valid data from the execution

unit.

1.5 INTERNAL BUS INTERFACE UNIT

The internal bus interface unit provides a bridge from the

GX1 processor to the integrated system functions (i.e.,

memory subsystem, display controller, graphics pipeline)

and the PCI bus interface.

When external memory access is required, the physical

address is calculated by the memory management unit and

then passed to the internal bus interface unit, which translatesthecycletoanX-Buscycle(theX-Busisaproprietary

internal bus which provides a common interface for all of

the integrated functions). The X-Bus memory cycle is arbitrated between other pending X-Bus memory requests to

the SDRAM controller before completing.

In addition, the internal bus interface unit provides configuration control for up to 20 different regions within system

memory with separate controls for read access, write

access, cacheability, and PCI access.

www.national.com 12 Revision 1.0

Geode™ GX1 Processor Series

Architecture Overview (Continued)

1.6 INTEGRATED FUNCTIONS

The GX1 processor integrates the following functions traditionally implemented using external devices:

• High-performance 2D graphics accelerator

• Separate CRT and TFT control from the display

controller

• SDRAM memory controller

• PCI bridge

The processor has also been enhanced to support VSA

technology implementation.

The GX1 processor implements a Unified Memory Architecture (UMA). By using DCT (Display Compression Technology) architecture, the performance degradation inherent

in traditional UMA systems is eliminated.

1.6.1 Graphics Accelerator

The graphics accelerator is a full-featured GUI accelerator.

The graphics pipeline implements a bitBLT engine for

frame buffer bitBLTs and rectangular fills. Additional

instructions in the integer unit may be processed, as the

bitBLT engine assists the CPUin the bitBLToperations that

take place between system memory and the frame buffer.

This combination of hardware and software is used by the

display driver to provide very fast bidirectional transfers

between system memory and the frame buffer. The bitBLT

engine also draws randomly oriented vectors, and scanlines for polygon fill. All of the pipeline operations described

in the following list can be applied to any bitBLT operation.

• Pattern Memory: Renderwith 8x8 dither, 8x8 monochrome, or 8x1 color pattern.

• Color Expansion: Expand monochrome bitmaps to full

depth 8- or 16-bit colors.

• Transparency: Suppresses drawing of background

pixels for transparent text.

• Raster Operations: Boolean operation combines

source, destination, and pattern bitmaps.

1.6.2 Display Controller

The display port is a direct interface to the Geode I/O companion (i.e., CS5530) which drives a TFT flat panel display,

LCD panel, or a CRT display.

The display controller (video generator) retrieves image

data from the frame buffer, performs a color-look-up if

required, inserts the cursor overlay into the pixel stream,

generates display timing, and formats the pixel data for output to a variety of display devices. The display controller

contains DCT architecture that allows the GX1 processor

to refresh the display from a compressed copy of the frame

buffer. DCT architecture typically decreases the screen

refresh bandwidth requirement by a factor of 15 to 20, minimizing bandwidth contention.

1.6.3 XpressRAM Memory Subsystem

The memory controller drives a 64-bit SDRAM port directly.

The SDRAM memory array contains both the main system

memory and the graphics frame buffer. Up to four module

banks of SDRAM are supported. Each module bank can

havetwo or four component banks depending on the memory size and organization. The maximum configuration is

four module banks with four component banks, each providing a total of 16 open banks. The maximum memory

size is 512 MB.

The memory controller handles multiple requests for memory data from the GX1 processor, the graphics accelerator

and the display controller. The memory controller contains

extensive buffering logic that helps minimize contention for

memory bandwidth between graphics and CPU requests.

The memory controller cooperates with the internal bus

controller to determinethe cacheability of all memory references.

1.6.4 PCI Controller

The GX1 processor incorporates a full-function PCI interface module that includes the PCI arbiter. All accesses to

external I/O devices are sent over the PCI bus, although

most memory accesses are serviced by the SDRAM controller. The internal bus interface unit contains address

mapping logic that determines if memory accessesare targetedfortheSDRAMorforthePCIbus.ThePCIbusina

GX1 based system is 3.3 volt only. Do not connect 5 volt

deviceson this bus.

Revision 1.0 13 www.national.com

Geode™ GX1 Processor Series

Architecture Overview (Continued)

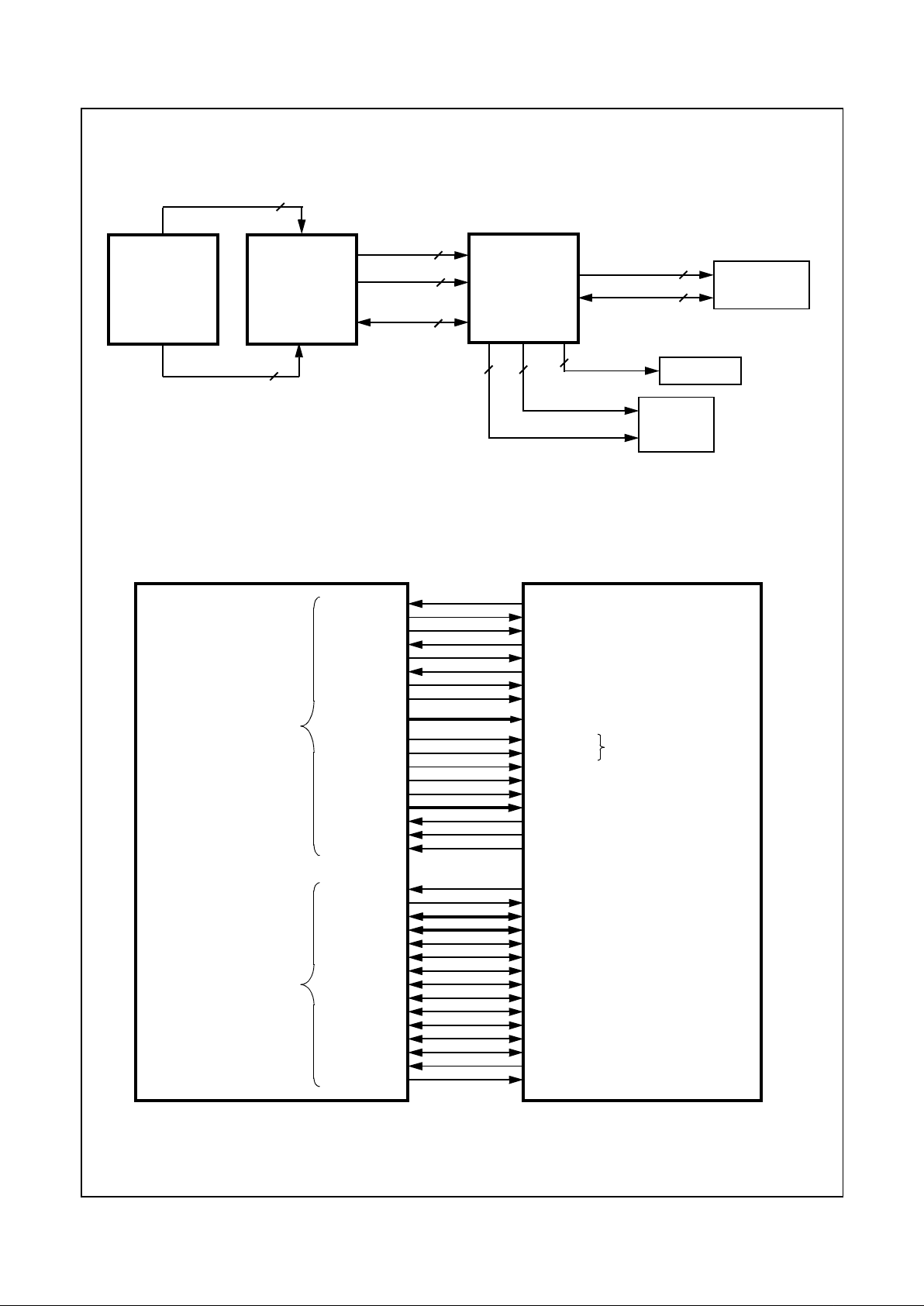

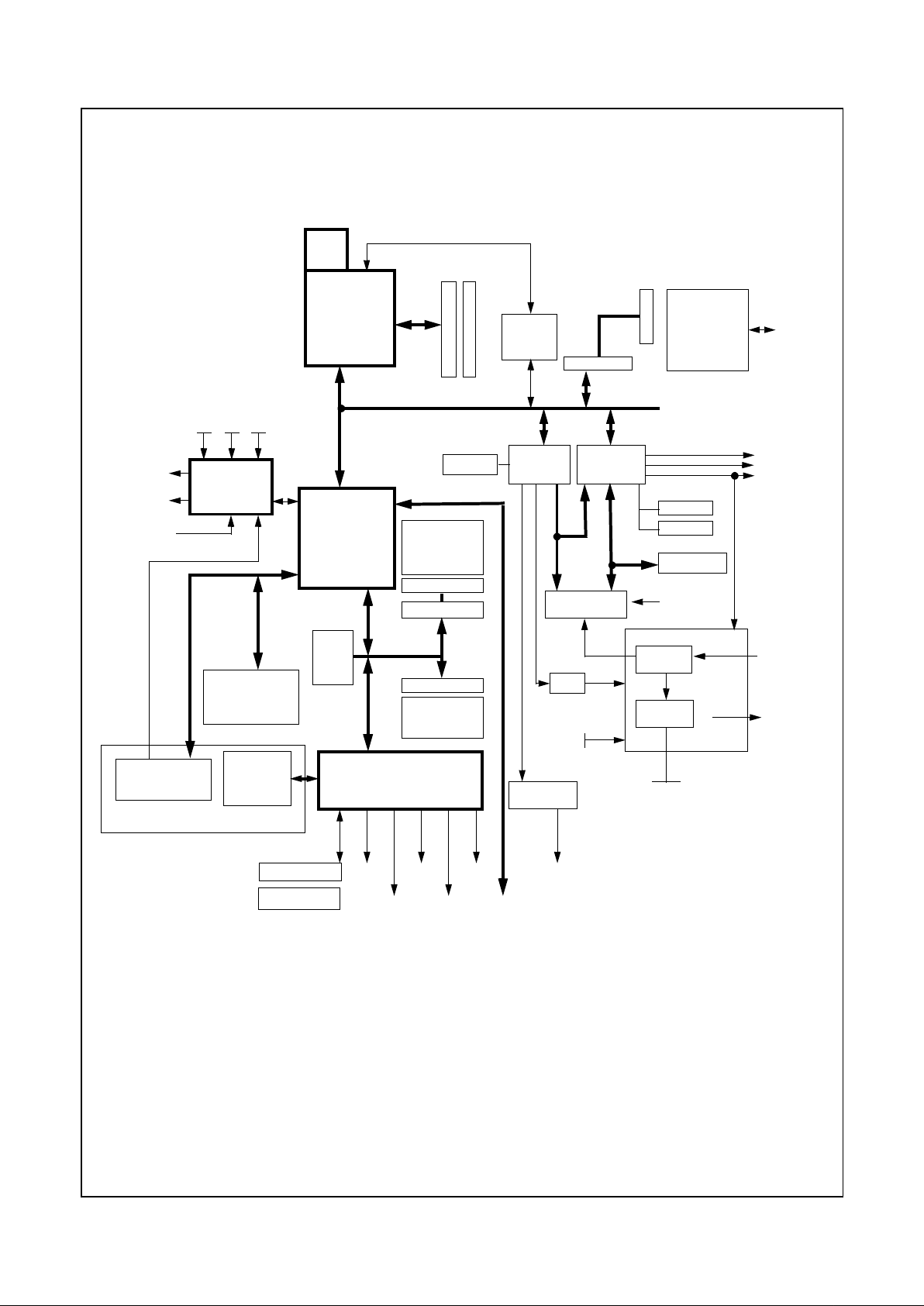

1.7 GEODE GX1/CS5530 SYSTEM DESIGNS

A GX1 processor and Geode CS5530 I/O companion

based design provides high performance using 32-bit x86

processing. The two chips integrate video, audio and memory interface functions normally performed by external

hardware.The CS5530 enables the fullfeatures of theGX1

processor with MMX support. These features include full

VGA and VESA video, 16-bit stereo sound, IDE interface,

ISA interface, SMM power management, and IBM’s AT

compatibility logic. In addition, the CS5530 provides an

Ultra DMA/33 interface, MPEG1 assist, and AC97 Version

2.0 compliant audio.

Figure 1-2 shows a basic block system diagram which also

includes the Geode CS9211 graphics companion for

designs that need to interface to a Dual Scan Super

Twisted Pneumatic (DSTN) panel (instead of a TFT panel).

Figure 1-3 shows an example of a CS9211 interface in a

typical GX1/CS5530 based system design. The CS9211

converts the digital RGB output of the CS5530 to the digital

output suitable for driving a color DSTN flat panel LCD. It

can drive all standard color DSTN flat panels up to a

1024x768 resolution.

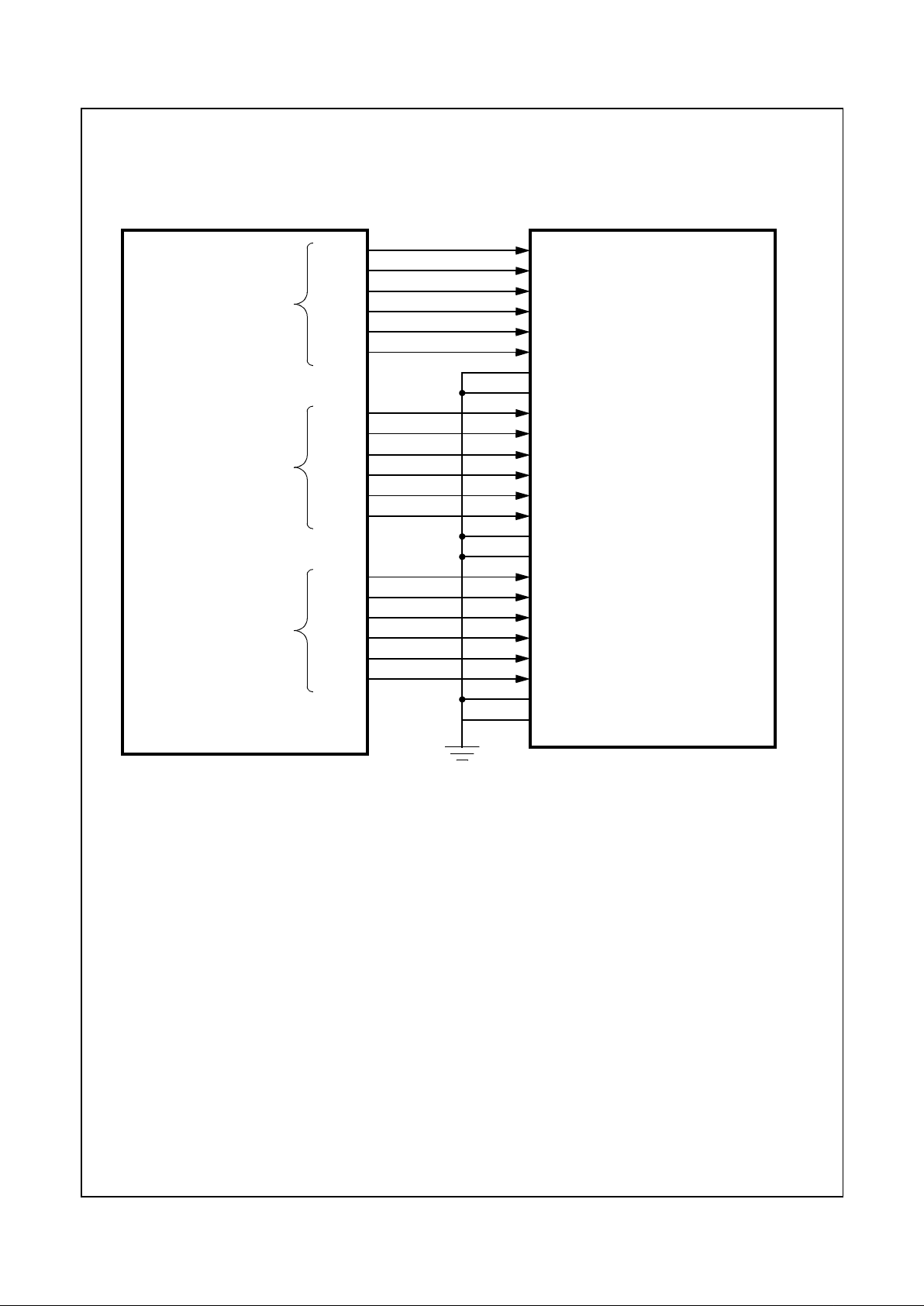

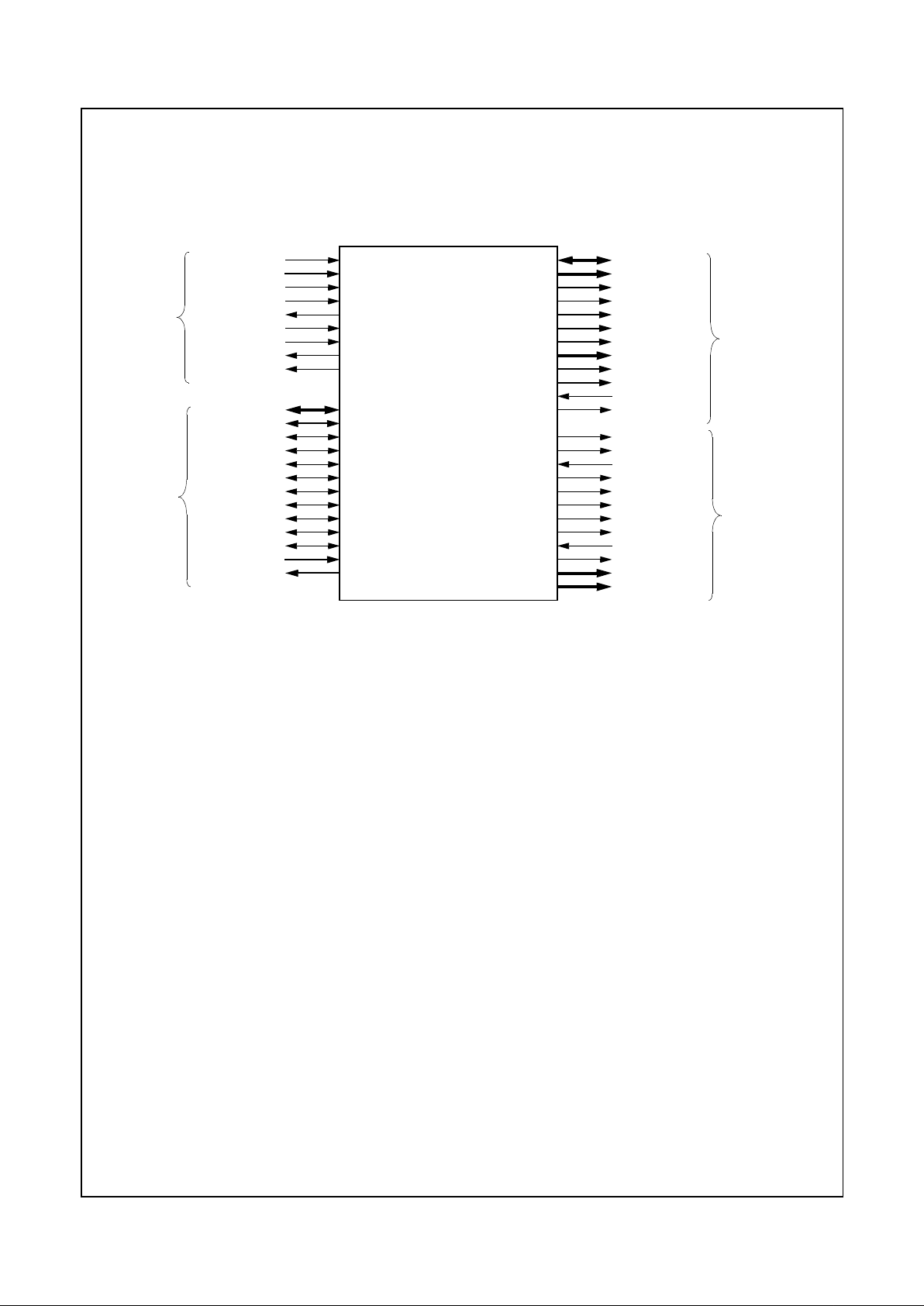

Figures 1-4 and 1-5 show the signal connections between

the GX1 processorand the CS5530. For connections to the

CS9211, refer to the CS9211 data book.

Figure 1-2. Geode™ GX1/CS5530 System Block Diagram

YUV Port

(Video)

RGB Port

PCI Interface

SDRAM

MD[63:0]

3.3V PCI Bus

Graphics Data

Video Data

Analog RGB

Digital RGB (to TFT or DSTN Panel)

CRT

TFT

Panel

USB

(2 Ports)

AC97

Codec

Speakers

CD

ROM

Audio

Microphone

GPIO

Port

(Graphics)

Super

ISA Bus

SDRAM

Serial

Packet

Clocks

I/O

BIOS

IDE

Devices

14.31818

MHz Crystal

IDE Control

DC-DC & Battery

CS9211

Graphics

Companion

DSTN Panel

Geode™

Geode™

CS5530

I/O Companion

Geode™

GX1

Processor

www.national.com 14 Revision 1.0

Geode™ GX1 Processor Series

Architecture Overview (Continued)

.

Figure 1-3. Geode™ CS9211 Interface System Diagram

Figure 1-4. Geode™ GX1/CS5530 Signal Connections

MemData

Addr & Control

21

16

LCD Power

3

Control

Panel Timing

424

Panel Data

DSTN/TFT

Pixel Port

18

Serial

4

PixelData

LCD

18

CS9211

Graphics

DRAM/SDRAM

256Kx16

GX1

Configuration

CS5530 I/O

Companion

Companion

Processor

Geode™

Geode™

Geode™

Video Port (YUV)

8

Timing Control

4

SYSCLK

SERIALP

IRQ13

SMI#

PCLK

CRT_HSYNC

CRT_VSYNC

PIXEL[17:0]

FP_HSYNC

FP_VSYNC

ENA_DISP

VID_VAL

VID_CLK

VID_DATA[7:0]

VID_RDY

INTR

SUSP#

SUSPA#

AD[31:0]

C/BE[3:0]#

PAR

FRAME#

IRDY#

TRDY#

STOP#

LOCK#

DEVSEL#

PERR#

SERR#

REQ0#

GX_CLK

PSERIAL

IRQ13

SMI#

PCLK

HSYNC

VSYNC

PIXEL[23:0]

FP_HSYNC

FP_VSYNC

ENA_DISP

VID_VAL

VID_CLK

VID_DATA[7:0]

VID_RDY

CPU_RST

INTR

SUSP#

SUSPA#

AD[31:0]

C/BE[3:0]#

PAR

FRAME#

IRDY#

TRDY#

STOP#

LOCK#

DEVSEL#

PERR#

SERR#

REQ#

GNT#GNT0#

Geode™ GX1 Geode™ CS5530

I/O Companion

Exclusive

Interconnect

Signals

(Do not connect to

any other device)

Nonexclusive

Interconnect

Signals

(May also connect

to other 3.3V circuitry)

Not needed if

CRT only (no TFT)

(Note)

Note: Refer to Figure 1-5 for interconnection of the pixel lines.

RESET

DCLK DCLK

Processor

Revision 1.0 15 www.national.com

Geode™ GX1 Processor Series

Architecture Overview (Continued)

Figure 1-5. PIXEL Signal Connections

PIXEL17

PIXEL16

PIXEL15

PIXEL14

PIXEL13

PIXEL12

PIXEL11

PIXEL10

PIXEL9

PIXEL8

PIXEL7

PIXEL6

PIXEL5

PIXEL4

PIXEL3

PIXEL2

PIXEL1

Geode™ CS5530

I/O Companion

PIXEL0

PIXEL23

PIXEL22

PIXEL21

PIXEL20

PIXEL19

PIXEL18

PIXEL17

PIXEL16

PIXEL15

PIXEL14

PIXEL13

PIXEL12

PIXEL11

PIXEL10

PIXEL9

PIXEL8

PIXEL7

PIXEL6

PIXEL5

PIXEL4

PIXEL3

PIXEL2

PIXEL1

PIXEL0

R

G

B

Geode™ GX1

Processor

www.national.com 16 Revision 1.0

Geode™ GX1 Processor Series

Architecture Overview (Continued)

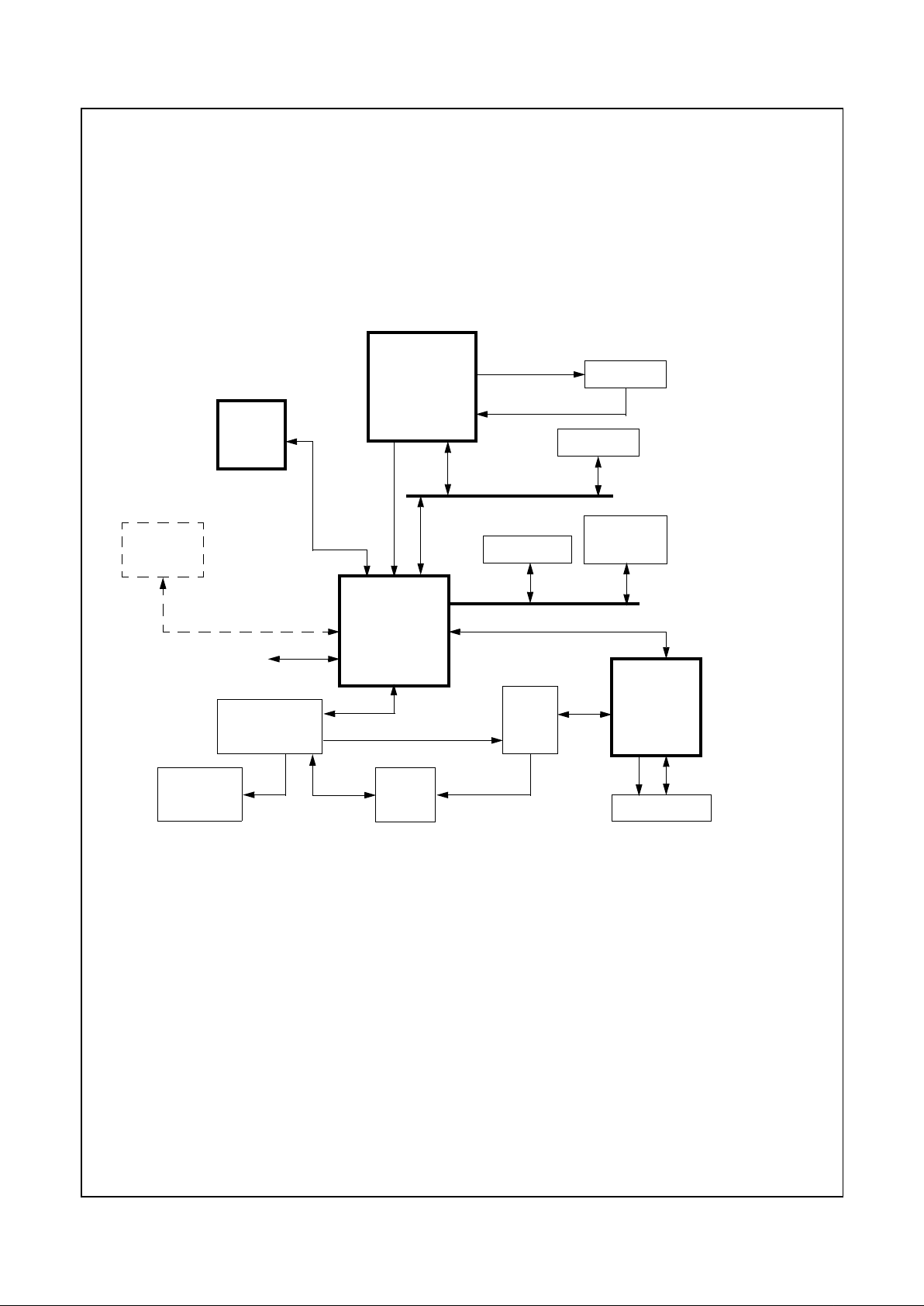

1.7.1 Reference Designs

As described previously, the GX1 series of integrated processors is designed specifically to work with National’s

Geode I/O and graphics companion devices. To help define

and drive the emerging information appliance market, several reference systems have been developed by National

Semiconductor. These GX1 processor based reference

systems provide optimized and targeted solutions for three

main segments of the information appliance market: Personal Internet Access, Thin Client, and Set-top Box. Contact your local National Semiconductor sales or field

support representative for further information on reference

designs for the information appliance market.

Figure 1-6. Example WebPAD™ System Diagram

PCMCIA

Touch

Control

512 KB DRAM

Li Batteries/

Charger

Data

3.3V PCI Bus

RF Interface

Backlight

Ultra DMA/33

Buttons

Pwr Mgmt

Embedded OS

Applications

DC Sense

Bootloader

Run-Time Diagnostics

Storage

Embedded OS

Applications

Bootloader

Run-Time Diagnostics

Storage

Microcontroller

DSTN

ISA Bus

USB Port

Control

Flash

Card

Optional

SDRAM

CS5530

I/O

Companion

Geode™

Geode™

CS9211

Graphics

Companion

Geode™

GX1

Processor

NSC

LM4549

Codec

Linear

Flash

(8 MB)

Revision 1.0 17 www.national.com

Geode™ GX1 Processor Series

Architecture Overview (Continued)

Figure 1-7. Example Thin Client System Diagram

SDRAM SO-DIMM

Video

3.3V PCI Bus

Termination

Reset

PWR CTL

CPU Core

Power

Power

Clock

MK1491-06

TFT

USB (2x)

CRT

MIC In

Audio Out

Term ination

64 MB Flash

ISA Bus

Generator

CS5530

I/O

Companion

Geode™

Geode™

GX1

Processor

NSC

LM4546

Codec

NSC

DP83815

Ethernet

Controller

NSC

PC97317IBW/VUL

SuperI/O

www.national.com 18 Revision 1.0

Geode™ GX1 Processor Series

Architecture Overview (Continued)

Figure 1-8. Example Set-Top Box System Diagram

CS5530

Notebook DVD

Drive

Notebook

Floppy

Drive

Internal Assembly Options

Flash

BIOS

2.5” UDMA33

Hard Drive

Headphone

Audio Line

Output

Tuner

AC3

Anlg

MIC MIC

CPU Temp.

Sensor

SDRAM DIMM

SDRAM DIMM

DMA

3.3V PCI Bus

1IN2

IN

CD In

Riser Slot

PCI Slot

Optional

LAN PCI

Card

LAN /

WAN

ISA Slot

Riser Slot

ROM Slot

WinCE ROM

Modul

e

TDA8006

LPT

COM

Mouse

(IR)

Keybd

(IR)

Front

Panel

USB

Ports

AC3

Anlg

Optional

V.90

Modem

SDRAM

PCM1723

IGS 50x5

Graphics

SAA7112

SGRAM

SGRAM

Video Port

TV Tuner

Composite

Video In

9638

TDA9851

TV

Tuner

Module

Arbiter

C-CUBE

“ZIVA”

CATV In

AC3

Digital

Tuner FM Out

VGA

S-Video

PAL or

NTSC

Audio

Line

Out

SPDIF

ISA Bus

I/O

Companion

GX1

LM4548

Codec

Processor

Geode™

Geode™

NSC

LM75

Output

FM In

Smartcard

NSC

PC97317VUL-ICF

SuperI/O

Revision 1.0 19 www.national.com

Geode™ GX1 Processor Series

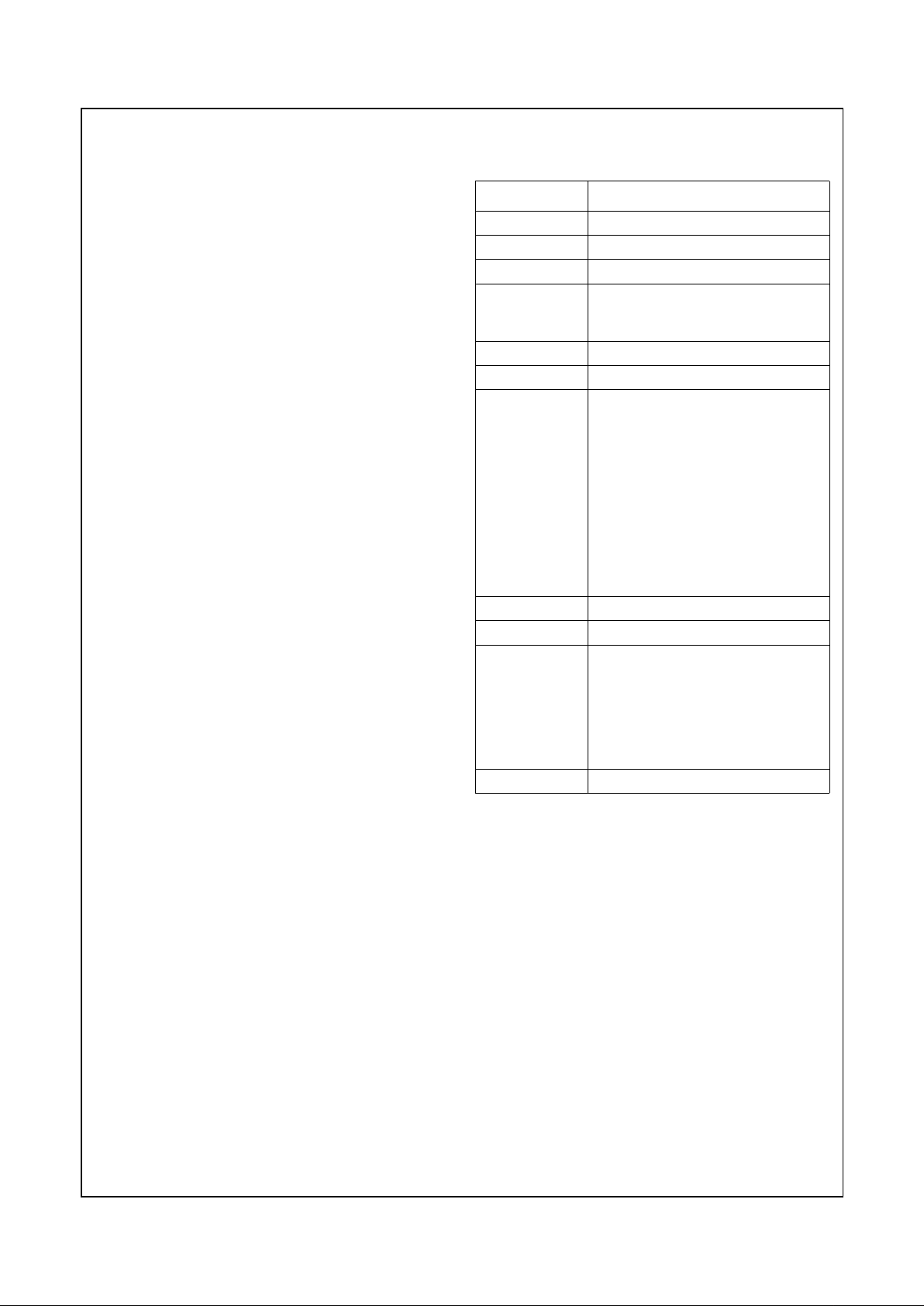

2.0 Signal Definitions

This section describes the external interface of the Geode GX1 processor. Figure 2-1 shows the signals organized by their

functional interface groups (internal test and electrical pins are not s hown).

Figure 2-1. Functional Block Di agram

SYSCLK

CLKMODE[2:0]

RESET

INTR

IRQ13

SMI#

SUSP#

SUSPA#

SERIALP

AD[31:0]

C/BE[3:0]#

PAR

FRAME#

IRDY#

TRDY#

STOP#

LOCK#

DEVSEL#

PERR#

SERR#

REQ[2:0]#

GNT[2:0]#

MD[63:0]

MA[12:0]

BA[1:0]

RASA#, RASB#

CASA#, CASB#

CS[3:0]#

WEA#, WEB#

DQM[7:0]

CKEA, CKEB

SDCLK[3:0]

SDCLK_IN

SDCLK_OUT

PCLK

VID_CLK

DCLK

CRT_HSYNC

CRT_VSYNC

FP_VSYNC

FP_HSYNC

ENA_DISP

VID_RDY

VID_VAL

VID_DATA[7:0]

PIXEL[17:0]

Memory

Controller

Interface

Video

Interface

Signals

PCI

Interface

Signals

System

Interface

Signals

Signals

GX1

Processor

Geode™

www.national.com 20 Revision 1.0

Geode™ GX1 Processor Series

Signal Definitions (Continued)

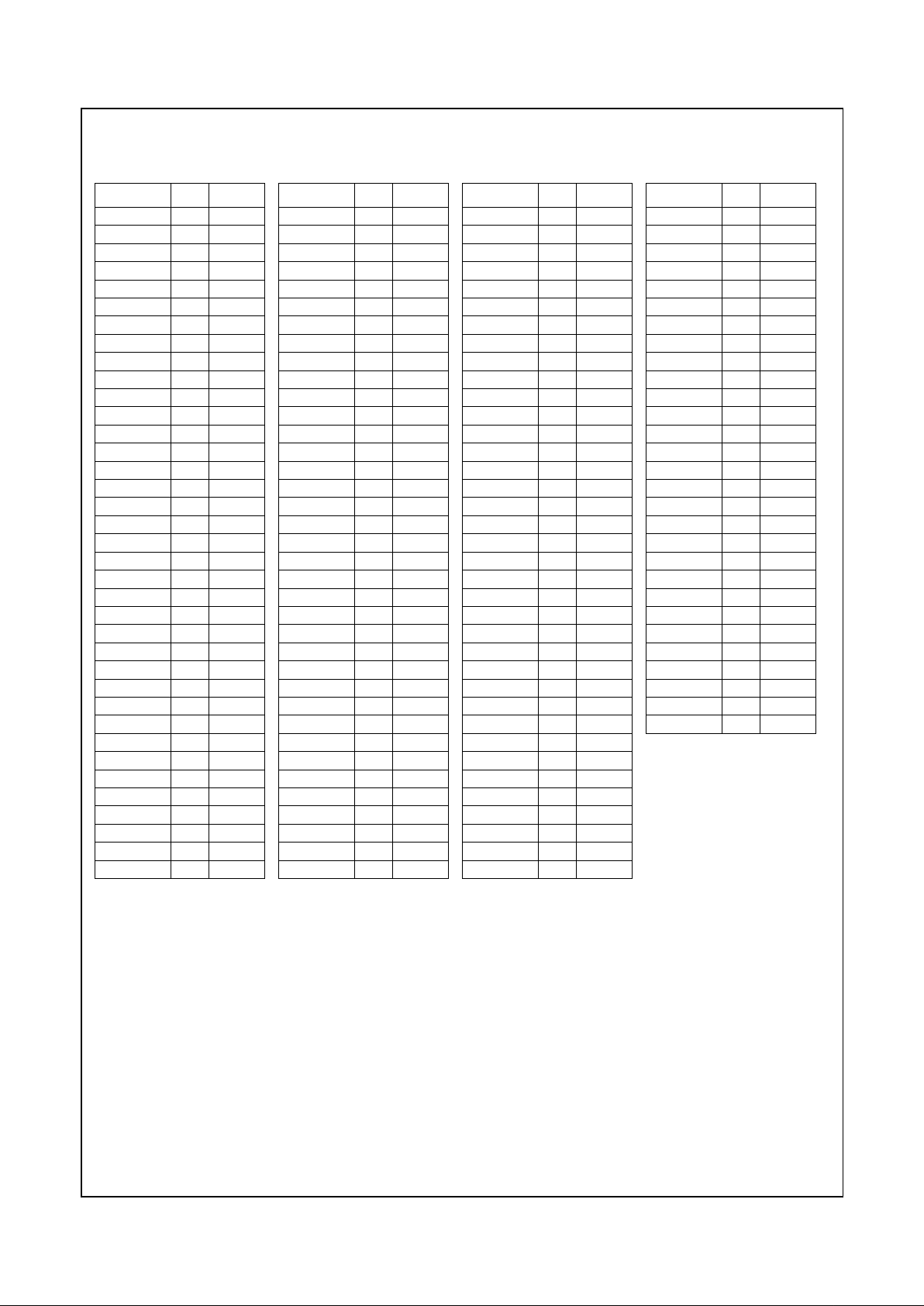

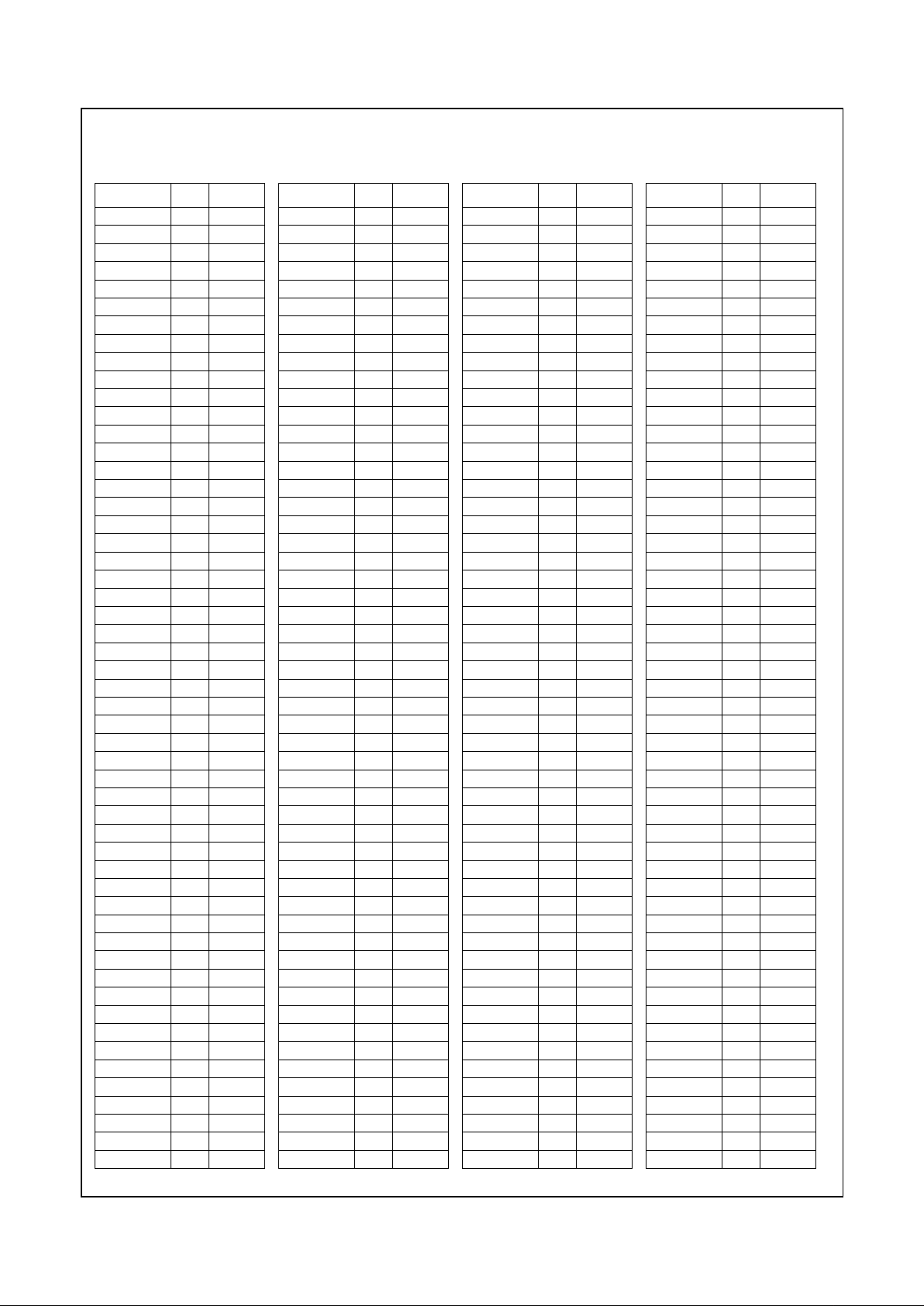

2.1 PIN ASSIGNMENTS

The tables in this section use several common abbreviations. Table 2-1 lists the mnemonics and their meanings.

Figure 2-2 shows the pin assignment for the 352 BGA with

Table 2-2 and Table 2-3 listing the pin assignments sorted

by pin number and alphabetically by signal name, respectively.

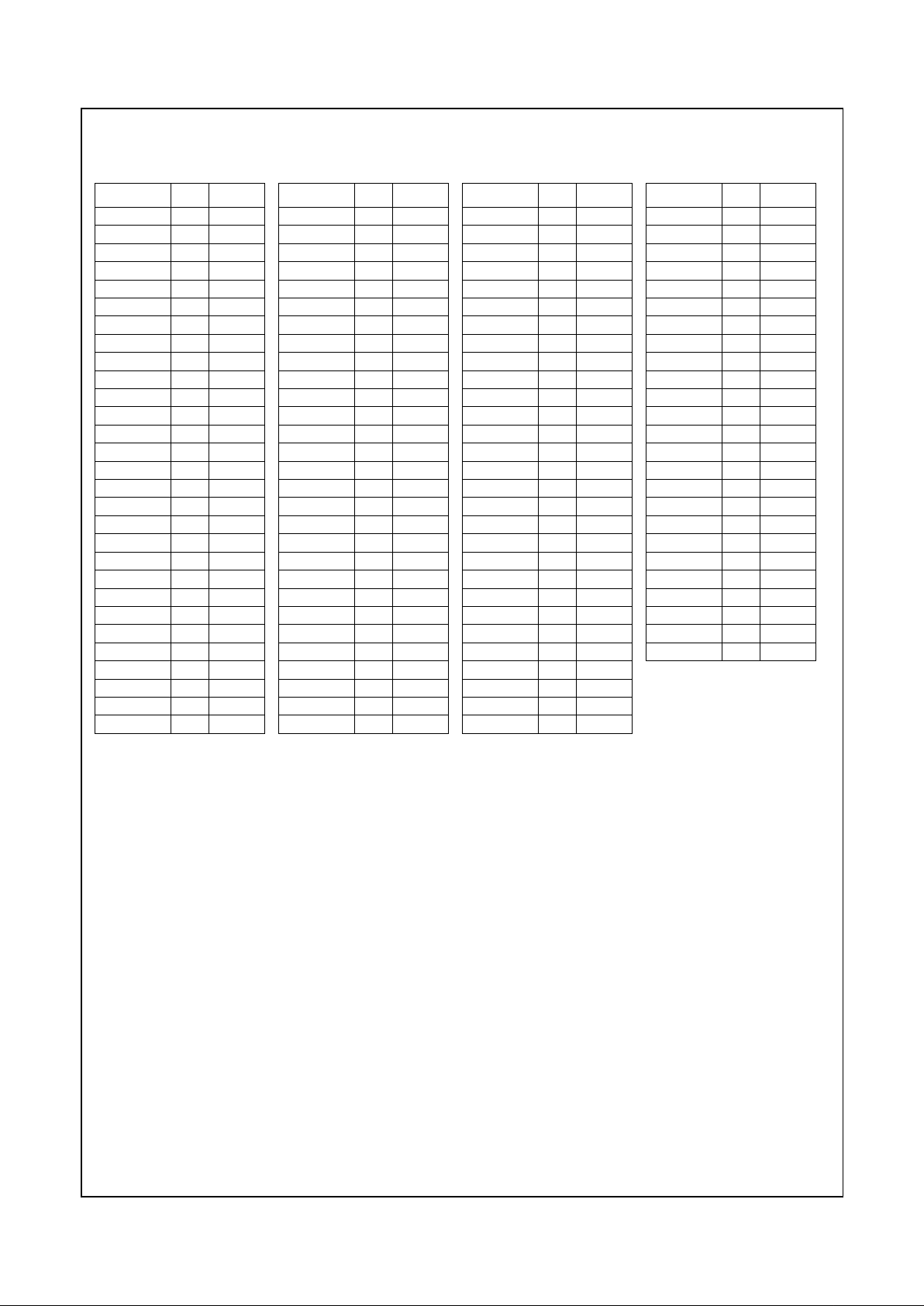

Figure 2-3 shows the pin assignment for the 320 SPGA

with Table 2-4 and Table 2-5 listing the pin assignments

sorted by pin number and alphabetically by signal name,

respectively.

In Section 2.2 “Signal Descriptions” on page 31 a description of each signal is provided within its associated functional group.

Table 2-1. Pin Type Definitions

Mnemonic Definition

I Standard input pin.

I/O Bidirectional pin.

O Totem-pole output.

OD Open-drain output structure that

allows multiple devices to share the

pin in a wired-OR configuration.

PU Pull-up resistor.

PD Pull-down resistor.

s/t/s Sustained tri-state, an active-low tri-

state signal ownedand drivenby one

and only one agent at a time. The

agent that drives an s/t/s pin low

must drive it high for at least one

clock before letting it float. A new

agent cannot start dr iving an s/t/s

signal any sooner than one clock

after the previous owner lets it float.

Apull-up resistor on the motherboard

is required to sustain the inactive

state until another agent drives it.

VCC (PWR) Power pin.

VSS (GND) Ground pin.

# The "#" symbol at the end of a signal

name indicates that the active, or

asserted state occurs when the sig-

nal is at a low voltage level.When "#"

is not present after the signal name,

the signal is asserted whenat a high

voltage level.

t/s Tri-state signal.

Revision 1.0 21 www.national.co

Geode™ GX1 Processor Series

Signal Definitions (Continued)

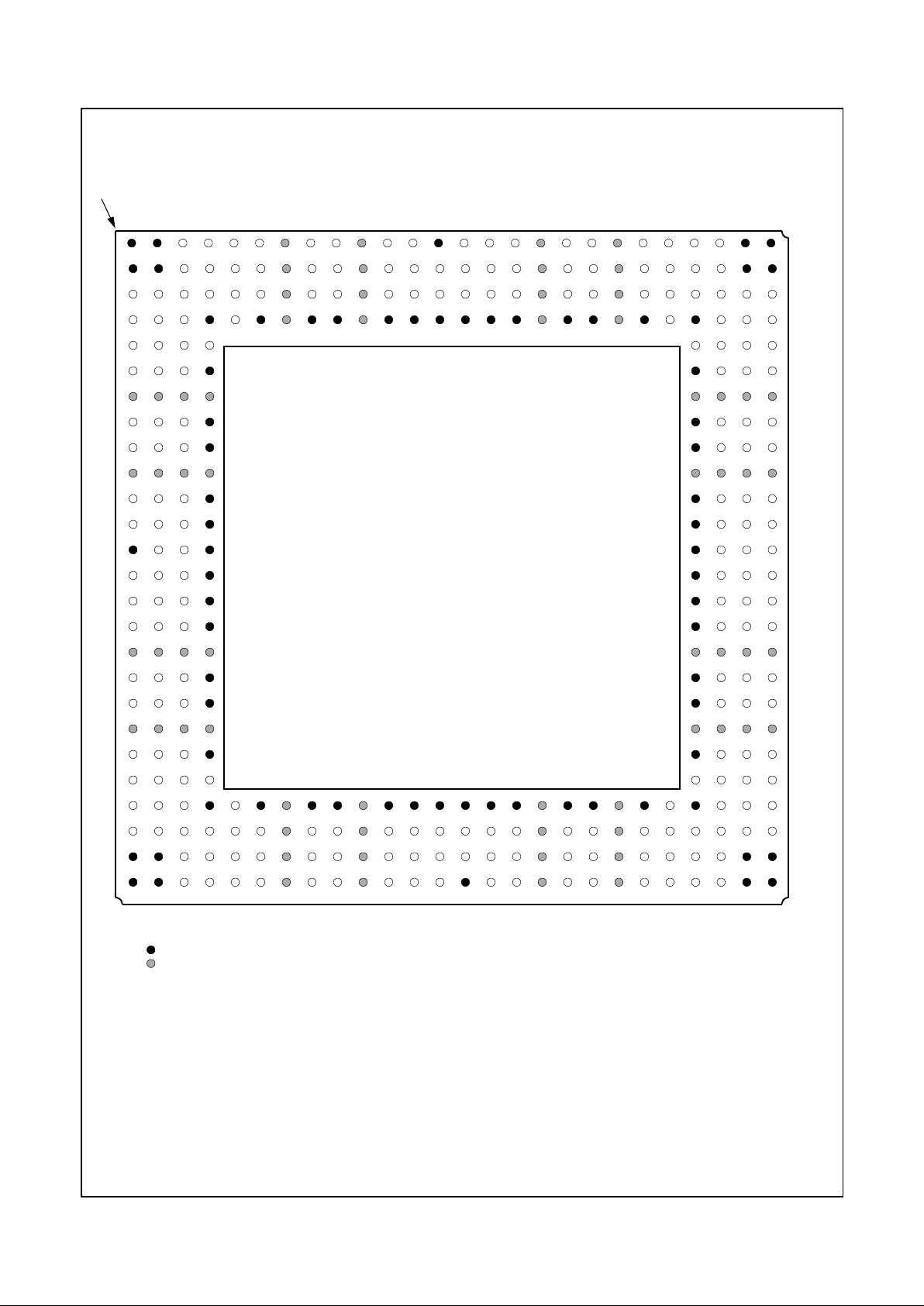

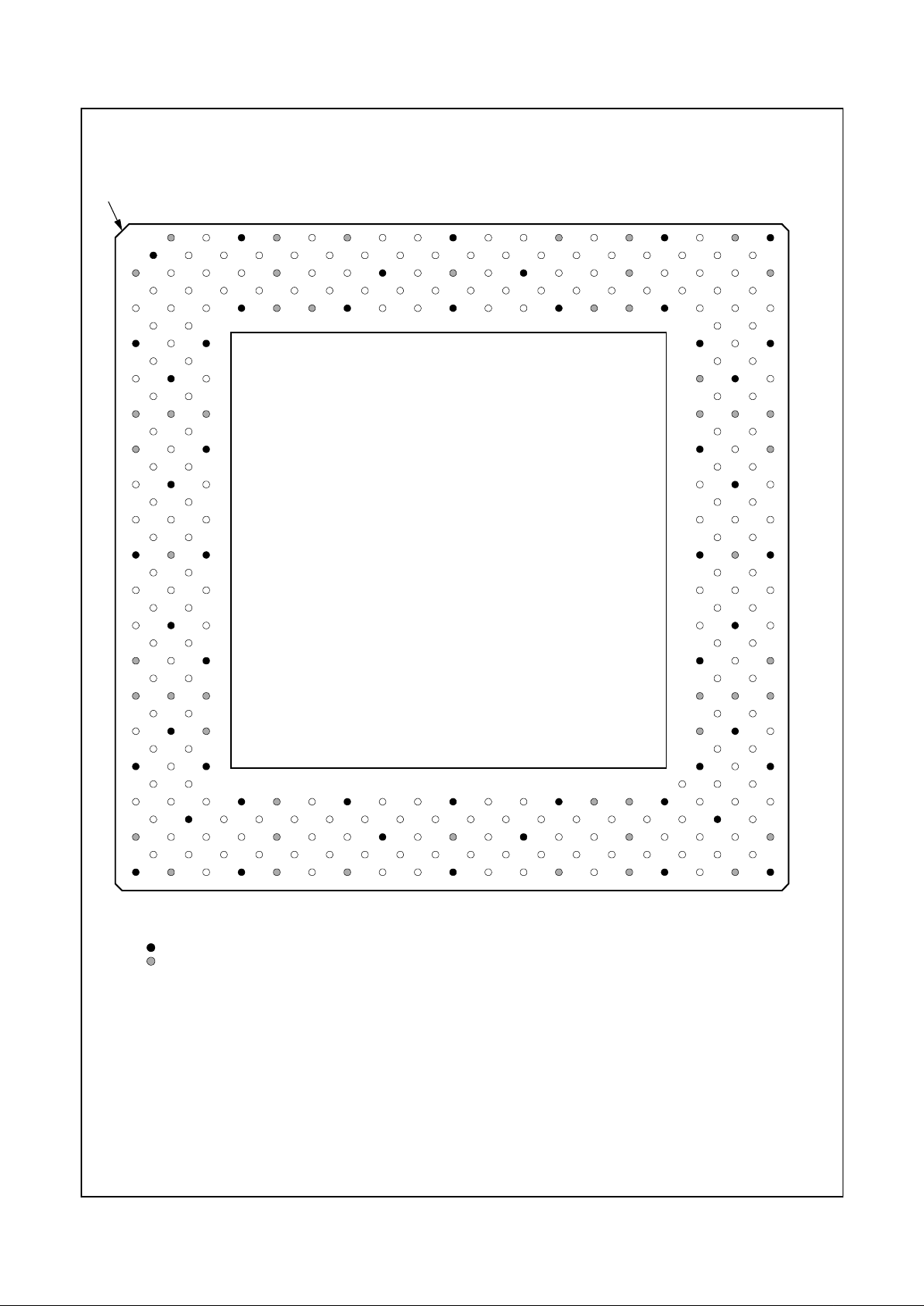

Figure 2-2. 352 BGA Pin Assignment Diagram

(

For order information, refer to Section A.1 “Order Information” on page 246.)

1234567891011121314151617181920

21 22 23 24 25 26

A

B

C

D

E

F

G

H

J

K

L

M

N

P

R

T

U

V

W

Y

AA

AB

AC

AD

AE

AF

Index Corner

VSS VSS AD27 AD24 AD21 AD16 VCC2 FRAM# DEVS# VCC3 PERR# AD15 VSS AD11 CBE0# AD6 VCC2 AD4 AD2 VCC3 AD0 AD1 TEST2 MD2 VSS VSS

VSS VSS AD28 AD25 AD22 AD18 VCC2 CBE2# TRDY# VCC3 LOCK# PAR AD14 AD12 AD9 AD7 VCC2 INTR AD3 VCC3 TEST1 TEST3 MD1 MD33 VSS VSS

AD29 AD31 AD30 AD26 AD23 AD19 VCC2 AD17 IRDY# VCC3 STOP# SERR# CBE1# AD13 AD10 AD8 VCC2 AD5 SMI# VCC3 TEST0 IRQ13 MD32 MD34 MD3 MD35

GNT0# TDI REQ2# VSS CBE3# VSS VCC2 VSS VSS VCC3 VSS VSS VSS VSS VSS VSS VCC2 VSS VSS VCC3 VSS MD0 VSS MD4 MD36 TDN

GNT2#SUSPA#REQ0# AD20 MD6 TDP MD5 MD37

TD0 GNT1# TEST VSS VSS MD38 MD7 MD39

VCC3 VCC3 VCC3 VCC3 VCC3 VCC3 VCC3 VCC3

TMS SUSP# REQ1# VSS VSS MD8 MD40 M D9

FPVSY TCLK RESET VSS VSS MD41 MD10 MD42

VCC2 VCC2 VCC2 VCC2 VCC2 VCC2 VCC2 VCC2

CKM1 FPHSY SERLP VSS VSS MD11 MD43 MD12

CKM2 VIDVAL CKM0 VSS VSS MD44 MD13 MD45

VSS PIX1 PIX0 VSS VSS MD14 MD46 MD15

VIDCLK PIX3 PIX2 VSS VSS MD47 CASA# SYSCLK

PIX4 PIX5 PIX6 VSS VSS WEB# WEA# CASB#

PIX7 PIX8 PIX9 VSS VSS DQM0 DQM4 DQM1

VCC3 VCC3 VCC3 VCC3 VCC3 VCC3 VCC3 VCC3

PIX10 PIX11 PIX12 VSS VSS DQM5 CS2# CS0#

PIX13 CRTHSY PIX14 VSS VSS RASA# RASB# MA0

VCC2 VCC2 VCC2 VCC2 VCC2 VCC2 VCC2 VCC2

PIX15 PIX16 CRTVSY VSS VSS MA1 MA2 MA3

DCLK PIX17 VDAT6 VDAT7 MA4 MA5 MA6 MA7

PCLK FLT# VDAT4 VSS NC VSS VCC2 VSS VSS VCC3 VSS VSS VSS VSS VSS VSS VCC2 VSS VSS VCC3 VSS DQM6 VSS MA8 MA9 MA10

VRDY VDAT5 VDAT3 VDAT0 EDISP MD63 VCC2 MD62 MD 29 VCC3 MD59 MD26 MD56 MD55 MD22 CKEB VCC2 MD51 MD18 VCC3 MD48 DQM3 CS1# MA11 BA0 BA1

VSS VSSVDAT2SCLK3SCLK1RWCLKVCC2SCKINMD61VCC3MD28MD58MD25MD24MD54MD21VCC2MD20MD50VCC3MD17DQM7CS3#MA12 VSS VSS

VSS VSS VDAT1 SCLK0 SCLK2 MD31 VCC2 SCKOUT MD30 VCC3 MD60 MD27 MD57 VSS MD23 MD53 VCC2 MD52 MD19 VCC3 MD49 MD16 DQM2 CKEA VSS VSS

1234567891011121314151617181920

21 22 23 24 25 26

A

B

C

D

E

F

G

H

J

K

L

M

N

P

R

T

U

V

W

Y

AA

AB

AC

AD

AE

AF

352 BGA - Top View

Note: Signal names have been abbreviated in this f ig ure due to space constraints.

= GND terminal

= PWR terminal (VCC2 = VCC_CORE; VCC3 = VCC_IO)

GX1

Processor

Geode™

www.national.com 22 Revision 1.0

Geode™ GX1 Processor Series

Signal Definitions (Continued)

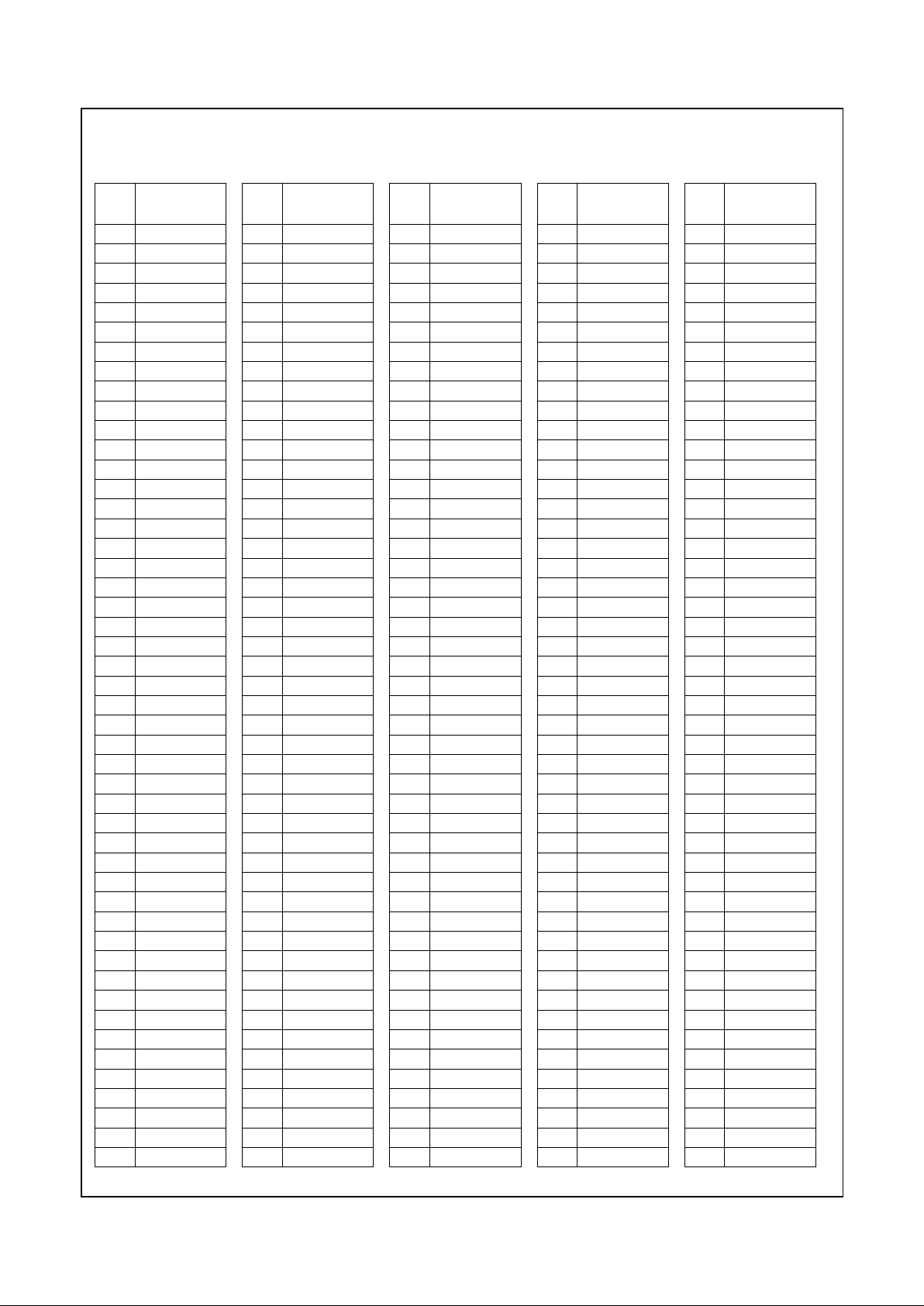

Table 2-2. 352 BGA Pin Assignments - Sorted by Pin Number

Pin

No. Signal Name

A1 VSS

A2 VSS

A3 AD27

A4 AD24

A5 AD21

A6 AD16

A7 VCC2

A8 FRAME#

A9 DEVSEL#

A10 VCC3

A11 PERR#

A12 AD15

A13 VSS

A14 AD11

A15 C/BE0#

A16 AD6

A17 VCC2

A18 AD4

A19 AD2

A20 VCC3

A21 AD0

A22 AD1

A23 TEST2

A24 MD2

A25 VSS

A26 VSS

B1 VSS

B2 VSS

B3 AD28

B4 AD25

B5 AD22

B6 AD18

B7 VCC2

B8 C/BE2#

B9 TRDY#

B10 VCC3

B11 LOCK#

B12 PAR

B13 AD14

B14 AD12

B15 AD9

B16 AD7

B17 VCC2

B18 INTR

B19 AD3

B20 VCC3

B21 TEST1

B22 TEST3

B23 MD1

B24 MD33

B25 VSS

B26 VSS

C1 AD29

C2 AD31

C3 AD30

C4 AD26

C5 AD23

C6 AD19

C7 VCC2

C8 AD17

C9 IRDY#

C10 VCC3

C11 STOP#

C12 SERR#

C13 C/BE1#

C14 AD13

C15 AD10

C16 AD8

C17 VCC2

C18 AD5

C19 SMI#

C20 VCC3

C21 TEST0

C22 IRQ13

C23 MD32

C24 MD34

C25 MD3

C26 MD35

D1 GNT0#

D2 TDI

D3 REQ2#

D4 VSS

D5 C/BE3#

D6 VSS

D7 VCC2

D8 VSS

D9 VSS

D10 VCC3

D11 VSS

D12 VSS

D13 VSS

D14 VSS

D15 VSS

D16 VSS

D17 VCC2

D18 VSS

Pin

No. Signal Name

D19 VSS

D20 VCC3

D21 VSS

D22 MD0

D23 VSS

D24 MD4

D25 MD36

D26 TDN

E1 GNT2#

E2 SUSPA#

E3 REQ0#

E4 AD20

E23 MD6

E24 TDP

E25 MD5

E26 MD37

F1 TDO

F2 GNT1#

F3 TEST

F4 VSS

F23 VSS

F24 MD38

F25 MD7

F26 MD39

G1 VCC3

G2 VCC3

G3 VCC3

G4 VCC3

G23 VCC3

G24 VCC3

G25 VCC3

G26 VCC3

H1 TMS

H2 SUSP#

H3 REQ1#

H4 VSS

H23 VSS

H24 MD8

H25 MD40

H26 MD9

J1 FP_VSYNC

J2 TCLK

J3 RESET

J4 VSS

J23 VSS

J24 MD41

J25 MD10

J26 MD42

Pin

No. Signal Name

K1 VCC2

K2 VCC2

K3 VCC2

K4 VCC2

K23 VCC2

K24 VCC2

K25 VCC2

K26 VCC2

L1 CLKMODE1

L2 FP_HSYNC

L3 SERIALP

L4 VSS

L23 VSS

L24 MD11

L25 MD43

L26 MD12

M1 CLKMODE2

M2 VID_VAL

M3 CLKMODE0

M4 VSS

M23 VSS

M24 MD44

M25 MD13

M26 MD45

N1 VSS

N2 PIXEL1

N3 PIXEL0

N4 VSS

N23 VSS

N24 MD14

N25 MD46

N26 MD15

P1 VID_CLK

P2 PIXEL3

P3 PIXEL2

P4 VSS

P23 VSS

P24 MD47

P25 CASA#

P26 SYSCLK

R1 PIXEL4

R2 PIXEL5

R3 PIXEL6

R4 VSS

R23 VSS

R24 WEB#

R25 WEA#

R26 CASB#

Pin

No. Signal Name

T1 PIXEL7

T2 PIXEL8

T3 PIXEL9

T4 VSS

T23 VSS

T24 DQM0

T25 DQM4

T26 DQM1

U1 VCC3

U2 VCC3

U3 VCC3

U4 VCC3

U23 VCC3

U24 VCC3

U25 VCC3

U26 VCC3

V1 PIXEL10

V2 PIXEL11

V3 PIXEL12

V4 VSS

V23 VSS

V24 DQM5

V25 CS2#

V26 CS0#

W1 PIXEL13

W2 CRT_HSYNC

W3 PIXEL14

W4 VSS

W23 VSS

W24 RASA#

W25 RASB#

W26 MA0

Y1 VCC2

Y2 VCC2

Y3 VCC2

Y4 VCC2

Y23 VCC2

Y24 VCC2

Y25 VCC2

Y26 VCC2

AA1 PIXEL15

AA2 PIXEL16

AA3 CRT_VSYNC

AA4 VSS

AA23 VSS

AA24 MA1

AA25 MA2

AA26 MA3

Pin

No. Signal Name

Revision 1.0 23 www.national.co

Geode™ GX1 Processor Series

Signal Definitions (Continued)

AB1 DCLK

AB2 PI XEL17

AB3 VID_DATA6

AB4 VID_DATA7

AB23 MA4

AB24 MA5

AB25 MA6

AB26 MA7

AC1 PCLK

AC2 FLT#

AC3 VID_DATA4

AC4 VSS

AC5 NC

AC6 VSS

AC7 VCC2

AC8 VSS

AC9 VSS

AC10 VCC3

AC11 VSS

AC12 VSS

AC13 VSS

AC14 VSS

AC15 VSS

Pin

No. Signal Name

AC16 VSS

AC17 VCC2

AC18 VSS

AC19 VSS

AC20 VCC3

AC21 VSS

AC22 DQM6

AC23 VSS

AC24 MA8

AC25 MA9

AC26 MA10

AD1 VID_RDY

AD2 VID_DATA5

AD3 VID_DATA3

AD4 VID_DATA0

AD5 ENA_DISP

AD6 MD63

AD7 VCC2

AD8 MD62

AD9 MD29

AD10 VCC3

AD11 MD59

AD12 MD26

Pin

No. Signal Name

AD13 MD56

AD14 MD55

AD15 MD22

AD16 CKEB

AD17 VCC2

AD18 MD51

AD19 MD18

AD20 VCC3

AD21 MD48

AD22 DQM3

AD23 CS1#

AD24 MA11

AD25 BA0

AD26 BA1

AE1 VSS

AE2 VSS

AE3 VID_DATA2

AE4 SDCLK3

AE5 SDCLK1

AE6 RW_CLK

AE7 VCC2

AE8 SDCLK_IN

AE9 MD61

Pin

No. Signal Name

AE10 VCC3

AE11 MD28

AE12 MD58

AE13 MD25

AE14 MD24

AE15 MD54

AE16 MD21

AE17 VCC2

AE18 MD20

AE19 MD50

AE20 VCC3

AE21 MD17

AE22 DQM7

AE23 CS3#

AE24 MA12

AE25 VSS

AE26 VSS

AF1 VSS

AF2 VSS

AF3 VID_DATA1

AF4 SDCLK0

AF5 SDCLK2

AF6 MD31

Pin

No. Signal Name

AF7 VCC2

AF8 SDCLK_OUT

AF9 MD30

AF10 VCC3

AF11 MD60

AF12 MD27

AF13 MD57

AF14 VSS

AF15 MD23

AF16 MD53

AF17 VCC2

AF18 MD52

AF19 MD19

AF20 VCC3

AF21 MD49

AF22 MD16

AF23 DQM2

AF24 CKEA

AF25 VSS

AF26 VSS

Pin

No. Signal Name

Table 2-2. 352 BGA Pin Assignments - Sorted by Pin Number (Continued)

www.national.com 24 Revision 1.0

Geode™ GX1 Processor Series

Signal Definitions (Continued)

Table 2-3. 352 BGA Pin Assignments - Sorted Alphabetically by Signal Name

Signal Name Type Pin No.

1

AD0 I/O A21

AD1 I/O A22

AD2 I/O A19

AD3 I/O B19

AD4 I/O A18

AD5 I/O C18

AD6 I/O A16

AD7 I/O B16

AD8 I/O C16

AD9 I/O B15

AD10 I/O C15

AD11 I/O A14

AD12 I/O B14

AD13 I/O C14

AD14 I/O B13

AD15 I/O A12

AD16 I/O A6

AD17 I/O C8

AD18 I/O B6

AD19 I/O C6

AD20 I/O E4

AD21 I/O A5

AD22 I/O B5

AD23 I/O C5

AD24 I/O A4

AD25 I/O B4

AD26 I/O C4

AD27 I/O A3

AD28 I/O B3

AD29 I/O C1

AD30 I/O C3

AD31 I/O C2

BA0 O AD25

BA1 O AD26

CASA# O P25

CASB# O R26

C/BE0# I/O A15

C/BE1# I/O C13

C/BE2# I/O B8

C/BE3# I/O D5

CKEA O AF24

CKEB O AD16

CLKMODE0 I M3

CLKMODE1 I L1

CLKMODE2 I M1

CRT_HSYNC O W2

CRT_VSYNC O AA3

CS0# O V26

CS1# O AD23

CS2# O V25

CS3# O AE23

DCLK I AB1

DEVSEL# s/t/s A9 (PU)

DQM0 O T24

DQM1 O T26

DQM2 O AF23

DQM3 O AD22

DQM4 O T25

DQM5 O V24

DQM6 O AC22

DQM7 O AE22

ENA_DISP O AD5

FLT# I AC2

FP_HSYNC O L2

FP_VSYNC O J1

FRAME# s/t/s A8 (PU)

GNT0# O D1

GNT1# O F2

GNT2# O E1

INTR I B18

IRDY# s/t/s C9 (PU)

IRQ13 O C22

LOCK# s/t/s B11 (PU)

MA0 O W26

MA1 O AA24

MA2 O AA25

MA3 O AA26

MA4 O AB23

MA5 O AB24

MA6 O AB25

MA7 O AB26

MA8 O AC24

MA9 O AC25

MA10 O AC26

MA11 O AD24

MA12 O AE24

MD0 I/O D22

MD1 I/O B23

MD2 I/O A24

MD3 I/O C25

MD4 I/O D24

MD5 I/O E25

MD6 I/O E23

MD7 I/O F25

MD8 I/O H24

MD9 I/O H26

MD10 I/O J25

MD11 I/O L24

MD12 I/O L26

MD13 I/O M25

MD14 I/O N24

MD15 I/O N26

MD16 I/O AF22

MD17 I/O AE21

MD18 I/O AD19

MD19 I/O AF19

Signal Name Type Pin No.

1

MD20 I/O AE18

MD21 I/O AE16

MD22 I/O AD15

MD23 I/O AF15

MD24 I/O AE14

MD25 I/O AE13

MD26 I/O AD12

MD27 I/O AF12

MD28 I/O AE11

MD29 I/O AD9

MD30 I/O AF9

MD31 I/O AF6

MD32 I/O C23

MD33 I/O B24

MD34 I/O C24

MD35 I/O C26

MD36 I/O D25

MD37 I/O E26

MD38 I/O F24

MD39 I/O F26

MD40 I/O H25

MD41 I/O J24

MD42 I/O J26

MD43 I/O L25

MD44 I/O M24

MD45 I/O M26

MD46 I/O N25

MD47 I/O P24

MD48 I/O AD21

MD49 I/O AF21

MD50 I/O AE19

MD51 I/O AD18

MD52 I/O AF18

MD53 I/O AF16

MD54 I/O AE15

MD55 I/O AD14

MD56 I/O AD13

MD57 I/O AF13

MD58 I/O AE12

MD59 I/O AD11

MD60 I/O AF11

MD61 I/O AE9

MD62 I/O AD8

MD63 I/O AD6

NC -- AC5

PAR I/O B12

PCLK O AC1

PERR# s/t/s A11 (PU)

PIXEL0 O N3

PIXEL1 O N2

PIXEL2 O P3

PIXEL3 O P2

PIXEL4 O R1

Signal Name Type Pin No.

1

PIXEL5 O R2

PIXEL6 O R3

PIXEL7 O T1

PIXEL8 O T2

PIXEL9 O T3

PIXEL10 O V1

PIXEL11 O V2

PIXEL12 O V3

PIXEL13 O W1

PIXEL14 O W3

PIXEL15 O AA1

PIXEL16 O AA2

PIXEL17 O AB2

RASA# O W24

RASB# O W25

REQ0# I E3 (PU)

REQ1# I H3 (PU)

REQ2# I D3 (PU)

RESET I J3

RW_CLK O AE6

SDCLK_IN I AE8

SDCLK_OUT O AF8

SDCLK0 O AF4

SDCLK1 O AE5

SDCLK2 O AF5

SDCLK3 O AE4

SERIALP O L3

SERR# OD C12 (PU)

SMI# I C19

STOP# s/t/s C11 (PU)

SUSP# I H2 (PU)

SUSPA# O E2

SYSCLK I P2 6

TCLK I J2 (PU)

TDI I D2 (PU)

TDN O D26

TDO O F1

TDP O E24

TEST I F3 (PD)

TEST0 O C21

TEST1 O B21

TEST2 O A23

TEST3 O B22

TMS I H1 (PU)

TRDY# s/t/s B9 (PU)

VCC2 PWR A7

VCC2 PWR A17

VCC2 PWR B7

VCC2 PWR B17

VCC2 PWR C7

VCC2 PWR C17

VCC2 PWR D7

VCC2 PWR D17

Signal Name Type Pin No.

1

Revision 1.0 25 www.national.co

Geode™ GX1 Processor Series

Signal Definitions (Continued)

VCC2 PWR K1

VCC2 PWR K2

VCC2 PWR K3

VCC2 PWR K4

VCC2 PWR K23

VCC2 PWR K24

VCC2 PWR K25

VCC2 PWR K26

VCC2 PWR Y1

VCC2 PWR Y2

VCC2 PWR Y3

VCC2 PWR Y4

VCC2 PWR Y23

VCC2 PWR Y24

VCC2 PWR Y25

VCC2 PWR Y26

VCC2 PWR AC7

VCC2 PWR AC17

VCC2 PWR AD7

VCC2 PWR AD17

VCC2 PWR AE7

VCC2 PWR AE17

VCC2 PWR AF7

VCC2 PWR AF17

VCC3 PWR A10

VCC3 PWR A20

VCC3 PWR B10

VCC3 PWR B20

VCC3 PWR C10

VCC3 PWR C20

VCC3 PWR D10

VCC3 PWR D20

VCC3 PWR G1

VCC3 PWR G2

VCC3 PWR G3

VCC3 PWR G4

VCC3 PWR G23

Signal Name Type Pin No.

1

VCC3 PWR G24

VCC3 PWR G25

VCC3 PWR G26

VCC3 PWR U1

VCC3 PWR U2

VCC3 PWR U3

VCC3 PWR U4

VCC3 PWR U23

VCC3 PWR U24

VCC3 PWR U25

VCC3 PWR U26

VCC3 PWR AC10

VCC3 PWR AC20

VCC3 PWR AD10

VCC3 PWR AD20

VCC3 PWR AE10

VCC3 PWR AE20

VCC3 PWR AF10

VCC3 PWR AF20

VID_CLK O P1

VID_DATA0 O AD4

VID_DATA1 O AF3

VID_DATA2 O AE3

VID_DATA3 O AD3

VID_DATA4 O AC3

VID_DATA5 O AD2

VID_DATA6 O AB3

VID_DATA7 O AB4

VID_RDY I AD1

VID_VAL O M2

VSS GND A1

VSS GND A2

VSS GND A13

VSS GND A25

VSS GND A26

VSS GND B1

VSS GND B2

Signal Name Type Pin No.

1

VSS GND B25

VSS GND B26

VSS GND D4

VSS GND D6

VSS GND D8

VSS GND D9

VSS GND D11

VSS GND D12

VSS GND D13

VSS GND D14

VSS GND D15

VSS GND D16

VSS GND D18

VSS GND D19

VSS GND D21

VSS GND D23

VSS GND F4

VSS GND F23

VSS GND H4

VSS GND H23

VSS GND J4

VSS GND J23

VSS GND L4

VSS GND L23

VSS GND M4

VSS GND M23

VSS GND N1

VSS GND N4

VSS GND N23

VSS GND P4

VSS GND P23

VSS GND R4

VSS GND R23

VSS GND T4

VSS GND T23

VSS GND V4

VSS GND V23

Signal Name Type Pin No.

1

VSS GND W4

VSS GND W23

VSS GND AA4

VSS GND AA23

VSS GND AC4

VSS GND AC6

VSS GND AC8

VSS GND AC9

VSS GND AC11

VSS GND AC12

VSS GND AC13

VSS GND AC14

VSS GND AC15

VSS GND AC16

VSS GND AC18

VSS GND AC19

VSS GND AC21

VSS GND AC23

VSS GND AE1

VSS GND AE2

VSS GND AE25

VSS GND AE26

VSS GND AF1

VSS GND AF2

VSS GND AF14

VSS GND AF25

VSS GND AF26

WEA# O R25

WEB# O R24

1. PU/PD indicates pin is internally connected to a

weak (> 20-kohm) pull-up/down resistor.

Signal Name Type Pin No.

1

Table 2-3. 352 BGA Pin Assignments - Sorted Alphabetically by Signal Name (Continued)

www.national.com 26 Revision 1.0

Geode™ GX1 Processor Series

Signal Definitions (Continued)

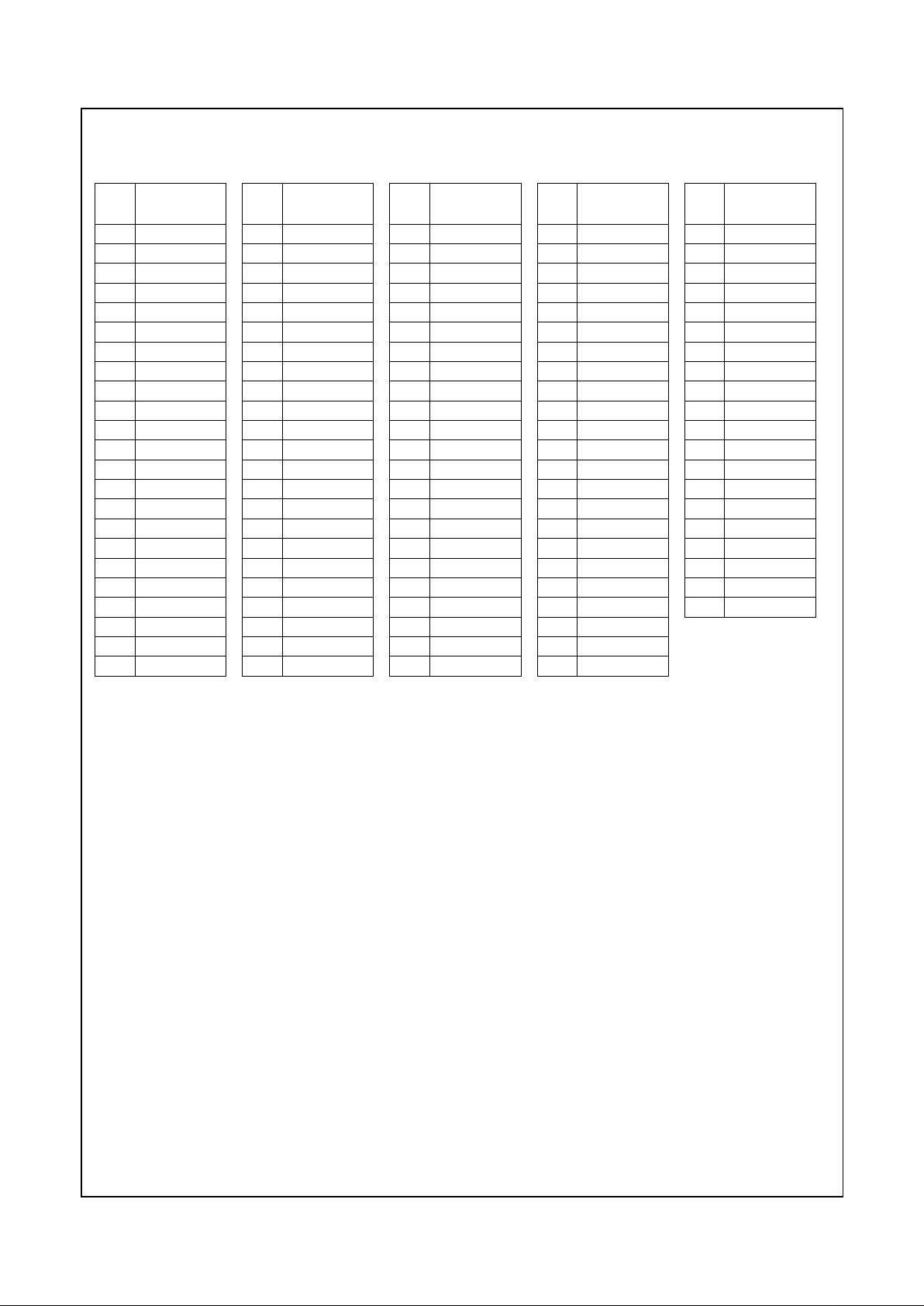

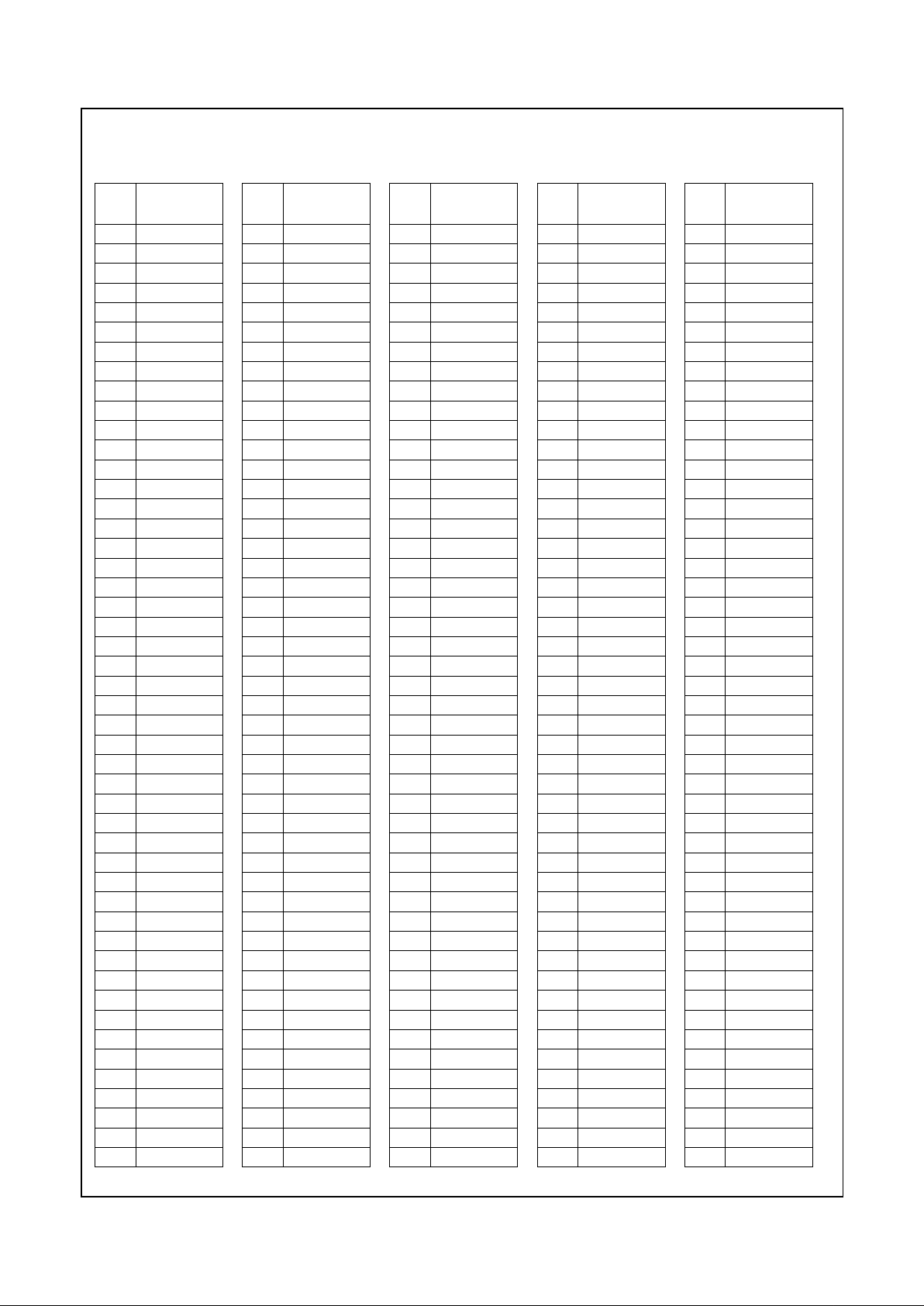

Figure 2-3. 320 SPGA Pin As signment Diagram

(For order information, refer to Section A.1 “Order Information” on page 246.)

1234567891011121314151617181920

21 22 23 24 25 26

A

B

C

D

E

F

G

H

J

K

L

M

N

P

Q

R

S

T

U

V

AA

AB

AC

AD

AE

AF

Index Corner

27 28 29 30 31 32 33 34 35 36 37

AG

AH

AJ

AK

AL

AM

W

Y

X

Z

AN

A

B

C

D

E

F

G

H

J

K

L

M

N

P

Q

R

S

T

U

V

AA

AB

AC

AD

AE

AF

AG

AH

AJ

AK

AL

AM

W

Y

X

Z

AN

1234567891011121314151617181920

21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37

VCC3 AD25 VSS VCC2 AD16 VCC3 STOP# SERR# VSS AD11 AD8 VCC3 AD2 VCC2 VSS TEST0 VCC3 VSS

VSS AD27 CBE3# AD21 AD19 CBE2# TRDY# LOCK# CBE1# AD13 AD9 AD6 AD3 SMI# AD1 TEST2 MD33 MD2

VCC3 AD31 AD26 AD23 VCC2 AD18 FRAME# VSS PAR VCC3 AD10 VSS AD4 AD0 VCC2 IRQ13 MD1 MD34 VCC3

AD30 AD29 AD24 AD22 AD20 AD17 IRDY# PERR# AD14 AD12 AD7 INTR TEST1 TEST3 MD0 MD32 MD3 MD35

REQ0# REQ2# AD28 VSS VCC2 VCC2 VSS DEVSEL# AD15 VSS CBE0# AD5 VSS VCC2 VCC2 VSS MD4 MD36 TDN

GNT0# TDI MD5 TDP

VSS CKMD2 VSS VSS MD37 VSS

GNT2# SUSPA#

TDO VSS TEST

REQ1# GNT1#

VCC2 VCC2 VCC2

RESET SUSP#

VCC3 TMS VSS

FPVSYNC TCLK

SERIALP VSS NC

CKMD1 FPHSYNC

CKMD0 VID_VAL PIX0

PIX1 PIX2

VSS VCC3 VSS

PIX3 VID_CLK

PIX6 PIX5 PIX4

NC PIX9

PIX8 VSS PIX7

NC PIX10

VCC3 PIX11 VSS

PIX12 PIX13

VCC2 VCC2 VCC2

CRTHSYNC DCLK

PIX14 VSS VCC2

PIX15 PIX16

VSS PIX17 VSS

CRTVSYNC VDAT6

MD6 MD38

VCC2 VSS MD7

MD39 MD8

VCC2 VCC2 VCC2

MD40 MD9

VSS MD41 VCC3

MD10 MD42

MD11 VSS MD43

MD44 MD12

MD14 MD13 MD45

MD15 MD46

VSS VCC3 VSS

SYSCLK MD47

WEA# W EB# CASA#

DQM0 CASB#

DQM1 VSS DQM4

CS2# DQM5

VSS CS0# VCC3

RASB# RASA#

VCC2 VCC2 VCC2

VCC2 VSS MA1

MA2 MA0

MA4 MA3

VSS MA5 VSS

MA8 MA6MA10

PCLK FLT# VDAT5 VSS VCC2 MD31 VSS MD60 MD57 VSS MD22 MD52 VSS VCC2 VCC2 VSS BA1 MA9 MA7

VRDY VS S VDAT0 S DCLK0 SDCLK2 SDCLKIN MD29 MD27 MD56 MD55 MD21 MD20 MD50 MD16 DQ M3 CS3#

VSS BA0

VCC2 VDAT4 VDAT2 SDCLK1 VCC2 RWCLK SDCLKOUT VSS MD58 VCC3 MD23 VSS MD19 MD49 VCC2 DQM6 CKEA MA11 VCC3

VDAT7 VDAT3 ENDIS SDCLK3 MD63 MD30 MD61 MD59 MD25 MD24 MD53 MD51 MD18 MD48 DQM7 DQM2 MA12 NC

VSS VCC2 VDAT1 VSS VCC2 MD62 VCC3 MD28 MD26 VSS MD54 CKEB VCC3 MD17 VCC2 VSS CS1# VCC3 VSS

Note: Signal names have been abbreviated in this f ig ure due to space constraints.

= Denotes GND terminal

= Denotes PWR terminal (VCC2 = VCC_CORE; VCC3 = VCC_IO)

320 SPGA - Top View

GX1

Processor

Geode™

Revision 1.0 27 www.national.co

Geode™ GX1 Processor Series

Signal Definitions (Continued)

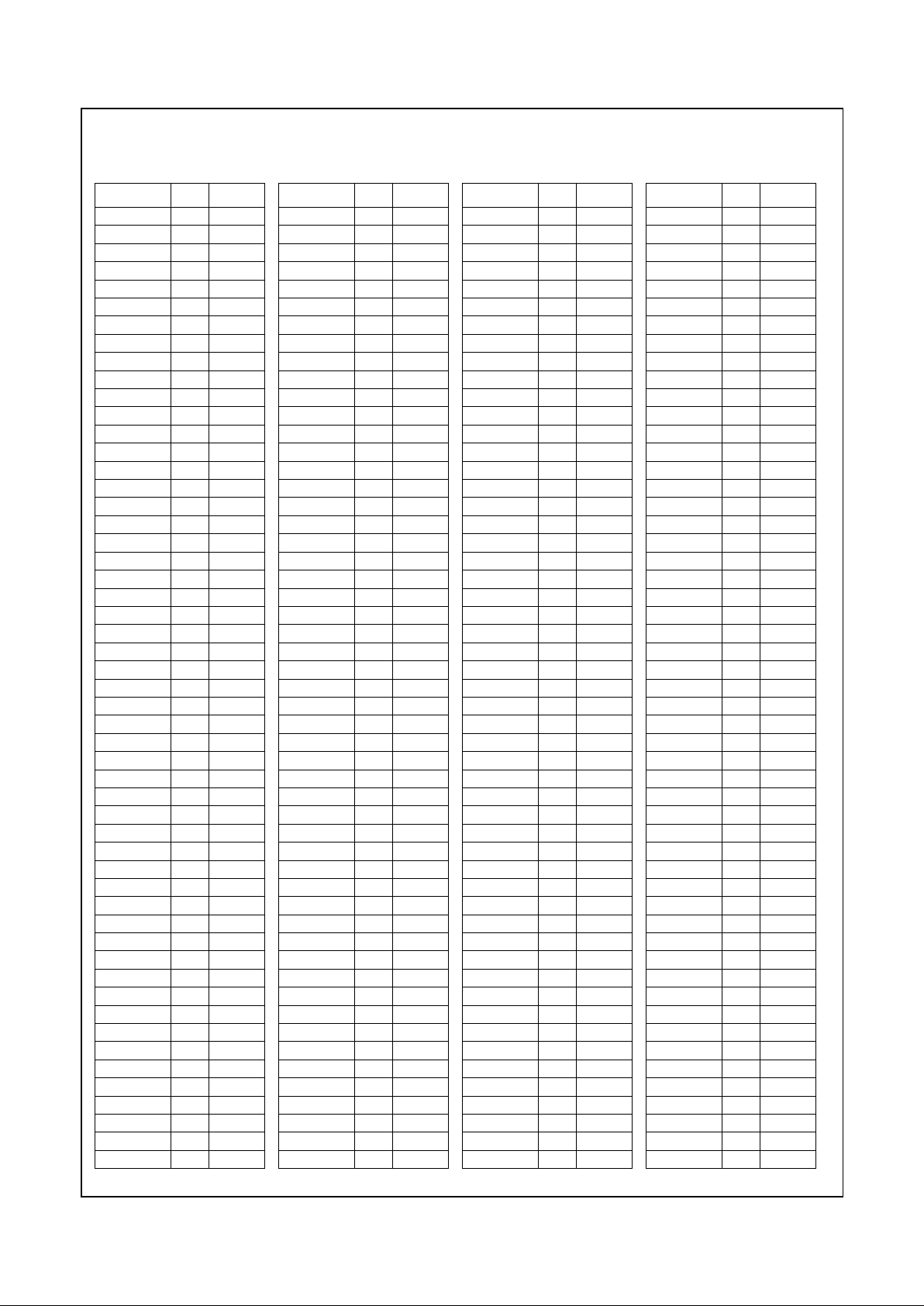

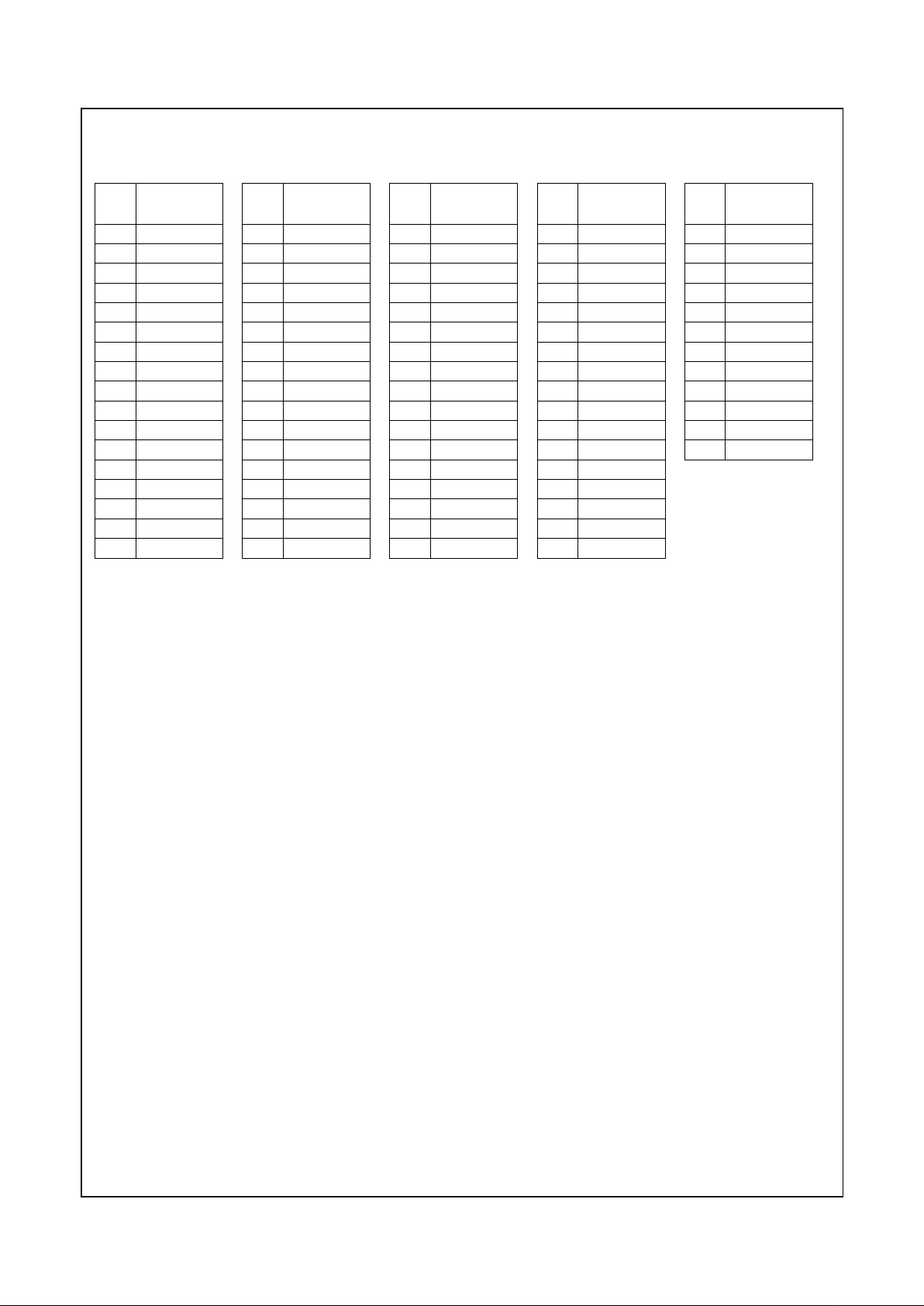

Table 2-4. 320 SPGA Pin Assignments - Sorted by Pin Number

Pin

No. Signal Name

A3 VCC3

A5 AD25

A7 VSS

A9 VCC2

A11 AD16

A13 VCC3

A15 STOP#

A17 SERR#

A19 VSS

A21 AD11

A23 AD8

A25 VCC3

A27 AD2

A29 VCC2

A31 VSS

A33 TEST0

A35 VCC3

A37 VSS

B2 VSS

B4 AD27

B6 C/BE3#

B8 AD21

B10 AD19

B12 C/BE2#

B14 TRDY#

B16 LOCK#

B18 C/BE1#

B20 AD13

B22 AD9

B24 AD6

B26 AD3

B28 SMI#

B30 AD1

B32 TEST2

B34 MD33

B36 MD2

C1 VCC3

C3 AD31

C5 AD26

C7 AD23

C9 VCC2

C11 AD18

C13 FRAME#

C15 VSS

C17 PAR

C19 VCC3

C21 AD10

C23 VSS

C25 AD4

C27 AD0

C29 VCC2

C31 IRQ13

C33 MD1

C35 MD34

C37 VCC3

D2 AD30

D4 AD29

D6 AD24

D8 AD22

D10 AD20

D12 AD17

D14 IRDY#

D16 PERR#

D18 AD14

D20 AD12

D22 AD7

D24 INTR

D26 TEST1

D28 TEST3

D30 MD0

D32 MD32

D34 MD3

D36 MD35

E1 REQ0#

E3 REQ2#

E5 AD28

E7 VSS

E9 VCC2

E11 VCC2

E13 VSS

E15 DEVSEL#

E17 AD15

E19 VSS

E21 C/BE0#

E23 AD5

E25 VSS

E27 VCC2

E29 VCC2

E31 VSS

E33 MD4

E35 MD36

E37 TDN

F2 GNT0#

F4 TDI

F34 MD5

F36 TDP

Pin

No. Signal Name

G1 VSS

G3 CLKMODE2

G5 VSS

G33 VSS

G35 MD37

G37 VSS

H2 GNT2#

H4 SUSPA#

H34 MD6

H36 MD38

J1 TDO

J3 VSS

J5 TEST

J33 VCC2

J35 VSS

J37 MD7

K2 REQ1#

K4 GNT1#

K34 MD39

K36 MD8

L1 VCC2

L3 VCC2

L5 VCC2

L33 VCC2

L35 VCC2

L37 VCC2

M2 RESET

M4 SUSP#

M34 MD40

M36 MD9

N1 VCC3

N3 TMS

N5 VSS

N33 VSS

N35 MD41

N37 VCC3

P2 FP_VSYNC

P4 TCLK

P34 MD10

P36 MD42

Q1 SERIALP

Q3 VSS

Q5 NC

Q33 MD11

Q35 VSS

Q37 MD43

R2 CLKMODE1

R4 FP_HSYNC

Pin

No. Signal Name

R34 MD44

R36 MD12

S1 CLKMODE0

S3 VID_VAL

S5 PIXEL0

S33 MD14

S35 MD13

S37 MD45

T2 PIXEL1

T4 PIXEL2

T34 MD15

T36 MD46

U1 VSS

U3 VCC3

U5 VSS

U33 VSS

U35 VCC3

U37 VSS

V2 PIXEL3

V4 VID_CLK

V34 SYSCLK

V36 MD47

W1 PIXEL6

W3 PIXEL5

W5 PIXEL4

W33 WEA#

W35 WEB#

W37 CASA#

X2 NC

X4 PIXEL9

X34 DQM0

X36 CASB#

Y1 PIXEL8

Y3 VSS

Y5 PIXEL7

Y33 DQM1

Y35 VSS

Y37 DQM4