NSC DS90CP22MX-8, DS90CP22M-8 Datasheet

DS90CP22

2X2 800 Mbps LVDS Crosspoint Switch

General Description

DS90CP22 is a 2x2 crosspoint switch utilizing LVDS (Low

VoltageDifferential Signaling) technology for low power, high

speed operation. Data paths are fully differential from input

to output for low noise generation and low pulse width distortion. The non-blocking design allows connection of any input

to any output or outputs. LVDS I/O enable high speed data

transmission for point-to-point interconnects. This device

can be used as a high speed differential crosspoint, 2:1 mux,

1:2 demux, repeater or 1:2 signal splitter. The mux and demux functions are useful for switching between primary and

backup circuits in fault tolerant systems. The 1:2 signal splitter and 2:1 mux functions are useful for distribution of serial

bus across several rack-mounted backplanes.

The DS90CP22 accepts LVDS signal levels, LVPECL levels

directly or PECL with attenuation networks.

The individual LVDS outputs can be put into TRI-STATE by

use of the enable pins.

For more details, please refer to the Application Information

section of this datasheet.

Features

n Low jitter 800 Mbps fully differential data path

n 75 ps (typ) of pk-pk jitter with PRBS = 2

23

−1 data

pattern at 800 Mbps

n Single +3.3 V Supply

n Less than 330 mW (typ) total power dissipation

n Non-blocking ’’Switch Architecture’’

n Balanced output impedance

n Output channel-to-channel skew is 35 ps (typ)

n Configurable as 2:1 mux, 1:2 demux, repeater or 1:2

signal splitter

n LVDS receiver inputs accept LVPECL signals

n Fast switch time of 1.2ns (typ)

n Fast propagation delay of 1.3ns (typ)

n Receiver input threshold

<

±

100 mV

n 16 lead SOIC package

n Inter-operates with ANSI/TIA/EIA-644-1995 LVDS

standard

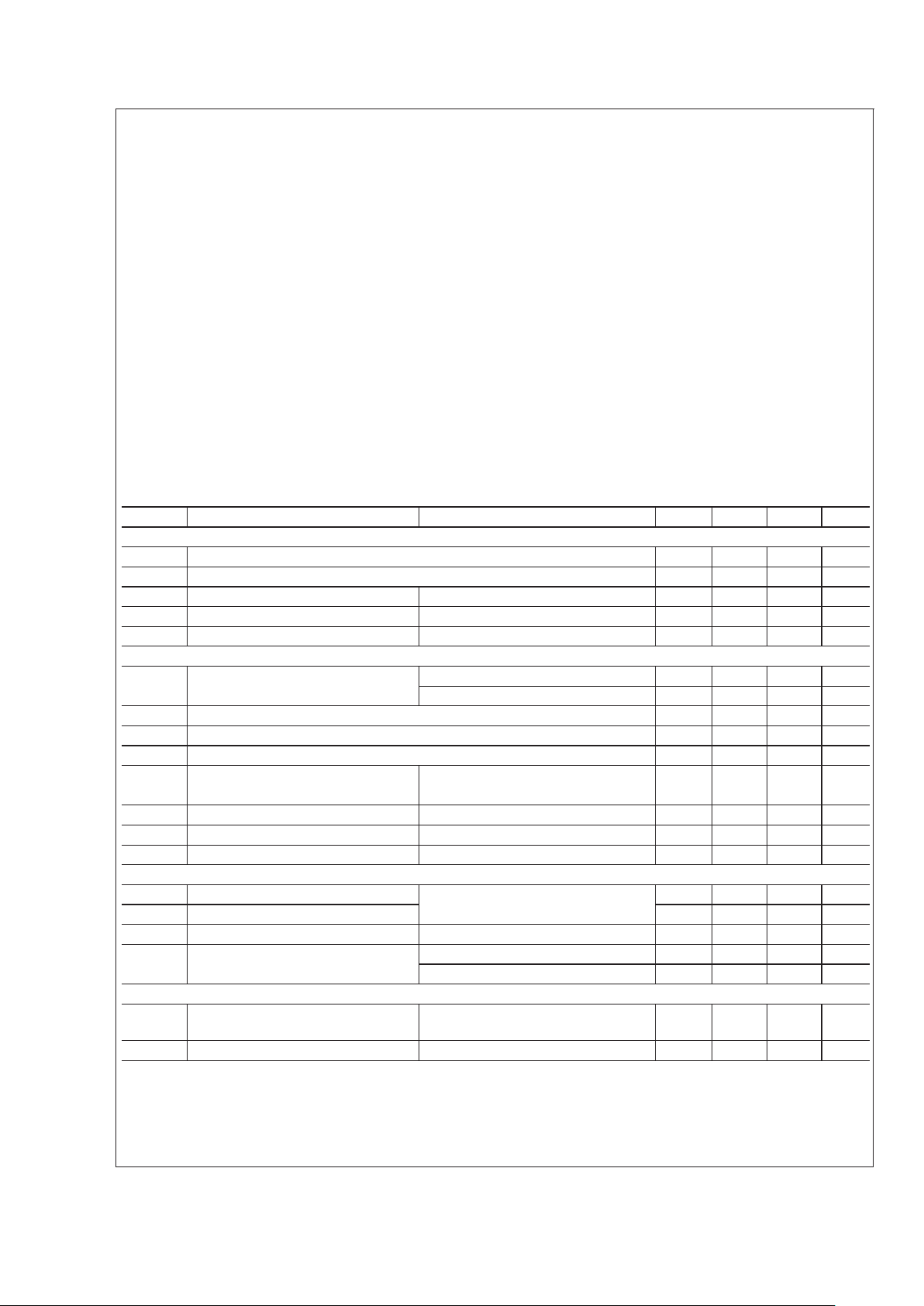

Connection Diagram

TRI-STATE®is a registered trademark of National Semiconductor Corporation.

DS101053-5

Order Number DS90CP22M-8

See NS Package Number M16A

DS101053-10

Diff. Output Eye-Pattern in 1:2 split mode@800 Mbps

Conditions: 3.3 V, PRBS = 2

23

−1 data pattern,

V

ID

= 300mV, VCM= +1.2 V, 200 ps/div, 100 mV/div

March 2000

2X2 800 Mbps LVDS Crosspoint Switch

© 2000 National Semiconductor Corporation DS101053 www.national.com

Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required,

please contact the National Semiconductor Sales Office/

Distributors for availability and specifications.

Supply Voltage (V

CC

) −0.3V to +4V

CMOS/TTL Input Voltage (EN0,

EN1, SEL0, SEL1)

−0.3V to (V

CC

+ 0.3V)

LVDS Receiver Input Voltage

(IN+, IN−) −0.3V to +4V

LVDS Driver Output Voltage

(OUT+, OUT−) −0.3V to +4V

LVDS Output Short Circuit

Current

Continuous

Junction Temperature +150˚C

Storage Temperature Range −65˚C to +150˚C

Lead Temperature

(Soldering, 4 sec.) +260˚C

Maximum Package Power Dissipation at 25˚C

16L SOIC 1.435 W

16L SOIC Package Derating 11.48 mW/˚C above

+25˚C

ESD Rating:

(HBM, 1.5kΩ, 100pF)

>

5kV

(EIAJ, 0Ω, 200pF)

>

250 V

Recommended Operating

Conditions

Min Typ Max Units

Supply Voltage (V

CC

) 3.0 3.3 3.6 V

Receiver Input Voltage 0 V

CC

V

Operating Free Air Temperature 0 +25 +70 ˚C

Electrical Characteristics

Over recommended operating supply and temperature ranges unless otherwise specified

Symbol Parameter Conditions Min Typ Max Units

CMOS/TTL DC SPECIFICATIONS (EN0,EN1,SEL0,SEL1)

V

IH

High Level Input Voltage 2.0 V

CC

V

V

IL

Low Level Input Voltage GND 0.8 V

I

IH

High Level Input Current VIN= 3.6V or 2.0V; VCC= 3.6V +7 +20 µA

I

IL

Low Level Input Current VIN= 0V or 0.8V; VCC= 3.6V

±

1

±

10 µA

V

CL

Input Clamp Voltage ICL= −18 mA −0.8 −1.5 V

LVDS OUTPUT DC SPECIFICATIONS (OUT0,OUT1)

V

OD

Differential Output Voltage RL=75Ω 270 365 475 mV

R

L

=75Ω,VCC= 3.3V, TA= 25˚C 285 365 440 mV

∆V

OD

Change in VODbetween Complimentary Output States 35 mV

V

OS

Offset Voltage (Note 3) 1.0 1.2 1.45 V

∆V

OS

Change in VOSbetween Complimentary Output States 35 mV

I

OZ

Output TRI-STATE®Current TRI-STATE Output,

±

1

±

10 µA

V

OUT=VCC

or GND

I

OFF

Power-Off Leakage Current VCC= 0V; V

OUT

= 3.6V or GND

±

1

±

10 µA

I

OS

Output Short Circuit Current V

OUT+

OR V

OUT−

= 0V −15 −25 mA

I

OSB

Both Outputs Short Circuit Current V

OUT+

AND V

OUT−

= 0V −30 −50 mA

LVDS RECEIVER DC SPECIFICATIONS (IN0,IN1)

V

TH

Differential Input High Threshold VCM= +0.05V or +1.2V or +3.25V, 0 +100 mV

V

TL

Differential Input Low Threshold Vcc = 3.3V −100 0 mV

V

CMR

Common Mode Voltage Range VID= 100mV, Vcc = 3.3V 0.05 3.25 V

I

IN

Input Current VIN= +3.0V, VCC= 3.6V or 0V

±

1

±

10 µA

V

IN

= 0V, VCC= 3.6V or 0V

±

1

±

10 µA

SUPPLY CURRENT

I

CCD

Total Supply Current RL=75Ω,CL= 5 pF,

EN0 = EN1 = High

98 125 mA

I

CCZ

TRI-STATE Supply Current EN0 = EN1 = Low 43 55 mA

Note 1: “Absolute Maximum Ratings” are these beyond which the safety of the device cannot be guaranteed. They are not meant to imply that the device should

be operated at these limits. The table of “Electrical Characteristics” provides conditions for actual device operation.

Note 2: All typical are given for V

CC

= +3.3V and TA= +25˚C, unless otherwise stated.

Note 3: V

OS

is defined and measured on the ATE as (VOH+VOL)/2.

DS90CP22

www.national.com 2

AC Electrical Characteristics

Over recommended operating supply and temperature ranges unless otherwise specified (Note 4)

Symbol Parameter Conditions Min Typ Max Units

T

SET

Input to SEL Setup Time,

Figures 1, 2

(Note 5) 0.7 0.5 ns

T

HOLD

Input to SEL Hold Time,

Figures 1, 2

(Note 5) 1.0 0.5 ns

T

SWITCH

SEL to Switched Output,

Figures 1, 2

0.9 1.2 1.7 ns

T

PHZ

Disable Time (Active to TRI-STATE) High to Z,

Figure 3

2.1 4.0 ns

T

PLZ

Disable Time (Active to TRI-STATE) Low to Z,

Figure 3

3.0 4.5 ns

T

PZH

Enable Time (TRI-STATE to Active) Z to High,

Figure 3

25.5 55.0 ns

T

PZL

Enable Time (TRI-STATE to Active) Z to Low,

Figure 3

25.5 55.0 ns

T

LHT

Output Low-to-High Transition Time, 20% to 80%,

Figure 5

290 400 580 ps

T

HLT

Output High-to-Low Transition Time, 80% to 20%,

Figure 5

290 400 580 ps

T

JIT

LVDS Data Path Peak to Peak Jitter,

(Note 6)

VID= 300mV; 50% Duty Cycle;

V

CM

= 1.2V at 800Mbps

40 90 ps

V

ID

= 300mV; PRBS=223-1 data

pattern; V

CM

= 1.2V at 800Mbps

75 190 ps

T

PLHD

Propagation Low to High Delay,

Figure 6

0.9 1.3 1.6 ns

Propagation Low to High Delay,

Figure 6

VCC= 3.3V, TA= 25˚C 1.0 1.3 1.5 ns

T

PHLD

Propagation High to Low Delay,

Figure 6

0.9 1.3 1.6 ns

Propagation High to Low Delay,

Figure 6

VCC= 3.3V, TA= 25˚C 1.0 1.3 1.5 ns

T

SKEW

Pulse Skew |T

PLHD-TPHLD

| 0 225 ps

T

CCS

Output Channel-to-Channel Skew,

Figure 7

35 80 ps

Note 4: The parameters are guaranteed by design. The limits are based on statistical analysis of the device performance over PVT (process, voltage and temperature) range.

Note 5: T

SET

and T

HOLD

time specify that data must be in a stable state before and after the SEL transition.

Note 6: The parameters are guaranteed by design. The limits are based on statistical analysis of the device performance over PVT range with the following equipment test setup: HP70004A (display mainframe) with HP70841B (pattern generator), 5 feet of RG-142 cable with DUT test board and HP83480A (digital scope mainframe) with HP83483A (20GHz scope module).

DS90CP22

www.national.com3

Loading...

Loading...