NSC DS25CP104TSQ, DS25CP104 Datasheet

November 8, 2007

DS25CP104

3.125 Gbps 4x4 LVDS Crosspoint Switch with Transmit

Pre-Emphasis and Receive Equalization

General Description

The DS25CP104 is a 3.125 Gbps 4x4 LVDS crosspoint switch

optimized for high-speed signal routing and switching over

lossy FR-4 printed circuit board backplanes and balanced cables. Fully differential signal paths ensure exceptional signal

integrity and noise immunity. The non-blocking architecture

allows connections of any input to any output or outputs. The

switch configuration can be accomplished via external pins or

the System Management Bus (SMBus) interface.

The DS25CP104 features four levels (Off, Low, Medium,

High) of transmit pre-emphasis (PE) and four levels (Off, Low,

Medium, High) of receive equalization (EQ) settable via the

SMBus interface. Off and Medium PE levels and Off and Low

EQ levels are settable with the external pins. In addition, the

SMBus circuitry enables the loss of signal (LOS

) monitors that

can inform a system of the presence of an open inputs condition (e.g. disconnected cable).

Wide input common mode range allows the switch to accept

signals with LVDS, CML and LVPECL levels; the output levels

are LVDS. A very small package footprint requires a minimal

space on the board while the flow-through pinout allows easy

board layout. Each differential input and output is internally

terminated with a 100Ω resistor to lower device insertion and

return losses, reduce component count and further minimize

board space.

Features

■

DC - 3.125 Gbps low jitter, low skew, low power operation

■

Pin and SMBus configurable, fully differential, nonblocking architecture

■

Pin (two levels) and SMBus (four levels) selectable preemphasis and equalization eliminate ISI jitter

■

Wide Input Common Mode Range enables easy interface

to CML and LVPECL drivers

■

LOS

circuitry detects open inputs fault condition

■

On-chip 100Ω input and output termination minimizes

insertion and return losses, reduces component count and

minimizes board space

■

8 kV ESD on LVDS I/O pins protects adjoining

components

■

Small 6 mm x 6 mm LLP-40 space saving package

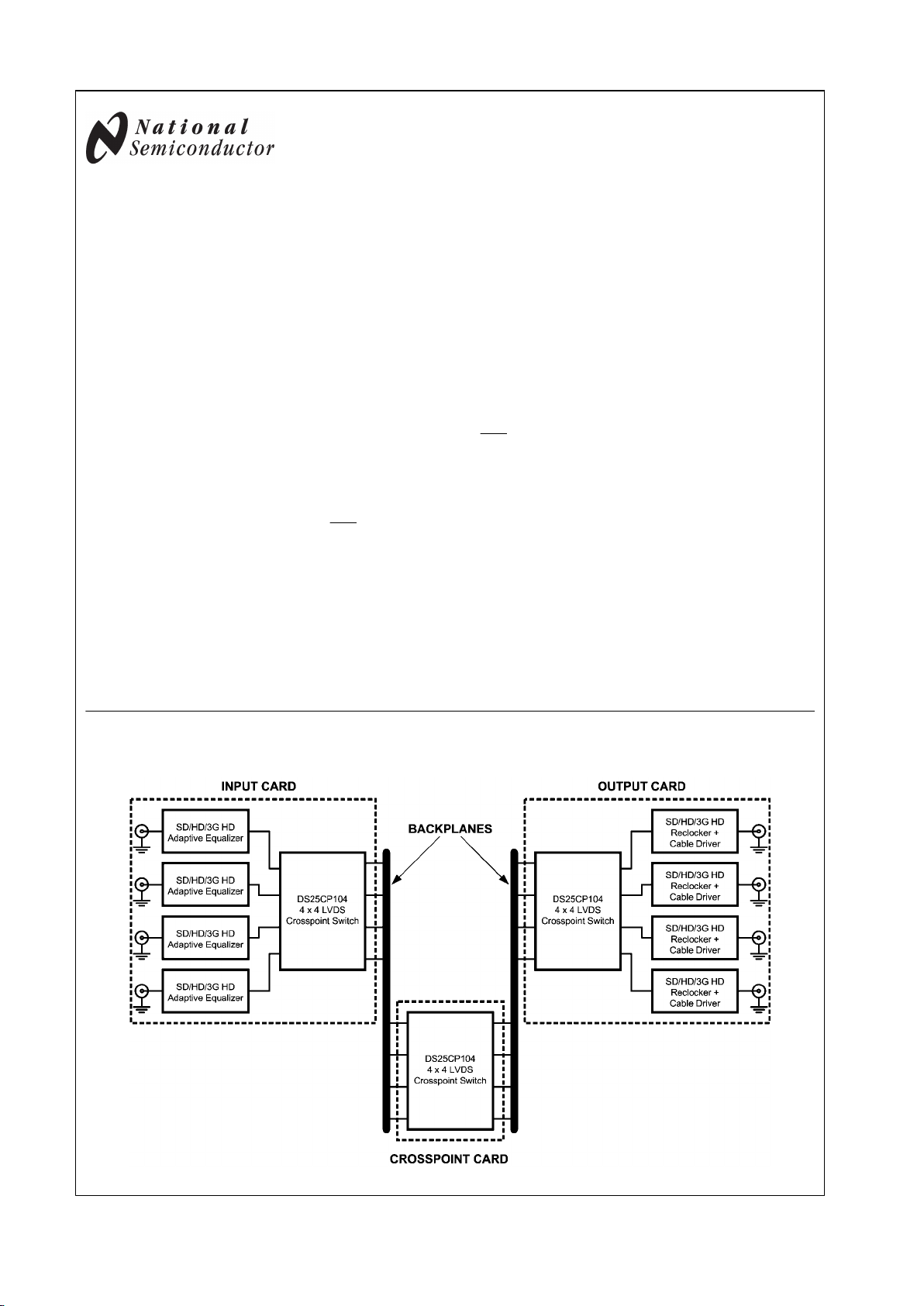

Applications

■

SD/HD/3G HD SDI Routers

■

OC-48 / STM-16

■

InfiniBand and FireWire

Typical Application

30003703

© 2007 National Semiconductor Corporation 300037 www.national.com

DS25CP104 3.125 Gbps 4x4 LVDS Crosspoint Switch with PE and EQ

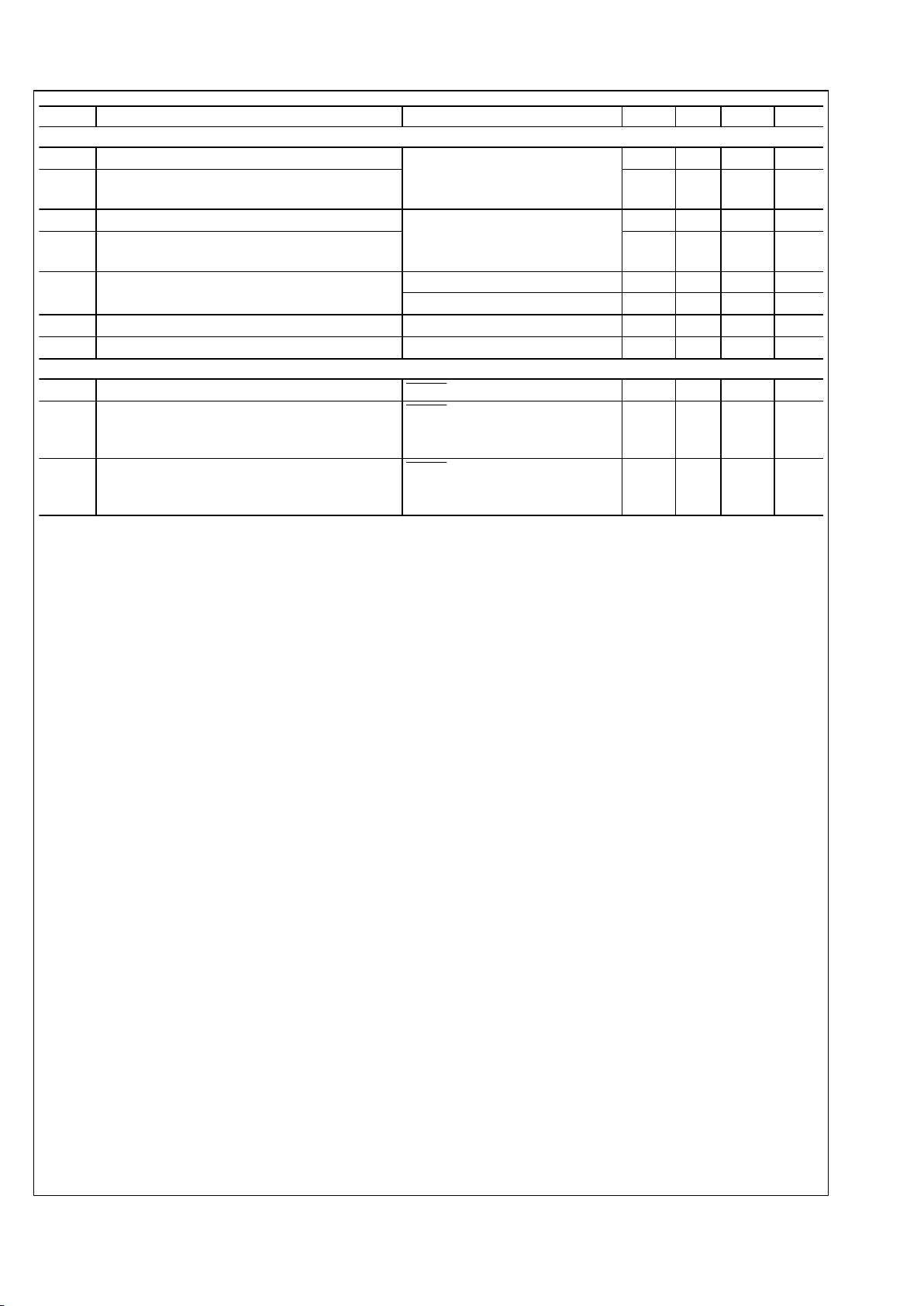

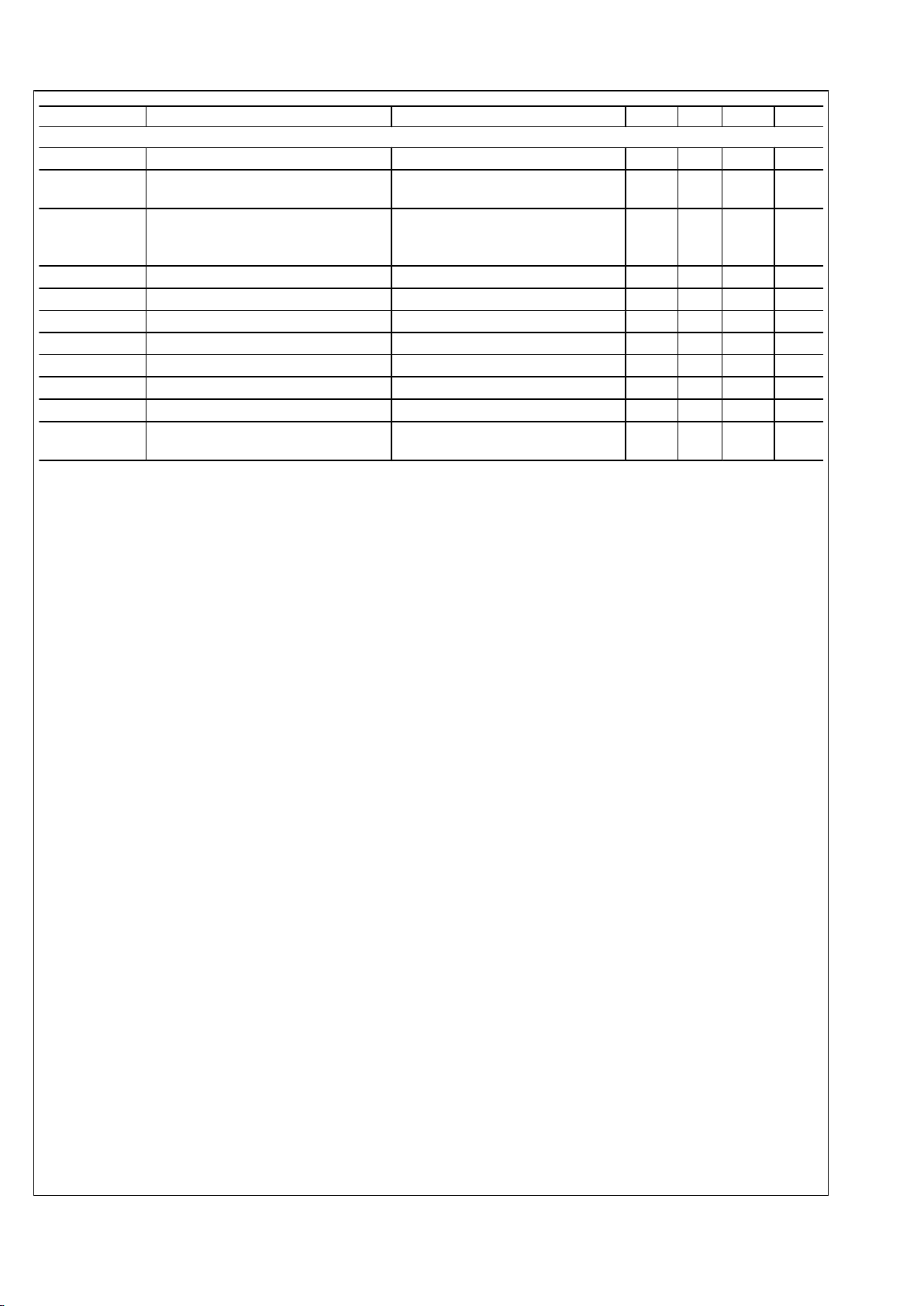

Ordering Code

NSID Function Available Equalization

Levels

Available Pre-Emphasis

Levels

DS25CP104TSQ Crosspoint Switch Off / Low / Medium / High Off / Low / Medium / High

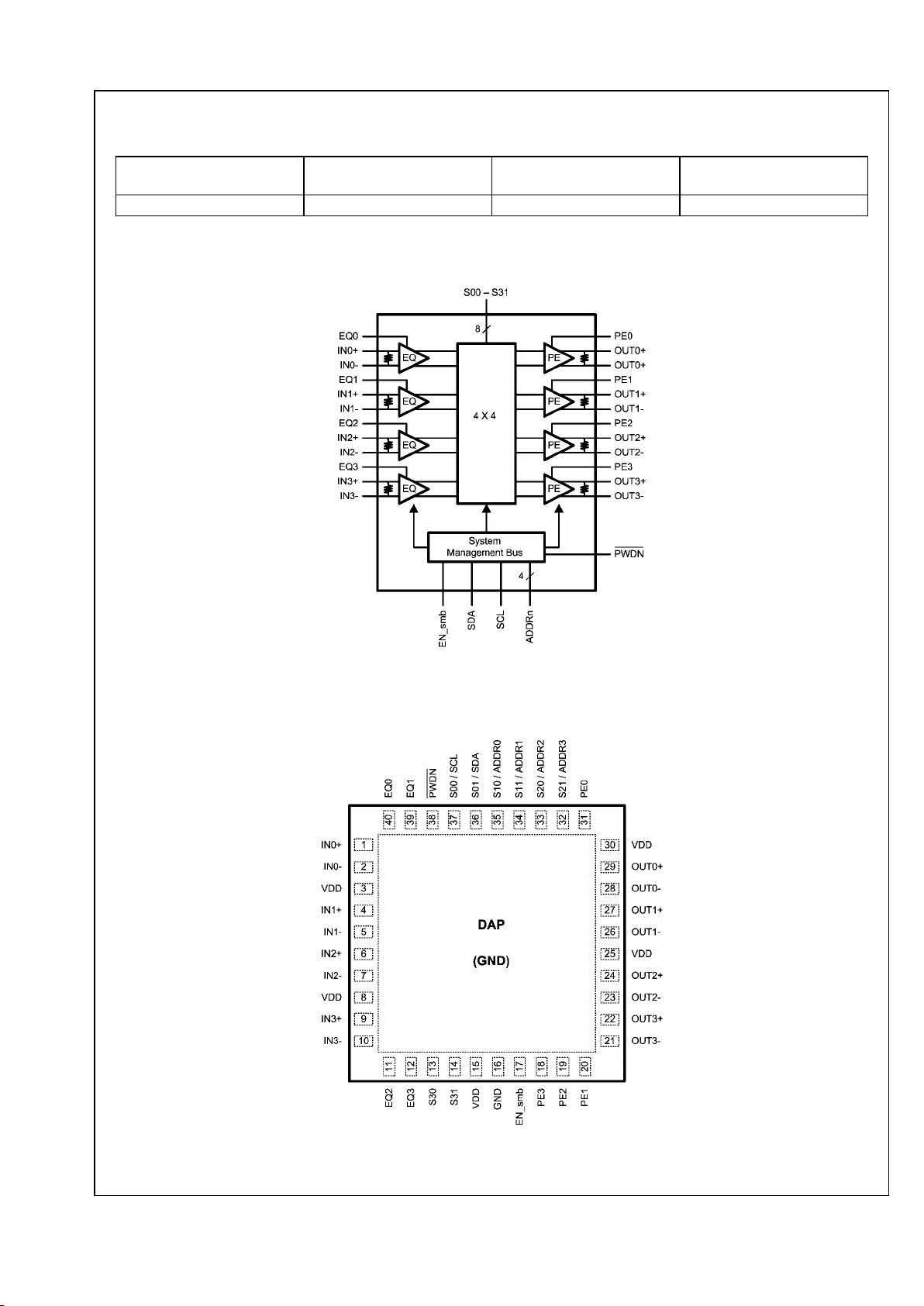

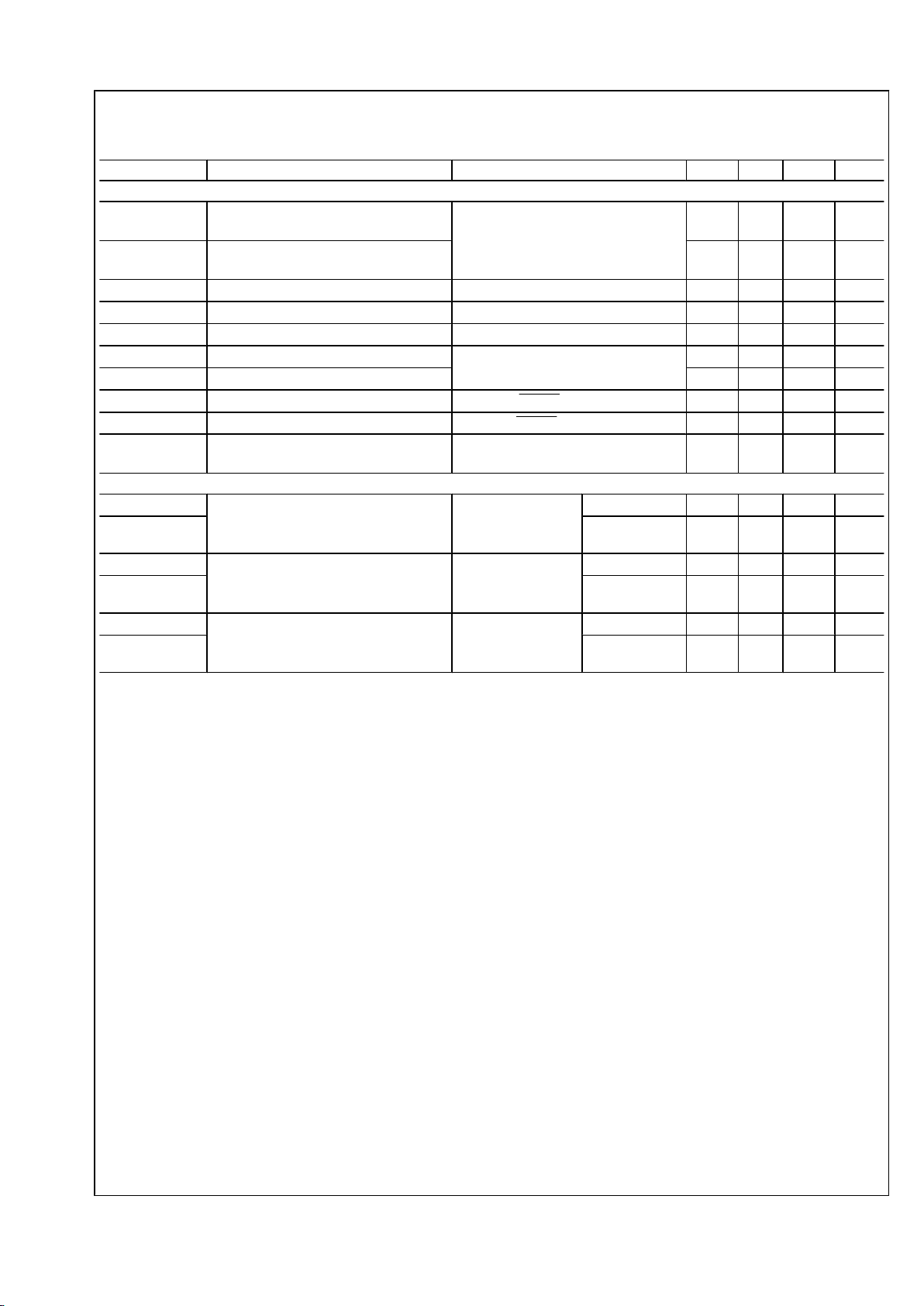

Block Diagram

30003701

Pin Diagram

30003702

DS25CP104 Pin Diagram

www.national.com 2

DS25CP104

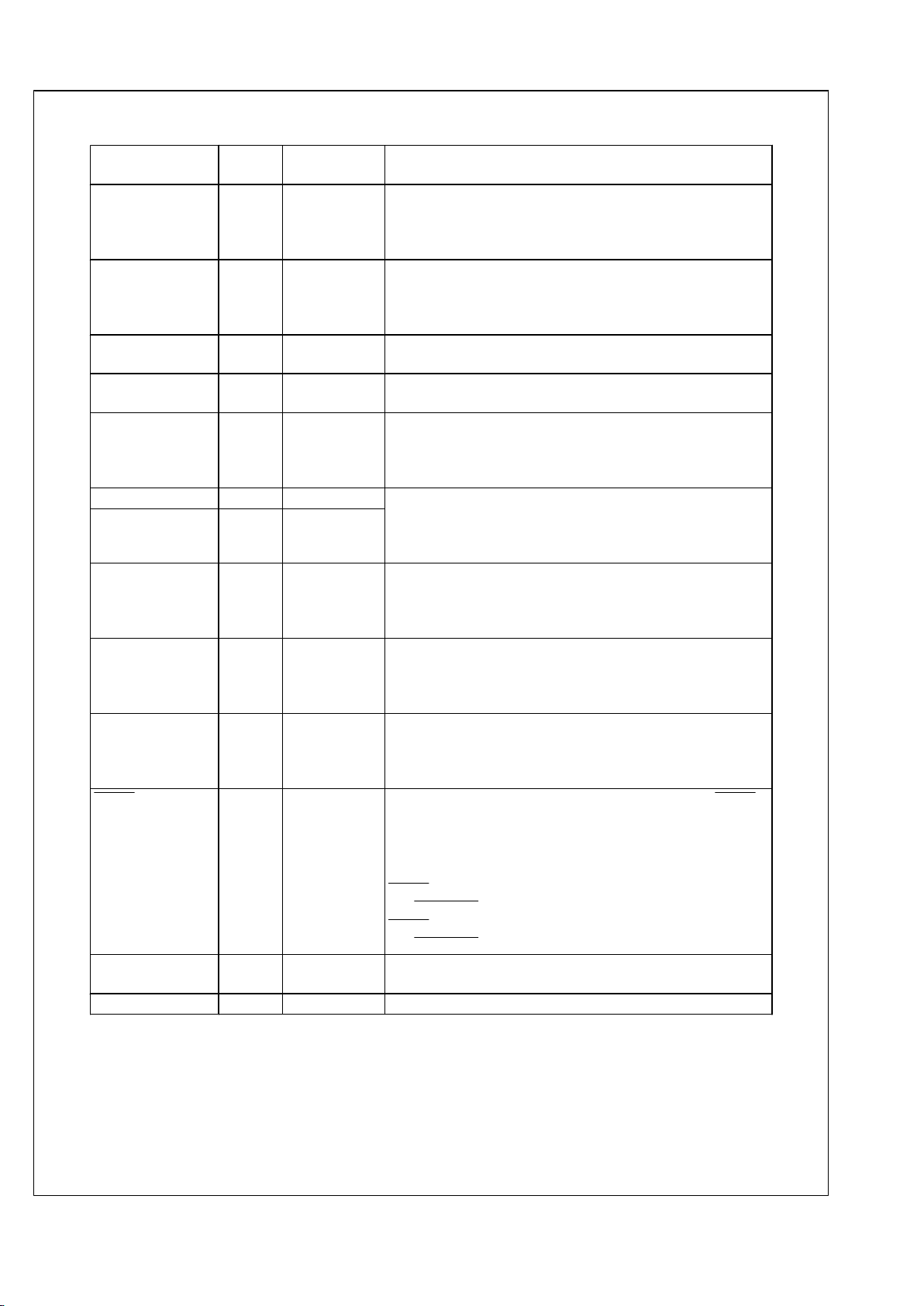

Pin Descriptions

Pin Name Pin

Number

I/O, Type Pin Description

IN0+, IN0- ,

IN1+, IN1-,

IN2+, IN2-,

IN3+, IN3-

1, 2,

4, 5,

6, 7,

9, 10

I, LVDS Inverting and non-inverting high speed LVDS input pins.

OUT0+, OUT0-,

OUT1+, OUT1-,

OUT2+, OUT2-,

OUT3+, OUT3-

29, 28,

27, 26,

24, 23,

22, 21

O, LVDS Inverting and non-inverting high speed LVDS output pins.

EQ0, EQ1,

EQ2, EQ3

40, 39,

11, 12

I, LVCMOS Receive equalization level select pins. These pins are functional

regardless of the EN_smb pin state.

PE0, PE1,

PE2, PE3

31, 20,

19, 18

I, LVCMOS Transmit pre-emphasis level select pins. These pins are functional

regardless of the EN_smb pin state.

EN_smb 17 I, LVCMOS System Management Bus (SMBus) enable pin. The pin has an

internal pull down. When the pin is set to a [1], the device is in the

SMBus mode. All SMBus registers are reset when this pin is

toggled. There is a 20k pulldown device on this pin.

S00/SCL 37 I, LVCMOS For EN_smb = [0], these pins select which LVDS input is routed

to the OUT0.

In the SMBus mode, when the EN_smb = [1], these pins are

SMBus clock input and data input pins respectively.

S01/SDA 36 I/O, LVCMOS

S10/ADDR0,

S11/ADDR1

35,

34

I, LVCMOS For EN_smb = [0], these pins select which LVDS input is routed

to the OUT1.

In the SMBus mode, when the EN_smb = [1], these pins are the

User-Set SMBus Slave Address inputs.

S20/ADDR2,

S21/ADDR3

33,

32

I, LVCMOS For EN_smb = [0], these pins select which LVDS input is routed

to the OUT2.

In the SMBus mode, when the EN_smb = H, these pins are the

User-Set SMBus Slave Address inputs.

S30, S31 13, 14 I, LVCMOS For EN_smb = [0], these pins select which LVDS input is routed

to the OUT3.

In the SMBus mode, when the EN_smb = [1], these pins are nonfunctional and should be tied to either logic H or L.

PWDN 38 I, LVCMOS For EN_smb = [0], this is the power down pin. When the PWDN is

set to a [0], the device is in the power down mode. The SMBus

circuitry can still be accessed provided the EN_smb pin is set to a

[1].

In the SMBus mode, the device is powered up by either setting the

PWDN pin to [1] OR by writing a [1] to the Control Register D[7]

bit ( SoftPWDN). The device will be powered down by setting the

PWDN pin to [0] AND by writing a [0] to the Control Register D[7]

bit ( SoftPWDN).

VDD 3, 8,

15,25, 30

Power Power supply pins.

GND 16, DAP Power Ground pin and a pad (DAP - die attach pad).

3 www.national.com

DS25CP104

Absolute Maximum Ratings (Note 4)

If Military/Aerospace specified devices are required,

please contact the National Semiconductor Sales Office/

Distributors for availability and specifications.

Supply Voltage −0.3V to +4V

LVCMOS Input Voltage −0.3V to (VCC + 0.3V)

LVCMOS Output Voltage −0.3V to (VCC + 0.3V)

LVDS Input Voltage −0.3V to +4V

LVDS Differential Input Voltage 0V to 1.0V

LVDS Output Voltage −0.3V to (VCC + 0.3V)

LVDS Differential Output Voltage 0V to 1.0V

LVDS Output Short Circuit Current

Duration

5 ms

Junction Temperature +150°C

Storage Temperature Range −65°C to +150°C

Lead Temperature Range

Soldering (4 sec.) +260°C

Maximum Package Power Dissipation at 25°C

SQA Package 4.65W

Derate SQA Package 37.2 mW/°C above +25°C

Package Thermal Resistance

θ

JA

+26.9°C/W

θ

JC

+3.8°C/W

ESD Susceptibility

HBM (Note 1)

≥8 kV

MM (Note 2)

≥250V

CDM (Note 3)

≥1250V

Note 1: Human Body Model, applicable std. JESD22-A114C

Note 2: Machine Model, applicable std. JESD22-A115-A

Note 3: Field Induced Charge Device Model, applicable std.

JESD22-C101-C

Recommended Operating

Conditions

Min Typ Max Units

Supply Voltage (VCC) 3.0 3.3 3.6 V

Receiver Differential Input

Voltage (VID)

0 1 V

Operating Free Air

Temperature (TA)

−40 +25 +85 °C

SMBus (SDA, SCL) 3.6 V

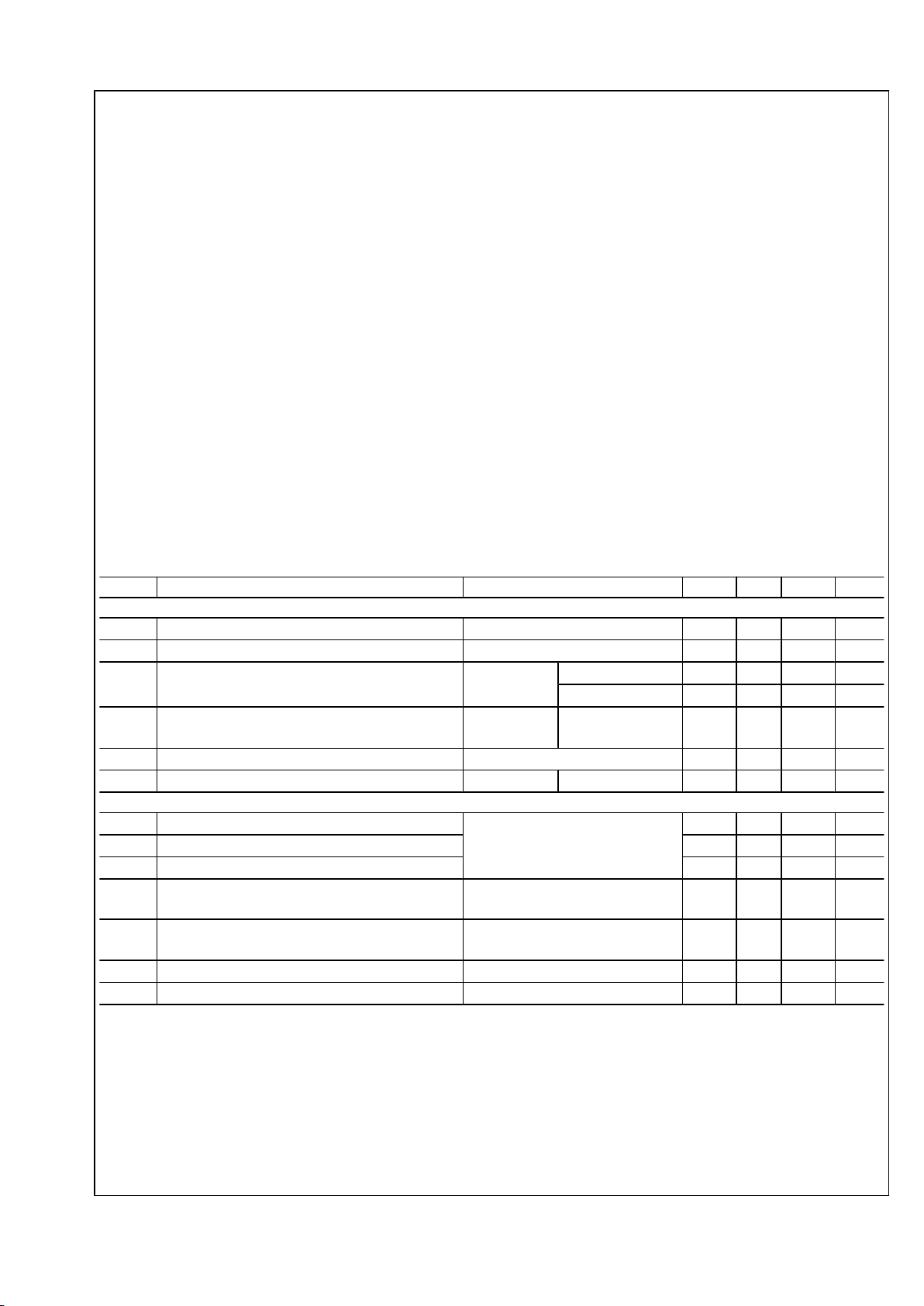

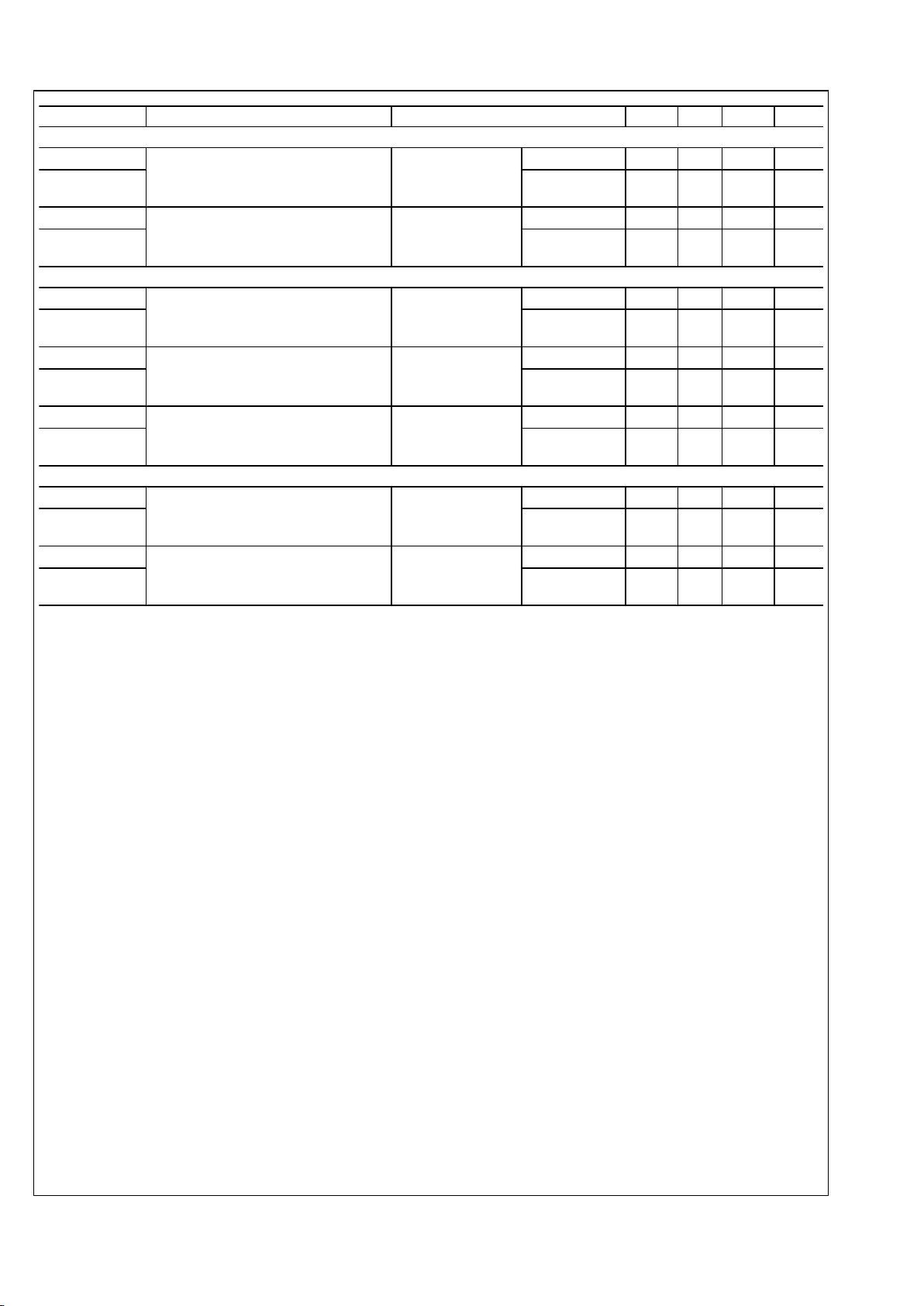

DC Electrical Characteristics

Over recommended operating supply and temperature ranges unless otherwise specified. (Notes 5, 6, 7)

Symbol Parameter Conditions Min Typ Max Units

LVCMOS DC SPECIFICATIONS

V

IH

High Level Input Voltage 2.0 V

CC

V

V

IL

Low Level Input Voltage GND 0.8 V

I

IH

High Level Input Current VIN = 3.6V

VCC = 3.6V

0 ±10

μA

EN_smb pin 40 175 250

μA

I

IL

Low Level Input Current VIN = GND

VCC = 3.6V

0 ±10

μA

V

CL

Input Clamp Voltage ICL = −18 mA, VCC = 0V −0.9 −1.5 V

V

OL

Low Level Output Voltage IOL= 4 mA SDA pin 0.4 V

LVDS INPUT DC SPECIFICATIONS

V

ID

Input Differential Voltage 0 1 V

V

TH

Differential Input High Threshold

VCM = +0.05V or VCC-0.05V

0 +100 mV

V

TL

Differential Input Low Threshold

−100 0 mV

V

CMR

Input Common Mode Voltage Range

VID = 100 mV

0.05

VCC -

0.05

V

I

IN

Input Current

VIN = +3.6V or 0V

VCC = 3.6V or 0V

±1 ±10

μA

C

IN

Input Capacitance Any LVDS Input Pin to GND 1.7 pF

R

IN

Input Termination Resistor Between IN+ and IN-

100

Ω

www.national.com 4

DS25CP104

Symbol Parameter Conditions Min Typ Max Units

LVDS OUTPUT DC SPECIFICATIONS

V

OD

Differential Output Voltage

RL = 100Ω

250 350 450 mV

ΔV

OD

Change in Magnitude of VOD for Complimentary

Output States

-35 35 mV

V

OS

Offset Voltage

RL = 100Ω

1.05 1.2 1.375 V

ΔV

OS

Change in Magnitude of VOS for Complimentary

Output States

-35 35 mV

I

OS

Output Short Circuit Current (Note 8)

OUT to GND -35 -55 mA

OUT to V

CC

7 55 mA

C

OUT

Output Capacitance Any LVDS Output Pin to GND

1.2 pF

R

OUT

Output Termination Resistor Between OUT+ and OUT-

100

Ω

SUPPLY CURRENT

I

CC1

Supply Current PWDN = 0 40 50 mA

I

CC2

Supply Current PWDN = 1

PE = Off, EQ = Off

Broadcast (1:4) Mode

145 175 mA

I

CC3

Supply Current PWDN = 1

PE = Off, EQ = Off

Quad Buffer (4:4) Mode

157 190 mA

Note 4: “Absolute Maximum Ratings” indicate limits beyond which damage to the device may occur, including inoperability and degradation of device reliability

and/or performance. Functional operation of the device and/or non-degradation at the Absolute Maximum Ratings or other conditions beyond those indicated in

the Recommended Operating Conditions is not implied. The Recommended Operating Conditions indicate conditions at which the device is functional and the

device should not be operated beyond such conditions.

Note 5: The Electrical Characteristics tables list guaranteed specifications under the listed Recommended Operating Conditions except as otherwise modified

or specified by the Electrical Characteristics Conditions and/or Notes. Typical specifications are estimations only and are not guaranteed.

Note 6: Current into device pins is defined as positive. Current out of device pins is defined as negative. All voltages are referenced to ground except VOD and

ΔVOD.

Note 7: Typical values represent most likely parametric norms for VCC = +3.3V and TA = +25°C, and at the Recommended Operation Conditions at the time of

product characterization and are not guaranteed.

Note 8: Output short circuit current (IOS) is specified as magnitude only, minus sign indicates direction only.

5 www.national.com

DS25CP104

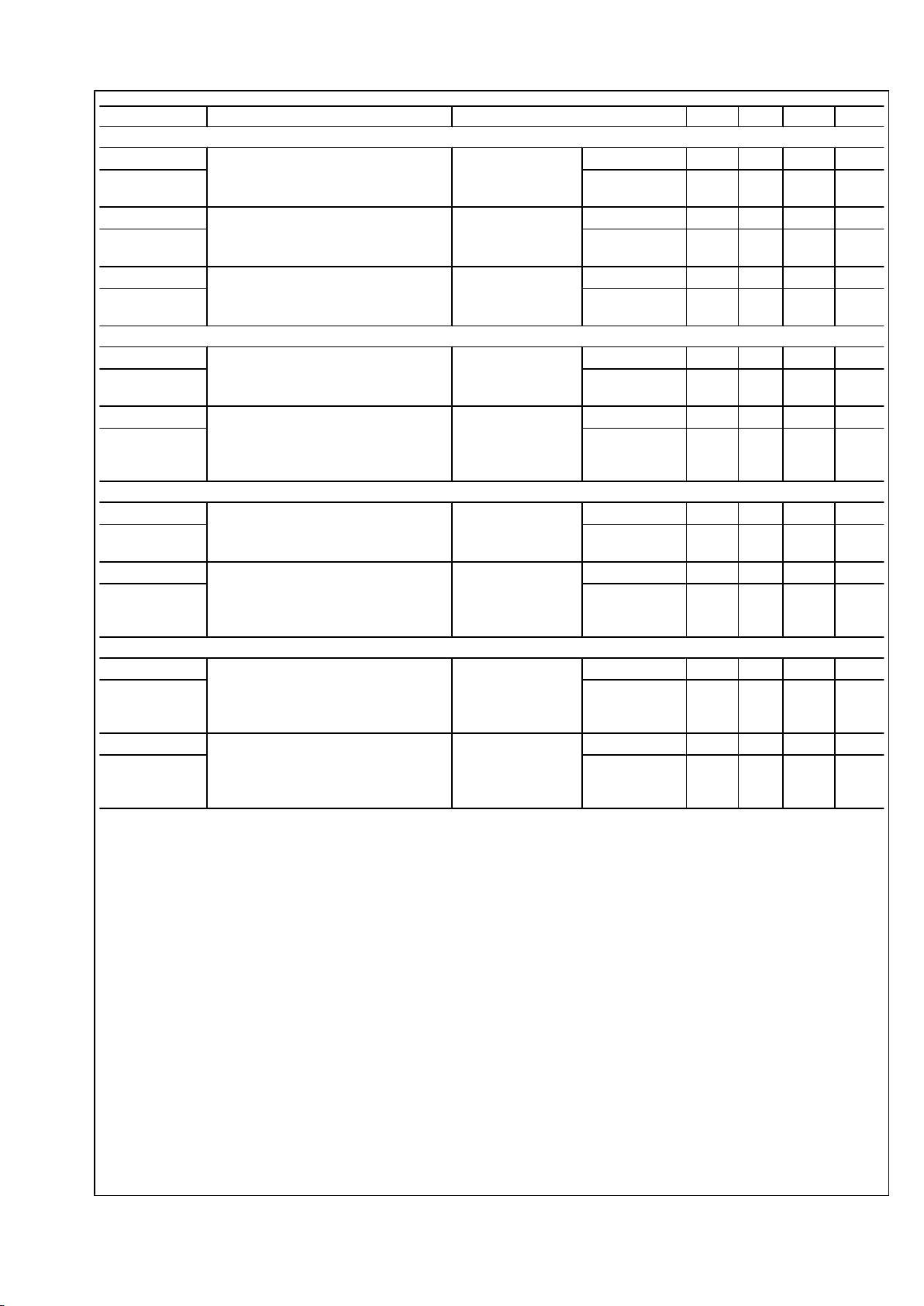

AC Electrical Characteristics

Over recommended operating supply and temperature ranges unless otherwise specified. (Notes 9, 10)

Symbol Parameter Conditions Min Typ Max Units

LVDS OUTPUT AC SPECIFICATIONS (Note 11)

t

PLHD

Differential Propagation Delay Low to

High

RL = 100Ω

480 650 ps

t

PHLD

Differential Propagation Delay High to

Low

460 650 ps

t

SKD1

Pulse Skew |t

PLHD

− t

PHLD

| , (Note 12) 20 100 ps

t

SKD2

Channel to Channel Skew , (Note 13) 40 125 ps

t

SKD3

Part to Part Skew , (Note 14) 50 200 ps

t

LHT

Rise Time

RL = 100Ω

80 150 ps

t

HLT

Fall Time 80 150 ps

t

ON

Power Up Time

Time from PWDN =LH to OUTn active

6 20

μs

t

OFF

Power Down Time

Time from PWDN =HL to OUTn inactive

8 25 ns

t

SEL

Select Time Time from Sn =LH or HL to new signal

at OUTn

8 12 ns

JITTER PERFORMANCE WITH EQ = Off, PE = Off (Note 11)(Figure 5)

t

RJ1

Random Jitter (RMS Value)

No Test Channels

(Note 15)

VID = 350 mV

VCM = 1.2V

Clock (RZ)

1.25 GHz 0.5 1.1 ps

t

RJ2

1.5625 GHz 0.5 1.1 ps

t

DJ1

Deterministic Jitter (Peak to Peak)

No Test Channels

(Note 16)

VID = 350 mV

VCM = 1.2V

K28.5 (NRZ)

2.5 Gbps 10 22 ps

t

DJ2

3.125 Gbps 10 27 ps

t

TJ1

Total Jitter (Peak to Peak)

No Test Channels

(Note 17)

VID = 350 mV

VCM = 1.2V

PRBS-23 (NRZ)

2.5 Gbps 0.07 0.11

UI

P-P

t

TJ2

3.125 Gbps 0.13 0.16

UI

P-P

www.national.com 6

DS25CP104

Symbol Parameter Conditions Min Typ Max Units

JITTER PERFORMANCE WITH EQ = Off, PE = Low(Note 11) (Figure 6 Figure 9)

t

RJ1A

Random Jitter (RMS Value)

Test Channels A

(Note 15)

VID = 350 mV

VCM = 1.2V

Clock (RZ)

1.25 GHz 0.5 1.1 ps

t

RJ2A

1.5625 GHz 0.5 1.1 ps

t

DJ1A

Deterministic Jitter (Peak to Peak)

Test Channels A

(Note 16)

VID = 350 mV

VCM = 1.2V

K28.5 (NRZ)

2.5 Gbps 10 22 ps

t

DJ2A

3.125 Gbps 10 27 ps

JITTER PERFORMANCE WITH EQ = Off, PE = Medium (Note 11) (Figure 6 Figure 9)

t

RJ1B

Random Jitter (RMS Value)

Test Channels B

(Note 15)

VID = 350 mV

VCM = 1.2V

Clock (RZ)

1.25 GHz 0.5 1.1 ps

t

RJ2B

1.5625 GHz 0.5 1.1 ps

t

DJ1B

Deterministic Jitter (Peak to Peak)

Test Channels B

(Note 16)

VID = 350 mV

VCM = 1.2V

K28.5 (NRZ)

2.5 Gbps 12 30 ps

t

DJ2B

3.125 Gbps 12 30 ps

t

TJ1B

Total Jitter (Peak to Peak)

Test Channels B

(Note 17)

VID = 350 mV

VCM = 1.2V

PRBS-23 (NRZ)

2.5 Gbps 0.08 0.10

UI

P-P

t

TJ2B

3.125 Gbps 0.10 0.15

UI

P-P

JITTER PERFORMANCE WITH EQ = Off, PE = High (Note 11) (Figures 6, 9)

t

RJ1C

Random Jitter (RMS Value)

Test Channels C

(Note 15)

VID = 350 mV

VCM = 1.2V

Clock (RZ)

1.25 GHz 0.5 1.1 ps

t

RJ2C

1.5625 GHz 0.5 1.1 ps

t

DJ1C

Deterministic Jitter (Peak to Peak)

Test Channels C

(Note 16)

VID = 350 mV

VCM = 1.2V

K28.5 (NRZ)

2.5 Gbps 30 60 ps

t

DJ2C

3.125 Gbps 30 65 ps

7 www.national.com

DS25CP104

Symbol Parameter Conditions Min Typ Max Units

JITTER PERFORMANCE WITH PE = Off, EQ = Low (Note 11) (Figure 7 Figure 9)

t

RJ1D

Random Jitter (RMS Value)

Test Channels D

(Note 15)

VID = 350 mV

VCM = 1.2V

Clock (RZ)

1.25 GHz 0.5 1.1 ps

t

RJ2D

1.5625 GHz 0.5 1.1 ps

t

DJ1D

Deterministic Jitter (Peak to Peak)

Test Channels D

(Note 16)

VID = 350 mV

VCM = 1.2V

K28.5 (NRZ)

2.5 Gbps 20 40 ps

t

DJ2D

3.125 Gbps 20 40 ps

t

TJ1D

Total Jitter (Peak to Peak)

Test Channels D

(Note 17)

VID = 350 mV

VCM = 1.2V

PRBS-23 (NRZ)

2.5 Gbps 0.08 0.15

UI

P-P

t

TJ2D

3.125 Gbps 0.09 0.20

UI

P-P

JITTER PERFORMANCE WITH PE = Off, EQ = Medium (Note 11) (Figures 7, 9)

t

RJ1E

Random Jitter (RMS Value)

Test Channels E

(Note 15)

VID = 350 mV

VCM = 1.2V

Clock (RZ)

1.25 GHz 0.5 1.1 ps

t

RJ2E

1.5625 GHz 0.5 1.1 ps

t

DJ1E

Residual Deterministic Jitter (Peak to

Peak)

Test Channels E

(Note 16)

VID = 350 mV

VCM = 1.2V

K28.5 (NRZ)

2.5 Gbps 35 60 ps

t

DJ2E

3.125 Gbps 28 55 ps

JITTER PERFORMANCE WITH PE = Off, EQ = High (Note 11) (Figures 7, 9)

t

RJ1F

Random Jitter (RMS Value)

Test Channels F

(Note 15)

VID = 350 mV

VCM = 1.2V

Clock (RZ)

1.25 GHz 1.3 1.8 ps

t

RJ2F

1.5625 GHz 1.4 2.4 ps

t

DJ1F

Residual Deterministic Jitter (Peak to

Peak)

Test Channels F

(Note 16)

VID = 350 mV

VCM = 1.2V

K28.5 (NRZ)

2.5 Gbps 30 75 ps

t

DJ2F

3.125 Gbps 35 90 ps

JITTER PERFORMANCE WITH PE = Medium, EQ = Low (Note 11) (Figures 7, 9)

t

RJ1G

Random Jitter (RMS Value)

Input Test Channels D

Output Test Channels B

(Note 15)

VID = 350 mV

VCM = 1.2V

Clock (RZ)

1.25 GHz 0.5 1.1 ps

t

RJ2G

1.5625 GHz 0.5 1.1 ps

t

DJ1G

Deterministic Jitter (Peak to Peak)

Input Test Channels D

Output Test Channels B

(Note 16)

VID = 350 mV

VCM = 1.2V

K28.5 (NRZ)

2.5 Gbps 25 ps

t

DJ2G

3.125 Gbps 20 ps

www.national.com 8

DS25CP104

Symbol Parameter Conditions Min Typ Max Units

SMBus AC SPECIFICATIONS

f

SMB

SMBus Operating Frequency 10 100 kHz

t

BUF

Bus free time between Stop and Start

Conditions

4.7

μs

t

HD:SDA

Hold time after (Repeated) Start

Condition. After this period, the first clock

is generated.

4.0

μs

t

SU:SDA

Repeated Start Condition setup time. 4.7

μs

t

SU:SDO

Stop Condition setup time 4.0

μs

t

HD:DAT

Data hold time 300 ns

t

SU:DAT

Data setup time 250 ns

t

TIMEOUT

Detect clock low timeout 25 35 ms

t

LOW

Clock low period 4.7

μs

t

HIGH

Clock high period 4.0 50

μs

t

POR

Time in which a device must be

operational after power-on reset

500 ms

Note 9: The Electrical Characteristics tables list guaranteed specifications under the listed Recommended Operating Conditions except as otherwise modified

or specified by the Electrical Characteristics Conditions and/or Notes. Typical specifications are estimations only and are not guaranteed.

Note 10: Typical values represent most likely parametric norms for VCC = +3.3V and TA = +25°C, and at the Recommended Operation Conditions at the time of

product characterization and are not guaranteed.

Note 11: Specification is guaranteed by characterization and is not tested in production.

Note 12: t

SKD1

, |t

PLHD

− t

PHLD

|, Pulse Skew, is the magnitude difference in differential propagation delay time between the positive going edge and the negative

going edge of the same channel.

Note 13: t

SKD2

, Channel to Channel Skew, is the difference in propagation delay (t

PLHD

or t

PHLD

) among all output channels in Broadcast mode (any one input to

all outputs).

Note 14: t

SKD3

, Part to Part Skew, is defined as the difference between the same signal path of any two devices running at the same VCC and within 5°C of each

other within the operating temperature range.

Note 15: Measured on a clock edge with a histogram and an acummulation of 1500 histogram hits. Input stimulus jitter is subtracted geometrically.

Note 16: Tested with a combination of the 1100000101 (K28.5+ character) and 0011111010 (K28.5- character) patterns. Input stimulus jitter is subtracted

algebraically.

Note 17: Measured on an eye diagram with a histogram and an acummulation of 3500 histogram hits. Input stimulus jitter is subtracted.

9 www.national.com

DS25CP104

Loading...

Loading...