NSC DP83905AVQB Datasheet

PRELIMINARY

November 1995

DP83905 AT/LANTIC AT Local Area Network Twisted-Pair Interface Controller

DP83905 AT/LANTIC

TM

AT Local Area Network Twisted-Pair

Interface Controller

General Description

The AT/LANTIC AT Local Area Network Twisted-pair Interface Controller is a CMOS VLSI device designed for easy

implementation of CSMA/CD local area networks.

Unique to the AT/LANTIC is the integration of the entire bus

interface for PC-AT

bus based systems. Hardware and software selectable options allow the AT/LANTIC’s bus interface to be configured

software compatible to either an NE2000 or Ethercard

TM

PLUS16

. All bus drivers and control logic are integrated

to reduce board cost and area.

Supported network interfaces include 10BASE5 or

10BASE2 Ethernet via an external transciever connected to

its AUI port, and Twisted-pair Ethernet (10BASE-T) using

the on-board transceiver. The AT/LANTIC provides the

Ethernet Media Access Control (MAC), Encode-Decode

(ENDEC) with an AUI interface, and 10BASE-T transceiver

functions in accordance with the IEEE 802.3 standards.

The AT/LANTIC’s integrated 10BASE-T transceiver fully

complies with the IEEE standard.This functional block incorporates the receiver, transmitter, collision, heartbeat, Ioopback, jabber, and link integrity blocks as defined in the standard. The transceiver when combined with equalization resistors, transmit/receive filters, and pulse transformers provides a complete physical interface from the AT/LANTIC

Controller’s ENDEC module and the twisted pair medium.

ISA (Industry Standard Architecture)

É

(Continued)

Features

Y

Controller and integrated bus interface solution for IEEE

802.3, 10BASE5, 10BASE2, and 10BASE-T

Y

Software compatible with

try standard Ethernet Adapters

Y

Selectable buffer memory size

Y

No external bus logic or drivers

Y

Integrated controller, ENDEC, and transceiver

Y

Full IEEE 802.3 AUI interface

Y

Single 5V supply

10BASE-T TRANSCEIVER MODULE:

Y

Integrates transceiver functionality:

Ð Transmitter and receiver functions

Ð Collision detect, heartbeat and jabber

Ð Selectable link integrity test or link disable

Ð Polarity Detection/Correction

ENDEC MODULE:

Y

10 Mbit/s Manchester encoding/decoding

Y

Squelch on receive and collision pairs

MAC/CONTROLLER MODULE:

Y

Software compatible with DP8390, DP83901, DP83902

Y

Efficient buffer management implementation

NovellÉ’s NE2000/Plus

indus-

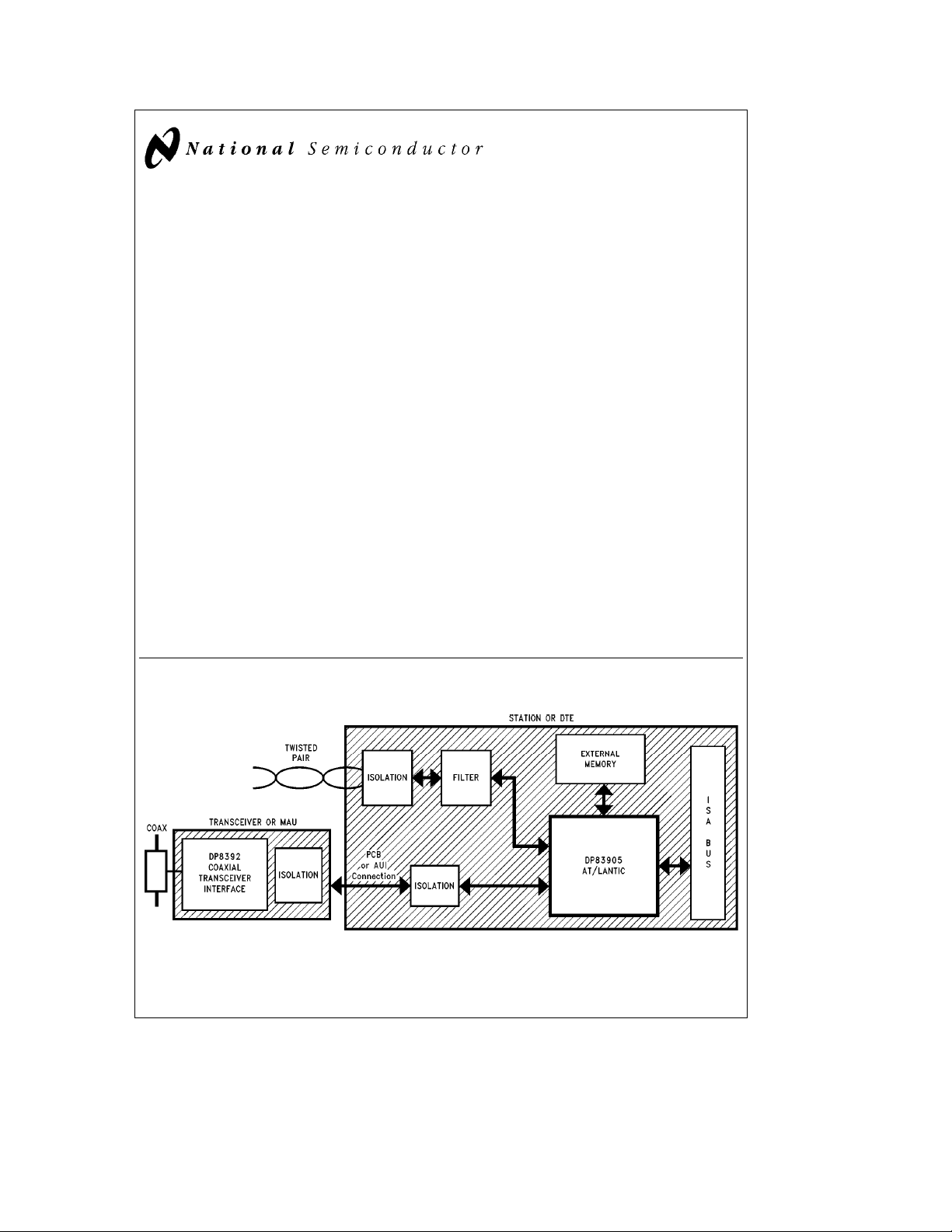

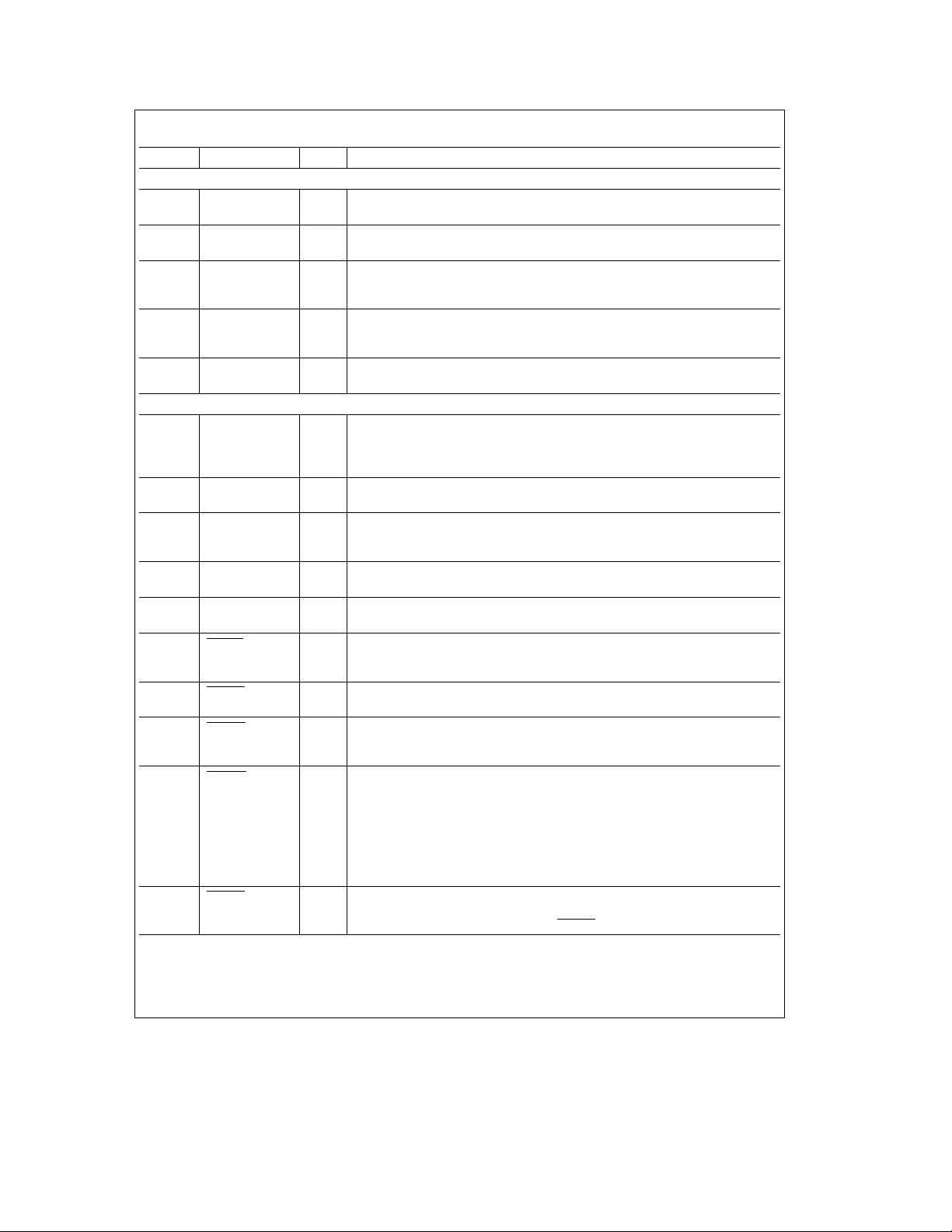

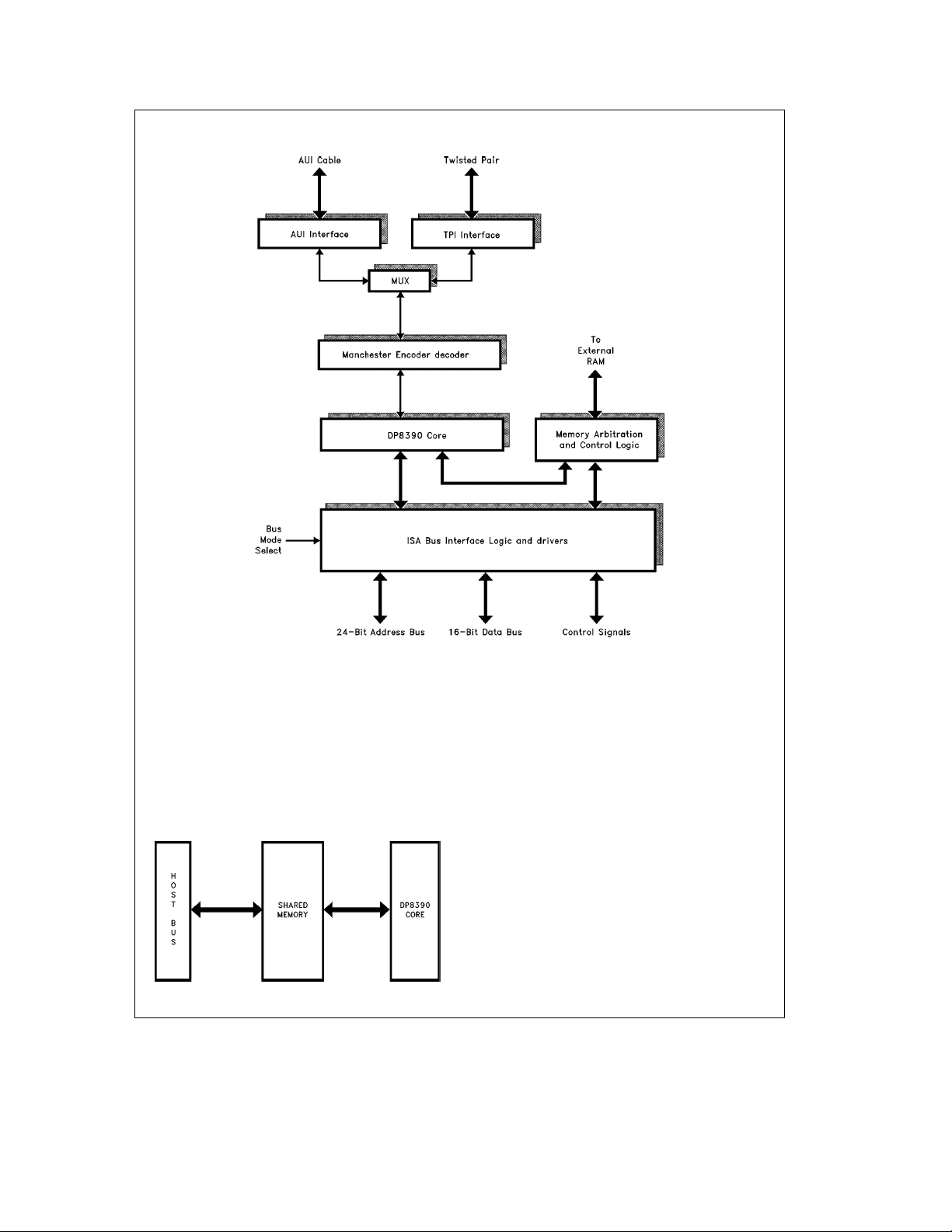

1.0 System Diagram

TL/F/11498– 1

TRI-STATEÉis a registered trademark of National Semiconductor Corporation.

TM

AT/LANTIC

PC-AT

Novell

EtherCard PLUS

C

1995 National Semiconductor Corporation RRD-B30M115/Printed in U. S. A.

is a trademark of National Semiconductor Corporation.

is a registered trademark of International Business Machines Corp.

É

is a registered trademark of Novell, Inc.

É

TM

and EtherCard PLUS 16TMare trademarks of Standard Microsystems Corp.

TL/F/11498

General Description (Continued)

The integrated ENDEC module allows Manchester encoding and decoding via a differential transceiver and phase

lock Ioop decoder at 10 Mbit/sec. Also included are a collision detect translator and diagnostic loopback capability.

The ENDEC module interfaces directly to the transceiver

module, and also provides a fully IEEE compliant AUI (Attachment Unit Interface) for connection to other media

transceivers.

Table of Contents

1.0 SYSTEM DIAGRAM

1.1 Connection Diagram

2.0 PIN DESCRIPTION

3.0 SIMPLIFIED APPLICATION DIAGRAM

4.0 FUNCTIONAL DESCRIPTION

4.1 Bus Interface Block

4.2 Power on RESET operation

4.3 EEPROM Operation

4.4 Jumpered and Jumperless Operation Support

4.5 Low Power Operation

4.6 Boot PROM Operation

4.7 DP8390 Core (Network Interface Controller)

4.8 Twisted Pair Interface Module

4.9 Encoder/Decoder (ENDEC) Module

The Media Access Control function which is provided by the

Network Interface Control module (NIC) provides simple

and efficient packet transmission and reception control by

means of off-board memory which can be accessed either

through an I/O port or mapped into the system memory.

AT/LANTIC Controller provides a comprehensive solution

for 10BASE-T IEEE 802.3 networks. Due to the inherent

constraints of CMOS processing, isolation is required at the

AUI differential signal interface for 10BASE5 and 10BASE2

applications.

5.0 REGISTER DESCRIPTIONS

5.1 Configuration Registers

5.2 Shared Memory Mode Control Registers

5.3 NIC Core Registers

5.4 DP8390 Core DMA Registers

6.0 OPERATION OF AT/LANTIC CONTROLLER

6.1 Transmit/Receive Packet Encapsulation/

Decapsulation

6.2 Buffer Memory Access Control (DMA)

6.3 Packet Reception

6.4 Packet Transmission

6.5 Loopback Diagnostics

6.6 Memory Arbitration and Bus Operation

6.7 Functional Bus Timing

7.0 PRELIMINARY ELECTRICAL CHARACTERISTICS

8.0 PRELIMINARY SWITCHING CHARACTERISTICS

9.0 AC TIMING TEST CONDITIONS

2

1.0 System Diagram (Continued)

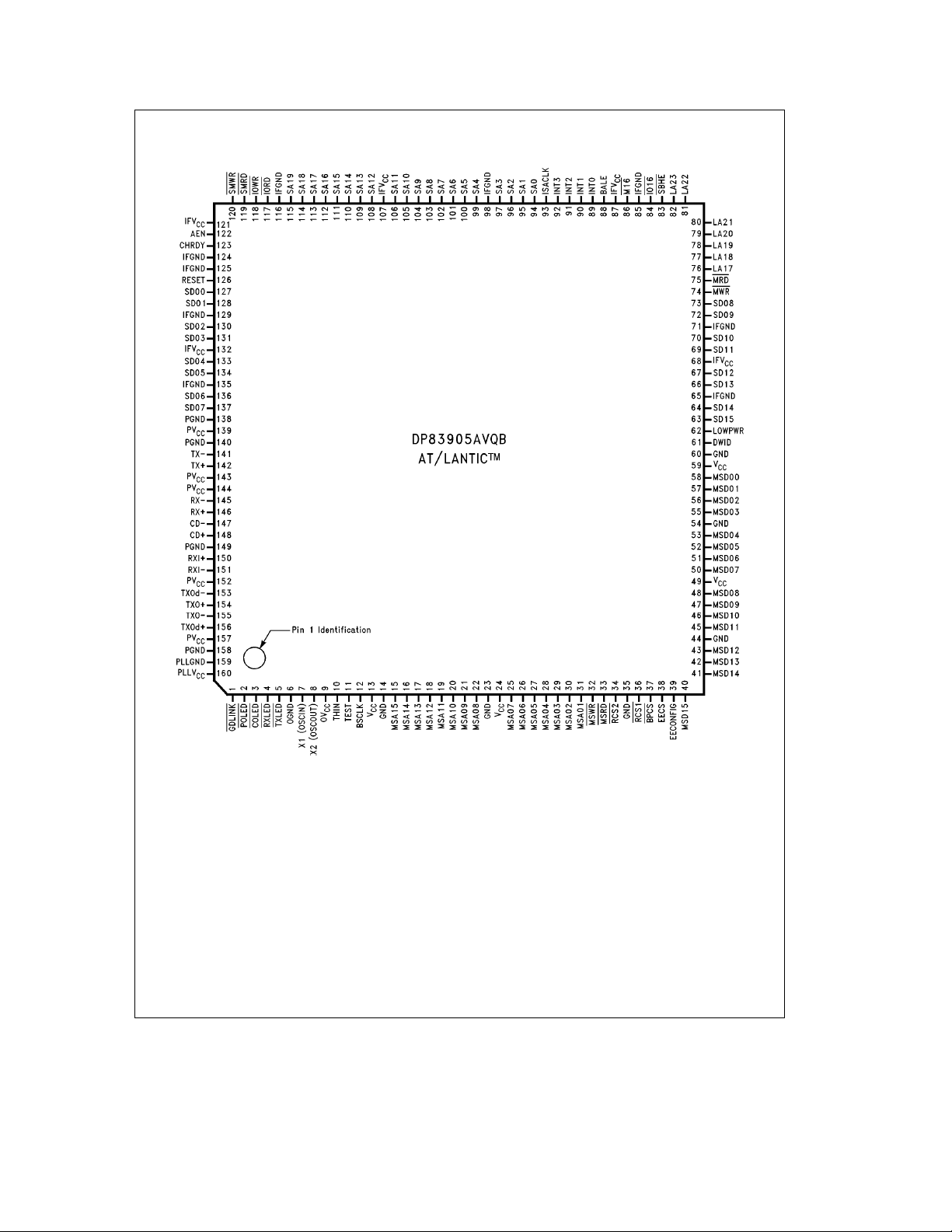

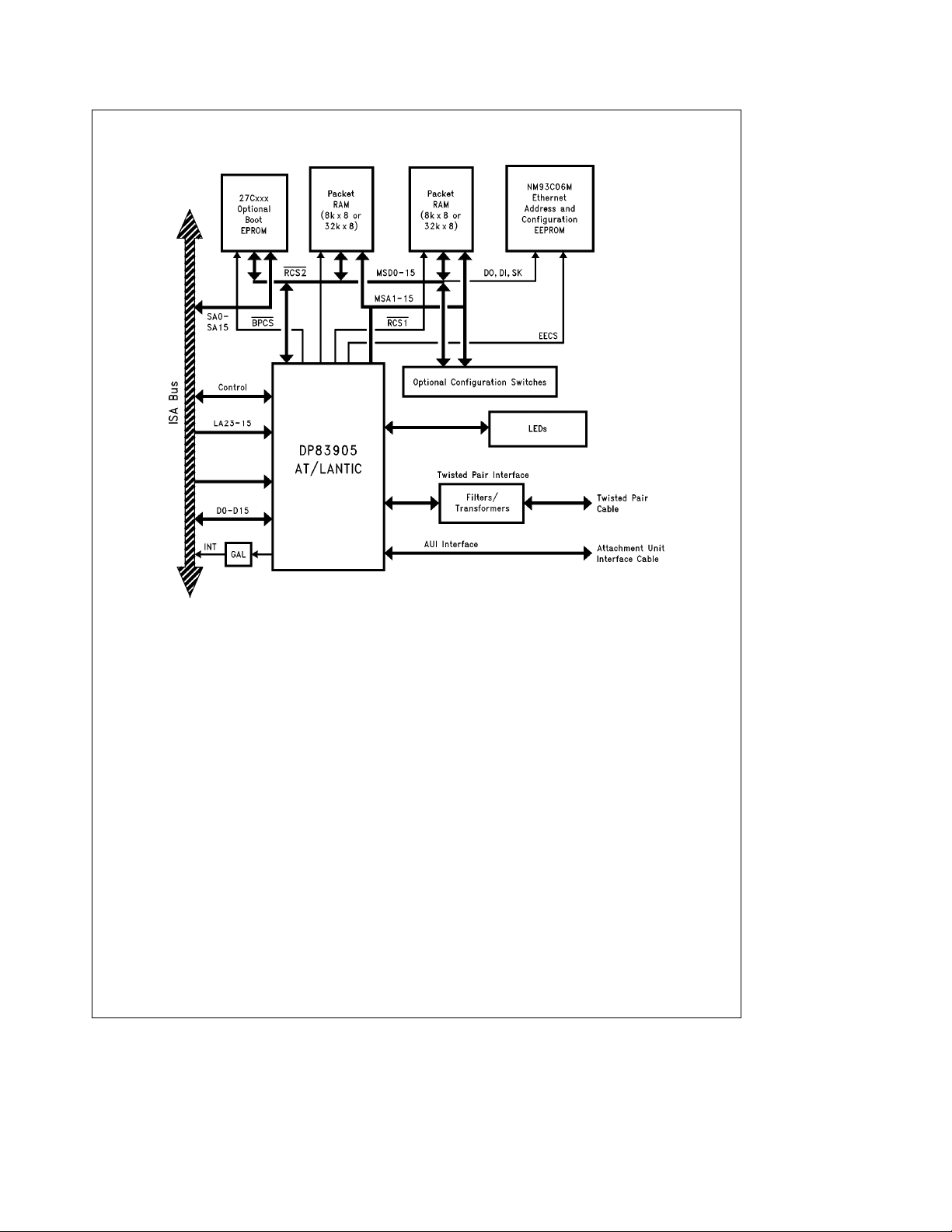

1.1 CONNECTION DIAGRAM

Order Number DP83905AVQB

See NS Package Number VUL160A

3

TL/F/11498– 2

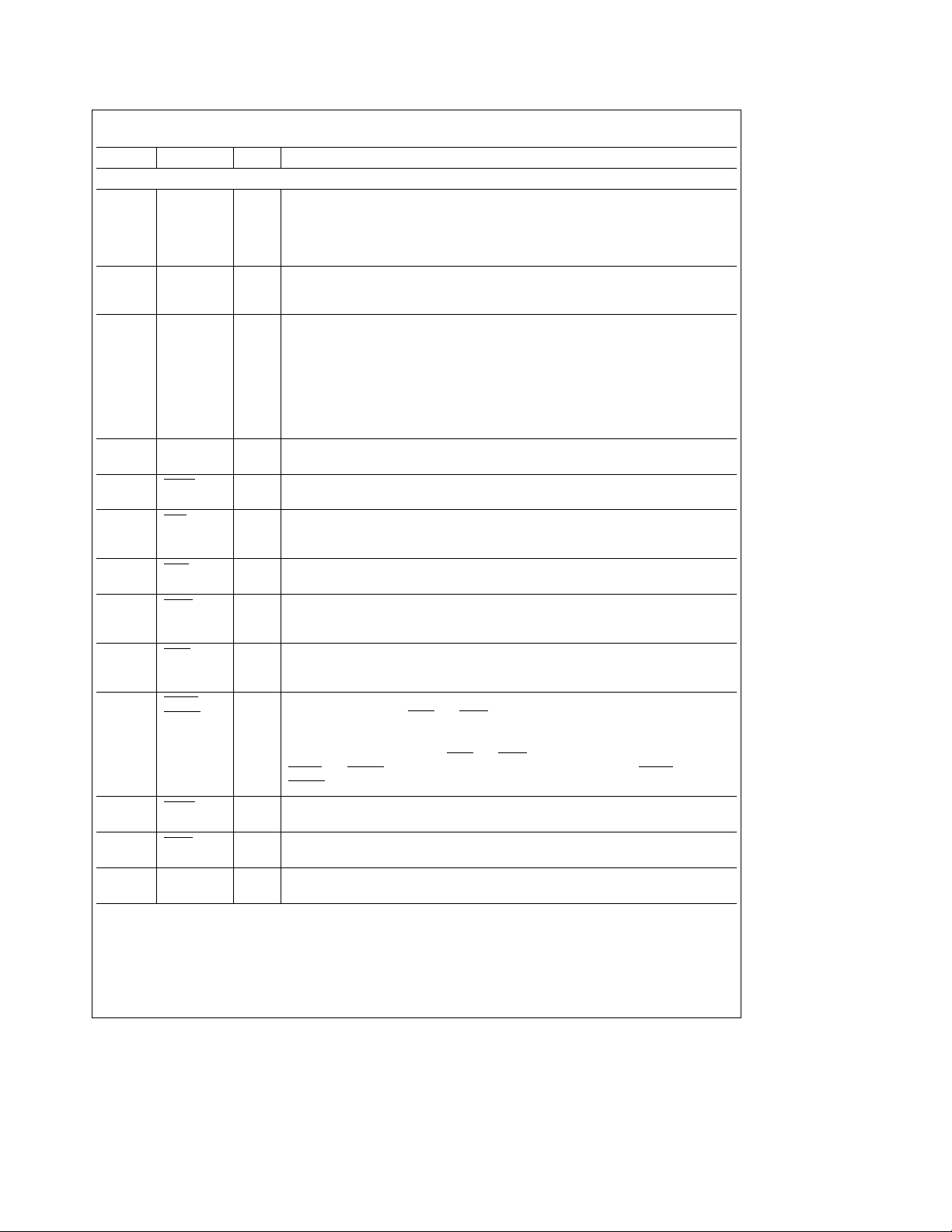

2.0 Pin Description

Pin No. Pin Name Type* Description

ISA BUS INTERFACE PINS

94–97 SA0–SA1 9 I LATCHED ADDRESS BUS: Low-order 20 bits of the system’s 24 bit address bus.

99–106 TTL

108–115

76–82 LA17–LA23 I UNLATCHED ADDRESS BUS: High order 7 bits of the 24-bit system address bus.

127, 128, SD0–SD15 I/O SYSTEM DATA BUS: 16-bit system data bus. Used to transfer data between the

130, 131, 3SH

133, 134,

136, 137,

73, 72,

70, 69,

67, 66,

64, 63

88 BALE I BUS ADDRESS LATCH ENABLE: This signal indicates when the system address

83 SBHE I SYSTEM BUS HIGH ENABLE: This signal indicates that the system expects a

86 M16 O 16-BIT MEMORY TRANSFER: In 16-bit shared memory mode this signal indicates

84 IO16 O 16-BIT I/O TRANSFER: In I/O mode this signal indicates that the AT/LANTIC

74 MWR I MEMORY WRITE STROBE: Strobe from system to write to AT/LANTIC Controller’s

75 MRD I MEMORY READ STROBE: Strobe from system to read from AT/LANTIC Controller’s

119, SMRD &ILOW MEMORY STROBES: In Memory mode these signals strobe memory transfers

120 SMWR

118 IOWR I I/O WRITE STROBE: Strobe from system to write to the AT/LANTIC Controller’s I/O

117 IORD I I/O READ STROBE: Strobe from system to read from the AT/LANTIC Controller’s

126 RESET I RESET: This signal is output by the system to reset all devices on the bus.

*Driver Types are: IeInput, OeOutput, I/OeBi-directional Output, OCHeOpen Collector, 3SHeTRI-STATE Output, TTLeTTL Compatible, AUI

Attachment Unit Interface, TPIeTwisted Pair Interface, LEDeLED Drive, MOSeCMOS Level Compatible, XTALeCrystal.

These lines are enabled onto the bus, by the system, when BALE is high and are

Iatched when BALE returns Iow. These bits are used to decode accesses to the

AT/LANTIC Controller’s I/O map and to the boot PROM. In addition they are used to

decode accesses to the AT/LANTIC Controller’s memory in shared memory mode.

These Iines are valid on the falling edge of BALE. These bits are used to decode

TTL

accesses to the AT/LANTIC Controller’s memory in shared memory mode.

system and the AT/LANTIC Controller.

lines are valid.

TTL

transfer on the upper byte lane.

TTL

that the AT/LANTIC Controller has decoded an address within the 128 kbyte space

OCH

that it occupies part of.

Controller is responding to a 16-bit I/O access by driving 16-bits of data on the bus.

OCH

memory map.

TTL

to operate correctly

memory map.

TTL

to operate correctly

in the same manner as MRD

TTL

This pin should be connected to allow the CHRDY fix in 16-bit I/O mode

. (See Section 6.0)

This pin should be connected to allow the CHRDY fix in 16-bit I/O mode

. (See Section 6.0)

and MWR except that these signals only occur if the

access is to the lowest 1 Megabyte. This partial address decode means that these

signals can be used in an 8-bit slot to properly decode an access to this area.

AT/LANTIC Controller will use MRD

and SMWR in Memory mode when DWID is low (8-bit mode).

SMRD

SMWR

are also used to access the BOOT PROM.

map.

TTL

I/O map.

TTL

and MWR in 16-bit Memory mode and will use

TTL

The

SMRD and

e

4

2.0 Pin Description (Continued)

Pin No. Pin Name Type* Description

ISA BUS INTERFACE PINS (Continued)

123 CHRDY O CHANNEL READY: This signal is used to insert wait states into system accesses.

122 AEN I DMA ACTIVE: This signal indicates that the system’s DMA controller has control

89–92 INT0–3 O INTERRUPT REQUEST: The operation of these 4 outputs is determined by the

61 DWID I DATA WIDTH: This input specifies whether the AT/LANTIC Controller is

93 lSACLK I ISA CLOCK: Clock from ISA bus. This signal is only required if CHRDY timing has

NETWORK INTERFACE PINS

156–153 TXOda, TXOb,OTWISTED PAIR TRANSMIT OUTPUTS: These high drive CMOS level outputs

a

, TXOd

TXO

150, 151 RXIa, RXI

141, TX

142 TX

145, RX

146 RX

147, CD

148 CD

b

b

a

b

a

b

a

5 TXLED O TRANSMIT: An open-drain active Iow output. It is asserted for approximately

4 RXLED O RECEIVE: An open-drain active low output. It is asserted for approximately 50 ms

3 COLED O COLLISION: An open-drain active Iow output. It is asserted for approximately 50

1 GDLNK O GOOD LINK: An open-drain active low output. This pin operates as an output to

2 POLED O POLARITY: An open-drain active low output. This signal is normally inactive.

*Driver Types are: IeInput, OeOutput, I/OeBi-directional Output, OCHeOpen Collector, 3SHeTRI-STATE Output, TTLeTTL Compatible, AUI

Attachment Unit Interface, TPIeTwisted Pair Interface, LEDeLED Drive, MOSeCMOS Level Compatible, XTALeCrystal.

OCH

of the bus.

TTL

Configuration registers. They can either be used to directly drive the interrupt lines

3SH

or used as a 3-bit code with a strobe to generate up to 8 interrupts.

interfacing to an 8- or 16-bit ISA bus. When high it is in 16-bit mode. It has an

MOS

internal pull-down resistor.

to be altered, by changing the CHRDY bit of Configuration Register B.

TTL

b

are resistively combined external to the chip to produce a differential output signal

TPI

with equalization to compensate for Intersymbol Interference (lSI) on the twisted

pair medium.

I TWISTED PAIR RECEIVE INPUTS: These inputs feed a differential amplifier

which passes valid data to the ENDEC module.

TPI

O AUI TRANSMIT OUTPUT: Differential driver which sends the encoded data to the

transceiver. The outputs are source followers which require 270X pull-down

AUI

resistors.

I AUI RECEIVE INPUT: Differential receive input pair from the transceiver.

AUI

I AUI COLLISION INPUT: Differential collision pair input from the transceiver.

AUI

50 ms whenever the AT/LANTIC Controller transmits data in either AUI or TPI

LED

modes.

whenever receive data is detected in either AUI or TPI mode.

LED

ms whenever the AT/LANTIC Controller detects a collision in either AUI or TPI

LED

modes.

display link integrity status if this function has not been disabled by the GDLNK bit

LED

in Configuration Register B.

This output is off if the AT/LANTIC Controller is in AUI mode or if link testing is

enabled and the link integrity is bad (i.e. the twisted pair link has been broken).

This output is on if the AT/LANTIC Controller is in Twisted Pair Interface (TPI)

mode, link integrity checking is enabled and the link integrity is good (i.e. the

twisted pair link has not been broken) or if the link testing is disabled.

When the TPI module detects seven consecutive link pulses or three consecutive

LED

received packets with reversed polarity POLED

is asserted.

e

5

2.0 Pin Description (Continued)

Pin No. Pin Name Type* Description

NETWORK INTERFACE PINS (Continued)

7 X1 (OSCIN) I CRYSTAL OR EXTERNAL OSCILLATOR INPUT

8 X2 (OSCOUT) O CRYSTAL FEEDBACK OUTPUT: Used in crystal connections only. Should be left

10 THIN O THIN CABLE: This output is high if AT/LANTIC Controller is configured for thin

EXTERNAL MEMORY SUPPORT

58–50 MSD0–7, I/O, I, O MEMORY SUPPORT DATA BUSÐCONFIGURATION REGISTER A INPUT

CA0–7, MOS

DO, DI, SK

48–45 MSD8–15 or I/O, I MEMORY SUPPORT DATA BUSÐCONFIGURATION REGISTER B INPUT:

43-40 CB0– 7 MOS MSD8– 15: When RESET is inactive these pins can be used to access external

31–25, MSA1 –8 or O, I MEMORY SUPPORT ADDRESS BUSÐCONFIGURATION REGISTER C INPUT:

22 CC0 –7 MOS MSA1– 8: When RESET is inactive these pins drive the memory support address

21–15 MSA9–15 O MEMORY SUPPORT ADDRESS BUS: MSA9– 15: When RESET is inactive these

33 MSRD O MEMORY SUPPORT BUS READ: Strobes data from the external RAM into the AT/

32 MSWR O MEMORY SUPPORT BUS WRITE: Strobes data from the AT/LANTIC Controller

37 BPCS O BOOT PROM CHIP SELECT: Selects the boot PROM on the memory support data

*Driver Types are: IeInput, OeOutput, I/OeBi-directional Output, OCHeOpen Collector, 3SHeTRI-STATE Output, TTLeTTL Compatible, AUI

Attachment Unit Interface, TPIeTwisted Pair Interface, LEDeLED Drive, MOSeCMOS Level Compatible, XTALeCrystal.

XTAL

XTAL

DCDC

MOS

MOS

MOS

MOS

completely unconnected when using an oscillator module.

cable. It can be used to enable the DC-DC converter required by the thin ethernet

configuration.

EEPROM SIGNALS:

MSD0–7: When RESET is inactive these pins can be used to access external

memory and boot PROM.

CA0–7: When RESET is active Configuration Register A is loaded with the data

value on these pins. If the user puts an external pull-up on any of these pins then the

corresponding register bit is set to a 1. If the pin is left unconnected then the register

bit is 0.

DO, DI, SK: When RESET goes from an active to an inactive level AT/LANTIC

Controller will read the contents of an EEPROM, using these signals, and load the

contents into internal registers. These internal registers will then be mapped into the

space taken up by the PROM in the NE2000 and Ethercard PLUS16. After the

EEPROM read operation has completed these pins will revert to MSD0 –2 (D0

e

MSD0, DIeMSD1, SKeMSD2).

memory.

CB0–7: When RESET is active Configuration Register B is loaded with the data

value on these pins. If the user puts an external pull-up on any of these pins then the

corresponding register bit is set to a 1. If the pin is left unconnected then the register

bit is 0.

bus.

CC0–7: When RESET is active Configuration Register C is loaded with the data

value on these pins. If the user puts an external pull-up on any of these pins then the

corresponding register bit is set to a 1. If the pin is left unconnected then the register

bit is 0.

pins drive the memory support address bus. When the memory is only 8 bits wide A0

will appear on A13, in compatible mode, and on A15, in non-compatible mode.

LANTIC Controller via the memory support data bus.

into the external RAM via the memory support data bus.

bus.

e

6

2.0 Pin Description (Continued)

Pin No. Pin Name Type* Description

EXTERNAL MEMORY SUPPORT (Continued)

36 RCS1 O RAM CHIP SELECT 1: Drives the chip select of the external RAM on the lower half

34 RCS2 O RAM CHIP SELECT 2: Drives the chip select of the external RAM on the upper half

38 EECS O EEPROM CHIP SELECT: Strobes data from the EEPROM onto the memory support

39 EECONFIG I CONFIGURE FROM EEPROM: When this pin is tied high the AT/LANTIC Controller

12 BSCLK I INTERNAL BUS CLOCK: This controls the speed of the NIC core if it is not running

LOW POWER SUPPORT

62 LOWPWR I LOW POWER: Instructs AT/LANTIC Controller to enter its low power mode, as

TEST SUPPORT

11 TEST I TEST: This input is only used for test mode. It should be left unconnected as it has

POWER SUPPLY PINS

160 PLLV

CC

159 PLLGND PLL NEGATIVE (GROUND) SUPPLY PINS

157, 152, PV

144, 143,

CC

139

158, 149, PGND PHYSICAL LAYER NEGATIVE (GROUND) SUPPLY PINS: These pins are the

140, 138

9OV

CC

6 OGND OSCILLATOR NEGATIVE (GROUND) SUPPLY PINS: This pin is the ground to the

59, 49, V

24, 13

CC

60, 54, 44, GND NEGATIVE (GROUND) SUPPLY PINS: These are the supply pins for the

35, 23, 14

132, 121, IFV

107, 87, 68

CC

135, 129, lFGND INTERFACE NEGATIVE (GROUND) SUPPLY PINS: These are the supply pins for

125, 124,

116, 98,

85, 71, 65

*Driver Types are: IeInput, OeOutput, I/OeBi-directional Output, OCHeOpen Collector, 3SHeTRI-STATE Output, TTLeTTL Compatible, AUI

Attachment Unit Interface, TPIeTwisted Pair Interface, LEDeLED Drive, MOSeCMOS Level Compatible, XTALeCrystal.

of the memory support data bus.

MOS

of the memory support data bus.

MOS

data bus.

MOS

loads the configuration from an EEPROM.

TTL

off of an internal clock (see Configuration Register C). This pin should be tied to

TTL

ground if it is unused.

detailed in Section 4.5. Should be tied to ground for normal operation.

TTL

an internal pull-down resistor which will enable correct operation.

MOS

PLL 5V SUPPLY PINS: This pin supplies 5V to the AT/LANTIC’s analog PLL inside

the ENDEC block. To maximize data recovery it is recommended that analog layout

and decoupling rules be applied between this pin and PLLGND.

PHYSICAL MEDIA 5V SUPPLY PINS: These pins supply 5V to the AT/LANTIC’s

analog physical media interface circuitry.

ground to the AT/LANTIC’s analog physical media interface circuitry.

OSClLLATOR 5V SUPPLY PINS: This pin supplies 5V to the AT/LANTIC’s oscillator

and LED circuitry.

AT/LANTIC’s oscillator and LED circuitry.

POSITIVE 5V SUPPLY PINS: These pins supply power to the AT/LANTIC

Controller’s logic.

AT/LANTIC Controller’s logic. It is suggested that decoupling capacitors be

connected between the V

for the GND pins with the lowest possible impedance.

and GND pins. It is essential to provide a path to ground

CC

INTERFACE POSITIVE 5V SUPPLY PINS: These pins supply power to the

AT/LANTIC Controller’s ISA interface.

the AT/LANTIC Controller’s ISA interface. It is suggested that decoupling capacitors

be connected between the IFV

ground for the IFGND pins with the lowest possible impedance.

and IFGND pins. It is essential to provide a path to

CC

e

7

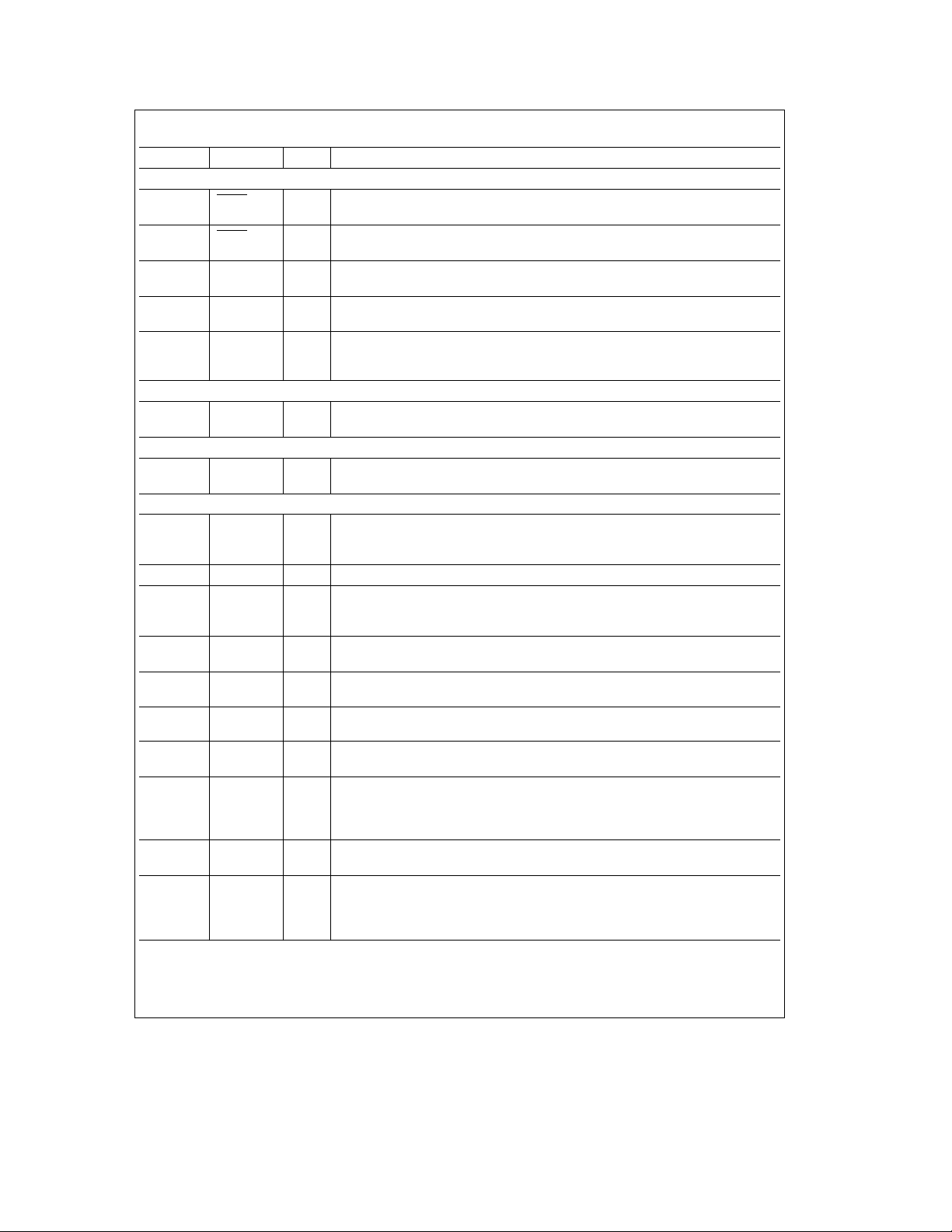

3.0 Simplified Application Diagram

4.0 Functional Description

The AT/LANTIC Controller is a highly integrated and configurable Ethernet controller making it suitable for most Ethernet applications. The AT/LANTIC Controller integrates the

functions of the following blocks:

1. DP8390 Ethernet Controller Core and Media Access

Control logic.

2. ISA Bus Interface containing all logic required to connect

the DP8390 core to a packet buffer RAM and the ISA

bus.

3. Media Interface which includes an Encoder/Decoder

block with an AUI (Attachment Unit Interface) and a

10BASE-T Twisted Pair Interface.

TL/F/11498– 3

4.1 BUS INTERFACE BLOCK

The AT/LANTIC Controller’s Bus interface block provides

the circuitry to interface the Ethernet controller logic, and

the external packet buffer RAM to an ISA (Industry Standard

Architecture) Bus. The bus interface provides several configuration modes which offer various different features depending on the designer’s specific design requirements.

The possible modes are:

1. 16-Bit or 8-Bit Shared Memory Compatible Mode

2. 16-Bit or 8-Bit Shared Memory Enhanced Mode

3. 16-Bit or 8-Bit I/O Port Compatible Mode

4. 16-Bit or 8-Bit I/O Port Enhanced Mode

This section describes the function of each of these modes.

8

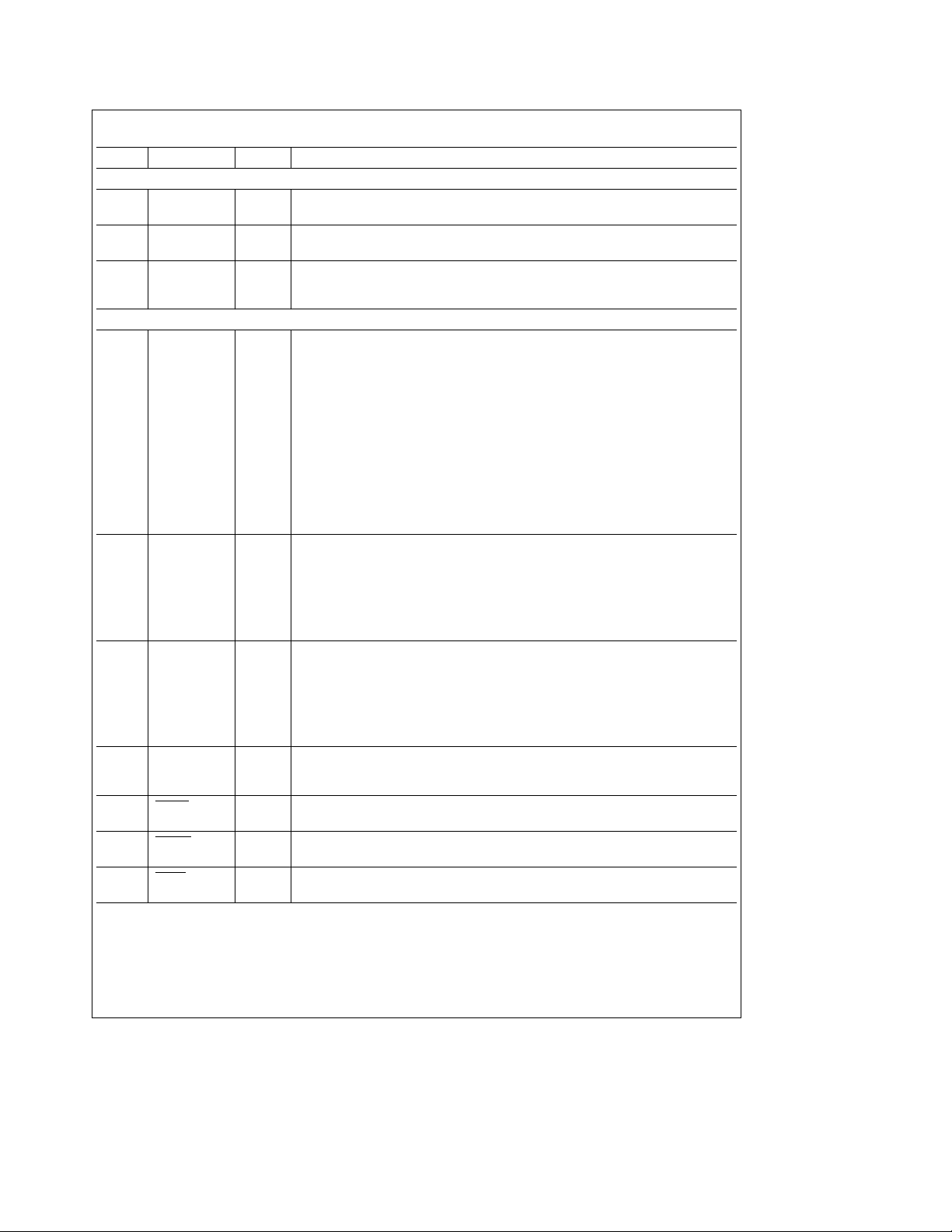

4.0 Functional Description (Continued)

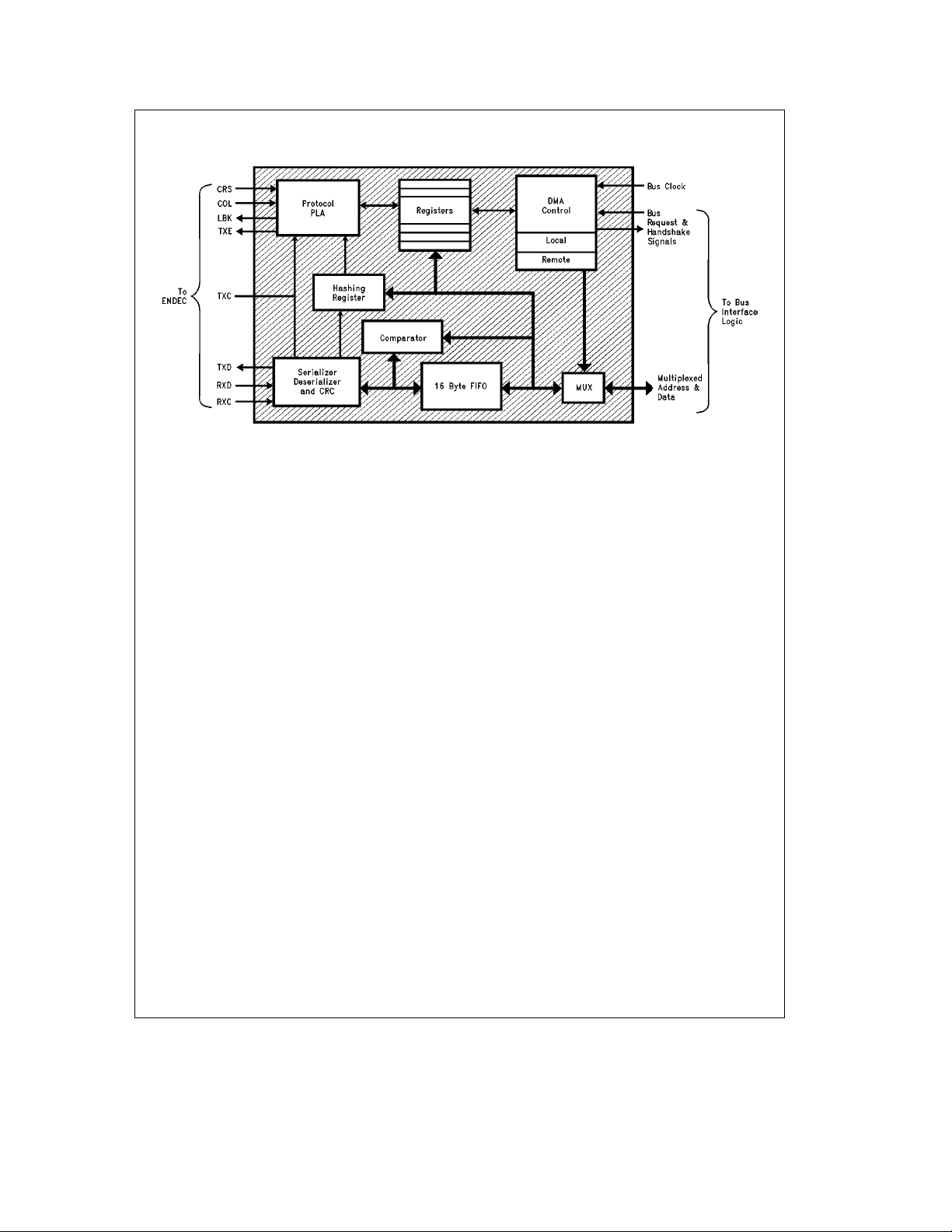

FIGURE 1. Block Diagram of AT/LANTIC Controller

DETERMINING 8- OR 16-BIT WIDE DATA

AT/LANTIC Controller can treat the system data bus and all

internal data busses as 8 or 16 bits wide. 8- or 16-bit mode

is determined by the DWlD pin. For an adapter card this bit

can be used to automatically detect if the card has been

plugged into an 8- or 16-bit slot. If this pin is connected to a

V

on the upper connector it will be high when plugged

DD

into a 16-bit slot, enabling 16-bit mode, and floating when

plugged into an 8-bit slot. When floating the internal pulldown resistor will enable 8-bit mode.

SHARED MEMORY ARCHITECTURE

FIGURE 2. Shared Memory

TL/F/11498– 5

TL/F/11498– 4

In this mode the AT/LANTIC Controller’s internal memory

map, using external RAM devices, is mapped into the host

system’s memory map. Both the AT/LANTIC Controller and

the host system can directly access this memory. The

AT/LANTIC Controller controls the arbitration for this memory area, giving priority to its internal accesses. It also has

an internal FIFO to allow for any latency on internal transfers introduced by system accesses. If a system access occurs while an internal access is current the AT/LANTIC

Controller will insert wait states into the system cycle until

the internal transfer is complete.

In this mode the AT/LANTIC Controller’s internal registers

are accessed within the system’s I/O map. The address

within this I/O map is set by Configuration Register A. The

user programs the address of the shared memory within the

host systems memory map by writing to a register in

AT/LANTIC Controller. The memory is not accessible by

the user until after this register has been programmed.

There are two basic Shared Memory modes, compatible

mode, and non-compatible mode, as described in the following text.

9

4.0 Functional Description (Continued)

Shared Memory Compatible Mode I/O Address

Mapping

The shared memory is at an address decided by the Address Decode Register and the base I/O address of

AT/LANTIC Controller is configured in Configuration Register A. At that address the following structure appears.

Addr D7– 0

00 Control 1

01 AT detect (Read only)

02 Unused

03 Unused

04 Unused

05 Control 2

06 Unused

07 Unused

08 Node addr 0 (Read only)

09 Node addr 1 (Read only)

0A Node addr 2 (Read only)

0B Node addr 3 (Read only)

0C Node addr 4 (Read only)

0D Node addr 5 (Read only)

0E 05h (Read only)

0F Checksum (Read only)

10

to

1F

0000H

NIC

registers

(a)

D15 D0

8kx16

Buffer RAM

specified as the PROM space for compatibility with the Ethercard PLUS16. This is actually an array of 8-bit registers

which are loaded from an external EEPROM after

AT/LANTIC Controller is initialized by a reset pulse. The

user should program the EEPROM to contain these values.

The 8k words of memory can be accessed directly by the

host system in the same manner as any other memory. Typically the programmer would remove data from this buffer

using a ‘‘MOV’’ or ‘‘MOVSW’’ instruction.

8-BIT SHARED MEMORY COMPATIBLE MODE

In this mode the I/O map remains the same. The NIC core

can still operate in 16-bit mode, if bit 6 of Control Register 2

is set high and the full 16 kbytes of RAM are still available.

However, only 8-bit system accesses are allowed. If bit 6 of

Control register 2 is low the NIC core must operate in 8-bit

mode and only 8k of memory is available. The NIC Core

data width is set by the WTS bit in the Data Configuration

Register.

A low cost card, using only one 8 kbyte RAM, can be designed. If the DWlD pin is left unconnected, or tied to GND,

then the AT/LANTIC Controller will always operate in 8-bit

mode, regardless of the slot the board is in.

If DWID is low the address bits of Control Register 2 should

not be written to as they have no effect. In this mode the

address comparator assumes that SA19 is to be compared

to a logic high, with the other address comparisons programmed into Control Register 1.

SHARED MEMORY NON-COMPATIBLE MODE

These modes are similar to the compatible mode. The difference is that they map a full 64 kbytes of RAM into the

PC’s memory address space. The I/O map remains the

same.

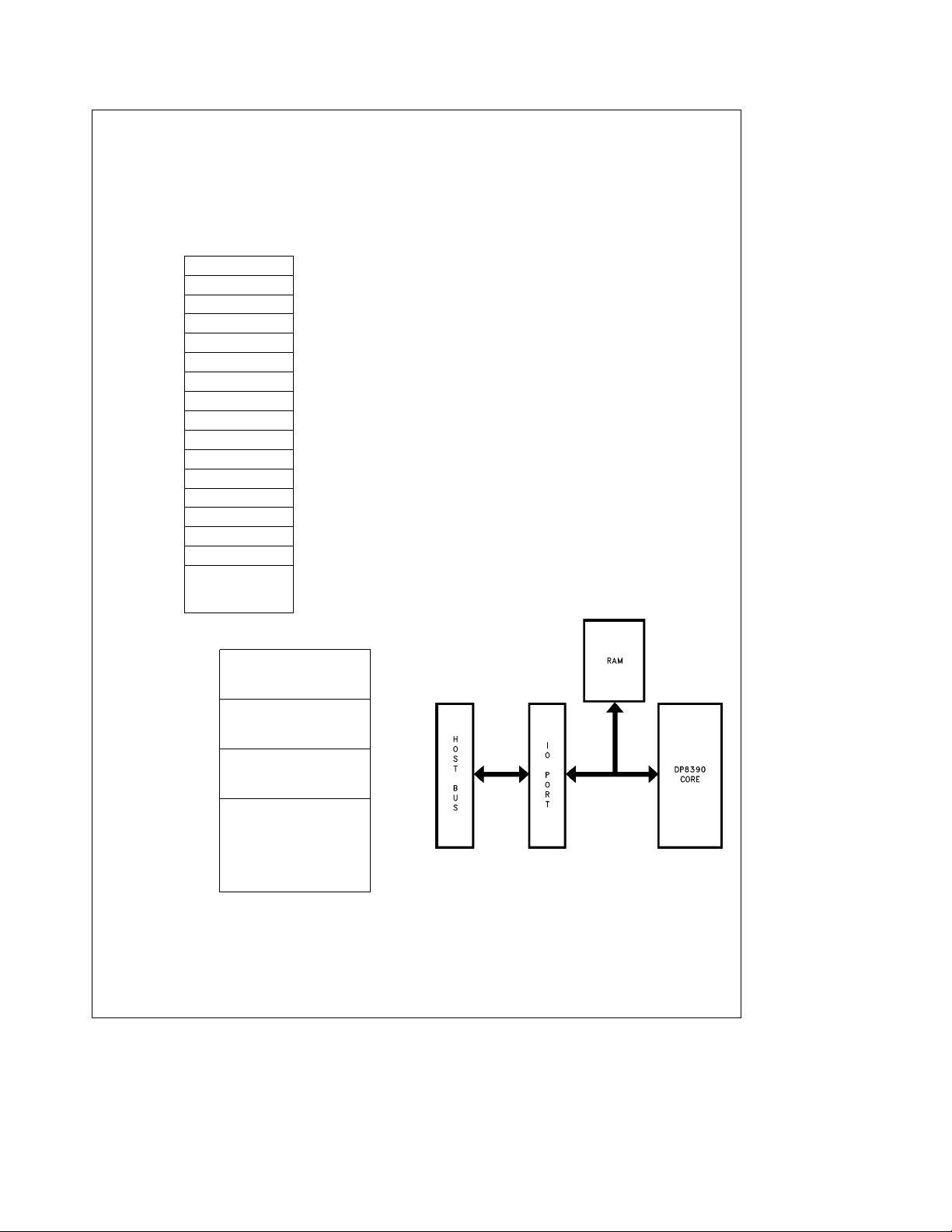

I/O PORT ARCHITECTURE

4000H

8000H

C000H

FFFFH

FIGURE 3. Shared Memory Mode a) Register

Mapping and b) NIC Core Memory Map

The AT Detect Register indicates whether AT/LANTIC Controller is in an 8- or 16-bit slot. The least significant bit of this

register is set high when AT/LANTIC Controller is in 16-bit

mode and low in 8-bit mode. Addresses 08H to 10H are

Aliased

Buffer RAM

Aliased

Buffer RAM

Aliased

Buffer RAM

(b)

FIGURE 4. I/O Port

TL/F/11498– 6

This is the architecture used by Novell’s NE2000. In this

mode the AT/LANTIC Controller’s internal memory map is

accessed byte or word at a time, via a port within the system’s I/O space. AT/LANTIC Controller is programmed by

the user to control the transfers between its internal memory and the I/O port.

In this mode the AT/LANTIC Controller’s internal registers

and the memory access port are accessed within the system’s I/O map. The address within this I/O map is set by

Configuration Register A.

10

4.0 Functional Description (Continued)

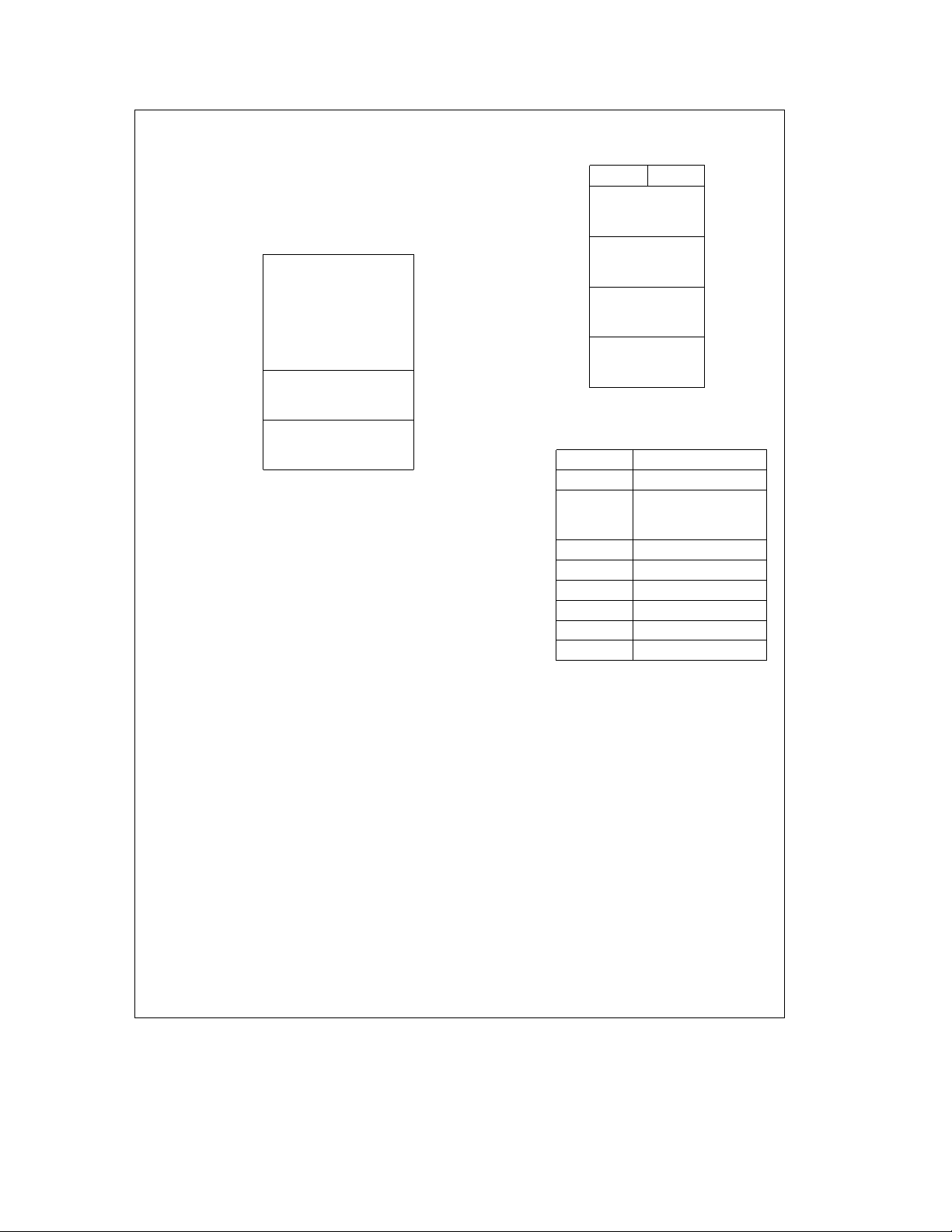

16-BIT I/O PORT COMPATIBLE MODE I/O ADDRESS

MAPPING

This mode is compatible with Novell’s NE2000. The base

I/O address of the AT/LANTIC Controller is configured by

Configuration Register A (either upon power up or by software writing to this register). At that address the following

structure appears.

Basea00H

DP8390

Core

Registers

Basea0FH

Basea10H

a

Base

17H

Basea18H

a

Base

1FH

FIGURE 5. I/O Port Mode Register I/O Map

The registers within this area are 8 bits wide, but the data

transfer port is 16 bits wide. The AT/LANTIC Controller’s

registers can be programmed to control the passing of data

between its internal memory and the data transfer port. By

accessing the data transfer port (using I/O instructions) the

user can transfer data to or from the AT/LANTIC Controller’s internal memory. The AT/LANTIC Controller’s internal

memory map is as shown in

AT/LANTIC Controller actually has a 64k address range but

only does partial decoding on these devices. The PROM

data is mirrored at all decodes up to 4000H and the entire

map is repeated at 8000H. To access either the PROM or

the RAM the user must initiate a Remote DMA transfer between the I/O port and memory.

On a remote read the AT/LANTIC Controller moves data

from its internal memory map to the I/O port and the host

system reads it by using an ‘‘INW’’ or ‘‘INSW’’ instruction

from the I/O address of the data transfer port. If the system

attempts to read the port before AT/LANTIC Controller has

written the next word of data to it AT/LANTIC Controller will

insert wait states into the system cycle, using the CHRDY

Data Transfer Port

Reset Port

Figure 6

.

0000H

001FH

D15 D0

PROM

Aliased PROM

4000H

8kx16

7FFFH

Buffer RAM

8000H

Aliased PROM

C000H

Aliased

FFFFH

Buffer RAM

(a)

D15 D0

1EH 00 57H

1CH 00 57H

##

00 RESERVED

##

0AH 00 E’net Address 5

08H 00 E’net Address 4

06H 00 E’net Address 3

04H 00 E’net Address 2

02H 00 E’net Address 1

00H 00 E’net Address 0

(b)

FIGURE 6. a) NIC Core’s Memory Map

b) 16-Bit Prom Map

11

4.0 Functional Description (Continued)

line. AT/LANTIC Controller will not begin the next memory

read until the previous word of data has been read.

On a remote write the system writes data to the I/O port,

using an ‘‘OUTW’’ or ‘‘OUTSW’’ instruction, and

AT/LANTIC Controller moves it to its buffer memory. If the

system attempts to write to the port before AT/LANTIC

Controller has moved the data to memory AT/LANTIC Controller will insert wait states into the system cycle, using the

CHRDY line. AT/LANTIC Controller will not begin the next

memory write until a new word has been written to the I/O

port.

Addresses 00H to 1FH are specified as the PROM space

for compatibility with the NE2000. This is actually an array of

8-bit registers which are loaded from an external EEPROM

after AT/LANTIC Controller is initialized by an ISA RESET.

They should contain the same data as the PROM did in the

NE2000 and in the same format. As can be seen the PROM

registers are only 8-bits wide. To transfer the data out the

user must initiate a 16-bit DMA read transfer and discard the

most significant byte of data on each transfer.

At address 00H of the PROM is a six byte Ethernet address

for this node. The upper two addresses of the PROM store

contain bytes which identify whether the AT/LANTIC Controller is in 8- or 16-bit mode. For 16-bit mode these bytes

both contain the value 57H, for 8-bit mode they both contain

42H.

8-BIT I/O PORT COMPATIBLE MODE

This mode is compatible with the 8-bit mode offered by

Novell’s NE2000. The NE2000 automatically detects whether it is in an 8- or 16-bit slot and configures itself appropriately. As explained in the previous paragraphs, the user can

determine whether the board is in 8- or 16-bit mode by reading the PROM. In 8-bit mode only 8 kbytes of RAM are

addressable, as in the 8-bit mode of the NE2000. The I/O

map is the same as the 16-bit mode, the memory map is

shown in

code, so is mirrored at all addresses up to 4000H. The

PROM still occupies 32 bytes of address space, although it

only has 16 bytes of data, as the data at all odd address

locations is merely a mirror of the data at the previous even

address location. The RAM is mirrored at 6000H and the

entire map mirrored at 8000H.

A low cost card, using only one 8 kbyte RAM, can be designed. If the DWlD pin is left unconnected, or tied to GND,

then the AT/LANTIC Controller will always operate in 8-bit

mode, regardless of the slot the board is in.

I/O PORT NON-COMPATIBLE MODE

This mode is similar to Novell’s NE2000, but this mode allows the user to use the full 64 kbytes of address space

except for an initial page for the PROM. The memory map

for this board is shown in

same for both 8- and 16-bit modes. Although the PROM

store occupies 256 bytes, it is only 16 bytes long. The entire

map is mirrored at 8000H.

A low cost card, using only one 8 kbyte RAM, can be designed. If the DWID pin is left unconnected, or tied to GND,

then the AT/LANTIC Controller will always operate in 8-bit

mode, regardless of the slot the board is in.

Figure 7

. Again the PROM has only a partial de-

Figure 8

. The memory map is the

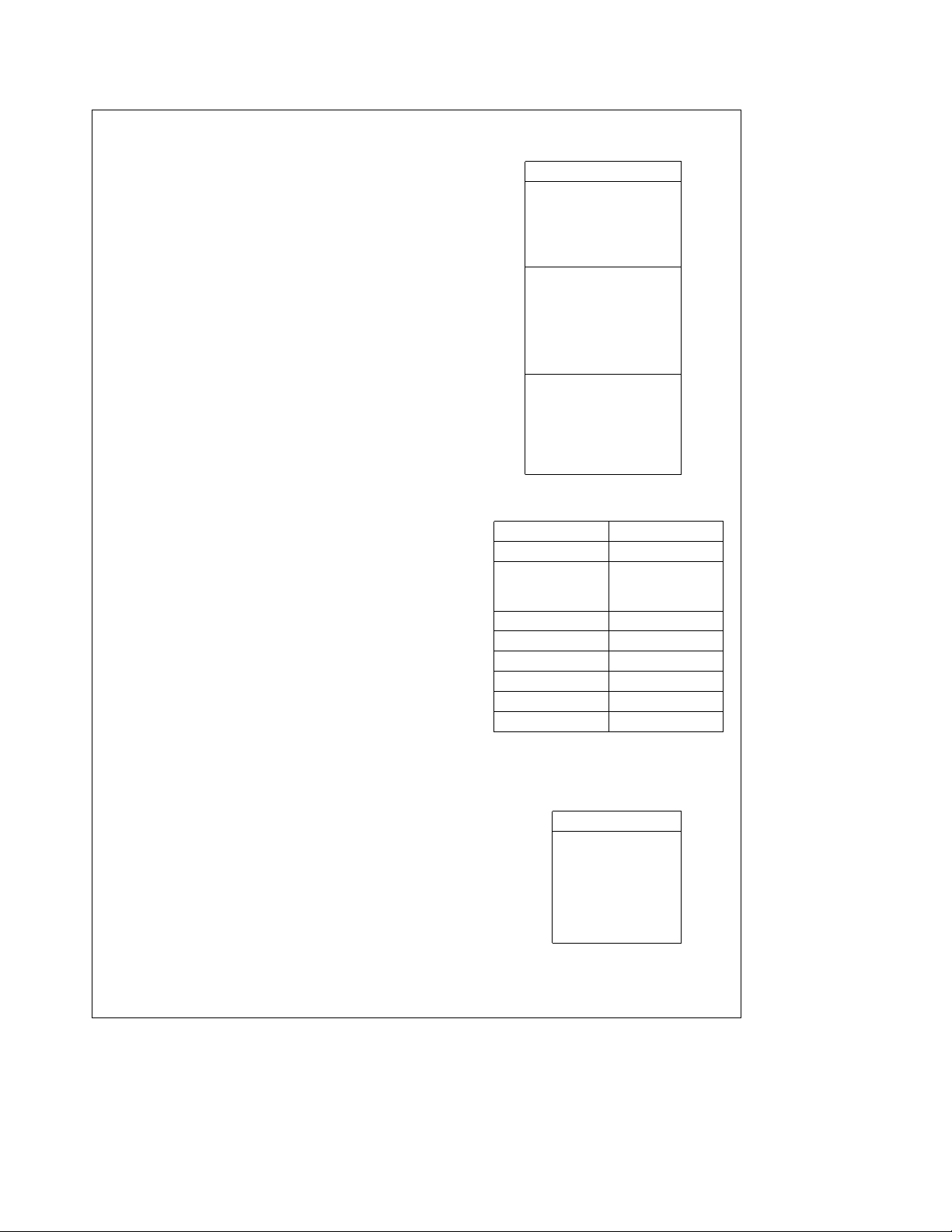

0000h

0020h

4000h

6000h

8000h

1EH 42H 42H

1CH 42H 42H

PROM

Aliased PROM

8k x 8 BUFFER RAM

RESERVED

(a)

D15 D0

##

RESERVED RESERVED

##

0AH E’net Address 5 E’net Address 5

08H E’net Address 4 E’net Address 4

06H E’net Address 3 E’net Address 3

04H E’net Address 2 E’net Address 2

02H E’net Address 1 E’net Address 1

00H E’net Address 0 E’net Address 0

(b)

FIGURE 7. a) 8-Bit NIC Core’s Memory Map

0000H

00FFH

0100H

FFFFH

b) 8-Bit PROM Map

PROM

BUFFER RAM

FIGURE 8. I/O Port Enhanced Mode

DP8390 Core Memory Map

12

4.0 Functional Description (Continued)

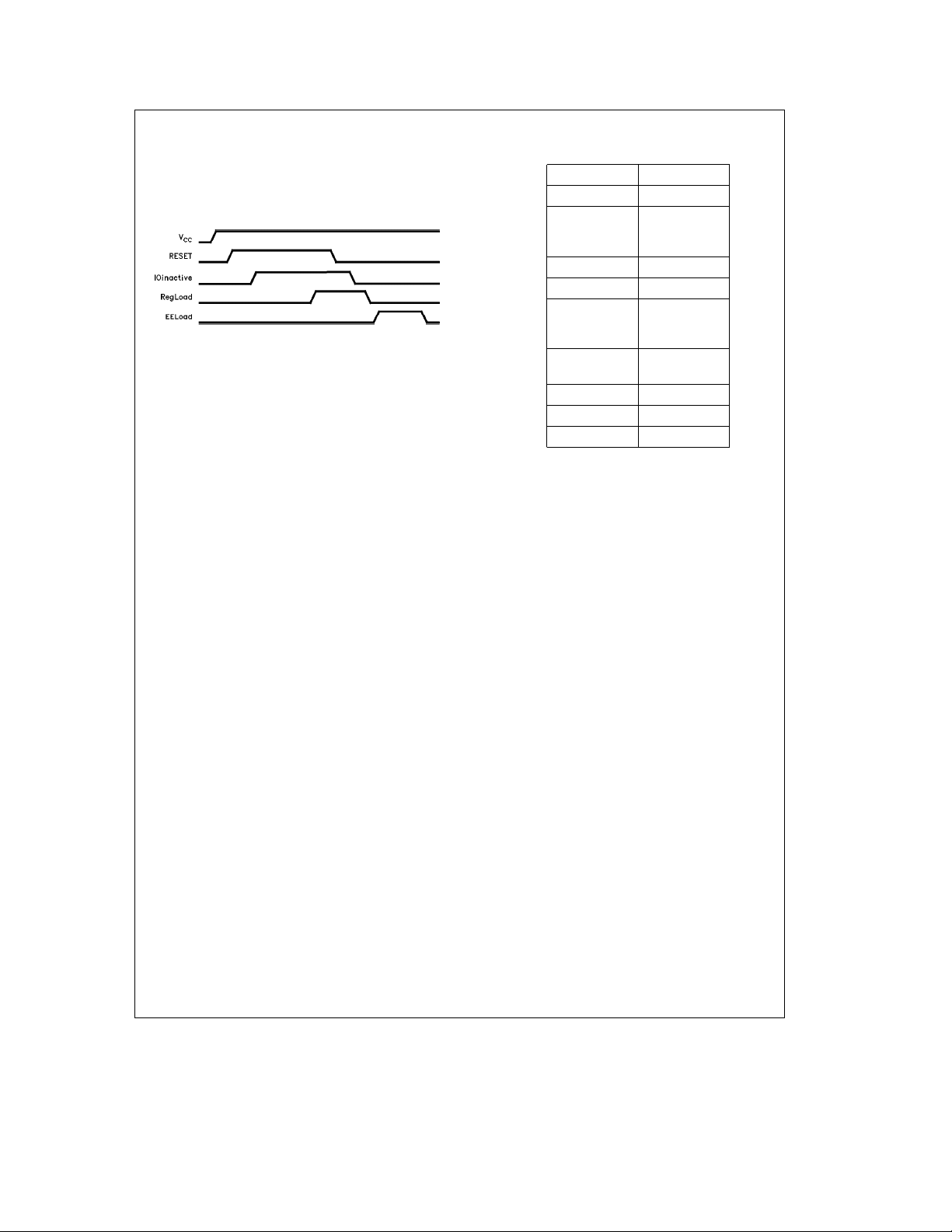

4.2 POWER ON RESET OPERATION

The AT/LANTIC Controller configures itself after a Reset

signal is applied. To be recognized as a valid Power-On-Reset the Reset signal must be active for at least 415 ms.

Figure 9

shows how the RESET circuitry operates.

FIGURE 9. RESET Operation

The ISA standard determines that within 500 ns of RESET

going active all devices should enter the appropriate reset

condition. The AT/LANTIC Controller will generate the internal signal IOinactive after RESET has been active for

415 ns, which will disable all outputs and cause RESET to

be the only input monitored. The AT/LANTIC Controller will

not respond to a RESET pulse of shorter duration than this.

An internal timer continues to monitor the amount of time

RESET is active. After 415 ms it is considered a valid PowerOn-Reset and an internal signal called RegLoad is generated.

When a Power-On-Reset occurs the AT/LANTIC Controller

latches in the values on the configuration pins and uses

these to configure the internal registers and options. Internally these pins contain pull-down resistors, which are enabled when IOinactive goes active. If any pins are unconnected they default to a logic zero. The internal pull-down

resistor has a high resistance to allow the external pull-up

resistors to be of a high value. This limits the current taken

by the memory support bus. The suggested external resistor

value is 10 kX. The configuration registers are loaded from

the memory support bus when RESET goes inactive if RegLoad is active. The internal pull-down resistors are enabled

onto the bus until RegLoad has gone inactive.

A Power-On-Reset also causes the AT/LANTIC Controller

to load the internal PROM store from the EEPROM, which

can take up to 320 ms. This occurs after RegLoad has gone

inactive. The AT/LANTIC Controller will be inaccessible during this time. If EECONFIG is held high the configuration

data loaded on the falling edge of RESET will be overwritten

with data read from the serial EEPROM. Regardless of the

level on EECONFIG the PROM store will always be loaded

with data from the serial EEPROM during the time specified

as EELoad.

4.3 EEPROM OPERATION

The AT/LANTIC Controller uses an NM93C06, or

EEPROM with compatible timings. The NM93C06 is a 256bit device, arranged as 16 words each 16 bits wide. The

programmed contents of the EEPROM is shown in

10

.

Mapping EEPROM Into PROM Space

Data is read from the EEPROM at boot time and stored in

registers within the AT/LANTIC Controller. While this operation takes place the AT/LANTIC Controller can not be ac-

TL/F/11498– 7

Figure

D15 D0

0FH 73H Config. C

0EH Config B Config. A

##

##

##

08H 42H 42H

07H 57H 57H

##

##

##

03H Reserved Reserved

(Checksum) (Board Type)

02H E’net Address 5 E’net Address 4

01H E’net Address 3 E’net Address 2

00H E’net Address 1 E’net Address 0

Note 1: The contents of locations 03H and 04H differ between I/O Mode

and Shared Memory Mode. The Shared Memory Mode values are shown in

parentheses. For compatibility with both modes default to the shared memory mode values.

Note 2: Programming 73H into the upper address is not absolutely required

but is strongly recommended for future compatibility of manufacturing process.

FIGURE 10. EEPROM Programming Map

cessed by the system. These registers are mapped into the

space traditionally occupied by the PROM in the NE2000 or

the EtherCard PLUS16. The size and format of this data

read is determined by the mode of operation.

SHARED MEMORY MODE

In this mode, program the EEPROM to contain the node’s

Ethernet address in the first six bytes, a byte identifying the

type of board AT/LANTIC Controller is emulating in byte 7

and a checksum byte in byte 8. The two’s complement sum

of these eight bytes should equal FFH.

In this Mode the AT/LANTIC Controller reads the first 4

words from the EEPROM and maps them into the I/O map

at the appropriate address.

I/O PORT MODE

In this mode, program the EEPROM to contain the node’s

Ethernet address in the first six bytes. The user should then

program 5757H and 4242H into the subsequent bytes. The

AT/LANTIC Controller will decide which of these values

should be loaded into the PROM store depending on the

DWlD pin. (The data width is programmed in this mode by

setting the WTS bit in the Data Configuration Register and

setting the DWlD pin for the proper mode.) If some other

numerical values are preferred to indicate the mode then

they can be programmed at this location in the EEPROM

and AT/LANTIC Controller will put them at the correct address.

In this mode the AT/LANTIC Controller reads the first 7

words from the EEPROM and maps them into the memory

map at the appropriate address. If in 16-bit mode it also

13

4.0 Functional Description (Continued)

reads the next word in the EEPROM and appends this. If in

8-bit mode it skips a word, then reads and appends the next

word.

Storing and Loading Configuration from EEPROM

If the EECONFIG pin is high during boot up the AT/LANTIC

Controller’s configuration is read from the EEPROM, before

the PROM data is read. The configuration data is stored

within the upper two words of the EEPROM’s address

space. Configuration Registers A and B are located in the

lower of these words, Register C in the lower byte of the

upper word, as shown in

To write this configuration into the EEPROM the user must

follow the routine specified in the pseudo code below. This

operation will work regardless of the level on EECONFIG.

The EELOAD bit of Configuration Register B being set starts

the EEPROM write process. Care should be taken not to

accidently set the GDLINK bit and therefore disable link integrity checking. The next 3 writes to this register load the

values that will be stored in the configuration register (note

that the last 2 of these writes do not have to follow the

normal practice of preceding a write to this register with a

read to this address). The AT/LANTIC Controller will then

commence the EEPROM write. The write has been completed when the EELOAD bit goes to zero. This loading procedure should be followed exactly and interrupts should be

disabled until it has completed, to prevent any accidental

accesses to the AT/LANTIC Controller.

EEPROMÐLOAD()

À

DISABLEÐINTERRUPTS();

e

value

READ(CONFIGÐB);

e

value

value AND 1 GDLINK;

e

value

value OR EELOAD;

WRITE(CONFIGÐB, value);

READ(CONFIGÐB);

WRITE(CONFlGÐB, configÐforÐA);

WRITE(CONFIGÐB, configÐforÐB);

WRITE(CONFIGÐB, configÐforÐC);

while (value AND EELOAD)

À

valueeREAD(CONFIGÐB);

WAIT();

Ó

ENABLEÐINTERRUPTS();

Ó

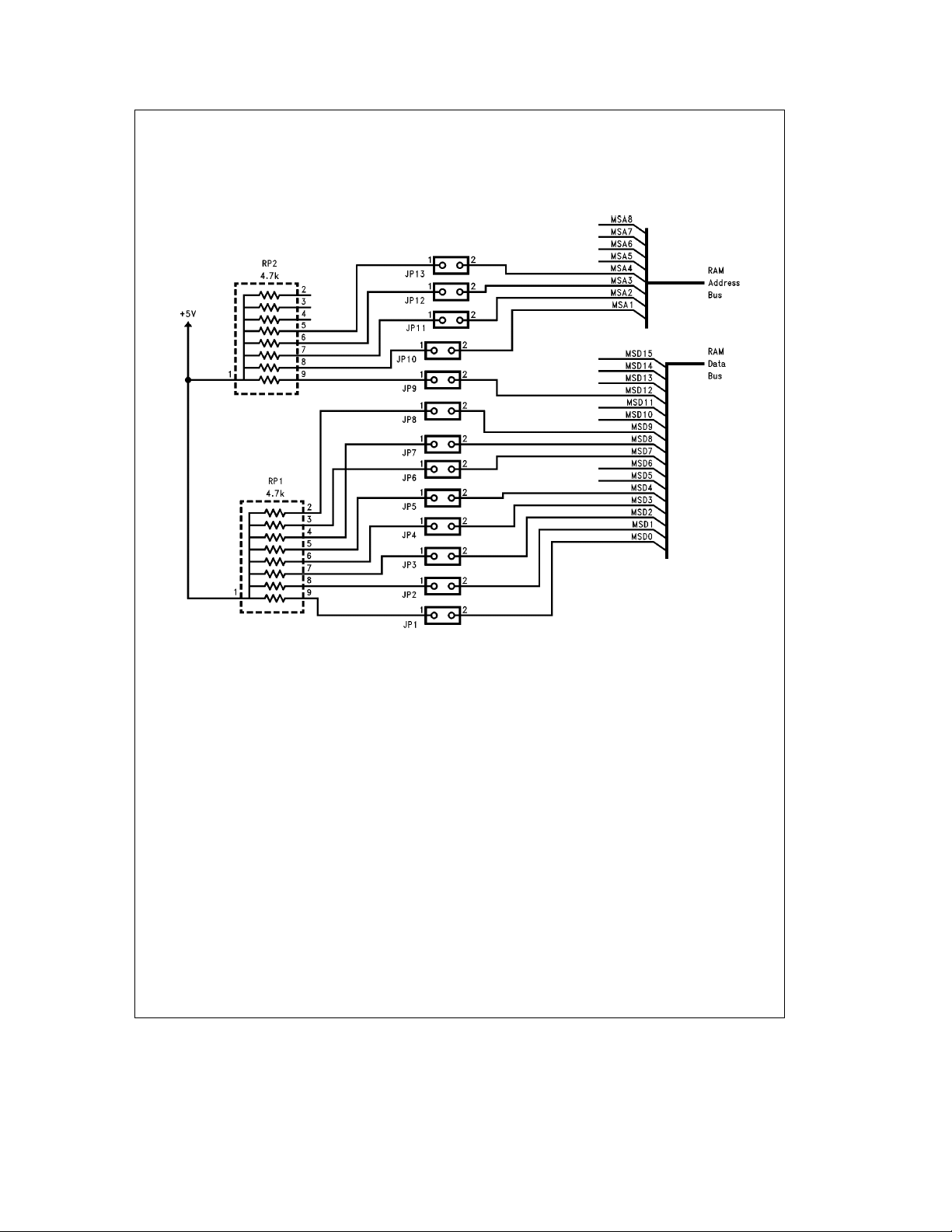

4.4 JUMPERED AND JUMPERLESS OPERATION

SUPPORT

The AT/LANTIC Controller supports several options that

enable the implementation of either a ‘‘jumpered’’ or ‘‘jumperless’’ power on configuration when installed into a standard PC compatible’s ISA bus. A wide range of options are

provided to ensure that the AT/LANTIC Controller can be

configured by an end user to function in all possible PC-AT

system configurations. Several types of configuration options can be implemented examples including:

1. Full jumper options: All programmable options are selected by utilizing jumpers on the board. Option selection

requires no special software. An example of this is

shown in the

Figure 11

Figure 10

.

.

2. I/O address jumpers only: All other options configurable

via software. This option simplifies installation while maximizing compatibility.

3. Jumperless: Special scheme provides contention-free

I/O address selection.

The AT/LANTIC Controller’s Configuration Registers are

the key to providing the ability to implement various configuration options. These registers are configured by the same

method in shared memory and I/O port modes, 8- or 16-bit

modes. The bit definitions of these registers are provided in

Section 5. All three registers are configured by hardware

selection during the Power-On-Reset of the system. Two of

these registers can be configured via software (the Mode

Configuration Registers A and B). The third register (Hardware Configuration Register C) is only configured during reset.

The following table indicates

troller options that a designer may like to have user configurable. (This list does not represent the complete list. For the

full list see the Configuration register descriptions in

Section 5.)

TABLE I. Some Configuration Options

for AT/LANTIC Controller

most

of the AT/LANTIC Con-

Option Selections

I/O Base Address 0300H 02C0H

Software 0320H

0240H 0340H

0280H 0360H

Interrupt No. 4 Interrupts 8 Interrupts

Boot PROM Disabled 0CC00H

Address 0C000H 0D000H

0C400H 0D400H

0C800H 0D800H

0DC00H

Boot PROM Size None 32k

16k 64k

Media Selection Twisted Pair Thin Ethernet

AUI Port

Architecture I/O Mode Shared RAM

Mode

Bus Timing IOCHRDY MEM16 Mode

Options Mode

The three basic options are described below. Because of

the variety of programmable options there are a number of

variations possible, only a few typical examples will be discussed.

FULLY JUMPERED OPERATION

This option is shown in

options are selected by jumpers on the AT/LANTIC Controller’s memory bus. For this option all configuration options

are set upon power-on by the AT/LANTIC Controller as described in Section 4.2. Accessing the configuration registers

is unnecessary and the EEPROM need only contain the

Figure 11

. In this configuration most

14

4.0 Functional Description (Continued)

JP1. .JP3 I/O Address

JP4..JP5 INTR Jumper

JP6 IO OR Shared RAM

JP7, JP8 Thin, Thick or TP Interface

JP9, CHRDY Assertion

JP10..JP13 EPROM Address and Size

FIGURE 11. Example of Jumper Configuration

Ethernet ID address (Configuration Register B bit 7 should

be set to disable EEPROM configuration mode, and Configuration Register C bit 7 could be set to disable software

configuration completely).

MINIMAL JUMPERS

The AT/LANTIC Controller’s configuration registers provide

the capability to enable software to configure various options (some may be hardwired). For the one option that is

not easily configured on the ISA bus is the I/O address

options. The reason for this is that the I/O locations must

first be known by the software in order for the software (usually a device driver) to access the AT/LANTIC Controller.

However, upon power up, in order to access a register to

configure the I/O base address to avoid conflicts some default location must be given (typically set in hardware on the

memory bus). It is possible that this default location conflicts

with an already installed device. If this is the case then one

possible solution, is to provide a jumper option for only the

I/O Addresses. A similar situation exists for the boot PROM

memory addresses.

In this application all options except the I/O address and

the boot PROM are hardwired on the memory bus to a default setting. After power up software can change the con-

TL/F/11498– 8

figuration to avoid conflicts on these settings. The advantage of this approach is that for most systems the default

I/O address setting is the correct one and no installation will

be required in this case. This approach minimizes any compatibility issues.

NO JUMPERS

The conflicts possible in the I/O base selection can be overcome by a special mode for software configuration of the

I/O base address. By using this mode, and by using the

configuration storage capability of the EEPROM a fully software configurable design on the ISA bus can be realized

without address conflict problems.

This mode is invoked by having the AT/LANTIC Controller

default to jumperless software configuration option in the

I/O base selection. This mode enables configuration register A to be mapped to address location 278H which is defined to be a printer port’s data register. If software writes to

this location four consecutive times on the fourth write the

AT/LANTIC Controller will load the data written into the I/O

address bits of Configuration Register A. This data should

set the I/O base address to a known conflict-free value. The

AT/LANTIC Controller can now be configured and operated

15

4.0 Functional Description (Continued)

at the desired base I/O address. If desired the configuration

software could change the EEPROM content to the new

values eliminating the need to reconfigure upon each power

up. Alternately the software could leave the EEPROM alone

and execute the configuration using the printer port’s data

register upon each power up. This configuration scheme will

only work once after each power-up. Therefore the user

cannot enable the AT/LANTIC Controller from reserved

mode, change it back into reserved mode, and enable it

again. A power-on reset must occur between the first time it

is enabled from the reserved mode and the second.

A second consideration is the location of the boot PROM in

the system memory map, which also has the same conflict

and programming considerations as the I/O address selection. However the solution is different, primarily because the

boot PROM must be configured before power up. This is

because during normal usage of the boot PROM the PC’s

BIOS will look for the ROM immediately after reset, not allowing configuration software to first select the boot PROM

addressing prior to usage.

To configure the boot PROM without jumpers the configuration software must first power up the AT/LANTIC Controller,

configure the EEPROM to the desired location, then hardware reset the AT/LANTIC Controller. After the reset the

AT/LANTIC Controller’s EEPROM will load in the desired

boot PROM configuration automatically during the reset.

Now after reset when the PC scans for the boot PROM, the

ROM will be correctly mapped in the memory space enabling the network boot operation to proceed.

Ethernet Cable Configuration

AT/LANTIC Controller offers the choice of all the possible

Ethernet cabling options, that is Ethernet (10BASE5), Thin

Ethernet (10BASE2) and Twisted-pair Ethernet (10BASE-T).

The type of cabling used is controlled by Configuration Register B. AT/LANTIC Controller also supplies a THIN output

signal which can be used to disable/enable an external

DC–DC converter which is required for 10BASE2.

4.5 LOW POWER OPERATION

The AT/LANTIC Controller has a low power support mode

that can be used to disable the Ethernet port and conserve

power. It should be noted that the device is not operational

in this mode and requires to be initialized after exiting this

mode.

The power and ground pins to the AT/LANTIC Controller

are split up into two groups, interface and core. By switching

the power off to the core logic while still powering the interface logic the AT/LANTIC Controller can be powered down

without crashing the ISA bus. The LOWPWR pin should be

driven high to indicate that the device is about to go into low

power then the power to the V

off. The same signal that is used to drive the LOWPWR pin

can be used to drive a p-channel load switch to disable

power to the core. This switch must have a very low on

resistance to minimize the voltage difference between the

V

and the lFVCC. All devices on the memory support bus

CC

should also be powered from the V

pins should be switched

DD

supply.

CC

4.6 BOOT PROM OPERATION

The AT/LANTIC Controller supports an optional boot

PROM, the address and size of which can be set in Configuration Register C. This boot PROM can be any 8 bits wide

storage device implemented with a non-volatile technology.

Write cycles to this device can be enabled and disabled by

programming Configuration Register B. This can be used to

prevent unwanted write cycles to certain devices, such as a

Flash EEPROM. It should be noted that the address pins

for the boot PROM should be connected directly to the

ISA bus. The AT/LANTIC Controller supplies the chip se-

lect to the device and buffers the data onto and from the

ISA bus, so the memory support data bus should be connected to the boot PROM’s data pins.

4.7 DP8390 CORE (NETWORK INTERFACE

CONTROLLER)

The DP8390 Core logic,

Deserializer which is controlled by the Protocol PLA, DMA

Control, FIFO, Address Comparator, Multicast Hashing Register. The DP8390 core implements all of the IEEE 802.3

Media access control functions for the AT/LANTIC Controller, and interfaces to the internal ENDEC (on the left of the

block diagram) and also interfaces to the Bus Interface and

memory support bus via a number of address, data and control signal (and the right side of the block diagram). The

following sections describe the functions of the DP8390

core.

Receive Deserializer

The Receive Deserializer is activated when the input signal

Carrier Sense is asserted to allow incoming bits to be shifted into the shift register by the receive clock. The serial

receive data is also routed to the CRC generator/checker.

The Receive Deserializer includes a synch detector which

detects the SFD (Start of Frame Delimiter) to establish

where byte boundaries within the serial bit stream are located. After every eight receive clocks, the byte wide data is

transferred to the 16-byte FlFO and the Receive Byte Count

is incremented. The first six bytes after the SFD are

checked for valid comparison by the Address Recognition

Logic. If the Address Recognition Logic does not recognize

the packet, the FlFO is cleared.

CRC Generator/Checker

During transmission, the CRC logic generates a local CRC

field for the transmitted bit sequence. The CRC encodes all

fields after the synch byte. The CRC is shifted out MSB first

following the last transmit byte. During reception the CRC

logic generates a CRC field from the incoming packet. This

local CRC is serially compared to the incoming CRC appended to the end of the packet by the transmitting node. If

the local and received CRC match, a specific pattern will be

generated and decoded to indicate no data errors. Transmission errors result in different patterns and are detected,

resulting in rejection of a packet.

Figure 12

, contains the Serializer/

16

4.0 Functional Description (Continued)

FIGURE 12. DP8390 Controller Core Simplified Block Diagram

Transmit Serializer

The Transmit Serializer reads parallel data from the FIFO

and serializes it for transmission. The serializer is clocked by

the transmit clock generated internally. The serial data is

also shifted into the CRC generator/checker. At the beginning of each transmission, the Preamble and Synch Generator append 62 bits of 1,0 preamble and a 1,1 synch pattern. After the last data byte of the packet has been serialized the 32-bit FCS (Frame Check Sequence) field is shifted

directly out of the CRC generator. In the event of a collision

the Preamble and Synch generator is used to generate a

32-bit JAM pattern of all 1’s.

Comparator-address Recognition Logic

The address recognition logic compares the Destination Address Field (first 6 bytes of the received packet) to the Physical address registers stored in the Address Register Array.

If any one of the six bytes does not match the pre-programmed physical address, the Protocol Control Logic rejects the packet. All multicast destination addresses are filtered using a hashing technique. (See register description.)

If the multicast address indexes a bit that has been set in

the filter bit array of the Multicast Address Register Array

the packet is accepted, otherwise it is rejected by the Protocol Control Logic. Each destination address is also checked

for all 1’s which is the reserved broadcast address.

FIFO and Packet Data Operations

OVERVIEW

To accommodate the different rates at which data comes

from (or goes to) the network and goes to (or comes from)

the packet buffer memory, the AT/LANTIC Controller contains a 16-byte FIFO for buffering data between the media

and the buffer RAM located on the memory support bus.

The FIFO threshold is programmable, allowing filling (or

emptying) the FIFO at different rates. When the FIFO has

filled to its programmed threshold, the local DMA channel

transfers these bytes (or words) into local memory (via the

TL/F/11498– 9

memory bus). It is crucial that the local DMA is given access

to the bus within a minimum bus latency time; otherwise a

FIFO underrun (or overrun) occurs.

FIFO underruns or overruns are caused when a local DMA

request is issued while an ISA bus access is current and the

ISA cycle takes longer to complete than the local DMA’s

tolerable latency. This tolerable latency depends on the

FIFO threshold, whether it is in byte or word wide mode and

the speed of the DMA clock (BSCLK frequency). Note that

this refers to standard ISA cycles NOT those where the

CHRDY is deasserted extending the cycle.

FIFO THRESHOLD DETECTION

To assure that there is no overwriting of data in the FIFO,

the FIFO logic flags a FIFO overrun as the 13th byte is

written into the FIFO, effectively shortening the FIFO to 13

bytes. The FIFO logic also operates differently in Byte Mode

and in Word Mode. In Byte Mode, a threshold is indicated

when the n

a

1 byte has entered the FIFO; thus, with an 8

byte threshold, the AT/LANTIC Controller issues a request

to the buffer RAM when the 9th byte has entered the FIFO,

making the effective threshold 9 bytes. For Word Mode, the

request is not generated until the n

a

2 bytes have entered

the FIFO. Thus, with a 4 word threshold (equivalent to 8

byte threshold), a request to the buffer RAM is issued when

the 10th byte has entered the FIFO, making the effective

threshold 10 bytes.

TOLERABLE LATENCY CALCULATION

To prevent a FIFO overrun a byte (or word) of data must be

removed from the FIFO before the 13th byte is written.

Therefore the worst case tolerable latency is the time from

the effective threshold being reached to the time the 13th

byte is written minus the time taken to load the first byte (or

word) of data to the FIFO during a local DMA burst (8

BSCLKs).

tolerable latency

e

((overrunbeffective) threshold

c

time to transfer byte on network)

b

time to fill 1st FIFO location

17

4.0 Functional Description (Continued)

For the case of a 4 word threshold using a 20 MHz BSCLK:

tolerable latency

To prevent a FIFO underrun a byte (or word) of data must

be added from the FIFO before the last byte is removed.

Therefore the worst case tolerable latency is the time from

the effective threshold being reached to the time the last

byte is removed minus the time taken to load the first byte

(or word) of data to the FIFO during a local DMA burst (8

BSCLKs).

tolerable latency

For the case of a 4 word threshold using a 20 MHz BSCLK:

tolerable latencye(4c800)b(8c50) ns

The worst case latency, either overrun or underrun, ultimately limits the overall latency that the AT/LANTIC Controller can tolerate. If the standard ISA cycles are shorter

than the worst case latency then no FIFO overruns or underruns will occur.

BEGINNING OF RECEIVE

At the beginning or reception, the AT/LANTIC Controller

stores entire Address field of each incoming packet in the

FIFO to determine whether the packet matches its Physical

Address Registers or maps to one of its Multicast Registers.

This causes the FIFO to accumulate 8 bytes.

Furthermore, there are some synchronization delays in the

DMA PLA. Thus, the actual time that a request to access

the buffer RAM is asserted from the time the Start of Frame

Delimiter (SFD) is detected is 7.8 ms. This operation affects

the bus latencies at 2 byte and 4 byte thresholds during the

first receive request since the FIFO must be filled to 8 bytes

(or 4 words) before issuing a request to the buffer RAM.

END OF RECEIVE

When the end of a packet is detected by the ENDEC module, the AT/LANTIC Controller enters its end of packet processing sequence, emptying its FIFO and writing the status

information at the beginning of the packet. The AT/LANTIC

Controller holds onto the memory bus for the entire sequence. The longest time that local DMA will hold the buffer

RAM occurs when a packet ends just as the AT/LANTIC

Controller performs its last FIFO burst. The AT/LANTIC

Controller, in this case, performs a programmed burst transfer followed by flushing the remaining bytes in the FIFO, and

completed by writing the header information to the buffer

memory. The following steps occur during this sequence.

e

((13b10)c800)b(8c50) ns

e

2 ms

e

(threshold

c

time to transfer byte on network)

b

time to fill 1st FIFO location

e

2.8 ms

1. AT/LANTIC Controller issues request to access the

RAM because the FIFO threshold has been reached.

2. During the burst, packet ends, resulting in the request

being extended.

3. AT/LANTIC Controller flushes remaining bytes from

FIFO.

4. AT/LANTIC Controller performs internal processing to

prepare for writing the header.

5. AT/LANTIC Controller writes 4-byte (2-word) header

6. AT/LANTIC Controller de-asserts access to the buffer

RAM.

BEGINNING OF TRANSMIT

Before transmitting, the AT/LANTIC Controller performs a

prefetch from memory to load the FIFO. The number of

bytes prefetched is the programmed FIFO threshold. The

next request to the buffer RAM is not issued until after the

AT/LANTIC Controller actually begins transmitting data, i.e.,

after SFD.

READING THE FIFO

If the FIFO is read during normal operation the AT/LANTIC

Controller will ‘‘hang’’ the ISA bus by deasserting CHRDY

and never asserting it. The FIFO should only be read during

loopback diagnostics, when it will operate normally.

PROTOCOL PLA

The Protocol PLA is responsible for implementing the IEEE

802.3 protocol, including collision recovery with random

backoff. The Protocol PLA also formats packets during

transmission and strips preamble and synch during reception.

DMA AND BUFFER CONTROL LOGIC

The DMA and Buffer Control Logic is used to control two

16-bit DMA channels. During reception, the Local DMA

stores packets in a receive buffer ring, located in buffer

memory. During transmission the Local DMA uses programmed pointer and length registers to transfer a packet

from local buffer memory to the FIFO.

A second DMA channel is used when the AT/LANTIC Controller is used in I/O Port mode. This DMA is used as a slave

DMA to transfer data between the local buffer memory and

the host system. The Local DMA and Remote DMA are internally arbitrated, with the Local DMA channel having highest priority. Both DMA channels use a common external bus

clock to generate all required bus timing. External arbitration

is performed with a standard bus request, bus acknowledge

handshake protocol.

In the shared memory mode the Remote DMA is not used,

because in this mode the system has direct read/write access to the buffer RAM.

18

4.0 Functional Description (Continued)

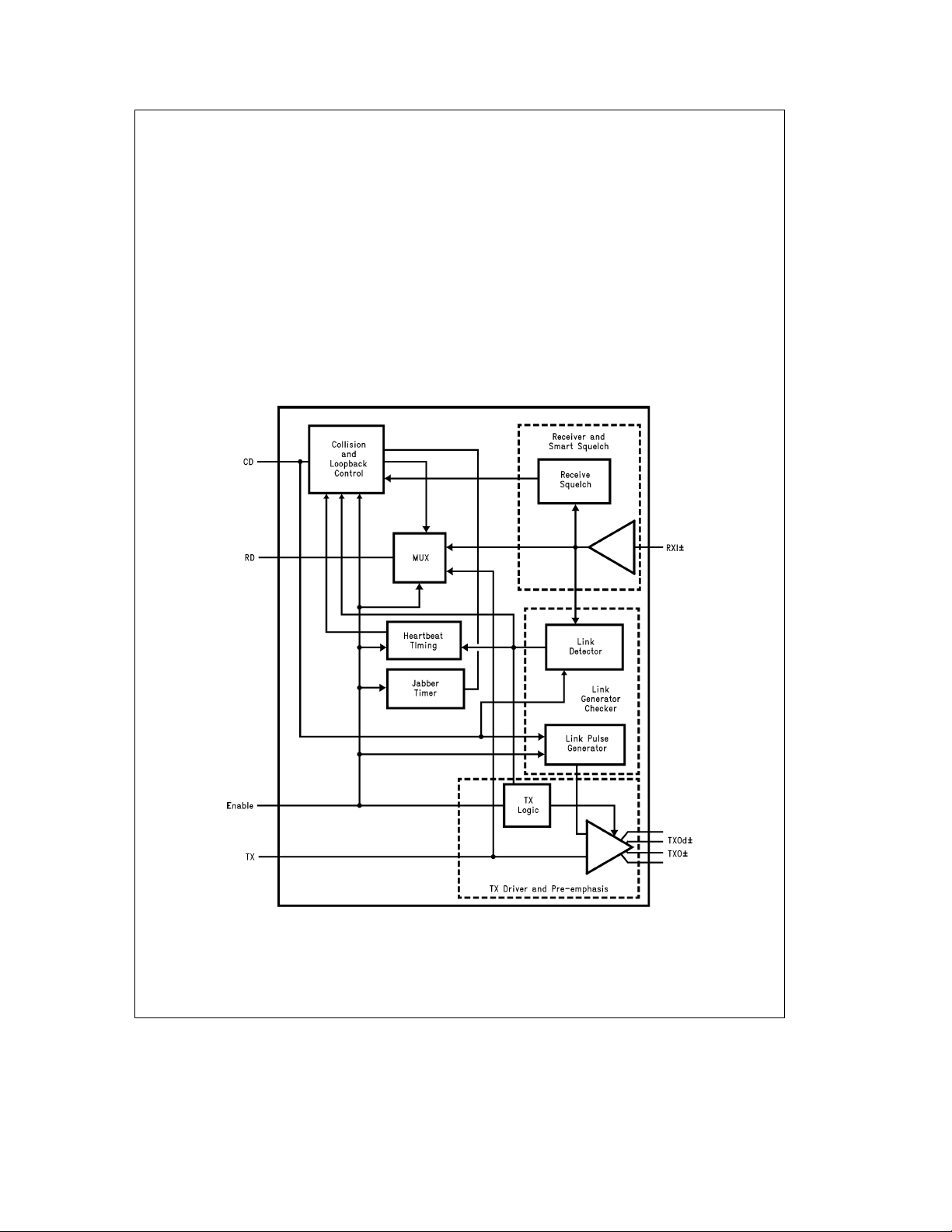

4.8 TWISTED PAIR INTERFACE MODULE

The TPI consists of five main logical functions:

a) The Receiver/Smart Squelch, responsible for determin-

ing when valid data is present on the differential receive

inputs (RXI

b) The Collision function checks for simultaneous transmis-

sion and reception of data on the TXO

c) The Link Detector/Generator checks the integrity of the

cable connecting the two twisted pair MAUs.

d) The Jabber disables the transmitter if it attempts to

transmit a longer than legal packet.

e) The TX Driver and Pre-emphasis transmits Manchester

encoded data to the twisted pair network via the summing resistors and transformer/filter.

g

) and receiving the data.

g

and RXIgpins.

Receiver and Smart Squelch

The AT/LANTIC Controller implements an intelligent receive squelch on the RXI

g

differential inputs to ensure that

impulse noise on the receive inputs will not be mistaken for

a valid signal.

The squelch circuitry employs a combination of amplitude

and timing measurements to determine the validity of data

on the twisted pair inputs. There are two voltage level options for the smart squelch. One mode, 10BASE-T mode,

uses levels that meet the 10BASE-T specification. The second mode, reduced squelch mode, uses a lower squelch

threshold level, and can be used in longer cable applications where smaller signal levels may be applied. The

squelch level mode can be selected in the AT/LANTIC Controller configuration registers.

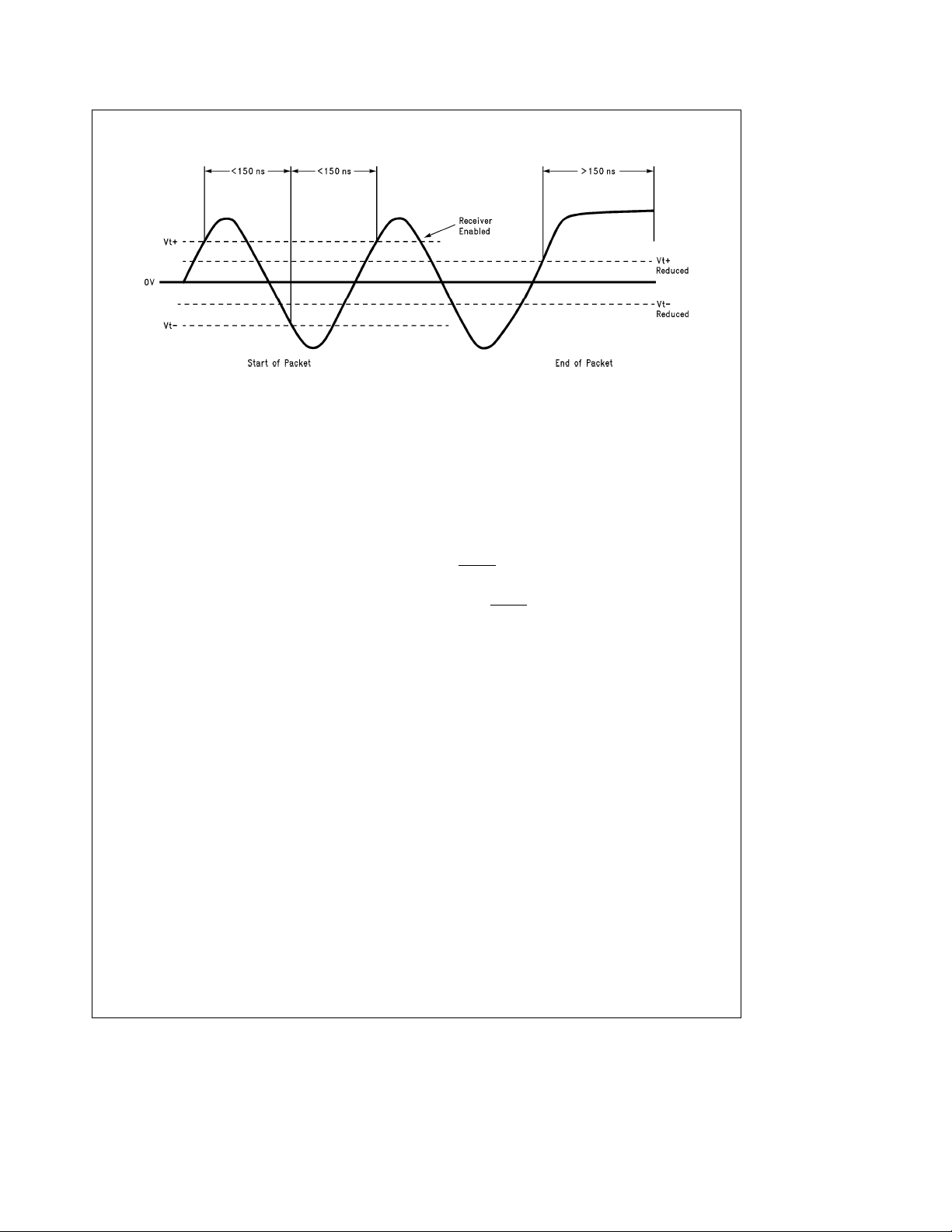

Figure 14

shows the operation of the smart squelch in

10BASE-T mode.

FIGURE 13. Twisted Pair Interface Module Block Diagram

19

TL/F/11498– 10

4.0 Functional Description (Continued)

FIGURE 14. Twisted Pair Squelch Waveform

The signal at the start of packet is checked by the smart

squelch and any pulses not exceeding the squelch level

(either positive or negative, depending upon polarity) will be

rejected. Once this first squelch level is overcome correctly

the opposite squelch level must then be exceeded within

150 ns later. Finally the signal must exceed the original

squelch level within a further 150 ns to ensure that the input

waveform will not be rejected. The checking procedure results in the loss of typically three bits at the beginning of

each packet.

Only after all these conditions have been satisfied will a

control signal be generated to indicate to the remainder of

the circuitry that valid data is present. At this time the smart

squelch circuitry is reset.

In the reduced squelch mode the operation is identical except that the lower squelch levels shown in

Figure 14

are

used.

Valid data is considered to be present until either squelch

level has not been generated for a time longer than 150 ns,

indicating End of Packet. Once good data has been detected the squelch levels are reduced to minimize the effect of

noise causing premature End of Packet detection.

Collision

A collision is detected by the TPI module when the receive

and transmit channels are active simultaneously. If the TPI

is receiving when a collision is detected it is reported to the

controller immediately. If, however, the TPI is transmitting

when a collision is detected the collision is not reported until

seven bits have been received while in the collision state.

This prevents a collision being reported incorrectly due to

noise on the network. The signal to the controller remains

for the duration of the collision.

Approximately 1 ms after the transmission of each packet a

signal called the Signal Quality Error (SQE) consisting of

typically 10 cycles of 10 MHz is generated. This 10 MHz

signal, also called the Heartbeat, ensures the continued

functioning of the collision circuitry.

TL/F/11498– 11

Link Detector/Generator

The link generator is a timer circuit that generates a link

pulse as defined by the 10 Base-T specification that will be

generated by the transmitter section. The pulse which is

100 ns wide is transmitted on the TXO

a

output, every

16 ms, in the absence of transmit data.

The pulse is used to check the integrity of the connection to

the remote MAU. The link detection circuit checks for valid

pulses from the remote MAU and if valid link pulses are not

received the link detector will disable the transmit, receive

and collision detection functions.

The GDLNK

output can directly drive a LED to show that

there is a good twisted pair link. For normal conditions the

LED will be on. The link integrity function can be disabled by

setting the GDLNK

bit of Configuration Register B.

Jabber

The jabber timer monitors the transmitter and disables the

transmission if the transmitter is active for greater than

26 ms. The transmitter is then disabled for the whole time

that the Endec module’s internal transmit enable is asserted. This signal has to be deasserted for approximately

750 ms (the unjab time) before the Jabber re-enables the

transmit outputs.

Transmitter

The transmitter consists of four signals, the true and compliment Manchester encoded data (TXO

delayed by 50 ns (TXOd

These four signals are resistively combined TXOawith

b

TXOd

and TXObwith TXOda. This is known as digital

g

)

g

) and these signals

pre-emphasis and is required to compensate for the twisted

pair cable which acts like a low pass filter causing greater

attenuation to the 10 MHz (50 ns) pulses of the Manchester

encoded waveform than the 5 MHz (100 ns) pulses.

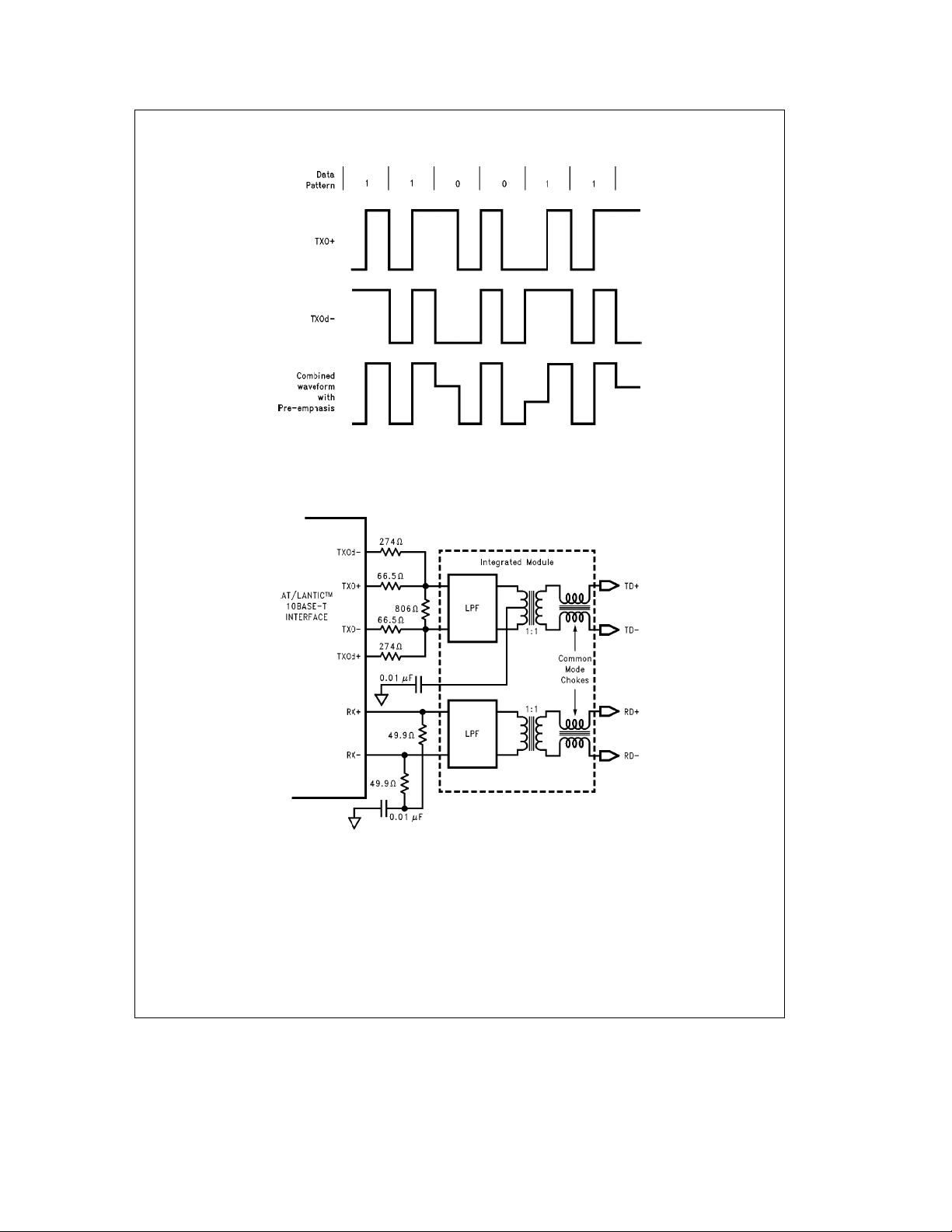

An example of how these siqnals are combined is shown in

the following diagram.

20

4.0 Functional Description (Continued)

FIGURE 15. Typical Summed Transmit Waveform

The signal with pre-emphasis shown above is generated by resistively combining TXO

compliment is passed to the transmit filter.

FIGURE 16. External Circuitry to Connect AT/LANTIC Controller to Twisted Pair Cable

TL/F/11498– 12

a

and TXOdb. This signal along with its

TL/F/11498– 13

21

4.0 Functional Description (Continued)

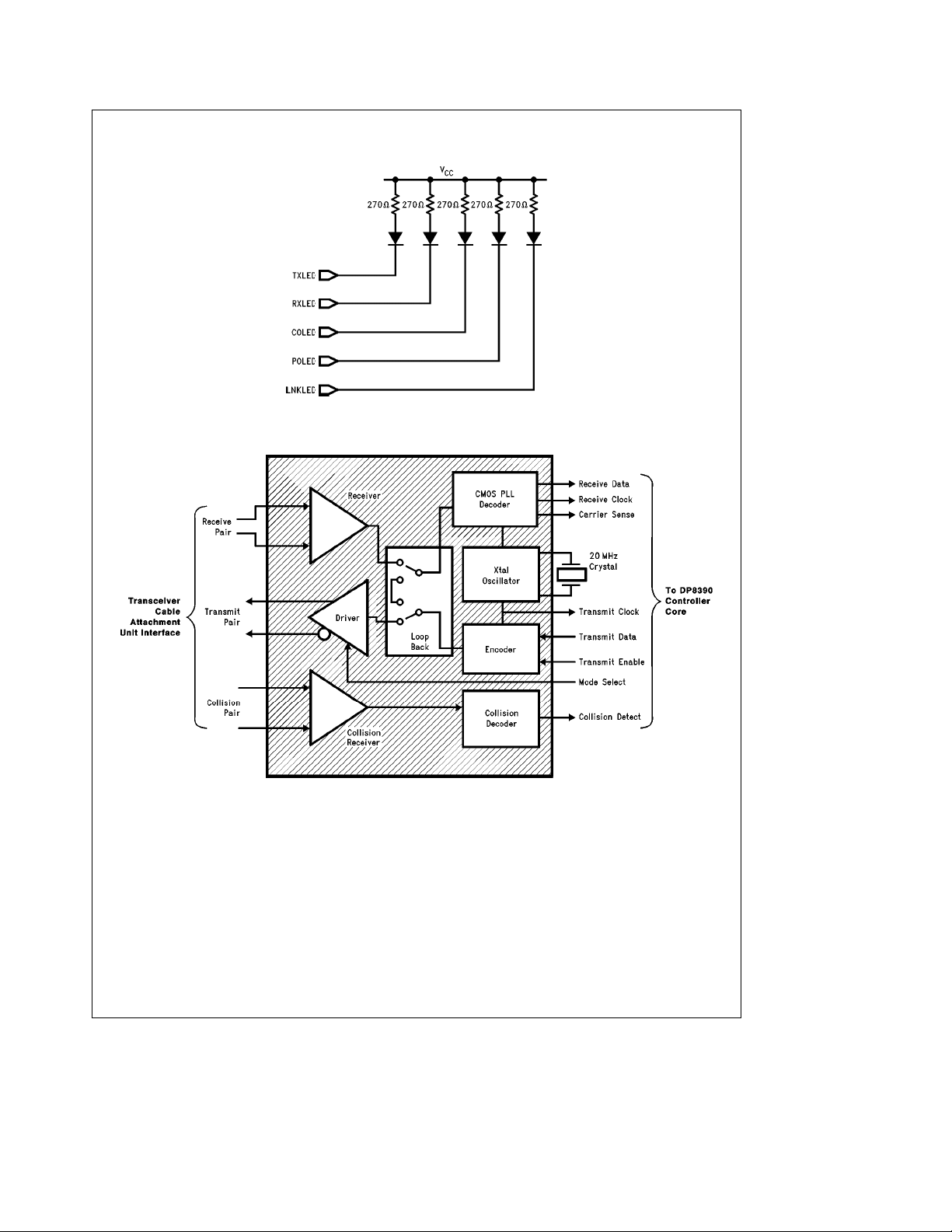

FIGURE 17. Typical AT/LANTIC Controller LED Connection

TL/F/11498– 15

FIGURE 18. Encoder/Decode Block Diagram

22

TL/F/11498– 14

4.0 Functional Description (Continued)

Status Information

Status information is provided by the AT/LANTIC Controller

on the RXLED, TXLED, COLED and POL outputs as described in the pin description table. These outputs are suitable for driving status LED’s as shown in

puts are open drain.

Recommended integrated Filter-Transformer-choke modules:

1. Pulse Engineering PE65424

2. Valor FL1012 or FL1030.

4.9 ENCODER/DECODER (ENDEC) MODULE

The ENDEC consists of four main logical blocks:

a. The oscillator generates the 10 MHz transmit clock sig-

nal for system timing.

b. The Manchester encoder accepts NRZ data from the

controller, encodes the data to Manchester, and transmits the data differentially to the transceiver, through the

differential transmit driver.

c. The Manchester decoder receives Manchester data from

the transceiver, converts it to NRZ data and clock pulses, and sends it to the controller.

d. The collision translator indicates to the controller the

presence of a valid 10 MHz collision signal to the PLL.

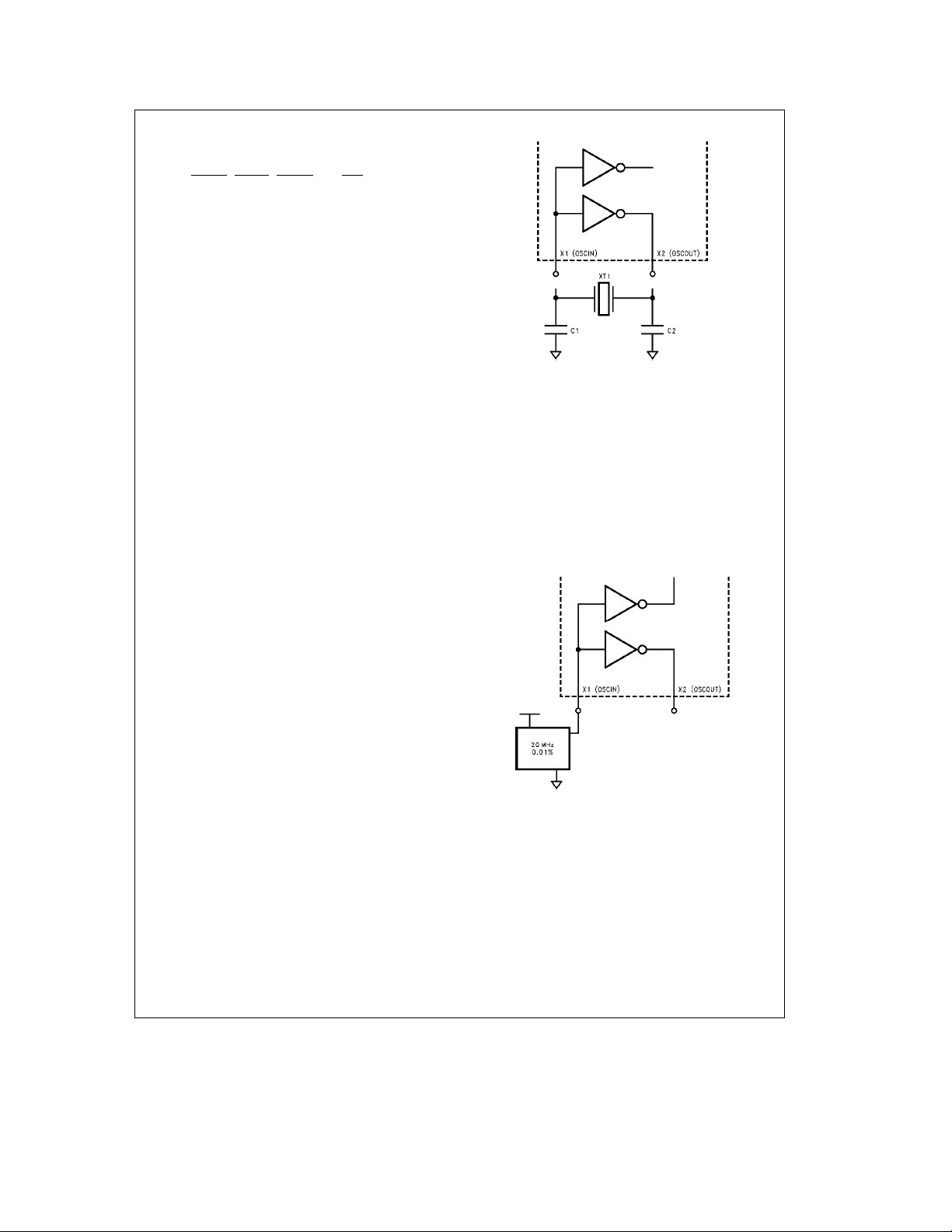

Oscillator

The oscillator is controlled by a 20 MHz parallel resonant

crystal connected between X1 and X2 or by an external

clock on X1. The 20 MHz output of the oscillator is divided

by 2 to generate the 10 MHz transmit clock for the controller. The oscillator also provides internal clock signals to the

encoding and decoding circuits.

CRYSTAL OPERATION

If the crystal used with the internal oscillator circuit is not

properly selected, the AT/LANTIC Controller oscillator may

not reliably start oscillation under all conditions.

If this occurs, it could be deceiving to a designer, since his

prototypes may work fine. However, when the designer

does qualification testing or starts production, he may encounter a higher than expected board yield loss due to the

oscillator not starting. The AT/LANTIC Controller’s oscillator circuit clocks the Encoder-Decoder logic. The

AT/LANTIC Controller’s oscillator also clocks the twisted

pair interface block. If the oscillator does not start, the

AT/LANTIC Controller will not be able to transmit or receive.

If a crystal is connected to the AT/LANTIC Controller, it is

recommended that the circuit shown in

and that the components used meet the following:

Crystal XT1: AT cut parallel resonant crystal

Series Resistance:

Specified Load Capacitance:

Accuracy: 0.005% (50 ppm)

Typical Load: 50 mW–75 mW

The recommended values for capacitors C1 and C2 are

26 pF minus the board capacitance on that pin. Therefore if

both X1 and X2 have 4 pF of board capacitance, then a

22 pF capacitor should be used.

According to the IEEE 802.3 standard, the entire oscillator

circuit (crystal and amplifier) must be accurate to 0.01%.

When using a crystal, the X2 pin is not guaranteed to provide a TTL compatible logic output, and should not be used

Figure 17

. All out-

Figure 19

s

25X

s

be used

20 pF

FIGURE 19. Crystal Connection to AT/LANTIC

Controller (see text for component values)

to drive external standard logic. If additional logic needs to

be driven, then an external oscillator should be used, as

described in the following section.

OSCILLATOR MODULE OPERATION

If the designer wishes to use a crystal clock oscillator, one

that provides the following should be employed:

1. TTL or CMOS output with a 0.01% frequency tolerance

2. 40% – 60% duty cycle

The circuit is shown in

Figure 20

. When using a clock oscillator it is recommended that the designer connect the oscillator output to the X1 pin and leave the X2 pin floating.

FIGURE 20. AT/LANTIC Controller

Connection for Oscillator Module

Manchester Encoder and Differential Driver

The differential transmit pair, on the secondary of the employed transformer, drives up to 50 meters of twisted pair

AUI cable. These outputs are source followers which require

two 270X pull-down resistors to ground (see

The AT/LANTIC Controller allows full-step to be compatible

with IEEE 802.3. Transmit

a

and Transmitbare equal in the

Figure 21

idle state, providing zero differential voltage to operate with

transformer coupled loads.

Manchester Decoder

The decoder consists of a differential receiver and a PLL to

separate a Manchester encoded data stream into internal

23

TL/F/11498– 16

TL/F/11498– 17

).

4.0 Functional Description (Continued)

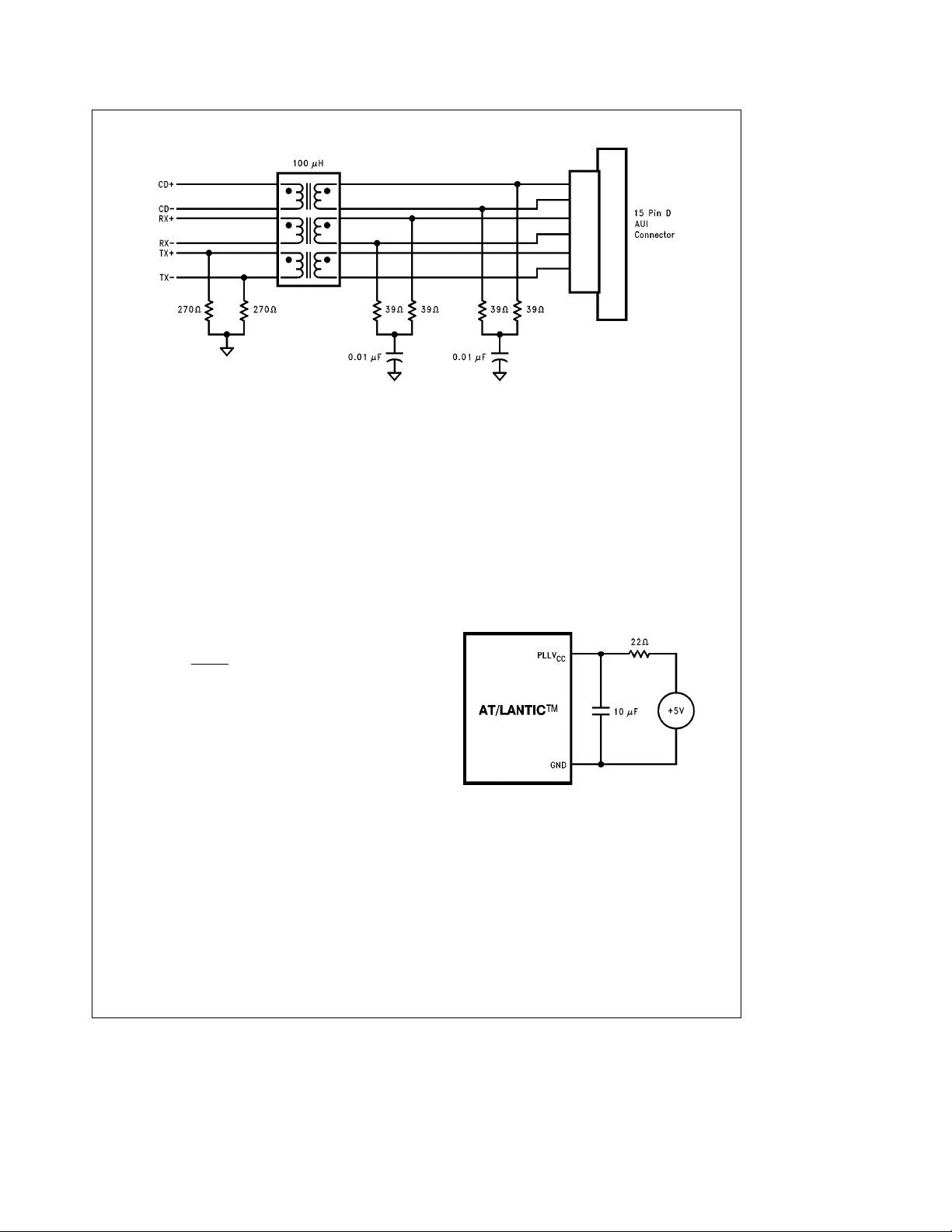

FIGURE 21. Connection from AT/LANTIC Controller’s AUI Port to the AUI Connector

clock signals and data. The differential input must be externally terminated with two 39X resistors connected in series

if the standard 78X transceiver drop cable is used, in thin

Ethernet applications, these resistors are optional. To prevent noise from falsely triggering the decoder, a squelch

circuit at the input rejects signals with levels less than

b

175 mV. Data becomes valid typically within 6 bit times.

The AT/LANTIC Controller may tolerate bit jitter up to 20 ns

in the received data. The decoder detects the end of a

frame when no more mid-bit transitions are detected.

Collision Translator

When in AUI Mode, the Ethernet transceiver (DP8392 CTl)

detects a collision, it generates a 10 MHz signal to the differential collision inputs (CD

g

) of the AT/LANTIC Controller. When these inputs are detected active, the AT/LANTIC

Controller uses this signal to back off its current transmission and reschedule another one.

In this mode the COLED

output will indicate when the CD

lines are active during activity on the network. This means it

will correctly indicate any collision on the network, but will

not be lit for heartbeat or if there is no cable connected.

The collision differential inputs are terminated the same way

as the differential receive inputs. The squelch circuitry is

also similar, rejecting pulse levels less than

PLL V

Power Supply Consideration

CC

b

175 mV.

The PLL VCCpin is thea5V power supply for the phase

lock loop (PLL) of the ST-NIC ENDEC unit. Since this is an

TL/F/11498– 19

analog circuit, excessive noise on the PLL V

fect the performance of the PLL. This noise, if in the

pin can af-

CC

10 kHz–400 kHz range, can reduce the jitter performance of

the ENDEC, resulting in missing packets or CRC errors.

If the power supply noise is causing significant packet reception error, a low pass filter could be added to reduce the

power supply noise and hence improve the jitter performance. Standard analog design techniques should be utilized

when laying out the power supply traces on the board. If the

digital power supply is used, it may be desirable to add a

one pole RC filter (designed to have a cut-off frequency of

1 kHz) as shown in

ance. The PLL V

across the resister is less than 90 mV, which will not affect

Figure 4

only draws 3 mA – 4 mA so the voltage

CC

to improve the jitter perform-

the PLL’s operation.

g

TL/F/11498– 18

FIGURE 22. Filtering Power Supply Noise

24

Loading...

Loading...