DP83891 Gig PHYTER™ 10/100/1000M

© 2000 National Semiconductor Corporation

www.national.com

Subject to change Last Modified: 1/27/00 REVISION 0.0

Advance Information

January 2000

DP83891 Gig PHYTER™10/100/1000M

General Description

The DP83891 is the first fully integrated,feature rich Physical Layer transceiverwithintegrated PMD sublayersto support 10BASE-T,100BASE-TX and 1000BASE-T Ethernet

protocols. It operates on existing CAT5 cables which

reduces deployment costs.

The DP83891 is designed for easy implementation of

10/100/1000 Mb/s Ethernet LANs. It interfaces directly to

Twisted Pair media via an external standard Quad transformer. The DP83891 connects to the MAC layer through

the IEEE 802.3u Standard Media Independent Interface

(MII) or the IEEE 802.3z Gigabit Media Independent Interface (GMII).

Applications

The DP83891 fits applications in:

■ 10/100/1000 Mb/s capable node cards

■ Switches with 10/100/1000 Mb/s capable ports

■ High speed uplink ports (backbone)

■ High end workstations

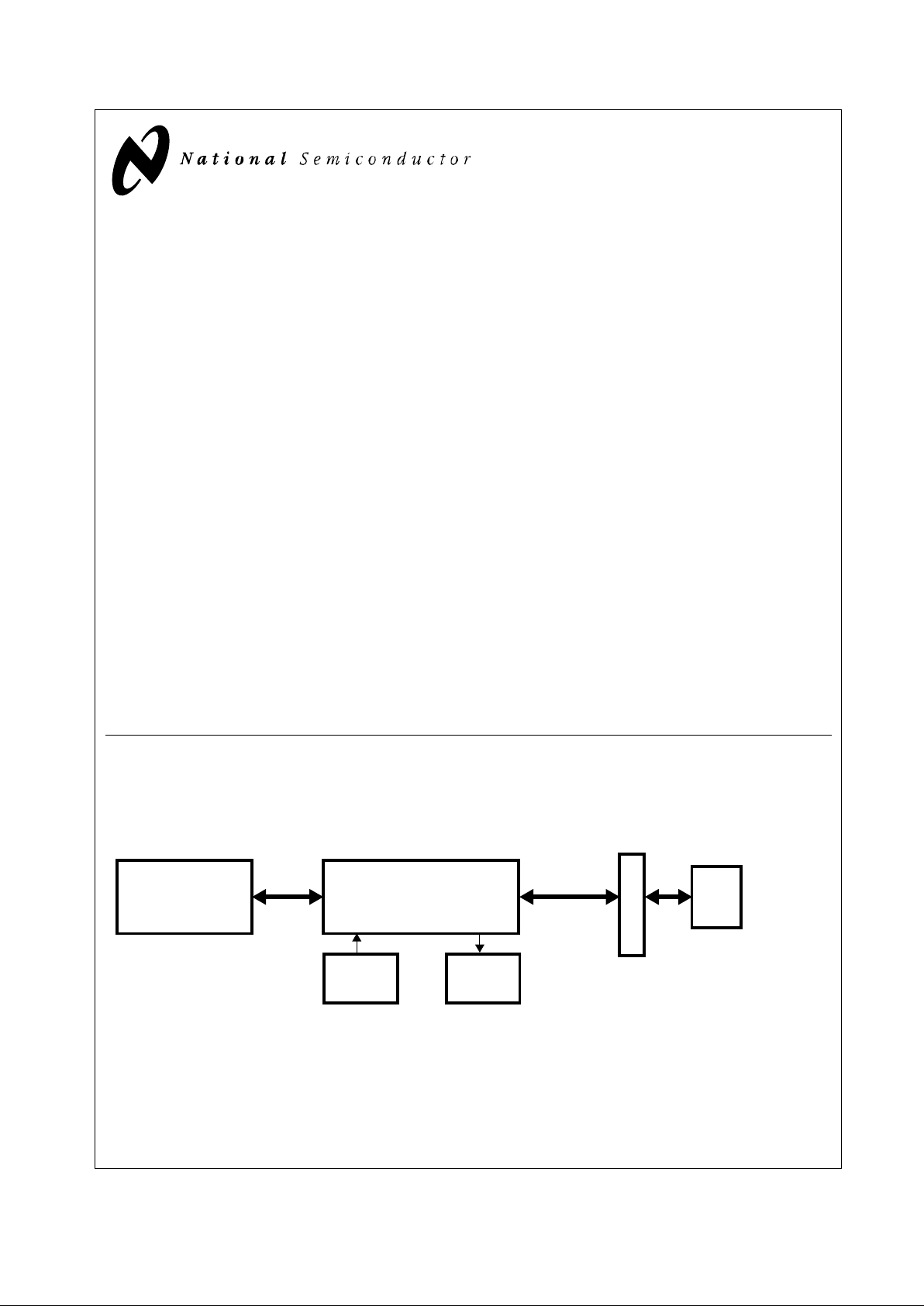

System Diagram

TRI-STATE® is a registered trademark of National Semiconductor Corporation.

ETHERNET

DP83891

ETHERNET PHYSICAL LAYER

STATUS

LED

MAGNETICS

RJ-45

100BASE-TX

MII/GMII

MAC

100BASE-TX

CLOCK

125 MH

1000BASE-T

or

1000BASE-T

z

s

or

10/100/1000

10/100/1000 Mb/s

10BASE-T,

10BASE-T,

Features

■ Fully integrated 10BASE-T,100BASE-TX and

1000BASE-T capable

■ Single Quad TX-Transformer interface for all speeds

■ Fully compliant to IEEE 802.3u 100BASE-TX and IEEE

802.3z/ab 1000BASE-T specifications. Fully integrated

and fully compliantANSI X3.T12 PMD physical sublayer

that includes adaptive equalization and Baseline Wander compensation.

■ Supports Auto-MDIX

■ IEEE 802.3u Auto-Negotiation and Parallel Detection

– Fullyauto-negotiatesbetween10,100and1000Mb/s

full duplex and half duplex devices

■ 3.3 V MAC interfaces:

– IEEE 802.3u MII

– IEEE 802.3z GMII

■ LED support (Link, Speed, Activity, Duplex, Collision,

Auto-Negotiation, TX and RX indications)

■ Management Register Set (MDIO and MDC)

■ Single 3.3 V power supply

– 5 V tolerant I/Os

■ 208-pin PQFP package

DP83891 Gig PHYTER™ 10/100/1000M

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

LIFE SUPPORT POLICY

NATIONAL’SPRODUCTSARENOTAUTHORIZEDFORUSEASCRITICALCOMPONENTSINLIFESUPPORT

DEVICESORSYSTEMSWITHOUTTHEEXPRESSWRITTENAPPROVALOFTHEPRESIDENTOFNATIONAL

SEMICONDUCTOR CORPORATION. As used herein:

1.Lifesupportdevicesorsystemsaredevicesorsystems

which,(a)areintendedforsurgicalimplantintothebody,

or (b) support or sustain life, and whose failure to perform,whenproperlyusedinaccordancewithinstructions

for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

2.A critical component is any component of a life support

device or system whose failure to perform can be reasonablyexpectedtocausethefailureofthelifesupport

device or system, or to affect its safety or effectiveness.

National Semiconductor

Corporation

Tel: 1-800-272-9959

Fax: 1-800-737-7018

Email: support@nsc.com

National Semiconductor

Europe

Fax: (+49) 0-180-530 85 86

Email:europe.support@nsc.com

Deutsch Tel: (+49) 0-180-530 85 85

English Tel: (+49) 0-180-532 78 32

National Semiconductor

Japan Ltd.

Tel: 81-3-5620-6175

Fax: 81-3-5620-6179

National Semiconductor

Asia Pacific

Customer Response Group

Tel: 65-254-4466

Fax: 65-250-4466

Email: sea.support@nsc.com

www.national.com

Loading...

Loading...