®

DP83861VQM-3 EN Gig PHYTER

10/100/1000 Ethernet Physical Layer

DP83861 EN Gig PHYTER® 10/100/1000 Ethernet Physical Layer

PRELIMINARY

April 2001

General Description

The DP83861 is a full featured Physical Layer transceiver

with integrated PMD sublayers to support 10BASE-T,

100BASE-TX and 1000BASE-T Ethernet protocols.

The DP83861 uses state of the art 0.18 µm , 1.8 V/3.3 V

CMOS technology, fabricated at National Semiconductor’s

South Portland Maine facility.

The DP83861 is designed for easy implementation of

10/100/1000 Mb/s Ethernet LANs. It interfaces directly to

Twisted Pair media via an external transformer. This device

interfaces directly to the MAC layer through the IEEE

802.3u Standard Media Independent Interface (MII) or the

IEEE 802.3z Gigabit Media Independent Interface (GMII).

Applications

The DP83861 fits applications in:

■ 10/100/1000 Mb/s capable node cards

■ Switches with 10/100/1000 Mb/s capable ports

■ High speed uplink ports (backbone)

Features

■ 100BASE-TX and 1000BASE-T compliant

■ Fully compliant to IEEE 802.3u 100BASE-TX and IEEE

802.3z/ab 1000BASE-T specifications. Fully integrated

and fully complian t ANSI X3.T12 PMD phy sical sublayer

that includes adaptiv e equalization and Baseline Wander compensation

■ 10BASE-T compatible

■ IEEE 802.3u Auto-Negotiation and Parallel Detection

– Fully Auto-Negotiates between 1000 Mb/s, 100 Mb/s,

and 10 Mb/s Full Duplex and Half Duplex devices

■ Interoperates with first generati on 1000BASE-T Physical

layer transceivers

■ 3.3V MAC interfaces:

– IEEE 802.3u MII

– IEEE 802.3z GMII

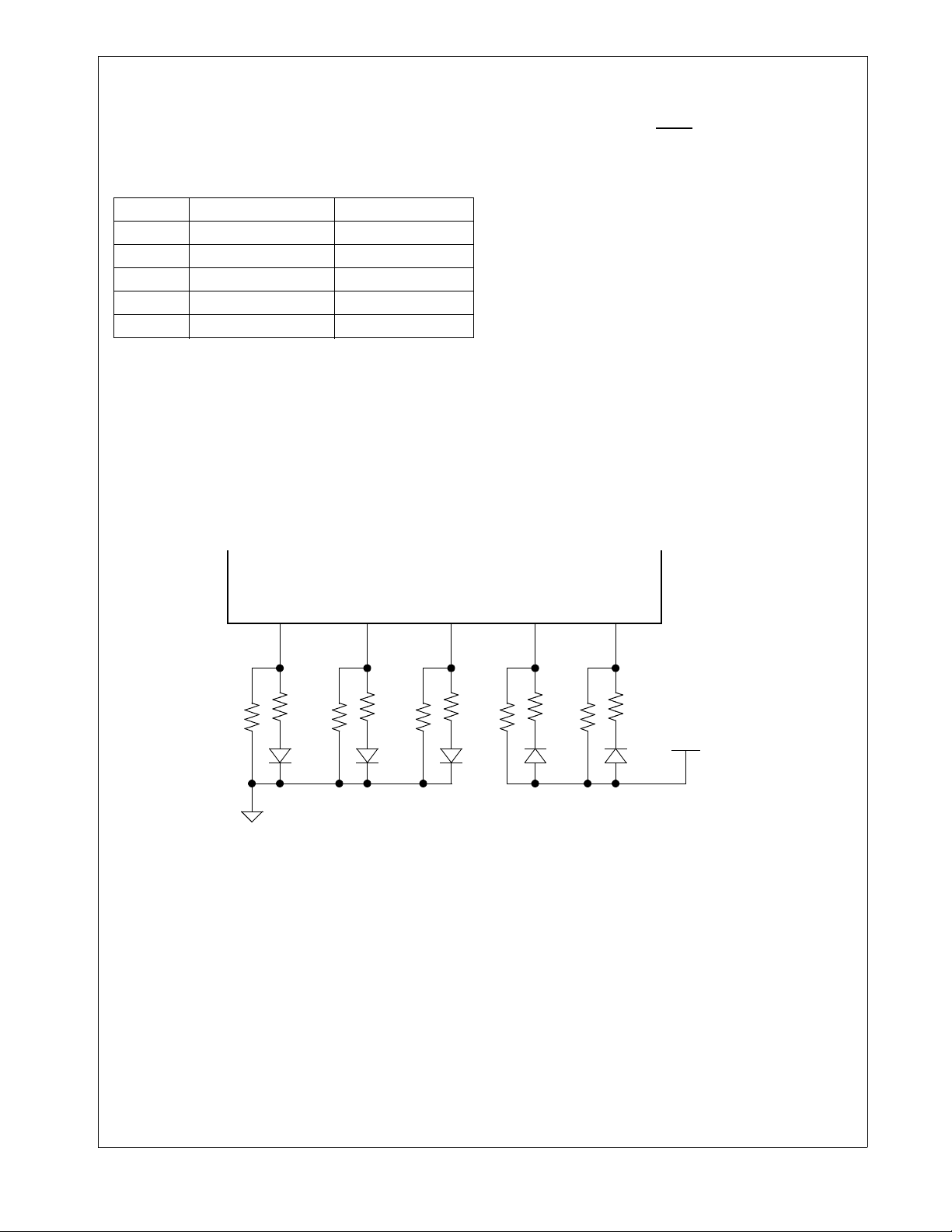

■ LED support: Link, Spe ed, Activi ty, Co llisi on, TX an d RX

■ Supports 125 MHz or 25 MHz reference clock

■ Requires only one 1.8 V and one 3.3 V supply

■ Supports MDIX at 10, 100, and 1000 Mb/s

■ Supports JTAG (IEEE1149.1)

■ Dissipates 1 watt in 10/100 Mb/s mode

■ Programmable Interrupts

■ 208-pin PQFP package

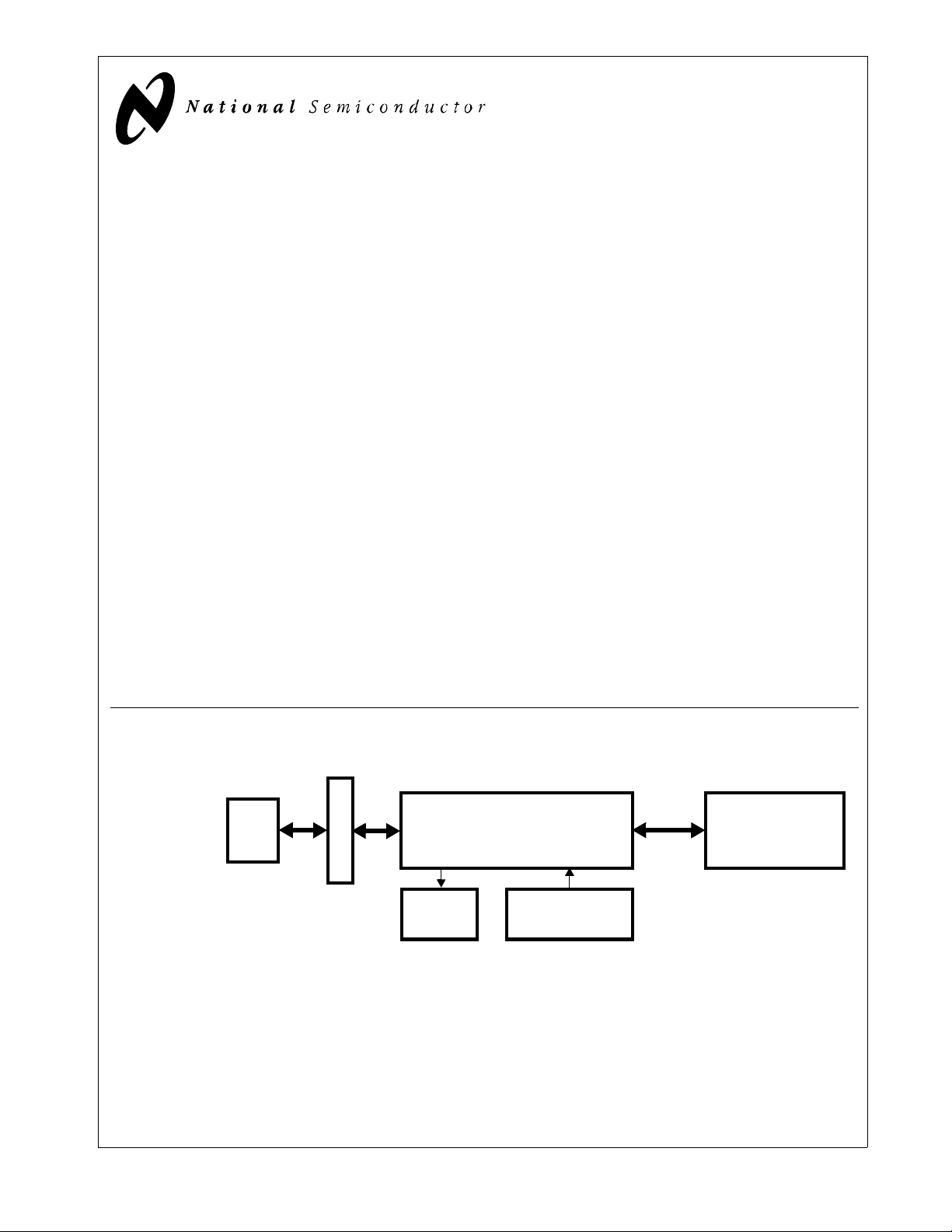

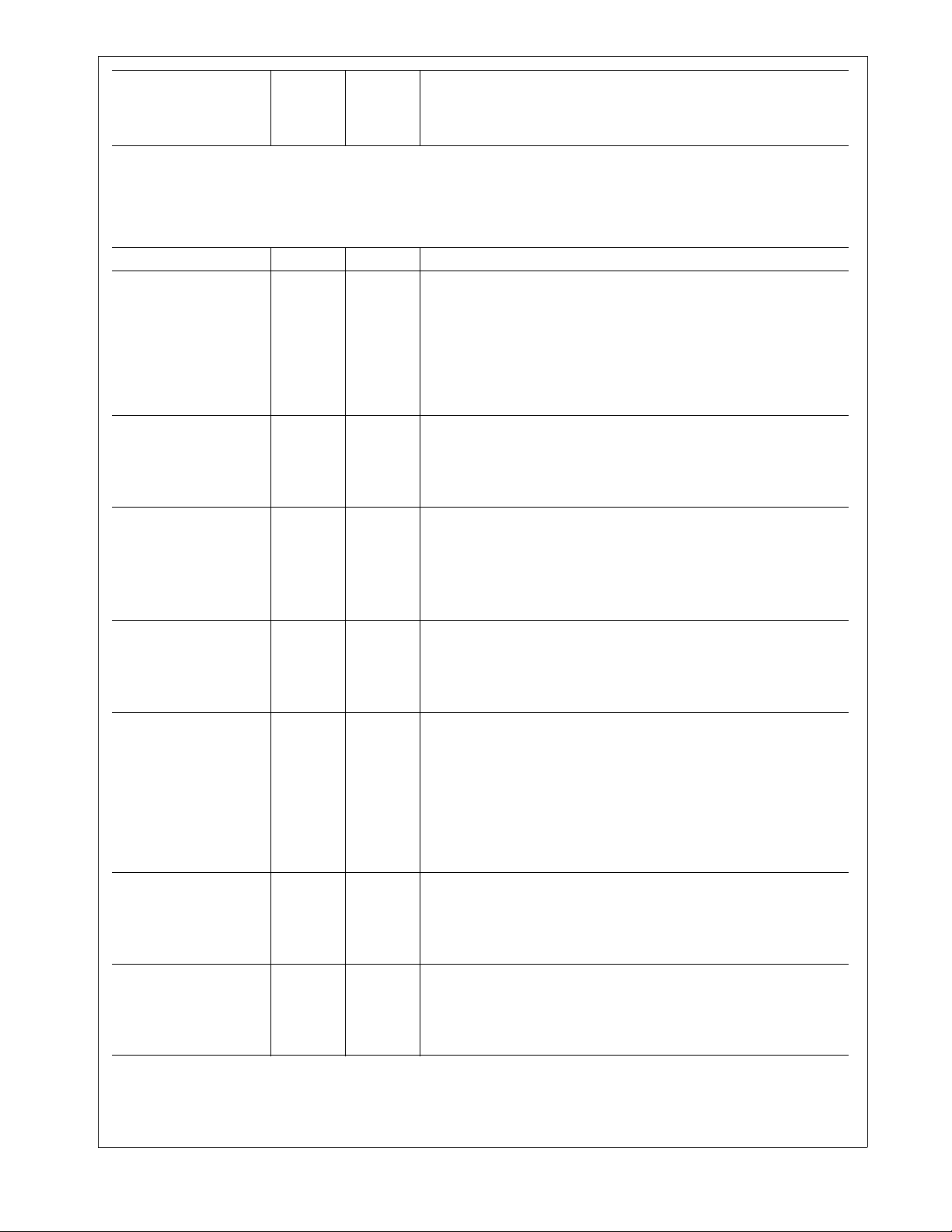

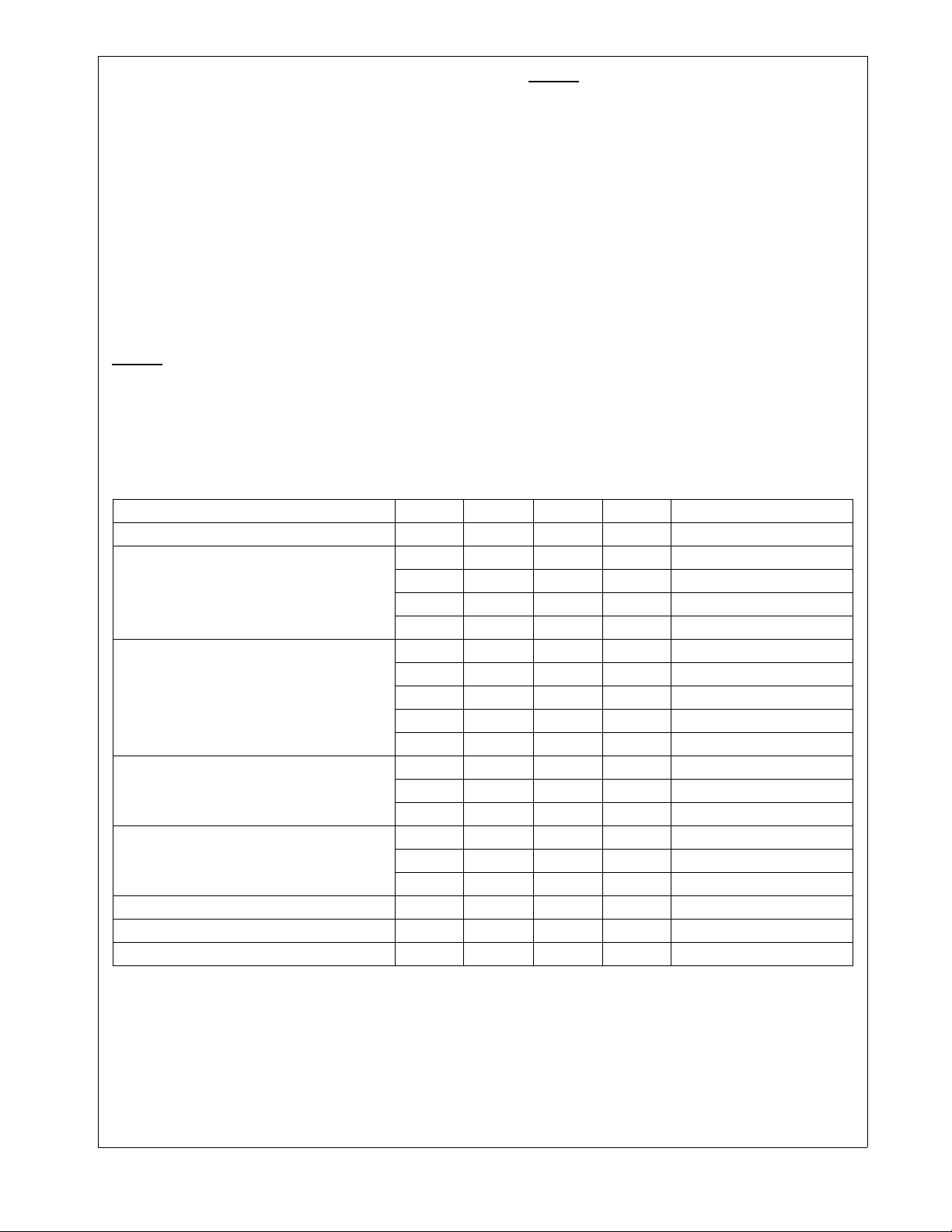

System Diagram

10BASE-T

100BASE-TX

1000BASE-T

PHYTER® is a registered trademark of National Semiconductor Corporation.

© 2001 National Semiconductor Corporation

RJ-45

MAGNETICS

STATUS

LEDs

DP83861

10/100/1000Mb/s

Ethernet Physical Layer

125 MHz or 25 MHz

CLOCK

MII/GMII

DP83820

10/100/1000Mb/s

ETHERNET

MAC

www.national.com

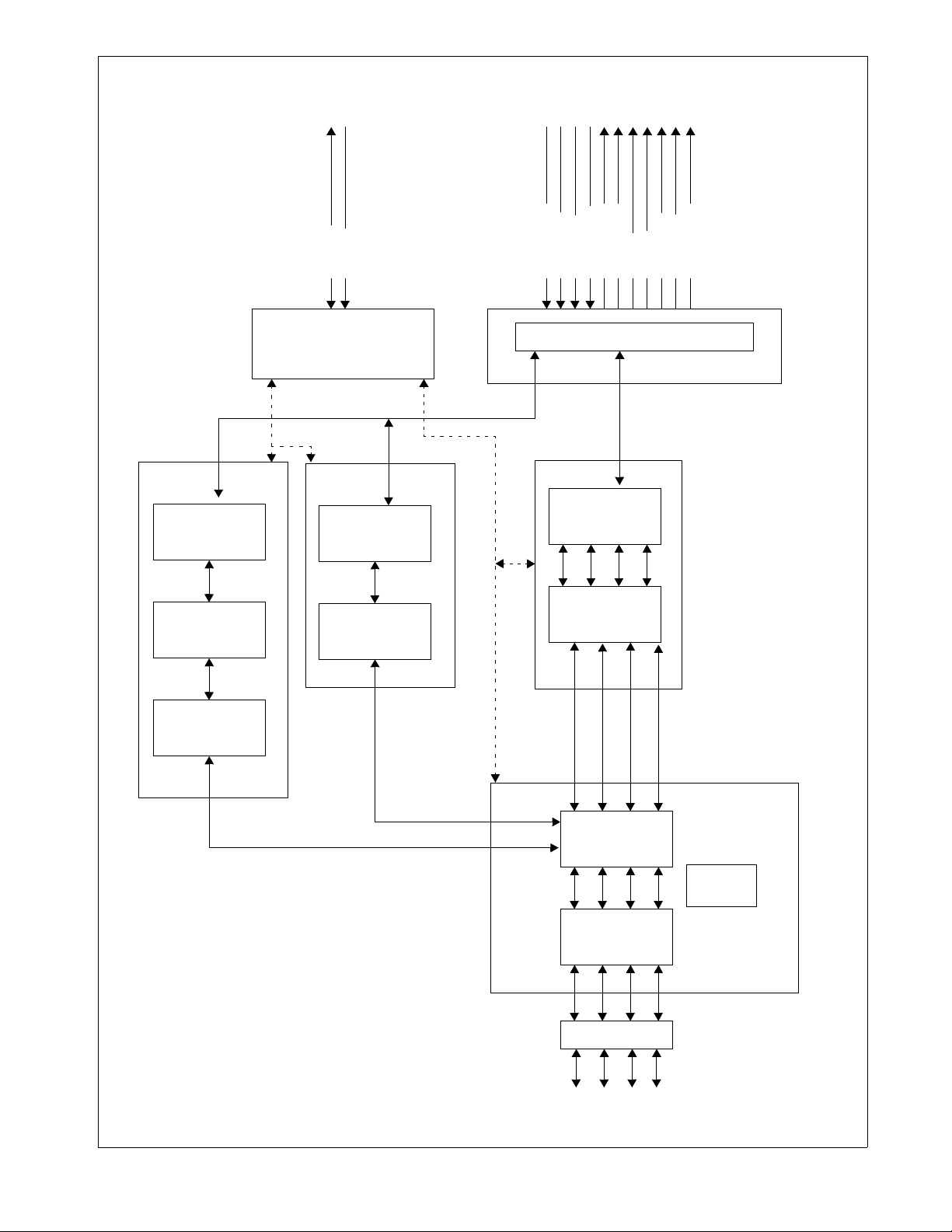

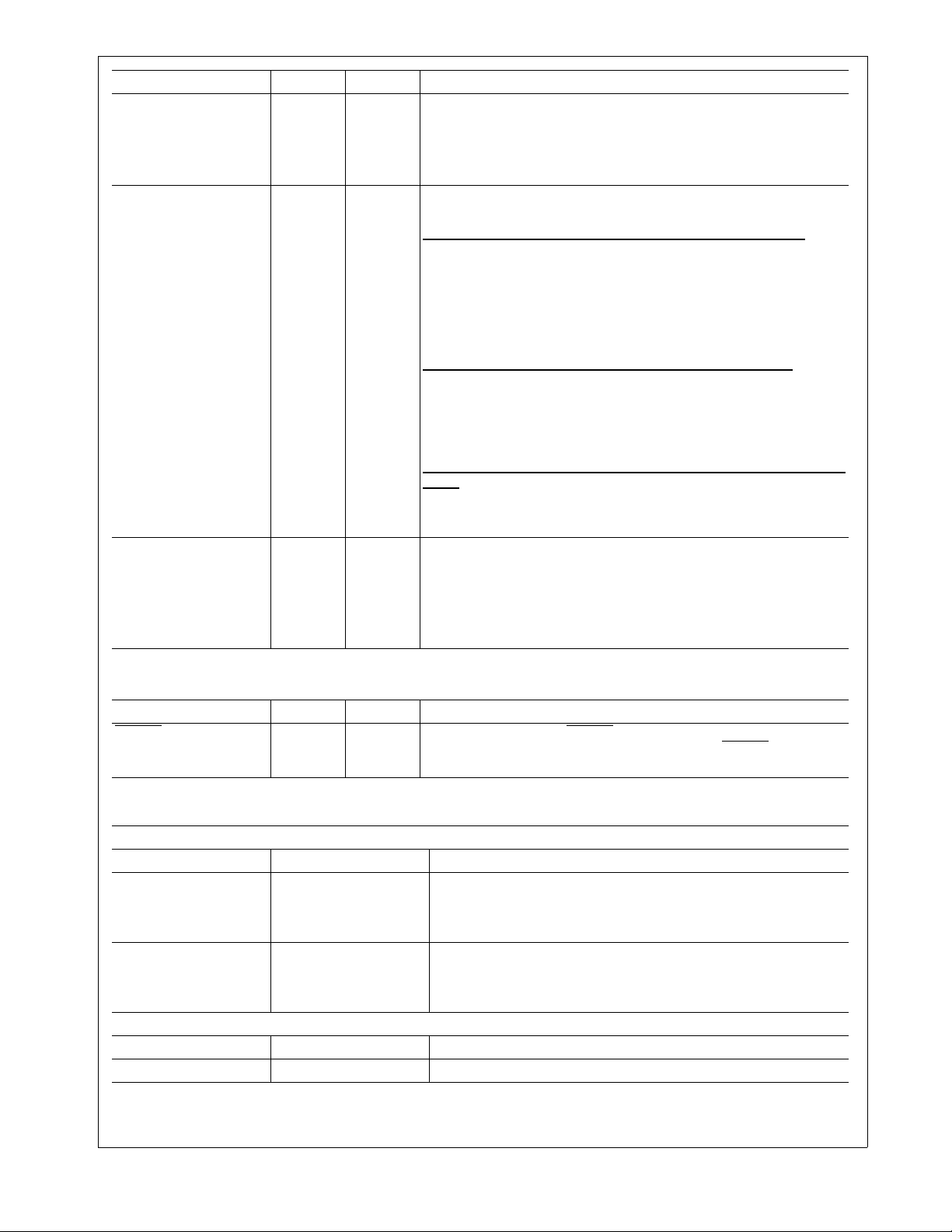

Block Diagram

DP83861

100BASE-TX Block

MII

100BASE-TX

PCS

MGMT INTERFACE

MDIO

MDC

µC MGMT

& PHY CNTRL

10BASE-T Block

MII

10BASE-T

PLS

COMBINED GMII, MII INTERFACE

GTX_CLK

TX_EN

TXD[7:0]

TX_CLK

RX_CLK

COL

CRS

RX_ER

RX_DV

TX_ER

MUX/DMUX

GMIIMII

1000BASE-T Block

GMII

1000BASE-T

PCS

RXD[7:0]

100BASE-TX

PMA

100BASE-TX

PMD

MLT -3

100 Mb/s

10BASE-T

PMA

Manchester

10 Mb/s

1000BASE-T

PMA

DAC/ADC

SUBSYSTEM

DRIVERS/

RECEIVERS

MAGNETICS

PAM-5

PR Shaped

125 Msymbols/s

DAC/ADC

TIMING BLOCK

TIMING

4-pair CAT-5 Cable

2 www.national.com

Table of Contents

1.0 Pin Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5

1.1 MAC Interfac e . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

1.2 TP Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

1.3 JTAG Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . .7

1.4 E2PROM Interface . . . . . . . . . . . . . . . . . . . . . . . . .8

1.5 Clock Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . .8

1.6 LED/Interrupt Interface . . . . . . . . . . . . . . . . . . . . .8

1.7 Device Configuration Interface . . . . . . . . . . . . . . .9

1.8 Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10

1.9 Power And Ground Pins . . . . . . . . . . . . . . . . . . . 10

1.10 Special Connect Pins . . . . . . . . . . . . . . . . . . . . . .11

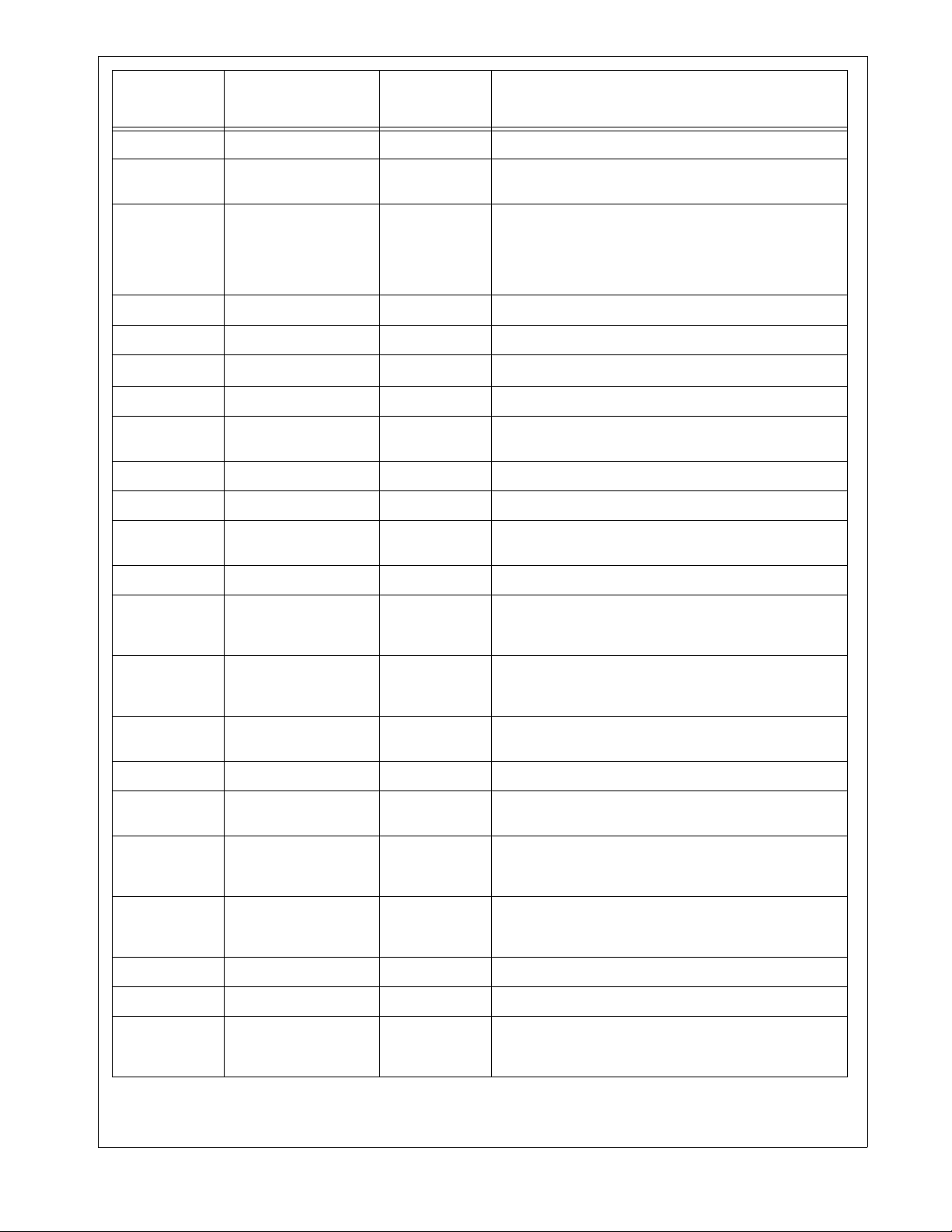

2.0 Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12

2.1 Speed/Duplex Mode Selection . . . . . . . . . . . . . .12

2.2 Manual Mode Configurations . . . . . . . . . . . . . . . .12

2.3 Auto-Negotiation . . . . . . . . . . . . . . . . . . . . . . . . .13

2.4 MII Isolate Mode . . . . . . . . . . . . . . . . . . . . . . . . .15

2.5 Loopback . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

2.6 MII/GMII Interface and Speed of Operation . . . . . 15

2.7 Test Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16

2.8 Automatic MDI / MDI-X Configuration . . . . . . . . .16

2.9 Polarity Correction . . . . . . . . . . . . . . . . . . . . . . . .16

2.10 Firmware Interrupt . . . . . . . . . . . . . . . . . . . . . . . .16

3.0 Design and Layout Guide . . . . . . . . . . . . . . . . . . . . . .17

3.1 Power Supply Filtering . . . . . . . . . . . . . . . . . . . . .17

3.2 Twisted Pair Interface . . . . . . . . . . . . . . . . . . . . . 18

3.3 MAC Interfac e . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

3.4 Clocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

3.5 Strapping Options . . . . . . . . . . . . . . . . . . . . . . . .20

3.6 Unused Pins/Reserved Pins . . . . . . . . . . . . . . . . 20

3.7 Hardware Reset . . . . . . . . . . . . . . . . . . . . . . . . . .21

3.8 Temperature Considerations . . . . . . . . . . . . . . . .21

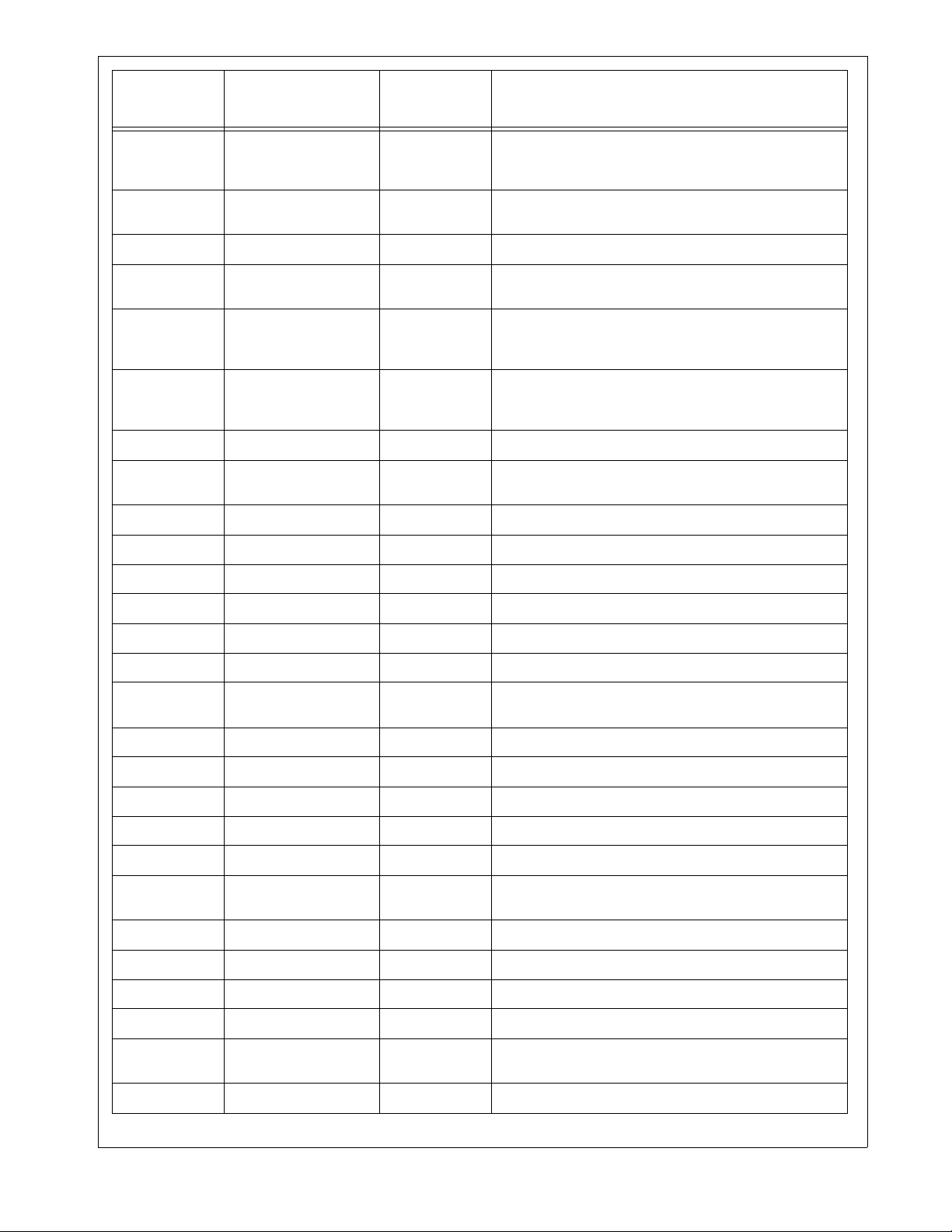

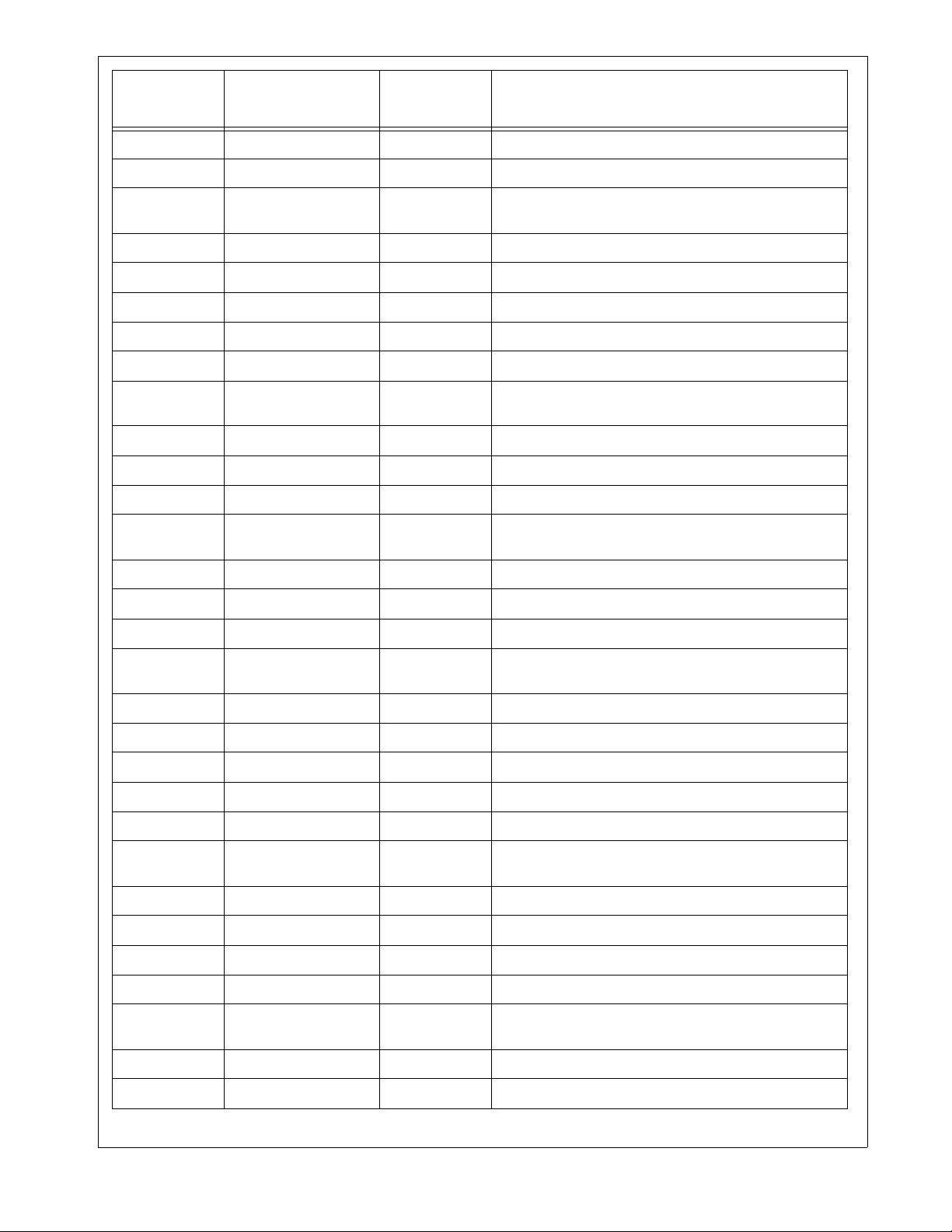

3.9 Pin List and Connections . . . . . . . . . . . . . . . . . . . 21

4.0 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . .34

4.1 1000BASE-T Functional Description . . . . . . . . . .34

4.2 1000BASE-T PCS TX . . . . . . . . . . . . . . . . . . . . .35

4.3 1000BASE-T PMA TX Block . . . . . . . . . . . . . . . .36

4.4 PMA Receiver . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

4.5 1000BASE-T PCS RX . . . . . . . . . . . . . . . . . . . . . 37

4.6 Gigabit MII (GMII) . . . . . . . . . . . . . . . . . . . . . . . .38

4.7 ADC/DAC/Timing Subsystem . . . . . . . . . . . . . . .38

4.8 10BASE-T and 100BASE-TX Transmitter . . . . . .39

4.9 100BASE-TX Receiver . . . . . . . . . . . . . . . . . . . .42

4.10 10BASE-T Functional Description . . . . . . . . . . . .45

4.11 ENDEC Module . . . . . . . . . . . . . . . . . . . . . . . . . .45

4.12 802.3u MII . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .46

4.13 Status Information . . . . . . . . . . . . . . . . . . . . . . . .47

4.0 Register Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

4.1 Register Definitions . . . . . . . . . . . . . . . . . . . . . . . 49

4.2 Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

5.0 Electrical Specifications . . . . . . . . . . . . . . . . . . . . . . . 68

5.1 DC Electrical Specification . . . . . . . . . . . . . . . . . .68

5.2 PGM Clock Timing . . . . . . . . . . . . . . . . . . . . . . .70

5.3 Serial Management Interface Timing . . . . . . . . .70

5.4 1000 Mb/s Timing . . . . . . . . . . . . . . . . . . . . . . . .71

5.5 100 Mb/s Timing . . . . . . . . . . . . . . . . . . . . . . . . .72

5.6 Auto-Negotiation Fast Link Pulse (FLP) Timing . . 75

5.7 Reset Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . .76

5.8 Loopback Timing . . . . . . . . . . . . . . . . . . . . . . . .77

5.9 Isolation Timing . . . . . . . . . . . . . . . . . . . . . . . . . .78

6.0 Test C o nditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

6.1 CMOS Outputs (GMII/MII and LED) . . . . . . . . . .79

6.2 TXD± Outputs (sourcing 100BASE-TX) . . . . . . . .79

6.3 TXD± Outputs (sourcing 1000BASE-T) . . . . . . . .79

6.4 Idd Measurement Conditions . . . . . . . . . . . . . . . .79

6.5 GMII Point-to-Point Test Conditions . . . . . . . . . .79

DP83861

6.6 GMII Setup and Hold Test Conditions . . . . . . . . 79

7.0 User Information: . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

7.1 10Mb/s VOD . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

7.2 Asymmetrical Pause . . . . . . . . . . . . . . . . . . . . . . 82

7.3 Next Page . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

7.4 125 MHz Oscillator Operation with Ref_Sel Floating

83

7.5 MDI/MDIX Operation when in Forced 10 Mb/s and 100MB/s

83

7.6 Receive LED in 10 Mb/s Half Duplex mode . . . . 83

8.0 EN Gig PHYTER Frequently Asked Questions: . . . . 84

8.1 Q1: What is the difference between TX_CLK,

TX_TCLK, and GTX_CLK? 84

8.2 Q2: What happens to the TX_CLK during 1000 Mb/s

operation? Similarly what happens to RXD[4:7] during 10/100 Mb/s operation? 84

8.3 Q3: What happens to the TX_CLK and RX_CLK during Auto-Negotiation and during idles? 84

8.4 Q4: Why doesn’t the EN Gig PHYTER complete

Auto-Negotiation if the link partner is a forced 1000

Mb/s PHY? 84

8.5 Q5: My two EN Gig PHYTERs won’t talk to each other, but they talk to another vendor’s PHY. 84

8.6 Q6: You advise not to use Manual Master/Slave configuration. How come it’s an option? 84

8.7 Q7: How can I write to EN Gig PHYTER expanded

address or RAM locations? Why do I need to write to

these locations? 84

8.8 Q8: What specific addresses and values do I have to

use for each of the functions mentioned in Q7 above?

85

8.9 Q9: How can I do firmware updates? What are some

of the benefits of the firmware updates? 85

8.10 Q10: How long does Auto-Negotiation take? . . . 86

8.11 Q11: I know I have good link, but register 0x01, bit 2

“Link Status” doesn’t contain value = ‘1’ indicating

good link. 86

8.12 Q12: I have forced 100 Mb/s operation but the 100

Mb/s speed LED doesn’t come on. 86

8.13 Q13: Your reference design shows pull-up or pulldown resistors attached to certain pins, which conflict with the pull-up or pull-down information specified in the datasheet? 86

8.14 Q14: What are some other applicable documents?

86

8.15 Q15: How is the maximum junction temperature calculated?

86

8.16 Q16: How do I measure FLP’s? . . . . . . . . . . . . . 86

8.17 Q17: The DP83861 will establish Link in 10 Mb/s and

100Mb/s mode with a Broadcom part, but it will not

establish link in 1000 Mb/s mode. When this happens

the DP83861’s Link led will blink on and off. 86

8.18 Q18: Why isn’t the Interrupt Pin (Pin 208) an Open

Drain Output? 87

9.0 Physical Dimensions . . . . . . . . . . . . . . . . . . . . . . . . . 88

3 www.national.com

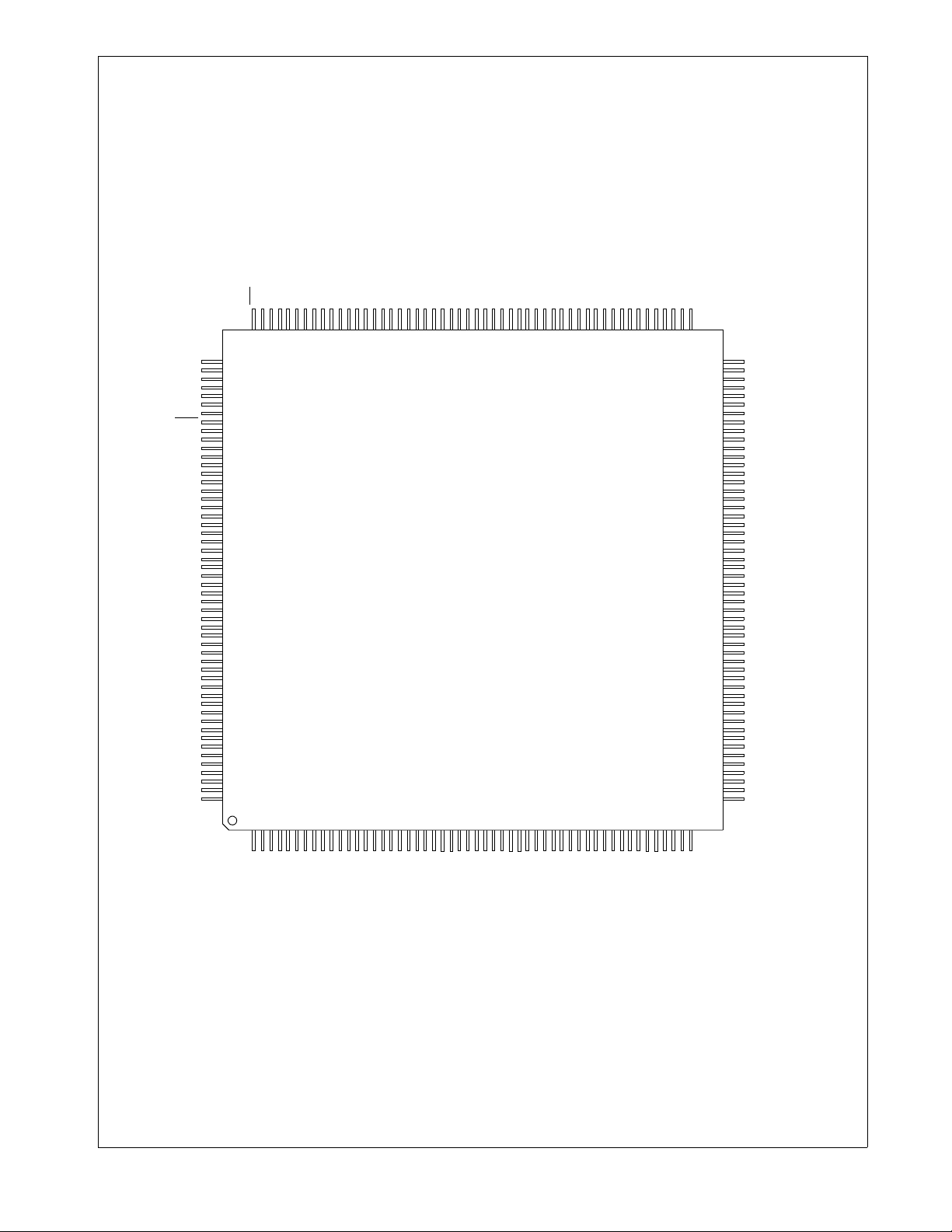

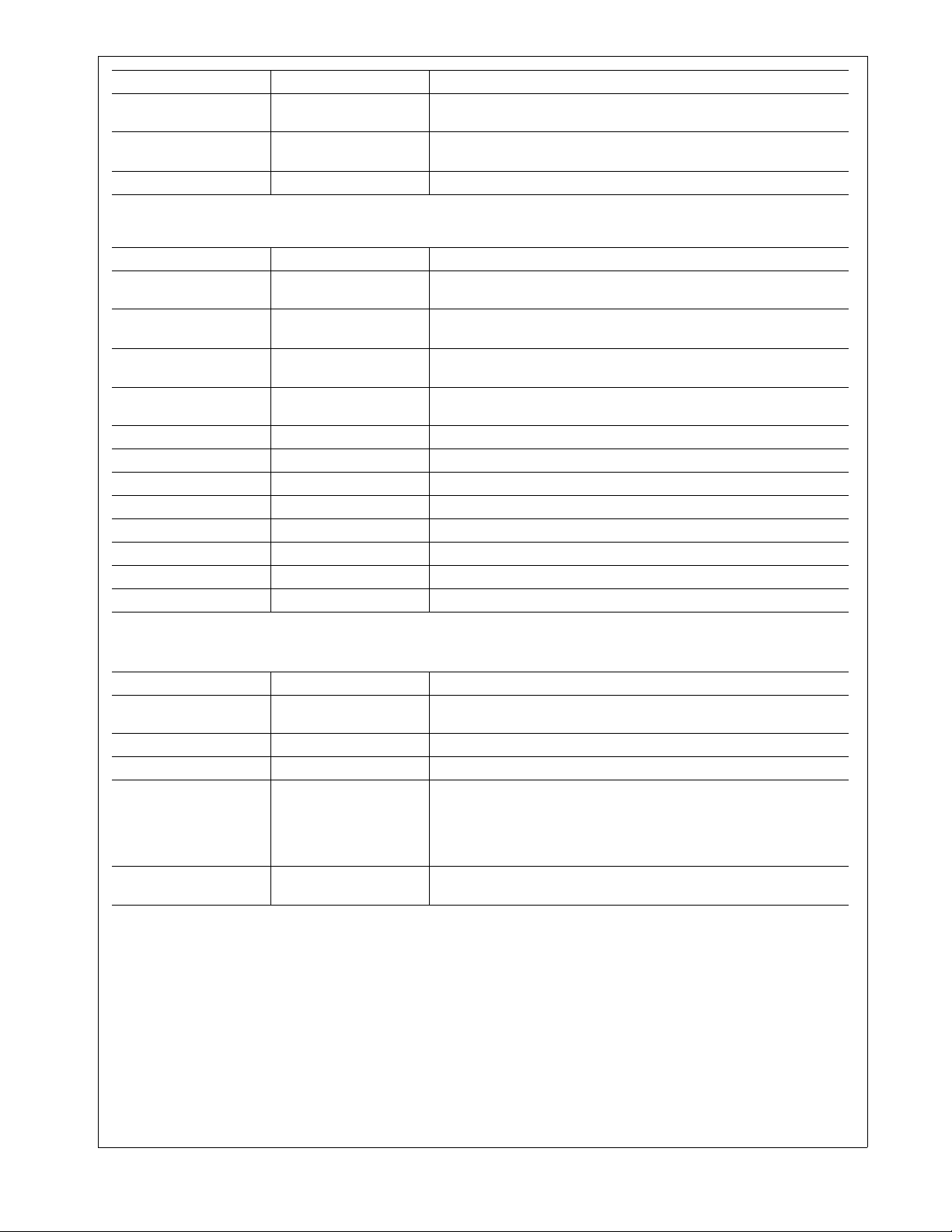

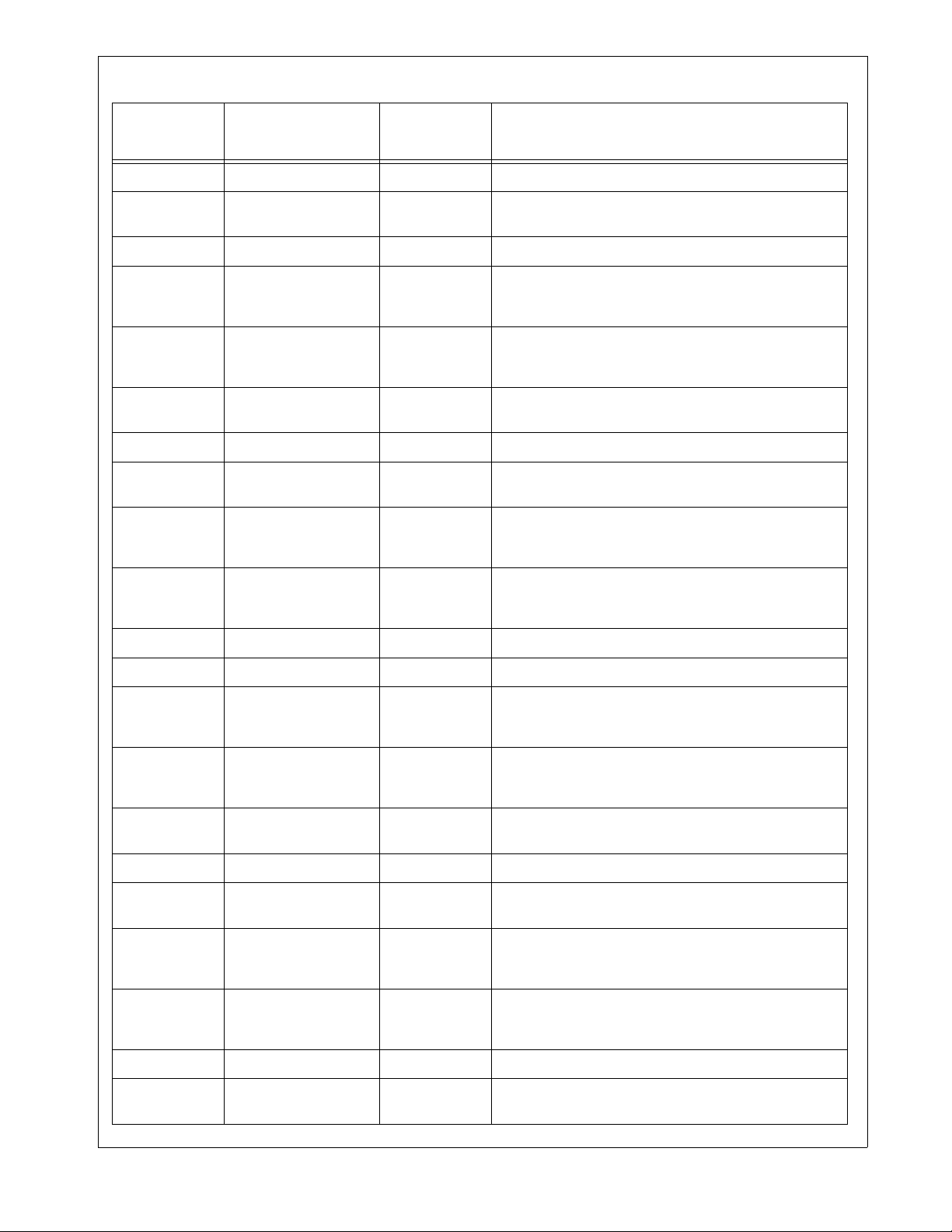

PQFP (VQM) Pin Layout

g

TRST

OSC_VDD

REF_SEL

REF_CLK

OSC_VSS

MDC

MDIO

DP83861

IO_VDD

IO_VSS

GTX_CLK

TXD0

TXD1

TXD2

IO_VDD

IO_VSS

TXD3

TXD4

TXD5

TXD6

CORE_VDD

CORE_VSS

TXD7

TX_EN

TX_ER

IO_VDD

IO_VSS

TX_CLK

CORE_VDD

CORE_VSS

CORE_SUB

RX_CLK

RXD0

RXD1

IO_VDD

IO_VSS

RXD2

RXD3

RXD4

RXD5

IO_VDD

IO_VSS

RXD6

RXD7

RX_DV

RX_ER

CRS

COL

IO_VDD

IO_VSS

RESERVE_FLOAT

RESERVE_FLOAT

SO

CORE_VDD

CORE_VSS

CORE_SUB

Reserved

Reserved

Reserved

Reserved

CORE_VDD

CORE_VSS

CORE_SUB

Reserved

Reserved

Reserved

Reserved

LED_10/

10_ADV/SPEED[1]

LED_100/

100_ADV

CORE_VDD

CORE_VSS

LED_1000/

LED_DUPLEX/

1000FDX_ADV

1000HDX_ADV

Manual_M/S_Advertise

TX_TCLK

AN_EN /

Manual_M/S_Enable

NC_MODE

CORE_VDD

CORE_VSS

CORE_SUB

LED_ACT/

PHYAD_0

LED_COL/

PHYAD_1

LED_LNK/

PHYAD_2

LED_TX/

PHYAD_3

LED_RX/

SPEED[0]/PORT_TYPE/INT

PHYAD_4

TDO

TMS

TCK

RESET

IO_VDD

IO_VSS

IO_VDD

IO_VSS

TEST

IO_VDD

IO_VSS

SDA

SCL

IO_VDD

IO_VSS

IO_VDD

IO_VSS

TEST

119

118

156

155

154

153

152

151

150

149

148

147

146

145

144

143

142

141

140

139

138

137

136

135

134

133

132

131

130

129

128

127

126

125

124

123

157

TDI

158

159

160

161

162

163

164

165

166

167

168

169

170

171

172

173

174

175

176

177

178

179

180

181

182

183

184

185

186

187

188

189

190

191

192

193

194

195

196

197

198

199

200

201

202

203

204

205

206

207

208

DP83861VQM-3

EN Gi

PHYTER

117

122

121

120

111

116

115

114

113

112

110

109

108

107

106

105

SI

104

Reserved

103

IO_VDD

102

IO_VSS

101

Reserved

100

Reserved

99

CORE_VDD

98

CORE_VSS

97

CORE_SUB

96

Reserved

95

Reserved

94

IO_VDD

93

IO_VSS

92

Reserved

91

Reserved

90

Reserved

89

RESERVE_FLOAT

88

IO_VDD

87

IO_VSS

86

RESERVE_FLOAT

85

RESERVE_FLOAT

84

CORE_VDD

83

CORE_VSS

82

RRESERVE_FLOAT

81

RESERVE_FLOAT

80

IO_VDD

79

IO_VSS

78

RESERVE_FLOAT

77

RESERVE_FLOAT

76

RESERVE_FLOAT

75

RESERVE_FLOAT

74

IO_VDD

73

IO_VSS

72

RESERVE_FLOAT

71

RESERVE_FLOAT

70

CORE_VDD

69

CORE_VSS

68

CORE_SUB

67

RESERVE_FLOAT

66

RESERVE_FLOAT

65

IO_VDD

64

IO_VSS

63

Reserved

62

Reserved

61

Reserved

60

Reserved

59

IO_VDD

58

IO_VSS

57

RESERVE_FLOAT

56

RESERVE_FLOAT

55

RESERVE_FLOAT

54

RESERVE_FLOAT

53

123456789101112131415161718192021222324252627282930313233343536373839404142434445464748495051

TXDA-

RA_ASUB

RA_AVDD

RA_AGND

RXDA+

RXDA-

RA_AVDD

TXDA+

RA_AGND

CDA_AVDD

TXDB-

TXDB+

CDA_AGND

CDB_AGND

RXDB-

RXDB+

RB_AVDD

RB_AGND

RB_AGND

CDB_AVDD

pin names are strap options (e. g.

Bold

RB_AVDD

RB_ASUB

BG_AVDD

BG_REF

BG_AGND

BG_SUB

PGM_AVDD

RC_ASUB

SHR_VDD

SHR_GND

PGM_AGND

RC_AVDD

RC_AGND

AN_EN)

RXDC+

RXDC-

RC_AVDD

TXDC+

RC_AGND

CDC_AVDD

TXDC-

CDC_AGND

CDD_AGND

TXDD-

TXDD+

RD_AGND

CDD_AVDD

RD_AVDD

RXDD-

RXDD+

RD_AGND

208 Lead Plastic Quad Flat Pack

Order Number DP83861VQM-3

NS Package VQM-208A

4 www.national.com

52

RD_AVDD

RD_ASUB

1.0 Pin Descriptions

The DP83861 pins are c lassifi ed into the follow ing i nterface

categories (each is described in the sections that follow):

— MAC Interface

— TP Interface

— JTAG Interface

2

PROM Interface

—E

— Clock Interface

— LED Interface

— Device Configuration / Strapping Options

—Reset

— Power and Ground Pins

— Special Connect Pins

Note: Strapping pin option (

BOLD

) (e.g.

AN_EN

)

1.1 MAC Interface

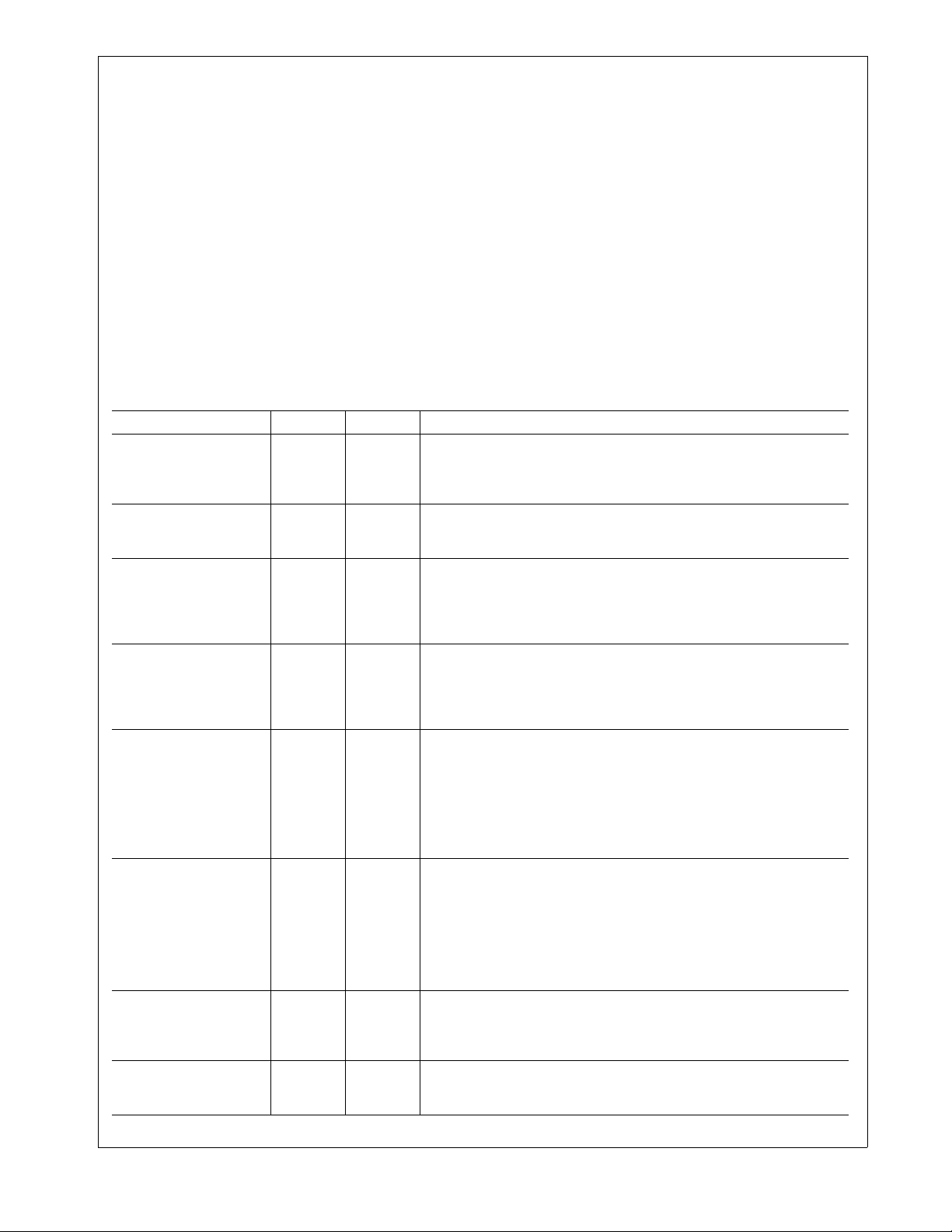

Signal Name Type Pin # Description

MDC I 151

MDIO I/O 150

CRS O 111

COL O 110

TX_CLK O 130

TXD0

TXD1

TXD2

TXD3

TXD4

TXD5

TXD6

TXD7

TX_EN I 134

GTX_CLK I 147

I 146

145

144

141

140

139

138

135

MANAGEMENT DATA CLOCK:

management data input/output serial interface which may be asynchronous to transmit and receive clocks. The maximum clock rate is

2.5 MHz with no minimum clock rate.

MANAGEMENT DATA I/O:

tion/data signal that may be sourced by the station management entity or the PHY. This pin requires a 1.5 kΩ pullup resistor.

CARRIER SENSE:

due to receive or transmit activity in Half Duplex mode. This signal is

not defined (LOW) for 1000BASE-T Full Duplex mode. For

1000BASE-T, 100BASE-TX and 10BASE-T Full Duplex operation

CRS is asserted only for receive activity.

COLLISION DETECT:

sion condition (as sertion of CRS due to simul taneous tr ansmit and re ceive activi ty) in Half Duplex mo des. This signal is not sync hronous

to either MII clock (G TX_CLK, TX_CLK or R X_CLK). This signal is not

defined (LOW) for Full Duplex modes.

TRANSMIT CLOCK (10 Mb/s and 100 Mb/s):

nal generated from REF_CLK and driven by the PHY during 10Mb/s

and 100 Mb/s operation. It is used on the MII to cloc k all MII Tra nsmi t

(data, error) signals into the PHY.

The Transmit Clock frequency is constant and the frequency is

2.5 MHz for 10Mb/s mode and 25 MHz for 100Mb/s mode.

TX_CLK should not be confused with the TX_TCLK signal.

TRANSMIT DATA:

during 10 Mb/s and 100 Mb/s MII mode and 8-bit data (TXD[7:0]) in

1000 Mb/s GMII mode. They are synchrono us to the Transmi t Clocks

(TX_CLK, GTX_CLK. Transmit data is input enabled by TX_EN for all

modes all sourced by the controller.

TRANSMIT ENABLE:

ing transmission of the data present on the TXD lines (nibble data for

10 Mb/s and 100 Mb/s mode and 8-bit data for 1000 Mb/s GMII

mode.)

GMII-TRANSMIT CLOCK:

from the upper level MAC to th e PHY. Nominal frequenc y of 125 MHz,

derived in t he MAC from its 125 MHz reference clock.

Type: I Inputs

Type: O Output

Type: O_Z Tristate Output

Type: I/O_Z Tristate Input_Output

Type: S Strapping Pin

Type: PU Pull-up

Type: PD Pull-down

Asserted high to indicate the presence of carrier

Asserted high to indicate detection of a colli-

These signals carry 4B data nibbles (TXD[3:0])

Active high input driven by the MAC request-

DP83861

Synchronous clock to the MDIO

Bi-directional management instruc-

Continuous clock sig-

This continuous clock signal is sourced

5 www.national.com

g

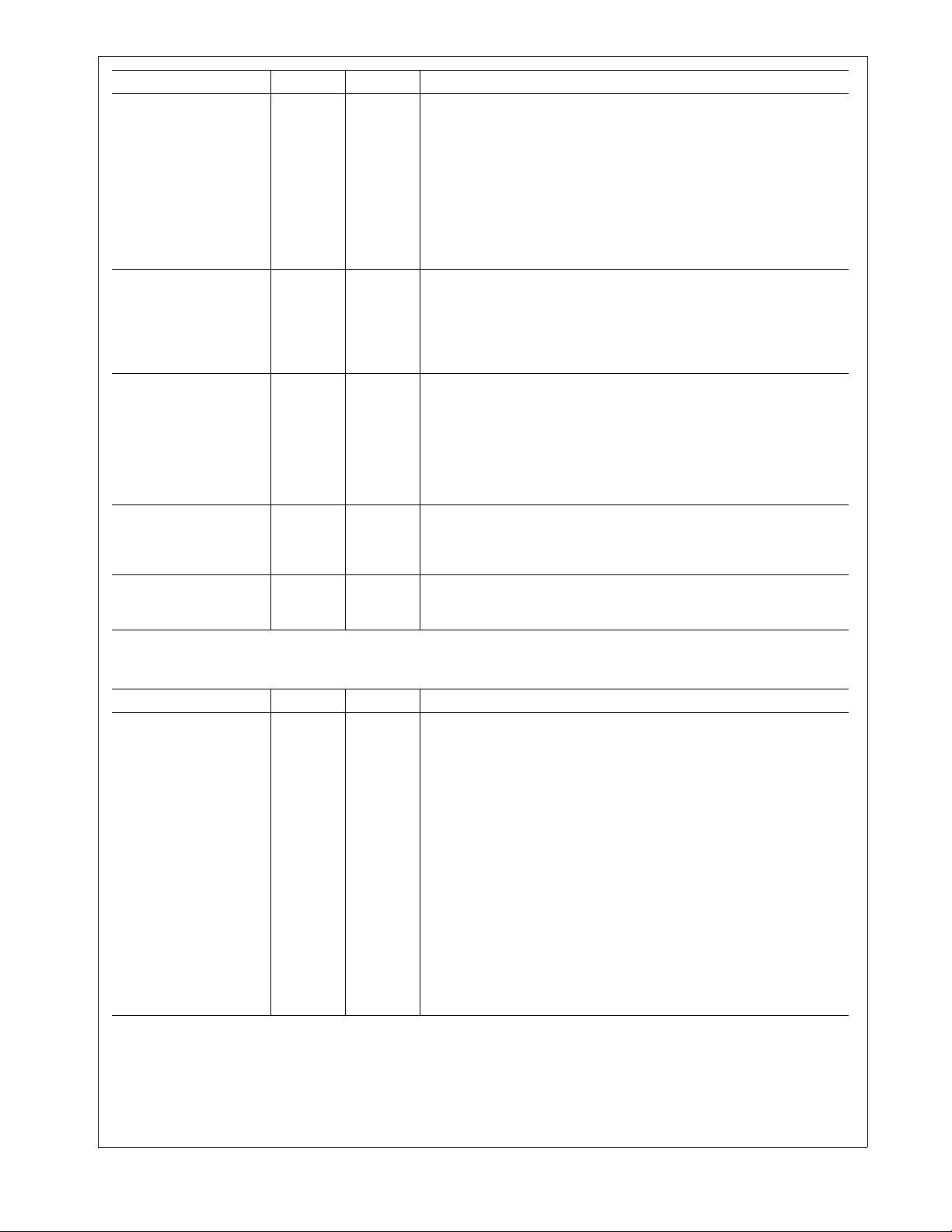

nal Name Type Pin # Description

Si

TX_ER I 133

RX_CLK O 126

RXD0

RXD1

RXD2

RXD3

RXD4

RXD5

RXD6

RXD7

RX_ER O 112

RX_DV O 113

O 125

124

121

120

119

118

115

114

TRANSMIT ERROR:

or 1000 Mb/s GMII mode. Thi s forces the PHY to transmit invalid symbols. The TX_ER si gnal mus t be synchro nous to the Tran smit C loc ks

(TX_CLK and GTX_CLK).

In 4B nibble mode, a sserti on of Tran smit Error by t he control ler ca uses the PHY to issue invalid sy mbols follow ed by Halt ( H) symbols un til

deassertion occurs.

In 1000 Mb/s GMII mode, assertion c auses the PHY to emit one or

more code-groups that are not valid data or delimiter set in the transmitted frame.

RECEIVE CLOCK:

ent modes of operation:

2.5 MHz nibble clock in 10 Mb/s MII mode.

25 MHz nibble clock in 100 Mb/s MII mode.

125 MHz byte clock in 1000 Mb/s GMII mode.

RECEIVE DATA:

during 10Mb/s and 100 Mb/s MII mode and 8-bit data (RXD[7:0]) in

1000 Mb/s GM II mode . They are synchro nous to the Recei ve Cloc k

(RX_CLK). Receive data is dr iven by the PHY to the controll er, and is

strobed by Receive Data Va lid (RX_D V) which is also sourc ed by the

PHY.

RECEIVE ERROR:

this active hi gh outp ut ind icate s that the PHY ha s det ect ed a Re ceive

Error. The RX_ER signal must be synchronous with the Receive

Clock (RX_CLK).

RECEIVE DATA VALID:

present on the corresponding RXD[3:0] for 10 Mb/s or 100 Mb/s MII

mode and RXD[7:0] in 1000 Mb/s GMII mode.

Active high in pu t du r ing 100 Mb /s ni bb l e mo de

Provides th e recove red rec eive clo cks for differ -

These signals carry 4-bit data nibbles (RXD[3:0])

In 100 Mb/s MII mod e and 1000 Mb/s GMII m ode

Asserted high to indicate that valid data is

DP83861

1.2 TP Interface

Signal Name Type PIn # Description

TXDA+

TXDATXDBTXDB+

TXDC+

TXDCTXDDTXDD+

O9

10

13

14

39

40

43

44

TRANSMIT DATA:

CAT-5 cable through a single common magnetics transformer. The

Transmit (TXD) and Receive (RXD) Twisted Pair pins carry bit-serial

data at 125 MHz baud rate. These differential outputs are configurable to either 100 BASE-T, 100BASE-TX or 1000BASE-T signalling:

10BASE-T: Transmission of MANCHESTER encoded signals. The

10BASE-T signal does not meet IEEE transmit output voltages. See

Sectio n 7.1.

100BASE-TX: Transmission of 3-level MLT-3 data.

1000BASE-T: Transmission of 17 -level PAM-5 with PR-shapi ng data.

The DP83861 will a utomat icall y conf igure th e co mmon driv er outp uts

for the proper signal type as a result of either forced configuration or

Auto-Negotiation.

NOTE:

TXDB+ and TXDB- are active. (See DP83861 Datas heet for automat ic crossover configuration.)

The TP Interface connects the DP83861 to the

During 10/100 Mb/s operation only TXDA+ and TXDA- or

6 www.national.com

g

nal Name Type PIn # Description

Si

RXDA+

RXDARXDBRXDB+

RXDC+

RXDCRXDDRXDD+

I4

18

19

34

35

48

49

RECEIVE DATA:

5

NOTE:

RXDA+ and RXDA- are active (See DP83 861 Datas heet for a utomatic crossover configuration.)

Differential receive signals.

During 10/100 Mb/s operation only RXDB+ and RXDB- or

1.3 JTAG Interface

Signal Name Type PIn # Description

TRST

TDI I 157

TDO O 158

TMS I 159

TCK I 163

I 156

TEST RESET:

for asynchronous res et of the Tap Controller. This reset h as n o effect

on the device registers.

This pin should be tied low during regular chip operation.

TEST DATA INPUT:

scanned into the device via TDI.

This pin should be tied low during regular chip operation.

TEST DATA OUTPUT:

recent test results are scanned out of the device via TDO.

This pin can be left floating if not used.

TEST MODE SELECT:

pin sequences the Tap Controller (16-state FSM) to select the desired

test instruction.

This pin should be tied low during regular chip operation.

TEST CLK:

all test logic input and output controlled by the testing entity.

This pin should be tied low during regular chip operation.

IEEE 1149.1 Test Reset pin, active lo w reset provides

IEEE 1149.1 Test Data Input pin, test data is

IEEE 1149.1 Test Data Output pin, the most

IEEE 1149.1 Test Mode Select pin, the TMS

IEEE 1149.1 Test Clock input, primary clock source for

DP83861

7 www.national.com

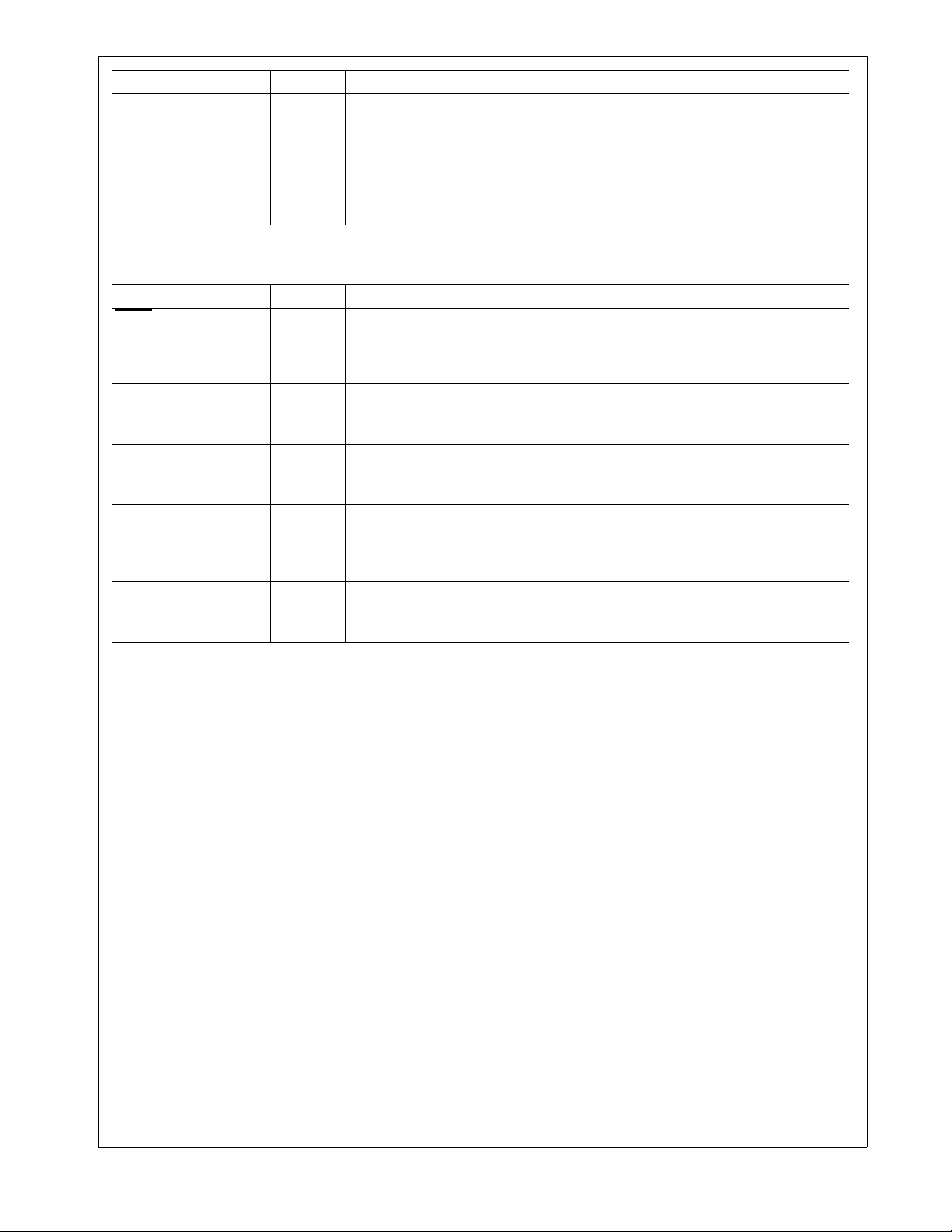

1.4 E2PROM Interface

p

Signal Name Type PIn # Description

SDA I/O, PU 189

SCL I/O, PD 190

Serial Data:

2

PROM Usage Guide” on how to use this interface. This pin should

E

be left floating if the E

SERIAL CLOCK:

E2PROM Usage Guide” on how to use this interface. This pin should

be left floating if the E

See application note “DP83861 EN Gig PHYTER

2

PROM interface is not used.

See application note “DP83861 EN Gig PHYTER

2

PROM interface is not used.

1.5 Clock Interface

Signal Name Type Pin # Description

REF_CLK I 153

REF_SEL I 154

CLOCK INPUT:

ance and less than 200 ps of jitter) See Section 3.4.

Clock Select:

REF_CLK when pulled directly or through a 2 KΩ resistor to 3.3V supply. When pulled low directly or throu gh a 2KΩ resistor to ground enables a 25 MHz clock source. This pin should never be floated.

125 MHz or 25 MHz (both require +/-50ppm toler-

This pin enables the use o f a 12 5 MHz cl ock sou rce to

DP83861

1.6 LED/Interru

Signal Name Type PIn # Description

LED_RX I/O, S, PD 207

LED_TX I/O, S, PD 205

LED_LNK I/O, S, PD 204

LED_DUPLEX I/O, S, PD 185

LED_COL I/O, S, PD 201

LED_ACT I/O, S, PU 200

LED_10 I/O, S, PD 180

LED_100 I/O, S, PU 181

LED_1000 I/O, S, PU 184

t Interface

RECEIVE ACTIVITY LED:

PHY is receiving.

TRANSMIT ACTIVITY LED:

the PHY is transmitting.

GOOD LINK LED STATUS:

ria for good link are:

10BASE-T: Link is established by detecting Normal Link Pulses sep-

arated by 16 ms or by packet data received.

100BASE-T: Link is establishe d as a res ult o f an in put rece iv e ampli-

tude compliant with TP-PM D specifications which will re sult in internal

generation of Signal Detect. LED_LNK will assert after the internal

Signal Detect has remained asserted for a minimum of 500 µs.

LED_LNK will de-assert immediately following the de-assertion of the

internal Signal Detect.

1000BASE-T: Link is established as a result of training, Auto-Negotiation completed, valid 1000BASE-T link established and reliable reception of signals transmitted from a remote PHY is established.

DUPLEX LED STATUS:

mode of operation, else Half Duplex operation.

COLLISION LED STATUS:

collision conditi on (simultaneou s transmit and recei ve activity whil e in

Half Duplex mode).

TX/RX ACTIVITY LED STATUS:

activity.

10 Mb/s SPEED LED:

tion is 10 Mb/s.

100 Mb/s SPEED LED:

ation is 100 Mb/s.

1000 Mb/s SPEED LED:

eration is 1000 Mb/s.

1

If the LED is on, it indicates Full Duplex

If LED is on, then the current speed of opera-

If LED is on, then the current speed of oper-

1

If LED is on, then the current speed of op-

1

The Receive LED output indicates that the

The Transmit LED output indic ates t hat

Indicates status for Good Link the crite-

Indicates that the PHY has detected a

Indicates either tr ansmit o r recei ve

8 www.national.com

DP83861

g

INT I/O, S, PD 208

1. Each of the Speed LEDs (LED_10, LED_100, LED_1000) is AND’ed with good link LEDs. They will only come

on when the PHY has established good link at the speed indicated.

INTERRUPT:

interrupt function is enabled in the extended register set. This pin is

not an Open Drain Output and can not be wired OR to other pins.

See Section 2.10

Generates a interrupt upon PHY status changes. The

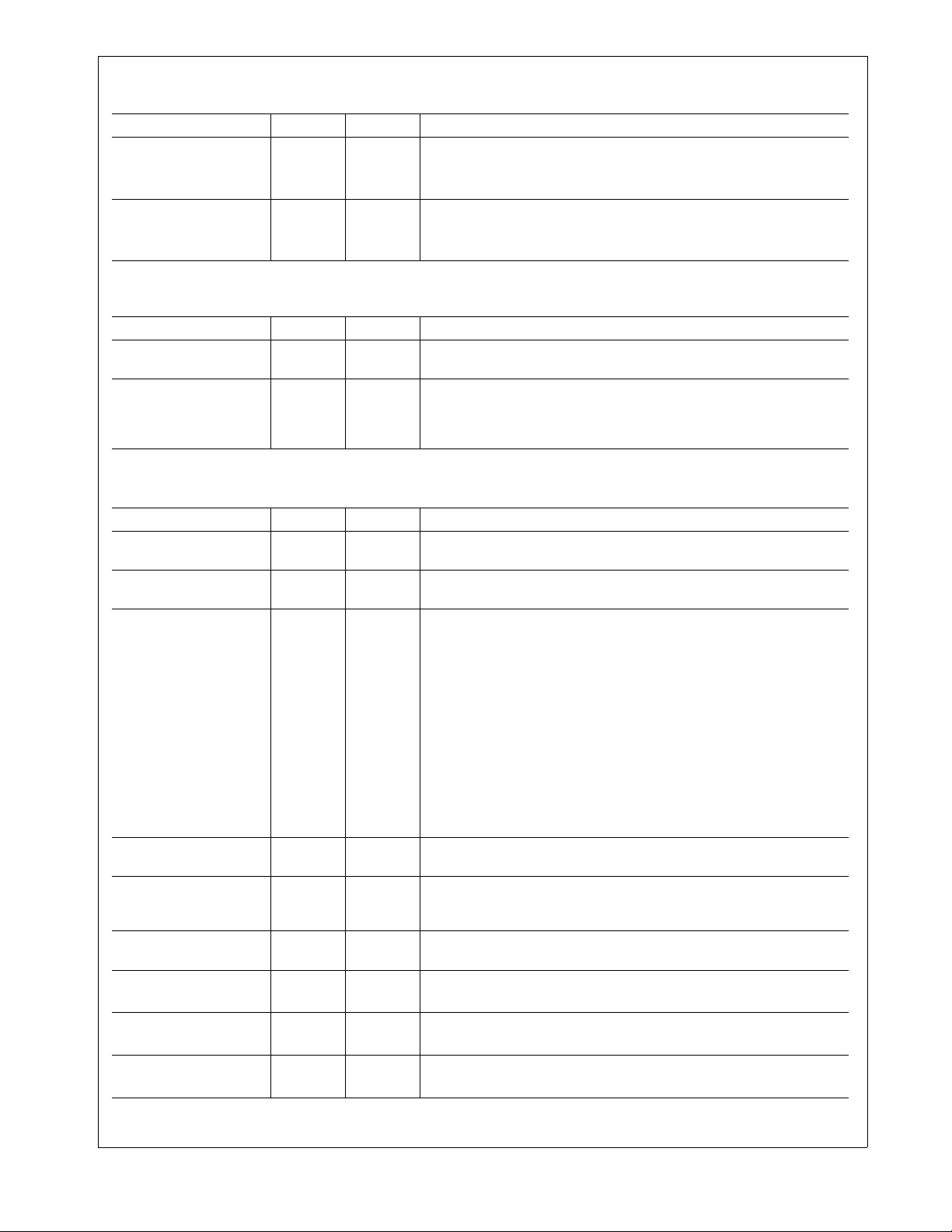

1.7 Device Configuration Interface

nal Name Type Pin # Description

Si

AN_EN

TX_TCLK

MANUAL_M/S_Enable

Manual M/S Advertise

1000FDX_ADV

LED_DUPLEX

1000HDX_ADV

100_ADV

10_ADV

I/O, S, PU 192

I/O, S, PD 195

I/O, S, PD 191

I, S, PU 184

I/O, S, PD 185

I/O, S, PU 181

I/O, S, PD 180

AUTO-NEGOTIATION ENABLE:

tion Enable bit (register 0 bit-12).

‘1’ Enables Auto-Negotiation

‘0’ Disables Auto-Negotiation

TX_TCLK:

scribed by IEEE 802.3ab specification. TX_TCLK should not be confused with the TX_CLK signal.

MANUAL MASTER/SLAVE ENABLE:

Master/Slave Configuration Enable bit (register 9 bit-12). The

DP83861 still goes through the Auto-Negotiation process.

‘1’ Enables manual Master/Slave Configuration

‘0’ Disables manual Master/Slave Configuration

Manual MASTER/ SLAVE CONFIGURATION VALUE:

value of Master/Slave Advertise bit (register 9 bit 11). DP83861 still

goes through the Auto-Negotiation process.

‘1’ Configures PHY to Master during Master/Slave negotiation

‘0’ Configures PHY to Slave during Master/Slave negotiation.

This bit is only used if the Manual_M/S_Configuration is enabled.

AUTO_NEG 1000 FDX ADVERTISE:

power/on reset determines the mode of operation advertised during

Auto-Negotiation.

‘1’ Advertises 1000 Mb/s Full Duplex capability

‘0’ Does not advertise 1000 Mb/s Full Duplex capability

DUPLEX MODE SELECT/ 1000 Mb/s HALF DUPLEX ADVERTISE:

This strap option has two functions depending on whether Auto-Negotiation is enabled or not:

Auto-Negotiation disabled:

‘1’ straps on Full Duplex mode of operation

‘0’ straps on Half Duplex mode of operation.

Auto-Negotiation enabled:

‘1’ Advertises 1000 Mb/s Half Duplex capability

‘0’ Does not advertise 1000 Mb/s Half Duplex capability.

100 Mb/s FULL/HALF DUPLEX ADVERTISE:

determines if 100 Mb/s Full/Half Duplex capability will be advertised

during Auto-Negotiation.

‘1’ Advertises both Full and Half Duplex capability

‘0’ Advertises neither 100 Mb/s capability

10 Mb/s FULL/HALF DUPLEX ADVERTISE:

determine s if 10 Mb/s Full/Half Duplex capability will be advertised

during Auto-Negotiation.

‘1’ Advertises both Full and Half Duplex capability

‘0’ Advertises neither 10 Mb/s capability

Output used to measure jitter during Test Mode 3 as de-

Input to set value of Auto-Negotia-

Input to set value of manual

The value strapped during

This strap option pin

This strap option pin

Input to set

9 www.national.com

g

nal Name Type Pin # Description

g

g

Si

NC MODE

SPEED[1]/10_ADV

SPEED[0]/PORT_TYPE

PHYAD_0

PHYAD_1

PHYAD_2

PHYAD_3

PHYAD_4

I/O, S, PD 196

I/O, S,PD

I/O, S, PD

I/O, S, PU

I/O, S, PD

I/O, S, PD

I/O, S, PD

I/O, S, PD

180

208

200

201

204

205

207

NON-COMPLIANT MODE:

certain NON-IEEE compliant 1000BASE-T transceivers. See

Section 8.17.

‘1’ Enables Non-Compliant mod e

‘0’ Disables Non-Compliant mode

SPEED SELECT:

depending on whether Auto-Negotiation is enabled or not.

SPEED[1:0] Auto-Negotiation disabled (Forced Speed mode:)

00 10BASE-T

01 100BASE-TX

10 1000BASE-T

11 Reserved

SPEED[1] Auto-Negotiation enabled (Advertised capability:)

‘1’ Advertises 10 M b/s c ap abi lity (Both Full Duplex and Half Dup lex .)

‘0’ Does not advertise 10 Mb/s capability. (Neither Full Duplex nor

Half Duplex is advertised.)

SPEED[0]/PORT_TYPE Auto-Negotiatio n enabled (Ad vertised capability:)

‘1’ Advertises Multi-Node (e.g. Repeater or Switch)

‘0’ Advertises Single-Node mode. (e.g. NIC)

PHY ADDRESS [4:0]:

sensing pins for multi ple applicati ons. The five PH YAD[4:0] are regis tered as inputs at reset with PHYAD_4 being the MSB of the 5-bit

PHY address. The PHY address can only be set through the strapping option.

These strap option pins have 2 different functions

This mode allows interoperability with

The DP83861 provides five PHY address-

DP83861

1.8 Reset

Signal Name Type Pin # Description

RESET

I 164

RESET:

and TRI-STATE output reset combinations. The RESET input must

be low for a minimum of 140 µs.

The active low RESET input allows for hard-reset, soft-rese t,

1.9 Power And Ground Pins

TTL/CMOS INPUT/OUTPUT SUPPLY

nal Name Pin # Description

Si

IO_VDD 58, 64, 73, 79, 87, 93,

102, 109, 117, 123, 132,

143, 149, 167, 178, 187,

193, 202

IO_VSS 57, 63, 72, 78, 86, 92,

101, 108, 116, 122, 131,

142, 148, 168, 179, 188,

194, 203

TRANSMIT/RECEIVE SUPPLY

nal Name PQFP Pin # Description

Si

CD#_AVDD 8, 15, 38, 45 3.3V Common Driver Supply

3.3V I/O Supply

I/O Ground

10 www.national.com

CD#_AGND 11, 12, 41, 42 Common Driver Ground

g

R#_AVDD# 2, 6, 17, 21, 32, 36, 47, 513.3V Receiver Analog Supply

R#_AGND# 3, 7, 16, 20, 33, 37, 46, 50Receiver Analog Ground

R#_ASUB 1, 22, 31, 52 Receiver Substrate Ground

INTERNAL SUPPLY PAIRS

nal Name PQFP Pin # Description

Si

CORE_VDD 69, 83, 98, 129, 137,

1.8V Digital Supply

160, 171, 182, 197

CORE_VSS 68, 82, 97, 128, 136,

Digital Ground

161, 172, 183, 198

CORE_SUB 67, 96, 127, 162, 173,

Substrate Ground

199

PGM_AVDD 27 3.3V PGM/CGM Supply. We recommend a low pass RC filter of a

18-22 Ω resistor and a 22 µF capacitor connected to this pin.

PGM_AGND 28 PGM/CGM Ground

BG_SUB 26 BG Substrate Ground

BG_AVDD 23 3.3V BG Supply

BG_AGND 25 BG Ground

SHR_VDD 29 3.3V Share Logic Supply

SHR_GND 30 Share Logic Ground

OSC_VDD 155 3.3V Oscillator Supply

OSC_VSS 152 Oscillator Ground

DP83861

1.10 Special Connect Pins

Signal Name PQFP Pin # Description

BG_REF 24 Internal Reference Bias (requires connection to ground via a 9.31

kΩ resistor).

TEST 186, 206 These pins should be tied to 3.3 V.

SI,SO 104,105 These two pins should be floated.

RESERVE_FLOAT

(Please also see next row.

There are two sets of reserved

pins-- one set needs to be

pulled-down to gnd while the

other set needs to be floated.)

53-56, 59-62, 65, 66, 70,

71, 74-77, 80, 81, 84, 85,

88-91, 94, 95, 99, 100,

103,106, 107

RESERVE_GND 165, 166, 169,

170,174,175, 176,177

Note:I = Input, O = Output, I/O = Bidirectional, Z = Tri-state output, S = Strapping pi n

These pins are reserved. These pins are to be left floating.

These pins are reserved and need to be tied to gnd.

11 www.national.com

2.0 Configuration

g

This section in clude s inform ation on the vari ous con figura tion options available with the DP83861. The configuration

options described herein include:

— Speed/Duplex Mode Selection

— Manual Mode Configurations

— Auto-Negotiation

— Isolate Mode

— Loopback Mode

— MII/GMII MAC Interface

— Test Modes

— Auto MDI / MDI-X Configuration

— Polarity Correction

— Firmware Interrupt

2.1 Speed/Duplex Mode Selection

The DP83861 supports six different Ethernet protocols:

10BASE-T Full Duplex, 10BASE-T Half Duplex, 100BASETX Full Duplex, 100BASE-TX Half Duplex, 1000BASE-T

Full Duplex and 1000BASE-T Half Duplex. Both the speed

and the Duplex mode of operation can be determined by

either Auto-Negotiation or set by manual configuration.

Both Auto-Negotiation and manual configuration can be

controlled by strap values applied to certain pins during

power-on/reset. They can be also controlled by access to

internal registers.

2.2 Manual Mode Configurations

2.2.1 Forced Speed/Duplex Selection

The manual configuration of the speed and duplex modes

of operation must be done with the Auto-Negotiation function has to be disabled. This can be achieved by strapping

AN_EN low during power-on/reset. Auto-Negotiation can

also be disabled by writing a “0” to bit 12 of the BMCR register. (0x00). Once AN_EN is disabled then the strap value

of the SPEED[1:0] pins will be used to determine speed of

operation, and the strap value of the LED_DUPLEX will be

used to determine duplex mode.

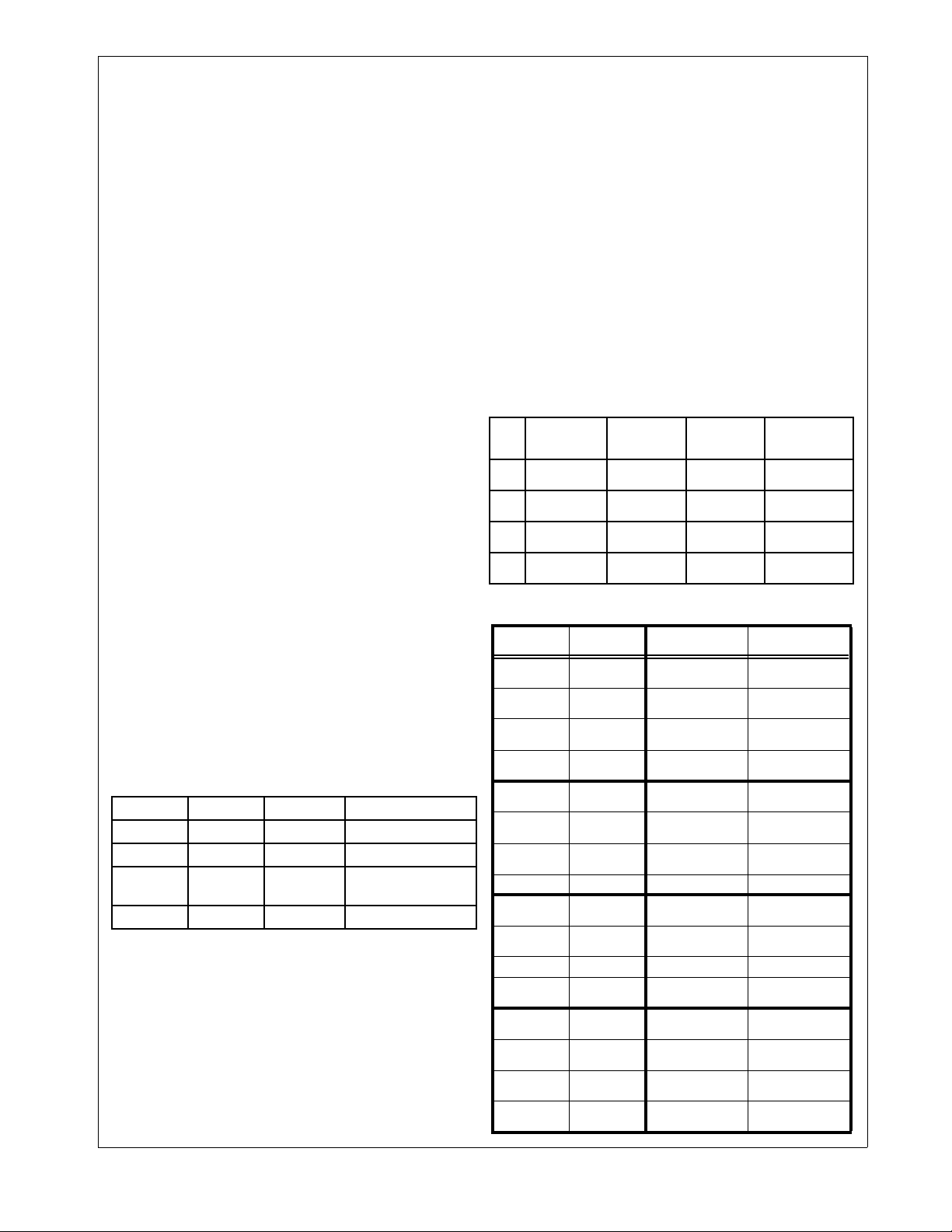

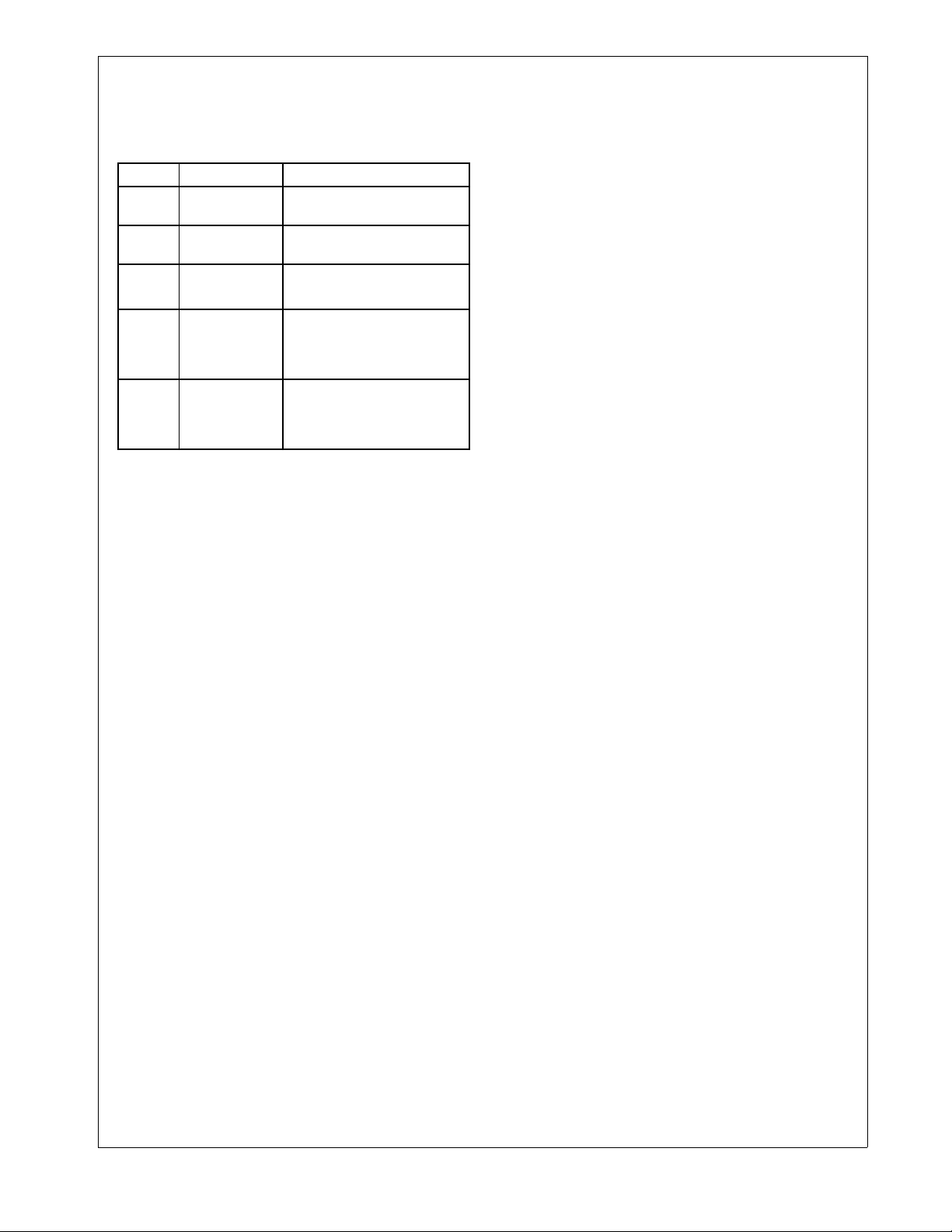

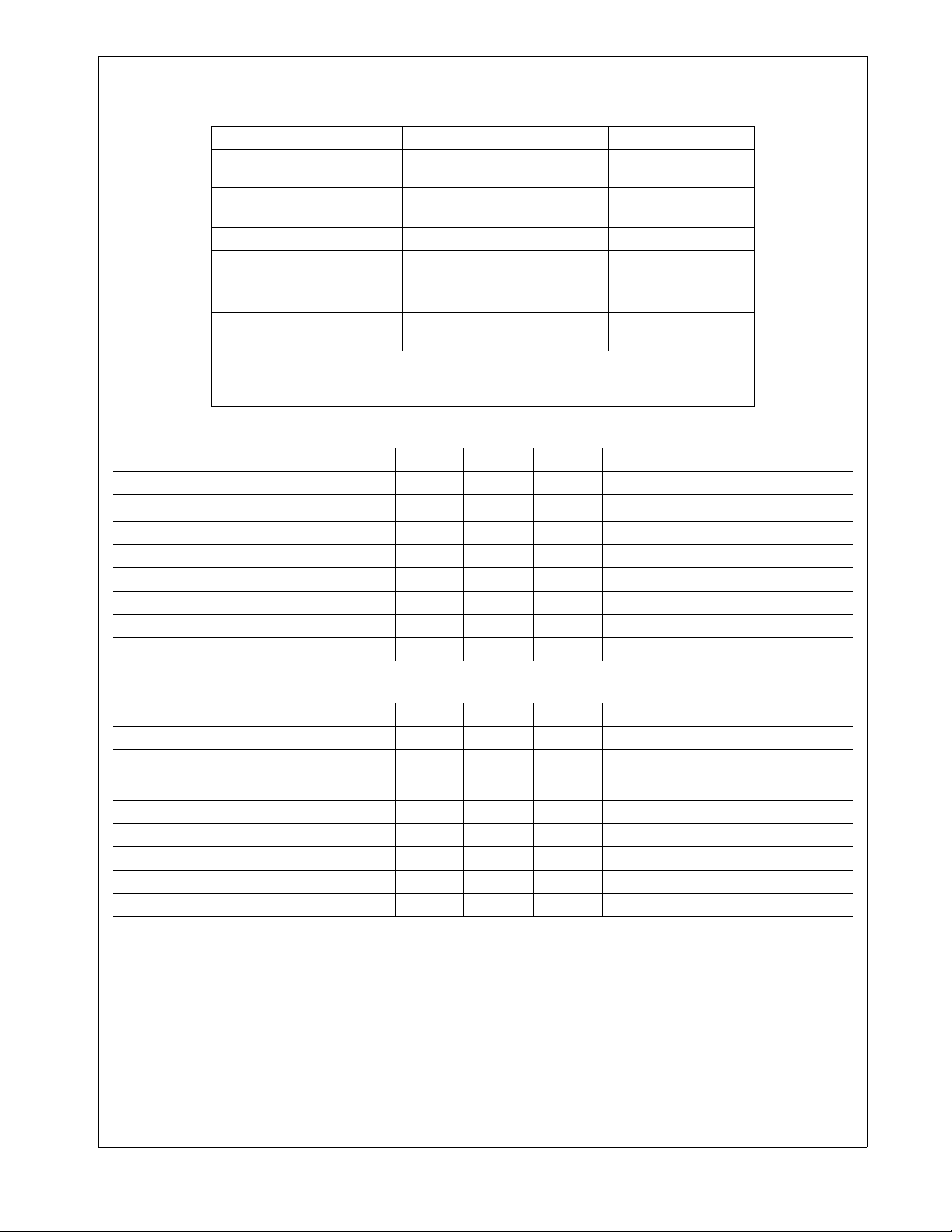

Table 1. Non Auto-Ne

AN_EN SPEED [1] SPEED [0] Forced Mode

0 0 0 10BASE-T

0 0 1 100BASE-TX

0 1 0 1000BASE-T

0 1 1 Reserved

For all of the modes above, DUPLEX strap value “1”

selects Full Duplex, while “0” selects Half Duplex. The

strap values latched-in during power-on/reset can be overwritten by access to the BMCR register 0x00 b its 13,1 2, 8

and 6.

It should be noted that Force 1000BASE-T mode is not

supported by IEEE. This mode should be used for test purposes only. The DP83861 when in forced 1000BASE-T

mode will only communicate with another DP83861 where

one Phy is set for Slave operation and the other is set for

Master operation.

otiation Modes

(Test Mode Only)

2.2.2 Manual MASTER/SLAVE Resolution

In 1000BASE-T mode, one device needs to be configured

as a Master and the other as a Slave. The Master device

by definition uses a local clock to transmit data on the wire;

while the Slave device uses the clock recovered from the

incoming data for transmitting its own data. The DP83861

uses the Ref_CLK as the local clock for transmit purposes

when configured as a Master. The Master and Slave

assignments can be manually set by using strap options or

register writes. Manual M/S Advertise(Pin 191, Reg. 9.11),

Manual M/S Enable(Pin 195, Reg. 9.12), and Port

Type (Pin 208, Reg. 9.10 ).

MASTER/SLAVE resolution for 1000BASE-T between a

PHY and it’s Link Partner can be resolved to sixteen possible outcomes (SeeTable 3). The resolution outcome is

based on the rankings wh ich are s hown in Table 2, where a

Rank of 1 has the highest priority.

Table 2. Master/Slave Rankings and Settings

Rank Configuration

1 Manual Master Don’t Care

2 Multi-Port 1

3 Single-Port 0

4 Manual Slave Don’t Care

Port Type

Reg. 9.10

Pin 208

Don’t Care

Pull High

Pull Low

Don’t Care

M/S Advertise

Reg. 9.11

Pin 191

1

Pull High

Don’t Care

Don’t Care

Don’t Care

Don’t Care

0

Pull Low

M/S Enable

Reg. 9.12

Pin 195

1

Pull High

Don’t Care

Don’t Care

Don’t Care

Don’t Care

1

Pull High

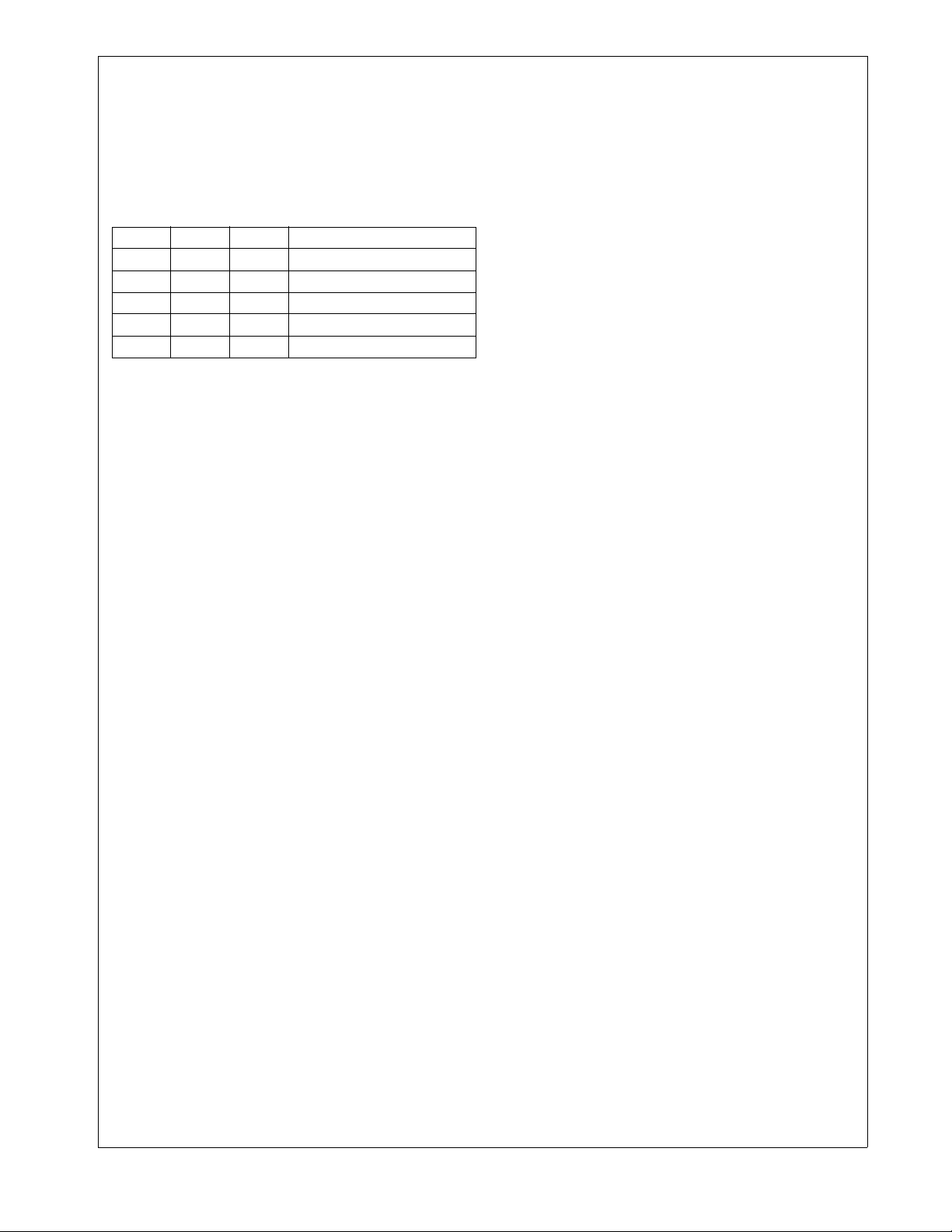

Table 3. Master/Slave Outcome

DP83861

Advertise

Manual

Master

Manual

Master

Manual

Master

Manual

Master

Mult-Port Manual

Mult-Port Manual

Mult-Port Multi-Port M/S resolved

Mult-Port Single-Port Master Slave

Single-Port Manual

Single-Port Manual

Single-Port Multi-Port Slave Master

Single-Port Single-Port M/S resolved

Manual

Slave

Manual

Slave

Manual

Slave

Manual

Slave

Link Partner

Advertise]

Manual

Master

Manual

Slave

Multi-Port M aster Slave

Single-Port Master Slave

Master

Slave

Master

Slave

Manual

Master

Manual

Slave

Multi-Port Slave Master

Single-Port Slave Master

DP83861

Outcome

Unresolved

No Link

Master Slave

Slave Master

Master Slave

by random seed

Slave Master

Master Slave

by random seed

Slave Master

Unresolved

No Link

Link Partner

Outcome

Unresolved

No Link

M/S resolved

by random seed

M/S resolved

by random seed

Unresolved

No Link

DP83861

12 www.national.com

If both the link partner and the local device are manually

g

g

g

g

g

given the same MASTER/SLAVE assignment, then an

error condition will exist as indicated by bit 15 of register

0x0A. If one of the link partners is manually assigned a

Master/Slave status while the other is not, then the manual

assignment will take higher priority during the resolution

process.

When Manual Slave or Manual Master mode is enabled

Auto-Negotiation should also be enabled as per the 802.3

IEEE specification. The DP83861, however will link up to

another DP83861 when Auto-Negotiation is disabled and

one DP83861 is manually configured as a Master and the

other is manually configured as a Slave.

An alternative way of specifyi ng Maste r or Slave mode is to

use the Port_Type strapping option pin 208 or by writing to

register 0x09 bit 10. When pin 208 is pulled high or a 1 is

written t o bit 1 0 th e part wil l adver tise that i t wa nts to be a

Master . When pin 208 is pull ed low or a 0 is writ ten t o bit 10

the part will advertise that it wants to be a Slave. If two

devices advertise that they want to both be Master or both

to be Slaves then the Auto-Negotiation statemachine will

go through a random number arbitration sequence to pick

which one will be the Master and which one will be the

Slave. Using this method will eliminate the chance of an

unresolved link.

2.3 Auto-Negotiation

All 1000BASE-T PHYs are required to support Auto-Negotiation. The Auto-Negotiation function in 1000BASE-T has

four primary purposes:

— Auto-Negotiation Priority Resolution

— Auto-Negotiation MASTER/SLAVE Resolution

— Auto-Negotiation PAUSE/ ASYMMETRICAL PAUSE

Resolution

— Auto-MDIX resolution

2.3.1 Auto-Ne

First the Au to-Negotiati on function provi des a mechanism

for exchanging con fig urati on in form ati on bet we en two ends

of a link segmen t and automatically se lecting the highest

performance mode of operation s upported by b oth devices .

Fast Link Pulse (FLP) Bursts provide the signalling used to

communicate Auto-Negotiation abilities between two

devices at each end of a link segment. For furthe r details

regarding Auto-Negotiation, refer to Clause 28 of the IEEE

802.3u specification. The DP83861 supports six different

Ethernet protocols: 10BASE-T Full Duplex, 10BASE-T Half

Duplex, 100BASE-TX Full Duplex, 100BASE-TX Half

Duplex, 1000BASE-T Full Duplex and 1000BASE-T Half

Duplex, so the inclusion of Auto-Negotiation ensures that

the highest performance protocol will be selected based on

the advertised ability of the Link Partner.

Auto-Negotiation Priority Resolution for the DP83861:

1. 1000BASE-T Full Duplex (Highest Priority)

2. 1000BASE-T Half Duplex

3. 100BASE-TX Full Duplex

4. 100BASE-TX Half Duplex

5. 10BASE-T Full Duplex

6. 10BASE-T Half Duplex (Lowest Priority)

otiation Priority Resolution

2.3.2 Auto-Ne

The second goal of Auto-Negotiation in 1000BASE-T

devices is to resol ve MAST ER/SLAVE configuration. If both

devices have disabled manual Master/Slave configuration,

MASTER priority is given to the dev ices wh ich su pport mu ltiport nodes (i.e. Switches and Repeaters take higher

priority over DTEs or single node systems.).

SPEED[0]/PORT_TYPE is a strap option for advertising

the Multi-node functionality. (See Table 4) If both PHYs

advertise the same options then the Master/Slave resolution is resolved by a random number generation. See IEEE

802.3ab Clause 40.5.1.2 and Table 3 for more details.

2.3.3 Auto-Ne

PAUSE Resolution

Auto-Negotiation is also used to determine the Flow Control capabilities of the two link partners. Flow control was

originally introduced as a mechanism to force a busy station’s Link Partne r to stop s ending da ta wh en in Full D uplex

mode of operation. Unlike Half Duplex mode of operation

where a link partner could be forced to back off by simply

causing collisions , the Full Duplex operation needed a formal mechanism to slow down a link partner in the event of

the receiving station’s buffers becoming full. A new MAC

control layer was added to handle the generation and

reception of Pause Frames which contained a timer indicating the amount of Pause requested. Each MAC/Controller has to advertise whether it can handle PAUSE frames,

and whether they support PAUSE frames in both directions. (i.e. receive and transmit. If the MAC/C ontroller will

only generate PAUSE frames but will not respond to

PAUSE frames generated by a link partner, then this is

called Asymmetrical PAUSE.) Advertisement of these

capabilities can be ac hieved by writing a ‘1’ to bits 10 and

11 of the Auto-Neg Advertisement register (Address 0x04).

The link partners PAUSE capabilities can be determined

from register 0x05 using these same bits. The MAC/controller has to write to and read from these registers and

determine which mode of PAUSE operation to choose. The

PHY layer i s not involved in P ause resolution o ther than

the simple advertising and reporting of PAUSE capabilities.

These capabilities are MAC specific. The MAC conveys

these capabilities by writing to the appropriate PHY registers.

2.3.4 Auto-Ne

The DP83861 can determine if a “straight” or “c ross-over”

cable is being used to connect to the link partner and can

automatically re-assign channel A and channel B to establish link wit h the li nk pa rt ner. Although not pa rt of the Au toNegotiation FLP exchange process, the Auto-MDIX resolution requires that Auto-Negotiation is enabled. Auto-MDIX

resolution will precede the actual Auto-Negotiation process

which involv es exc hange of FLP s to adve rtise capab ilitie s.

If Auto-Negotiation is not enabled, then the MDIX function

can be manually configured by disabling Auto-MDIX. See

Section 8.16 on FAQs for details.

2.3.5 Auto-Ne

The Auto-Negotiation function within the DP83861 can be

controlled either by internal register access or by the use of

the AN_EN, and various strap pin values during poweron/reset. Table 4 shows how the various strap pin values

otiation MASTER/SLAVE Resolution

otiation PAUSE and Asymmetrical

otiation Auto-MDIX Resolution

otiation Strap Option Control

DP83861

13 www.national.com

are used during Auto-Negotiation to advertise different

g

g

g

capabilities.

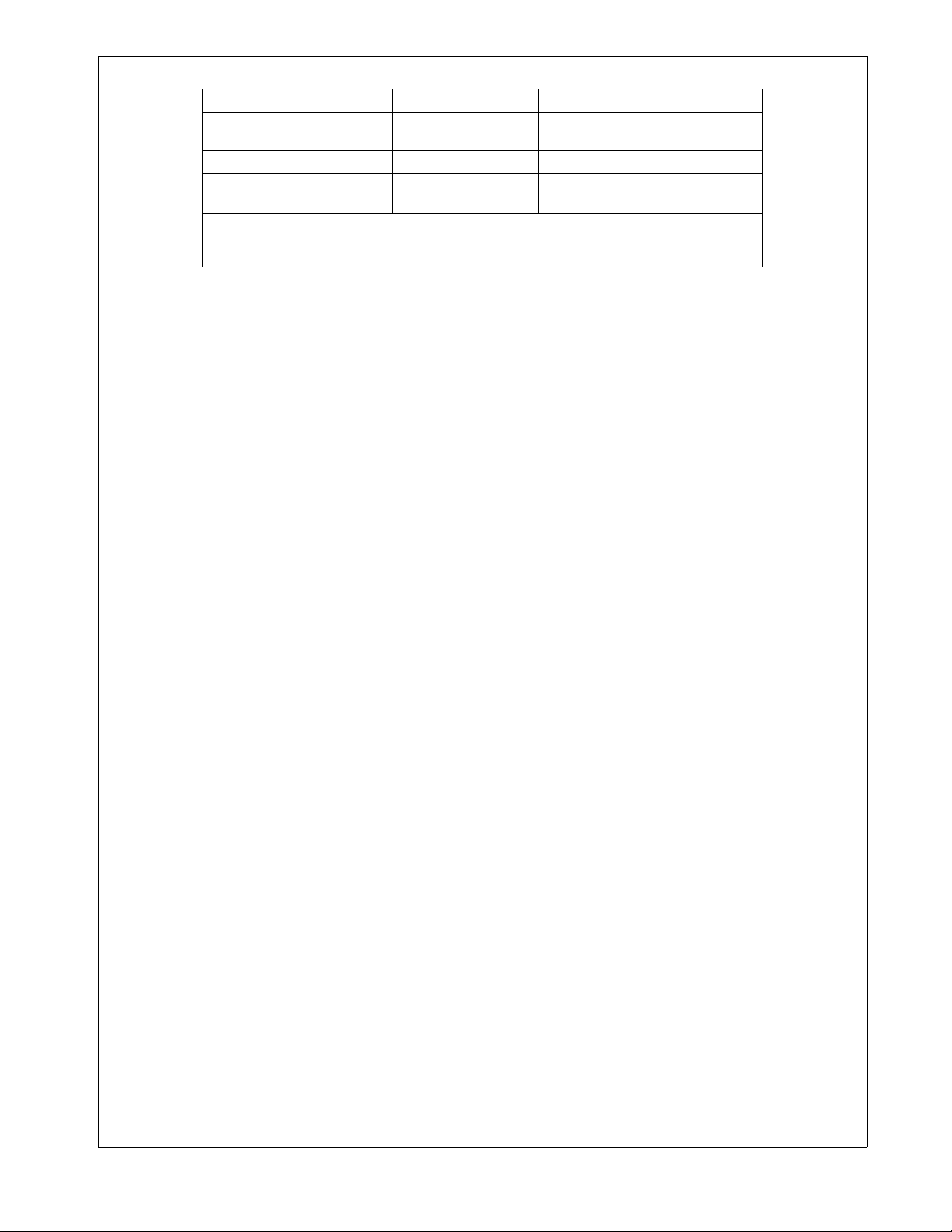

Table 4. Auto-Ne

Pin # Pin Name Comments

184 1000FDX_ADV

/LED_1000

185 LED_DUPLEX/

1000HDX_ADV

181 LED_100/

100_ADV

180 LED_10/

10_ADV/

SPEED[1]

208 SPEED[0]/

PORT_TYPE

2.3.6 Auto-Ne

The state of AN_EN, SPEED [1:0], DUPLEX pins as well

as the xxx_ADV pins during power-on/reset determines

whether the Auto-Negotiation is enabled and what specific

ability (or set of abilities) are advertised as given in Table 4.

These strapping option pins allow configuration options to

be selected without requiring internal register access.

The Auto-Negotiation function selected at power-up or

reset can be changed at an y time by writi ng to the Bas ic

Mode Control Register (BMCR) at address 0x00, AutoNegotiation Advertisement Register 0x04 or to 1000BASET Control Register (1KTCR) 0x09.

When Auto-Negotiation is enabled, the DP83861 transmits

the abilit ies programme d into the Au to-Negotiati on Advertisement register (ANAR) at address 0x04, and

1000BASE-T Control register at address 0x09 via FLP

Bursts. Any combination of 10 Mb/s,100 Mb/s, 1000 Mb/s,

Half Duplex, and Full D uple x mod es ma y be s elect ed. T he

Auto-Negotiation protocol compares the contents of the

ANLPAR and ANAR registers (for 10/100 Mb/s operation)

and the contents of 1000BASE-T status and control registers, and uses the results to automatically configure to the

highest performance protocol between the local and farend port. The results of Auto-Negotiation may be accessed

in registers BMCR (Duplex Status and Speed Status), and

BMSR (Auto-Neg Complete, Remote Fault, Link).

The Basic Mode Control Register (BMCR) at address 00h

provides control for enabling, disabling, and restarting the

Auto-Negotiation process.

The Basic Mode Status Register (BMSR) at address 01h

indicates the set of available abilities for technology types,

Auto-Negotiation ability, and Extended Register Capability.

These bits are permanently set to indicate the full functionality of th e DP83861.

The BMSR also provides status on:

— Whether Auto-Negotiation is complete (bit 5)

— Whether the Link Partner is advertising that a remote

fault has occurred (bit 4)

— Whether a valid link has been established (bit 2)

otiation Register Control

otiation Modes AN_EN = 1

‘1’ Advertises 1000 Mb/s

FDX capability.

‘1’ Advertises 1000 Mb/s

HDX capability.

‘1’ Advertises both 100 Mb/s

FDX & HDX capability.

‘1’ Advertises 10 Mb/s FDX

and HDX. ‘0’ advertises neither FDX nor HDX 10 Mb/s

capability.

‘1’ Advertises Multi-Node

functionality. (e.g. Switch or

Repeater, in contrast to NIC

single node operation.)

The Auto-Negotiation Advertisement Register (ANAR) at

address 04h indicates the Auto-Negotiation abilities to be

advertised by the DP8 3861. All available abilities are transmitted by default, but any ability can be s up pres s ed by w ri ting to the ANAR. Updating the AN AR to s upp res s an abi lit y

is one way for a management agent to change (force) the

technology that is used.

The Auto-Negotiation Link Partner Ability Register

(ANLPAR) at address 05h is used to receive the base link

code word as well as all Next Page code words during

Auto-Negotiation.

If Next Page is NOT being used, then the ANLPAR will

store the base link code word (link partner's abilities) and

retain this information from the time the page is received,

as indicated by a 1 in bit 1 of the ANER register (address

06h), through the end of the negotiation and beyond.

When using the Next Page operation, the DP83861 cannot

wait for Auto-Negotiation to complete in order to read the

ANLPAR because the register is used to store both the

base and next pages. Software must be available to perform several functions. The ANER (re gister 06h ) must hav e

a page received indication (bit 1), once the DP83861

receives the first p age, softwa re mus t store it in memo ry if it

wants to keep the information. Auto-Negotiation keeps a

copy of the base pag e i nformation bu t it is no lon ger accessible by software. After reading the base page information,

software needs to write to ANNPTR (register 07h) to load

the next page information to be sent; continue to poll the

page received bit in the ANER and when active, read the

ANLPAR. The contents of the ANLPAR will tell if the partner has further pages to be sent. As long as the partner

has more pages to send, software must write to the next

page transmit register and load another page.

The Auto-Negotiation Expansion Register (ANER) at

address 06h indicates additional Auto-Negotiation status.

The ANER provides status on:

— Whether a Parallel Detect Fault has occurred (bit 4, reg-

ister address 06h.)

— Whether the Link Partner supports the Next Page func-

tion (bit 3, register address 06h.)

— Whether the DP83861 supports the Next Page function

(bit 2, register address 06h). (The DP83861 does support the Next Page function.)

— Whether the current page being exchang ed by Auto-N e-

gotiation has been received (bit1, register address 06h.)

— Whether the Link Partner supports Au to-Negoti ation (bit

0, register address 06h.)

The Auto-Negotiation Next Page Transmit Register

(ANNPTR) at address 07h contains the next page code

word to be sent. See Auto-Negotiation Next Page Transmit

Register (ANNPTR) address 07h for a bit description of this

register.

2.3.7 Auto-Ne

The DP83861 supports the Parallel Detection function as

defined in the IEEE 802.3u specifi ca tio n. Paral le l Detect io n

requires the 10/100 Mb/s receivers to monitor the receive

signal and report link status to the Auto-Negotiation function. Auto-Negotiation uses this information to configure

the correct technology in the event that the Link Partner

does not support Auto-Negotiation, yet is transmitting link

signals that the 10BASE-T or 100BASE-X PMA recognize

as valid link signals.

otiation Parallel Detection

DP83861

14 www.national.com

If the DP83861 completes Auto-Negotiation as a result of

g

g

g

g

g

Parallel Detection, without Next Page operation, bits 5 and

7 within the ANLPAR register (address 05h) will be set to

reflect the mode of operation present in the Link Partner.

Note that bits 4:0 of the ANLPAR will also be set to 00001

based on a succ essf ul pa ra llel det ecti on to i ndica te a va lid

802.3 selector field. Software may determine that AutoNegotiation completed via Parallel Detection by reading a

zero in the Link Partner Auto-Negotiation Ability register

(bit 0, register address 06h) once the Auto-Negotiation

Complete bit (bit 5, register address 01h) is set. If configured for parallel detect mode and any condition other than

a single good link occurs then the parallel detect fault bit

will set (bit 4, register 06h).

2.3.8 Auto-Ne

Once Auto-Negotiation has completed, it may be restarted

at any time by settin g bit 9 (Restart Au to-Negot iation ) of the

BMCR to one. If the mode confi gure d by a su cces sful Au toNegotiation loses a valid link, then the Auto-Negotiation

process will resume and attempt to determine the configuration for the link. This function ensures that a valid configuration is maintained if the cable becomes disconnected.

A re-Auto-Negotiation request from any entity, such as a

management agent, will cause the DP83861 to halt any

transmit data and link pulse activity until the

break_link_timer expires (~1500 ms). Consequently, the

Link Partner will go into link fail and normal Auto-Negotiation resumes. The DP83861 will resume Auto-Negotiation

after the break_link_ti me r has ex pi red b y i ss uin g FL P (Fas t

Link Pulse) bursts.

2.3.9 Enablin

It is important to note that if the DP83861 has been initialized upon power-up as a Non-Auto-Negotiating device

(forced technology), and it is then required that Auto-Negotiation or re-Auto-Negotiation be initiated via software,

bit 12 (Auto-Negotiation Enable) of the Basic Mode Control

Register must first be cleared and then set for any AutoNegotiation function to take effect.

2.3.10 Auto-Ne

Parallel detection and Auto-Negotiation take approximately

2-3 seconds for 10/100 Mb/s devices and 5-6 seconds for

1000 Mb/s devices to complete. In addition, Auto-Negotiation with Next Page should take an additional 2-3 seconds

to complete, depending on the number of next pages sent.

Refer to Clause 28 of the IEEE 802.3u standard for a full

description of the individual timers related to Auto-Negotiation.

2.3.11 Auto-Ne

The DP83861 supports the optional Auto-Negotiation Next

Page protocol. The ANNPTR register (address 07h) allows

for the configuration and transmission of Next Page. Refer

to clause 28 of the IEEE 802.3u standard for detailed information regarding the Auto-Negotiation Next Page function.

This functionality is also discussed in Section 2.3.6 above

and in the Section7.0 (User Information).

otiation Restart

Auto-Negotiation via Software

otiation Complete Time

otiation Next Page Support

2.4 MII Isolate Mode

2.4.1 10/100 Mb/s Isolate Mode

The DP83861 can be put into MII Isolate mode b y writ ing to

bit 10 of the BMCR register.

With bit 10 in the BMCR set to one, the DP83861 will not

respond to pa cket data present at TXD [3:0], TX_EN, and

TX_ER inputs and the TX_CLK, RX_CLK, RX_DV,

RX_ER, RXD[3:0], COL, and CRS outputs will be TRIST ATED. The DP83861 wil l co nti nue to re spo nd to al l management transactions on the MDIO line.

While in Isolate mode, the TD± outputs will not transmit

packet data but will continue to source 100BASE-TX

scrambled idles or the 10 Mb/s link pulses.

2.4.2 1000 Mb/s Isolate Mode

During 1000 Mb/s operation, entering the isolate mode will

TRI-STATE the GMII outputs of the EN Gig PHYTER.

When the DP83861 enters into the isolate mode all media

access operations are halted and the DP83861 goes into

power-down mode. The only way to communicate to the

PHY is through the MDIO management port.

2.5 Loopback

The DP83861 includes a Loopback Test mode for easy

board diagnosti cs . The L oop bac k m od e is selected through

bit 14 (Loopback) of the Basic Mode Control Register

(BMCR). Writing 1 to this bit enables MII/GMII transmit

data to be routed to the MII/GMII receive outputs. While in

Loopback mode the data will not be transmitted onto the

media. This is true for 10 Mb/s, 100 Mb/s, as well

1000 Mb/s data.

In 10BASE-T, 100BASE-TX, 1000BASE-T Loopback mode

the data is routed through the PCS and PM A layer s into the

PMD sublayer before it is looped back. Therefore, in addition to serving as a b oard dia gnost ic, thi s mode ser ves as a

quick functional verification of the device.

2.6 MII/GMII Interface and Speed of Operation

The DP83861 supports 2 different MAC interfaces. MII for

10 and 100 Mb/s, GMII for 1000 Mb/s. The speed of operation determines the interface chosen. The speed can be

determined by Auto-Negotiation, or by strap options, or by

register writes.

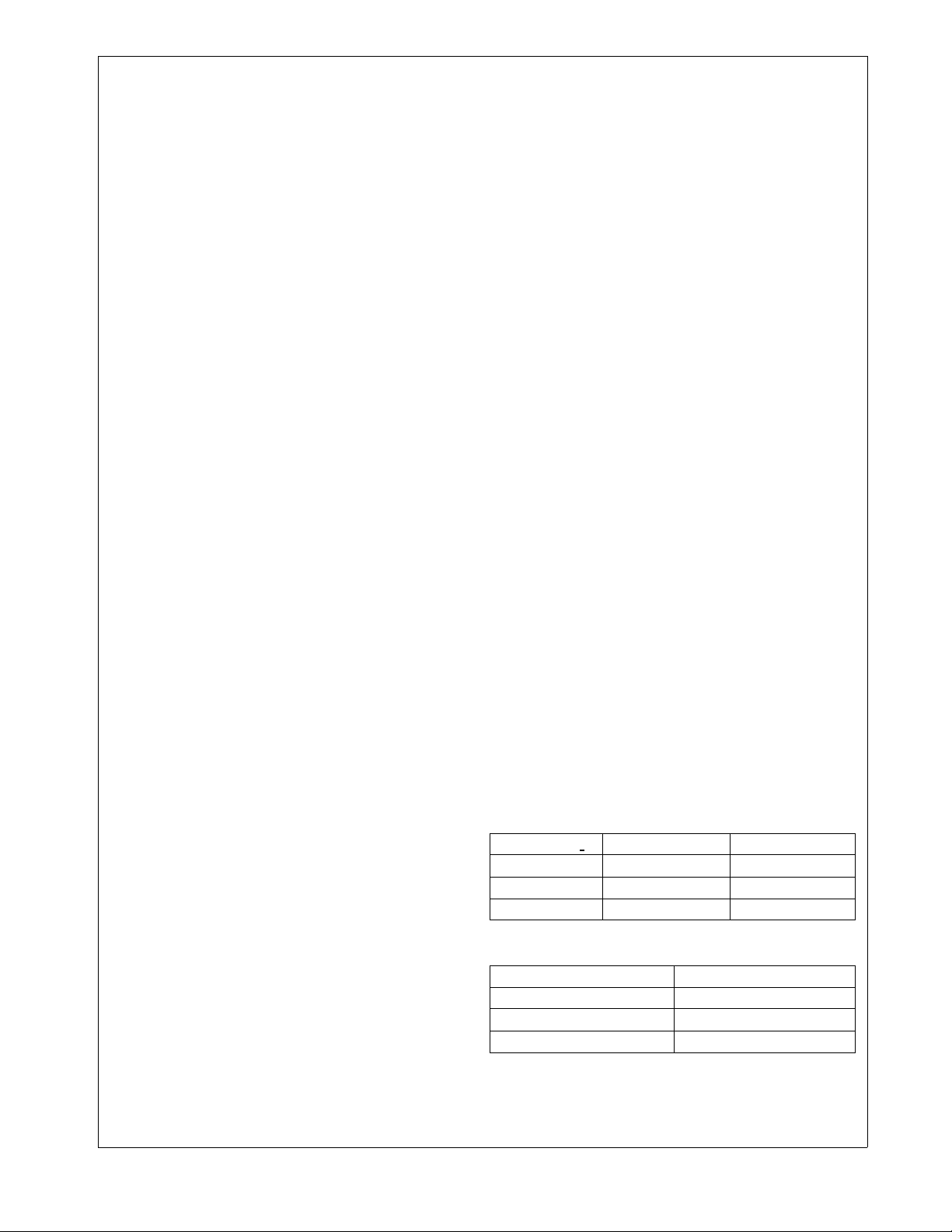

Table 5. Auto-Ne

SPEED[1:0]

00 10BASE-T MII

01 100BASE-TX MII

10 1000BASE-T GMII

Table 6. Auto-Negotiation Enabled:

Link Negotiated Controller I/F

10BASE-T MII

100BASE-TX MII

1000BASE-T GMII

Link Strapped Controller I/F

otiation Disabled:

DP83861

15 www.national.com

2.7 Test Modes

IEEE 802.3ab specification for 1000BASE-T requires that

the Physical layer device be able to generate certain well

defined test patterns. Clause 40 section 40.6.1.1.2 “Test

Modes” describes these tests in detail. There are four test

modes as well as a normal mode. Th ese modes can be

selected by writing to the 1000BASE-T control register

(0x09) as shown.

Table 7. Test Mode Select:

bit 15 bit 14 bit 13 Test Mode Selected

1 0 0 = Test Mode 4

0 1 1 = Test Mode 3

0 1 0 = Test Mode 2

0 0 1 = Test Mode 1

0 0 0 = Normal Operation

See IEEE 802.3ab section 40 .6.1.1.2 “Test modes” for more

information.

2.8 Automatic MDI / MDI-X Configuration

The DP83861 implements the automatic MDI/MDI-X configuration functionality as described in IEEE 802.3ab

Clause 40, Section 40.4.4.1. This functionality eliminates

the need for crossover cables between similar devices.

The switching between the +/- A port with the +/- B port will

be automatically taken care of, as well as switching

between the +/- C port and the +/- D port.

The spec. calls for the physical layer device to detect it’s

Link Partners link pulses within 62 ms. During the MDIX

detection phase the DP83861 sends out link pulses that

are spaced 150 µs apart. The 150 µs link pu lse spacing

was purposely selected to transmit non-FLP bursts (FLP

pulses are spaced 124 µs +/- 14 µs) so that th e li nk partn er

would not mistakenly attempt to “link up” on the MDIX link

pulses.

2.9 Polarity Correction

The EN Gig PHYTER will automatically detect and correct

for polarity reversa l in w iri ng b etwee n th e +/ - wires for eac h

of the 4 ports.

2.10 Firmware Interrupt

DP83861 can be configured to generate an interrupt on pin

208 when changes of internal status occur. The interrupt

allows a MAC to act upon t he status in the PHY without

polling the PHY registers. The interrupt source can be

selected through the interrupt register set. This register set

consists of:

— Interrupt Status Registers

– ISR0 0x810D

– ISR1 0x810E

— Interrupt Enable Registers

– IER0 0x8113

– IER1 0x8114

— Interrupt Clear Registers

– ICLR0 0x8115

– ICLR1 0x8116

— Interrupt Control Register

– ICTR 0x8117

— Interrupt Raw Reason Registers

– RRR0 0x8111

– RRR1 0x8112

— Interrupt Reason Registers

– IRR0 0x810F

– IRR1 0x8110

Upon reset, interrupt is disabled and the interrupt registers

are initialized with their default values.

The interrup t s ign al ’s po l ari t y ca n be e as il y pro g ram me d in

the ICTR. The polarity can be configured active high or

active low. In the latched mode, the interrupt signal is

asserted and remains asserted while the corresponding

enabled status bit is asserted.

Open Drain Output and should not be wired OR’ed to

other pins.

These bits are mapped in the ISR. When the interrupt status bit is “ 1”, the interrupt sig nal is asserted if the c orresponding IER bit is enabled. An interrupt status bit can be

cleared by writing a “1” to the corresponding bit in the

ICLR. The clear bit returns to “0” automatically after the

interrupt status bit is cleared.

The RRR contains the current status of the signals being

monitored. Note that t he stat us of th e conf igurati on, dup lex,

and speed are recorded in th e m os t rec ent p erio d whi le th e

link was up.

The IRR records the “reason” that an interrupt status bit is

asserted. F or example, if the isr_li nk bit is asse rted in the

ISR because a link is achieved, then a “1” is stored in the

corresponding IRR bit field. This IRR bit field is not

changed until the interrupt is serviced, regardless how

many times the source status (in RRR) changes in the

interveni ng pe rio d. Th e IRR bi t can be cl ear ed by wr itin g a

“1” to the corresponding bit in the ICLR register.

The purpose of the IRR is for the interrupt logic to determine the next state change to cause an interrupt. In reality,

the PHY may operate at muc h faster pac e than the inte rrupt service provider. The IRR provides a mechanism for

the higher layers to decipher the context of the interrupt

although the context of the system may have changed by

the time the interrupt is serviced. For instance, when link is

lost and regained in quick succession, it is likely that a

sequence of interrupts are generated by the same event.

The IRR preserves the status of the event that may have

changed during the interrupt service. A new interrupt may

be generated if the status is changed based on the comparison between the IRR and the RRR.

Note that all the interrupt registers are extended registers

located in the expanded memory space. Please refer to

Register Block section for details.

The status bits are the sources of the interrupt.

The Interrupt pin is not an

DP83861

16 www.national.com

3.0 Design and Layout Guide

g

g

g

This guide will provide information to assist in the design

and layout of the DP83861 Gigabit Ethernet Transceiver.

This guide will cover the following areas:

— Power Supply Filtering

— Twisted Pair Interface

— MAC Interface

—Clocks

— LED/Strapping Configuration

— Unused Pins/ Reserved Pins

— Hardware Reset

— Temperature Considerations

— List of Pins and Pin Connection Guide

3.1 Power Supply Filterin

It is recommended that the PCB have at least one solid

ground plane, one solid 3.3 V plane, and one solid 1.8 V

plane, with no breaks in any of these planes. The interplane capacitance between the supply and ground planes

should be maximized by minimizing the distance between

these planes. Filling unused signal planes with copper and

connecting them to the proper power plane will also

increase the interplane capacitance. The inter-plane

capacitance acts like a short at high frequencies to reduce

supply plane impedance. Not all designs will be able to

incorporate the recommended suggestions because of

board cost constraints. Working designs have been done

using only 4 layers. National has a reference design built

using the EN Gig PHYTER and our GigMAC. This reference design is a PCI NIC card, using only 4 layers and

DP83861

having component pla ceme nt on onl y one s ide of the board

to reduce cost. The schematic, layout and gerber files for

this reference design are available upon request.

The 3.3 V & the 1.8 V supply pins come in pairs with their

corresponding ground pins (i.e. a 3.3 V supply-ground pair

is formed by pin 2 [RA_AVDD] and pin 3 [RA_AGND]).

These paired pins are physically adjacent to each other.

The matching pins should be bypassed with low impedance surface mo unt capacito rs of value 0.1 µF connected

directly into the p ower plan es w ith vi as as clo se as poss ible

to the pins. This will reduce the inductance in series with

the bypass ca paci t or. Any incr eas e in in d uc tan ce wil l l owe r

the capacitor’s self resonant frequency which will degrade

the high frequency performance of the capacitor. It’s also

recommended that 0.01 µF capacitors are connected in

parallel with the 0.1 µF capacitors, or at least "dispersed",

replacing some of the 0.1 µF capacitors. The lower value

capacitance will increase the frequency range of effectiveness of the bypassing scheme. This is due to the unavoidable inductance o f th e l eads and connections on the board,

which cause resonance at low frequencies for large value

capacitors.

The Analog PGM supply requires special filtering to attenuate high frequencies. High frequencies will increase the jitter of the PGM. We recommend a low pass filter formed by

a 18-22 Ω resistor and two capacitors in parallel. One of

the capacitors should be 22 µF a nd the other 0.01 µF. (This

will implem ent a single pole low pass fi lter with 3 dB f req.

around 360 - 400 Hz.). The maximum current on this supply is 5 mA.

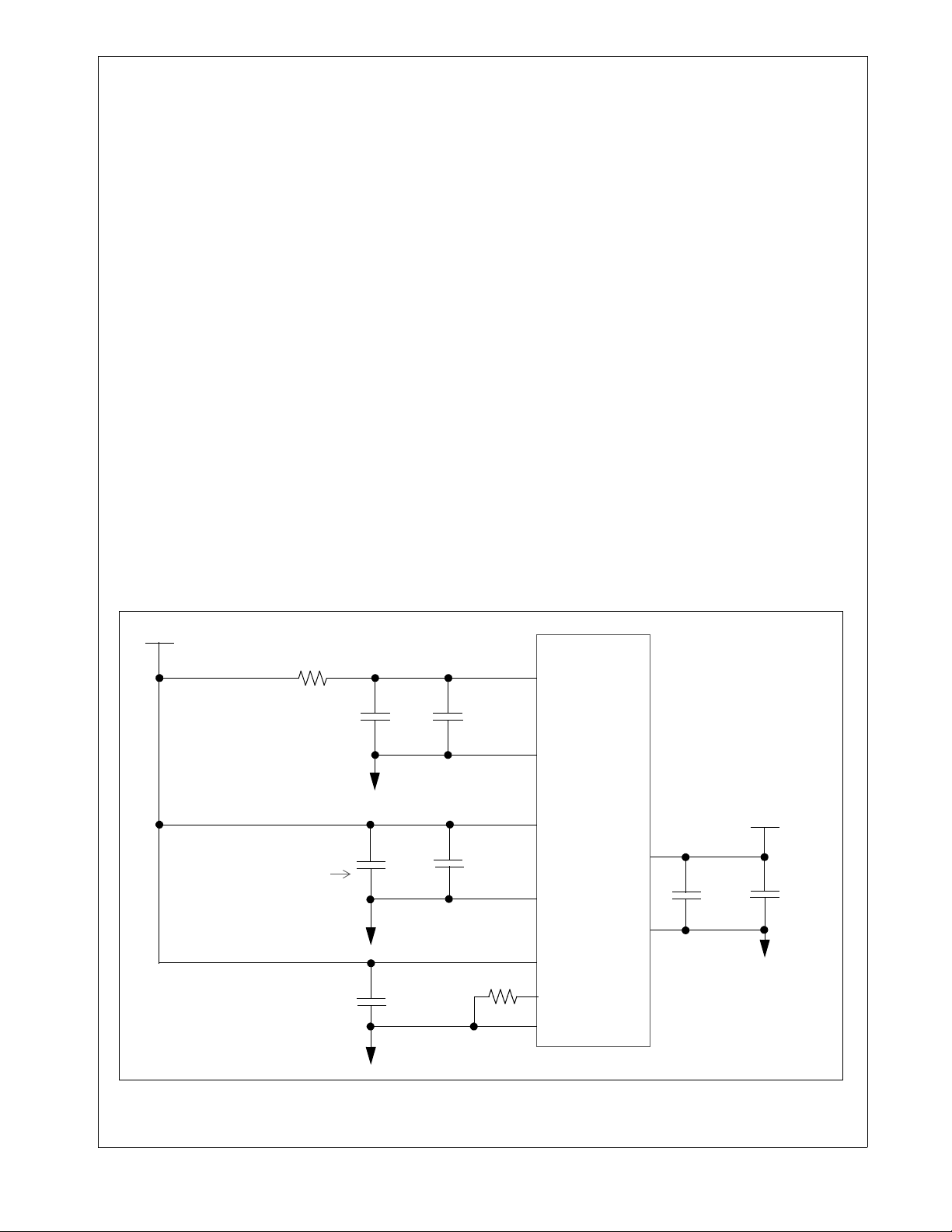

= 3.3 V

V

DD

Typical supply bypassing

(Near pins of the device)

Low pass filter for

PG M _AVDD only

18

Ω −

22

Ω

22

µF

0.01 µF

0.01

µF

0.01

0.1

µF

µF

9.31 k

DP83 861

PGM_A

PGM_AGND

IO_

VDD

CORE_

IO_GND

BG_A

Ω

BG_REF

AGND

VDD

CORE_

VDD

VDD

VSS

0.01 µF

V

DD

= 1.8 V

0.1

µF

ure 1. Power Supply Filterin

Fi

17 www.national.com

A 10 µF capacitor should also be placed close to the

g

DP83861 (possibly on the bottom side of the PCB) bypassing the VCC and ground planes.

There has been considerable discussion in the literature

about the use of ferrite beads to isolate power plane noise

from certain noisy VCC pins and preventing this noise from

coupling into sensitive analog VCC pins. This is typically

achieved by using ferrite beads (inductors) between noisy

VCC and quiet VCC line. An inductor in conjunction with

the bypass capacitor at the VCC pins will form a low pass

filter which will prevent the high frequency noise from coupling into the quite VCC. However, using this scheme can

give mixed results. There is considerable debate about

whether this approach is necessary or even useful. In most

of our boards we put in a stuffing option for inductors (zero

Ohm resistors). In general we have not found any improvements with th e us e of ferr ite bea ds, ho we ver no ise cons iderations are very dependent on PCB’s specific layout,

function and power supplies. The board designer should

evaluate whether they w ill ben efi t from ferr ite b eads in their

particular board.

The pin check list on Table 14 show the suggested connections of these capacitors for every supply, ground and substrate pin.

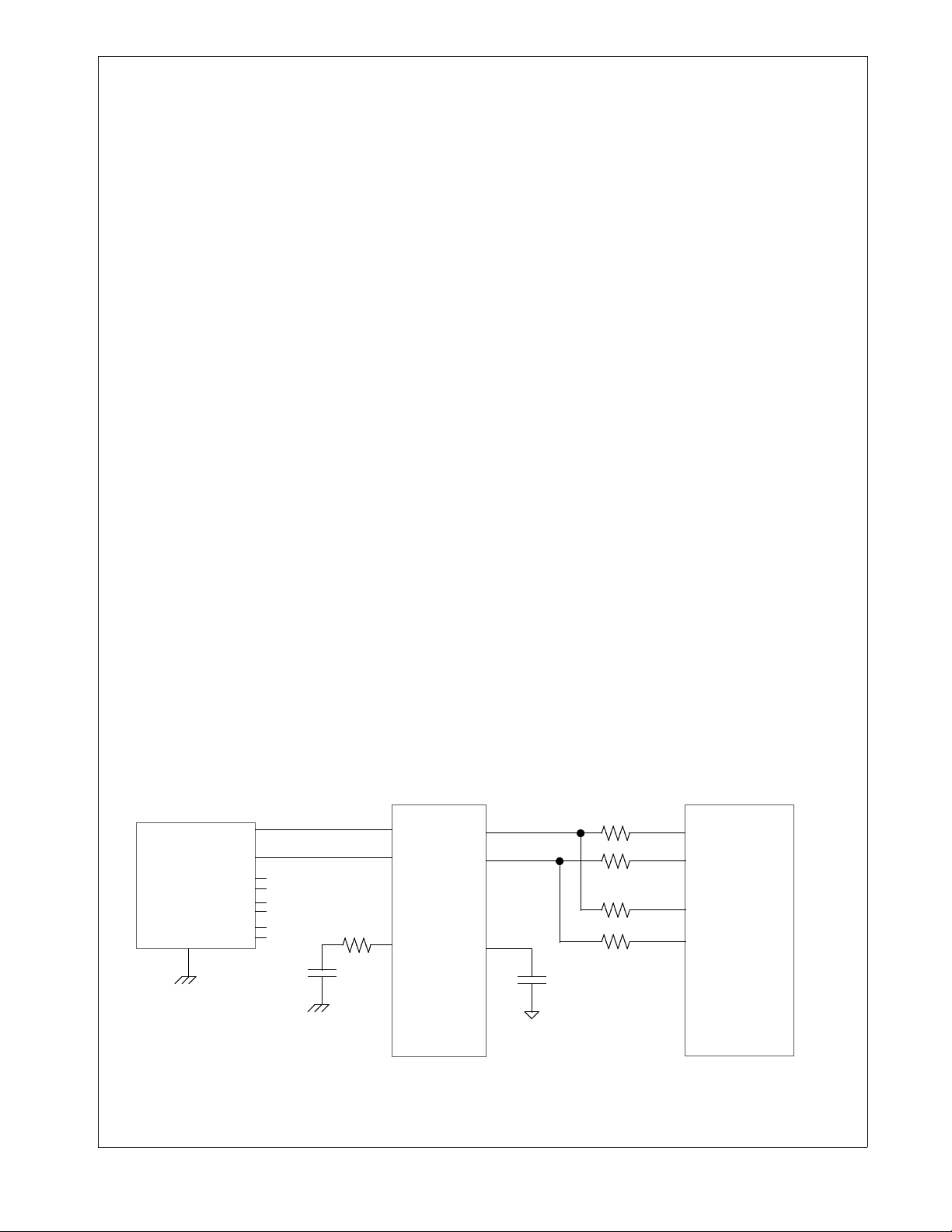

3.2 Twisted Pair Interface

The Twisted Pair Interface consists of four differential

transmit pairs (Channels A, B, C, and D) and four differen tial receive pairs (Channels A, B, C, and D). Each transmit

pair is connected to its’ corresponding receive pair through

47 Ω and 150 Ω resistors respectively (The two 47 Ω resistors in combination with the so urce imp edanc e of the transmitter will form a 100 Ω differential input impedance as

seen from the line. This is required to minimize reflections.). Figure 2 shows a typical connection for Channel A.

Channels B, C, and D are identical. The combined transmit

and receive trace then goes directly to 1:1 magnetics. We

currently recommend using the Pulse H-5007 or Pulse H-

5008. Both magnetics are pin for pin compatible, but with

different package orientations. The H-5007/8 has an isolation transformer followed by a common mode choke to

reduce EMI. There is an additional auto-transformer which

is center tapped. These 2 transformers as well as other

suppliers’ transformers from Halo, Belfuse, Transpower,

Midcom, etc. should be evaluated for best performance for

each design. See Table 9 and Table 10.

Ω

— Place the 47

1% transmit r esistors as close as possi-

ble to the TXDA+/-, TXDB+/-, TXDC+/-, and TXD+/- pins

— Place the 150

Ω 1% receive resistors close as possible

to the RXDA+/-, RXDB+/-, RXDC+/-, and RXDD+/- pins.

— All traces to and from the twisted pair interface should

have a controlled impedance of 50 Ω to the ground

plane. This is a strict requirement. They should be as

close in length to each other as possible to prevent mismatches in delay which will increase common mode

noise.

Ideally there should be no crossovers or vias on the signal

paths of these traces.

3.3 MAC Interface

The DP83861 can be configured in one of two different

modes:

— GMII (Gigabit Media Indep endent Interface) MODE : This

interfaces is used to support 802.3z compliant 1000

Mb/s MACs.

— MII (Media Independent Inte rface) MODE: This interface

is used to support 10/100 Mb/s MACs.

Only one mode can be supported at a time, since the GMII

and MII share some pins in common.

These outputs are capable of driving 35 pF under worst

case conditions. Thes e outputs were not designed to drive

multiple loads, connectors, backplanes, or cabl es. It is recommended that the outputs be series terminated through a

resistor as close to the output pins as possible. The purpose of the series termination is to reduce reflections on

the line. The value of the series termination and length of

trace the output c an driv e will de pend on the dr iver out put

impedance, the characteristic impedance of the PCB trace

(we recommend 50

(capacitance/inch), and the load capacitance (MAC input).

For short traces, less than 0.5 inches, the series resistors

may not be required, thus reducing component count.

However, each specific board design should be evaluated

for reflections and signal integrity to determine the need for

the series terminations. As a general rule of thumb, if the

trace length is less than 1/6 of the equivalent length of the

Ω

), the distributed trace capacitance

DP83861

RJ-45

1

2

3

6

4

5

7

8

A+

AB+

BC+

CD+

D-

100 pF

3 kV

75

MX4+

MX4-

Ω

MCT4

TD4+

TD4-

TCT4

0.1

µF

47

47

150

150

Ω

Ω

Ω

Ω

PULSE H-5007

DP83861

TXDA+

TXDA-

RXDA+

RXDA-

Chassis Ground

Chassis Ground

Only the connections for one of the twisted pair channels is shown. Connections for channels B, C, D are similar.

Fi

ure 2. Twisted Pair / Magnetics Interface (Channel A Only)

18 www.national.com

rise and fall times then the series terminations might not be

g

g

g

g

needed. Equivalent length of rise time = Rise time (ps) /

Delay (ps/inch). Rise and fall times are required to be less

than 1 ns for some GMII s ignal s, typi cally being in the ord er

of 500 ps for those pins. (i.e. RX_CLK, GTX_CLK). Delay

typically = 170 ps/inch on a FR4 board. Using the above

numbers we get critical trace length = (1/6) *(500/ 170) =

0.5 inches.

.In summary:

— Place series termination resis tors as close to the pi ns as

possible.

— Keep capacitance < 35 pF as seen by the output.

— Keep output trace lengths approximately the same

length to avoid skew problems.

— Keep input trace lengths approximately the same length

to avoid skew problems.

All GMII traces should be impedance controlled. 50 ohms

to ground plane is recommended, but this is not a strict

requirement and the board designer can experiment with

different values if needed, to minimize reflections

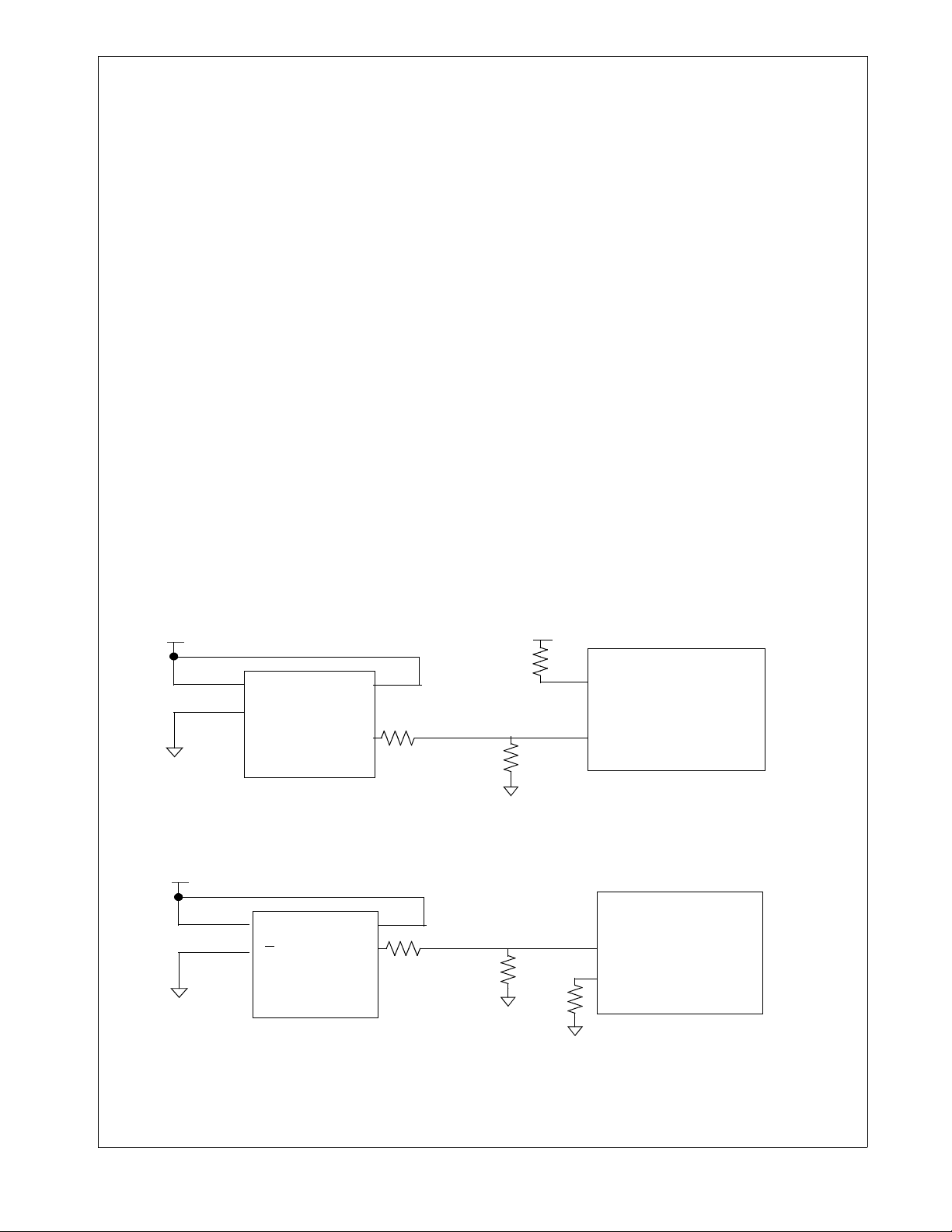

3.4 Clocks

REF_CLK is capable of using either a 125 MHz oscillator

or a 25 MHz oscillator. The 125 MHz or 25 MHz clock is

used by the internal PLL to generate the various clocks

needed both internally and externally. This input should

come from an 125 MH z os ci lla tor (+/- 50 ppm, < 25ps cycle

to cycle jitter, < 200 ps accumulative jitter) or a 25 MHz

oscillator (+/- 50 ppm, < 25ps cycle to cycle jitter, < 200 ps

accumulative jitter). For 125 MHz operation, REF_SEL (pin

154) must be either connected directly to a 3.3 V supply or

pulled high through a 2 KΩ resistor t o a 3 .3 V supply. When

using a 25 MHz oscillator the REF_SEL (pin 154) should

be pulled to ground through a 2 KΩ resistor.

The cycle to cy cle ji tter an d the lo ng te rm accum ulati ve jitter (accumulative jitter can be measured using an osilloscope with a delay trigger set at 10 µs or using a

Wavecrest TIA). Both the 125 MHz and 25 MHz oscillators

should have less than 25 ps of cycle to cycle jitter and less

than 200 ps accumulative jitter for optimal cable performance.

Te st in

using the 25 MHz oscillator showed

that the DP83861 will exceed the 100 meter cable

th requirement in 1000 Mb/s, 100 Mb/s and 10

len

Mb/s, but the transmit jitter in 1000 mb/s mode will be

outside the IEEE spec. 40.6. 1.2 .5 (tra nsm it cl ock jitter +

transmit output jitter) of less than 300 ps.

The clock signal requires the same termination considerations mentioned in the MAC interface section. The clock

signal might require both series source termination (R

the output of the clock source and/or load termination (RT)

S

) at

close to the PHY to eliminate reflections. This will depend

on the distance of the clock source from the PHY clock

input, the source impedance of the clock source, as well as

the board impedance for the clock line considered as a

transmissio n line. Typically no ser ies or lo ad term inatio n is

required for short traces. For long traces a series resistor is

recommended. Unlike load termination, this doesn’t add to

the load current. The value of the series termination resistor has to be chosen to match the line impedance. As an

example, if the clock source has output impedance of 20Ω

and the clock tr ace has transm ission lin e impedance Zo =

50Ω then Rs = 50 - 20 = 30Ω.

DP83861

VDD = 3.3 V

GND

VDD = 3.3 V

V

DD

125 M Hz O sc

+ 50 ppm

< 2 5 p s Jitte r

(Cycle to Cycle)

< 200 ps Jitter

(Accumulative)

V

DD

25 M Hz O sc

GND

+ 50 ppm

< 2 5 p s J itter

(Cycle to Cycle)

< 200 ps Jitter

(Accumulative)

VDD = 3.3 V

DP83861

2K

Ω

ENA

Tie high

Rs

(Optional)

ure 3. 125 MHz Oscillator Option

Fi

Zo

R

(Optional)

T