NSC DP83847ALQA56A Datasheet

February 2002

DP83847 DsPHYTER II — Single 10/100 Ethernet Transceiver

DP83847 DsPHYTER II — Single 10/100 Ethernet Transceiver

General Description

The DP83847 is a full feature single Physical Layer device

with integrated PMD sublayers to support both 10BASE-T

and 100BASE-TX Ethernet protocols over Category 3 (10

Mb/s) or Category 5 unshielded twisted pair cables.

The DP83847 is designed for easy implementation of

10/100 Mb/s Ethernet hom e or office solutions. It in terfa ce s

to Twisted Pair media via an external transformer. This

device interface s direc tly to M A C de vi ces th roug h the IEEE

802.3u standard Media Independent Interface (MII) ensuring interoperability between products from different vendors.

The DP83847 utilizes on chip Digital Signal Processing

(DSP) technology and digital Phase Lock Loops (PLLs) for

robust performance under all operating conditions,

enhanced noise immunity, and lower external component

count when compared to analog solutions.

Applications

■ LAN on Motherboard

■ Embedded Applications

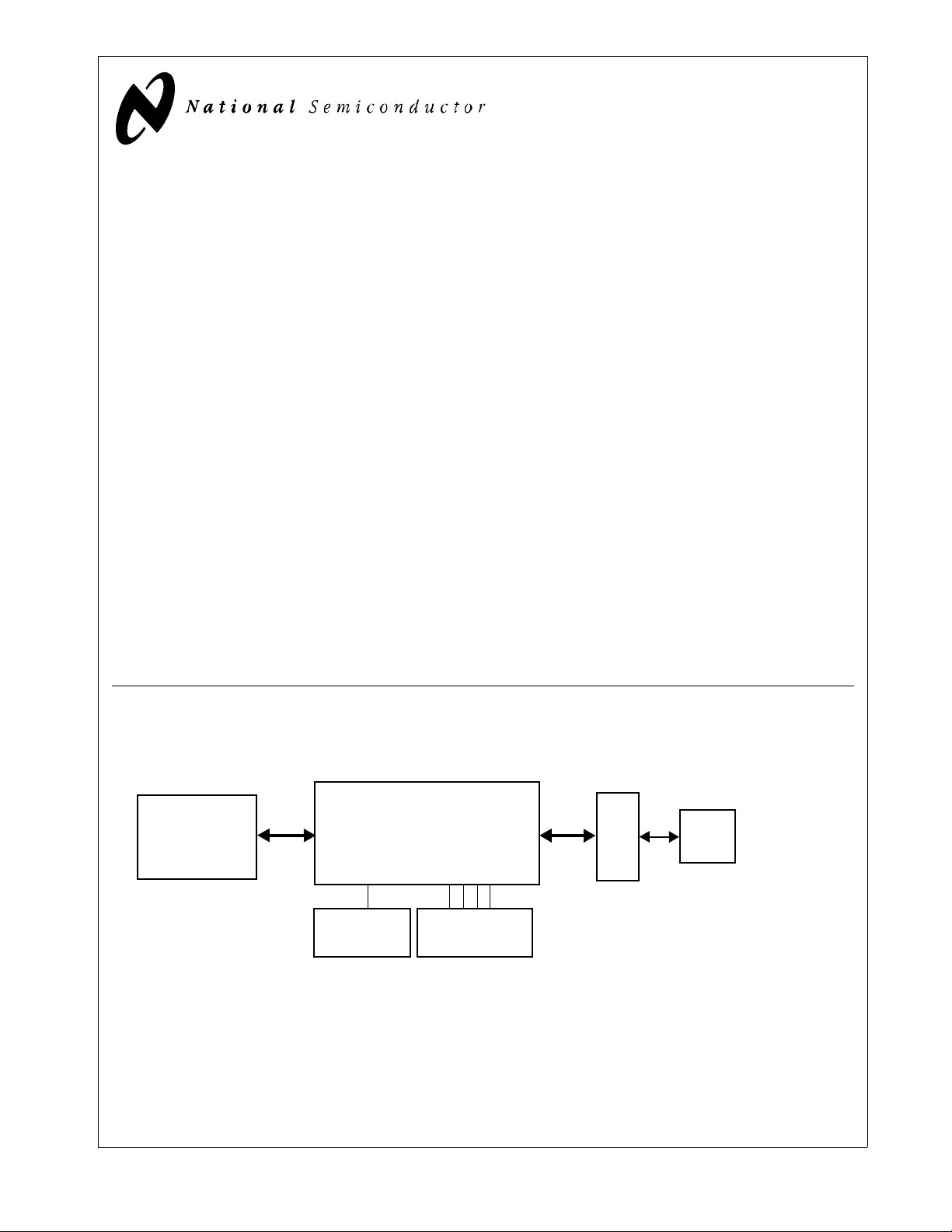

System Diagram

Features

■ Low-power 3.3V, 0.18µm CMOS technology

■ Power consumption < 351mW (typical)

■ 5V tolerant I/Os

■ 5V/3.3V MAC interface

■ IEEE 802.3 ENDEC, 10BASE-T transceivers and filters

■ IEEE 802.3u PCS, 100BASE-TX transceivers and filters

■ IEEE 802.3 compliant Auto-Negotiation

■ Output edge rate control eliminates external filtering for

Transmit outputs

■ BaseLine Wander compensation

■ IEEE 802.3u MII (16 pins/port)

■ LED support (Link, Rx, Tx, Duplex, Speed, Collision)

■ Single register access for complete PHY status

■ 10/100 Mb/s packet loopback BIST (Built in Self Test)

■ 56-pin LLP package (9w) x (9l) x (.75h) mm

Ethernet MAC

MII

25 MHz

Clock

©2002 National Semiconductor Corporation

DP83847

10/100 Mb/s

DsPHYTER II

Status

LEDs

Typical DsPHYTER II application

Magnetics

RJ-45

10BASE-T

or

100BASE-TX

www.national.com

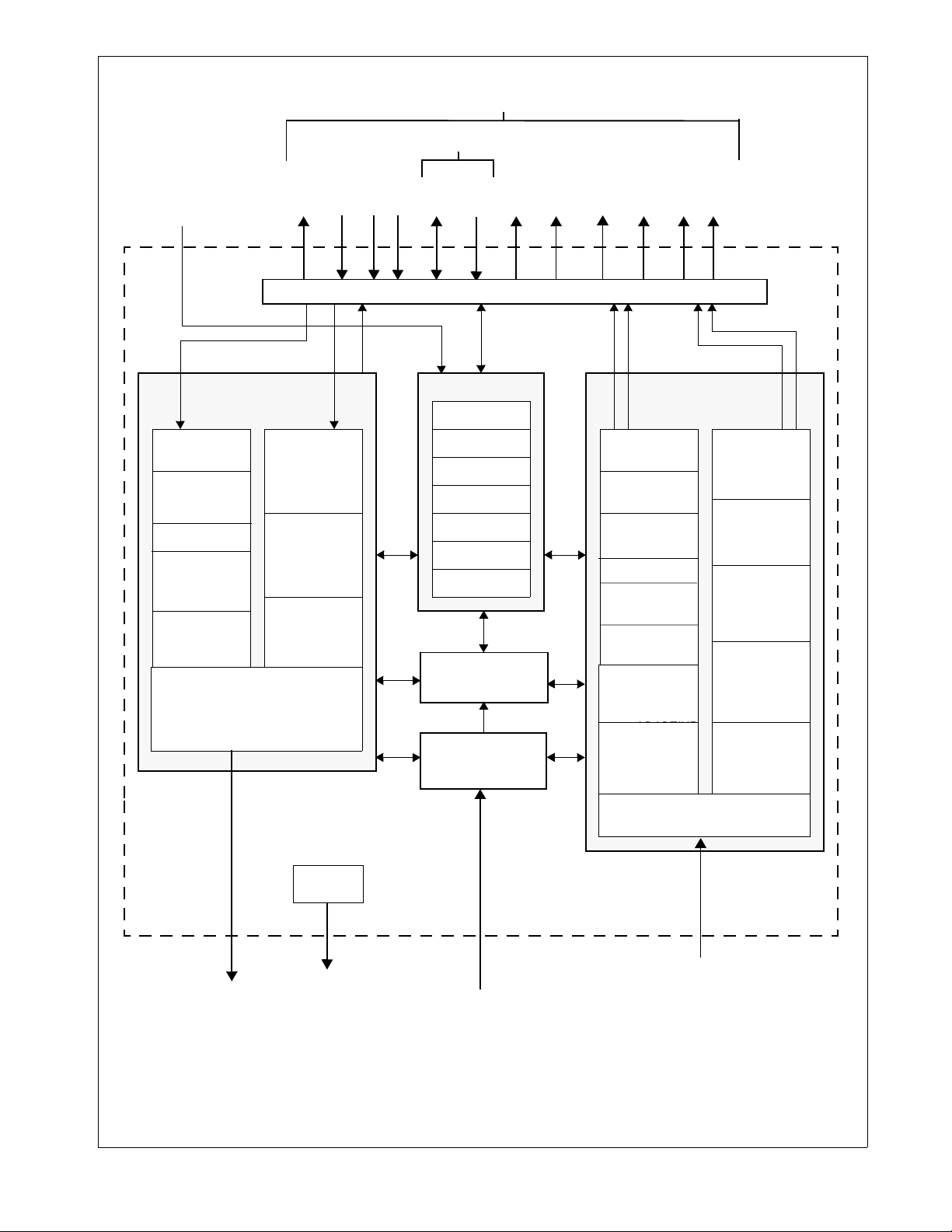

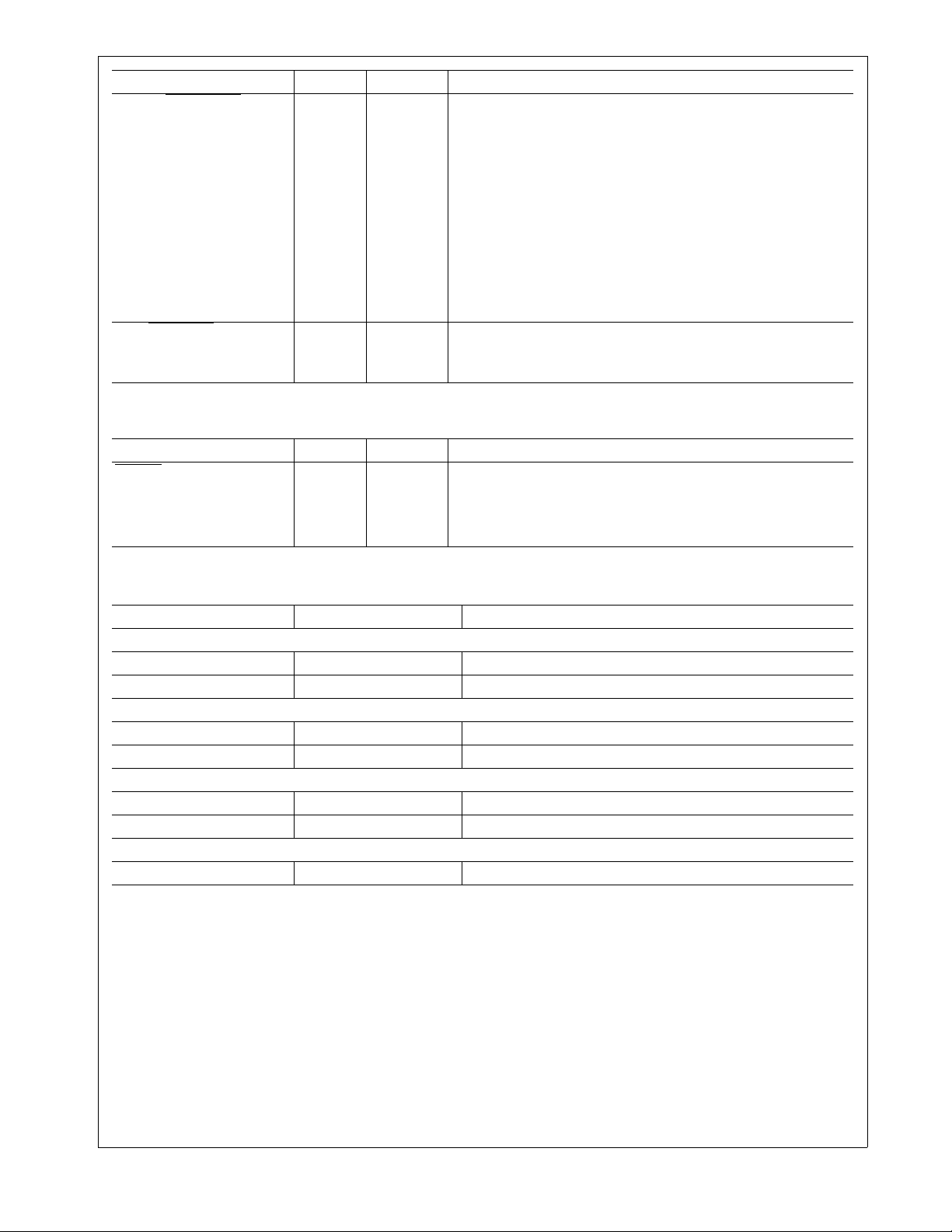

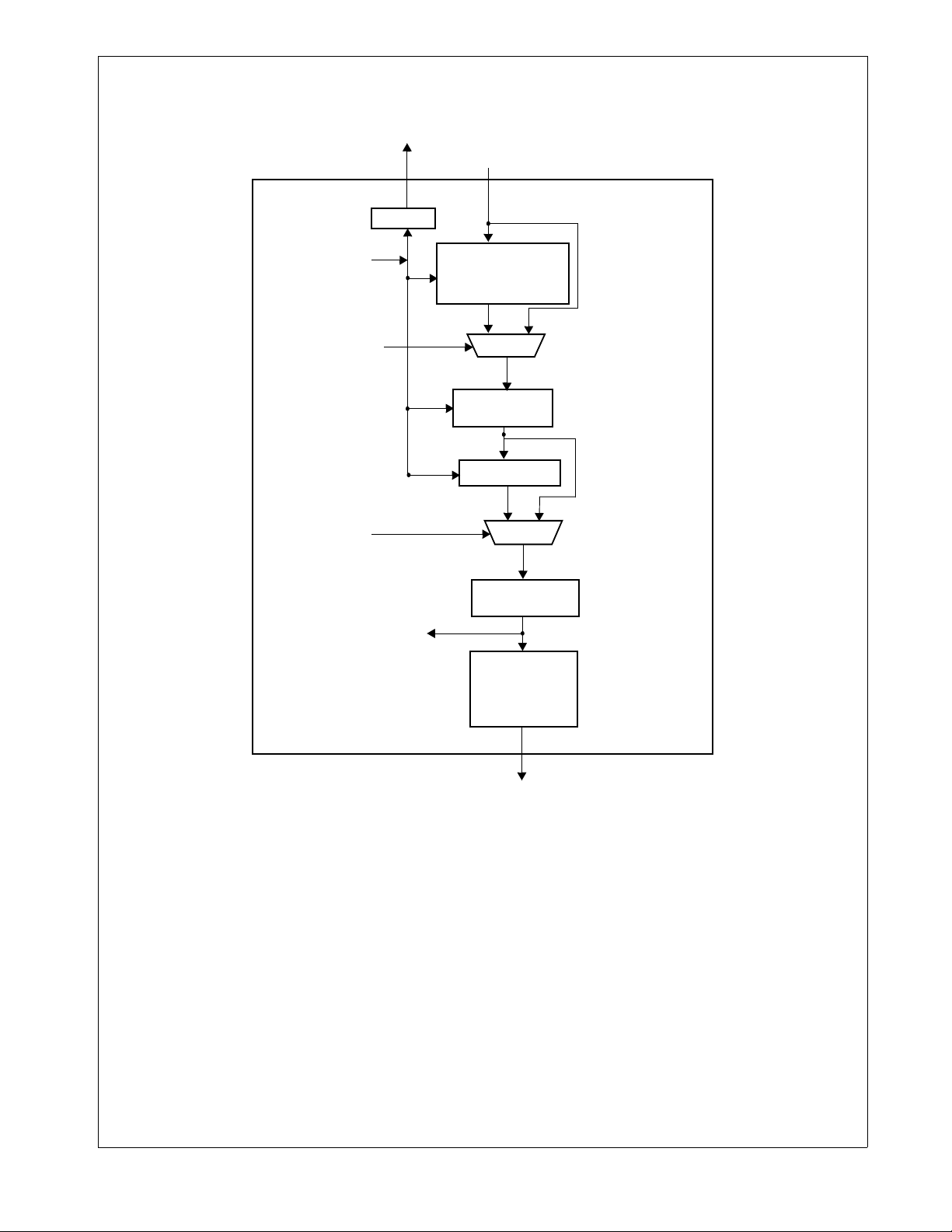

MII

DP83847

HARDWARE

CONFIGURATION

PINS

(AN_EN, AN0, AN1)

(PAUSE_EN)

(LED_CFG, PH YAD)

TX_DATA

TRANSMIT CHANNELS &

STATE MACHINES

100 Mb/s 10 Mb/s

4B/5B

ENCODER

PARALLEL TO

SERIAL

SCRAMBLER

NRZ TO NRZI

ENCODER

BINARY TO

MLT-3

ENCODER

10/100 COMMON

OUTPUT DRIVER

TX_CLK

TXD[3:0]

TX_DATA

NRZ TO

MANCHESTER

ENCODER

LINK PULSE

GENERATOR

TRANSMIT

FILTER

TX_ER

TX_CLK

SERIAL

MANAGEMENT

TX_EN

MDIO

MII INTERFACE/ CO NTROL

REGISTERS

PHY ADDRESS

AUTO

NEGOTIATION

BASIC MODE

CONTROL

PCS CONTROL

10BASE-T

100BASE-TX

AUTO-NEGOTIATION

STATE MACHINE

CLOCK

GENERATION

MII

COL

MDC

CRS

RX_DV

RX_ER

RX_DATARX_CLK

RECEIVE CHANNELS &

4B/5B

DECODER

CODE GROUP

ALIGNMENT

SERIAL TO

PARALLEL

DESCRAMBLER

NRZI TO NRZ

DECODER

CLOCK

RECOVERY

MLT-3 TO

BINARY

DECODER

ADAPTIVE

BLW

AND EQ

COMP

RXD[3:0]

STATE MACHINES

100 Mb/s 10 Mb/s

RX_CLK

RX_DATA

RX_CLK

MANCHESTER

TO NRZ

DECODER

CLOCK

RECOVERY

LINK PULSE

DETECTOR

RECEIVE

FILTER

SMART

SQUELCH

TD±

LED

DRIVERS

LEDS

SYSTEM CLOCK

REFERENCE

Figure 1. Block Diagram of the 10/100 DSP based core.

2 www.national.com

10/100 COMMON

INPUT BUFFER

RD±

Table of Content

1.0 Pin Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5

1.1 MII Interfa ce . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

1.2 10 Mb/s and 100 Mb/s PMD Interface . . . . . . . . . .6

1.3 Clock Inte r fa ce . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

1.4 Special Connections . . . . . . . . . . . . . . . . . . . . . . . 7

1.5 LED Interfa ce . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

1.6 Strapping Options/Dua l Pu r p o se Pins . . . . . . . . . . 8

1.7 Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

1.8 Power and Ground Pin . . . . . . . . . . . . . . . . . . . . . 9

1.9 Package Pin Assignments . . . . . . . . . . . . . . . . . .10

2.0 Confi guration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

2.1 Auto-Negotiation . . . . . . . . . . . . . . . . . . . . . . . . .11

2.2 PHY Address and LEDs . . . . . . . . . . . . . . . . . . . 12

2.3 LED INTERFACES . . . . . . . . . . . . . . . . . . . . . . .13

2.4 Half Duple x vs. Full Dup l e x . . . . . . . . . . . . . . . . . 13

2.5 MII Isolate Mode . . . . . . . . . . . . . . . . . . . . . . . . .14

2.6 Loopback . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14

2.7 BIST . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

3.0 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . .15

3.1 802.3u MII . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

3.2 100BASE-TX TRANSMITTER . . . . . . . . . . . . . . .16

3.3 100BASE-TX RECEIVER . . . . . . . . . . . . . . . . . . 20

3.4 10BASE-T TRANSCEIVER M OD ULE . . . . . . . . . 23

3.5 TPI Networ k Ci rcuit . . . . . . . . . . . . . . . . . . . . . . . 24

3.6 ESD Protect i o n . . . . . . . . . . . . . . . . . . . . . . . . . .25

3.7 Crystal Osci llato r Circuit . . . . . . . . . . . . . . . . . . .26

3.8 Reference Bypass Couple . . . . . . . . . . . . . . . . . .26

4.0 Reset Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

4.1 Hardware R e se t . . . . . . . . . . . . . . . . . . . . . . . . . . 26

4.2 Software R e s e t . . . . . . . . . . . . . . . . . . . . . . . . . .26

5.0 Regis t e r B lo c k . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

5.1 Register Definition . . . . . . . . . . . . . . . . . . . . . . . .29

5.2 Extended Registers . . . . . . . . . . . . . . . . . . . . . . .37

6.0 Elect rical Speci fications . . . . . . . . . . . . . . . . . . . . . . .44

6.1 Reset Timi n g . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

6.2 PGM Clock Timing . . . . . . . . . . . . . . . . . . . . . . .47

6.3 MII Serial Management Timing . . . . . . . . . . . . . .47

6.4 100 Mb/s Timing . . . . . . . . . . . . . . . . . . . . . . . . .48

6.5 10 Mb/s Tim i n g . . . . . . . . . . . . . . . . . . . . . . . . . .52

6.6 Loopback Timing . . . . . . . . . . . . . . . . . . . . . . . . .57

6.7 Isolation Timing . . . . . . . . . . . . . . . . . . . . . . . . . .59

7.0 Physical Dimensions . . . . . . . . . . . . . . . . . . . . . . . .60

DP83847

3 www.national.com

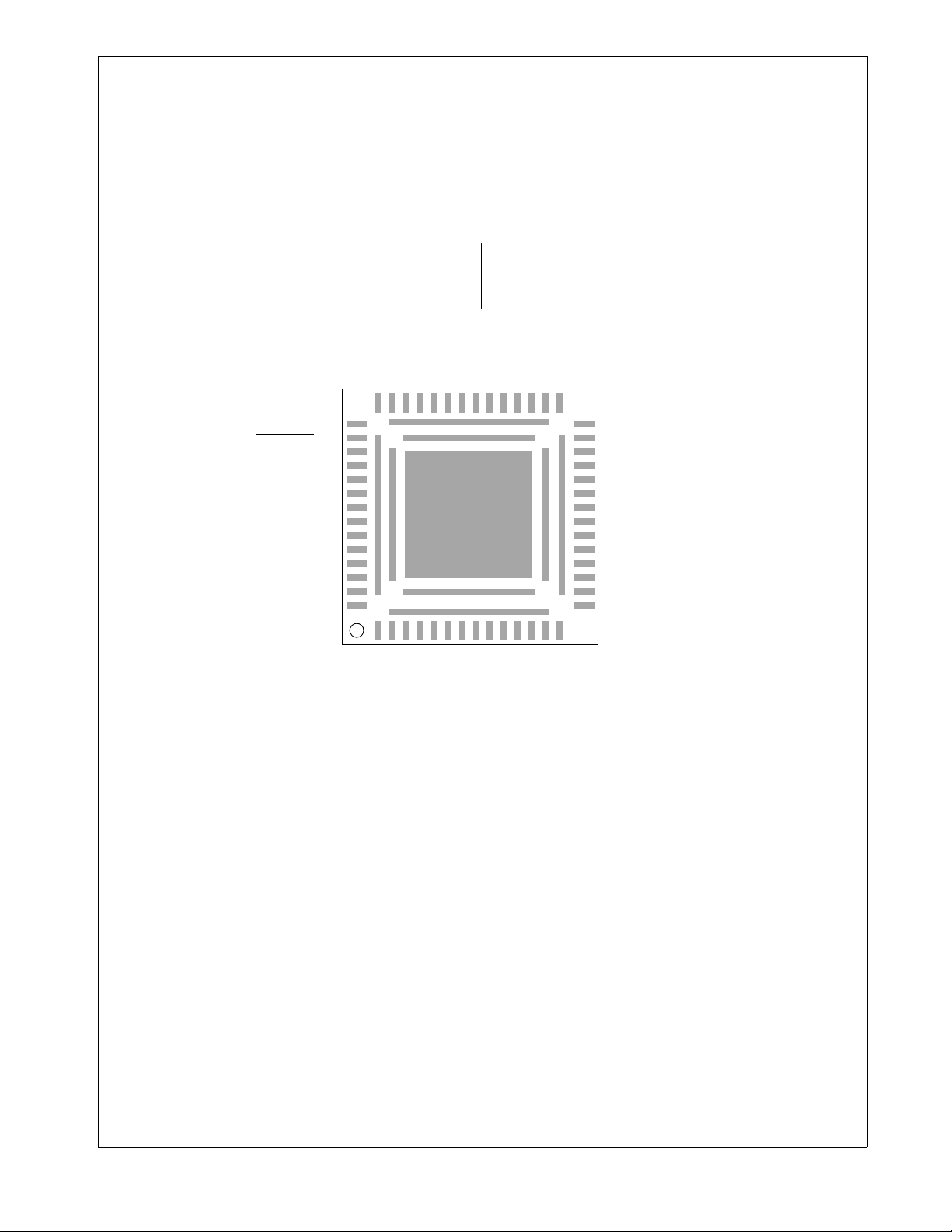

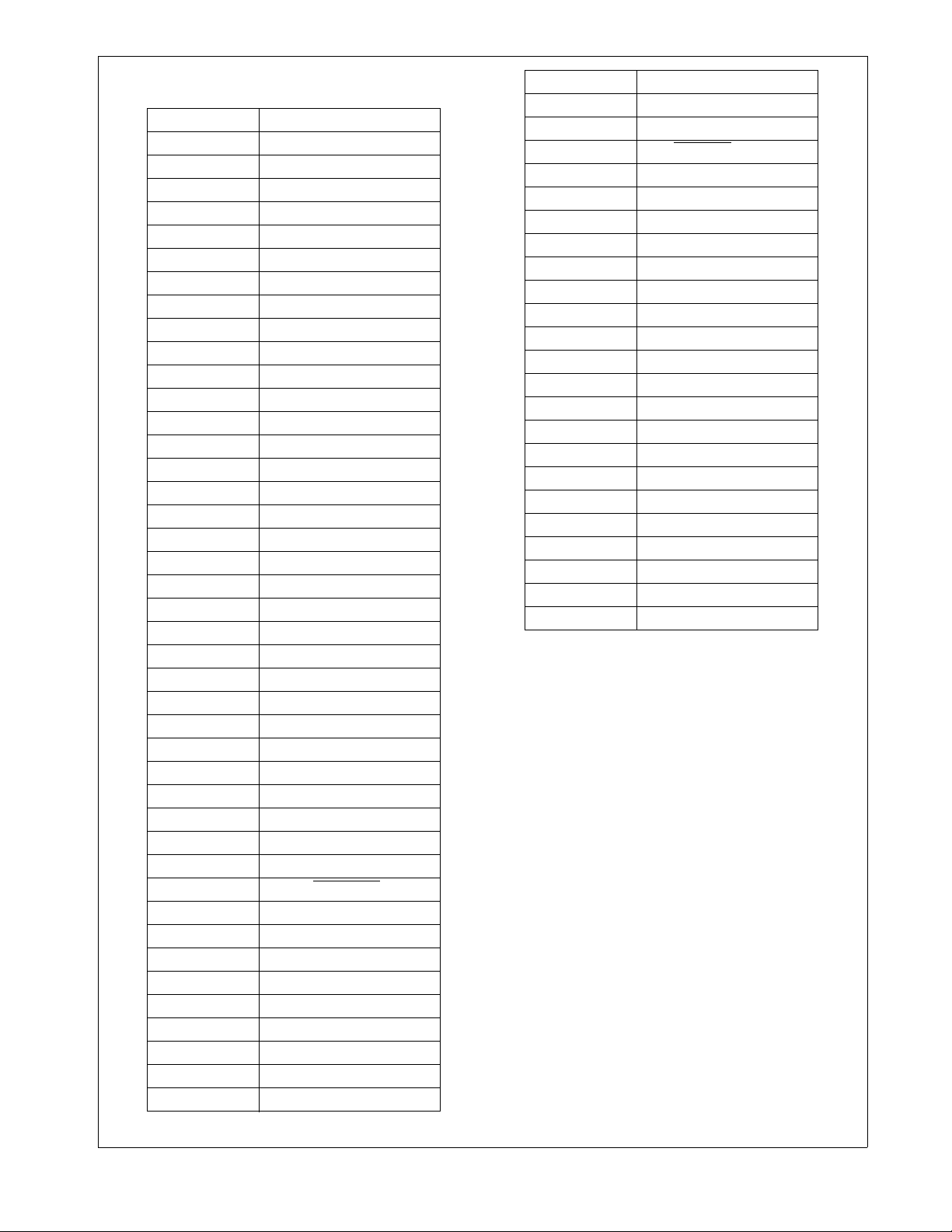

Pin Layout

42 C1

41 TXD_3

40 TXD_2

39 TXD_1

38 TXD_0

37 TX_EN

36 TX_CLK

35 TX_ER

DP83847

34 RESERVED

33 RX_ER/PAUSE_EN

32 RX_CLK

31 RX_DV

30 RXD_0

29 RXD_1

COL 43

RESERVED 44

CRS/LED_CFG

RESET 46

RESERVED 47

X2 48

X1 49

RESERVED 50

RESERVED 51

RESERVED 52

RESERVED 53

RESERVED 54

RESERVED 55

VDD 56

45

61

59

RESERVED 1

62

60

65 Gnd

64

63

58

57

RD+ 7

RD - 6

RBIAS 3

RESERVED 2

RESERVED 4

RESERVED 5

TD- 11

TD+ 10

RESERVED 8

RESERVED 9

RESERVED 12

VDD 14

RESERVED 13

28 VDD

27 RXD_2

26 RXD_3

25 MDC

24 MDIO

23 LED_DPLX/PHYAD0

22 LED_COL/PHYAD1

21 LED_GDLNK/PHYAD2

20 LED_TX/PHYAD 3

19 LED_RX/PHYAD4

18 LED_SPEED

17 AN_EN

16 AN_1

15 AN_0

Top View

Leadless Leadframe Package (LLP)

Order Number DP83847 ALQA 5 6A

NS Package Number LQA-56A

Note 1: Pins 57 to 65 required soldering care. Check Package Instruction, AN-1187, for details.

4 www.national.com

1.0 Pin Descriptions

The DP83847 pins are c lassifi ed into the fol lowing i nterfac e

categories (each interface is described in the sections that

follow):

— MII Interface

— 10/100 Mb/s PMD Interface

— Clock Interface

— Special Connect Pins

— LED Interface

— Strapping Options/Dual Function pins

—Reset

— Power and Ground pins

Note: Strapping pin option (BOLD) Please see Section 1.6

for strap definitions.

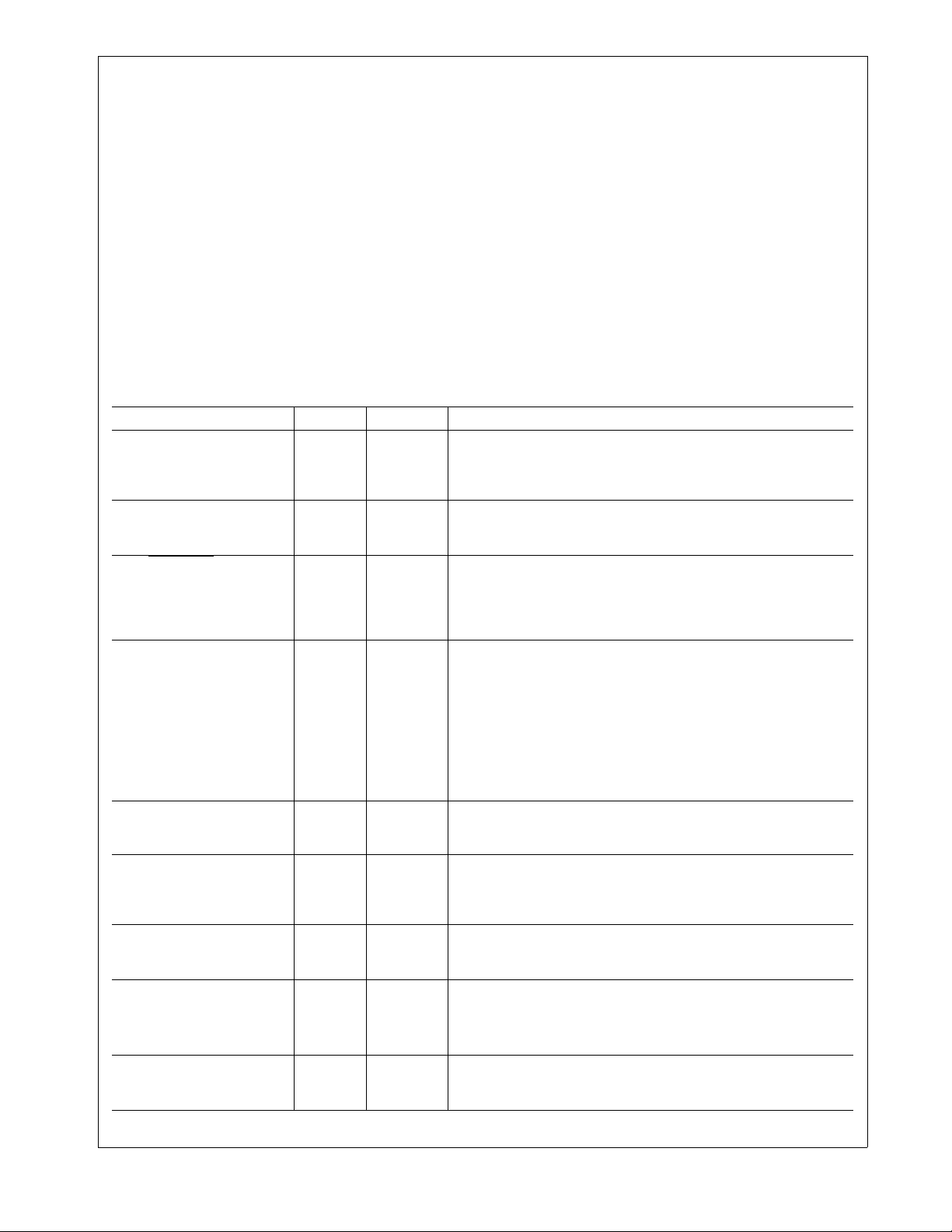

1.1 MII Interface

Signal Name Type LLP Pin # Description

MDC I 25 MANAGEMENT DATA CLOCK: Synchronous clock to the M DIO

MDIO I/O, OD 24 MANAGEMENT DATA I/O: Bi-directional management instruc-

CRS/LED_CFG

COL O 43 COLLISION DETECT: Asserted high to indicate detection of a

TX_CLK O 36 TRANSMIT CLOCK: 25 MHz Transmit clock outputs in

TXD[3]

TXD[2]

TXD[1]

TXD[0]]

TX_EN I 37 TRANSMIT ENABLE: Active high input in dicates t he presenc e of

TX_ER I 35 TRANSMIT ERROR: In 100MB/s mode, when this signal is high

RX_CLK O, PU 32 RECEIVE CLOCK: Provides the 25 MHz recovered receive

O, S 45 CARRIER SENSE: Asserted high to indicate the presence of car-

I 41, 40, 39, 38TRANSMIT DATA: Transmit data MII input pins that accept nib-

All DP83847 signal pins are I/O cells regardless of the particular use. Below definitions define the functionality of the

I/O cells for each pin.

Type: I Inputs

Type: O Outputs

Type: I/O Input/Output

Type OD Open Drain

Type: PD,PU Internal Pulldown/Pullup

Type: S Strapping Pin (All strap pins except PHY-

AD[0:4] have internal pull-ups or pulldowns. If the default strap value is needed

to be changed then an ext ernal 5 kΩ resistor

should be used. Please see Table 1.6 on

page 8 for details.)

management data input/output serial interface which may be

asynchronous to transmit and receive clocks. The maximum clock

rate is 25 MHz with no minimum clock rate.

tion/data signal th at m ay be s ourc ed by th e st ation management

entity or the PHY. This pin requires a 1.5 kΩ pullup resistor.

rier due to receive or transmit activity in 10BASE-T or 100BASETX Half Duple x Mo des , while in full du ple x mo de ca rrier sense is

asserted to indicate the presence of car rier due only to re ceive activity.

collision condition (simultaneous transmit and receive activity) in

10 Mb/s and 100 Mb/s Half Duplex Modes.

While in 10BASE-T Half Duplex mode with Heart beat enabled this

pin are also asserted for a duration of approximately 1µs at the

end of transmission to indicate heartbeat (SQE test).

In Full Duplex Mode, for 10 Mb/s or 100 Mb/s operation, this signal is always logic 0. There is no heartbeat function during 10

Mb/s full duplex operation.

100BASE-TX mode or 2.5 MHz in 10 BASE-T mod e derived f rom

the 25 MHz reference clock.

ble data synchronous to the TX_CLK (2.5 MHz in 10BASE-T

Mode or 25 MHz in 100BASE-TX mode).

valid nibble data o n data i nputs , TXD[3 :0] for b oth 100 Mb/s o r 10

Mb/s nibble mode.

and the corresponding TX_EN is active the HALT s y mbol is substituted for data.

In 10 Mb/s this input is ignored.

clocks for 100BASE-TX mode and 2.5 MHz for 10BASE-T nibble

mode.

DP83847

5 www.national.com

Signal Name Type LLP Pin # Description

RXD[3]

RXD[2]

RXD[1]

RXD[0]

RX_ER/PAUSE_EN

RX_DV O 31 RECEIVE DATA VALID: Asserted high to indi ca te that va lid data

O, PU/PD 26, 27, 29, 30RECEIVE DATA: Nibble wide receive data (synchronous to cor-

responding RX_CLK, 25 MHz for 100BASE-TX mode, 2.5 MHz

for 10BASE-T nibble mode). Data is driven on the falling edge of

RX_CLK. RXD[2] has an internal pull-down resistor. The remaining RXD pins have pull-ups.

S, O, PU 33 RECEIVE ERROR: Asserted high to i ndi ca te that an invalid s ym -

bol has been detected within a received packet in 100BASE-TX

mode.

is present on the corresponding RXD[3:0] for nibble mode. Data

is driven on the falling edge of the corresponding RX_CLK.

1.2 10 Mb/s and 100 Mb/s PMD Interface

Signal Name Type LLP Pin # Description

TD+, TD- O 10, 11 Differential comm on dri ver tran smit output . Th ese di fferenti al out -

RD-, RD+ I 6, 7 Differential receive input. These differential inputs can be config-

puts are configurable to e ither 10BASE-T o r 100BASE- TX sig naling.

The DP83847 will a utomat ically con figure th e common dri ver out puts for the proper signal type as a result of either forced configuration or Auto-Negotiation.

ured to accept either 100BASE-TX or 10BASE-T signaling.

The DP83847 will automatically configure the receive inputs to

accept the proper signal type as a result of either forced configuration or Auto-Negotiation.

DP83847

6 www.national.com

1.3 Clock Interface

Signal Name Type LLP Pin # Description

X1 I 49 REFERENCE CLOCK INPUT 25 MHz: This pin is the primary

clock reference inpu t for the DP 8384 7 and mu st be c onnect ed to

a 25 MHz 0.005% (±50 ppm) clock source. The DP83847 supports CMOS-level oscillator sources.

X2 O 48 REFERENCE CLOCK OUTPUT 25 MHz: This pin is the primary

clock reference output.

1.4 Special Connections

Signal Name Type LLP Pin # Description

RBIAS I 3 Bias Resistor Connection. A 10.0 kΩ 1% resist or shou ld be con-

nected from RBIAS to GND.

C1 O 42 Reference Bypass Re gulator. Parall el caps, 10µ F (Tantalum pre-

RESERVED I/O 1, 2, 4, 5, 8,

9, 12, 13,

34, 44, 47,

50, 51, 52,

53, 54, 55,

61

ferred) and .1µF, should be placed close to C1 and connected to

GND. See Section 3.8 for proper placement.

RESERVED: These pins must be left unconnected

DP83847

1.5 LED Interface

Signal Name Type LLP Pin # Description

LED_DPLX/PHYAD0 S, O 23 FULL DUPLEX LED STATUS: Indicates Full-Duplex status.

LED_COL/PHYAD1 S, O 22 COLLISION LED STATUS: Indicates Collision activity in Half Du-

LED_GDLNK/PHYAD2 S, O 21 GOOD LINK LED STATUS: Indicates Good Link Status for

LED_TX/PHYAD3 S, O 20 TRANSMIT LED STATUS: Indicates transmit activity. LED is on

LED_RX/PHYAD4 S, O 19 RECEIVE LED STATUS: Indicates receive act iv ity. LED is on fo r

LED_SPEED O 18 SPEED LED STATUS: Indicates link speed; high for 100 Mb/s,

plex mode.

10BASE-T and 100BASE-TX.

for activity, off for no activity.

activity, off for no activity.

low for 10 Mb/s.

7 www.national.com

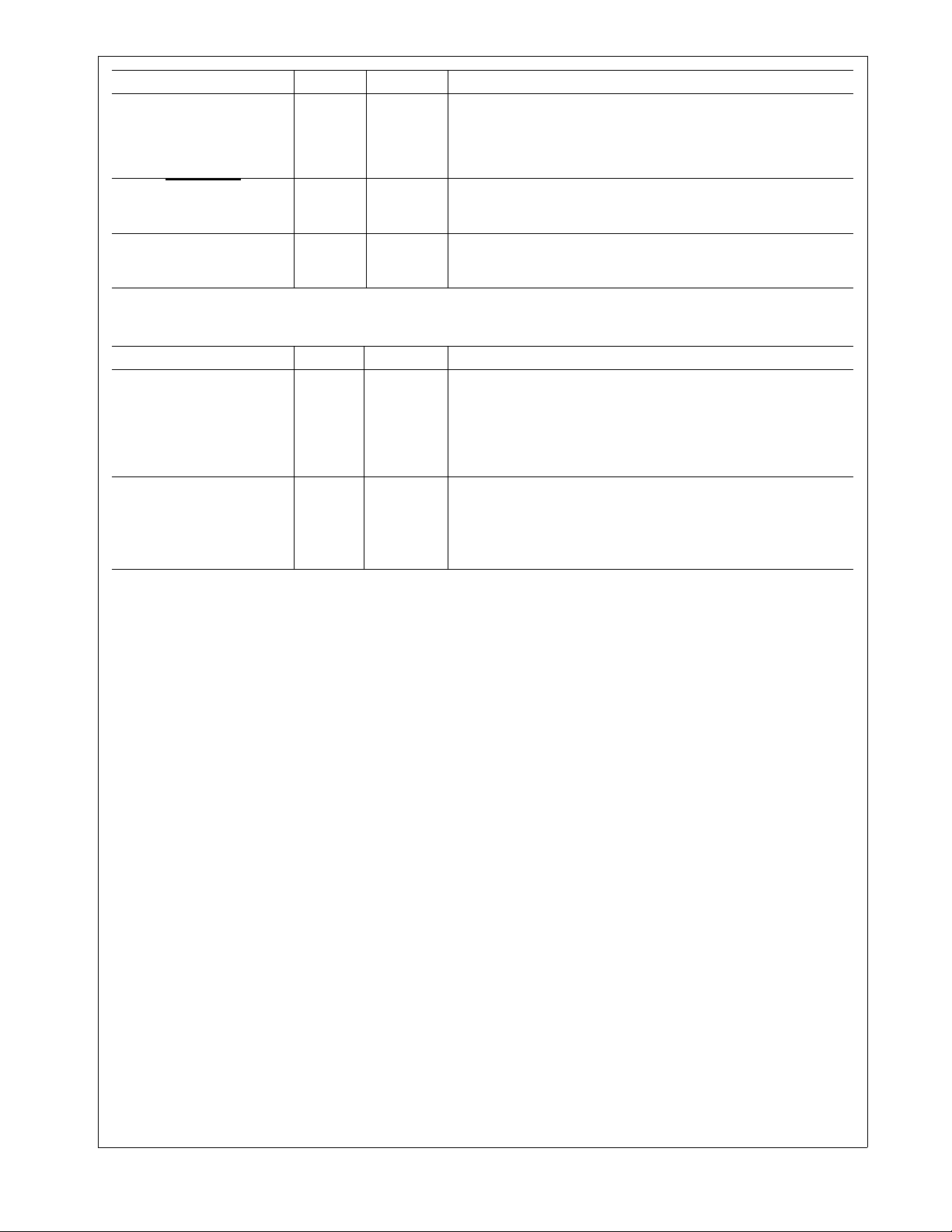

1.6 Strapping Options/Dual Purpose Pins

A 5 kΩ resistor should be used for pull-down or pull-up to

change the default strap option. If the default option is

required, then there is no need for external pull-up or pull

down resistors, sinc e the int ernal pu ll-up or p ull down re sis-

Signal Name Type LLP Pin # Description

LED_DPLX/PHYAD0

LED_COL/PHYAD1

LED_GDLNK/PHYAD2

LED_TX/PHYAD3

LED_RX/PHYAD4

AN_EN

AN_1

AN_0

S, O 23

22

21

20

19

S, O, PU 17

16

15

PHY ADDRESS [4:0]: The DP83847 provid es fiv e PHY address

pins, the state of which a re latc hed in to the PHYC TRL regi ster at

system Hardware-Reset.

The DP83847 supports PHY Address strapping values 0

(<00000>) through 31 (<1 1111>). PHY Address 0 puts the part

into the MII Isolate Mode. The MII isolate mode must be selecte d

by strapping Phy Address 0; changing to Address 0 by register

write will not put the Phy in the MII isolate mode.

The status of these pins are latc hed into the PHY Control Regi ster

during Hardware-Reset. (Pleas e note the se pins have no internal

pull-up or pull-down resistors and they must be strapped high or

low using 5 kΩ resistors.)

Auto-Negotiation Enable: When high enab les Auto-N egotiation

with the capability set by AN O and AN1 pins. W hen low , puts the

part into Forced Mode with the capability set by AN0 and AN1

pins.

AN0 / AN1: These input pins control the forced or advertised operating mode of the DP83847 according to the following table.

The value on these pins is set by connecting the input pins to

GND (0) or V

NEVER be connected directly to GND or V

The value set at this input is latched into the DP83847 at Hardware-Reset.

The float/pull-down sta tus of these pin s ar e latch ed into the Bas ic

Mode Control Register and the Auto_Negotiation Advertisement

Register during Hardware-Reset. After res et is deasserte d, these

pins may switch to outputs so if pull-ups or pull-downs are i m plemented, they should be pulled through a 5 kΩ resistor.

The default is 111 since these pins have pull-ups.

tors will set the default value. Please note that the

PHYAD[0:4] pins have no internal pull-ups or pull-downs

and they must be strapped. Since these pins may have

alternate functions after reset is deasserted, they should

not be connected directly to Vcc or GND.

(1) through 5 kΩ resistors. These pins should

CC

CC.

DP83847

AN_EN AN1 AN0 Forced Mode

0 0 0 10BASE-T, Half-Duplex

0 0 1 10BASE-T, Full-Duplex

0 1 0 100BASE-TX, Half-Duplex

0 1 1 100BASE-TX, Full-Duplex

AN_EN AN1 AN0 Advertised Mode

1 0 0 10BASE-T, Half/Full-Duplex

1 0 1 100BASE-TX, Half /Full-Duplex

1 1 0 10BASE-T Half-Duplex

100BASE-TX, Half-Duplex

1 1 1 10BASE-T, Half/Full-Duplex

100BASE-TX, Half/Full-Duplex

8 www.national.com

Signal Name Type LLP Pin # Description

RX_ER/PAUSE_EN S, O, PU 33 PAUSE ENABLE: This strapping option allows advertisement of

whether or not the DTE(MAC) h as imp lemented b oth the op tional

MAC control sublayer and the pause function as specified in

clause 31 and annex 31B of the IEEE 802.3x specification (Full

Duplex Flow Control).

When left floating the Auto-Negotiation Advertisement Register

will be set to 0, i ndicatin g that Ful l Duplex Fl ow Contro l is not sup ported.

When tied low through a 5 kΩ, the Auto-Negotiation Advertise-

ment Registe r will be set to 1 , indicating th at Full Duplex Fl ow

Control is supported.

The float/ pul l-do wn st atu s of th is pi n is latc hed int o th e Aut o- Negotiation Advertisement Register during Hardware-Reset.

CRS/LED_CFG

S, O

PU

,

45 LED CONFIGURATION: This strapping option defines th e polar-

ity and function of the FDPLX LED pin.

See Section 2.3 for further descriptions of this strapping option.

1.7 Reset

Signal Name Type LLP Pin # Description

RESET

I46RESET: Active Low input that initializes or re-initializes the

DP83847. Asserting thi s pin low fo r at least 1 60 µs wil l force a reset process to occu r which wi ll result in all intern al registe rs re-initializing to their default states as specified for each bit in the

Register Block sect ion and all s trappin g options are re-initialized .

DP83847

1.8 Power and Ground Pin

Signal Name LLP Pin # Description

TTL/CMOS INPUT/OUTPUT SUPPLY

IO_VDD 28, 56 I/O Supply

IO_GND GND I/O Ground

INTERNAL SUPPLY PAIRS

CORE_VDD Internal Digital Core Supply

CORE_GND GND Digital Core Ground

ANALOG SUPPLY PINS

ANA_VDD 14 Analog Supply

ANA_GND GND Analog Ground

SUBSTRATE GROUND

SUB_GND GND Bandgap Substrate connection

9 www.national.com

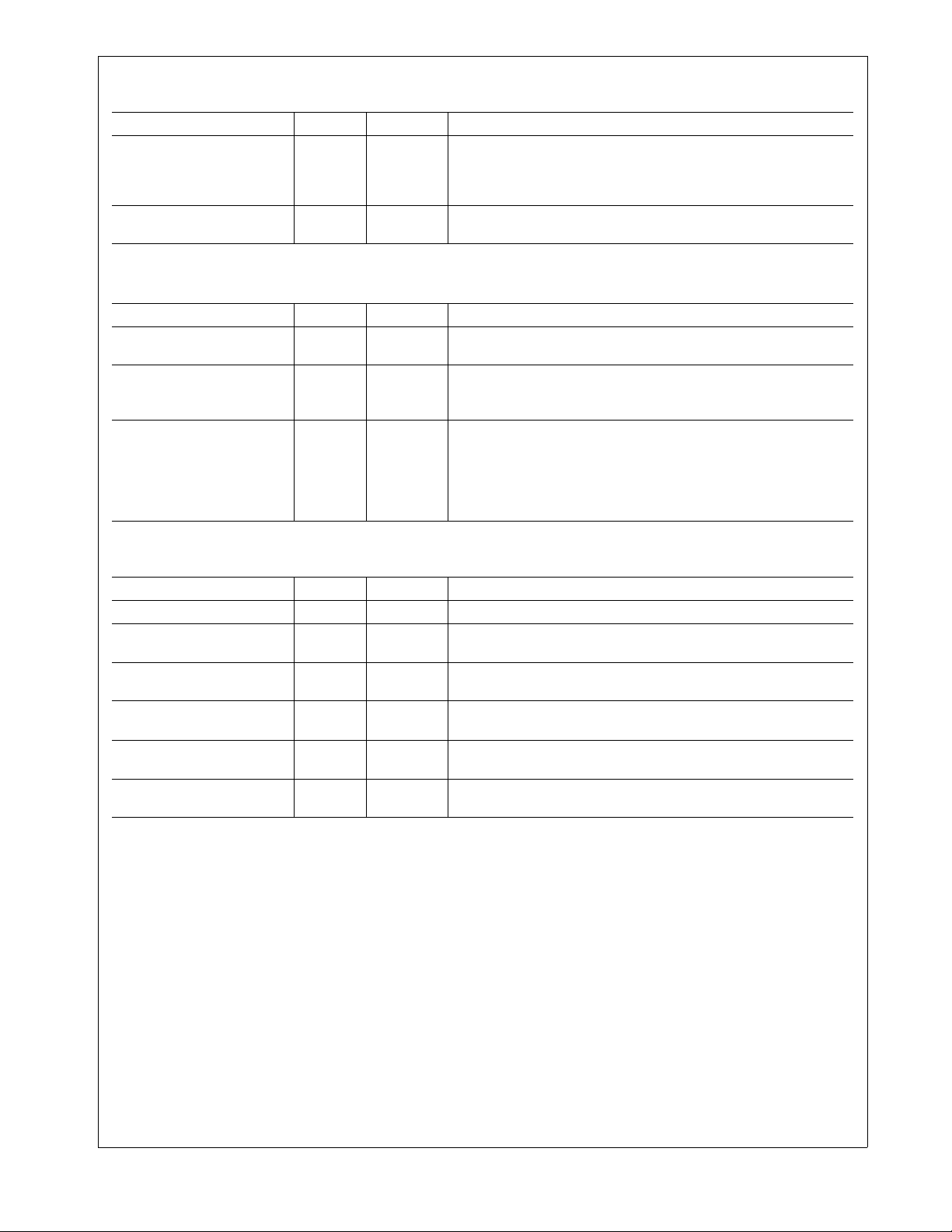

1.9 Package Pin Assignments

LLP Pin # Pin Name

1 RESERVED

2 RESERVED

3 RBIAS

4 RESERVED

5 RESERVED

6 RD7 RD+

8 RESERVED

9 RESERVED

10 TD+

11 TD12 RESERVED

13 RESERVED

14 VDD (ANA_VDD)

15 AN_0

16 AN_1

17 AN_EN

18 LED_SPEED

19 LED_RX /PHYAD4

20 LED_TX /PHYAD3

21 LED_GDLNK/PHYAD2

22 LED_COL /PHYAD1

23 LED_FDPLX /PHYAD0

24 MDIO

25 MDC

26 RXD_3

27 RXD_2

28 VDD (IO_VDD)

29 RXD_1

30 RXD_0

31 RX_DV

32 RX_CLK

33 RX_ER/

34 RESERVED

35 TX_ER

36 TX_CLK

37 TX_EN

38 TXD_0

39 TXD_1

40 TXD_2

41 TXD_3

42 C1

PAUSE_EN

LLP Pin # Pin Name

43 COL

44 RESERVED

45 CRS/

46 RESET

47 RESERVED

48 X2

49 X1

50 RESERVED

51 RESERVED

52 RESERVED

53 RESERVED

54 RESERVED

55 RESERVED

56 VDD (IO_VDD)

57 VDD

58 GND

59 VDD

60 GND

61 RESERVED

62 GND

63 VDD

64 GND

65 GND

LED_CFG

DP83847

10 www.national.com

2.0 Configuration

This section in clude s inform atio n on the var ious con figura tion options available with the DP83847. The configuration

options described below include:

— Auto-Negotiation

— PHY Address and LEDs

— Half Duplex vs. Full Dup lex

— Isolate mode

— Loopback mode

—BIST

2.1 Auto-Negotiation

The Auto-Negotiation function provides a mechanism for

exchanging configuration information between two ends of

a link segment and automatically selecting the highest performance mode of operation supported by both devices.

Fast Link Pulse (FLP) Bursts provide the signalling used to

communicate Auto-Negotiation abilities between two

devices at each end of a link segment. For further detail

regarding Auto-Negotiation, refer to Clause 28 of the IEEE

802.3u specification. The DP83847 supports four different

Ethernet protocols (10 Mb/s Half Duplex, 10 Mb/s Full

Duplex, 100 Mb/s Half Duplex, and 100 Mb/s Full Duplex),

so the inclusion of Auto-Negotiation ensures that the highest performance protocol will be selected based on the

advertised ability of the Link Partner. The Auto-Negotiation

function within the DP83847 can be controlled either by

internal register access or by the use of the AN_EN, AN1

and AN0 pins.

2.1.1 Auto-Negotiation Pin Control

The state of AN_EN, AN0 an d AN1 det ermine s wheth er the

DP83847 is forced in to a specific mode or Aut o-Negoti ation

will advertise a s pe cif ic ab ili ty (o r s et of abi lities) as given i n

Table 1. These pins allow configuration options to be

selected without requiring internal register access.

The state of AN _EN, AN0 and A N1, upon po wer-up/ reset,

determines the state of bits [8:5] of the ANAR register.

The Auto-Negotiation function selected at power-up or

reset can be cha nged at any time by writin g to the Basic

Mode Contro l Register (B MCR) at address 00h.

DP83847

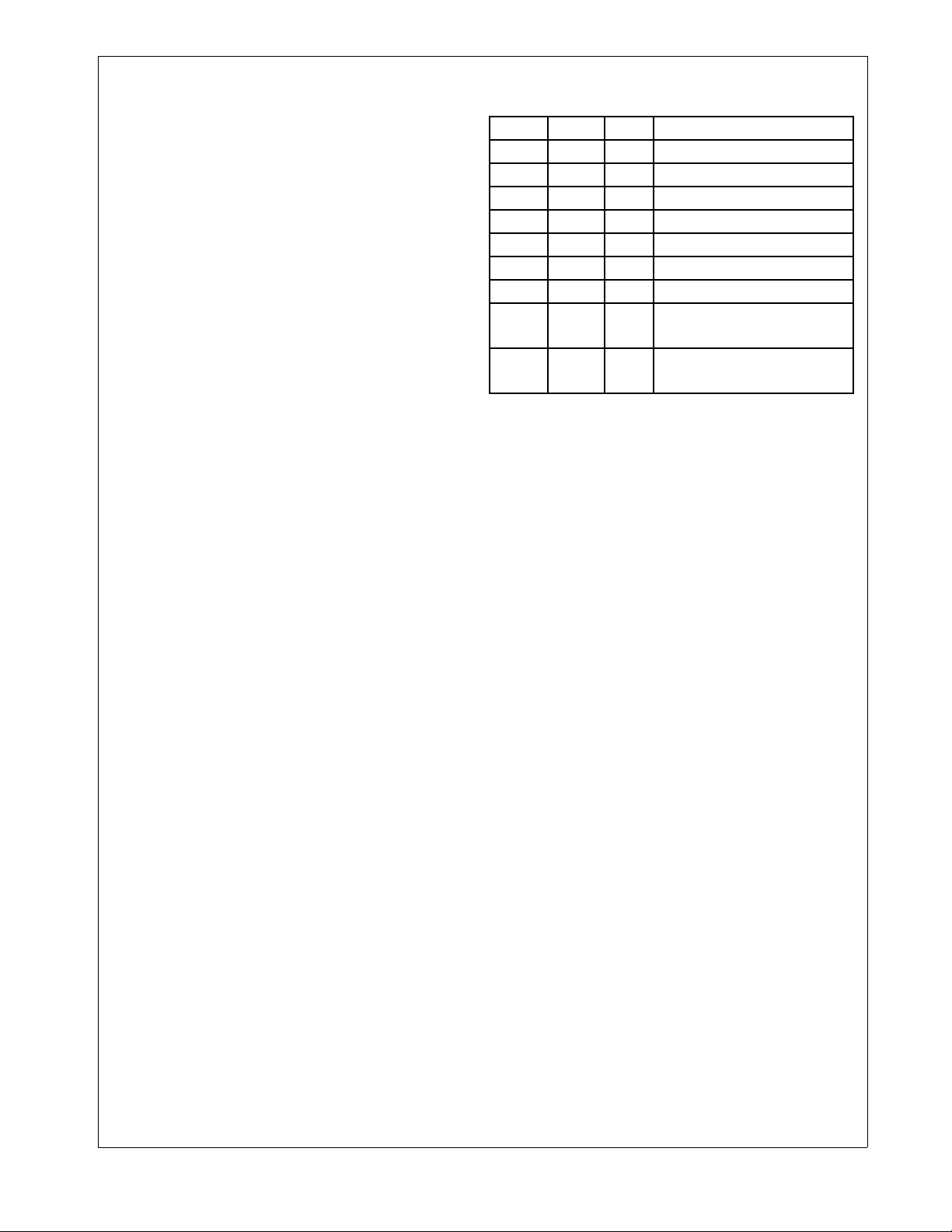

Table 1. Auto-Negotiation Modes

AN_EN AN1 AN0 Forced Mode

0 0 0 10BASE-T, Half-Duplex

0 0 1 10BASE-T, Full-Duplex

0 1 0 100 BASE-TX, Half-Du ple x

0 1 1 100 BASE-TX, Ful l-Dup lex

AN_EN AN1 AN0 Advertised Mode

1 0 0 10BASE-T, Half/Full-Duplex

1 0 1 100 BASE-TX, Half/ Ful l-Dup lex

1 1 0 10BASE-T Half-Duplex

100BASE-TX, Half-Duplex

1 1 1 10BASE-T, Half/Full-Duplex

100BASE-TX, Half/Full-Duplex

2.1.2 Auto-Negotiation Register Control

When Auto-Negotiation is enabled, the DP83847 transmits

the abilit ies program med into the Au to-Negotia tion Advertisement register (ANAR) at address 04h via FLP Bursts.

Any combination of 10 Mb/s, 100 Mb/s, Half-Duplex, and

Full Duplex modes may be selected.

The BMCR provides software with a mechanism to control

the operation of the DP83847. The AN0 and AN1 pins do

not affect the c ont ents of the BMCR a nd ca nno t be used by

software to obtain status of the mode selected. Bits 1 & 2 of

the PHYSTS register are only valid if Auto-Negotiation is

disabled or after Auto-Negotiation is complete. The AutoNegotiation protocol compares the contents of the

ANLPAR and ANAR registers and uses the results to automatically configure to the highest performance protocol

between the local and far-end port. The results of AutoNegotiation (Auto-Neg Complete, Duplex Status and

Speed) may be accessed in the PHYSTS register.

Auto-Negotiation Priority Resolution:

— (1) 100BASE-TX Full Duplex (Highest Priority)

— (2) 100BASE-TX Half Duplex

— (3) 10BASE-T Full Duplex

— (4) 10BASE-T Half Duplex (Lowest Priority)

The Basic Mode Control Register (BMCR) at address 00h

provides control for enabling, disabling, and restarting the

Auto-Negotiation process. When Auto-Negotiation is disabled the Speed Selectio n bi t in the BMCR controls switching between 10 Mb/s or 100 Mb/s operation, and the

Duplex Mode bit controls switching between full duplex

operation and half duplex operation. The Speed Selection

and Duplex Mode bits have no effect on the mode of operation when the Auto-Negotiation Enable bit is set.

The Basic Mode Status Register (BMSR) indicates the set

of available abilities for technology types, Auto-Negotiation

ability, and Extended Register Capability. These bits are

permanently set to indicate the full functionality of the

DP83847 (only the 100BASE-T4 bit is not set since the

DP83847 does not support that function).

11 www.national.com

The BMSR also provides status on:

— Whether Auto-Negotiation is complete

— Whether the Link Partner is advertising that a remote

fault has occurred

— Whether valid link has been established

— Support for Management Frame Preamble suppression

The Auto-Negotiation Advertisement Register (ANAR) indi-

cates the Auto-Negotiation abilities to be advertised by the

DP83847. All available abilities are transmitted by default,

but any ability can be suppressed by writing to the ANAR.

Updating the ANAR to suppress an ability is one way for a

management agent to ch ange (forc e) the tech nolog y that is

used.

The Auto-Negotiation Link Partner Ability Register

(ANLPAR) at address 05h is used to receive the base link

code word as wel l as all next page code word s during the

negotiati on. Furthermore, the ANLPAR will be updat ed to

either 0081h or 0021h for parallel detection to either 100

Mb/s or 10 Mb/s respectively.

The Auto-Negotiation Expansion Register (ANER) indicates additional Auto-Negotiation status. The ANER provides status on:

— Whether a Parallel Detect Fault has occurred

— Whether the Link Partner supports the Next Page func-

tion

— Whether the DP83847 supports the Next Page function

— Whether the current page being exchanged by Auto -Ne-

gotiation has been received

— Whether the Link Partner supports Auto-Negotiation

2.1.3 Auto-Negotiation Parallel Detection

The DP83847 supports the Parallel Detection function as

defined in the IEEE 802.3u specifi ca tio n. Para lle l De tect io n

requires both the 10 Mb/s and 100 Mb/s receivers to monitor the receive signal and report link status to the AutoNegotiation function. Auto-Negotiation uses this information to configure th e correct t echno logy i n the e vent th at the

Link Partner does not support Auto-Negotiation but is

transmitting link signals that the 100BASE-TX or 10BASET PMAs recognize as valid link signa ls .

If the DP83847 completes Auto-Negotiation as a result of

Parallel Detection, bits 5 and 7 within the ANLPAR register

will be set to reflect the mode of operation present in the

Link Partner. Note that bits 4:0 of the ANLPAR will also be

set to 00001 based on a successful parallel detection to

indicate a valid 802.3 selector field. Software may determine that negotiation completed via Parallel Detection by

reading a zero in the Link Partner Auto-Negotiation Able

bit, once the Auto-Negotiation Com ple te bit is set. If configured for parallel detect mode and any condition other than

a single good link occurs then the parallel detect fault bit

will set.

2.1.4 Auto-Negotia tion Rest art

Once Auto-Negotiation has completed, it may be restarted

at any time by setting bit 9 (Res tart Auto- Negotiat ion) of th e

BMCR to one. If the mode confi gured b y a su cces sful Au toNegotiation loses a valid link, then the Auto-Negotiation

process will resume and attempt to determine the configuration for the link. This function ensures that a valid configuration is maintained if the cable becomes disconnected.

DP83847

A renegotiation requ es t fro m a ny en tity, such as a management agent, will cause the DP83847 to halt any transmit

data and link pulse activity until the break_link_timer

expires (~1500 ms). Consequently, the Link Partner will go

into link fail and normal Auto-Negotiation resumes. The

DP83847 will resume Auto-Negotiation after the

break_link_timer has expired by issuing FLP (Fast Link

Pulse) bursts.

2.1.5 Enabling Auto-Negotiation via Software

It is important to note that if the DP83847 has been initialized upon power-up as a non-auto-negotiating device

(forced technology), and it is then requ ire d that Auto-Negotiation or re-Auto-Negotiation be initiated via software,

bit 12 (Auto-Negotiation Enable) of the Basic Mode Control

Register must first be cleared and then set for any AutoNegotiation function to take effect.

2.1.6 Auto-Negotiation Complete Time

Parallel detection and Auto-Negotiation take approximately

2-3 seconds to co mp let e. In addition, Auto-Neg otia tion with

next page should take approximately 2-3 seconds to complete, depending on the number of next pages sent.

Refer to Clause 28 of the IEEE 802.3u standard for a full

description of the individual timers related to Auto-Negotiation.

2.2 PHY Address and LEDs

The 5 PHY address inputs pins are shared with the LED

pins as shown below.

Table 2. PHY Address Mapping

Pin # PHYAD Function LED Function

23 PHYAD0 Duplex

22 PHYAD1 COL

21 PHYAD2 Good Link

20 PHYAD3 TX Activity

19 PHYAD4 RX Activity

18 n/a Speed

The DP83847 can be set to respond to any of 32 possible

PHY addresses. Each DP83847 or port sharing an MDIO

bus in a system must have a unique physical address.

Refer to Section 3.1.4, PHY Address Sensing section for

more details.

The state of each of the PHYAD inputs latched into the

PHYCTRL register bits [4:0]at system power-up/reset

depends on whether a pull-up or pull-down resistor has

been installed for each pin. For further detail relating to the

latch-in timing requirements of the PHY Address pins, as

well as the other hardware configuration pins, refer to the

Reset summary i n Section 4.0.

Since the PH YAD strap option s sh a re t he LED o utp ut pi n s,

the external components required for strapping and LED

usage must be considered in order to avoid contention.

Specifically, when the LED outputs are used to drive LEDs

directly, the active state of each output driver is dependent

on the logic level sampled by the corresponding PHYAD

input upon power-up/reset. For example, if a given PHYAD

input is resistively pu lle d lo w the n th e co rres pon di ng output

will be configured as an active high driver. Conversely, if a

12 www.national.com

given PHYAD input is resistively pulled high, then the corresponding output will be configured as an active low

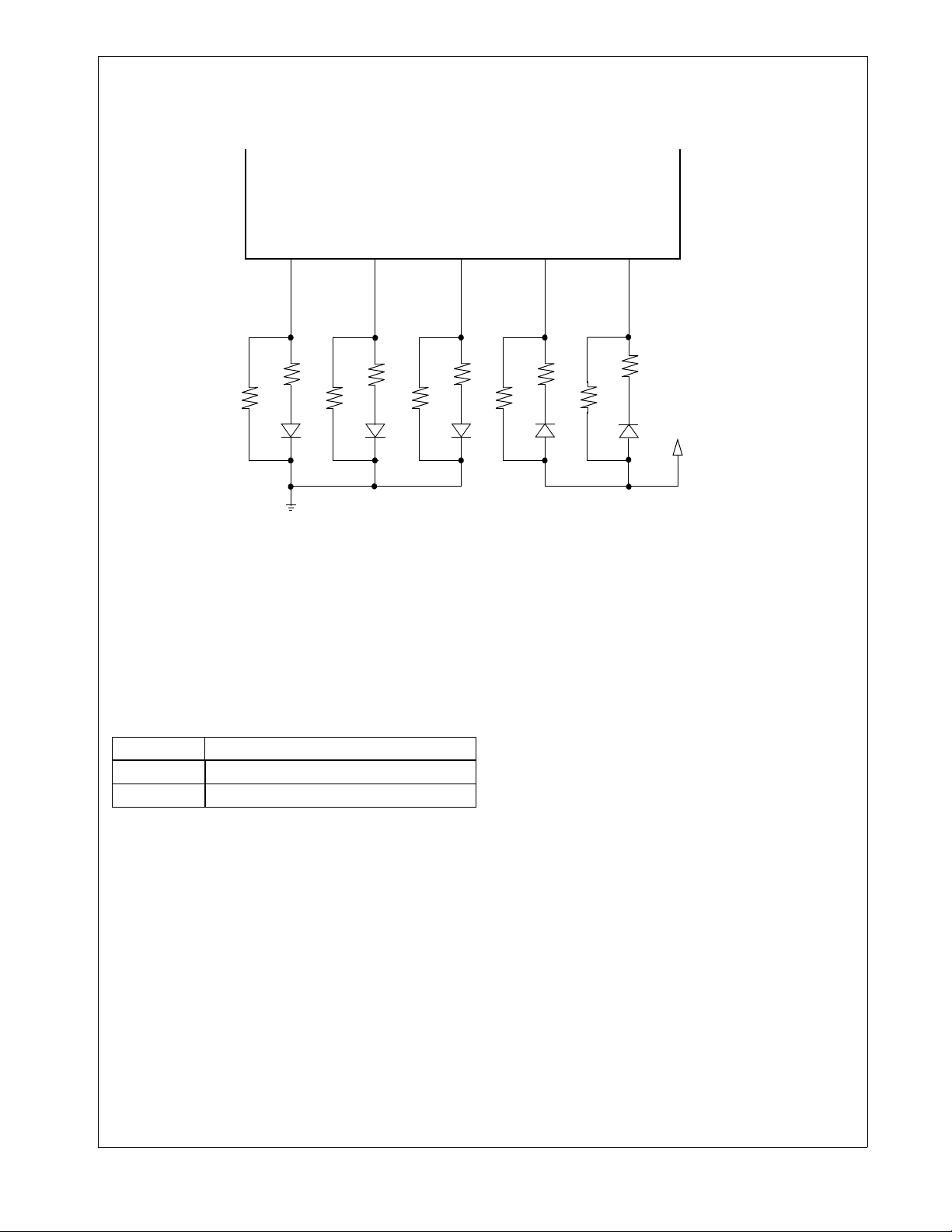

driver. Refer to Figure 1 for an example of a PHYAD con-

DP83847

nection to external components. In this example, the

PHYAD strapping results in address 00011 (03h).

The adaptive nature of the LED outputs helps to simplify

potential impleme ntation issues of thes e dual purpose pins.

LED_RX

PHYAD4= 0

1kΩ

10kΩ

Figure 1. PHYAD Strapping and LED Loading Example

LED_TX

1kΩ

10kΩ

LED_GDLNK

10kΩ

2.3 LED INTERFACES

The DP83847 has 6 Light Emitting Diode (LED) outputs,

each capable to drive a maximum of 10 mA, to indicate the

status of Link, Transmit, Receive, Collision, Speed, and

Full/Half Duplex operation. The LED_CFG strap option is

used to configure the LED_FDPLX output for use as an

LED driver or more general purpose control pin. See the

table below:

Table 3. LED Mode Select

LED_CFG Mode Description

1 LED polarity adjusted

0 Duplex active-high

The LED_FDPLX pin indicates the Half or Full Duplex configuration of the port in both 10 Mb/s and 100 Mb/s operation. Since t his pin is als o used as th e PHY address strap

option, the polarity of this indicator may be adjusted so that

in the “active” (FULL DUPLEX selected) state it drives

against the pullup/pulldown strap. In this configuration it is

suitable for use as an LED. When LED_CFG is high this

mode is selected and DsPHYTER automatically adjusts the

polarity of the output. If LED_CFG is low, the output drives

high to indicate the “active” state. In this configuration the

output is suitable for use as a control pin. The

LED_SPEED pin indicates 10 or 100 Mb/s data rate of the

port. The stan da rd C M OS dr i ve r go es hi g h wh en op e rat i ng

in 100 Mb/s operation. Since this pin is not utilized as a

strap option, it is not affected by polarity adjustment.

The LED_GDLNK pin indicates the link status of the port.

Since this pin is also used as the PHY address strap

option, the polarity of this indicator is adjusted to be the

inverse of the strap value.

LED_COL

PHYAD2 = 0PHY AD3 = 0

1kΩ

In 100BASE-T mode, link is established as a result of input

receive amplitude compliant with TP-PMD specifications

which will result in internal generation of signal detect.

10 Mb/s Link is estab lishe d as a resu lt of the rec eption of at

least seven consecutive normal Link Pulses or the reception of a valid 10BASE-T packet. This will cause the assertion of GD_LINK. GD_LINK will deassert in accordance

with the Link Loss Timer as specified in IEEE 802.3.

The Collision LED indicates the presence of collision activity for 10 Mb/s or 100 Mb/s Half Duplex operation. This bit

has no meaning in Full Duplex operation and will be deasserted when the port is operating in Full Duplex. Since this

pin is also used as the PHY address strap option, the

polarity of this indicator is adjusted to be the inverse of the

strap value. In 10 Mb/s half duplex mode, the collision LED

is based on the COL signal. When in this mode, the user

should disable the Heartbeat (SQE) to avoid asserting the

COL LED during transmission. See Section 3.4.2 for more

information about the Heartbeat signal.

The LED_RX and LED_TX pins indicate the presence of

transmit and/or receive activity. Since these pins are also

used in PHY address strap options, the polarity is adjusted

to be the inverse of the respective strap values.

PHYAD1 = 1

1kΩ

10kΩ

LED_FDPLX

PHYAD0 = 1

1kΩ

10kΩ

VCC

2.4 Half Duplex vs. Full Duplex

The DP83847 supports both half and full duplex operation

at both 10 Mb/s and 100 Mb/s speeds.

Half-duplex is the standard, traditional mode of operation

which relies on the CSMA/CD protocol to handle collisions

and network access. In Half-Dupl ex mode, CRS responds

to both transmit and receive activity in order to maintain

compliance with IEEE 802.3 specificat ion .

Since the DP83847 is designed to support simultaneous

transmit and receive activity it is capable of supporting full-

13 www.national.com

duplex switched ap pli ca tio ns with a throughput of up to 200

Mb/s per port when operating in 100BASE-TX mode.

Because the CSMA/CD protocol does not apply to fullduplex operation, the DP83847 disables its own internal

collision sensing and reporting functions and modifies the

behavior of Carrier Sense (CRS) such that it indicates only

receive act ivity. This allo ws a full-duplex c apable MAC to

operate properly.

All modes of operation (100BASE-TX and 10BASE-T) can

run either half-duplex or full-duplex. Additionally, other than

CRS and Collision reporting, all remaining MII signaling

remains the same regardless of the selected duplex mode.

It is important to understand that while Auto-Negotiation

with the use of Fast Link Pulse code words can interpret

and configure to full-duplex operation, parallel detection

can not recognize the difference between full and halfduplex from a fixed 10 Mb/s or 100 Mb/s link partner over

twisted pair. As specified in 802.3u, if a far-end link partner

is transmitting forced full duplex 100BASE-TX for example,

the parallel detection state machine in the receiving station

would be unable to detect the full duplex capability of the

far-end link partner and would negotiate to a half duplex

100BASE-TX configuration (same scenario for 10 Mb/s).

2.5 MII Isolate Mode

The DP83847 can be put into MII Isol ate mo de by wr iting to

bit 10 of the BMCR register. In addition, the MII isolate

mode can be selected by strapping in Physical Address 0.

It should be note d that selec ting P hysi cal Addre ss 0 via an

MDIO write to PHYCTRL will not put the device in the MII

isolate mode.

When in the MII isolate mode, the DP83847 does not

respond to packet data present at TXD[3:0], TX_EN, and

TX_ER inputs and presents a high impedance on the

TX_CLK, RX_CLK, RX_DV, RX_ER, RXD[3:0], COL, and

CRS outputs. The DP83847 will continue to respond to all

management transactions.

While in Isolate mode, the TD± outputs will not transmit

packet data but will continue to source 100BASE-TX

scrambled idles or 10BASE-T normal link pulses.

DP83847

2.6 Loopback

The DP83847 includes a Loopback Test mode for facilitating system diagnostics. The Loopback mode is selected

through bit 14 (Loopback) of the Basic Mode Control Register (BMCR). Writing 1 to this bit enables MII transmit data

to be routed to the MII receive outputs. Loopback status

may be checked in bit 3 of the PHY Status Register

(PHYSTS). While in Loopback mode the data will not be

transmitted onto the media in 100 Mb/s mode. To ensure

that the desired operating mode is maintained, Auto-Negotiation should be disabled before selecting the Loopback

mode.

During 10BASE-T operation, in order to be standard compliant, the loopback mo de loop s MII tran smit data to the MII

receive data, however, Link Pulses are not looped back. In

100BASE-TX Loopback mode the data is routed through

the PCS and PMA layers into the PMD sublayer before it is

looped back. In addition to serving as a board diagnostic,

this mode serves as a functional verification of the device.

2.7 BIST

The DsPHYTER incorporates an internal Built-in Self Test

(BIST) circuit to accommodate in-circuit testing or diagnostics. The BIST circuit can be utilized to test the integrity of

the transmit and receive data paths. BIST testing can be

performed with the part in the internal loopback mode or

externally looped back using a loopback cable fixture.

The BIST is implemented with independent transmit and

receive paths, with the tran sm it bl ock gene rati ng a con tin uous stream of a pseudo random sequence. The user can

select a 9 bit or 15 bit pseudo random sequence from the

PSR_15 bit in the PHY Control Register (PHYCTRL). The

looped back data is com p ared to the data generate d by the

BIST Linear Feedback Shift Register (LFSR, which generates a pseudo random sequence) to determine the BIST

pass/fail sta t us .

The pass/fail status of the BIST is stored in the BIST status

bit in the PHYCTRL register. The status bit defaults to 0

(BIST fail) and will transiti on on a su cc es sfu l co mparison. If

an error (mis-compare) occurs, the status bit is latched and

is cleared upon a subsequent write to the Start/Stop bit.

14 www.national.com

3.0 Functional Description

DP83847

3.1 802.3u MII

The DP83847 incorporates the Media Independent Interface (MII) as specified in Clause 22 of the IEEE 802.3u

standard. This interface may be used to connect PHY

devices to a MAC in 10/100 Mb/s systems. This section

describes both the serial MI I man age me nt inte rfac e as wel l

as the nibble wide MII data interface.

The serial management interface of the MII allows for the

configuration and control of multiple PHY devices, gathering of status, error in formation, and the de terminati on of th e

type and capabilities of the attached PHY(s).

The nibble wide MII data interfa ce c ons is t s of a rec ei ve bu s

and a transmit bus each with control signals to facilitate

data transfer between the PHY and the upper layer (MAC).

3.1.1 Seri al Managemen t Register Access

The serial management MII specification defines a set of

thirty-two 16-bit status and control registers that are accessible through the management interface pins MDC and

MDIO. The DP83847 implements all the required MII registers as well as several optional registers. These registers

are fully described in Secti on4.0. A description of the serial

management access protocol follows.

3.1.2 Serial Management Access Protocol

The serial control interface consists of two pins, Management Data Clock (MDC) and Management Data Input/Output (MDIO). MDC has a maximum clock rate of 25 MHz

and no minimum rate. The MDIO line is bi-directional and

may be shared by up to 32 devices. The MDIO frame for-

mat is shown below in Table 4: Typical MDIO Frame Format.

The MDIO pin requires a pull-up resistor (1.5 kΩ) which,

during IDLE and turnaro und, w ill pu ll MDIO hi gh. In order to

initialize the MDIO int erface , the st atio n manag ement entit y

sends a sequence of 32 contiguous logic ones on MDIO to

provide the DP83847 with a sequence that can be used to

establish synchronization. This preamble may be generated either by driving MDIO high for 32 consecutive MDC

clock cycles, or by simply allowing the MDIO pull-up resistor to pull the MDIO pin high during which time 32 MDC

clock cycles are provided. In addition 32 MDC clock cycles

should be used to re-sync the device if an invalid start,

opcode, or turnaround bit is detected.

The DP83847 waits until it has received this preamble

sequence before responding to any other transaction.

Once the DP83847 serial management port has been initialized no further preamble sequencing is required until

after a power-on/reset, invalid Start, invalid Opcode, or

invalid turnaround bit has occurred.

The St art co de is indicated by a <01> patte rn. Th is ass ure s

the MDIO line transitions from the default idle line state.

Turnaround is defined as an idle bit time inserted between

the Register Address field and the Data field. To avoid contention during a read transaction, no device shall actively

drive the MDIO signal during the first bit of Turnaround.

The addressed DP83847 drives the MDIO with a zero for

the second bit of turnaround and follows this with the

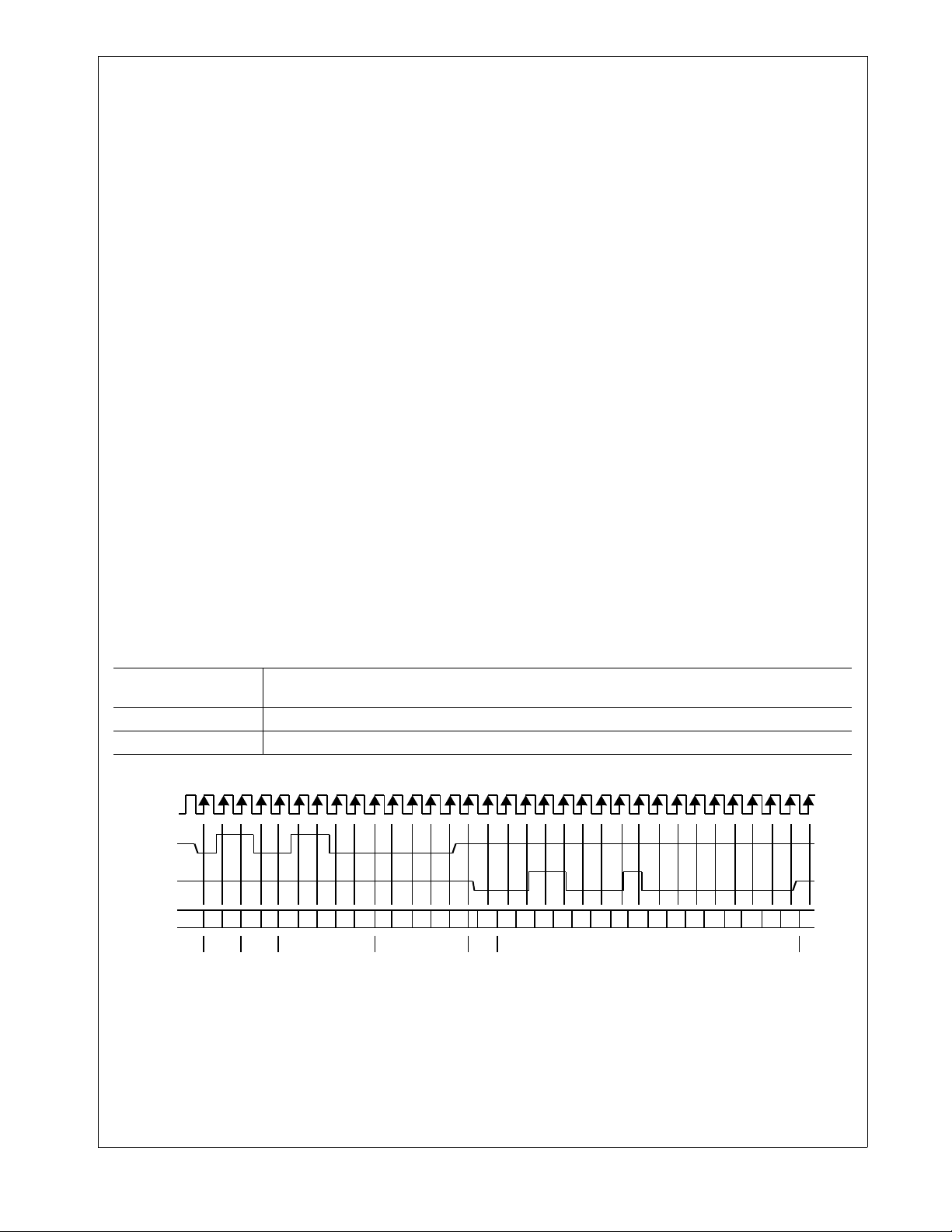

required data. Figure 2 shows the timing relationship

between MDC and th e MDIO as dr iven/re ceiv ed by the Station (STA) and the DP83847 (PHY) for a typical register

read access .

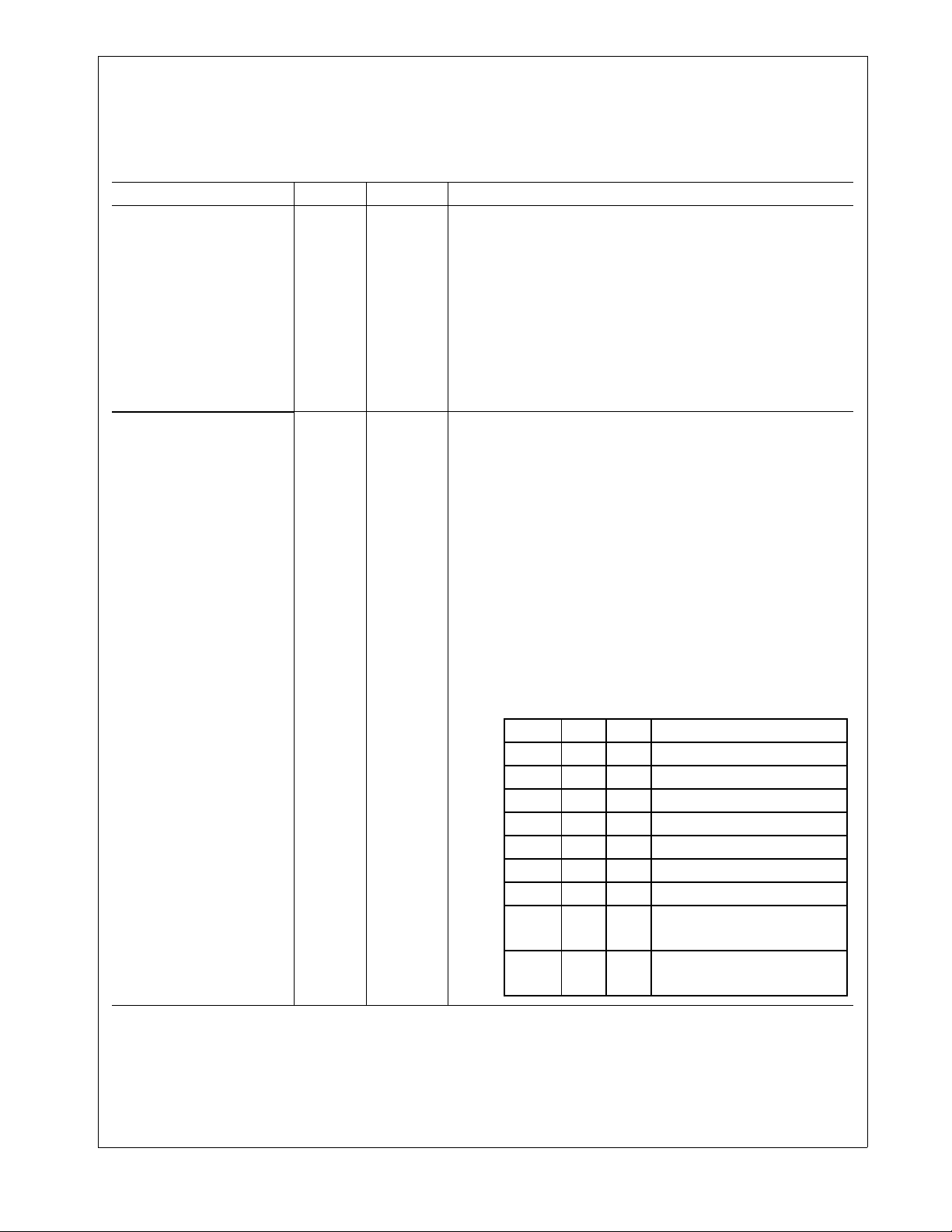

Table 4. Typical MDIO Frame Format

MII Management

<idle><start><op code><device addr><reg addr><turnaround><data><idle>

Serial Protocol

Read Operation <idle><01><10><AAAAA><RRRRR><Z0><xxxx xxxx xxxx xxxx><idle>

Write Operation <idle><01><01><AAAAA><RRRRR><10><xxxx xxxx xxxx xxxx><idle>

MDC

MDIO

(STA)

MDIO

(PHY)

Z

Z

00011 110000000

Idle Start

Opcode

(Read)

PHY Address

(PHYAD = 0Ch)

Register Address

(00h = BMCR)

Z

Z

Z

0 0 011000100000000

TA

Register Data

Figure 2. Typical MDC/MDIO Read Operation

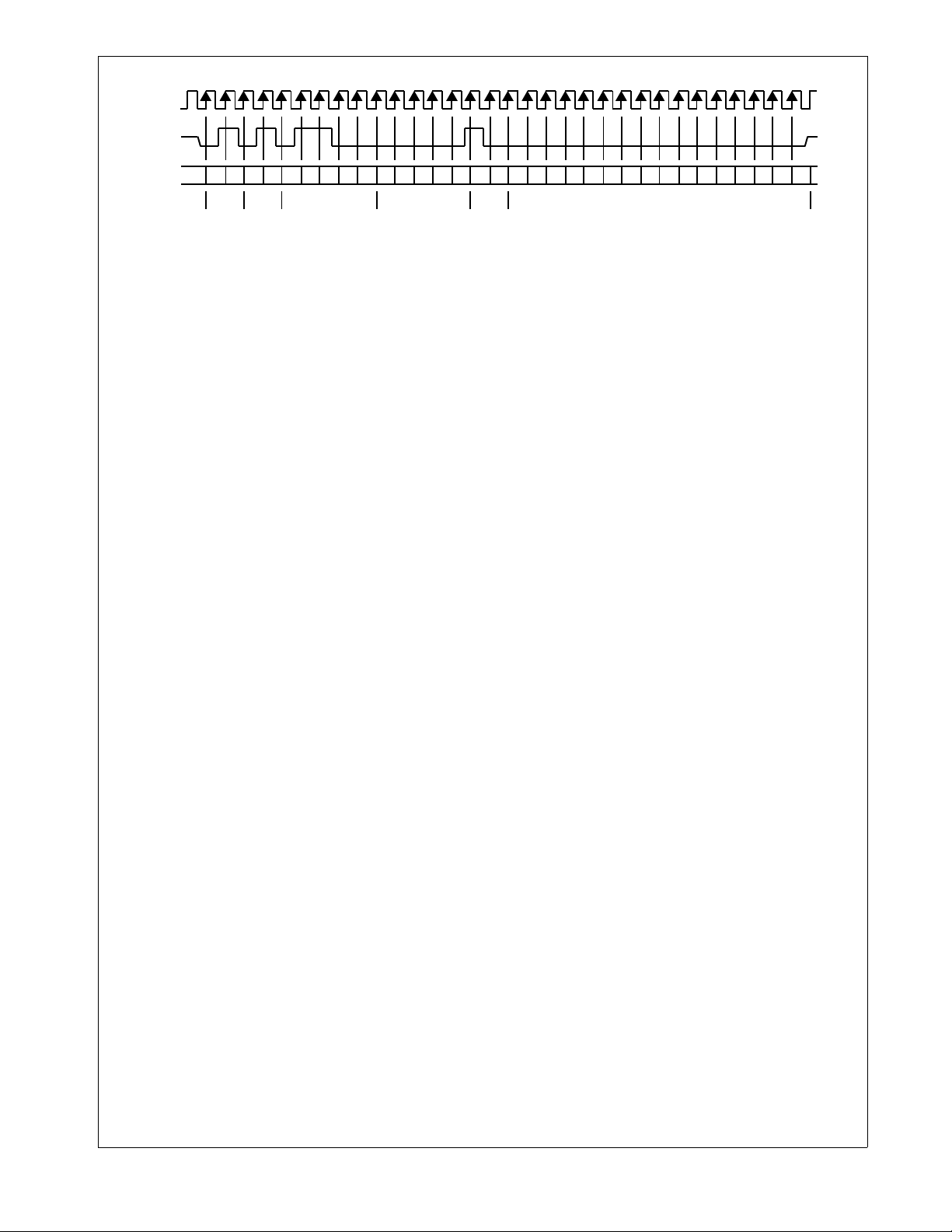

For write transactions, the station management entity

writes data to the addressed DP83847 thus eliminating the

requirement for MDIO Turnaround. The Turnaround time is

filled by the management entity by inserting <10>. Figure 3

shows the timing relationship for a typical MII register write

access.

3.1.3 Serial Management Preamble Suppression

The DP83847 supports a Preamble Suppression mode as

indicated by a one in bit 6 of the Basic Mode Status Register (BMSR, address 01h.) If the station management entity

(i.e. MAC or other management controller) determines that

all PHYs in the system support Preamble Suppression by

Z

Z

Idle

15 www.national.com

MDC

DP83847

MDIO

(STA)

Z

00011110000000

Idle Start

Opcode

(Write)

PHY Address

(PHYAD = 0Ch)

Register Address

(00h = BMCR)

Figure 3. Typical MDC/MDIO Write Operation

returning a one in this bit, then the station management

entity need not generate preamble for each management

transaction.

The DP83847 requires a single initialization sequence of

32 bits of preamble foll ow in g ha rdware/software reset. Thi s

requirement is generally met by the mandatory pull-up

resistor on MD I O in co nj unc ti o n wi th a co nt i nuo us MD C, or

the management access made to determine whether Preamble Suppression is supported.

While the DP83847 requires an initial preamble sequence

of 32 bits for management initialization, it does not require

a full 32-bit sequence between each subsequent transaction. A minimum of one idle bit between management

transactions is required as specified in IEEE 802.3u.

3.1.4 PHY Address Sensing

The DP83847 provides five PHY a ddress pins, the inform ation is latched into the PHYCTRL register (address 19h,

bits [4:0]) at device power-up/Hardware reset.

The DP83847 supports PHY Address strapping values 0

( <000 00> ) th rou gh 3 1 ( < 1 1111 > ) . St r a pp ing PHY Address

0 puts the part into Is ola t e Mod e . It should also be noted

that selecting PHY Address 0 via an MDIO write to PHYCTRL will not put the de vice i n Isolat e Mode; Add res s 0 must

be strapped in.

3.1.5 Nibble-wide MII Data Interface

Clause 22 of the IEEE 802.3u specification defines the

Media Independent Interface. This interface includes a

dedicated recei ve bu s an d a dedicated transmi t bus. These

two data buses, alo ng w i th va rio us c ontrol and indicate si gnals, allow for the simultaneous exchange of data between

the DP83847 and the upper layer agent (MAC).

The receive interface consists of a nibble wide data bus

RXD[3:0], a receive error signal RX_ER, a receive data

valid flag RX_DV, and a receive clock RX_CLK for synchronous transfer of the data. The receive clock can operate at either 2.5 MHz to support 10 Mb/s operation modes

or at 25 MHz to support 100 Mb/s operational modes.

The transmit interface consists of a nibble wide data bus

TXD[3:0], a transmit enable control signal TX_EN, and a

transmit cloc k TX_CL K which runs at ei ther 2. 5 MHz or 25

MHz.

Additionally, the MII includes the carrier sense signal CRS,

as well as a collision detect signal COL. The CRS signal

asserts to i ndicate the re ception of d ata from the ne twork

or as a function of transmit data in Half Duplex mode. The

COL signal asse rt s as an ind ic ation of a collision w hi ch ca n

occur during half-duplex operation when both a transmit

and receive operation occur simultaneously.

ZZ

0 0 0 000 00000000

1000

TA

Register Data

3.1.6 Collision Detect

For Half Duplex, a 10BASE-T or 100BASE-TX collision is

detected when the receive and transmit channels are

active sim ultaneously. Collisions ar e reported by the CO L

signal on the MII.

If the DP83847 is tran sm itti ng in 10 M b/s mode when a collision is detected, the collision is not reported until seven

bits have been received while in the collision state. This

prevents a collision being reported incorrectly due to noise

on the network. The COL signal remains set for the duration of the collision.

If a collision occ urs du ring a receive operation, it is immediately reported by the COL signal.

When heartbeat is enabled (only applicable to 10 Mb/s

operation), approximately 1µs after the transmission of

each packet, a Si gn al Q u ali ty Error (SQE) signal o f ap prox imately 10 bit times is generated (internally) to indicate

successful transmiss io n. SQ E is repo rted as a pul se on th e

COL signal of the MII.

3.1.7 Carrier Sense

Carrier Sense (CRS) may be ass ert ed due to receive activity, once valid data is de tec ted v ia the squ elc h fun ct ion during 10 Mb/s operation. During 100 Mb/s operation CRS is

asserted when a valid link (SD) and two non-contiguous

zeros are detected on the line.

For 10 or 100 Mb/s Half Duple x op era tio n, C RS is a sserted

during either packet transmission or reception.

For 10 or 100 Mb/s Full Duplex operation, CRS is asserted

only due to receive activity.

CRS is deasserted following an end of packet.

3.2 100BASE-TX TRANSMITTER

The 100BASE-TX transmitter consists of several functional

blocks which convert sync hronous 4-bit ni bble da t a, as p rovided by the MII, to a scrambled MLT-3 125 Mb/s serial

data stream. Because the 100BASE-TX TP-PMD is integrated, the differential output pins, TD±, can be directly

routed to the magnetics.

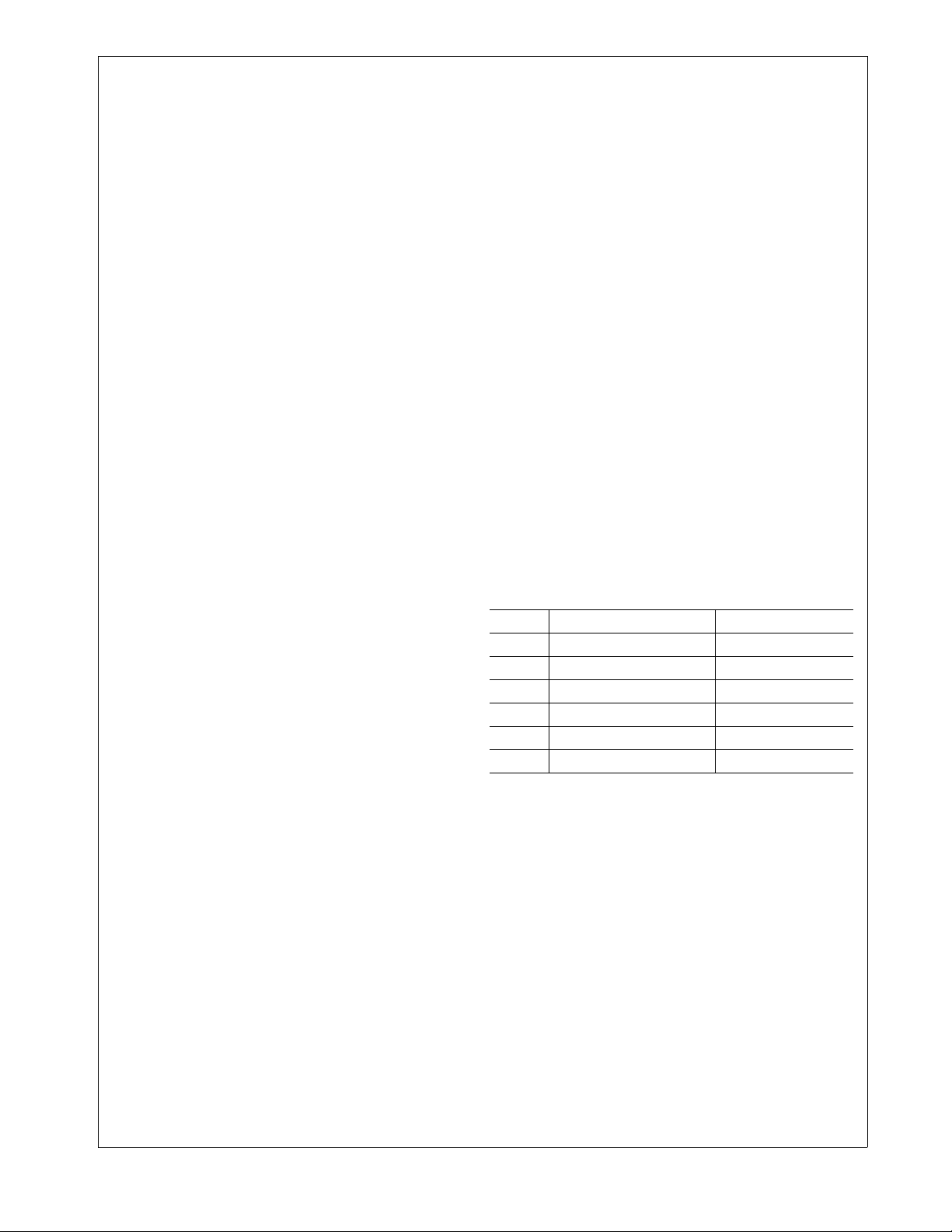

The block diagram in Figure 5 provides an overview of

each functional block within the 100BASE-TX transmit section.

The Transmitter section consists of the following functional

blocks:

— Code-group Encoder and Injecti on block ( bypass optio n)

— Scrambler block (bypass option)

— NRZ to NRZI encoder block

— Binary to MLT-3 converter / Common Driver

Z

Idle

16 www.national.com

The bypass option for the functional blocks within the

100BASE-TX transmitter provides flexibility for applications

where data conversion is not always required. The

TX_CLK

TXD[3:0] /

DIV BY 5

DP83847

DP83847 implements the 100BASE-TX transmit state

machine diagram as specified in the IEEE 802.3u Standard, Clause 24.

TX_ER

FROM PGM

BP_4B5B

BP_SCR

100BASE-TX

LOOPBACK

4B5B CODE-

GROUP ENCODER

& INJECTOR

MUX

5B PARALLEL

TO SERIAL

SCRAMBLER

MUX

NRZ TO NRZI

ENCODER

BINARY TO

MLT-3 /

COMMON

DRIVER

Figure 4. 100BASE-TX Transmit Block Diagram

3.2.1 Code-group Encoding and Injection

The code-group encoder converts 4-bit (4B) nibble data

generated by the MAC into 5-bit (5B) code-groups for

transmission. This conversion is required to allow control

data to be combined with packet data code-groups. Refer

to T able 5: 4B5B Code-Group Encoding/Decoding for 4B to

5B code-group mapping details.

The code-group encoder substitutes the first 8-bits of the

MAC preamble with a J/K code-group pair (11000 10001)

upon transmission. The code-group encoder continues to

replace subsequent 4B preamble and data nibbles with

corresponding 5B code-groups. At the end of the transmit

packet, upon the deassertion of Transmit Enable signal

from the MAC, the code-group encoder injects the T/R

code-group pair (01101 00111) indicating the en d o f fra me.

TD±

After the T/R code-group pair, the code-group encoder

continuously injects IDLEs into the transmit data stream

until the next transmit packet is detected (reassertion of

Transmit Enabl e).

3.2.2 Scrambler

The scrambler is required to control the radiated emissions

at the media connector and on the twisted pair cable (for

100BASE-TX applications). By scrambling the data, the

total energy launched onto the cable is randomly distributed over a wide frequency range. Without the scrambler,

energy levels at the PMD and on the cable could peak

beyond FCC limitations at frequencies related to repeating

5B sequences (i.e., continuous transmission of IDLEs).

The scrambler is configured as a closed loop linear feedback shift register (LFSR) with an 11-bit polynomial. The

output of the closed loop LFSR is X-ORd with the serial

17 www.national.com

NRZ data from the code-group encoder. The result is a

scrambled data stream with sufficient randomization to

decrease radiated emissions at certain frequencies by as

much as 20 dB. The DP83847 uses the PHY_ID (pins

PHYAD [4:0]) to set a unique seed value.

3.2.3 NRZ to NRZI Encoder

After the transmit data stream has been serialized and

scrambled, the data must be NRZI encoded in order to

comply with the TP-PMD standard for 100BASE-TX transmission over Category-5 Unsheilded twisted pair cable.

binary_plus

D

binary_in

Q

Q

binary_minus

differential MLT-3

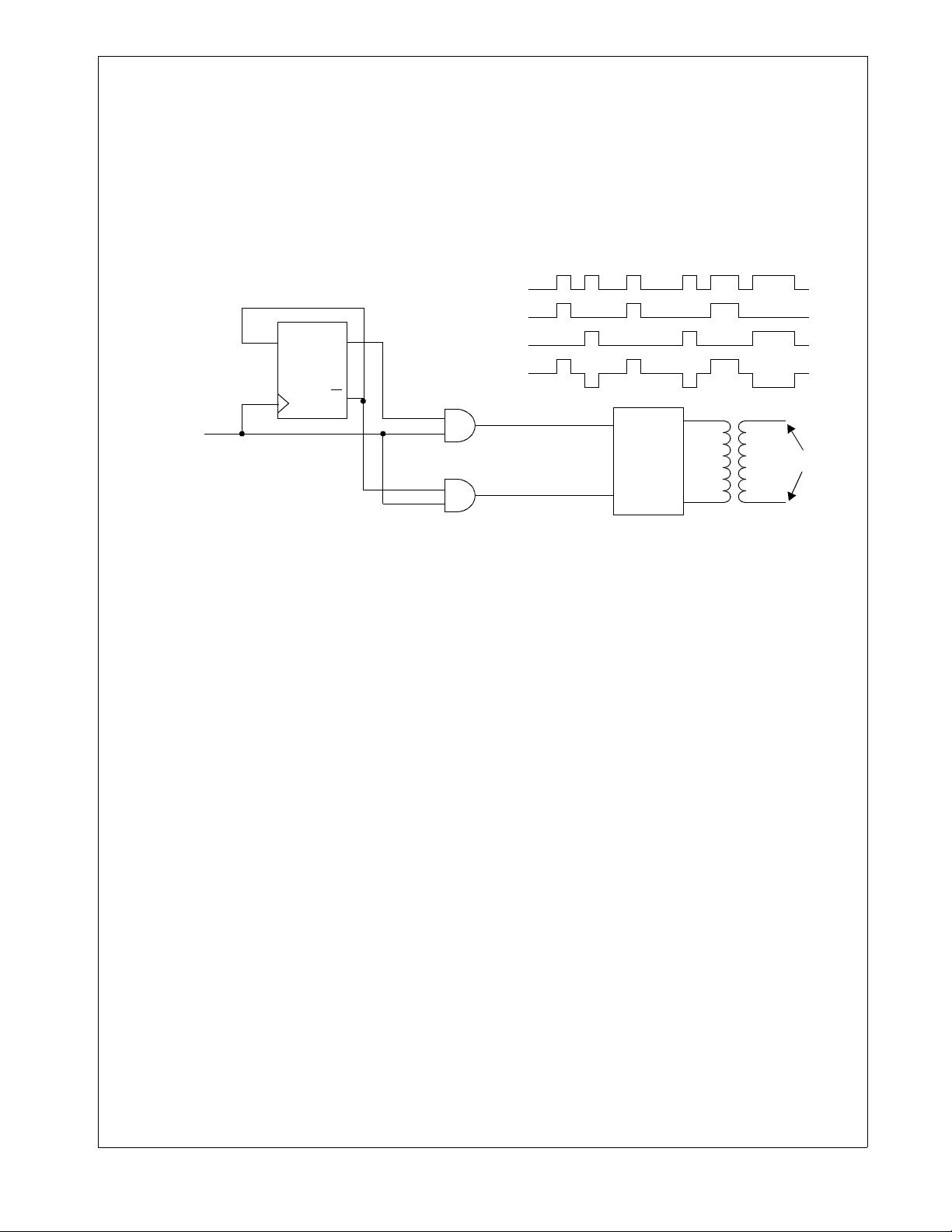

3.2.4 Binary to MLT-3 Convertor / Common Driver

The Binary to MLT-3 conversion is accomplished by converting the serial binary data stream output from the NRZI

encoder into two binary data streams with alternately

phased logic one events. These two binary streams are

then fed to the twisted pair outp ut drive r whic h con ve rt s the

voltage to current and alternately drives either side of the

transmit transformer primary winding, res ultin g in a mini mal

current (20 mA max) MLT-3 signal. Refer to Figure 5 .

binary_in

binary_plus

COMMON

DRIVER

binary_minus

MLT-3

DP83847

Figure 5. Binary to MLT-3 conversion

18 www.national.com

Loading...

Loading...