DP83815 10/100 Mb/s I ntegrated PCI Ethern et Media Access Control ler and Physical Layer (MacPhyter)

© 1999 National Semiconductor Corporation

www.national.com

PRELIMINARY

November 1999

DP83815 10/100 Mb/s Integrated PCI Ethernet Media Access

Controller and Physical Layer (MacPhyter)

General Description

DP83815 is a single-chip 10/100Mb/s Ethernet Controller

for the PCI bus. It is targeted at low-cost, high volume PC

mother boards, adapter cards, and embedded systems.

The DP83815 fully implements the V2.2 33MHz PCI bus

interface for host communications with power management

support. Packet descriptors and data are transferred via

bus-mastering, reducing the burden on the host CPU. The

DP83815 can support full duplex 10/100Mb/s transmission

and reception, with minimum interframe gap.

The DP83815 device is an integration of an enhanced

version of the NSC PCI MAC/BIU (Media Access

Controller/Bus Interface Unit) and a 3.3V CMOS physical

layer interface.

Features

—IEEE 802.3 Compliant, PCI V2.2 MAC/BIU supports

traditional data rates of 10Mb/s Ethernet and 100Mb/s

Fast Ethernet (via internal phy).

—Bus master - burst sizes of up to 128 dwords (512 bytes)

—BIU compliant with PC 97 and PC 98 Hardware Design

Guides, PC 99 Hardware Design Guide draft, ACPI v1.0,

PCI Power Management Specification v1.1, OnNow

Device Class Power Management Reference

Specification - Network Device Class v1.0a

—Wake on LAN (WOL) support compliant with PC98,

PC99, and OnNow, including directed packets, Magic

Packet, VLAN packets, ARP packets, pattern match

packets, and Phy status change

—Clkrun function for PCI Mobile Design Guide

—Virtual LAN (VLAN) and long frame support

—Support for 802.3x Full duplex flow control

—Extremely flexible Rx packet filtration including: single

address perfect filter with MSb masking, broadcast, 512

entry multicast/unicast hash table, deep packet pattern

matching for up to 4 unique patterns

—Statistics gathered for support of RFC 1213 (MIB II),

RFC 1398 (Ether-like MIB), IEEE 802.3 LME, reducing

CPU overhead for management

—Internal 2KB Transmit and 2KB Receive data FIFOs

—Serial EEPROM port with auto-load of configuration data

from EEPROM at power-on

—Flash/PROM interface for remote boot support

—Fully integrated IEEE 802.3/802.3u 3.3v CMOS physical

layer

—802.3 10BASE-T transceiver with integrated filters

—802.3u 100BASE-TX transceiver

—Fully integrated ANSI X3.263 compliant TP-PMD

physical sublayer with adaptive equalization and

Baseline Wander compensation

—802.3u Auto-Negotiation - advertised features

configurable via EEPROM

—Full Duplex support for 10 and 100 Mb/s data rates

—Single 25MHz reference clock

—144-pin TQFP package

—Low power 3.3V CMOS design with typical consumption

of 561mW operating, 380mW during WOL mode, 33mW

sleep mode

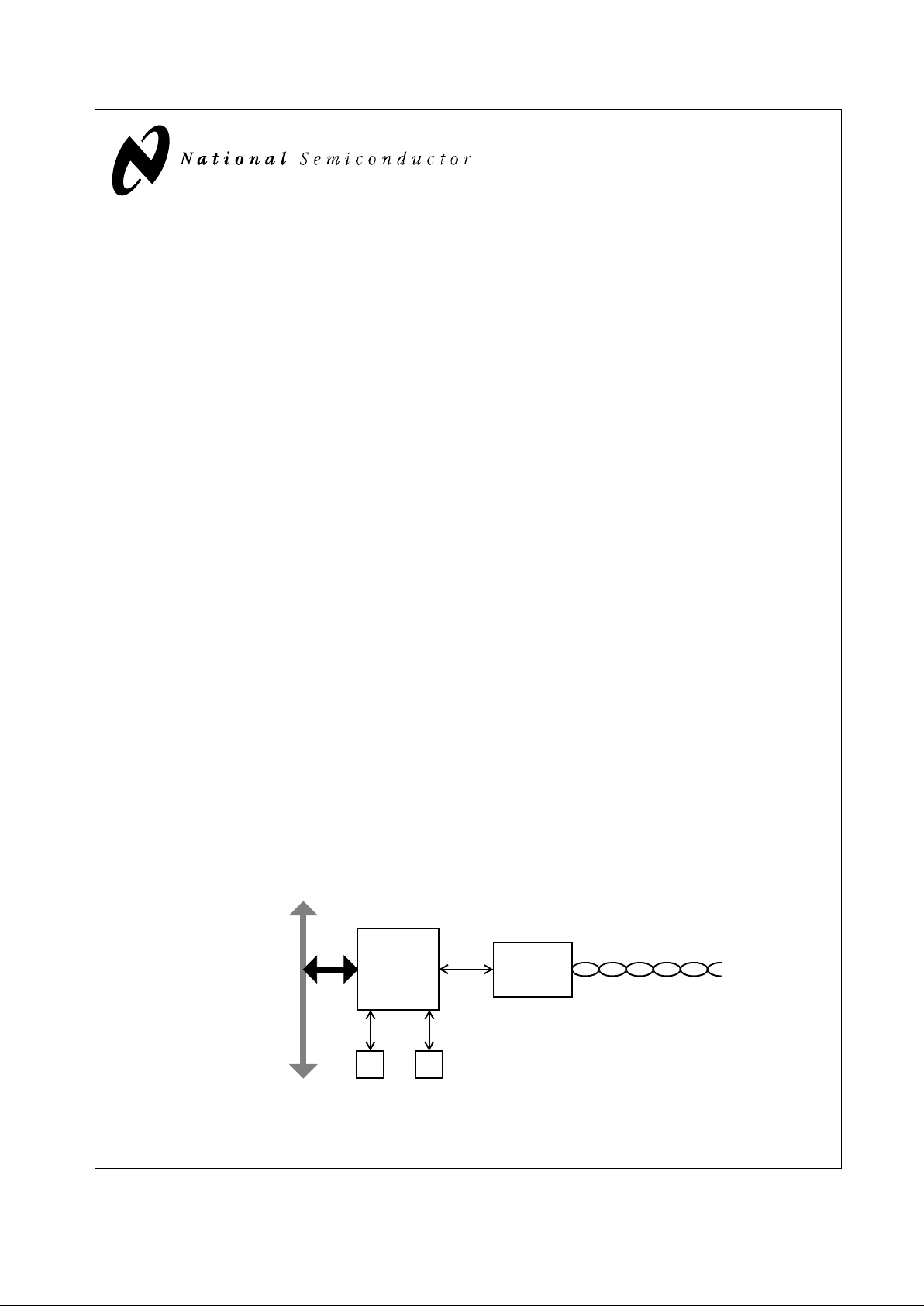

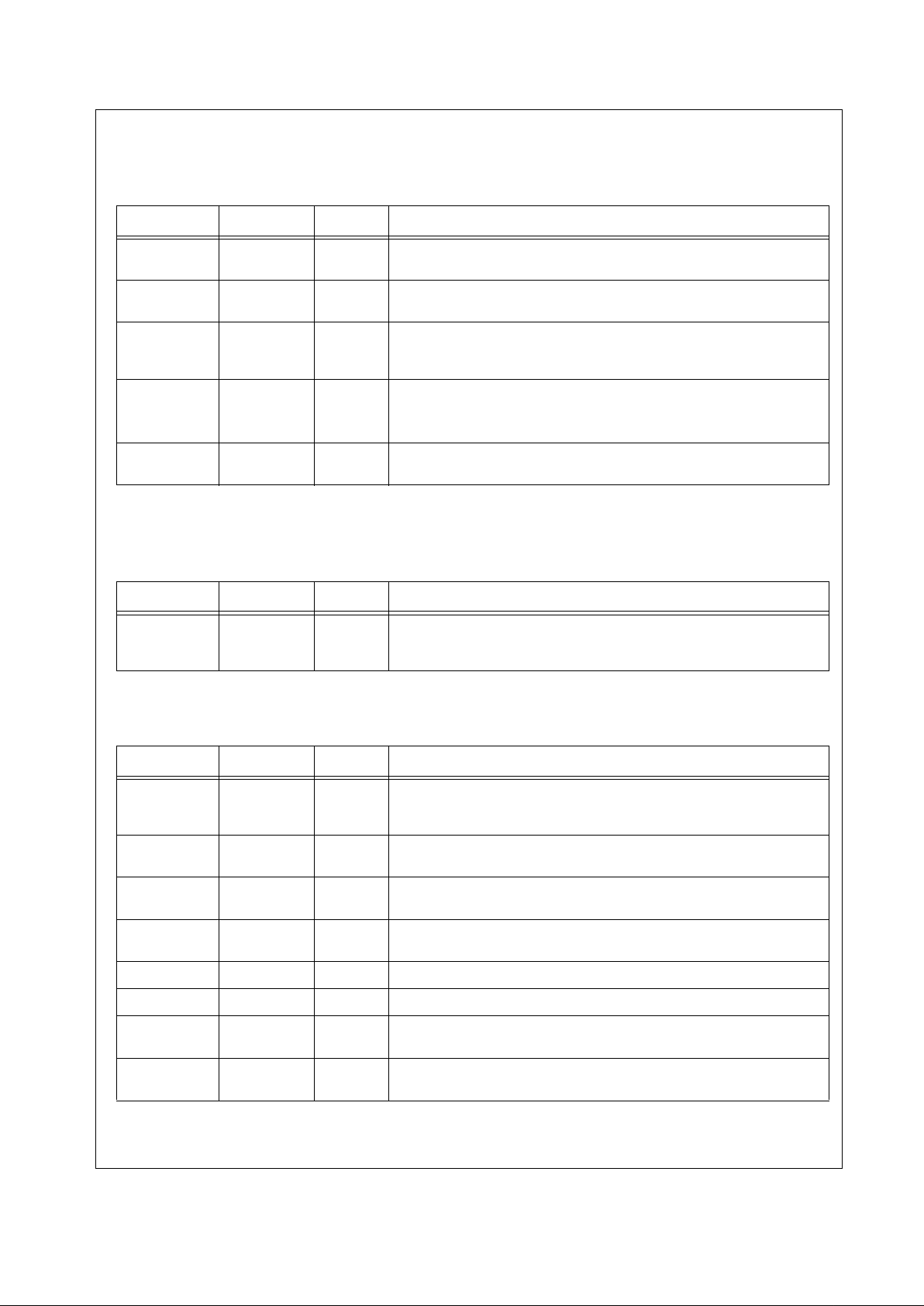

System Diagram

PCI Bus

DP83815

EEPROM

Isolation

10/100 Twisted Pair

BIOS ROM

(optional)

(optional)

2 www.national.com

Table of Contents

1.0 Connection Diagram . . . . . . . . . . . . . . . . . . 4

2.0 Pin Description . . . . . . . . . . . . . . . . . . . . . . 5

3.0 Functional Description . . . . . . . . . . . . . . . 11

3.1 MAC/BIU . . . . . . . . . . . . . . . . . . . . . . . . . 12

3.1.1 PCI Bus Interface . . . . . . . . . . . . . . . . . . . . . . . . . . 12

3.1.2 Tx MAC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

3.1.3 Rx MAC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

3.2 Buffer Management . . . . . . . . . . . . . . . . . 13

3.2.1 Tx Buffer Manager . . . . . . . . . . . . . . . . . . . . . . . . . 13

3.2.2 Rx Buffer Manager . . . . . . . . . . . . . . . . . . . . . . . . . 13

3.2.3 Packet Recognition . . . . . . . . . . . . . . . . . . . . . . . . 13

3.2.4 MIB . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

3.3 Interface Definitions . . . . . . . . . . . . . . . . . 14

3.3.1 PCI System Bus . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

3.3.2 Boot PROM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

3.3.3 EEPROM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

3.3.4 Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

3.4 Physical Layer . . . . . . . . . . . . . . . . . . . . . 16

3.4.1 Auto-Negotiation . . . . . . . . . . . . . . . . . . . . . . . . . . 16

3.4.2 Auto-Negotiation Register Control . . . . . . . . . . . . . 16

3.4.3 Auto-Negotiation Parallel Detection . . . . . . . . . . . . 16

3.4.4 Auto-Negotiation Restart . . . . . . . . . . . . . . . . . . . . 17

3.4.5 Enabling Auto-Negotiation via Software . . . . . . . . 17

3.4.6 Auto-Negotiation Complete Time . . . . . . . . . . . . . . 17

3.5 LED Interfaces . . . . . . . . . . . . . . . . . . . . . 17

3.6 Half Duplex vs. Full Duplex . . . . . . . . . . . 18

3.7 Phy Loopback . . . . . . . . . . . . . . . . . . . . . 18

3.8 Status Information . . . . . . . . . . . . . . . . . . 18

3.9 100BASE-TX TRANSMITTER . . . . . . . . . 18

3.9.1 Code-group Encoding and Injection . . . . . . . . . . . 19

3.9.2 Scrambler . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

3.9.3 NRZ to NRZI Encoder . . . . . . . . . . . . . . . . . . . . . . 20

3.9.4 Binary to MLT-3 Convertor / Common Driver . . . . 20

3.10 100BASE-TX Receiver . . . . . . . . . . . . . . 21

3.10. 1 Input and Base Line Wander Compensation . . . .21

3.10.2 Signal Detect . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

3.10.3 Digital Adaptive Equalization . . . . . . . . . . . . . . . . 21

3.10.4 Line Quality Monitor . . . . . . . . . . . . . . . . . . . . . . . 24

3.10.5 MLT-3 to NRZI Decoder . . . . . . . . . . . . . . . . . . . .24

3.10.6 Clock Recovery Module . . . . . . . . . . . . . . . . . . . . 25

3.10.7 NRZI to NRZ . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

3.10.8 Serial to Parallel . . . . . . . . . . . . . . . . . . . . . . . . . . 25

3.10.9 De-scrambler . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

3.10.10 Code-group Alignment . . . . . . . . . . . . . . . . . . . . 25

3.10.11 4B/5B Decoder . . . . . . . . . . . . . . . . . . . . . . . . . . 25

3.10.12 100BASE-TX Link Integrity Monitor . . . . . . . . . . 25

3.10.13 Bad SSD Detection . . . . . . . . . . . . . . . . . . . . . . 25

3.11 10BASE-T Transceiver Module . . . . . . . . 25

3.11.1 Operational Modes . . . . . . . . . . . . . . . . . . . . . . . . 25

3.11.2 Smart Squelch . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

3.11.3 Collision Detection . . . . . . . . . . . . . . . . . . . . . . . . 26

3.11.4 Normal Link Pulse Detection/Generation . . . . . . . 26

3.11.5 Jabber Function . . . . . . . . . . . . . . . . . . . . . . . . . . 26

3.11.6 Automatic Link Polarity Detection . . . . . . . . . . . . . 26

3.11.7 10BASE-T Internal Loopback . . . . . . . . . . . . . . . . 27

3.11.8 Transmit and Receive Filtering . . . . . . . . . . . . . . . 27

3.11.9 Transmitter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

3.11.10 Receiver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

3.11.11 Far End Fault Indication . . . . . . . . . . . . . . . . . . . 27

4.0 Register Set . . . . . . . . . . . . . . . . . . . . . . . . 28

4.1 Configuration Registers . . . . . . . . . . . . . . 28

4.1.1 Configuration Identification Register . . . . . . . . . . . 28

4.1.2 Configuration Command and Status Register . . . . 29

4.1.3 Configuration Revision ID Register . . . . . . . . . . . 30

4.1.4 Configuration Latency Timer Register . . . . . . . . . 31

4.1.5 Configuration I/O Base Address Register . . . . . . . 31

4.1.6 Configuration Memory Addr ess Register . . . . . . . 32

4.1.7 Configuration Subsystem Ident ification Register . 32

4.1.8 Boot ROM Configuration Register . . . . . . . . . . . . 33

4.1.9 Capabilities Pointer Register . . . . . . . . . . . . . . . . 33

4.1.10 Configuration Interrupt Select Register . . . . . . . . 34

4.1.11 Power Management Capabilities Register . . . . . 34

4.1.12 Power Management Control and Status Register 35

4.2 O perat ional Registers . . . . . . . . . . . . . . .36

4.2.1 Command Register . . . . . . . . . . . . . . . . . . . . . . . . 37

4.2.2 Configuration and Media Status Register . . . . . . . 38

4.2.3 EEPROM Access Register . . . . . . . . . . . . . . . . . . 40

4.2.4 EEPROM Map . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

4.2.5 PCI Test Control Register . . . . . . . . . . . . . . . . . . . 41

4.2.6 Interrupt Status Register . . . . . . . . . . . . . . . . . . . . 42

4.2.7 Interrupt Mask Register . . . . . . . . . . . . . . . . . . . . 43

4.2.8 Interrupt Enable Register . . . . . . . . . . . . . . . . . . . 45

4.2.9 Transmit Descriptor Pointer Register . . . . . . . . . . 45

4.2.10 Transmit Configuration Register . . . . . . . . . . . . . 46

4.2.11 Receive Descriptor Pointer Register . . . . . . . . . . 47

4.2.12 Receive Configuration Register . . . . . . . . . . . . . 48

4.2.13 CLKRUN Control/Status Register . . . . . . . . . . . . 49

4.2.14 Wake Command/Status Register . . . . . . . . . . . . 51

4.2.15 Pause Control/Status Register . . . . . . . . . . . . . . 53

4.2.16 Receive Filter/Match Control Register . . . . . . . . 54

4.2.17 Receive Filter/Match Data Register . . . . . . . . . . 55

4.2.18 Receive Filter Logic . . . . . . . . . . . . . . . . . . . . . . 56

4.2.19 Boot ROM Address Register . . . . . . . . . . . . . . . . 60

4.2.20 Boot ROM Data Register . . . . . . . . . . . . . . . . . . 60

4.2.21 Silicon Revision Register . . . . . . . . . . . . . . . . . . 60

4.2.22 Management Information Base Control Register 61

4.2.23 Management Inf ormation Base Registers . . . . . . 62

4.3 Internal PHY Registers . . . . . . . . . . . . . . .63

4.3.1 Basic Mode Control Register (BMCR) . . . . . . . . . 63

4.3.2 Basic Mode Status Register (BMSR) . . . . . . . . . . 64

4.3.3 PHY Identifier Register #1 (PHYIDR1) . . . . . . . . . 65

4.3.4 PHY Identifier Register #2 (PHYIDR2) . . . . . . . . . 66

4.3.5 Auto-Negotiation Advertisement Register (ANAR) 66

4.3.6 Auto-Neg Link Partner Ability Reg (ANLPAR) . . . 67

4.3.7 Auto-Negotiate Expansion Register (ANER) . . . . 68

4.3.8 Auto-Neg Next Page Transmit Reg (ANNPTR) . . 68

4.3.9 PHY Status Register (PHYSTS) . . . . . . . . . . . . . . 69

4.3.10 MII Interrupt Control Register (MICR) . . . . . . . . . 71

4.3.11 MII Interrupt Status and Misc. Cntrl Reg (MISR) 71

4.3.12 False Carrier Sense Counter Register (FCSCR) 72

4.3.13 Receiver Error Counter Register (RECR) . . . . . . 72

4.3.14 100 Mb/s PCS Config and Status Reg (PCSR) . 72

4.3.15 PHY Control Register (PHYCR) . . . . . . . . . . . . . 73

4.3.16 10BASE-T Status/Control Register (TBTSCR) . . 74

4.4 Re comm ende d Registers Configuration .75

5.0 Buffer Management . . . . . . . . . . . . . . . . . .76

5.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . .76

5.1.1 Descriptor Format . . . . . . . . . . . . . . . . . . . . . . . . . 76

5.1.2 Single Descriptor Packets . . . . . . . . . . . . . . . . . . 78

5.1.3 Multiple Descriptor Packets . . . . . . . . . . . . . . . . . 79

5.1.4 Descriptor Lists . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

5.2 Transmit Architecture . . . . . . . . . . . . . . . .80

5.2.1 Transmit State Machine . . . . . . . . . . . . . . . . . . . . 80

5.2.2 Transmit Data Flow . . . . . . . . . . . . . . . . . . . . . . . 82

5.3 Receive Architecture . . . . . . . . . . . . . . . .83

5.3.1 Receive State Machine . . . . . . . . . . . . . . . . . . . . . 83

5.3.2 Receive Data Flow . . . . . . . . . . . . . . . . . . . . . . . . 85

6.0 DC and AC Specifications. . . . . . . . . . . . .86

3 www.national.com

List of Figures

Figure 3-1 DP83815 Functional Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Figure 3-2 MAC/BIU Functional Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Figure 3-3 Ethernet Packet Format. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Figure 3-4 DSP Physical Layer Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Figure 3-5 LED Loading Example. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Figure 3-6 100BASE-TX Transmit Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Figure 3-7 Binary to MLT-3 conversion. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Figure 3-8 100 M/bs Receive Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Figure 3-9 100BASE-TX BLW Event Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Figure 3-10 EIA/TIA Attenuation vs. Frequency for 0, 50, 100, 130 & 150 meters of CAT V cable 24

Figure 3-11 MLT-3 Signal Measured at AII after 0 meters of CAT V cable. . . . . . . . . . . . . . . . . . . 24

Figure 3-12 MLT-3 Signal Measured at AII after 50 meters of CAT V cable. . . . . . . . . . . . . . . . . . 24

Figure 3-13 MLT-3 Signal Measured at AII after 100 meters of CAT V cable. . . . . . . . . . . . . . . . . 24

Figure 3-14 10BASE-T Twisted Pair Smart Squelch Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Figure 4-1 Pattern Buffer Memory -180h words (word=18bits). . . . . . . . . . . . . . . . . . . . . . . . . . . 57

Figure 4-2 Hash Table Memory - 40h bytes addressed on word boundaries. . . . . . . . . . . . . . . . 59

Figure 5-1 Single Descriptor Packets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

Figure 5-2 Multiple Descriptor Packets. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

Figure 5-3 List and Ring Descriptor Organization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

Figure 5-4 Transmit Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

Figure 5-5 Transmit State Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

Figure 5-6 Receive Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

Figure 5-7 Receive State Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

List of Tables

Table 3-1 4B5B Code-Group Encoding/Decodi ng. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

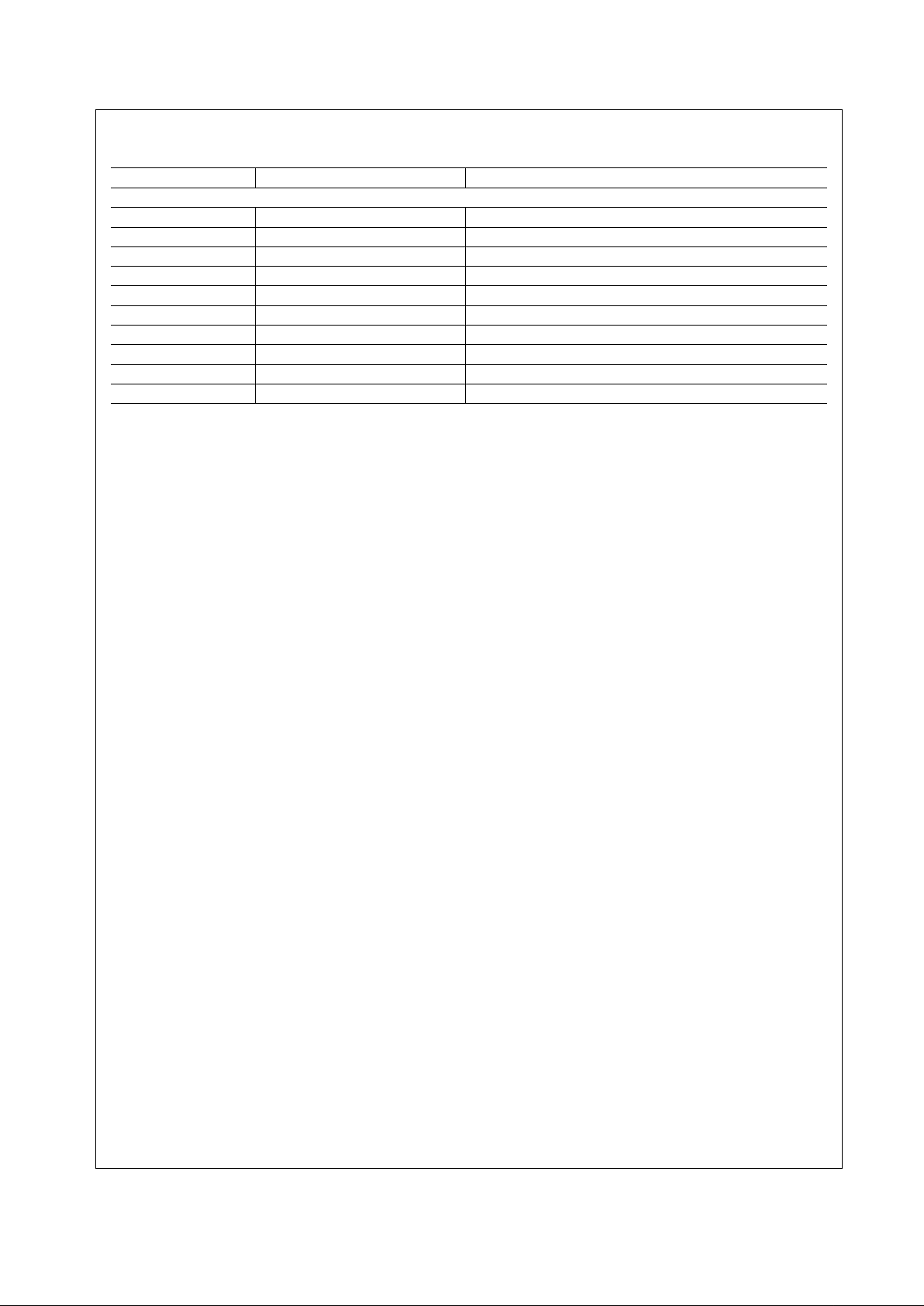

Table 4-1 Configuration Register Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Table 4-2 Operational Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Table 4-3 MIB Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

Table 5-1 DP83815 Descriptor Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

Table 5-2 cmdsts Common Bit Definitions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

Table 5-3 Transmit Status Bit Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

Table 5-4 Receive Status Bit Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

Table 5-5 Transmit State Tables . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

Table 5-6 Receive State Tables . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

4 www.national.com

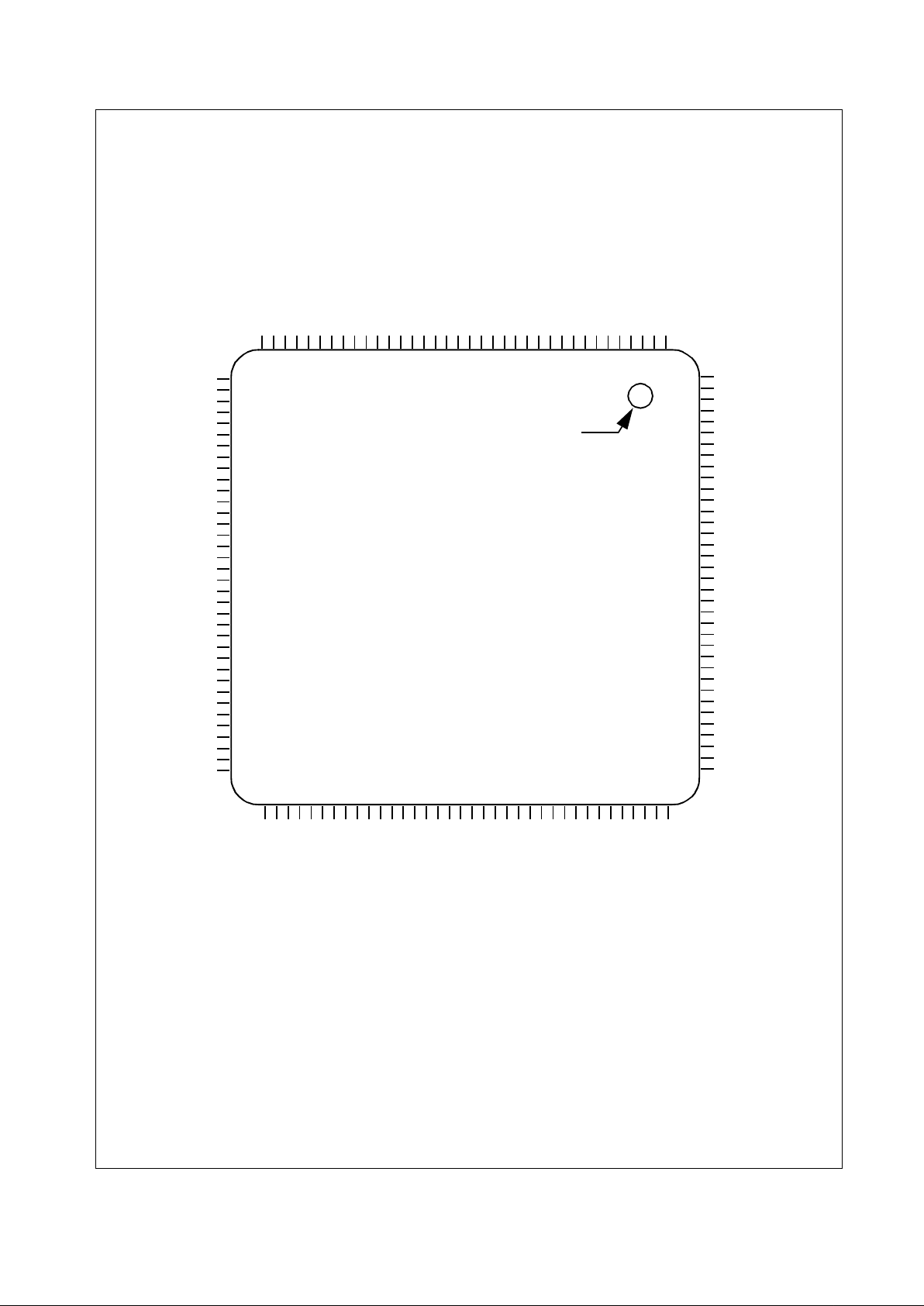

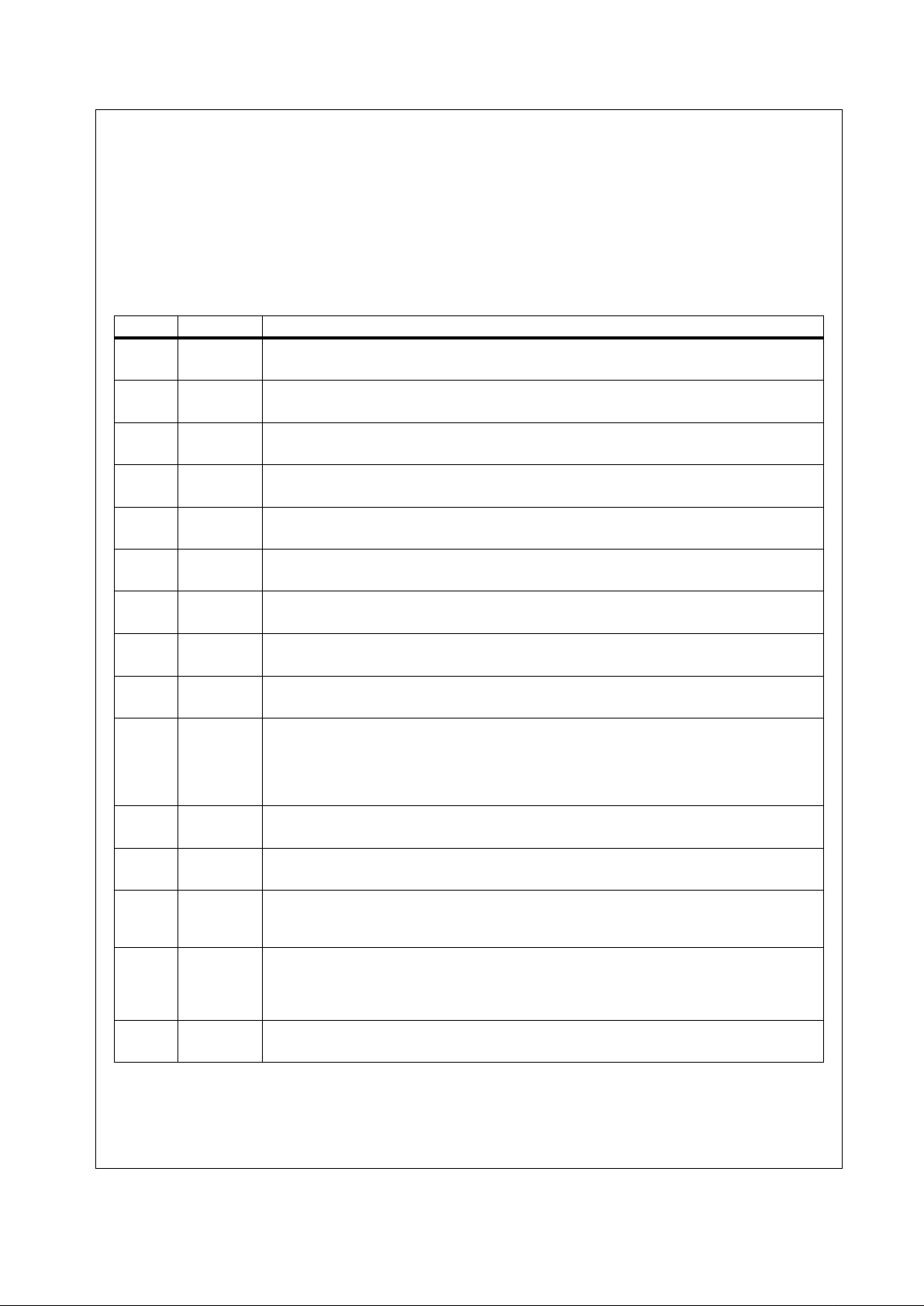

1.0 Connection Diagram

Order Number DP83815VNG

See NS Package Number VNG14 4A

121

122

123

124

125

126

127

128

129

130

131

132

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

80

79

78

77

76

75

74

73

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

123456789

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

30

31

323329

Identification

Pin1

37

38

39

40

120

119

118

117

116

115

114

113

112

110

109

111

DEVSELN

TRDYN

IRDYN

FRAMEN

CBEN2

AD16

AD17

AD18

STOPN

PERRN

SERRN

PAR

CBEN1

AD15

AD14

AD13

AD12

AD11

AD10

AD9

PCIVSS4

AD8

AD19

AD20

AD21

AD22

AD23

IDSEL

PCIVSS2

PCIVDD3

VSSIO4

PCIVDD4

VDDIO4

PCIVSS3

PCIVDD2

CBEN3

AD24

AD25

AD26

CBEN0

MACVSS1

MACVDD1

RESERVED

VREF

PCIVDD1

AD29

AD31

PCIVSS1

REQN

GNTN

RSTN

INTAN

AD28

PCICLK

AD30

PMEN/CLKRUNN

TXIOVSS2

TXIOVSS1

TPTDP

TPTDM

NC

RXAVDD2

RXAVSS2

TPRDP

TPRDM

SUBGND2

AD27

AD7

AD6

AD5

PCIVSS5

MA1/LED10N

MA2/LED100N

MA3/EEDI

MA4/EECLK

MA5

MWRN

MD4/EEDO

MD3

EESEL

AD0

AD1

AD2

AD3

AD4

MD0

MCSN

MD1/CFGDISN

MD2

MD5

MD6

MD7

MA0/LEDACTN

PCIVDD5

VSSIO2

VDDIO2

MACVSS2

MACVDD2

VDDIO5

VSSIO5

MDIO

MDC

RXCLK

RXD0/MA6

RXD1/MA7

RXD2/MA8

RXD3/MA9

RXOE

RXER/MA10

RXDV/MA11

TXD3/MA15

COL/MA16

CRS

TXEN

TXCLK

TXD2/MA14

TXD1/MA13

TXD0/MA12

VSSIO3

VDDIO3

VSSIO1

VDDIO1

X2

X1

DP83815

SUBGND3

PHYVSS1

PHYVDD1

NC

3VAUX

363534

67

68

69

70

71

72

100

101

102

103

104

105

106

107

108

144

143

142

141

140

139

138

137

136

135

134

133

RXAVSS1

RXAVDD1

PWRGOOD

MRDN

TXDVDD

FXVDD

FXVSS

PHYVSS2

PHYVDD2

SUBGND1

RESERVED

NC

NC

RESERVED

TXDVSS

5 www.national.com

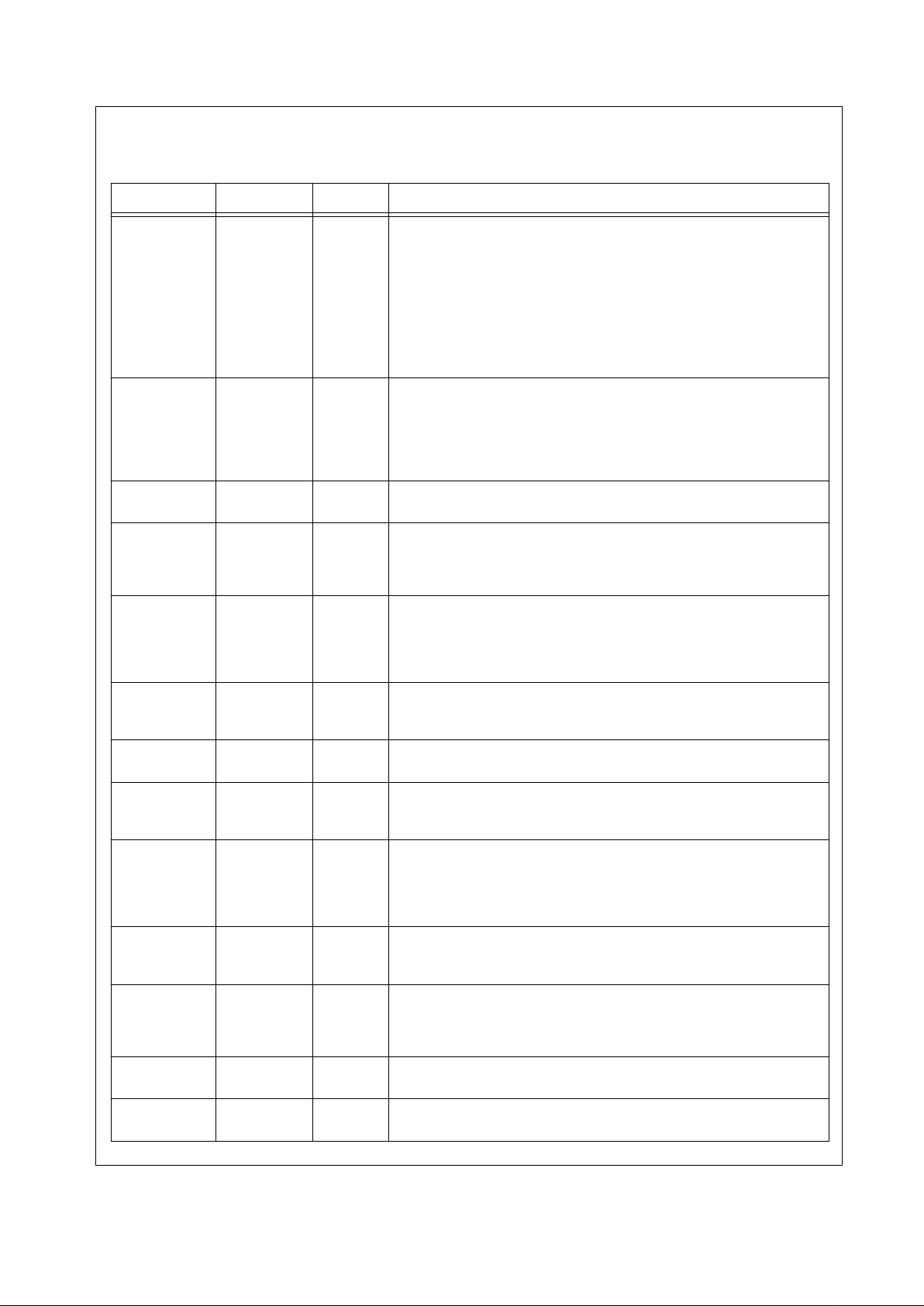

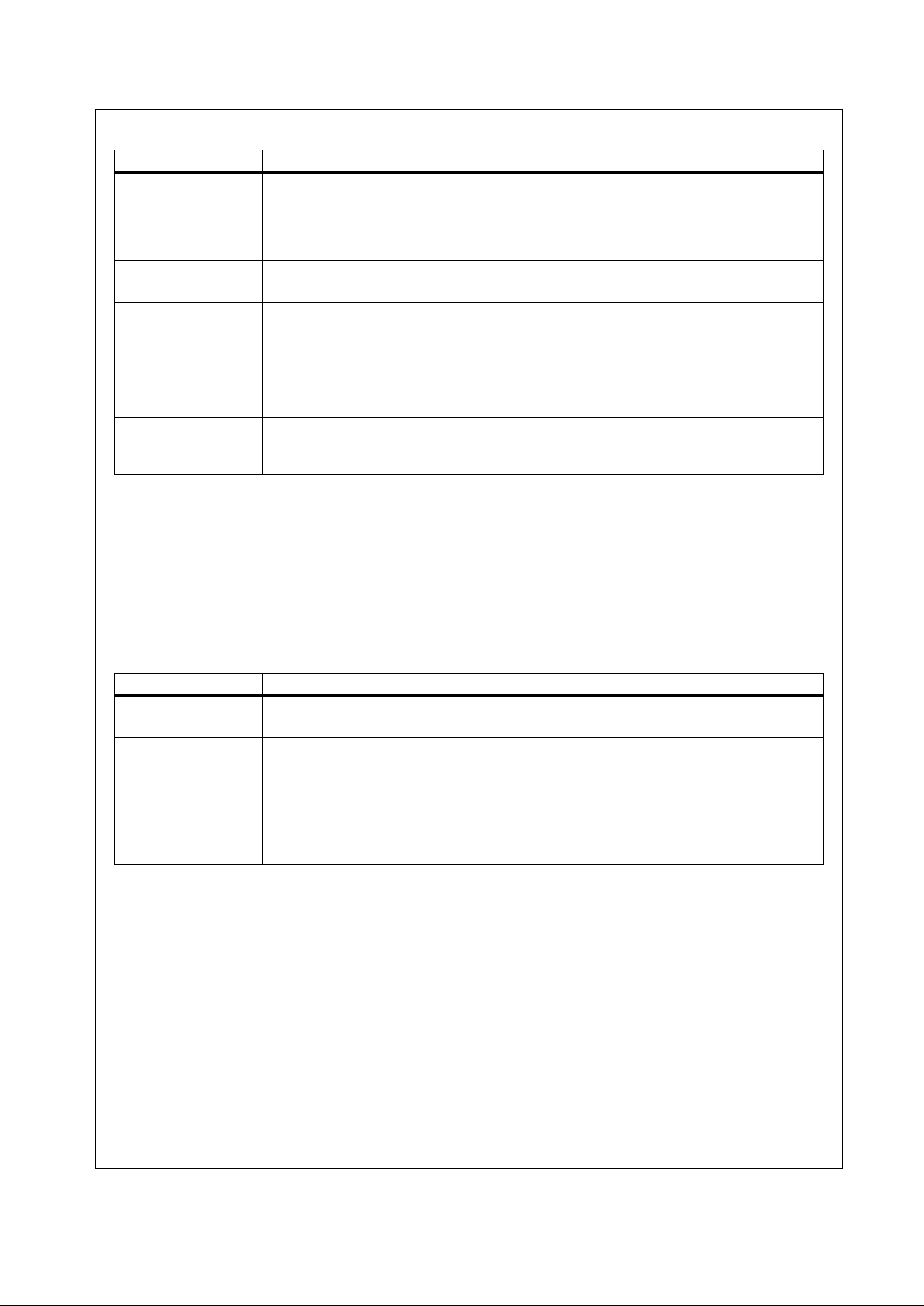

2.0 Pin Description

PCI Bus Interface

Symbol Pin No(s) Direction Descripti on

AD[31-0 ] 66, 67 , 6 8, 7 0,

71, 72, 73, 74,

78, 79, 81, 82,

83, 86, 87, 88,

101, 10 2, 104 ,

105, 10 6, 108 ,

109, 11 0, 112 ,

113, 11 5, 116 ,

118, 11 9, 120 ,

121

I/O

Address and Data:

Multipl exed address an d da ta bus. As a bus ma s t er, the

DP83815 will drive address during the first bus phase. During subsequent

phases, the DP83815 w ill either read or write data ex pecting the target to

increm ent its address pointer. As a bus target, the DP83815 will decode ea ch

address on the bus and respond if it is the target being addressed.

CBEN[3-0] 75,89,100,111 I/O

Bus Command/Byte Enable:

During the address phase these signals define

the “b us com man d” o r t he type of bus tr an sac ti o n tha t wil l ta k e pl ace. D uri ng the

data phase these pins indicate which byte lanes contain valid data. CBEN[0]

applies to byte 0 (bits 7-0) and CBEN[3] applies to byte 3 (bits 31-24) in the

Little Endian Mode. In Big Endian Mode, CBEN[0] applies to byte 0 (bits 31-24)

and CBEN[3] applies to byte 3 (bits 7-0 ).

PCICLK 60 I

Clock:

This PCI Bus clock provi des timing for all bus phases . The risi ng edge

defines the start of each phase. Th e clock frequency ranges from 0 to 33 MHz.

DEVSELN 95 I/O

Device Select:

As a target, the DP83815 asserts this signal low when it

recognizes its address after FRAMEN is asserted. As a bus master, the

DP83815 samples this signal to insure that the destination address for the data

transfer is recognized by a PCI target.

FRAMEN 91 I/O

Frame:

As a bus master, this signal is asserted low to indicate the beginning

and duration of a bus transaction. Data transfer tak es place when this signal is

asserted. It is de-asserted before the transaction is in its final phase. As a

target, the device monitors this signal before decoding the address to check if

the current transaction is addressed to it.

GNTN 63 I

Grant:

This signal is asserted low to ind icate to the DP83815 that it has been

granted ownership of the bus by the central arbiter. This input is used when the

DP83815 is acting as a bus master.

IDSEL 76 I

Initialization Device Select:

This pin is sampled by the DP83815 to identify

when configuration re ad and write accesses are intended for it.

INT AN 61 O

Interrupt A:

This signal is asserted low w hen an interrupt condition as defined

in the Interrupt Status Register, In terrupt Mask, and I nterrupt Enabl e registers

occurs.

IRDYN 92 I/O

Initiator Ready:

As a bus master, this signal will be asserted low when the

DP83815 is ready to complete the current data phase transaction. This signal is

used in conjunction with the TRYDN signal . Data transaction takes place at the

rising edge of PCICLK when both IRDYN and TRDYN are asserted low. As a

target, this signal indicates that the master has put the data on the bus.

PAR 99 I/O

Parity:

This signal indicates even parity across AD[31-0] and CBEN[3-0]

includ ing the PAR pin. As a master, PAR is asserte d during address and write

data phases. As a target, PAR is asserted during read data phases.

PERRN 97 I/O

Parity Error:

The DP83815 as a master or target w ill assert this signal low to

indica te a pa rity er ror o n any in com in g d ata ( exc ep t f or sp ec ial c ycl e s) . As a bus

master, it will monitor this signal on all write operati ons (except for special

cycles).

REQN 64 O

Request:

The DP83815 will assert this signal low to request the owne rship of

the bus to the central arbiter.

RSTN 62 I

Reset:

When this signa l is asserted all outputs of DP83815 will be tri -stated

and the devic e will be put into a known state.

6 www.national.com

2.0 Pin Description

(Continued)

SERRN 98 I/O

System Error:

This signal is asserted low by DP83815 during address parity

errors and system errors if enabled.

STOPN 96 I/O

Stop:

This signal is ass erted low by the target device to request the master

devi ce to stop the curr ent transacti on.

TRDYN 93 I/O

Target Ready:

As a target, this signal will be asserted low when the (sl ave )

device is ready to complete the current data phase transaction. This signal is

used in conjunct ion wit h the IRDYN signal. Data transaction takes place at the

rising edge of PCICLK when both IRDYN and TRDYN are asserted low. As a

master, this signal indicates that the targe t is ready for the data during writ e

operation and with the data during read operation.

PMEN/

CLKRUNN

59 I/O

Power Management Event/Clock Run Function:

This pin is a dual function

pin. The function of this pin is determined by the CLKRUN_EN bit 0 of the

CLKRUN Control and Status register (CCSR). This pin comes up with the

PMEN function selected.

Power Management Event:

This signal is asserted low by DP83815 to indicate

that a power management event has occurred.

Clock Run Function:

In this mode, this pin is used to indicate when the

PCICLK will be stopped.

3VAUX 122 I

PCI Aux Voltage Sense:

This pin is used to sense the presence of a 3.3v

auxili ary supply in order to define the PME Support available.

This pin has an internal weak pull down.

PWRGOOD 123 I

PCI bus power good:

Connected to PCI bus 3.3v power, this pin is used to

sense th e presence of PCI b us power during the D3 power management state.

This pin has an internal weak pull down.

Media Independent Interface (MII) - For Test Purposes Only.

Symbol Pin No(s) Direction Description

COL 28 I

Collision Detect:

The COL signal is asserted high asynchronously by the

external PMD upon detection of a collision on the medium. It will remain

asserted as long as the collision condition persists.

CRS 29 I

Carrier Sense:

This signal is asserted high asynch ronously by the external

physical un it up on detectio n of a non - id le med iu m .

MDC 5 O

Management Data Clock:

Clock signal with a maximum rate of 2.5 MHz used

to transfer management data for the external PMD on the MDIO pin.

MDIO 4 I/O

Management Data I/O:

Bidirectiona l signal used to transfer management

inf ormation for the external PMD. Requires an external 4.7 KΩ pullup resisto r.

RXCLK 6 I

Receive Clock:

A continuous clock, sourced by an external PMD device, that is

recovered from the incoming data. During 100 Mb/s operation RX_CLK is 25

MHz and duri ng 10 Mb/s this is 2.5 MHz.

RXD3/MA9,

RXD2/MA8,

RXD1/MA7,

RXD0/MA6

12, 11, 10, 7 I

O

Receive Data

: This is a group of 4 signals, sourced from an external PMD, that

conta in s da t a al ig ne d on nibble boundaries and are dr iven syn c hr o no us to t he

RX_CLK. RXD[3] is the most significant bit and RXD[0] is the least sign ificant

bit.

BIOS ROM Address:

During external BIOS ROM access, these signals

become part of the R OM address.

PCI Bus Interface

Symbol Pin No(s) Direction Descripti on

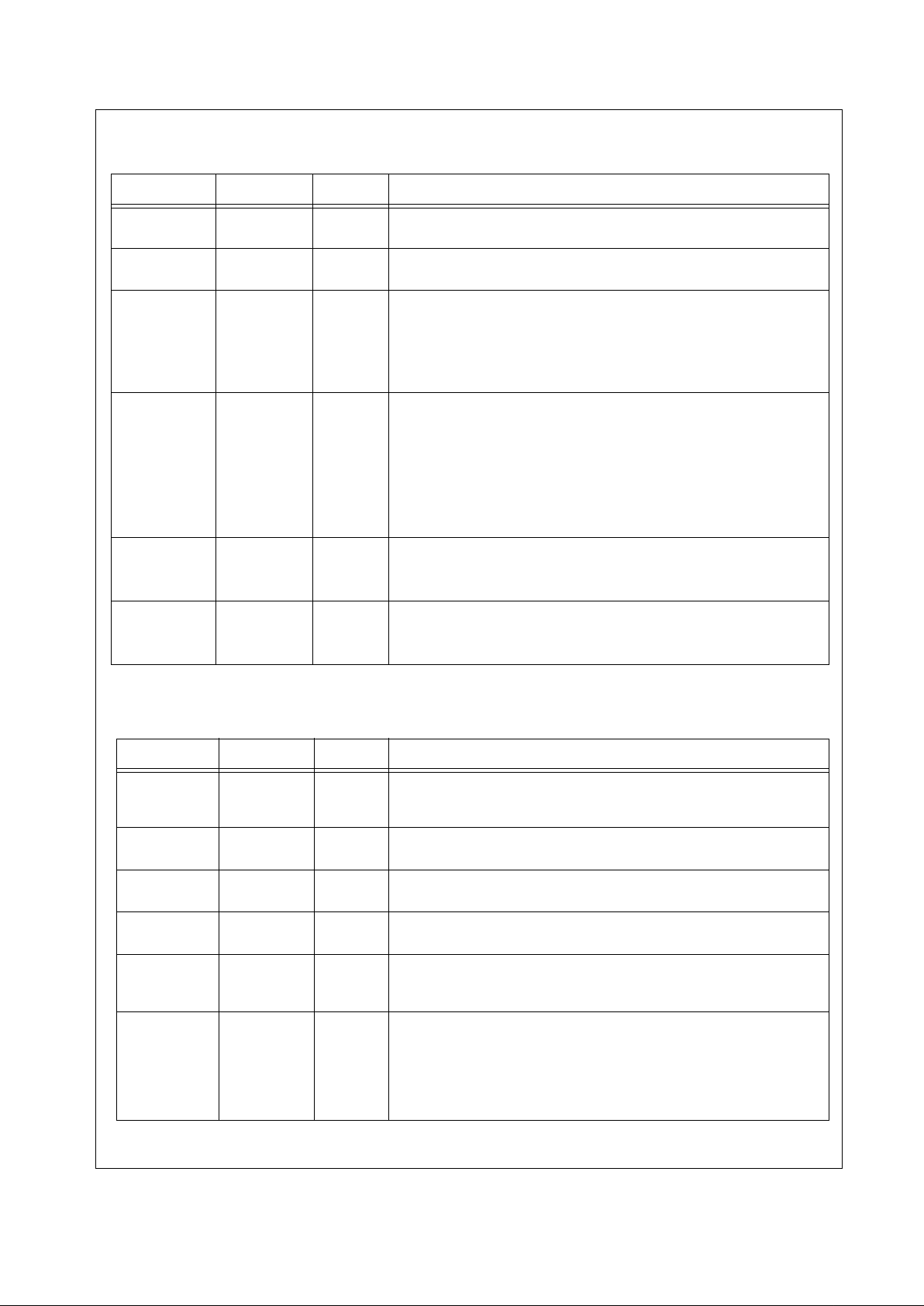

7 www.national.com

2.0 Pin Description

(Continued)

RXDV/MA11 15 I

O

Receive Data Valid:

This indicates that the external PMD is presenting

recovered and decoded nibbles on the RXD sign als, and that RX_CLK is

synchronous to the recovered data in 100Mps operation. This si gnal will

encompass the frame, starting with the Start-of-Frame delimiter (JK) and

excluding an y End-of-Frame delimiter (TR).

BIOS ROM Address:

During external BIOS ROM access, this signal becomes

part of the ROM address.

RXER/MA10 14 I

O

Receive Error:

This signal is asserted high synchronously by the external PMD

whenever it detects a media error and RXDV is asserted in 100Mps operation.

BIOS ROM Address:

During external BIOS ROM access, this signal becomes

part of the ROM address.

RXOE 13 O

Receive Output Enable:

This pin is used to disable an external PMD while th e

BIOS ROM is being accessed.

TXCLK 31 I

Transmit Clock:

A continuous clock that is sourced by the external PMD.

During 100 Mb/s operation this is 25 MHz +/- 100 ppm. During 10 Mb/s

operation thi s clock is 2.5 MHz +/- 100 ppm.

TXD3/MA15,

TXD2/MA14,

TXD1/MA13,

TXD0/MA12

25, 24, 23, 22 O

O

Transmit Data:

This is a group of 4 data signal s which are driven synchronous

to the T XCLK for transmission to th e external PMD. TXD [3] is the most

significant bit and TXD[0] is the least significant bit.

BIOS ROM Address:

During external BIOS ROM access, these signals

become part of the R OM address.

TXEN 30 O

Transmit Enable:

This signal is synchronous to TXCLK and provides precise

framing for data carried on TX D[3-0] for the exte rnal PMD. It is asserted when

TXD[3-0] contains valid data to be transmitted.

100BASE-TX/10BASE-T Interface

Symbol Pin No(s) Direction Description

TPTDP,

TPTDM

54, 53 A-O

Transmit Data:

Differential commo n output driver. This differential output is

configurable to either 10BASE-T or 100BASE-TX signaling:

10BASE-T: Transmission of Manchester encoded 10BASE-T packet data as

well as Link Pulses (including Fast Link Pulses for A uto-Negotiation purposes).

100BASE-TX: Transmission of ANS I X3T12 c ompliant MLT-3 data.

The DP83815 will automatically config ure this common output dri ver for the

proper signal type as a result of either forced configuration or Auto-Negotia tion.

TPRDP,

TPRDM

46, 45 A-I

Receive Data:

Different ial com m on input buffer. This diff erential input can be

configured to accept either 100BASE-TX or 10BASE-T signaling:

10BASE-T: Reception of Mancheste r encoded 10BASE-T pa cket data as well

as normal Link Puls es and Fast Link Pulses for Auto-Negotiation pu rposes.

100BASE-TX: Reception of ANSI X3T 12 compliant scrambled MLT-3 dat a.

The DP83815 will automatically configur e this common input buffer to accept

the proper signal type as a result of either fo rced configur ation or AutoNegotiation.

Media Independent Interface (MII) - For Test Purposes Only.

Symbol Pin No(s) Direction Description

8 www.national.com

2.0 Pin Description

(Continued)

Note: DP83815 supports NM27LV010 for the ROM interface device.

BIOS ROM/Flash Interface

Symbol Pin No(s) Direction Description

MCSN 129 O

BIOS PROM/Flash Chip Select:

During a BIOS ROM/Flash ac cess, this

signal is used to select the ROM device.

MD7, MD6, MD5,

MD4/EEDO, MD3,

MD2,

MD1/CFGDISN,

MD0

141, 140, 139,

138, 135, 134,

133, 13 2

I/O

BIOS ROM/Flash Data Bus:

During a BIOS ROM/Flash access these

signals are used to transfer data to or from the ROM/Flash device.

MD[5:0] and MD7 pins have an internal weak pull up.

MD6 pin has an internal weak pull down.

MA5, MA 4/EECLK ,

MA3/EEDI,

MA2/LE D100LNK,

MA1/LE D10LNK,

MA0/LE DACT

3, 2, 1, 144,

143, 14 2

O

BIOS ROM/Flash Address:

During a BIOS ROM/Flash access, these

signal s are used to drive the ROM/Flash address.

MWRN 131 O

BIOS ROM/Flash Write:

During a BIOS ROM/Flash access, this signal is

used to e nable data to be written to the Fl ash de vice.

MRDN 130 O

BIOS ROM/Flash Read:

During a BIOS ROM/Flash access, this signal is

used to enable data to be read from the Flash device.

Clock Interface

Symbol Pin No(s) Direction Description

X1 17 I

Crystal/Oscillator Input:

This pin is the primary clock reference input for the

DP83815 IC an d mus t be co nn ecte d t o a 25MH z 0.0 05 % (50 pp m) c loc k s our c e .

The DP83815 de vice supports either an external crystal resonator connected

across pins X1 and X2, or an external CMOS-level oscillator source connected

to pin X1 only.

X2 18 O

Crystal Output:

This pin is used in conjunction wi th the X1 p in to connect to an

external 25MHz crystal resonator device. This pin must be left unconnected if

an ext ernal CMOS oscillator cloc k source is utilized. For more information see

the definition for pin X1.

LED Interface

Symbol Pin No(s) Direction Description

LEDACTN/MA0 142 O

TX/RX Activity:

This pin is an output indicating transmit/receive activity. This

pin is d riv en l o w to i ndica t e a ctive transmissi on or r ec ep tio n, an d can be use d t o

drive a low current LED (<4mA). The activity event is stretched to a minimum

duration of approximately 50ms.

LED100N/MA2 144 O

100Mb/s Link:

This pi n i s a n out pu t in dica ti ng t he 1 00M b/s Li nk st atus . T hi s p in

is driven low t o indicate Good Link status for 100Mb/s operation, and can be

used to d rive a low current LED (<4mA).

LED10N/MA1 143 O

10Mb/s Link:

This pin is a n ou tp ut indi ca ti n g th e 1 0Mb /s Li nk sta tu s . T hi s pi n is

driven low to indicate Good Link status for 10Mb/s operation, and can be used

to drive a low current LED (<4mA).

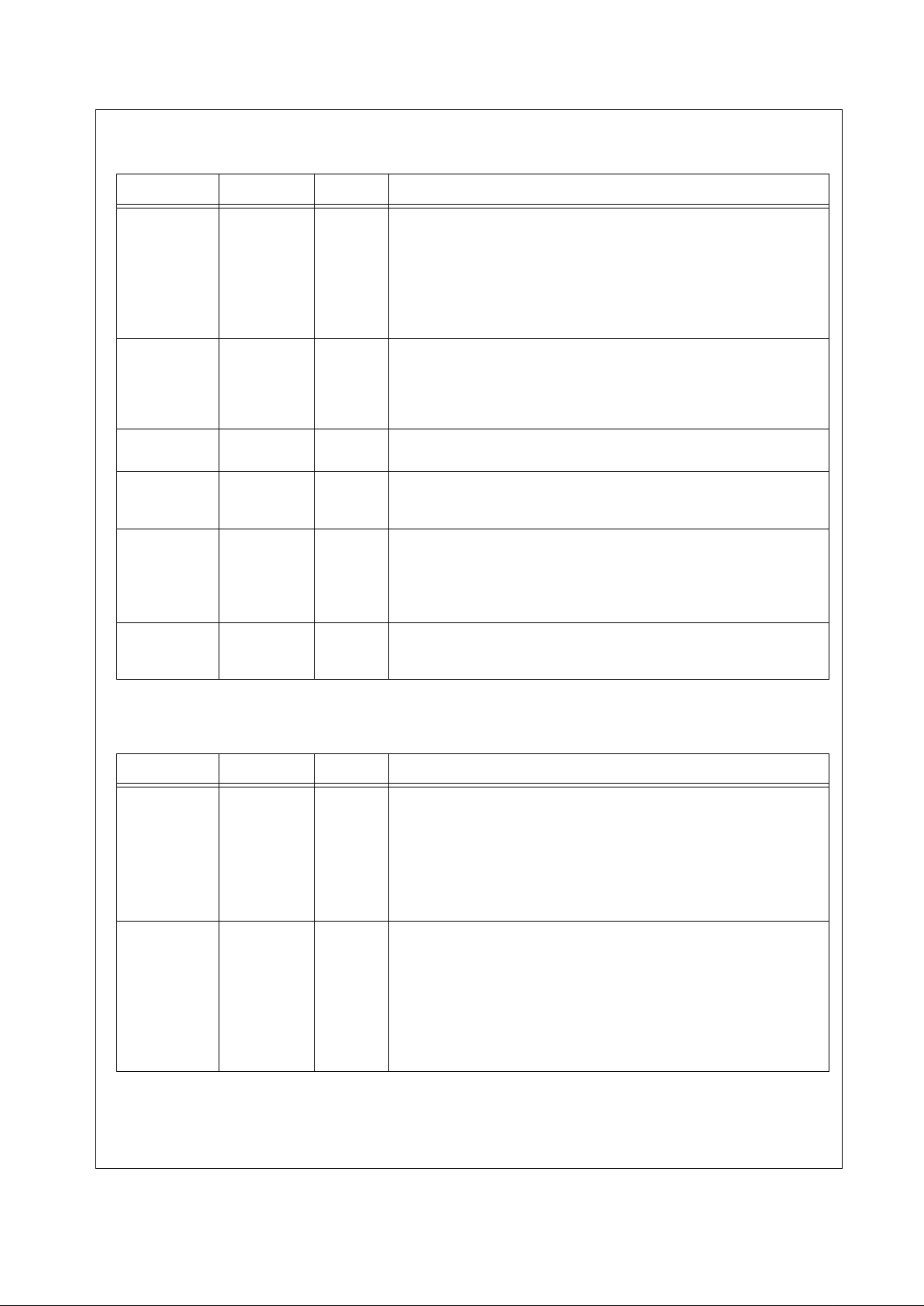

9 www.national.com

2.0 Pin Description

(Continued)

Note: DP83815 supports NMC93C46 for the EEPROM device.

Serial EEPROM Interface

Symbol Pin No(s) Direction Description

EESEL 128 O

EEPROM Chip Select:

This signal is used to enable the external EEPROM

device.

EECLK/MA4 2 O

EEPROM Clock:

During an EEPROM access (EESEL asserted), this pin is an

output used to drive the serial clock to an external EEPROM device.

EEDI/MA3 1 O

EEPROM Data In:

During an EEPROM access (EESEL asserted), this pin is

an outp ut used to dr ive opcode, address, and data to an external serial

EEPROM device.

EEDO/MD4 138 I

EEPROM Data Out:

During an EEPROM access (EESEL asserted), this pin is

an input used to retrieve EEPROM serial read data.

This pin has an internal weak pull up .

MD1/CFGDISN 133 I/O

Configuration Disable:

When pulled low at power-on time, disables load of

configuration data from the EEPROM. Use 1 KΩ to ground to disable cfg. load.

External Referen ce Inte rface

Symbol Pin No(s) Direction Description

VREF 40 I

Bandgap Reference:

External current reference resistor for internal Phy

bandga p circuitry. The value of this resistor is 9.31 KΩ 1% metal film

(100ppm/

o

C) which must be connected from the VREF pin to analog ground.

Supply Pins

Symbol Pin No(s) Direction Description

SUBGND1,

SUBGND2,

SUBGND3

37, 49, 126 S Substrate GND

RXAVDD1,

RXAVDD2

39, 47 S RX Analog VDD - connect to isolated Aux 3.3v supply VDD

RXAVSS1,

RXAVSS2

38, 44 S RX Analog GND

TXIOVSS1,

TXIOVSS2

52, 55 S TX Output driver VS S

TXDVDD 56 S TX Digital VDD - connec t to Aux 3.3v supply VDD

TXDVSS 51 S TX Digital VSS

MACVDD1,

MACVDD2

58,125 S Mac/BIU digital core VDD - connect to Aux 3.3v supply VDD

MACVSS1,

MACVSS2

57, 124 S Mac/BIU digital core VSS.

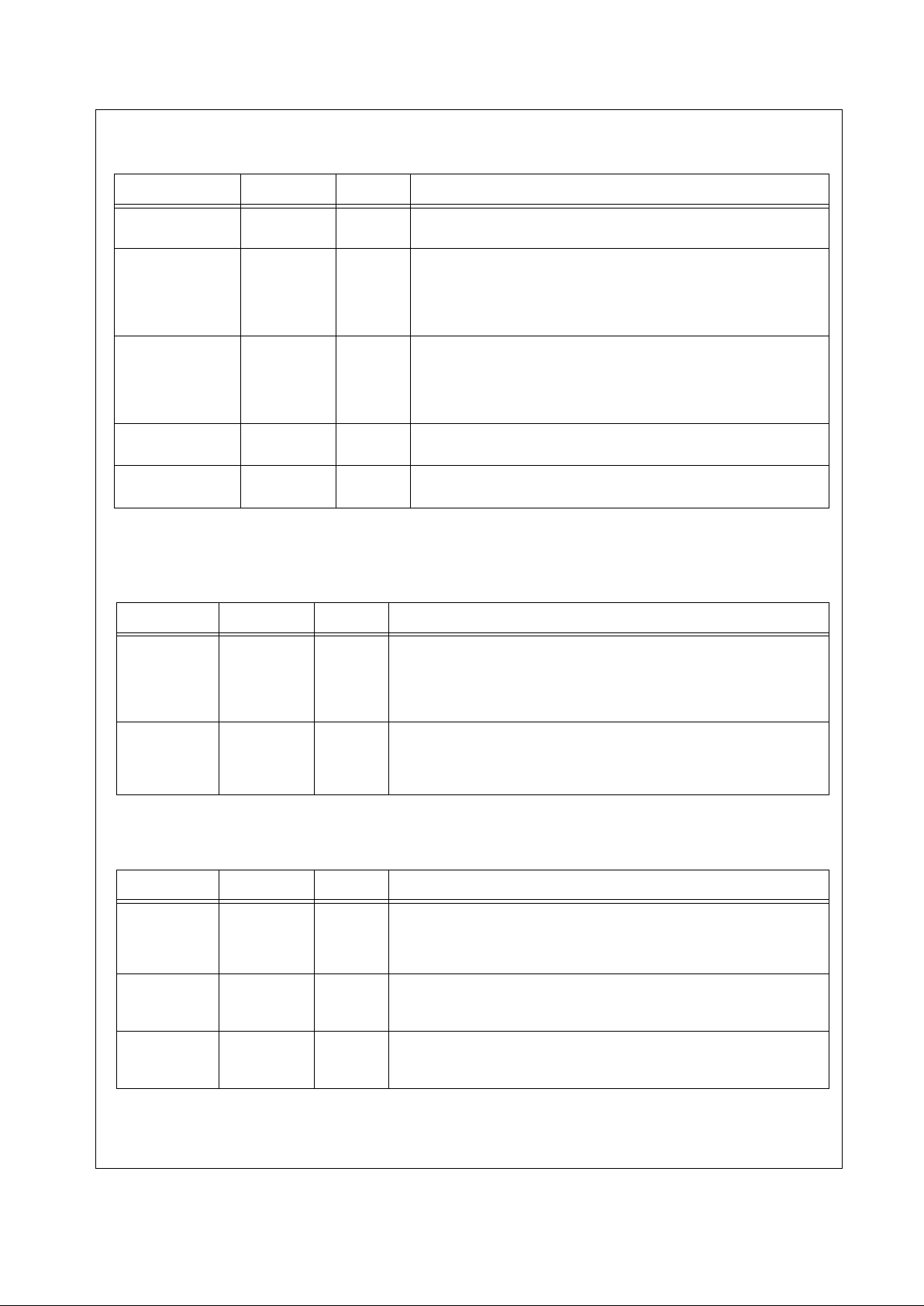

10 www.national.com

2.0 Pin Description

(Continued)

PCIVDD1,

PCIVDD2,

PCIVDD3,

PCIVDD4,

PCIVDD5

69, 80, 94,

107, 11 7

S PCI IO VDD - connect to PCI bus 3.3v VDD

PCIVSS1,

PCIVSS2,

PCIVSS3,

PCIVSS4,

PCIVSS5

65, 77, 90,

103, 11 4

S PCI IO VSS

VDDIO2,

VDDIO4

19, 85 S Misc. IO VDD - connect to Aux 3.3v supply VDD

VDDIO1,

VDDIO3,

VDDIO5

9, 27, 137 S Misc. IO VDD - connect to Aux 3.3v supply VDD

VSSIO2,

VSSIO4

16, 84 S Misc. IO VSS

VSSIO1,

VSSIO3,

VSSIO5

8, 26, 13 6 S Misc. IO VSS

PHYVDD1,

PHYVDD2

21, 33 S Phy digita l core VDD - connect to Aux 3.3v supply VDD

PHYVSS1,

PHYVSS2

20,32 S Phy digital core VSS

FSVDD 36 S Frequency Synthesizer VDD - co nnect to isolated Aux 3.3v supply VDD

FSVSS 35 S Fr equency Synthesi zer VSS

No Connects

Symbol Pin No(s) Direction Description

NC 34, 42, 43, 48 No Connect

Reserved 41, 50 , 127 These pins are reserved a nd cannot be connected to any external lo gic or net.

Supply Pins

Symbol Pin No(s) Direction Description

11 www.national.com

3.0 Functional Description

DP83815 consists of a MAC/BIU (Media Access

Controller/Bus Interface Unit), a physical layer interface,

SRAM, and miscellaneous support logic. The MAC/BIU

includes the PCI bus , BIOS ROM and EEPROM interfaces,

and an 802.3 MAC. The physical layer interface used is a

single-port version of the 3.3v DsPhyter. Internal memory

consists of on e - 0.5K B a nd two - 2K B SR A M blo cks.

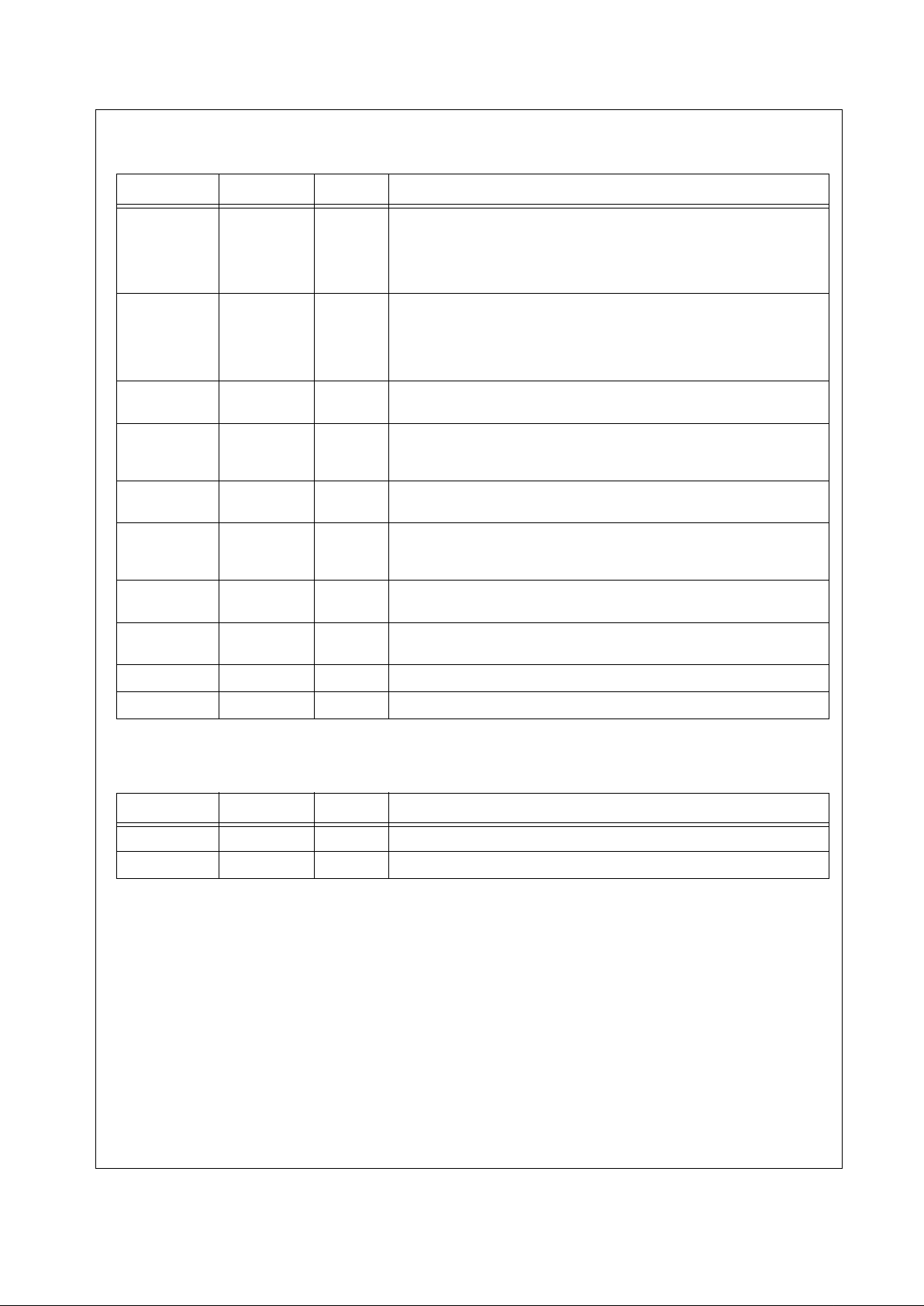

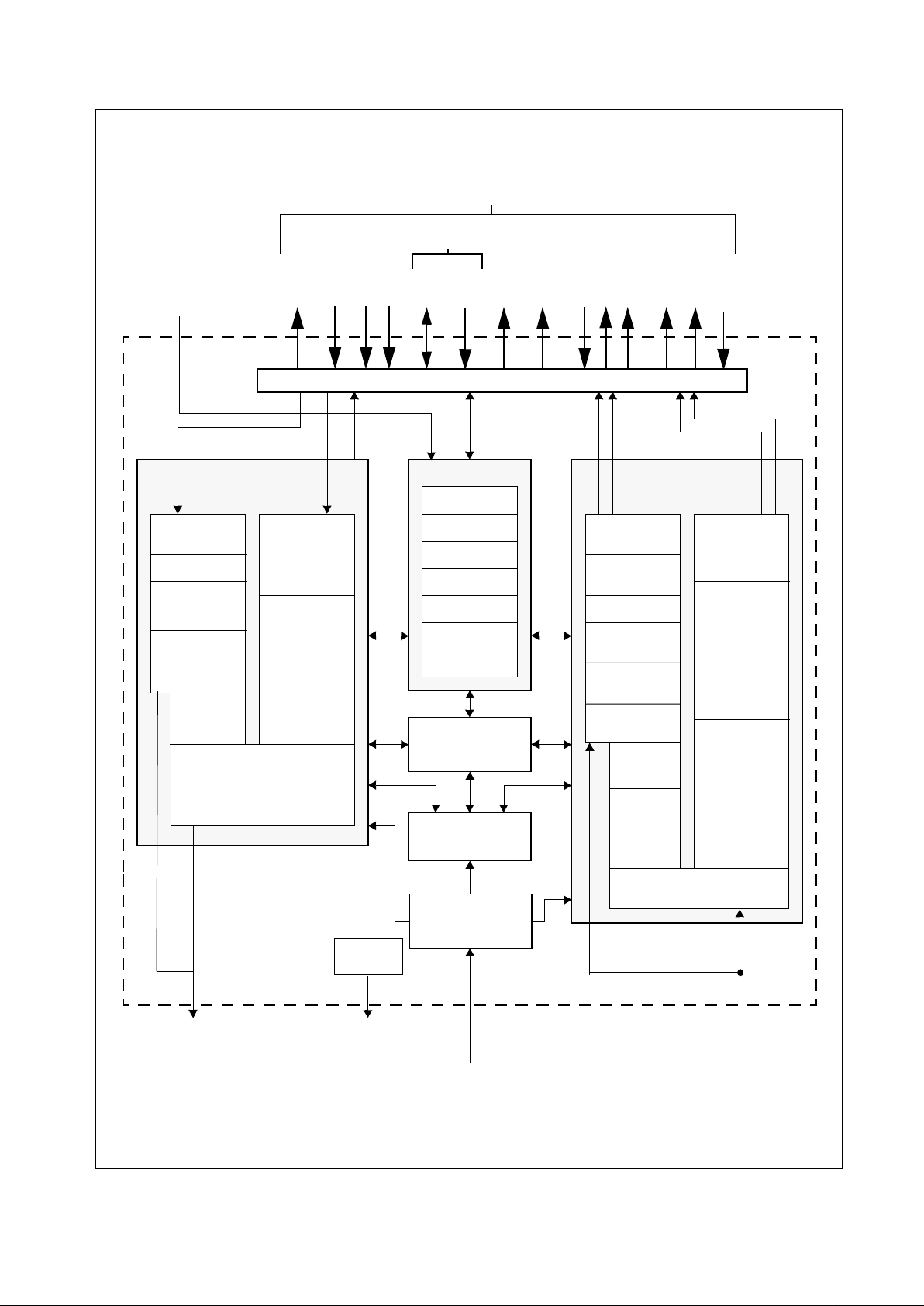

Figure 3-1 DP83815 Functional Block Diagram

MAC/BIU

Interface

SRAM

25Mhz Clk

MII RX

MII TX

MII Mgt

BIOS ROM Cntl

BIOS ROM Data

BROM/EE

PCI AD

PCI CNTL

PCI CLK

3v DSP Physical Layer

Logic

RX-2KB

SRAM

TX-2KB

TPRDP/M

EEPROM/LEDs

MII TX

MII RX

MII Mgt

Test data in

Test data out

MII TX

MII RX

MII Mgt

TPTDP/M

DP83815

Tx Addr

Tx wr data

Rx Addr

Rx wr data

Rx rd data

Tx rd data

RAM

BIST

Logic

SRAM

RXFilter

.5KB

3.0 Functional Description

(Continued)

12 www.national.com

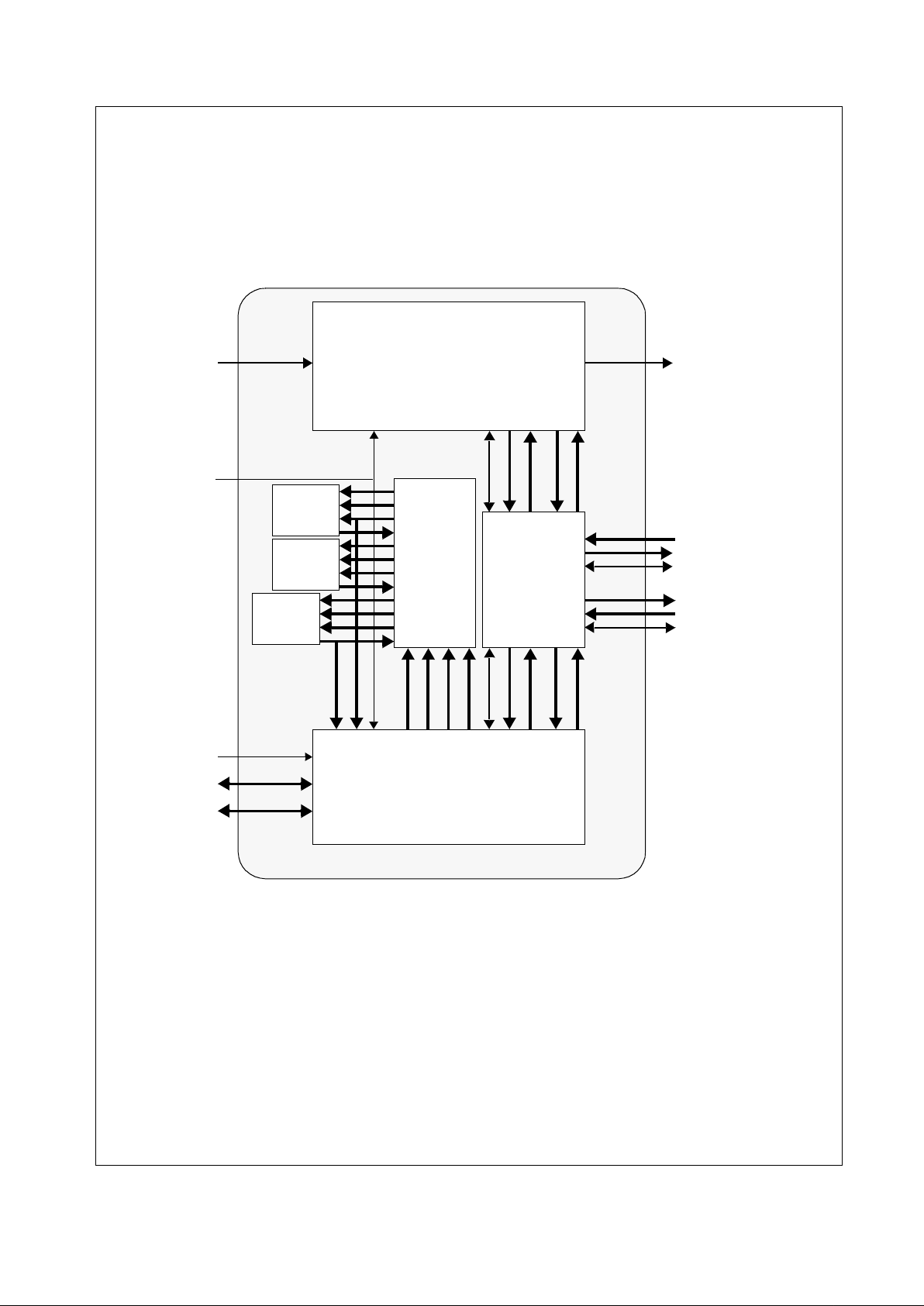

Figure 3-2

MAC/BIU

Functional Block Diagram

3.1 MAC/BIU

The MAC/BIU is a derivative design from the DP83810

(Euphrates). The original MAC/BIU design has been

optimized to improve logic efficiency and enhanced to add

features consistent with current market needs. The

MAC/BIU des ign blocks are di scussed in this secti on.

3.1.1 PCI Bus Interface

This block implements PCI v2.2 bus protocols, and

configura ti on space. Supports bu s master reads and writes

to CPU memory, and CPU access to on-chip register

space. Additional functions provided include: configuration

control, serial EEPROM access with auto configuration

load, interrupt control, power management control with

support for PME or CLKRUN function.

3.1.1.1 Byte Ordering

The DP83815 can be configured to order the bytes of data

on the AD[31:0] bus to conf orm to little endian or b ig endian

ordering through the use of the CFG:BEM bit

(Configuration Register, bit 0). On Power-up, the device is

in little endian ordering. Byte ordering only affects data

FIFOs. Regis ter information remains bit aligned (i.e . AD[31]

maps to bit 31 in any register space, AD[0] maps to bit 0,

etc).

Tx Buffer Manager

MIB

Tx MAC

Rx MAC

PCI Bus

Data FIFO

Physical Layer Interface

93C06

Serial

EEPROM

MAC/BIU

32

15

32

32

32

32

32

16

32

32

4

4

32

Rx Filter

Pkt Recog

Logic

SRAM

Rx Buffer Manager

Data FIFO

Boot ROM/

Flash

PCI Bus

Interface

3.0 Functional Description

(Continued)

13 www.national.com

Little Endian (CFG:BEM=0):

The byte orientation for

receive and transmit data and descriptors in system

memory is as follows:

Big Endian (CFG:BEM=1):

The byte orientation for

receive and transmit data and descriptors in system

memory is as follows:

3.1.1.2 PCI Bus Interr upt Control

PCI bus interrupts for the DP83815 are asynchronously

performed by asserting pin INTAN. This pin is an open

drain outp ut. The source o f t he interrupt can be determined

by reading the Interrupt Status Regis ter (ISR). One or more

bits in the ISR will be set, denoting all currently pending

interrupts.

Caution:

Reading of the ISR clears ALL bits.

Masking of specified interrupts can be accomplished by

using the Interrupt Mask Register (IMR).

3.1.1.3 Timer

The Latency Timer described in CFGLAT:LAT defines the

minimum number of bus clocks that the device will hold the

bus. Once the device gains control of the bus and issues

FRAMEN, the Latency Timer will begin counting down. If

GNTN is de-asserted before the DP83815 has finished

with the bus, the device will maintain ownership of the bus

until the timer reaches zero (or has finished the bus

transfer). The timer is an 8-b it counter .

3.1.2 Tx MAC

This block implements the transmit portion of 802.3 Media

Access Control. The Tx MAC retrieves packet data from the

Tx Buffer Manager and sends it out through the transmit

portion. Additionally, the Tx MAC provides MIB control

information for transmit packets .

3.1.3 Rx MAC

This block implements the receive portion of 802.3 Media

Access Control. The Rx MAC retrieves packet data from

the receive portion and sends it to the Rx Buffer Manager.

Additionally, the Rx MAC provides MIB control information

and packet address data for the Rx Filter .

3.2 Buffer Management

The buffer management scheme used on the DP83815

allows quick, simple and efficient use of the frame buffer

memory. Frames are saved in similar formats for both

transmit and receive. The buffer management scheme also

uses separate buffers and descriptors for packet

information. This allows effective transfers of data from the

receive buffer to the transmit buffer by simply transferring

the descriptor from the receive queue to the transmit

queue.

The format of the descriptors allows the packets to be

saved in a number of configurations. A packet can be

stored in memory with a single descriptor per single

packet, or multiple descriptors per single packet. This

flexibility allows the user to configure the DP83815 to

maximize efficiency. Architecture of the specific system’s

buffer memory, as well as the nature of network traffic, will

determine the most suitable configuration of packet

descriptors and fragments. Refer to the Buffer

Management Section for more information.

3.2.1 Tx Buffer Manager

This block DMAs packet data from PCI memory space and

places it in the 2KB transmit FIFO, and pulls data from the

FIFO to send to the Tx MAC. Multiple packets may be

present in the FIFO, al lowing pac kets to b e transmitted with

minimum interframe gap. The way in which the FIFO is

emptied and filled is controlled by the FIFO threshold

values in the TXCFG register: FLTH (Tx Fill Threshold),

DRTH (Tx Drain Threshold). These values determine how

full or empty the FIFO must be before the device requests

the bus. Additionally, once the DP83815 requests the bus,

it will attempt to empty or fill the FIFO as allowed by the

MXDMA setting in the TXCFG register.

3.2.2 Rx Buffer Manager

This block retrieves packet data from the Rx MAC and

places it in the 2KB receive data FIFO, and pulls data from

the FIFO for DMA to PCI memory space. The Rx Buffer

Manager maintains a status FIFO, allowing up to 4 packets

to reside in the FIFO at once. Similar to the transmit FIFO,

the receive FIFO is controlled by the FIFO threshold value

in the RXCFG register: DRTH (Rx Drain Threshold). This

value determines the number of long words written into the

FIFO from the MAC unit before a DMA request for system

memory access occurs. Once the DP83815 gets the bus, it

will continue to transfer the long words from the FIFO until

the data in the FIFO is less than one long word, or has

reached the end of the packet, or the max DMA burst size

is reached (RXCFG:MXDMA).

3.2.3 Packet Recognition

The Receive packet filter and recognition logic allows

software to control which packets are accepted based on

destination address and packet type. Address recognition

logic includes support for broadcast, multicast hash, and

unicast addresses. The packet recognition logic includes

Byte 0Byte 1Byte 2Byte 3

0781516

232431

LSB

C/BE[0]C/BE[1]C/BE[2]C/BE[3]

MSB

Byte 3Byte 2Byte 1Byte 0

0781516

232431

MSB

C/BE[0]C/BE[1]C/BE[2]C/BE[3]

LSB

3.0 Functional Description

(Continued)

14 www.national.com

support for WOL, Pause, and programmable pattern

recognition.

The standard 802.3 Ethernet packet consists of the

following fields: Preamble (PA), Start of Frame Delimiter

(SFD), Destination Address (DA), Source Address (SA),

Length (LEN), Data and Fr ame Check Sequence (FCS). All

fields are fixed length except for the data field. During

reception, the PA, SFD and FCS are stripped. During

transmissi on, the DP83815 generates and appends t he PA,

SFD and FCS.

3.2.4 MIB

The MIB block contains counters to track certain media

events required by the management specifications RFC

1213 (MIB II), RFC 1398 (Ether-like MIB), and IEEE 802.3

LME. The counters provided are for events which are eithe r

difficult or impossible to be intercepted directl y by software.

Not all counters are implemented, however required

counters can be calculated from the counters provided.

3.3 Interface Definitions

3.3.1 PCI System Bus

This interface allows direct connection of the DP83815 to a

33MHz PCI system bus. The DP83815 supports zero wait

state data transfers with burst sizes up to 128 dwords. The

DP83815 conforms to 3.3V AC/DC specifications, but has

5V tolerant inputs.

3.3.2 Boot PROM

The BIOS ROM interface allows the DP83815 to read from

and write data to an external PROM /Flash device .

3.3.3 EEPROM

The DP83815 supports the attachment of an external

EEPROM. The EEPROM interface provides the ability for

the DP83815 to read from and write data to an external

serial EEPROM device. Values in the external EEPROM

allow default fields in PCI configuration space and I/O

space to be overridden following a hardware reset. The

DP83815 will auto-load values from the EEPROM to these

fields in configuration space and I/O space and perform a

checksum to verify that the data is valid. If the EEPROM is

not present, the DP83815 initialization uses default values

for the appropriate Configuration and Operational

Registers. Software can read and write to the EEPROM

using “bit-bang” accesses via the EEPROM Access

Register.

3.3.4 Clock

The clock interface provides the 25MHz clock reference

input for the DP83815 IC. This interface supports operation

from a 25MHz, 50 ppm CMOS oscillator, or a 25MHz, 50

ppm crystal resonator.

Figure 3-3 Ethernet Packet Format

60b 4b 6B 2B 46B-1500B 4B

FCSDataLENSADAPA6BSFD

Note: B = Bytes

b = bits

3.0 Functional Description

(Continued)

15 www.national.com

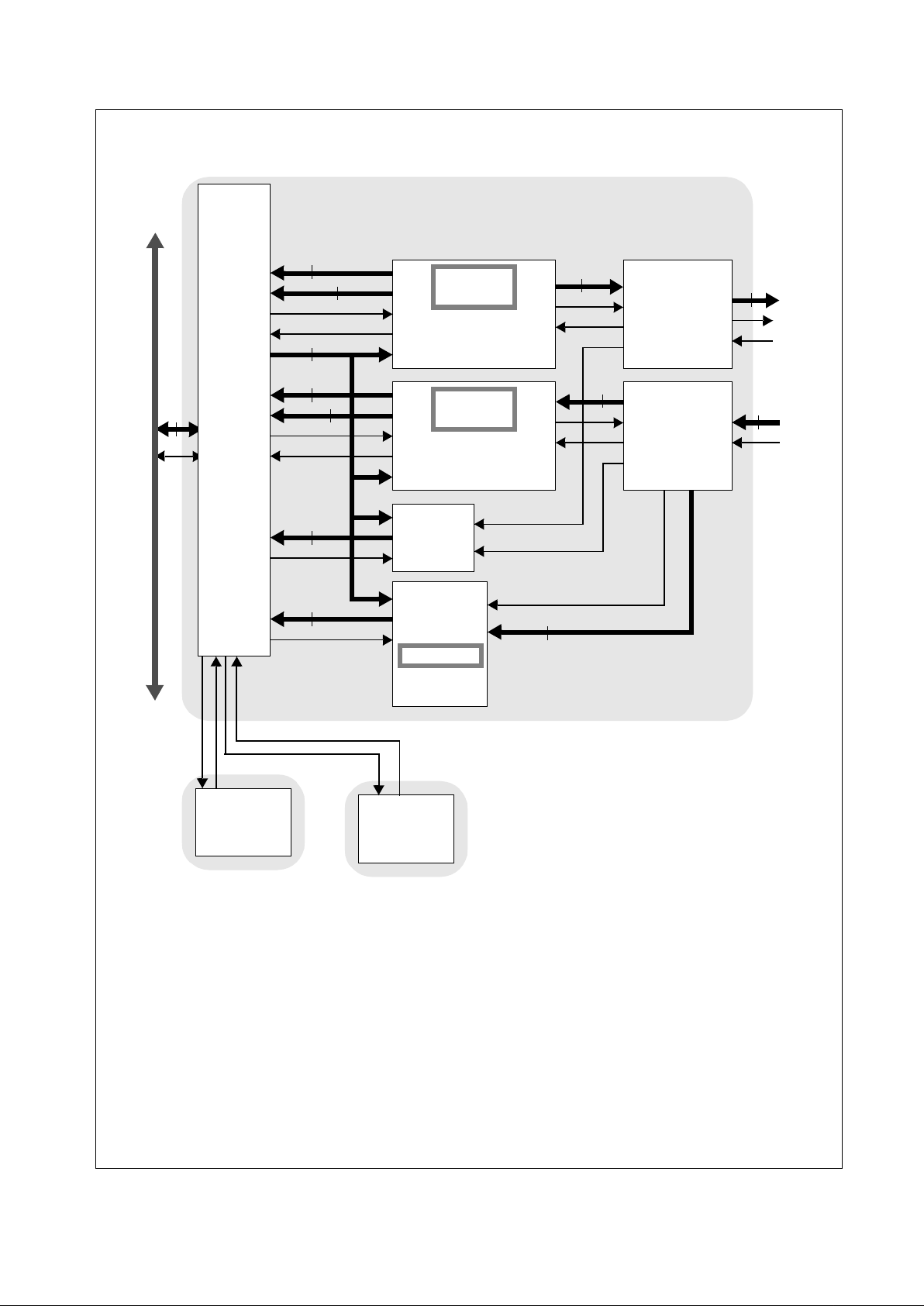

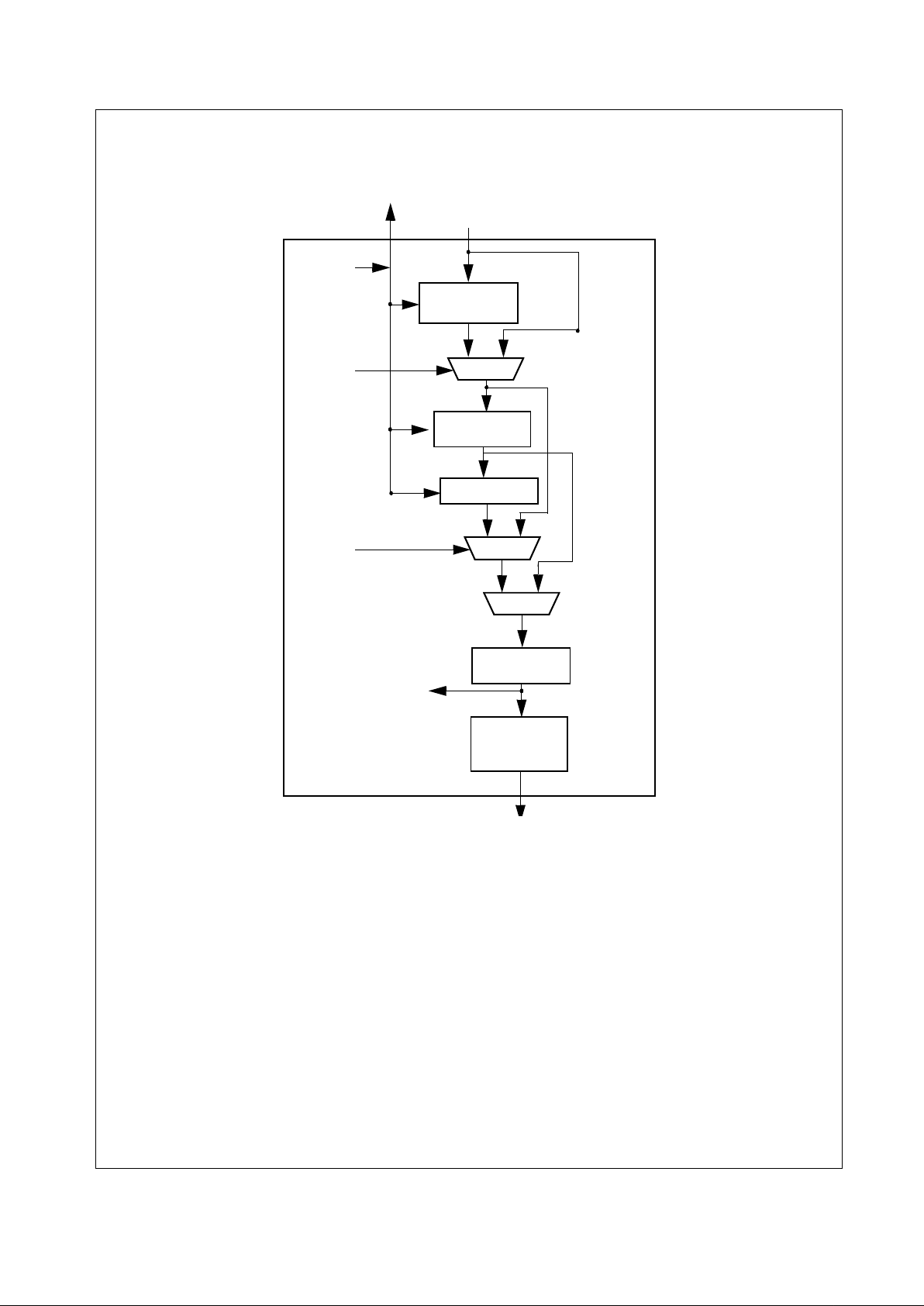

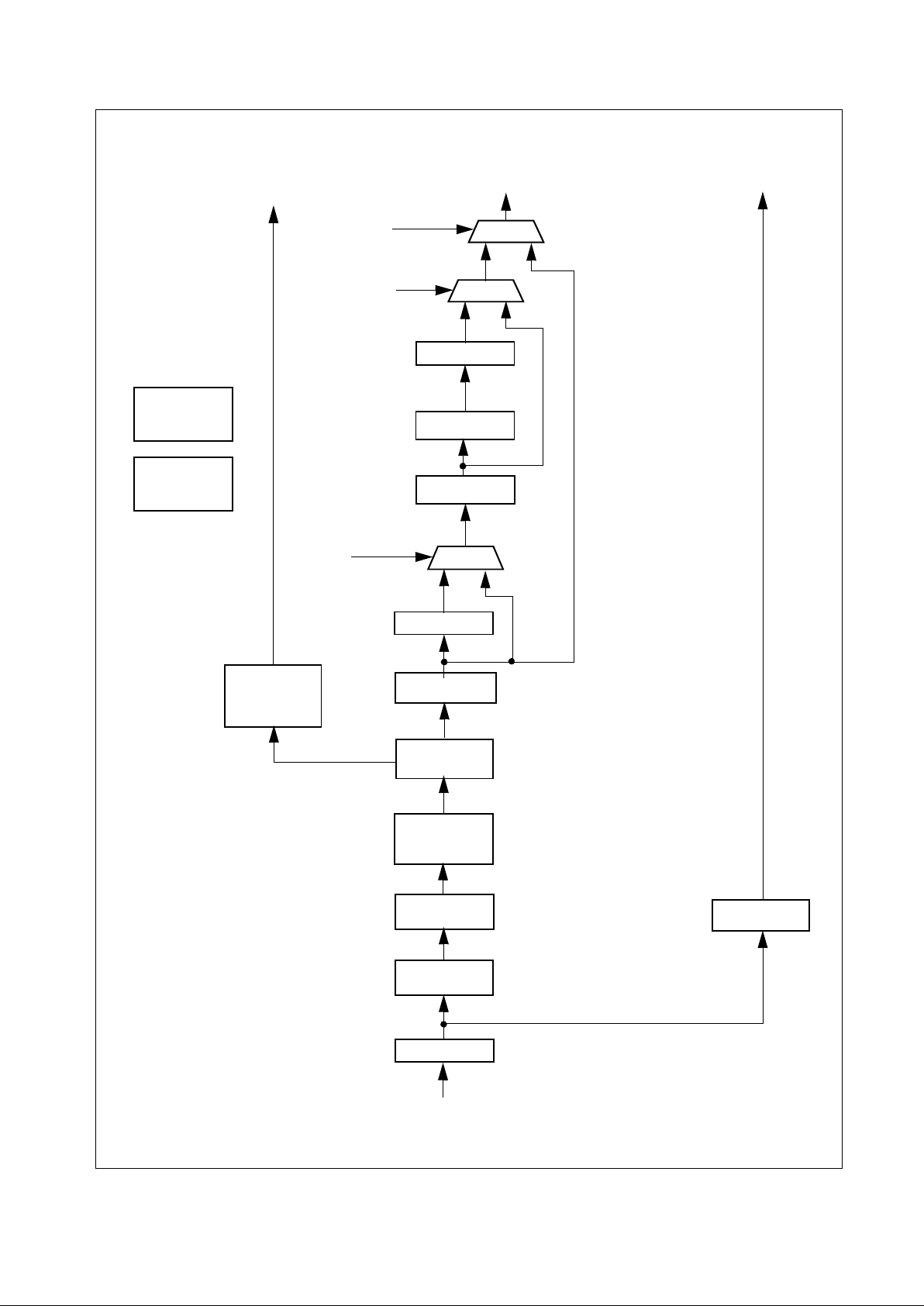

Figure 3-4 DSP Physical Layer Block Diagram

TRANSMIT CHANNELS &

100 MB/S 10 MB/S

NRZ TO

MANCHESTER

ENCODER

STATE MACHINES

TRANSMIT

FILTER

LINK PULSE

GENERATOR

4B/5B

ENCODER

SCRAMBLER

PARALLEL TO

SERIAL

NRZ TO NRZI

ENCODER

BINARY TO

MLT-3

ENCODER

10/100 COMMON

RECEIVE CHANNELS &

100 MB/S 10 MB/S

MANCHESTER

TO NRZ

DECODER

STATE MACHINES

RECEIVE

FILTER

LINK PULSE

DETECTOR

4B/5B

DECODER

DESCRAMBLER

SERIAL TO

PARALLEL

NRZI TO NRZ

DECODER

MLT-3 TO

10/100 COMMON

AUTO-NEGOTIATION

STATE MACHINE

FAR-END-FAULT

STATE MACHINE

REGISTERS

AUTO

100BASE-X

10BASE-T

MII

BASIC MODE

PCS CONTROL

PHY ADDRESS

NEGOTIATION

CLOCK

CLOCK

RECOVERY

CLOCK

RECOVERY

CODE GROUP

ALIGNMENT

SMART

SQUELCH

RX_DATA

RX_CLK

RX_DATARX_CLK

TX_DATA

TX_DATA

TX_CLK

SYSTEM CLOCK

REFERENCE

RD

±

TD

±

OUTPUT DRIVER

INPUT BUFFER

BINARY

DECODER

ADAPTIVE

EQ

AND

BLW

COMP.

(ALSO FX_RD

±)

LED

DRIVERS

LEDS

HARDWARE

CONFIGURATION

PINS

GENERATION

(AN_EN, AN0, AN1)

CONTROL

NCLK_50M

TX_CLK

TXD(3:0)

TX_ER

TX_EN

MDIO

MDC

COL

CRS

RX_EN

RX_ER

RX_DV

RXD(3:0)

RX_CLK

MAC INTERFACE

SERIAL

MANAGEMENT

3.0 Functional Description

(Continued)

16 www.national.com

3.4 P hysical Layer

The DP83815 has a full featured physical layer device with

integrated PMD sub-layers to support both 10BASE-T and

100BASE-TX Ethernet protocols. The physical layer is

designed for easy implementation of 10/100 Mb/s Ethernet

home or office solutions. It interfaces directly to twisted pair

media via an external transformer. The physical layer

utilizes on chip Digit al Signal Processing (DSP) technology

and digital PLLs for robust performance under all operating

conditions, enhanced noise immunity, and lower external

component count when com pared to analog solutions.

3.4.1 Auto-Negotiation

The Auto-Negotiation function provides a mechanism for

exchanging configuration inform ation between two ends of

a link segment and automatically selecting the highest

performance mode of operat ion supported by both devices.

Fast Link Pulse (FLP) Bursts provide the signalling used to

communicate Auto-Negotiation abilities between two

devices at each end of a link segment. For further detail

regarding Auto-Negotiation, refer to Clause 28 of the IEEE

802.3u specification. The DP83815 supports four different

Ethernet protocols (10 Mb/s Half Duplex, 10 Mb/s Full

Duplex, 100 Mb/s Half Duplex, and 100 Mb/s Full Duplex),

so the inclusion of Auto-Negotiation ensures that the

highest performance protocol will be selected based on the

advertised ability of the Link Partner. The Auto-Negotiation

function within the DP83815 is controlled by internal

register access. Auto-Negotiation will be set at powerup/reset, and also when a link status(up/valid) change

occurs.

3.4.2 Auto-Negotiation Register Control

When Auto-Negotiation is enabled, the DP83815 transmits

the abilities programmed into the Auto-Negotiation

Advertisement register (ANAR) via FLP Bursts. Any

combination of 10 Mb/s, 100 Mb/s, Half-Duplex, and Full

Duplex modes may be selected. The default setting of bits

[8:5] in the ANAR and bit 12 in the BMCR register are

dete rmined at pow e r -up.

The BMCR provides software with a mechanism to control

the operation of the DP83815. Bits 1 & 2 of the PHYSTS

register are only valid if Auto-Negotiation is disabled or

after Auto-Negotiation is complete. The Auto-Negotiation

protocol compares the contents of the ANLPAR and ANAR

registers and uses the results to automatically configure to

the highest performance protocol common to the local and

far-end port. The results of Auto-Negotiation may be

accessed in register C0h (PHYSTS), bit 4: AutoNegotiation Complete, bit 2: Duplex Status and bit 1:

Speed Status.

Auto-Negotiation Priority Resolution:

— (1) 100BASE-TX Full Duplex (Highest Priority)

— (2) 100BASE-TX Half Duplex

— (3) 10BASE-T Full Duplex

— (4) 10BASE-T Half Duplex (Lowest Priority)

The Basic Mode Control Register (BMCR) provides control

for enabling, disabling, and restarting the Auto-Negotiation

process. When Auto-Negotiation is disabled the Speed

Selection bit in the BCMR (bit 13) controls switching

between 10 Mb/s or 100 Mb/s operation, and the Duplex

Mode bit (bit 8) controls switching between full duplex

operation and half duplex operation. The Speed Selection

and Duplex Mode bits have no effect on the mode of

operation when the Auto-Negotiation Enable bit (bit 12) is

set.

The Basic Mode Status Register (BMSR) indicates the set

of available abilities for technology types, Auto-Negotiation

ability, and Extended Register Capability. These bits are

permanently set to indicate the full functionality of the

DP83815 (only the 100BASE-T4 bit is not set since the

DP83815 does not support that function).

The BMSR also provides st atus on:

— Whether Auto-Negotiation is complete (bit 5)

— W hether the Link Partner is advertising that a remote

fault has occurr ed (bit 4)

— Whether a valid lin k has been established (bit 2)

— Support for Management Frame Preamble suppression

(bit 6)

The Auto-Negotiation Advertisement Register (ANAR)

indicates the Auto-Negotiation abilities to be advertised by

the DP83815. All available abilities are transmitted by

default, bu t any a bilit y ca n be suppressed by writing to the

ANAR. Updating the ANAR to suppress an ability is one

way for a management agent to change (force) the

technology that is used.

The Auto-Negotiation Link Partner Ability Register

(ANLPAR) is used to receive the base link code word as

well as all next page code words during the negotiation.

Furthermore, the ANLPAR will be updated to either 0081h

or 0021h for parallel detection to either 100 Mb/s or 10

Mb/s respectively.

The Auto-Negotiation Expansion Register (ANER)

indicates additional Auto-Negotiation status. The ANER

provides status on:

— Whether a Parallel Detect Fault has occurred (bit 4)

— W hether the Link Partner supports the Next Page

function (bit 3)

— Whether the DP83815 supports the Next Page function

(bit 2). The DP83815 does support the Next Page

function.

— Whether the current page being exchanged by Auto-

Negotiation has been received (bit1)

— Whether the Link Partner supports Auto-Negotiation (bit

0)

3.4.3 Auto-Negotiation Parallel Detection

The DP83815 supports the Parallel Detection function as

defined in the IEEE 802.3u specification. Parallel Detection

requires both the 10 Mb/s and 100 Mb/s receivers to

monitor the receive signal and report link status to the

Auto-Negotiation function. Auto-Negotiation uses this

information to configure the correct technology in the event

that the Link P artner does not support Auto-Negotiation yet

is transmitting link signals that the 100BASE-TX or

10BASE-T PMAs (Physical Medium Attachments)

recognize as valid link si gnals.

If the DP83815 completes Auto-Negotiation as a result of

Parallel Detection, bits 5 and 7 within the ANLPAR register

will be updated to reflect the mode of operation present in

the Li nk Partner. Not e th a t b i ts 4 :0 o f th e A N L PAR will also

be set to 00001 based on a successful parallel detection to

indicate a valid 802.3 selector field. Software may

determine that negotiation completed via Parallel Detect ion

3.0 Functional Description

(Continued)

17 www.national.com

by reading the ANER (98h) register with bit 0, Link Partner

Auto-Negotiation Able bit, being reset to a zero, once the

Auto-Negotiation Complete bit, bit 5 of the BMSR (84h)

register is set to a one. If configured for parallel detect

mode, and any condition other than a single good link

occurs, then the parallel detect fault bit will set to a one, bit

4 of the ANER register (98h).

3.4.4 Auto-Negotiation Restart

Once Auto-Negotiation has completed, it may be restarted

at any time by setting bit 9 (Restart Auto-Negotiation) of the

BMCR to one. If the mode configured b y a successful AutoNegotiation loses a valid link, then the Auto-Negotiation

process will resume and attempt to determine the

configuration for the link. This function ensures that a valid

configuration is maintained if the cable becomes

disconnected.

A renegotiation request from any entity, such as a

management agent, will cause the DP83815 to halt any

transmit data and link pulse activity until the

break_link_timer expires (~1500 ms). Consequently, the

Link Partner will go into link fail and normal AutoNegotiation resumes. The DP83815 will resume AutoNegotiation after the break_link_timer has expired by

issuing FLP (Fast Link Puls e) bursts.

3.4.5 Enabling Auto-Negotiation via Software

It is important to note that if the DP83815 has been

initialized upon power-up as a non-auto-negotiating device

(forced technology), and it is then required that AutoNegotiation or re-Aut o-Negotiation be initiated via software ,

bit 12 (Auto-Negotiation Enable) of the Basic Mode Control

Register must first be cleared and then set for any AutoNegotiation function to take effect.

3.4.6 Auto-Negotiation Complete Time

Parallel detection and Auto-Negotiation take approximately

2-3 seconds to complete. In addi tion, Auto-Negotiation with

next page should take approximately 2-3 seconds to

complete, depending on the number of next pages sent.

Refer to Clause 28 of the IEEE 802.3u standard for a full

description of the individual timers related to AutoNegotiation.

.

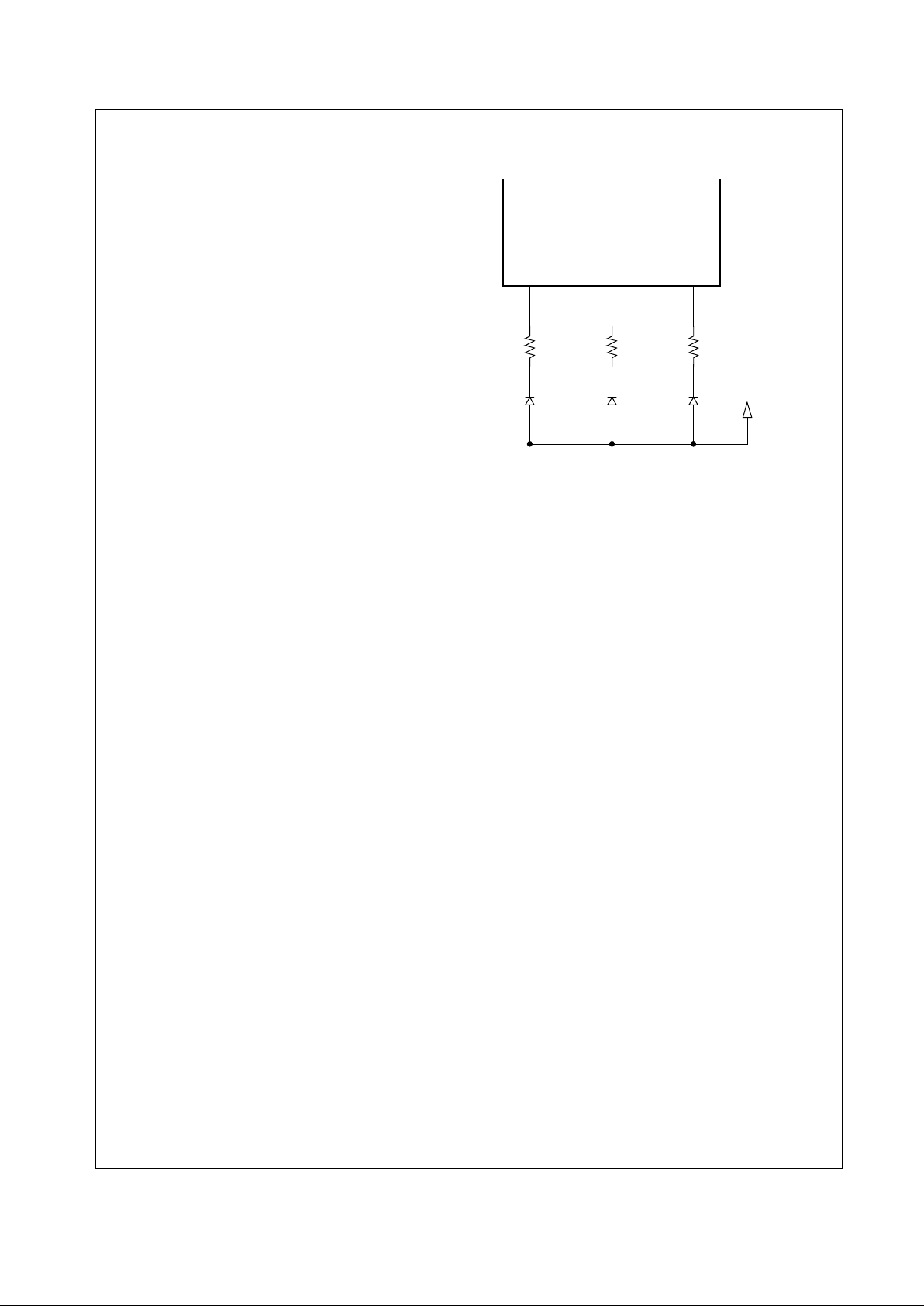

Figure 3-5 LED Loading Example

3.5 LED Interfaces

The DP83815 has parallel outputs to indicate the status of

Activity (Transmit or Receive), 100 Mb/s Link, and 10 Mb/s

Link.

The LEDACTN pin indicates the presence of transmit or

receive activity. The standard CMOS driver goes low when

RX or TX activity is detected in either 10 Mb/s or 100 Mb/s

operation.

The LED100N pin indicates a good link at 100 Mb/s data

rate. The standard CMOS driver goes low when this

occurs. In 100BASE-T mode, link is established as a result

of input receive amplitude compliant with TP-PMD

specifications which will result in internal generation of

signal detec t. This signal will a ssert af ter the int ernal Signal

Detect has remained asserted for a minimum of 500 us.

The signal will de-assert immediately following the deassertion of the internal signal detect.

The LED10N pin indic ates a good link at 10 Mb/s data rate.

The standard CMOS driver goes low when this occurs. 10

Mb/s Link is established as a result of the reception of at

least seven consecutive normal Link Pulses or the

reception of a valid 10BASE-T packet. This will cause the

assertion of this signal. the signal will de-assert in

accordance with the Link Loss Timer as specified in IEEE

802.3.

V

CC

LED10N

453

Ω

LEDACTN

453

Ω

LED100N

453

Ω

3.0 Functional Description

(Continued)

18 www.national.com

3.6 Half Duplex vs. Full Duplex

The DP83815 supports both half and full duplex operation

at both 10 Mb/s and 100 Mb/s speeds.

Half-duplex is the standard, traditional mode of operation

which relies on the CSMA/CD protocol to handle collisions

and network access. In Half-Duplex mode, CRS responds

to both transmit and receive activity in order to maintain

compliance with IEEE 802.3 specification.

Since the DP83815 is designed to support simultaneous

transmit and receive activity it is capable of supporting fullduplex switched applications with a throughput of up to 200

Mb/s per port when operating in 100BASE-TX mode.

Because the CSMA/CD protocol does not apply to fullduplex operation, the DP83815 disables its own internal

collision sensing and reporting functions.

It is imp ortant to understand that while ful l Auto-N egotiation

with the use of Fast Link Pulse code words can interpret

and configure to support full-duplex, parallel detection can

not recognize the difference between full and half-duplex

from a fixed 10 Mb/s or 100 Mb/s link partner over twisted

pair. Therefore, as specified in 802.3u, if a far-end link

partner is transmitting forced full duplex 100BASE-TX for

example, the parallel detection state machine in the

receiving station would be unable to detect the full duplex

capability of the far-end link partner and would negotiate to

a half duplex 100BASE-TX configuration (same scenario

for 10 Mb/s).

For full duplex operation, the following register bits must

also be set:

— TXCFG:CSI (Carrier Sense Ignore)

— TXCFG:HBI (HeartBeat Ignore)

— RXCFG:ATX (Accept Transmit Packets).

Additionally, the Auto-Negotiation Select bits in the

Configurat ion register must show full duplex support:

— CFG:ANEG_SEL.

3.7 P hy Loopbac k

The DP83815 includes a Phy Loopback Test mode for easy

board diagnostics. The Loopback mode i s selected through

bit 14 (Loopback) of the Basic Mode Control Register

(BMCR). Writing 1 to this bit enables transmit data to be

routed to the receive path early in the physical layer cell.

Loopback status may be check ed in bit 3 of the PHY Status

Register (C0h). While in Loopback mode the data will not

be transmitted onto the media. This is true for either 10

Mb/s as well 100 Mb/s dat a.

In 100BASE-TX Loopback mode the data is routed through

the PCS and PMA layers into the PMD sublayer before it is

looped back. Therefore, in addition to serving as a board

diagnostic , t his mode serves as quick functional verification

of the device .

Note: A Mac Loopback can be performed via setting bit 29

(Mac Loopback ) in the Tx Configuration Register .

3.8 Status Information

There are 3 pins that are available to convey status

information to the user through LEDs to indicate the speed

(10Mb/s or 100Mb/s) link status and receive or transmit

activity.

10 Mb/s Link is establi shed as a result of the reception of at

least seven consecutive Normal Link Pulses or the

reception of a valid 10BASE-T packet. LED10N will deassert in accordance with the Link Loss Timer specified in

IEEE 802.3.

100BASE-T Link is established as a result of an input

receive amplitude compliant with TP-PMD specifications

which will result in internal generation of Signal Detect.

LED100N will assert after the internal Signal Detect has

remained asserted for a minimum of 500 µs. LED100N will

de-assert immediately following the de-assertion of the

internal Signal Detect.

Activity LED status indi cates Receiv e or Transmit activity.

3.9 100BASE-TX TRANSMITTER

The 100BASE-TX transmitter consists of several functional

blocks which convert synchronous 4-bit nibble data, to a

scrambled MLT-3 125 Mb/s serial data stream. Because the

100BASE-TX TP-PMD is integrated, the differential output

pins, TD±, can be directl y routed to the magnetics.

The block diagram in Figure 4 provides an overview of

each functional block within the 100BASE-TX transmit

section.

The Transmitter section consists of the following functional

blocks :

— Code-group Encoder and I njection b lock (byp ass opt ion)

— Scrambler block (bypass option)

— NRZ to NRZI encoder block

— Binary to MLT-3 converter / Common Driver

The bypass option for the functional blocks within the

100BASE-TX transmitter provides flexibility for applications

such as 100 Mb/s repeaters where data conversion is not

always required. The DP83815 implements the 100BASETX transmit state machine diagram as specified in the

IEEE 802.3u Standard, Clause 24

3.0 Functional Description

(Continued)

19 www.national.com

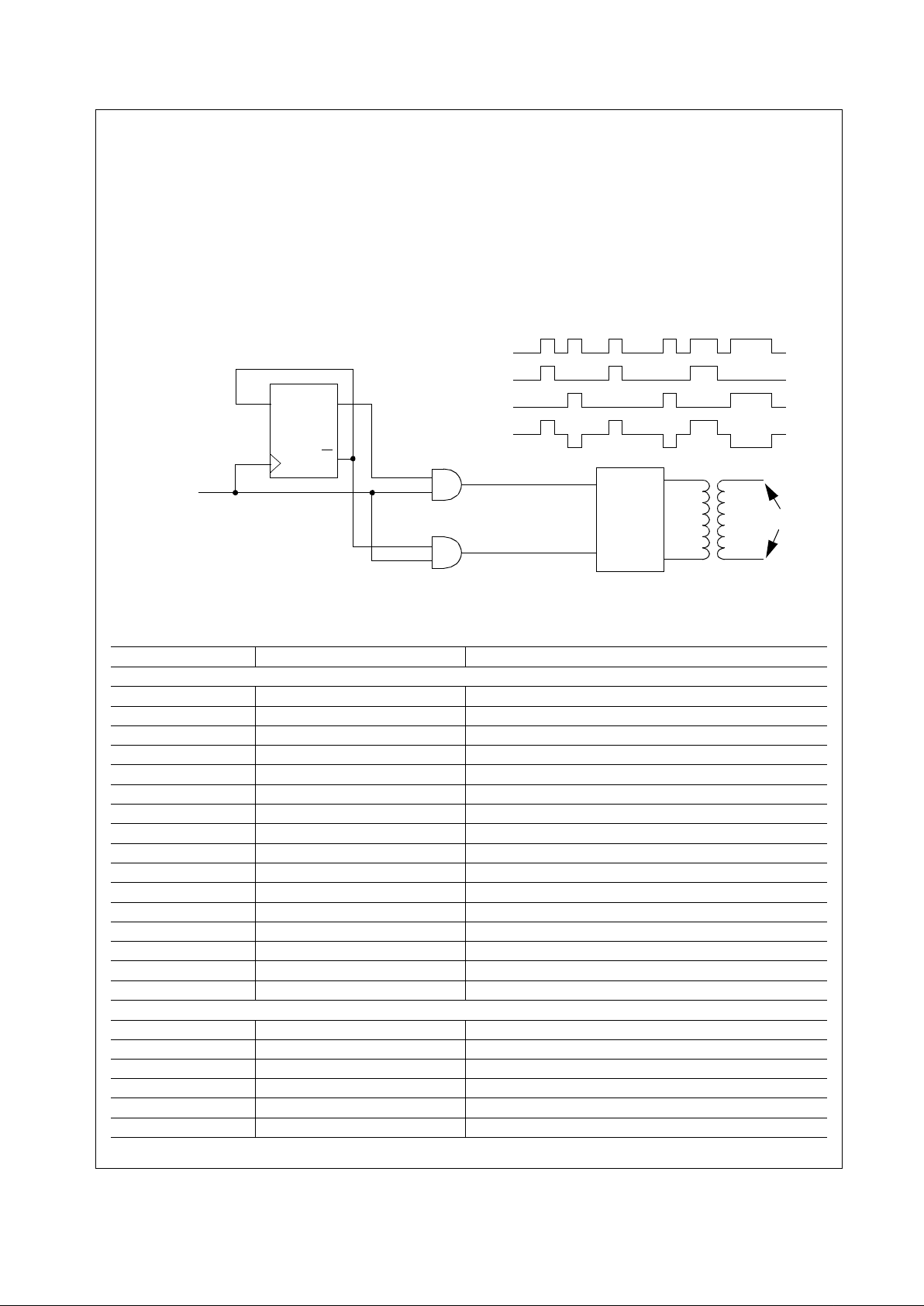

Figure 3-6 100BASE-TX Transmit Block Diagram

3.9.1 Code-group Encoding and Injection

The code-group encoder converts 4-bit (4B) nibble data

generated by the MAC into 5-bit (5B) code-groups for

transmission. This conversion is required to allow control

data to be combined with packet data code-groups. Refer

to Table 3-1 for 4B to 5B code-group mapping details.

The code-group encoder substitutes the first 8-bits of the

MAC preamble with a J/K code-group pair (11000 10001)

upon transmission. The code-group encoder continues to

replace subsequent 4B preamble and data nibbles with

corresponding 5B code-groups. At the end of the transmit

packet, upon the de-assertion of Transmit Enable signal

from the MAC, the code-group encoder injects the T/R

code-group pa ir (01 101 001 11) ind icati ng the end of fr ame .

After the T/R code-group pair, the code-group encoder

continuously injects IDLEs into the transmit data stream

until the next transmit packet is detected (re-assertion of

Transmit Enable) .

3.9.2 Scrambler

The scrambler is required to control the radiated emissions

at the media connector and on the twisted pair cable (for

100BASE-TX applications). By scrambling the data, the

total energy launched onto the cable is randomly

distributed over a wide frequency range. Without the

scrambler, energy levels at the PMD and on the cable could

peak beyond FCC limitations at frequencies related to

repeating 5B sequences (i.e., continuous transmission of

IDLEs).

The scrambler is configured as a closed loop linear

feedback shift register (LFSR) with an 11-bit polynomial.

The output of the closed loop LFSR is X-ORd with the

serial NRZ data from the code- group encoder. The result is

a scrambled data stream with sufficient randomization to

decrease radiated emissions at certain frequencies by as

much as 20 dB.

FROM CGM

BP_4B5B

BP_SCR

4B5B CODE-

MUX

5B PARALLEL

SCRAM BLER

MUX

MUX

NRZ TO NRZI

BINARY

100BASE-TX

GROUP ENABLER

TXD(3:0)/

TX_CLK

TX_ER

TO SERIAL

ENCODER

TO MLT-3/

COMMON

DRIVER

LOOPBACK

3.0 Functional Description

(Continued)

20 www.national.com

3.9.3 NRZ to NRZI Encoder

After the transmit data stream has been serialized and

scrambled, the data must be NRZI encoded in order to

comply with the TP-PMD standard for 100BASE-TX

transmission over Category-5 un-shielded twisted pair

cable. There is no ability to bypass this block within the

DP83815.

3.9.4 Binary to MLT-3 Convertor / Common Driver

The Binary to MLT-3 conversion is accomplished by

converting the serial binary data stream output from the

NRZI encoder into two binary data streams wit h alt ernately

phased logic one events. These two binary streams are

then fed to t he twi sted pair output driver which con verts the

voltage to current and alternately drives either side of the

transmit t ransf ormer prim ary winding, resul ti ng in a minim al

current (20 mA max) MLT-3 signal. Refer to Figur e3-7

.

Figure 3-7 Binary to MLT-3 conversion

D

Q

Q

binary_in

binary_plus

binary_minus

binary_in

binary_plus

binary_minus

COMMON

DRIVER

MLT-3

differential MLT-3

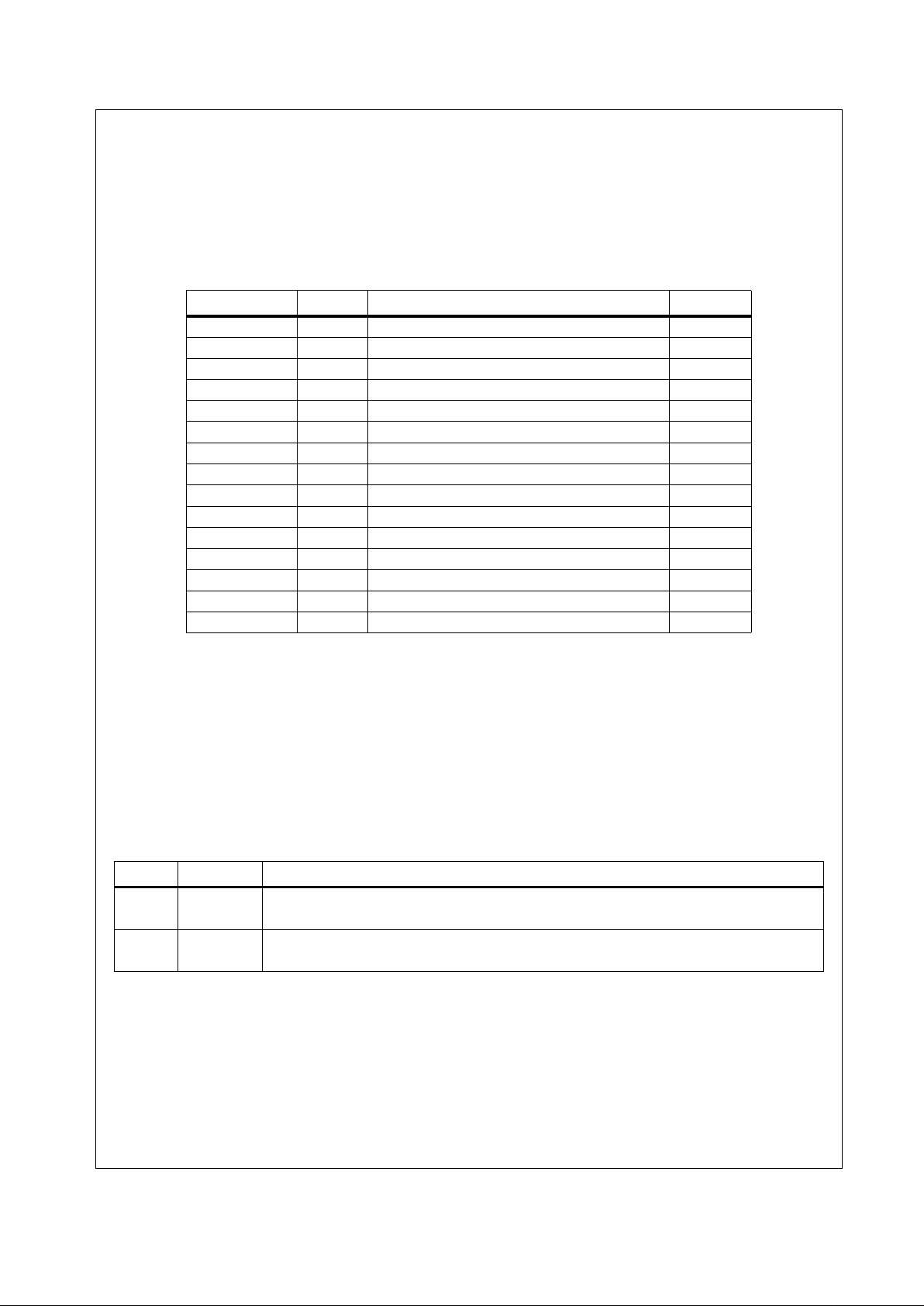

T able 3-1 4B5B Code-Group Encoding/Decoding

Name PCS 5B Code-group Description/4B Value

DATA CODES

0 11110 0000

1 01001 0001

2 10100 0010

3 10101 0011

4 01010 0100

5 01011 0101

6 01110 0110

7 01111 0111

8 10010 1000

9 10011 1001

A 10110 1010

B 10111 1011

C 11010 1100

D 11011 1101

E 11100 1110

F 11101 1111

IDLE AND CONTROL CODES

H 00100 HALT code-group - Error code

I 11111 Inter-Packet IDLE - 0000

J 11000 First Start of Packet - 0101

K 10001 Second Start of Packet - 0101

T 01101 First End of Packet - 0000

R 00111 Second End of Packet - 0000

3.0 Functional Description

(Continued)

21 www.national.com

The 100BASE-TX MLT-3 signal sourced by the TD±

common driver output pins is slew rate controlled. This

should be considered when selecting AC coupling

magnetics to ensure TP-PMD Standard compliant

transit ion times (3 ns < Tr < 5 ns).

The 100BASE-TX transmit TP-PMD function within the

DP83815 is capable of sourcing only MLT-3 encoded data.

Binary output from the TD± outputs is not possible in 100

Mb/s mode.

3.10 100B ASE-TX Receiver

The 100BASE-TX receiver consists of several functional

blocks which convert the scrambled MLT-3 125 Mb/s serial

data stream to synchronous 4-bit nibble data that is

provided to the MAC. Because the 100BASE-TX TP-PMD

is integrated, the differential input pins, RD±, can be

directly routed from the AC coup li ng m agnetics.

See Figure 3-8 for a block diagram of the 100BASE-TX

receive function. This provides an overview of each

functional block within the 100BASE-TX receiv e section.

The Receive section consists of the following functional

blocks:

—ADC

— Input and BLW Compensation

— Signal Detect

— Digital Adaptive Equalizat ion

— MLT-3 to Binary Decoder

— Clock Recovery Module

— NRZI to NRZ Decoder

— Serial to Par a lle l

— De-scrambler (bypass option)

— Code Group Alignment

— 4B/5B Decoder (bypass option)

— Link Integrity Monitor

— Bad SSD Detection

The bypass option for the functional blocks within the

100BASE-TX receiver provides flexibility for applications

such as 100 Mb/s repeaters where data conversion is not

always required.

3.10.1 Input and Base Line Wander Compensation

Unlike the DP83223V Twister, the DP83815 requires no

external attenuation circuitry at its receive inputs, RD+/−. It

accepts TP-PMD compliant waveforms directly, requiring

only a 100Ω termination plus a simple 1:1 transformer.

The DP83815 is completely ANSI TP-PMD compliant and

includes Base Line Wander (BLW) compensation. The

BLW compensation block can successfully recover the TPPMD defined “killer” pattern and pass it to the digital

adaptive equalization b lock.

BLW can generally be defined as the change in the

average DC content, over time, of an AC coupled digital

transmission over a given transmission medium. (i.e.

copper wire).

BLW results from the interaction between the low

frequency components of a transmitted bit stream and the

frequency response of the AC coupling component(s)

within the transmission system. If the low frequency

content of the digital bit stream goes below the low

frequency pole of the AC coupling transformers then the

droop characteristics of the transformers will dominate

result ing in p ot e nt ially seri ous B LW.

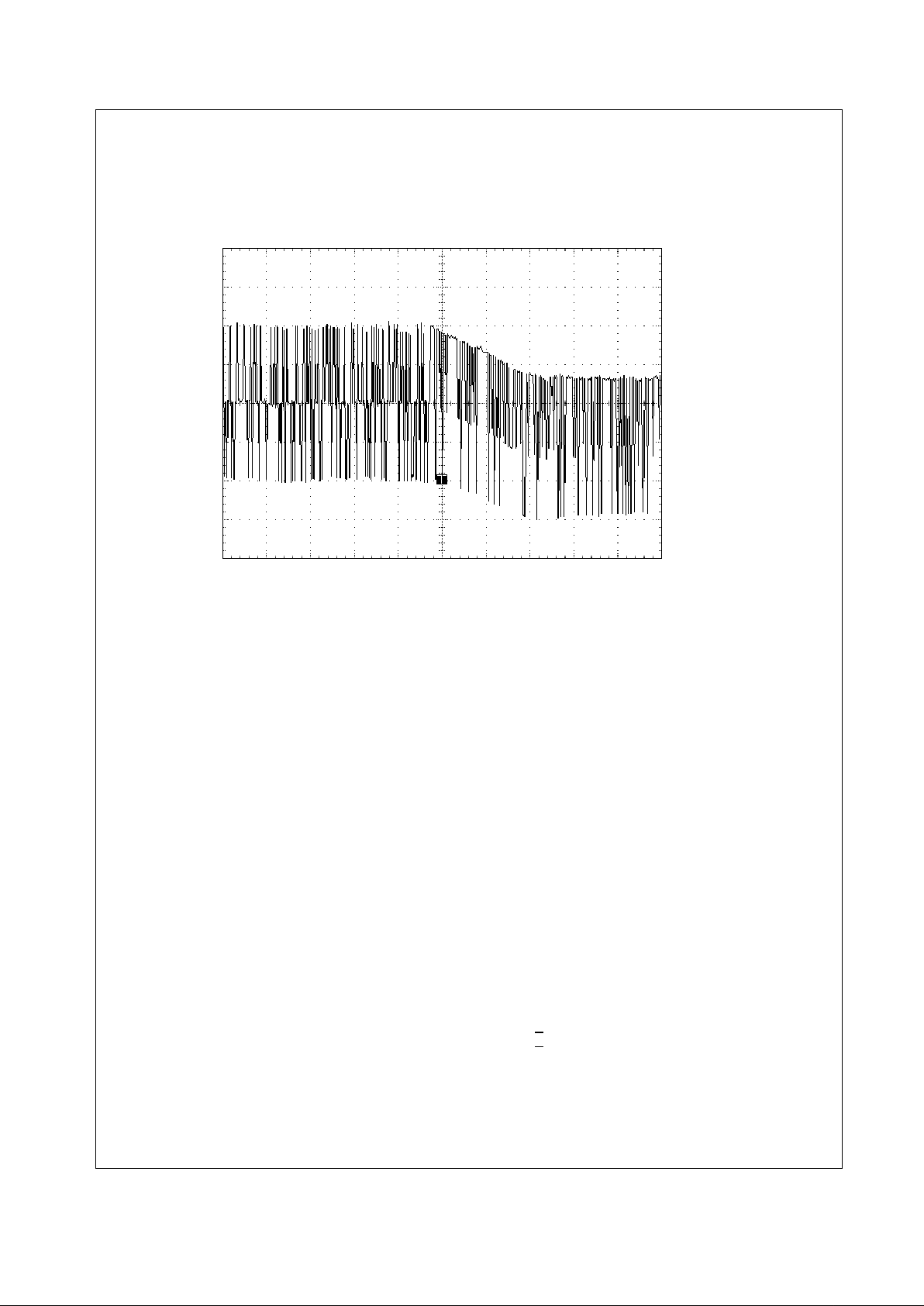

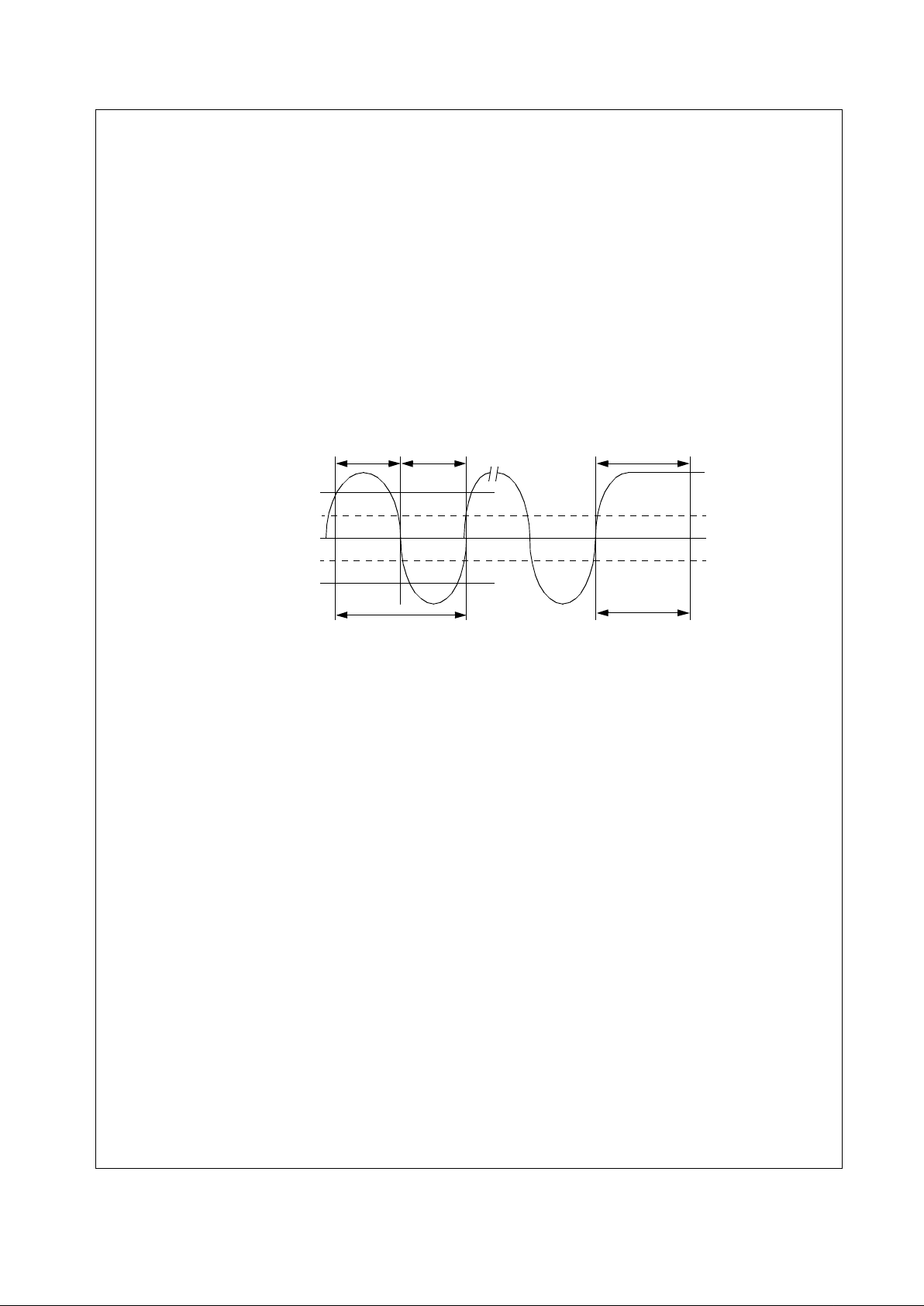

The digital oscilloscope plot provided in Figure3-9

illustrates the severity of the BLW event that can

theoretically be generated during 100BASE-TX packet

transmission. This event consists of approximately 800 mV

of DC offset for a period of 120 us. Left uncompensated,

events such as this can cause packet loss.

3.10.2 Signal Detect

The signal detect function of the DP83815 is incorporated

to meet the specifi cations mandated by the ANSI FDDI TPPMD Standard as well as the IEEE 802.3 100BASE-TX

Standard for both voltage thresholds and timing

parameters.

Note that the reception of normal 10BASE-T link pulses

and fast link pulses per IEEE 802.3u Auto-Negotiation by

the 100BASE-TX receiver do not cause the DP83815 to

assert signal detect.

3.10.3 Digital Adaptive Equalization

INVALID CODES

V 00000

V 00001

V 00010

V 00011

V 00101

V 00110

V 01000

V 01100

V 10000

V 11001

T able 3-1 4B5B Code-Group Encoding/Decoding

Name PCS 5B Code-group Description/4B Value

3.0 Functional Description

(Continued)

22 www.national.com

Figure 3-8 100 M/bs Receive Block Diagram

BP_4B5B

BP_SCR

BP_RX

CLOCK

MUX

MUX

4B/5B DECODER

SERIAL TO

CODE GROUP

MUX

DESCRAMBLER

NRZI TO NRZ

MLT-3 TO BINARY

DIGITAL

CLOCK

LINK INTEGRITY

RX_DATA VALID

AGC

INPUT BLW

ADC

SIGNAL

COMPENSATION

ADAPTIVE

EQUALIZATION

DECODER

DECODER

ALIGNMENT

RECOVERY

MODULE

PARALLEL

MONITOR

SSD DETECT

RX_CLK

SD

RXD(3:0)/RX_ER

RD +/-

DETECT

3.0 Functional Description

(Continued)

23 www.national.com

When transmitting data at high speeds over copper twisted

pair cable, frequency dependent attenuation becomes a

concern. In high-speed twisted pair signalling, the

frequency content of the t ransmitted signal can v ary greatly

during normal operation based primarily on the

randomness of the scrambled data stream. This variation in

signal attenuation caused by frequency variations must be

compensated for to ensure the i ntegrity of the transmission.

In order to ensure quality transmission when employing

MLT-3 encoding, the compensation must be able to adapt

to various cable lengths and cable types depending on the

installed environment. The selection of long cable lengths

for a given implementation, requires significant

compensation which will over-compensate for shorter, less

attenuating lengths. Conversely, the selection of short or

intermediate cable lengths requiring less compensation will

cause serious under-compensation for longer length

cables. Therefore, the compensation or equalization must

be adaptive to ensure proper conditioning of the received

signal independent of the cable length.

The DP88315 utilizes a extremely robust equalization

scheme referred to herein as ‘Digital Adaptive

Equalization’. Traditional designs use a pseudo adaptive

equalization scheme that determines the approximate

cable length by monitoring signal attenuation at certain

frequencies. This attenuation value was compared to the

internal receive input reference voltage. This comparison

would indicate the amount of equalization to use. Although

this scheme is used successfully on the DP83223V twister,

it is sensitive to transformer mismatch, resistor variation

and process induced offset. The DP83223V also required

an external a ttenuation network to help match the incoming

signal amplitude to t he internal refer ence.

The Digital Equalizer removes ISI (Inter Symbol

Interference) from the receive data stream by continuously

adapting to provide a filter with the inverse frequency

response of the channel. When used in conjunction with a

gain stage, this enables the receive 'eye pattern' to be

opened sufficiently to allow very reliable data recovery.

Traditionally 'adaptive' equalizers selected 1 of N filters in

an attempt to match the cables characteristics. This

approach will typically leave holes at certain cable lengths,

where the performance of the equalizer is not optimized.

The DP83815 equalizer is t ruly adaptive.

The curves given in Figure 3-10 illustrate attenuation at

certain frequencies for given cable lengths. This is derived

from the worst case frequency vs. attenuation figures as

specified in the EIA/TIA Bulletin TSB-36. These curves

indicate the significant variations in signal attenuation that

must be compensated for by the receive adaptive

equalization circuit.

Figure 3-11 represents a scrambled IDLE transmitted over

zero meters of cable as measured at the AII (Active Input

Interface) of the receiver. Figure3-12 and Figure3-13

represent th e signal deg radation over 50 and 100 meters of

category V

cable respectively, also measured at the AII.