TL/F/11705

DP83266 MACSI Device (FDDI Media Access Controller and System Interface)

PRELIMINARY

October 1994

DP83266 MACSITMDevice

(FDDI Media Access Controller and System Interface)

General Description

The DP83266 Media Access Controller and System Interface (MACSI) implements the ANSI X3T9.5 Standard Media

Access Control (MAC) protocol for operation in an FDDI

token ring and provides a comprehensive System Interface.

The MACSI device transmits, receives, repeats, and strips

tokens and frames. It produces and consumes optimized

data structures for efficient data transfer. Full duplex architecture with through parity allows diagnostic transmission

and self testing for error isolation and point-to-point connections.

The MACSI device includes the functionality of both the

DP83261 BMAC

TM

device and the DP83265 BSI-2TMdevice

with additional enhancements for higher performance and

reliability.

Features

Y

Over 9 kBytes of on-chip FIFO

Y

5 DMA channels (2 Output and 3 Input)

Y

12.5 MHz to 25 MHz operation

Y

Full duplex operation with through parity

Y

Supports JTAG boundary scan

Y

Real-time Void stripping indicator for bridges

Y

On-chip address bit swapping capability

Y

32-bit wide Address/Data path with byte parity

Y

Programmable transfer burst sizes of 4 or 8

32-bit words

Y

Receive frame filtering services

Y

Frame-per-Page mode controllable on each

DMA channel

Y

Demultiplexed Addresses supported on ABus

Y

New multicast address matching feature

Y

ANSI X3T9.5 MAC standard defined ring

service options

Y

Supports all FDDI Ring Scheduling Classes

(Synchronous, Asynchronous, etc.)

Y

Supports Individual, Group, Short, Long and

External Addressing

Y

Generates Beacon, Claim, and Void frames

Y

Extensive ring and station statistics gathering

Y

Extensions for MAC level bridging

Y

Enhanced SBus compatibility

Y

Interfaces to DRAMs or directly to system bus

Y

Supports frame Header/Info splitting

Y

Programmable Big or Little Endian alignment

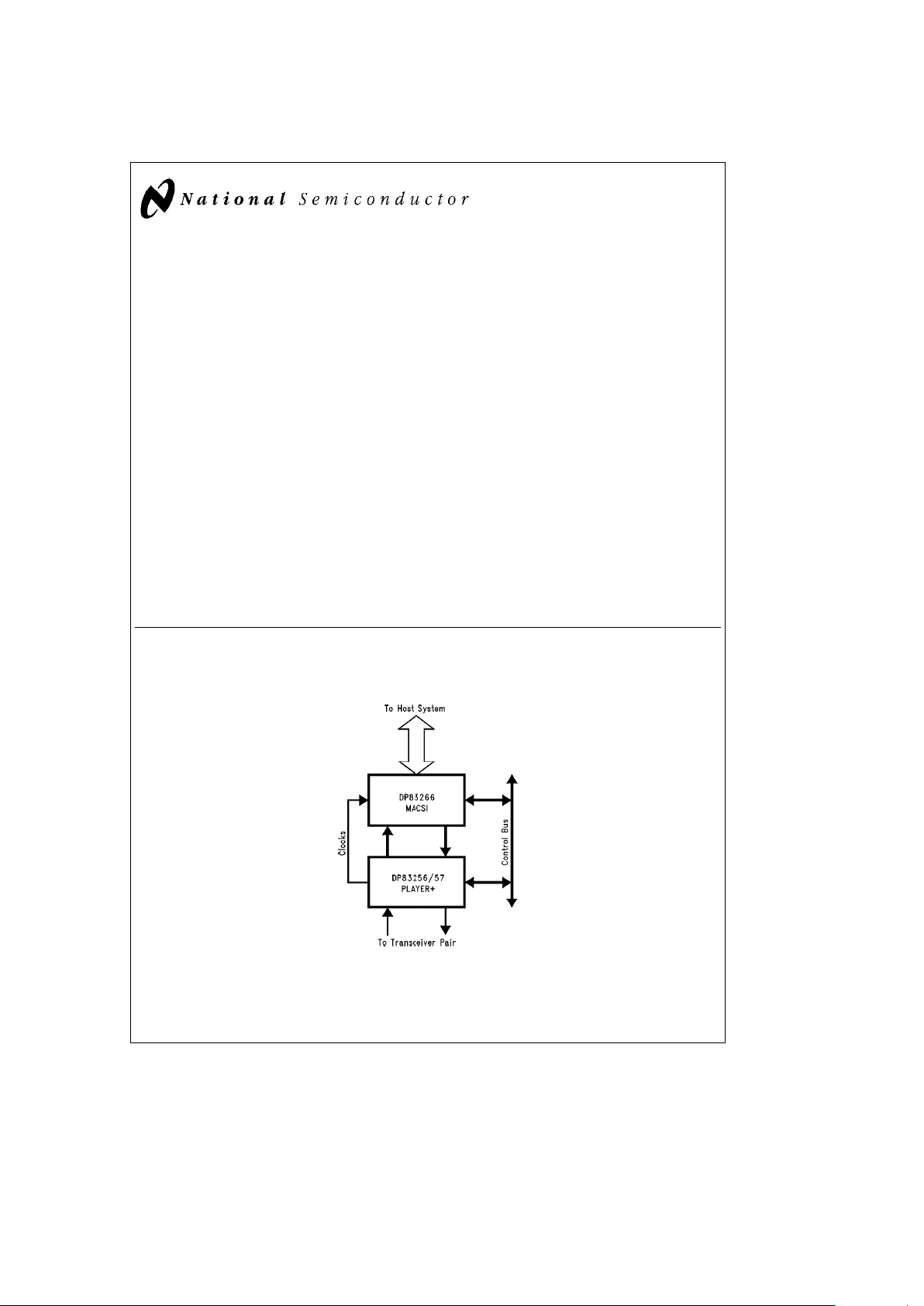

Block Diagram

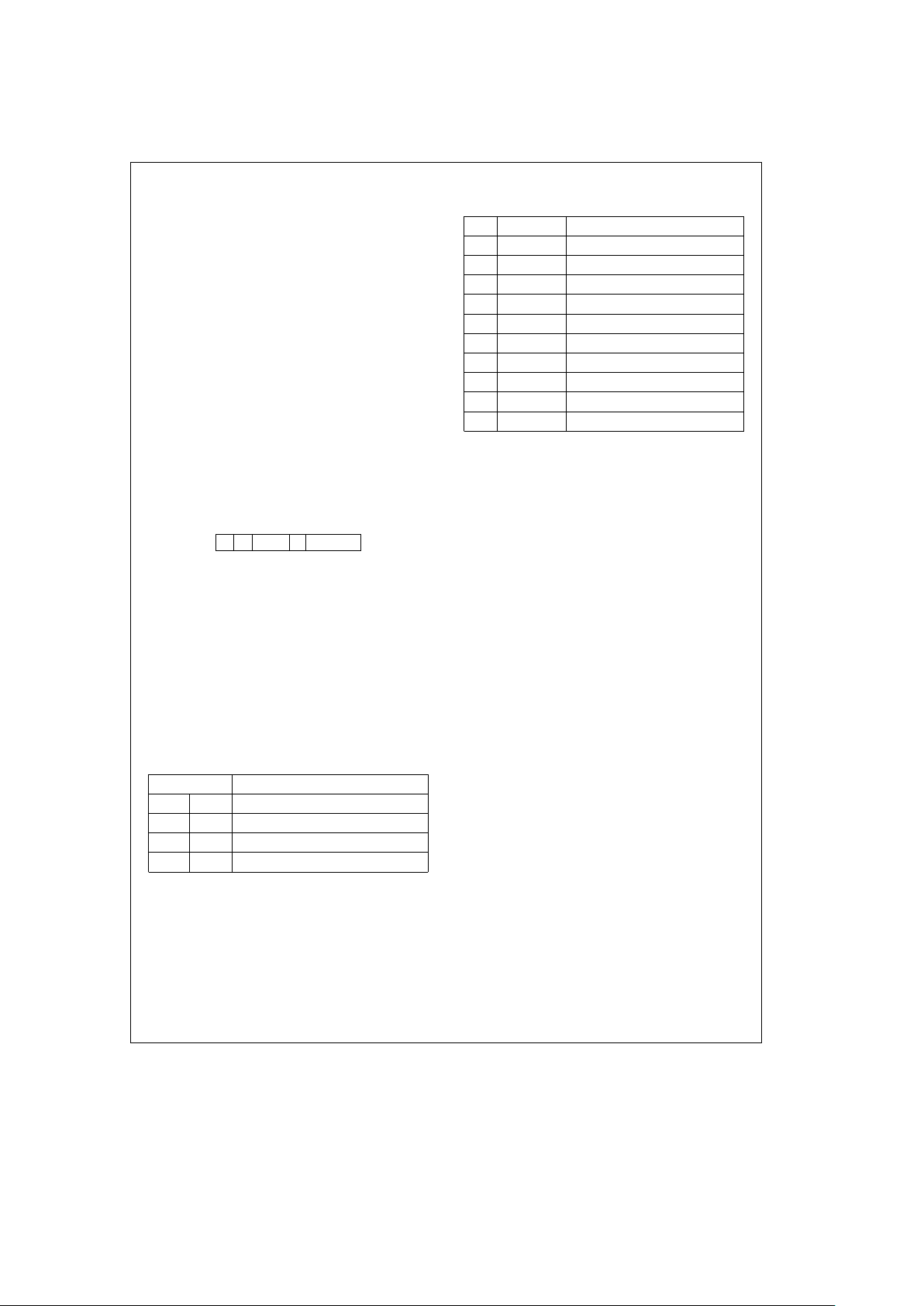

TL/F/11705– 1

FIGURE 1-1. FDDI Chip Set Block Diagram

TRI-STATEÉis a registered trademark of National Semiconductor Corporation.

BMAC

TM

, BSI-2TM, MACSITMand PLAYER

a

TM

are trademarks of National Semiconductor Corporation.

C

1995 National Semiconductor Corporation RRD-B30M105/Printed in U. S. A.

Table of Contents

1.0 FDDI CHIP SET OVERVIEW

2.0 GENERAL FEATURES

2.1 FDDI MAC Support

2.2 MAC Addressing Support

2.3 MAC Bridging Support

2.4 MAC Service Class Support

2.5 Diagnostic Counters

2.6 Management Services

2.7 Ring Parameter Tuning

2.8 Multi-Frame Streaming Interface

2.9 Beacon, Claim and Void Frames Generation

2.10 Self Testing

2.11 32-Bit Address/Data Path to Host Memory

2.12 Multi-Channel Architecture

2.13 Support for Header/Info Splitting

2.14 MAC Bridging Support

2.15 Address Bit Swapping

2.16 Status Batching Services

2.17 Receive Frame Filtering Services

2.18 Two Timing Domains

2.19 Clustered Interrupts

2.20 FIFO Memory

2.21 Frame-per-Page-per-Channel

2.22 Copy All Multicast

2.23 Bridge Stripping Information

2.24 LED Status Control Outputs

2.25 JTAG Boundary Scan

3.0 ARCHITECTURAL DESCRIPTION

3.1 Interfaces

3.2 Ring Engine

3.3 Data Structures

3.4 Service Engine

4.0 FDDI MAC FACILITIES

4.1 Symbol Set

4.2 Protocol Data Units

4.3 Frame Counts

4.4 Timers

4.5 Ring Scheduling

5.0 FUNCTIONAL DESCRIPTION (RING ENGINE)

5.1 Token Handling

5.2 Servicing Transmission Requests

5.3 Request Service Parameters

5.4 Frame Validity Processing

5.0 FUNCTIONAL DESCRIPTION (RING ENGINE)

(Continued)

5.5 Frame Status Processing

5.6 SMT Frame Processing

5.7 MAC Frame Processing

5.8 Receive Batching Support

5.9 Immediate Frame Transmission

5.10 Full Duplex Operation

5.11 Parity Processing

5.12 Handling Internal Errors

6.0 FUNCTIONAL DESCRIPTION (SERVICE ENGINE)

6.1 Overview

6.2 Operation

6.3 External Matching Interface

6.4 Bus Interface Unit

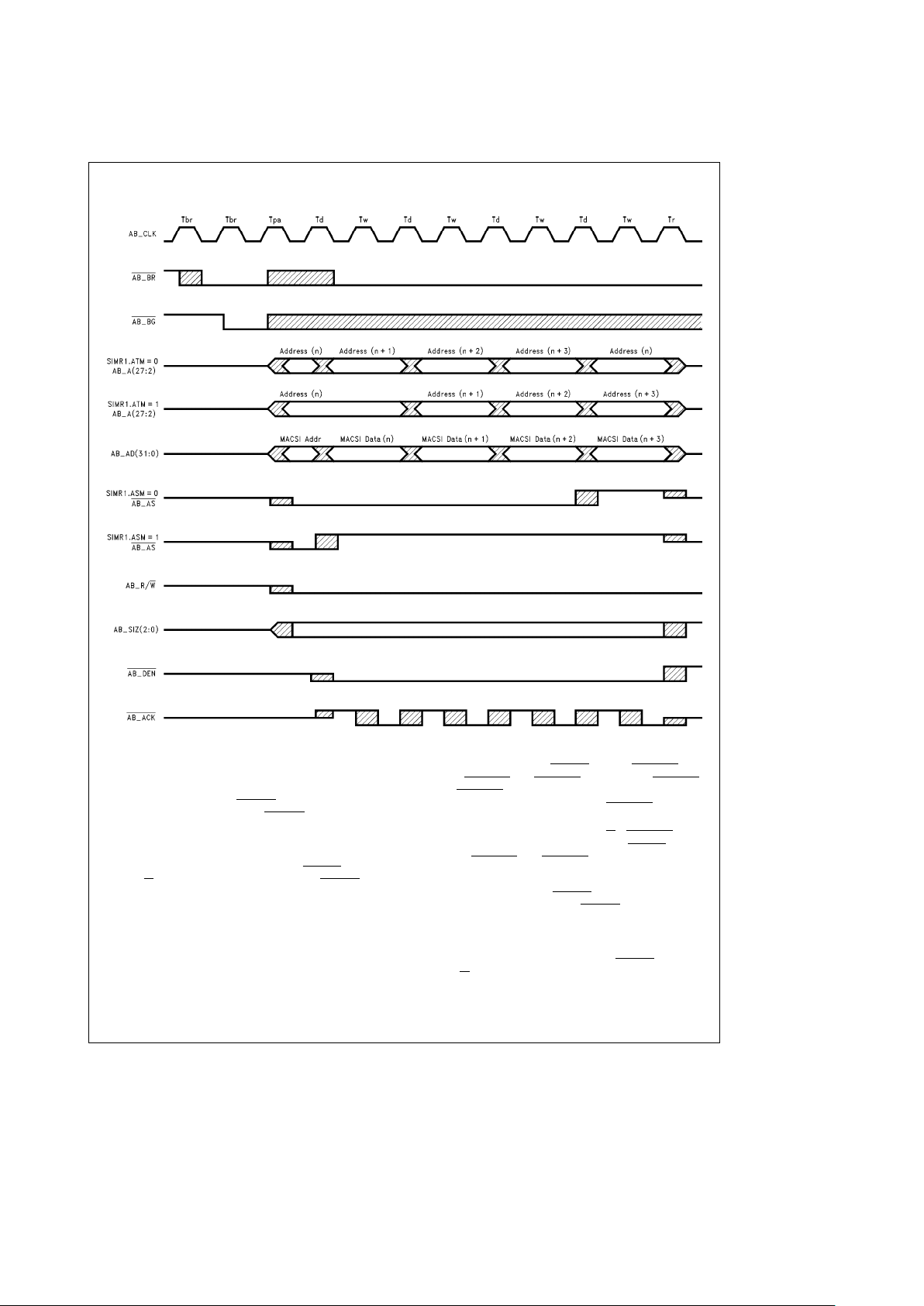

6.5 Enhanced ABUS Mode

7.0 CONTROL INFORMATION

7.1 Overview

7.2 Conventions

7.3 Access Rules

7.4 Ring Engine Operation Registers

7.5 MAC Parameters

7.6 Timer Values

7.7 Event Counters

7.8 Pointer RAM Registers

7.9 Limit RAM Registers

7.10 Descriptors

7.11 Operating Rules

7.12 Pointer RAM Register Descriptions

7.13 Limit RAM Register Descriptions

8.0 SIGNAL DESCRIPTIONS

8.1 Control Interface

8.2 PHY Interface

8.3 External Matching Interface

8.4 LED Interface

8.5 ABus Interface

8.6 Electrical Interface

9.0 ELECTRICAL CHARACTERISTICS

9.1 Absolute Maximum Ratings

9.2 Recommended Operating Conditions

9.3 DC Electrical Characteristics

9.4 AC Electrical Characteristics

10.0 PIN TABLE AND PIN DIAGRAM

2

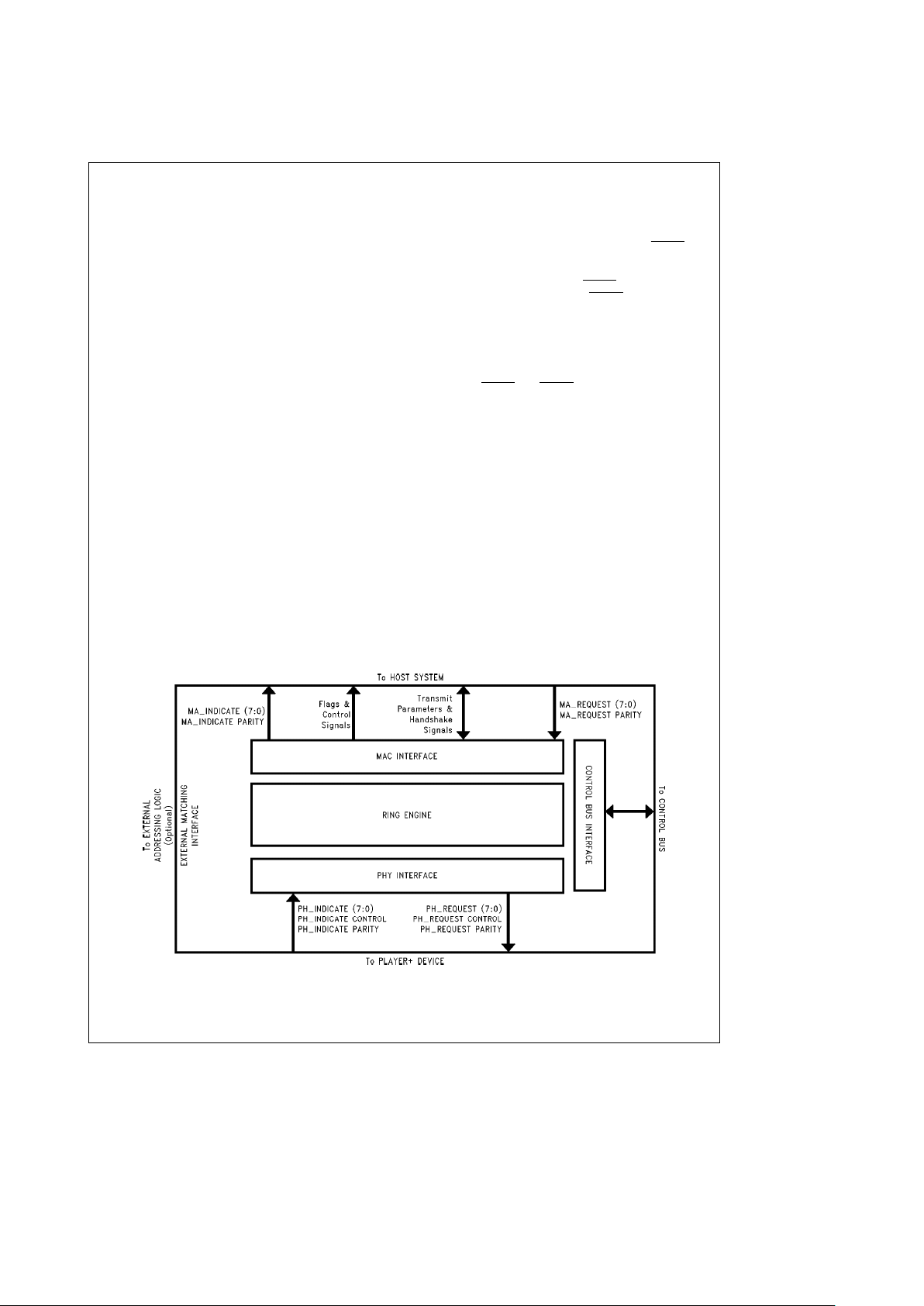

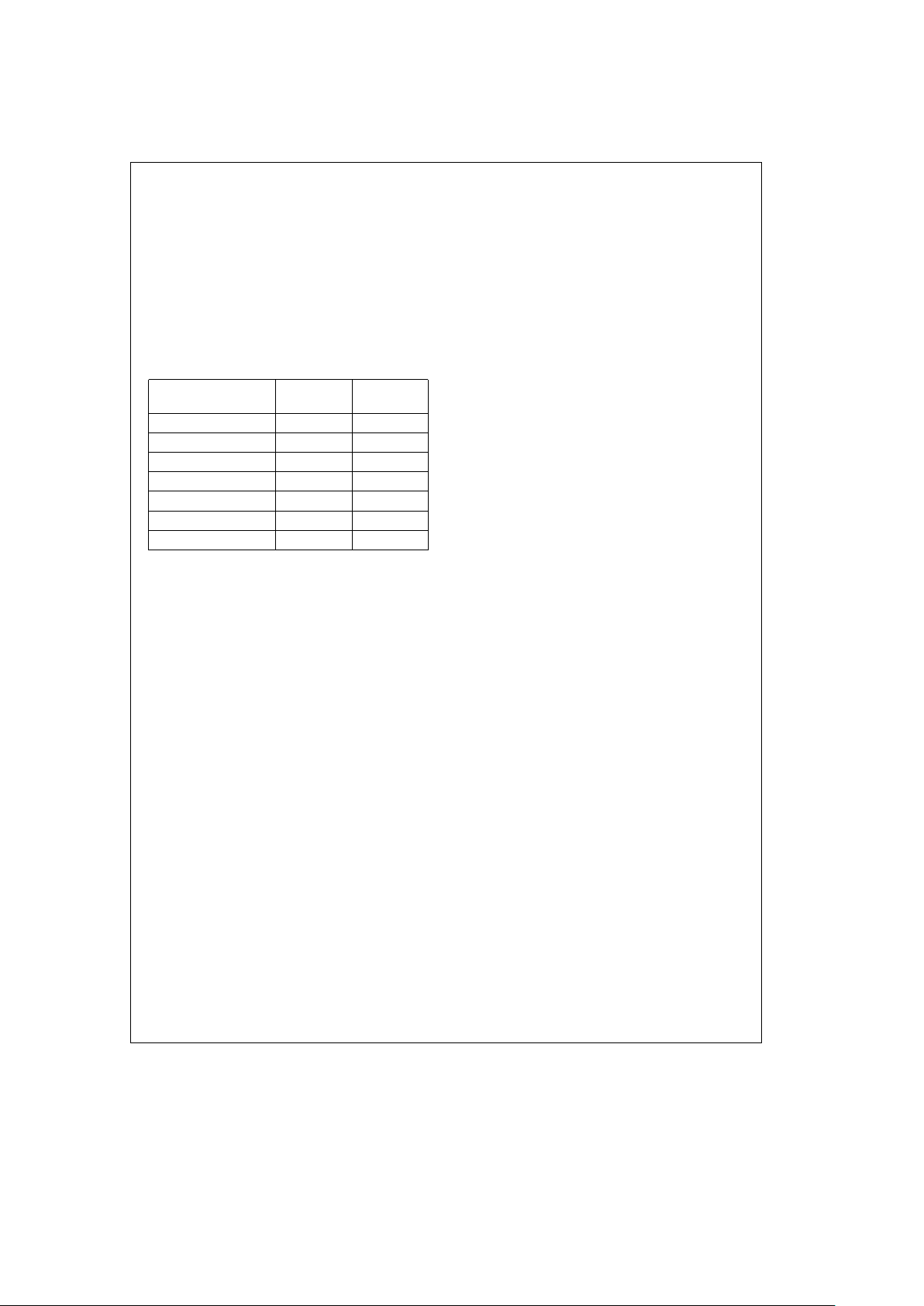

1.0 FDDI Chip Set Overview

National Semiconductor’s FDDI chip set is shown in

Figure

1-1.

For more information about the PLAYER

a

TM

device,

consult the appropriate datasheet and application notes.

DP83256/56-AP/57 PLAYER

a

Device Physical Layer Controller

The PLAYERadevice implements the Physical Layer

(PHY) protocol as defined by the ANSI FDDI PHY X3T9.5

Standard along with all the necessary clock recovery and

clock generation functions.

Features

#

Single chip FDDI Physical Layer (PHY) solution

#

Integrated Digital Clock Recovery Module provides enhanced tracking and greater lock acquisition range

#

Integrated Clock Generation Module provides all necessary clock signals for an FDDI system from an external

12.5 MHz reference

#

Alternate PMD Interface (DP83256-AP/57) Supports

UTP twisted pair FDDI PMDS with no external clock recovery or clock generations functions required

#

No External Filter Components

#

Connection Management (CMT) Support (LEM, TNE,

PCÐReact, CFÐReact, Auto Scrubbing)

#

Full on-chip configuration switch

#

Low Power CMOS-BIPOLAR design using a single 5V

supply

#

Full duplex operation with through parity

#

Separate management interface (Control Bus)

#

Selectable Parity on PHY-MAC Interface and Control Bus

Interface

#

Two levels of on-chip loopback

#

4B/5B encoder/decoder

#

Framing logic

#

Elasticity Buffer, Repeat Filter, and Smoother

#

Line state detector/generator

#

Supports single attach stations, dual attach stations and

concentrators with no external logic

#

DP83256/56-AP for SAS/DAS single path stations

#

DP83257 for SAS/DAS single/dual path stations

In addition, the DP83257 contains an additional

PHYÐData.request and PHYÐData.indicate port required

for concentrators and dual attach stations.

DP83266 MACSI Device

Media Access Controller and

System Interface

The MACSI device implements the Timed Token Media Access Control protocol defined by the ANSI FDDI X3T9.5

MAC Standard as well as a high performance system interface.

Features

#

Over 9 kBytes of on-chip FIFO

#

5 DMA channels (2 Output and 3 Input)

#

12.5 MHz to 25 MHz operation

#

Full duplex operation with through parity

#

Supports JTAG boundary scan

#

Real-time Void stripping indicator for bridges

#

On-chip address bit swapping capability

#

32-bit wide Address/Data path with byte parity

#

Programmable transfer burst sizes of 4 or 8 32-bit words

#

Receive frame filtering services

#

Frame-per-Page mode controllable on each

DMA channel

#

Demultiplexed Addresses supported on ABus

#

New multicast address matching feature

#

ANSI X3T9.5 MAC standard defined ring service options

#

Supports all FDDI Ring Scheduling Classes

(Synchronous, Asynchronous, etc.)

#

Supports Individual, Group, Short, Long and

External Addressing

#

Generates Beacon, Claim, and Void frames

#

Extensive ring and station statistics gathering

#

Extensions for MAC level bridging

#

Enhanced SBus compatibility

#

Interfaces to DRAMs or directly to system bus

#

Supports frame Header/Info splitting

#

Programmable Big or Little Endian alignment

3

2.0 General Features

The DP83266 MACSI device is a highly integrated FDDI

controller. Together with the DP83256/57 PLAYER

a

device, it forms a full-featured, high performance FDDI chip set

useful for designing end station attachments, concentrators,

bridges, routers, and other FDDI connections. The MACSI

device provides all of the features and services of both the

DP83261 BMAC device and the DP83265 BSI-2 device with

enhanced performance and reliability.

For system connection, the MACSI device provides a simple

yet powerful bus interface and memory management

scheme to maximize system efficiency and it is capable of

interfacing to a variety of host buses/environments. The

MACSI device provides a 32-bit wide data interface, which

can be configured to share a system bus to main memory or

to use external shared memory. Also provided are 28-bit

addresses multiplexed on the data pins as well as demultiplexed on dedicated pins. The system interface supports

virtual addressing using fixed-size pages.

For network connection, the MACSI device provides many

services which simplify network management and increase

system performance and reliability. The MACSI device is

capable of batching confirmation and indication status, filtering MAC frames with the same Information field as well

as Void frames, and performing network monitoring functions.

2.1 FDDI MAC SUPPORT

The MACSI device implements the ANSI X3T9.5 FDDI MAC

standard protocol for transmitting, receiving, repeating and

stripping frames. The MACSI device provides all of the information necessary to implement the service primitives defined in the standard.

2.2 MAC ADDRESSING SUPPORT

Both long (48-bit) and short (16-bit) addressing are supported simultaneously, for both Individual and Group addresses.

2.3 MAC BRIDGING SUPPORT

Several features are provided to increase performance in

bridging applications.

On the receive side, external address matching logic can be

used to examine the PHÐIndicate byte stream to decide

whether to copy a frame, how to set the control indicators

and how to increment the counters.

On the transmit side, transparency options are provided on

the Source Address, the most significant bit of the Source

Address, and the Frame Check Sequence (FCS).

In addition, support for an alternate stripping mechanism

(implemented using MyÐVoid frames) provides maximum

flexibility in the generation of frames by allowing the use of

Source Address Transparency (SAT).

2.4 MAC SERVICE CLASS SUPPORT

All FDDI MAC service classes are supported by the MACSI

device including Synchronous, Asynchronous, Restricted

Asynchronous, and Immediate service classes.

For Synchronous transmission, one or more frames are

transmitted in accordance with the station’s synchronous

bandwidth allocation.

For Asynchronous transmission, one programmable asynchronous priority threshold is supported in addition to the

threshold at the Negotiated Target Token Rotation time.

For Restricted Asynchronous transmission, support is provided to begin, continue and end restricted dialogues.

For Immediate transmissions, support is provided to send

frames from either the Data, Beacon or Claim states and

either ignore or respond to the received byte stream. After

an immediate transmission a token may optionally be issued.

2.5 DIAGNOSTIC COUNTERS

The MACSI device includes a number of diagnostic counters and timers that monitor ring and station performance.

These counters allow measurement of the following:

#

Number of frames transmitted and received by the

station

#

Number of frames copied as well as frames not copied

#

Frame error rate of an incoming physical connection to

the MAC

#

Load on the ring based on the number of tokens received and the ring latency

#

Ring latency

#

Lost frames

The size of these counters has been selected to keep the

frequency of overflow small, even under worst case operating conditions.

2.6 MANAGEMENT SERVICES

The MACSI device provides management services to the

Host System via the Control Bus Interface. This interface

allows access to internal registers to control and configure

the MACSI device.

2.7 RING PARAMETER TUNING

The MACSI device includes settable parameters to allow

tuning of the network to increase performance over a large

range of network sizes.

The MACSI device supports systems of two stations with

little cable between them to ring configurations much larger

than the 1000 physical attachments and/or 200 kilometer

distance that are specified as the default values in the standard.

The MACSI device also handles frames larger than the

4500 byte default maximum frame size as specified in the

standard.

2.8 MULTI-FRAME STREAMING INTERFACE

The MACSI device provides an interface to support multiframe streaming. Multiple frames can be transmitted after a

token is captured within the limits of the token timer thresholds.

2.9 BEACON, CLAIM, AND VOID FRAMES GENERATION

For purposes of transient token and ring recovery, no processor intervention is required. The MACSI device automatically generates the appropriate MAC frames.

2.10 SELF TESTING

Since the MACSI device has a full duplex architecture, loopback testing is possible before entering the ring and during

normal ring operation.

There are several possible loopback paths:

#

Internal to the MACSI device

#

Through the PLAYERadevice(s) using the PLAYER

a

configuration switch

#

Through the PLAYERaClock Recovery Module.

4

2.0 General Features (Continued)

These paths allow error isolation at the device level.

The MACSI device also supports through parity. Even when

parity is not used by the system, parity support can be provided across the PHY Interface.

2.11 32-BIT ADDRESS/DATA PATH TO HOST MEMORY

The MACSI device provides a 32-bit wide synchronous data

interface, which permits connection to a standard multimaster system bus operating from 12.5 MHz to 33 MHz, or

to local memory, using Big or Little Endian byte ordering.

Demultiplexed addresses are provided on dedicated pins.

Address information is also multiplexed on the data pins to

provide backward compatibility for designs based on the

BSI device. The local memory may be static or dynamic. For

maximum performance, the MACSI device uses burst mode

transfers, with four or eight 32-bit words to a burst. To assist

the user with the burst transfer capability, the three bits of

the address which cycle during a burst are output as demultiplexed signals. Maximum burst speed is one 32-bit word

per clock, but slower speeds may be accommodated by inserting wait states.

The MACSI device can operate within any combination of

cached, non-cached, paged or non-paged memory environments. To provide this capability, all data structures are contained within a page boundary, and bus transactions never

cross page boundaries. The MACSI device performs all bus

transactions within aligned blocks to ease the interface to a

cached environment.

2.12 MULTI-CHANNEL ARCHITECTURE

The MACSI device provides three Input Channels and two

Output Channels, which are designed to operate independently and concurrently. They are separately configured by

the user to manage the reception or transmission of a particular kind of frame (for example, synchronous frames

only).

2.13 SUPPORT FOR HEADER/INFO SPLITTING

In order to support high performance protocol processing,

the MACSI device can be programmed to split the header

and information portions of (non-MAC/SMT) frames between two Indicate Channels. Frame bytes from the Frame

Control field (FC) up to the user-defined header length are

copied onto Indicate Channel 1, and the remaining bytes

(Info) are copied onto Indicate Channel 2. This is useful for

separating protocol headers from data and allows them to

be stored in different regions of memory to prevent unnecessary copying. In addition, a protocol monitor application

may decide to copy only the header portion of each frame.

2.14 MAC BRIDGING SUPPORT

Support for bridging and monitoring applications is provided

by the Internal/External Sorting Mode. All frames matching

the external address (frames requiring bridging) are sorted

onto Indicate Channel 2, MAC and SMT frames matching

the internal (Ring Engine) address are sorted onto Indicate

Channel 0, and all other frames matching the device’s internal address (short or long) are sorted onto Indicate

Channel 1.

2.15 ADDRESS BIT SWAPPING

The MACSI contains the necessary logic for swapping the

address fields within each frame between FDDI and IEEE

Canonical bit order. This involves a bit reversal within each

byte of the address field (e.g., 08-00-17-C2-A1-03 would be-

come 10:00:E8:43:85:C0). This option is selectable on a per

channel basis and is supported on all transmit and receive

channels. This is useful for bridging FDDI to Ethernet or for

swapping addresses for higher level protocols.

2.16 STATUS BATCHING SERVICES

The MACSI device provides status for transmitted and received frames. Interrupts to the host are generated only at

status breakpoints, which are defined by the user on a per

DMA Channel basis. Breakpoints are selected when the

Channel is configured for operation. To allow batching, the

MACSI provides a status option called Tend, that causes

the device to generate a single Confirmation Message Descriptor (CNF) for one or more Request Descriptors (REQs).

The MACSI device further reduces host processing time by

separating received frame status from the received data.

This allows the CPU to scan quickly for errors when deciding whether further processing should be done on received

frames. If status was embedded in the data stream, all data

would need to be read contiguously to find the Status Indicator.

2.17 RECEIVE FRAME FILTERING SERVICES

To increase performance and reliability, the MACSI device

can be programmed to filter out identical MAC (same FC

and Info field) or SMT frames received from the ring. Void

frames are filtered out automatically. Filtering unnecessary

frames reduces the fill rate of the Indicate FIFO, reduces

CPU frame processing time, and reduces memory bus

transactions.

2.18 TWO TIMING DOMAINS

To provide maximum performance and system flexibility, the

MACSI device uses two independent clocks, one for the

MAC (ring) Interface, and one for the system/memory bus.

The MACSI device provides a fully synchronized interface

between these two timing domains.

2.19 CLUSTERED INTERRUPTS

The MACSI device can be operated in a polled or interruptdriven environment. The MACSI device provides the ability

to generate attentions (interrupts) at group boundaries.

Some boundaries are pre-defined in hardware; others are

defined by the user when the Channel is configured. This

interrupt scheme significantly reduces the number of interrupts to the host, thus reducing host processing overhead.

2.20 FIFO MEMORY

The MACSI device contains over 9 kBytes of on-chip FIFO

memory. This memory includes separate 4.6 kByte FIFOs

for both the Transmit (Request) and Receive (Indicate) data

paths. These data FIFOs allow the MACSI device to support

over 370 ms of bus latency for both transmit and receive.

They also allow the MACSI device to buffer entire maximum

length FDDI frames on-chip for both transmit and receive

simultaneously. This allows lower cost systems by enabling

the MACSI device to reside directly on system buses with

high latency requirements.

These FIFOs support all of the features available in the original BSI device including two transmit and three receive

channels to make efficient use of the FIFO resources. New

transmit thresholds are available to allow full use of the larger transmit FIFO.

5

2.0 General Features (Continued)

In addition to the 4.6 kByte data FIFOs, both the transmit

and receive data paths contain Burst FIFO Blocks, each of

which are organized as two banks of eight 32-bit words.

2.21 FRAME-PER-PAGE-PER-CHANNEL

The MACSI device has a feature which allows control of the

Frame-per-Page mode (available on the BSI device) on a

per-Channel basis. For example, this is useful in systems

where Frame-per-Page mode is used to speed up memory

space reclamation on an LLC channel, but where packing

multiple frames into each page is desired to save space on

the SMT channel.

2.22 COPY ALL MULTICAST

The MACSI provides a copy mode which allows all frames

which are addressed with multicast addresses to be copied.

Multicast addresses are those that have the Individual/

Group address bit (most significant bit of the FDDI address)

set. This simple scheme allows flexibility in the use of multicast addresses. The MACSI device copies all multicast

frames and software makes the final determination as to

which multicast groups this station belongs.

2.23 BRIDGE STRIPPING INFORMATION

The MACSI device provides an output designed to make it

easier to build transparent bridges. Source Address Transparency features are provided as well as features to allow

these frames to be stripped from the ring. For transparent

bridges, it is important to know when the MACSI is using this

stripping feature to remove frames from the ring which were

forwarded by this bridge but with an unknown source address, (i.e., Source Address Transparency enabled). This is

important because the bridge does not want to ‘‘learn’’

these addresses. This feature is provided by the MACSI in

the form of an output pin indicating which frames contain

addresses which should be added to the address filter table

(i.e. learned).

2.24 LED STATUS CONTROL OUTPUTS

The MACSI device (revision D and later) provides two outputs that give Transmit and Receive status information useful for controlling LEDs. The MACSI asserts the TXLED

pin

each time that it detects that the Request State machine

has entered the ‘‘sending’’ state, (once per transmitted

frame). Note that it will not assert TXLED

for internally gen-

erated MAC frames. It asserts the RXLED

pin each time it

detects the End Delimiter of a copied frame (VCOPY and

EDRCVD). Both of these pins use Open Drain output structures (this preserves pin compatibility with MACSI devices

prior to revision D). Therefore, they require pull-up resistors

when used for LED control information. To increase the LED

on-time for visibility, the User must supply one-shot circuits

triggered by TXLED

and RXLED.

2.25 JTAG BOUNDARY SCAN

The MACSI device supports the JTAG boundary scan standard (IEEE Std. 1149.1–1990).

3.0 Architectural Description

The MACSI is derived from the BMAC and BSI devices. The

MACSI is composed of the Ring Engine, the Service Engine,

and the Bus Interface Unit. The Ring Engine performs the

FDDI MAC Timed token protocol and contains the MAC

transmitter and receiver. The Service Engine implements

the Request and Indicate Data Services and contains the

Transmit and Receive Data FIFOs. The Bus Interface Unit

implements the high speed synchronous bus handshake

and contains the Burst FIFOs.

The MACSI device uses a full duplex architecture and provides sufficient bandwidth at the ABus for full duplex transmission with support for through parity.

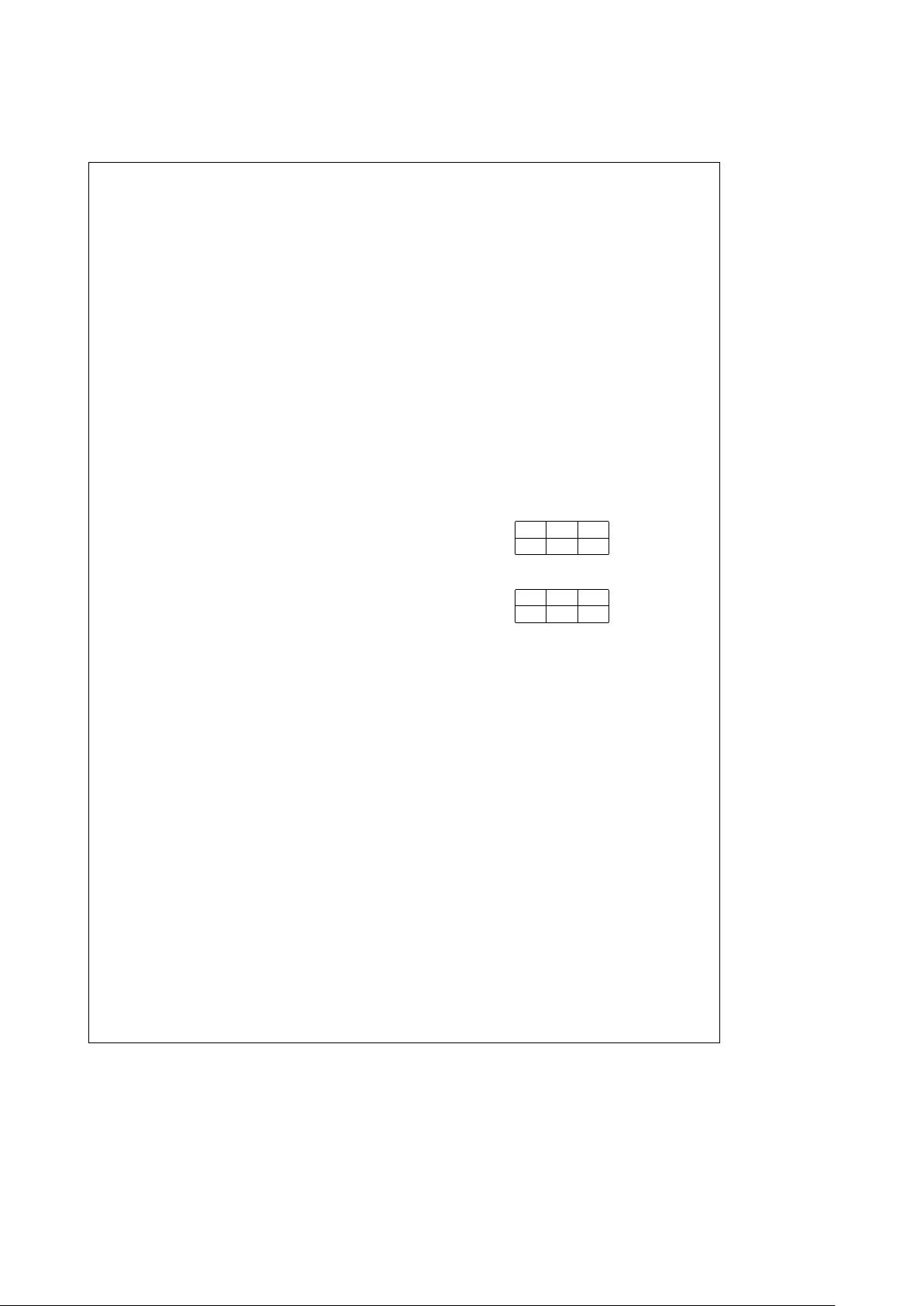

Figure 3-1

shows

the MACSI device architecture.

TL/F/11705– 2

FIGURE 3-1. MACSI Device Block Diagram

6

3.0 Architectural Description (Continued)

3.1 INTERFACES

3.1.1 PHY Interface

The PHY Interface is a synchronous interface that provides

a byte stream to the PLAYER

a

device (the PHY Request

byte stream, PHYÐRequest), and receives a byte stream

from the PLAYER

a

device (the PHY Indicate byte stream,

PHYÐIndicate).

The 10 bits transferred in both directions across the

PHÐIndicate and PHÐRequest Interfaces consists of one

parity bit (odd parity), one control bit, and 8 bits of data. The

control bit determines if the 8 data bits are a data symbol

pair or a control symbol pair.

3.1.2 ABus Interface

The ABus interface provides the high performance synchronous Data and Control interface to the Host System and/or

local memory. Data and Descriptors are transferred via this

interface over the 32-bit Data bus (with byte parity). Both

multiplexed and non-multiplexed address information is

available on this bus. Arbitration and transfer control signals

are provided and minimize the requirements for external

glue logic.

3.1.3 Control Bus Interface

The Control Interface implements the interface to the Control Bus which allows the user to initialize, monitor and diagnose the operation of the MACSI. The Control Interface is

an 8-bit interface. This reduces the pinout and minimizes

board space. All information that must be synchronized with

the data stream crosses the ABus Interface.

The Control Bus is separated completely from the high performance data path in order to allow independent operation

of the processor on the Control Bus. The Control Interface

provides synchronization between the asynchronous Control Bus and the synchronous operation of the device.

During operation, the host uses the Control Bus to access

the device’s internal registers, and to manage the attention/

notify (interrupt) logic.

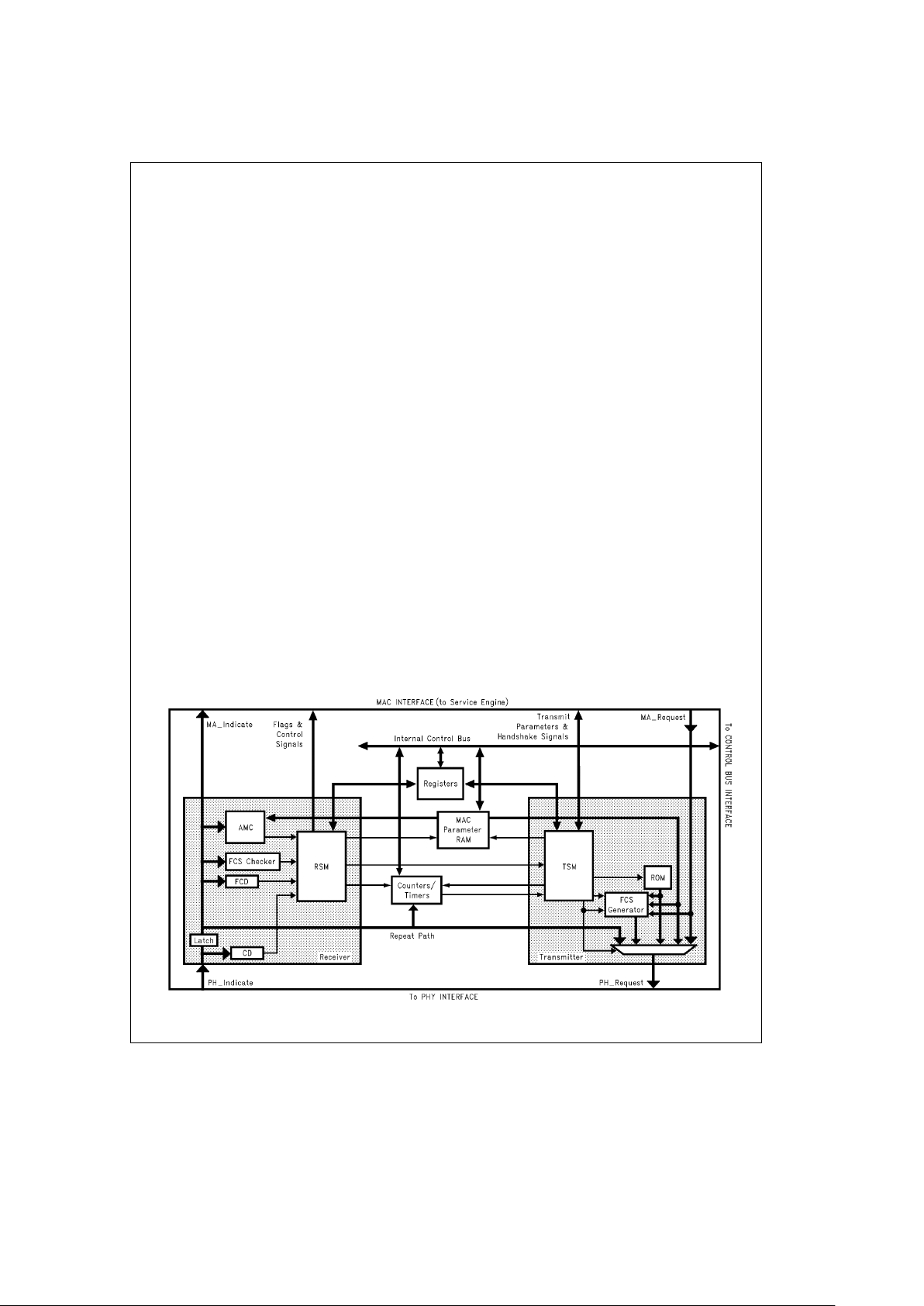

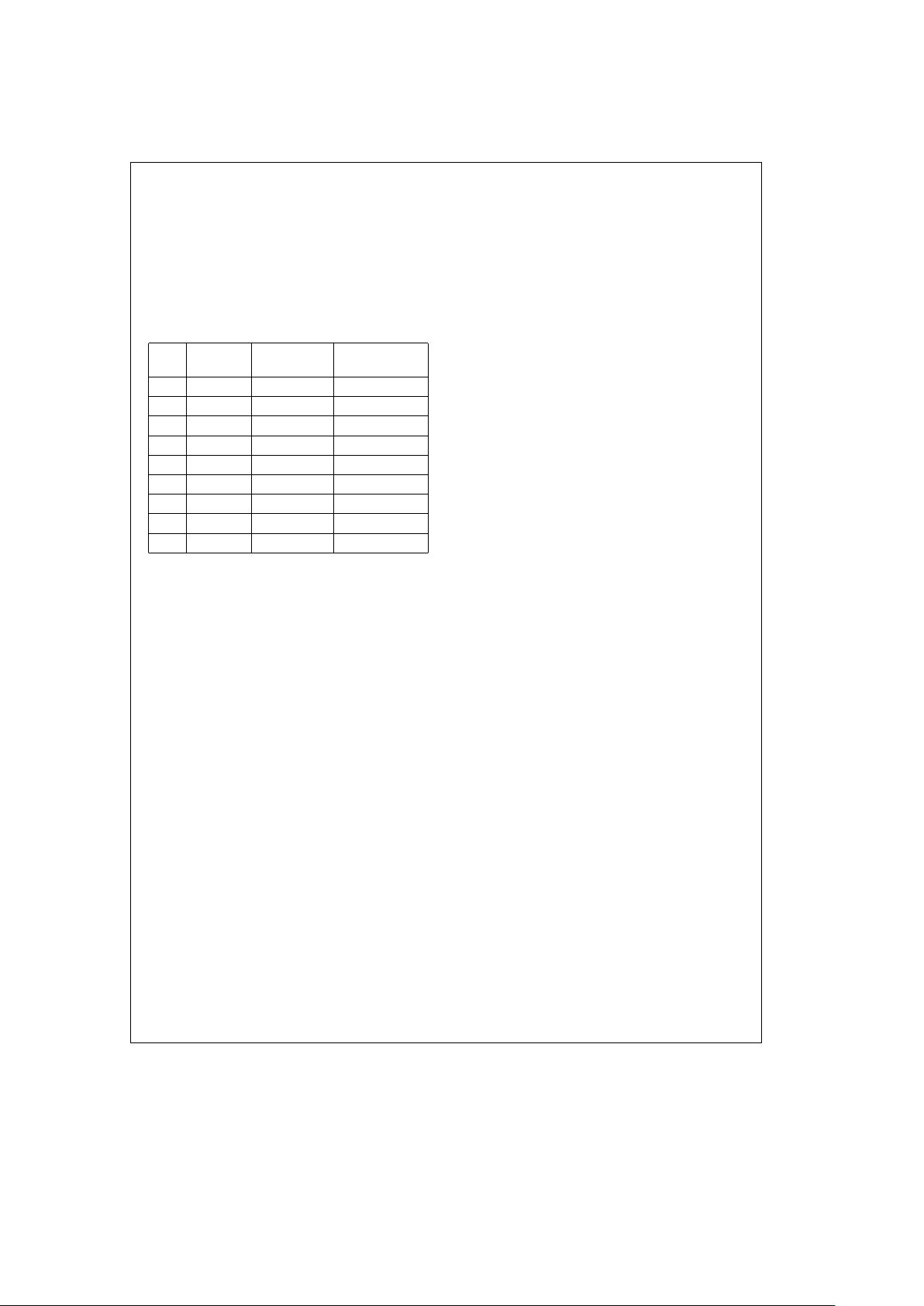

3.2 RING ENGINE

The Ring Engine consists of four blocks: Receiver, Transmitter, MAC Parameter RAM, and Counters/Timers as

shown in

Figure 3-2.

3.2.1 Receiver

The Receiver accepts data from the PHY level device in

byte stream format (PHÐIndicate).

Upon receiving the data, the Receiver performs the following functions:

#

Determines the beginning and ending of a Protocol Data

Unit (PDU)

#

Decodes the Frame Control field to determine the PDU

type (frame or token)

#

Compares the received Destination and Source Addresses with the internal addresses

#

Processes data within the frame

#

Calculates and checks the Frame Check Sequence at

the end of the frame

#

Checks the Frame Status field

And finally, the Receiver presents the data to the MAC Interface along with the appropriate control signals

(MAÐIndicate).

3.2.2 Transmitter

The Transmitter inserts frames from this station into the ring

in accordance with the FDDI Timed-Token MAC protocol. It

also repeats frames from other stations in the ring. The

Transmitter block multiplexes data from the MAÐRequest

Interface and data from the Receiver Block. During frame

transmission, data from the Request Interface is selected.

During frame repeating, data from the Receiver is selected.

TL/F/11705– 3

FIGURE 3-2. Ring Engine Block Diagram

7

3.0 Architectural Description (Continued)

During frame transmission, the Transmitter performs the following functions:

#

Captures a token to gain the right to transmit

#

Transmits one or more frames

#

Generates the Frame Check Sequence and appends it at

the end of the frame

#

Generates the Frame Status field that is transmitted at

the end of the frame

#

Issues the token at the end of frame transmission

During frame repeating, the Transmitter performs the following functions:

#

Repeats the received frame and modifies the Frame

Status field at the end of the frame as specified by the

standard

Whether transmitting or repeating frames, the Transmitter

also performs the following functions:

#

Strips the frame(s) that are transmitted by this station

#

Generates Idle symbols between frames

Data is presented from the Transmitter to the PLAYER

a

device in byte stream format (PHÐRequest).

3.2.3 MAC Parameter RAM

The MAC Parameter RAM is a dual port RAM that contains

MAC parameters such as the station’s short and long addresses. These parameters are initialized via the Control

Interface. Both the Receiver and Transmitter Blocks access

the RAM.

The Receiver uses these parameters to compare addresses

in incoming frames with the individual and group addresses

stored in the Parameter RAM.

The Transmitter uses the Parameter RAM for generating the

Source Address for all frames (except when Source Address Transparency is enabled) and for the Destination Address and Information fields on Claim and Beacon frames.

3.2.4 Counters/Timers

The Counter/Timer Block maintains all of the counters and

timers required by the ANSI X3T9.5 MAC standard.

Events which occur too rapidly for software to count, such

as the various Frame Counts, are included in the Event

Counters. The size of the wrap around counters has been

chosen to require minimal software intervention even under

marginal operating conditions. Most of the counters increment in response to events detected by the Receiver. The

counters are readable via the Control Interface.

The Token Rotation and Token Holding Timers which are

used to implement the Timed Token Protocol are contained

within the Timer Block.

3.3 DATA STRUCTURES

3.3.1 Data Types

The architecture of the MACSI device defines two basic

types of objects: Data Units and Descriptors. A Data Unit is

a group of contiguous bytes which forms all or part of a

frame. A Descriptor is a two-word (64-bit) control object that

provides addressing information and control/status information about MACSI device operations.

Data and Descriptor objects may consist of one or more

parts, where each part is contiguous and wholly contained

within a memory page. Descriptor pages are selectable as

all 1 kBytes or all 4 kBytes. Data Units are described by

Descriptors with a pointer and a count. A single Data Unit

may not cross a 4k boundary. All Descriptors may be

marked as First, Middle, Last, or Only. Thus, multiple Descriptors may be combined to describe a single entity (i.e.

one frame). A single-part object consists of one Only Part; a

multiple-part object consists of one First Part, zero or more

Middle Parts, and one Last Part. In Descriptor names, the

object part is denoted in a suffix, preceded by a dot. Thus

an Input Data Unit Descriptor (IDUD), which describes the

last Data Unit of a frame received from the ring, is called an

IDUD.Last.

A Data Unit is stored in contiguous locations within a single

4 kByte page in memory. Multiple-part Data Units are stored

in separate, and not necessarily contiguous 4 kByte pages.

Descriptors are stored in contiguous locations in Queues

and Lists, where each Queue occupies a single 1 kByte or

4 kByte memory page, aligned on the queue-size boundary.

For Queues, an access to the next location after the end of

a page will automatically wrap-around and access the first

location in the page.

Data Units are transferred between the MACSI’s Service

Engine and Ring Engine via five simplex Channels, three

used for Indicate (receive) data and two for Request (transmit) data. Parts of frames received from the ring and copied

to memory are called Input Data Units (IDUs); parts of

frames read from memory to be transmitted to the ring are

called Output Data Units (ODUs).

Descriptors are transferred between the MACSI device and

Host via the ABus, whose operation is for the most part

transparent to the user. There are five Descriptor types recognized by the MACSI device: Input Data Unit Descriptors

(IDUDs), Output Data Unit Descriptors (ODUDs), Pool

Space Descriptors (PSPs), Request Descriptors (REQs),

and Confirmation Message Descriptors (CNFs).

Input and Output Data Unit Descriptors describe a single

Data Unit part, i.e., its address (page number and offset), its

size in bytes, and its part (Only, First, Middle, or Last).

Frames consisting of a single part are described by a Descriptor.Only; frames consisting of multiple parts are described by a single Descriptor.First, zero or more Descriptor.Middles, and a single Descriptor.Last.

Every Output Data Unit part is described by an ODUD. Output Data Unit Descriptors are fetched from memory so that

frame parts can be assembled for transmission.

Every Input Data Unit part is described by an Input Data Unit

Descriptor (IDUD). Input Data Unit Descriptors are generated on Indicate Channels to describe where the MACSI device wrote each frame part and to report status for the

frame.

Request Descriptors (REQs) are written by the user to specify the operational parameters for the MACSI device Request operations. Request Descriptors also contain the start

address of part of a stream of ODUDs and the number of

frames represented by the ODUD stream part (i.e., the number of ODUD.Last descriptors). Typically, the user will define

a single Request Object consisting of multiple frames of the

same request and service class, frame control, and expected status.

8

3.0 Architectural Description (Continued)

Confirmation Messages (CNFs) are created by the MACSI

device to record the result of a Request operation.

Pool Space Descriptors (PSPs) describe the location and

size of a region of memory space available for writing Input

Data Units.

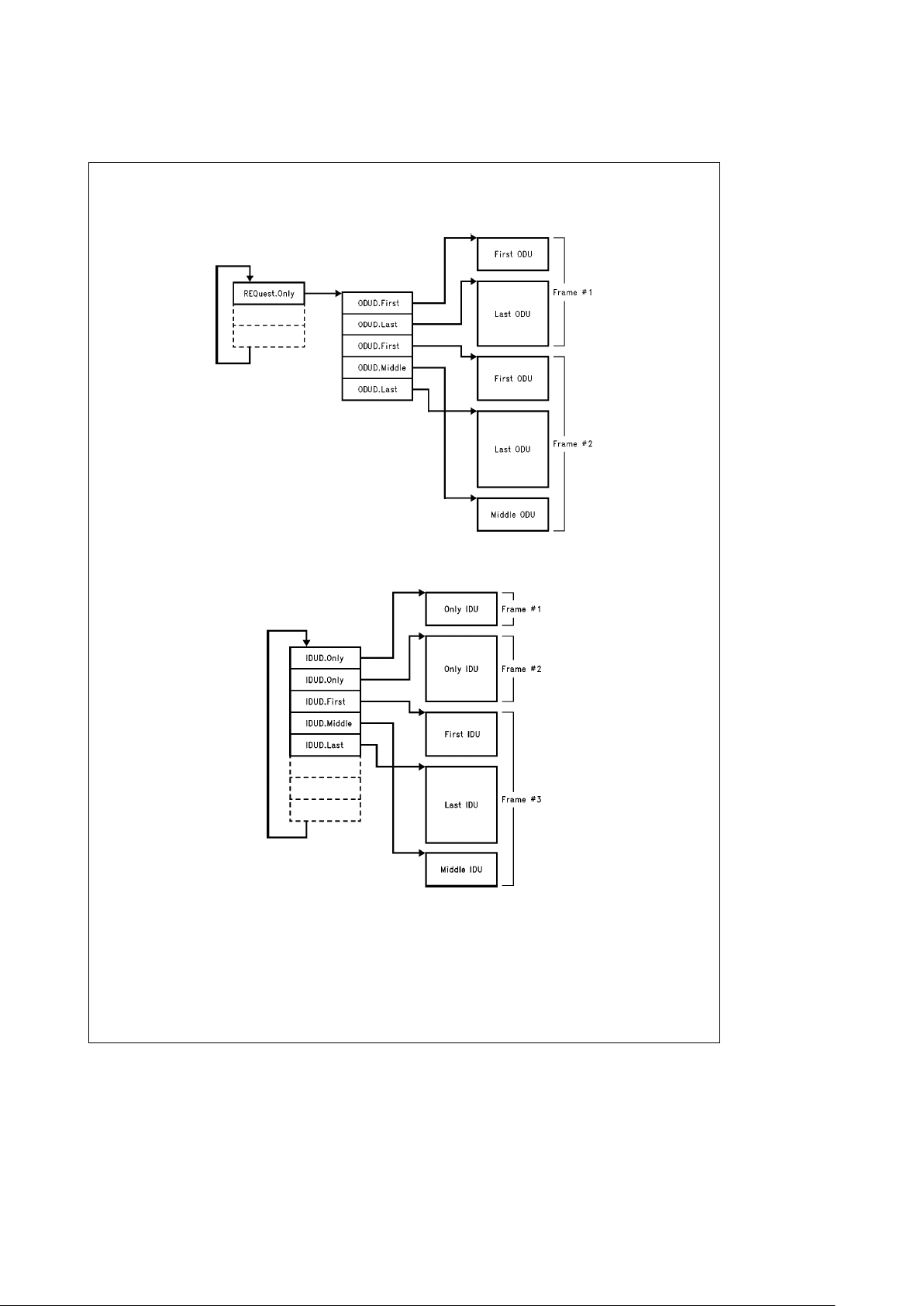

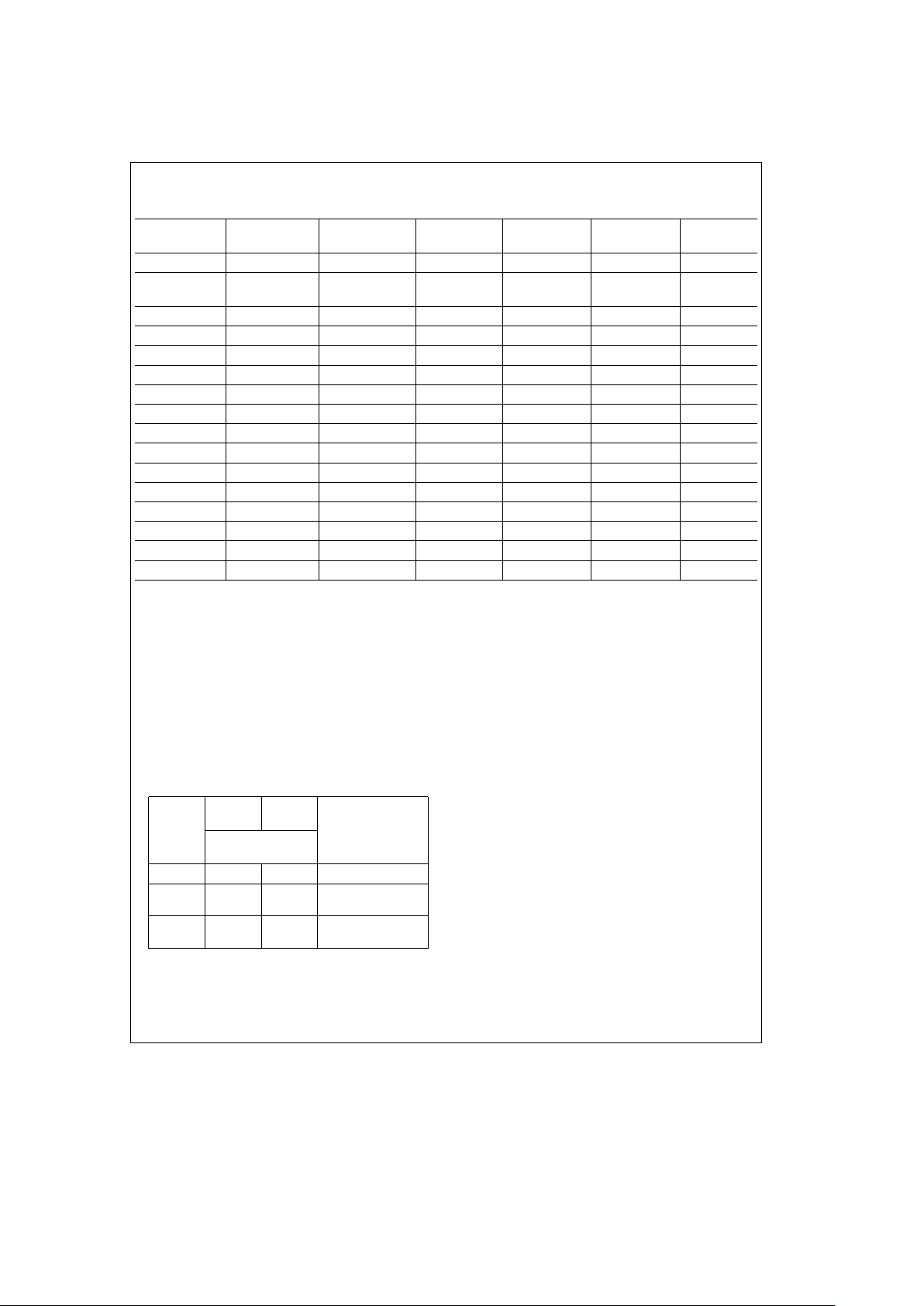

Request (transmit) and Indicate (receive) data structures

are summarized in

Figure 3-3.

3.3.2 Descriptor Queues and Lists

The MACSI device uses 10 Queues and two Lists which are

circular. There are six Queues for Indicate operations, and

four Queues and two Lists for Request operations. Each of

the three Indicate Channels has a Data Queue containing

Pool Space Descriptors (PSPs), and a Status Queue containing Input Data Unit Descriptors (IDUDs). Each Request

Channel has a Data Queue containing Request Descriptors

(REQs), a Status Queue containing Confirmation Messages

(CNFs), and a List containing Output Data Unit Descriptors

(ODUDs).

During Indicate and Request operations, Descriptor Queues

and Lists are read and written by the MACSI device, using

registers in the Pointer and Limit RAM Register files. The

Pointer RAM Queue and List Pointer Registers point to a

location from which a Descriptor will be read (PSPs and

REQs) or written (IDUDs and CNFs). All of the Queues and

Lists are strictly unidirectional. The MACSI consumes objects in those queues which are produced by the Host. The

Host consumes objects in those queues which are produced by the MACSI.

For each Queue Pointer Register there is a corresponding

Queue Limit Register in the Limit RAM Register file, which

holds the Queue’s limit as an offset value in units of 1 Descriptor (8 bytes). The address in the Queue Pointer is incremented before a Descriptor is read and after a Descriptor is

written, then compared with the value in the corresponding

Queue Limit Register. When a Queue Pointer Register becomes equal to the Queue Limit Register, an attention is

generated, informing the host that the Queue is empty.

When a pointer value is incremented past the end of the

page, it wraps to the beginning of the page.

3.3.3 Storage Allocation

The maximum unit of contiguous storage allocation in external memory is a Page. All MACSI device addresses consist

of a 16-bit page number and a 12-bit offset.

The MACSI device uses a page size of 1 kByte or 4 kBytes

for storage of Descriptor Queues and Lists (as selected by

the user), and a page size of 4 kBytes for storage of Data

Units. A single page may contain multiple Data Units, and

multiple-part Data Units may span multiple, disjoint or contiguous pages.

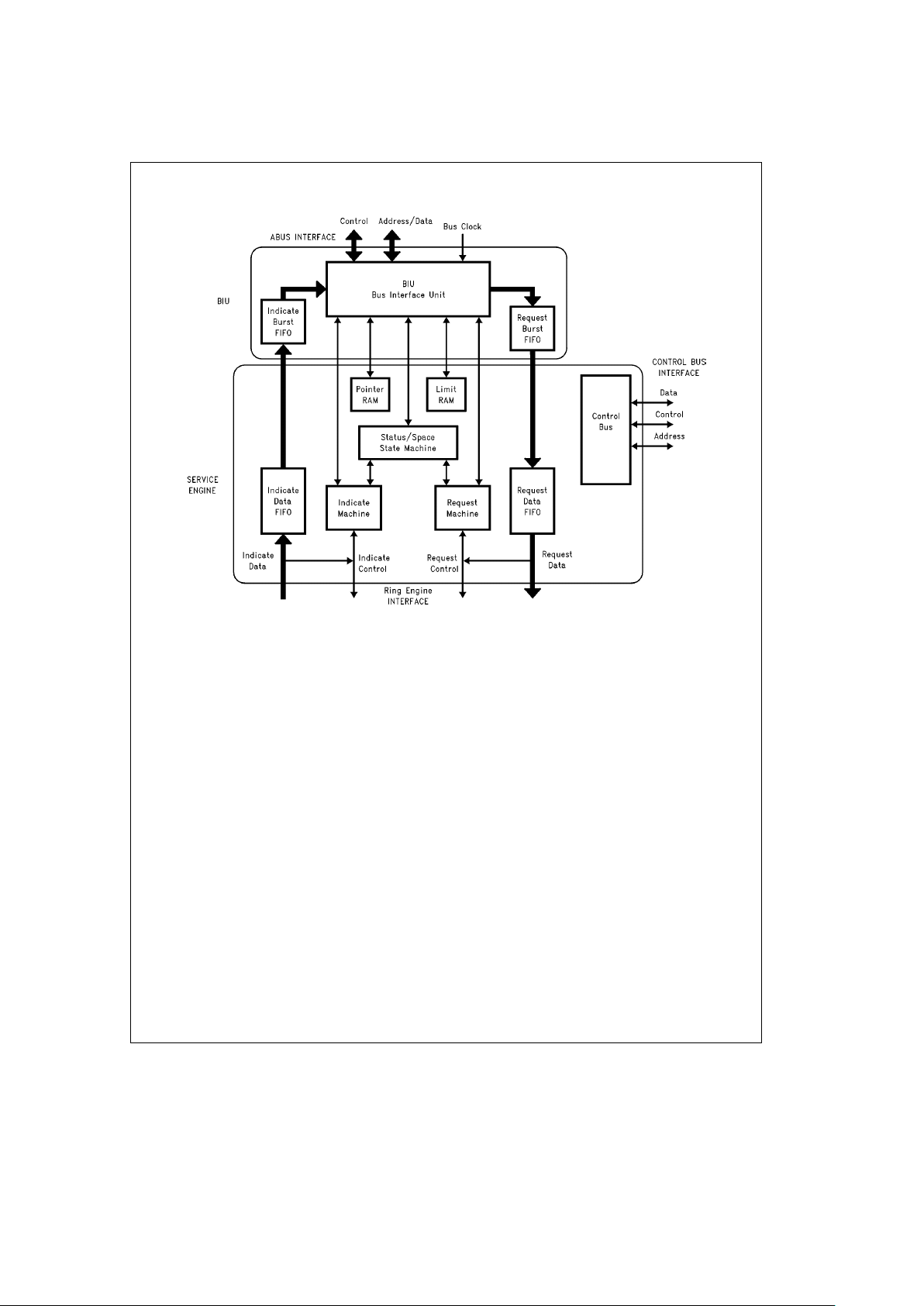

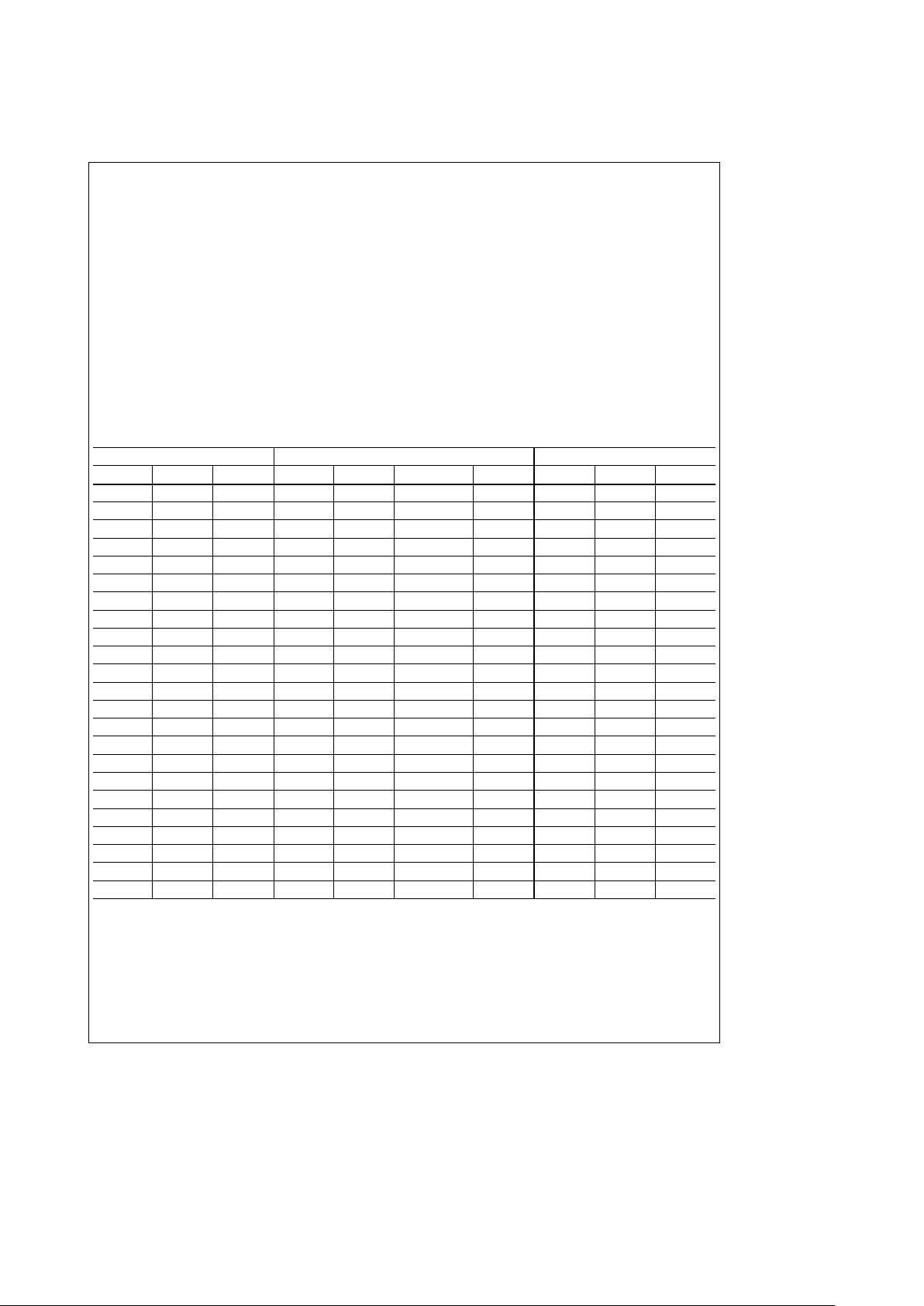

3.4 SERVICE ENGINE

The Service Engine, which manages the operation of the

MACSI, contains seven basic blocks: Indicate Machine, Request Machine, Status/Space State Machine, Pointer RAM,

Limit RAM, and Bus Interface Unit. An internal block diagram of the Service Engine is shown in

Figure 3-4.

3.4.1 Indicate Machine

The Indicate Block accepts Service Data Units (frames)

from the Ring Engine (MAC) in a byte stream format

(MAÐIndicate).

9

3.0 Architectural Description (Continued)

Request Data Structures

TL/F/11705– 4

Indicate Data Structures

TL/F/11705– 5

FIGURE 3-3. MACSI Device Data Structures

10

3.0 Architectural Description (Continued)

TL/F/11705– 6

FIGURE 3-4. Service Engine/BIU Internal Block Diagram

Upon receiving the data, the Indicate Block performs the

following functions:

#

Decodes the Frame Control field to determine frame type

#

Sorts received frames onto Channels according to the

Sort Mode

#

Optionally Filters identical MAC frames

#

Filters Void frames

#

Copies the received frames to memory according to

Copy Criteria

#

Writes status for the received frames to the Indicate

Status Queue

#

Issues interrupts to the host at host-defined status breakpoints

3.4.2 Request Machine

The Request Machine presents frames to the Ring Engine

(MAC) in a byte stream format (MAÐRequest).

The Request Machine performs the following functions:

#

Reads frames from host memory and assembles them

onto Request Channels

#

Prioritizes active requests

#

Transmits frames to the Ring Engine (MAC)

#

Optionally writes status for transmitted and returning

frames

#

Issues interrupts to the host on user-defined group

boundaries

3.4.3 Status/Space Machine

The Status/Space Machine is used by both the Indicate Machine and the Request Machine.

The Status/Space Machine manages all descriptor Queues

and writes status for received and transmitted frames.

3.4.4 Bus Interface Unit

The Bus Interface Unit (BIU) is used by both the Indicate

and Request Blocks. It manages the ABus Interface, providing the MACSI device with a 32-bit data path to local or

system memory.

The Bus Interface Unit controls the transfer of Data Units

and Descriptors between the MACSI device and Host memory via the ABus.

Data and Descriptors are transferred between the MACSI

device and Host memory. Each Channel type handles a set

of Data and Descriptor objects. The three Indicate (Receive)

Channels use the following objects:

1. Input Data Units (written by MACSI)

2. Input Data Unit Descriptors (written by MACSI)

3. Pool Space Descriptors (read by MACSI)

The two Request (Transmit) Channels each use the following objects:

1. Output Data Units (read by MACSI)

2. Output Data Unit Descriptors (read by MACSI)

3. Confirmation Message Descriptors (written by MACSI)

4. Request Descriptors (read by MACSI)

11

3.0 Architectural Description

(Continued)

Each Channel will only process one object type at a time.

The BIU arbitrates between the Channels and issues a Bus

Request when any Channel requests service. The priority of

Channel bus requests is as follows, from highest priority to

lowest priority:

1. Indicate Data Unit writes (highest priority when not transmitting)

2. Output Data Unit fetches (highest priority when transmitting)

3. Request Descriptor and Output Data Unit Descriptor

fetches

4. Input Data Unit Descriptor writes

5. Confirmation Message Descriptor writes

6. Next Pool Space Descriptor transfer to Current Pool

Space Descriptor (internal operation)

7. Pool Space Descriptor fetches

8. Limit RAM Operations (internal operation)

9. Pointer RAM Operations (lowest priority)

Addresses for Channel accesses are contained in the Pointer RAM Registers.

3.4.5 Pointer RAM

The Pointer RAM Block is used by both the Indicate and

Request Machines. It contains pointers to all Data Units and

Descriptors manipulated by the MACSI device, namely, Input and Output Data Units, Input and Output Data Unit Descriptors, Request Descriptors, Confirmation Message Descriptors, and Pool Space Descriptors.

The Pointer RAM Block is accessed by clearing the PTOP

(Pointer RAM Operation) bit in the Service Attention Register, which causes the transfer of data between the Pointer

RAM Register and a mailbox location in memory.

3.4.6 Limit RAM

The Limit RAM Block is used by both the Indicate and Request Machines. It contains data values that define the limits of the ten Queues maintained by the MACSI device.

Limit RAM Registers are accessed by clearing the LMOP

(Limit RAM Operation) bit in the Service Attention Register,

which causes the transfer of data between the Limit RAM

Register and the Limit Data and Limit Address Registers.

4.0 FDDI MAC Facilities

4.1 SYMBOL SET

The Ring Engine (MAC) recognizes and generates a set of

symbols. These symbols are used to convey Line States

(such as the Idle Line State), Control Sequences (such as

the Starting and Ending Delimiters) and Data.

Additional information regarding the symbol set can be

found in the ANSI X3T9.5 PHY standard.

The Ring Engine expects that the Starting Delimiter will always be conveyed on an even symbol pair boundary (i.e.,

the JK symbol will always arrive as a byte, not split across

two bytes). Following the starting delimiter, data symbols

should always come in matched pairs. Similarly the Ending

Delimiter should always come in one or more matched symbol pairs.

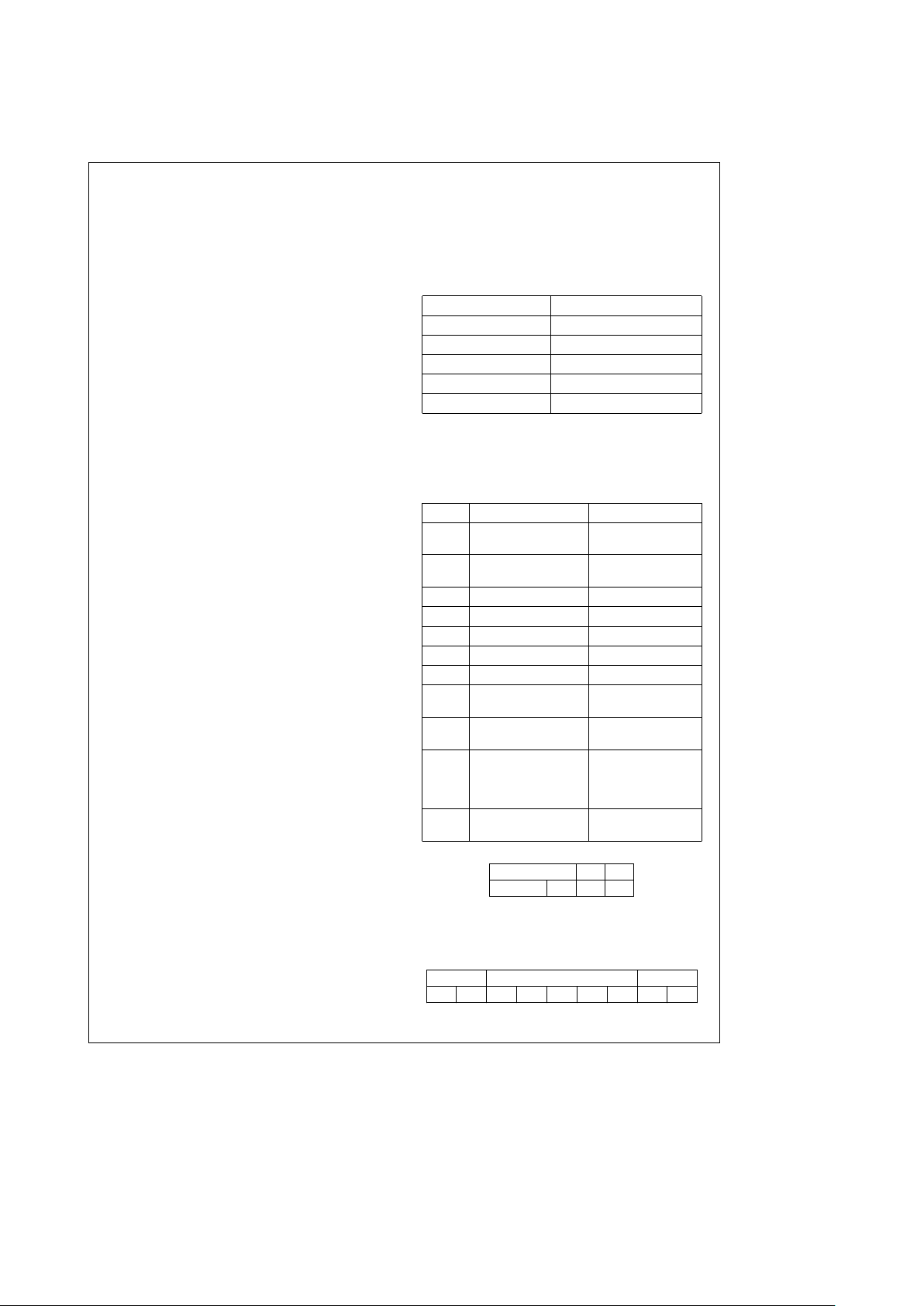

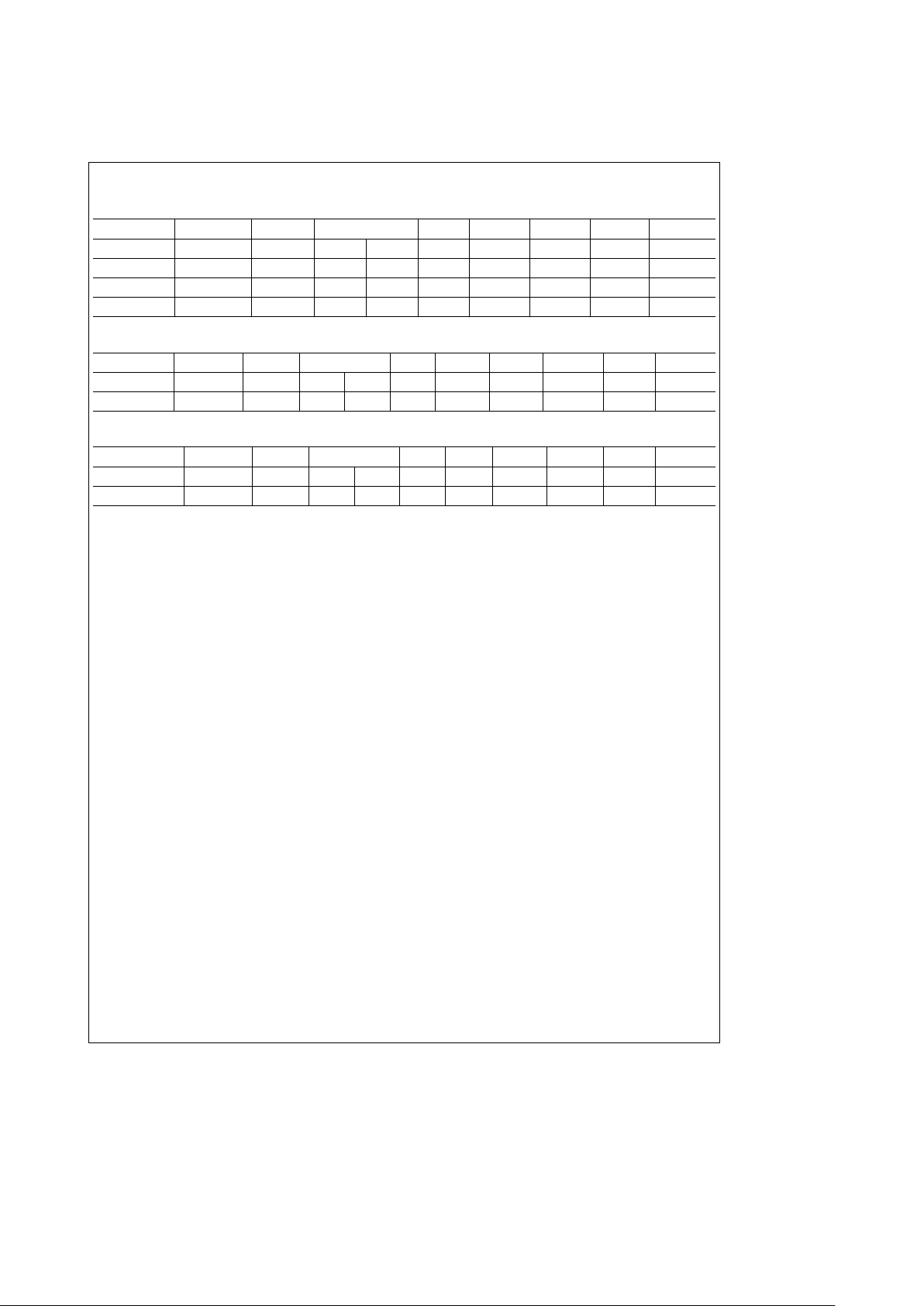

The symbol pairs conveyed at the PHY Interface are shown

in Table 4-1.

4.2 PROTOCOL DATA UNITS

The Ring Engine recognizes and generates Tokens and

Frames.

The Token is used to control access to the ring. Only the

station that has captured the token has the right to transmit

new information. The format of a token is shown in

Figure

4-1.

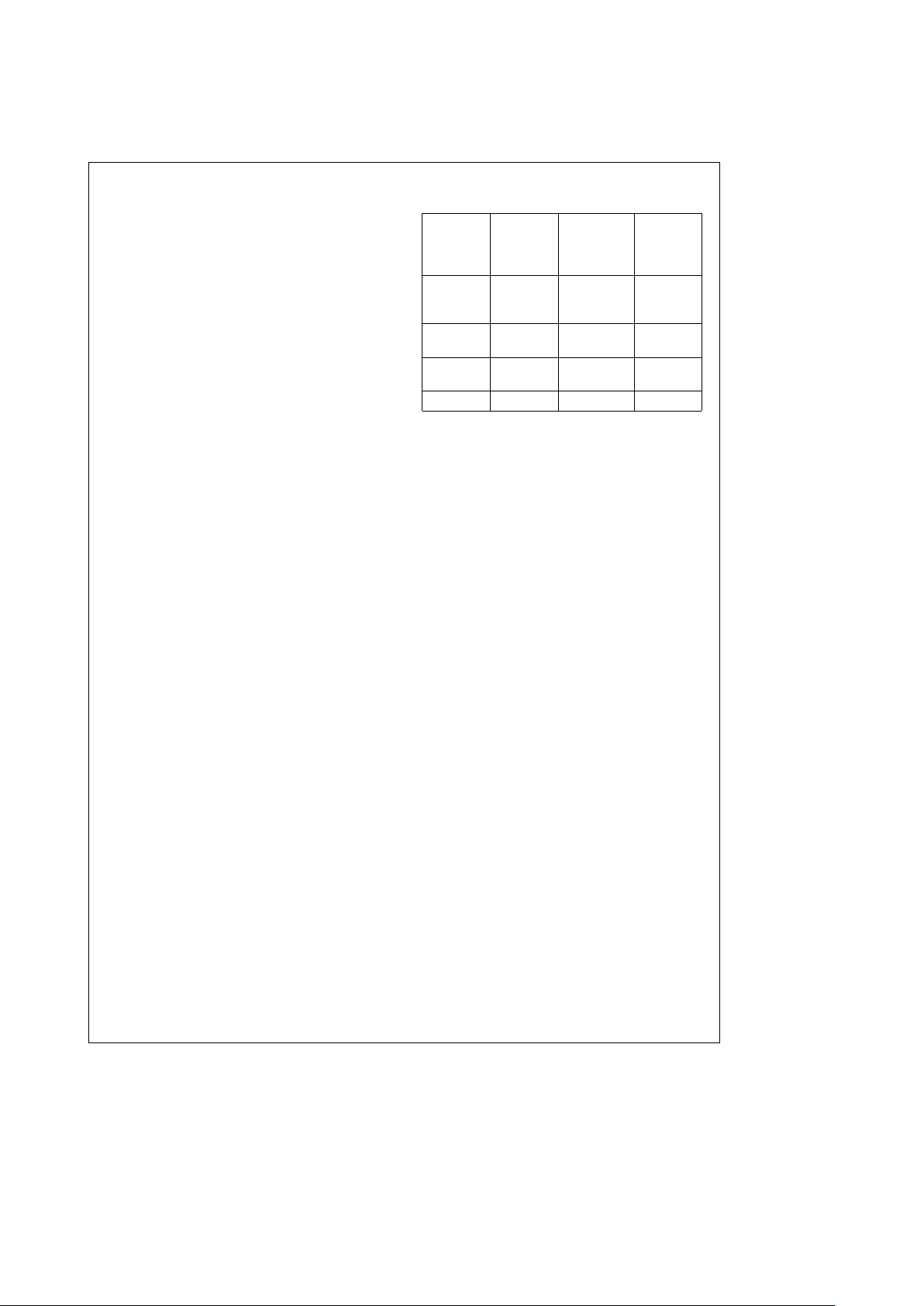

TABLE 4-1. Symbol Pair Set

Type Symbols

Starting Delimiter JK or IL

Ending Delimiter TT or TR or TS or TI

Frame Status RR or RS or SR or SS

Idle II or nI

Data Pair nn

n represents any data symbol (0 –F).

Symbol pairs other than the defined symbols are treated as code violations.

Additional information on the symbol pairs generated and interpreted by the

Ring Engine can be found in Section 8.2.1.

TABLE 4-2. Frame Fields

Name Description Size

SFS Start of Frame

Sequence

PA Preamble 8 or more Idle

symbol pairs

SD Starting Delimiter JK symbol pair

FC Frame Control Field 1 data symbol pair

DA Destination Address 2 or 6 symbol pairs

SA Source Address 2 or 6 symbol pairs

INFO Information Field

FCS Frame Check 4 symbol pairs

Sequence

EFS End of Frame

Sequence

ED Ending Delimiter at least 1 T symbol

for Frames;

at least 2 T symbols

for Tokens

FS Frame Status 3 or more R or S

symbols

SFS EFS

PA SD FC ED

FIGURE 4-1. Token Format

Frames are used to pass information between stations. The

format of a frame is shown in

Figure 4-2,

with the field defini-

tions in Table 4-2.

SFS Protected by FCS EFS

PA SD FC DA SA INFO FCS ED FS

FIGURE 4-2. Frame Format

12

4.0 FDDI MAC Facilities (Continued)

4.2.1 Frame Fields

Start of Frame Sequence (SFS)

The Start of Frame Sequence consists of the Preamble (PA)

followed by the Starting Delimiter (SD).

The Preamble is a sequence of zero or more Idle symbols

that is used to separate frames. The Ring Engine Receiver

can process and repeat a frame or token with no preamble.

The Ring Engine Transmitter generates frames with at least

8 bytes of preamble. The Ring Engine Transmitter also

guarantees that valid FDDl frames will never be transmitted

with more than 40 bytes of preamble.

The Starting Delimiter is used to indicate the start of a new

frame. The Starting Delimiter is the JK Symbol pair.

The Ring Engine expects the Starting Delimiter to be conveyed across the PHÐIndication Interface as a single byte.

Similarly, the Ring Engine only generates Starting Delimiters

aligned to the byte boundary.

Frame Control (FC)

The Frame Control field is used to discriminate frames. For

tokens, the FC field identifies Restricted and Non-restricted

tokens. For other frames, the FC field identifies the frame

type and format and how the frame is to be processed.

The one byte FC field is formatted as shown in

Figure 4-3

.

CLFFrZZZ

FIGURE 4-3. Frame Control Field

The C (Class) bit specifies the MAC Service Class as Asynchronous (C

e

0) or Synchronous (Ce1).

The L (Length) bit specifies the length of the MAC Address

as Short (L

e

0) or Long (Le1). A Short Address is a

16-bit address. A Long Address is a 48-bit address.

The FF (Format) bits specify the frame types as shown in

Table 4-3.

The r (Reserved) bit is currently not specified and should

always be transmitted as Zero.

The ZZZ (Control) bits are used in conjunction with the C

and FF bits to specify the type of frames. These bits may be

used to affect protocol processing criteria such as the Priority, Protocol Class, Status Handling, etc.

TABLE 4-3. Frame Control Format Bits

FC.FF Frame Types

0 0 SMT/MAC

0 1 LLC

1 0 reserved for implementer

1 1 reserved for future standardization

When the Frame Control Format bits (FC.FF) indicate an

SMT or MAC frame, the frame type is identified as shown in

Table 4-4.

TABLE 4-4. MAC/SMT Frame Types

CLFF rZZZ Frame Type

1000 0000 Non-restricted Token

1100 0000 Restricted Token

0L00 0000 Void Frame

0L00 0001 to 1110 SMT Frame

0L00 1111 SMT Next Station Addressing Frame

1L00 0001 Other MAC Frame

1L00 0010 MAC Beacon Frame

1L00 0011 MAC Claim Frame

1L00 0100 MAC Purge Frame

1L00 0101 to 1111 Other MAC Frame

Destination Address (DA)

The Destination Address (DA) field is used to specify the

station(s) that should receive and process the frame.

The DA can be an Individual or Group address. This is determined by the Most Significant Bit of the DA (DA.lG).

When DA.IG is 0 the DA is an Individual Address, when

DA.lG is 1 the DA is a Group Address. The Broadcast/Universal address is a Group Address.

The DA field can be a Long or Short Address. This is determined by the L bit in the FC field (FC.L). If FC.L is 1, the DA

is a 48-bit Long Address. If FC.L is 0, the DA is a 16-bit

Short Address.

The Ring Engine maintains a 16-bit Individual Address (My

Short Address (MSA)), and a 48-bit Individual Address (My

Long Address (MLA)).

On the receive side, if DA.lG is 0 the incoming DA is compared with MLA (if FC.L

e

1) or MSA (if FC.Le0). If the

received DA matches MLA or MSA the frame is intended for

this station and the address recognized flag (AÐFlag) is set.

If DA.lG is 1, the DA is a Group Address and is compared

with the set of Group Addresses recognized by the Ring

Engine. If a match occurs the address recognized flag

(AÐFlag) is set. The AÐFlag is used by system interface

logic as part of the criteria (with FC.L, DA.lG and MÐFlag)

to determine whether or not to copy the frame. lf the

AÐFlag is set, the system interface will normally attempt to

copy the frame.

On the transmit side, the DA is provided by the system interface logic as part of the data stream. The length of the

address to be transmitted is determined by the L bit of the

FC field. (The FC field is also passed in the data stream.)

The Destination Address can be an Individual, Group, or

Broadcast Address.

Source Address (SA)

The Source Address (SA) field is used to specify the address of the station that originally transmitted the frame.

The Source Address has the same length as the Destination

Address (i.e., if the DA is a 16-bit Address, the SA is a 16-bit

Address; if the DA is a 48-bit Address, the SA is a 48-bit

Address).

13

4.0 FDDI MAC Facilities (Continued)

On the receive side, the incoming SA is compared with either MSA or MLA. If a match occurs between the incoming

SA and this station’s MLA or MSA, the MFlag is set. This

flag is used to indicate that the frame is recognized as having been transmitted by this station and is stripped. The

most significant bit of the SA (SA.lG) is not evaluated in the

comparison.

On the transmit side, the station’s individual address is

transmitted as the SA. Since the SA field is normally used

for stripping frames from the ring, the SA stored by the Ring

Engine normally replaces the SA from the data stream. The

length of the address to be transmitted is determined by the

L bit of the FC field. (The FC field is passed in the data

stream.) The most significant bit of the SA (SA.IG) is normally transmitted as 0, independent of the value passed

through the data stream.

As a transmission option, the SA may also be transmitted

transparently from the data stream. When the SA Transparency option is used, an alternate stripping mechanism is

necessary to remove these frames from the ring. (The Ring

Engine provides a Void Stripping Option; see Request

Channel 0 and 1 Configuration Registers 0 (R0CR0 and

R1CR0) for further information.)

As a separate and independent transmission option, the

MSB of the SA may also be transmitted transparently from

the data stream. This is useful for end stations participating

in the Source Routing protocol that would like to continue to

perform reliable stripping based on the SA. (When this option is used without SAT, the transmitted SA is generated by

the Ring Engine, as always.)

Information (INFO)

The Information field contains the data transferred between

peer users of the MAC data service (SMT, LLC, etc.). There

is no INFO field in a Token.

The INFO field contains zero or more bytes.

On the receive side, the INFO field is checked to ensure

that it has at least the minimum length for the frame type

and contains an even number of symbols, as required by the

ANSl X3T9.5 MAC standard.

The first 4 bytes of the INFO field of MAC frames are stored

in an internal register and compared against the INFO field

of the next MAC frame. If the data of the two frames match

and both frames were MAC frames, the SameInfo signal is

generated. This signal may be used to copy MAC frames

only when new information is present.

On the transmit side, the Ring Engine does not limit the

maximum size of the INFO field, but it does insure that

frames are transmitted with a valid DA and SA.

Frame Check Sequence (FCS)

The Frame Check Sequence is a 32-bit Cyclic Redundancy

Check that is used to check for data corruption in frames.

There is no FCS field in a Token.

On the receive side, the Ring Engine checks the FCS to

determine whether the frame is valid or corrupted.

On the transmit side, the FCS field is appended to the end

of the INFO field. As a transmission option, appending the

FCS to the frame can be inhibited (FCS Transparency).

End of Frame Sequence (EFS)

The End of Frame Sequence (EFS) always begins with a T

symbol and should always contain an even number of symbols. For Tokens, an additional T symbol is added. For

frames, the Ending Delimiter (ED) is followed by one or

more of Frame Status Indicators (FS).

The Frame Status (FS) field is used to indicate the status of

the frame. The FS field consists of three Indicators: Error

Detected (E), Address Recognized (A), and Frame Copied

(C). These Indicators are created and modified as specified

in the ANSl X3T9.5 MAC standard.

For frames transmitted by the Ring Engine, the E, A and C

Indicators are appended to all frames and are transmitted

as R symbols. No provisions are made to generate additional trailing control indicators.

For frames repeated by the Ring Engine, the E, A and C

Indicators are handled as specified in the Standard. Additional trailing control indicators are repeated unmodified

provided they are properly aligned. See Section 5.5 for details on Frame Status Processing.

4.2.2 Token Formats

The Ring Engine supports non-restricted and restricted Tokens. See

Figure 4-4

and

Figure 4-5

.

SFS FC EFS

SD 80 ED

FIGURE 4-4. Non-Restricted Token Format

SFS FC ED

SD C0 ED

FIGURE 4-5. Restricted Token Format

Non-restricted

A non-restricted token is used for synchronous and non-restricted asynchronous transmissions. Each time the non-restricted token arrives, a station is permitted to transmit one

or more frames in accordance with its synchronous bandwidth allocation regardless of the status of the token (late or

early).

Asynchronous transmissions occur only if the token is early

(usable token) and the Token Holding Timer has not

reached the selected threshold.

Restricted

A restricted token is used for synchronous and restricted

asynchronous transmissions only.

A station which initiates the restricted dialogue captures a

non-restricted token and releases a restricted token. Stations that participate in the restricted dialogue are allowed

to capture the restricted token. A station ends the restricted

dialogue by capturing the restricted token and releasing a

non-restricted token.

4.2.3 Frame Formats

The Ring Engine supports all of the frame formats permitted

by the FDDl standard. All frame types may be created extemal to the Ring Engine and be passed through the MAC

Request Interface to the Ring. The Ring Engine also has the

ability to generate Void, Beacon, and Claim frames internally.

14

4.0 FDDI MAC Facilities (Continued)

Frames Generated Externally

The Ring Engine transmits frames passed to it from the System Interface. The data portion of the frame is created by

the System Interface. The data portion begins with the FC

field and ends with the last byte of the INFO field. The FC

field is passed transparently to the ring. The length bit in the

FC field is used to determine the length of the transmitted

addresses. The data is passed as a byte stream across the

MAC Request Interface as shown in Table 4-5.

TABLE 4-5. Frame Formats

Field

Size

MAÐRequest PHÐRequest

(bytes)

PA

t8;s

40 Idle Pairs

SD 1 JK

FC 1 FC FC

DA 2 or 6 DA DA

SA 2 or 6 SA MSA, MLA, or SA

INFO

t

0 INFO INFO

FCS 4 if present FCS FCS

ED 1 TR

FS 1 RR

Before the frame is transmitted, the Ring Engine inserts the

Start of Frame Sequence with at least 8 bytes of Preamble

but no more than 40 bytes of Preamble. The starting delimiter is transmitted as a JK symbol pair. The Source Address

is normally transmitted by the Ring Engine since it uses the

Source Address to determine when to strip a frame from the

ring. This can be overridden by using the Source Address

transparency capability. Similarly, the Frame Check Sequence (4 bytes) is normally transmitted by the Ring Engine.

This can be overridden with the FCS transparency capability. With FCS transparency, the FCS is transmitted from the

data stream. The End of Frame Sequence is always transmitted by the Ring Engine as TR RR.

Frames Generated by Ring Engine

The Ring Engine generates and detects several frames in

order to attain and maintain an operational ring.

Void Frames

Void frames are used during normal operation. The Ring

Engine generates two types of void frames: regular Void

frames and MyÐVoid frames.

If Short addressing is enabled, Void frames with the short

address (MSA) are transmitted. Otherwise, Void frames with

the long address (MLA) are transmitted. Table 4-6 shows

the Void frame format.

Void frames are transmitted in order to reset the Valid

Transmission timers (TVX) in other stations to eliminate unnecessary entry to the Claim state. Stations are not required

to copy Void frames. Void frames are transmitted by the

Ring Engine in two situations:

1. While holding a token when no data is ready to be trans-

mitted.

2. After a frame transmission is aborted.

MyÐVoid frames are transmitted by the Ring Engine in

three situations:

1. After a request to measure the Ring Latency has been

made and the next early token is captured.

2. After this station wins the Claim process and before the

token is issued.

3. After a frame has been transmitted with the STRIP op-

tion and before the token for that service opportunity is

issued.

Void frames are also detected by the Ring Engine. A Void

frame with a Source Address other than MSA or MLA is

considered an OtherÐVoid frame.

Claim Frames

Claim frames are generated continuously with minimum preamble while the Ring Engine is in the Transmit Claim state.

The format of Claim frames generated by the Ring Engine is

shown in Table 4-7. When long addressing is enabled,

frames with the long address (MLA) are transmitted. Otherwise frames with the short address (MSA) are transmitted.

The Ring Engine detects reception of valid Claim frames. A

comparison is performed between the first four bytes of the

received INFO field and the value of TREQ programmed in

the parameter RAM in order to distinguish HigherÐClaim,

LowerÐClaim, DuplicateÐClaim, and MyÐClaim.

Beacon Frames

Beacon frames are transmitted continuously with minimum

preamble when the Ring Engine is in the Transmit Beacon

state. The format of Beacon frames generated by the Ring

Engine is shown in Table 4-8. When long addressing is enabled, frames with the long address (MLA) are transmitted.

Otherwise frames with the short address (MSA) are transmitted.

15

4.0 FDDI MAC Facilities (Continued)

TABLE 4-6. Void Frames

Type Enable Size SFS FC DA SA FCS EFS

Void ESA Short PA SD 00 null MSA FCS TRRR

Void not ESA Long PA SD 40 null MLA FCS TRRR

MyÐVoid ESA Short PA SD 00 MSA MSA FCS TRRR

MyÐVoid not ESA Long PA SD 40 MLA MLA FCS TRRR

TABLE 4-7. Claim Frames

Type Enable Size SFS FC DA SA INFO FCS EFS

MyÐClaim not ELA Short PA SD 83 MSA MSA TREQ FCS TRRR

MyÐClaim ELA Long PA SD C3 MLA MLA TREQ FCS TRRR

TABLE 4-8. Beacon Frames

Type Enable Size SFS FC DA SA INFO FCS EFS

MyÐBeacon not ELA Short PA SD 82 null MSA TBT FCS TRRR

MyÐBeacon ELA Long PA SD C2 null MLA TBT FCS TRRR

When the Transmit Beacon State is entered from the Transmit Claim State the first byte of the 4 byte TBT field is transmitted as Zero.

Beacon frames that require alternative formats such as Directed Beacons must be generated externally.

The Ring Engine detects reception of valid Beacon frames

and distinguishes between Beacon frames transmitted by

this MAC (MyÐBeacon) and Beacon frames transmitted by

other stations (OtherÐBeacon).

4.3 FRAME COUNTS

To aid in fault isolation and to enhance the management

capabilities of a ring, the Ring Engine maintains several

frame counts. The Error and lsolated frame counts increment when a frame is received with one or more errors that

were previously undetected. The Ring Engine then modifies

the Error Control Indicator so that a downstream station will

not increment its count.

The size of the counters has been chosen such that minimal

software intervention is required, even under marginal operating conditions.

The following counts are maintained by the Ring Engine:

FRCT Frame Received

ElCT Error lsolated

LFCT Lost Frame

FCCT Frames Copied with Ax set

FNCT Frames Not Copied with Ax set

FTCT Frames Transmitted

4.3.1 Frame Received Count (FRCT)

The Frame Received Count is described in the FDDl MAC

standard, and is the count of all complete frames received.

This count includes frames stripped by this station.

4.3.2 Error lsolated Count (ElCT)

The Error lsolated Count is described in the FDDl MAC standard, and is the count of error frames detected by this station and no previous station. It increments when:

1. An FCS error is detected and the received Error Indicator

(Er) is not equal to S.

2. A frame of invalid length (i.e., off boundary T) is received

and Er is not equal to S.

3. Er is not R or S.

4.3.3 Lost Frame Count (LFCT)

The Lost Frame Count is described in the FDDl MAC standard, and is the count of all instances where a format error

is detected in a frame or token such that the credibility of

reception is placed in doubt. The Lost Frame Count is incremented when any symbol other than data or Idle symbols is

received between the Starting and Ending Delimiters of a

frame (this includes parity errors).

4.3.4 Frame Copied Count (FCCT)

The Frame Copied Count is described in the FDDl MAC

standard, and is the count of the number of frames addressed to and copied by this station. The count is incremented when an internal or external match occurs (when

Option.EMlND enabled) on the Destination Address, no errors were detected in the frame and the frame was successfully copied (which the Service Engine communicates to the

Ring Engine via the internal VCOPY signal). Frames copied

promiscuously, MAC frames, Void frames and NSA frames

received with the A indicator set are not included in this

count.

16

4.0 FDDI MAC Facilities (Continued)

4.3.5 Frames Not Copied Count (FNCT)

The Frames Not Copied Count is specified in the FDDI MAC

standard, and is the count of frames intended for this station

that were not successfully copied by this station. The count

is incremented when an internal or external (when

Option.EMIND is enabled) Destination Address match occurs, no errors were detected in the frame, and the frame

was not successfully copied (VCOPY

e

0). MAC frames,

Void frames, and NSA frames received with the A indicator

set are not included in this count.

4.3.6 Frames Transmitted Count (FTCT)

The Frames Transmitted Count is specified in the FDDI

MAC standard, and is incremented every time a complete

frame is transmitted from the MAC Request Interface. Void

and MAC frames generated by the Ring Engine are not included in the count.

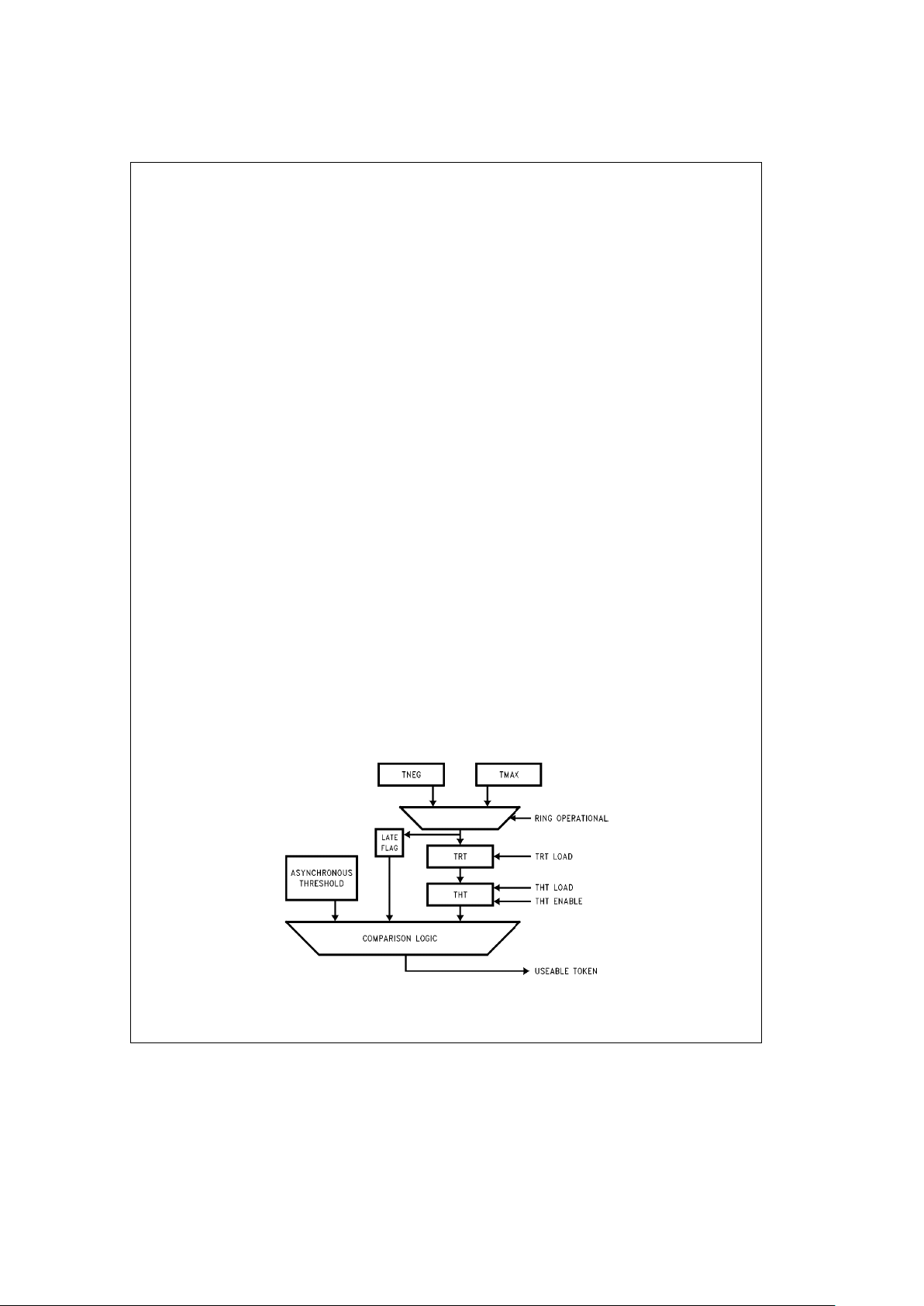

4.4 TIMERS

4.4.1 Token Rotation Timer (TRT)

The Token Rotation Timer (TRT) times token rotations from

arrival to arrival. TRT is used to control ring scheduling during normal operation and to detect and recover from serious

ring error situations.

TRT is loaded with the maximum token rotation time, TMAX,

when the ring is not operational. TRT is loaded with the

negotiated Target Token Rotation Time, TNEG, when the

ring is operational.

4.4.2 Token Holding Timer (THT)

The Token Holding Timer is used to limit the amount of ring

bandwidth used by a station for asynchronous traffic once

the token is captured. THT is used to determine if the captured token is (still) usable for asynchronous transmission. A

token is usable for asynchronous traffic if THT has not

reached the selected threshold. Two asynchronous thresholds are supported; one that is fixed at the Negotiated Target Token Rotation Time (TNEG), and one that is programmable at one of 16 Asynchronous Priority Thresholds. Requests to transmit frames at one of the priority thresholds

are serviced when the Token Holding Timer (THT) has not

reached the selected threshold.

4.4.3 Late Count (LTCT)

The Late Count is implemented differently than suggested

by the MAC standard, but provides similar information. The

function of the Late Count is divided between the Late

Ð

Flag that is equivalent to the MAC standard Late Count with

a non-zero value and a separate counter. LateÐFlag is

maintained by the Ring Engine to indicate if it is possible to

send asynchronous traffic. When the ring is operational,

Late Count indicates the time it took the ring to recover the

last time the ring became non-operational. When the ring is

non-operational, Late Count indicates the time it has taken

(so far) to recover the ring.

The Late Count is incremented every time TRT expires

while the ring is non-operational and LateÐFlag is set (once

every TMAX).

The Late Count is provided to assist Station Management,

SMT, in the isolation of serious ring errors. In many situations the ring will recover very quickly and late count will be

of marginal utility. However, in the case of serious ring er-

rors, it is helpful for SMT to know how long it has been since

the ring became non-operational (with TMAX resolution) in

order to determine if it is necessary to invoke recovery procedures. When the ring becomes non-operational, there is

no way to know how long it will stay non-operational. Therefore, a timer is necessary. If the Late Count were not provided, SMT would be forced to start a timer every time the ring

becomes non-operational even though it may seldom be

used. By using the provided Late Count, an SMT implementation may be able to alleviate this additional overhead.

4.4.4 Valid Transmission Timer (TVX)

The Valid Transmission Timer (TVX) is reset every time a

valid frame or token is received. TVX is used to increase the

responsiveness of the ring to errors. Expiration of the TVX

indicates that no frame or token has been received within

the timeout period and causes the Transmitter to invoke the

recovery (Claim) process.

The Value of TVX is also used as the Duplicate MAC frame

detection delay, DMÐMIN. This is the time after which a

MAC frame will be suspected as being generated by another station with this station’s address when the ring is nonoperational.

4.4.5 Token Received Count (TKCT)

The Token Received Count is incremented every time a valid token arrives. The Token Count can be used with the

Ring Latency Count to calculate the average network load

over a period of time. The frequency of token arrival is inversely related to the network load.

4.4.6 Ring Latency Count (RLCT)

The Ring Latency Count is a measurement of time for

frames to propagate around the ring. This counter contains

the last measured ring latency whenever the Ring Latency

Valid bit of the Token Event Register (TELR0.RLVLD) is

One.

The Latency Counter increments every 16 byte times

(1.28 ms) and is used to measure ring latencies up to

1.3421772 seconds directly with accuracy of 1.2 ms. No

overflow or increment event is provided with this counter.

4.5 RING SCHEDULING

FDDI uses a timed token protocol to schedule use of the

ring. The protocol measures load on the network by timing

the rotation of the token. The longer the token rotation time

the greater the instantaneous load on the network. By limiting the transmission of data when the token rotation time

exceeds a target rotation time, a maximum average token

rotation time is realized. The protocol is used to provide

different classes of service.

Multiple classes of service can be accommodated by setting

different target token rotation times for each class of service.

The Ring Engine supports Synchronous, Non-restricted

Asynchronous, Restricted Asynchronous, and Immediate

service classes. The Immediate service class is supported

when the ring is non-operational; the other classes are supported when the ring is operational.

4.5.1 Synchronous Service Class

The Synchronous Service Class may be used to guarantee

a maximum response time (2 times TTRT), minimum bandwidth, or both.

17

4.0 FDDI MAC Facilities (Continued)

Each time the token arrives, a station is permitted to transmit one or more frames in accordance with its synchronous

bandwidth allocation regardless of the status of the token

(late or early; Restricted or Non-Restricted).

Since the Ring Engine does not provide a mechanism for

monitoring a station’s synchronous bandwidth utilization,

the user must insure that no synchronous request requires

more than the allocated bandwidth.

To help ensure that synchronous bandwidth is properly allocated after ring configuration, synchronous requests are not

serviced after a Beacon frame is received. After a major

reconfiguration has occurred, management software must

intervene to verify or modify the current synchronous bandwidth allocation.

4.5.2 Non-Restricted Asynchronous Service Class

The Non-Restricted Asynchronous service class is typically

used with interactive and background traffic. Non-Restricted

Asynchronous requests are serviced only if the token is early and the Token Holding Timer has not reached the selected threshold.

Asynchronous service is available at two priority thresholds,

the Negotiated Target Token Rotation Time plus one programmable threshold. Management software may use the

priority thresholds to discriminate additional classes of traffic based on current loading characteristics of the ring. The

priority thresholds may be determined using the current

TTRT and the Ring Latency. In this case, application software is only concerned with the priority level of a request.

As an option, Asynchronous Requests may be serviced with

THT disabled. This is useful when it is necessary to guarantee that a multi-frame request will be serviced on a single

token opportunity. Because of the possibility of causing late

tokens, this capability should be used with caution, and

should only be allowed when absolutely necessary.

4.5.3 Restricted Asynchronous Service Class

The Restricted Asynchronous service class is useful for

large transfers requiring all of the available Asynchronous

bandwidth. The Restricted Token service is useful for large

transfers requiring all of the available (remaining) asynchronous bandwidth.

The Restricted Token service may also be used for operations requiring instantaneous allocation of the remaining

synchronous bandwidth when Restricted Requests are

serviced with THT disabled. This is useful when it is necessary to guarantee atomicity, i.e., that a multi-frame request

will be serviced on a single token opportunity.

A Restricted dialogue consists of three phases:

1. Initiation of a Restricted dialogue:

#

Capture a Non-restricted Token

#

Transmit zero or more frames to establish a Restricted

dialogue with other stations

#

Issue a Restricted Token to allow other stations in the

dialogue to transmit frames

2. Continuation of a Restricted dialogue:

#

Capture a Restricted Token

#

Transmit zero or more frames to continue the Restricted dialogue

#

Issue a Restricted Token to allow other stations in the

dialogue to transmit frames

3. Termination of a Restricted dialogue:

#

Capture a Restricted Token

#

Transmit zero or more frames to continue the Restricted dialogue

#

Issue a Non-Restricted Token to return to the Non-Restricted service class

Initiation of a Restricted dialogue will prevent all Non-Restricted Asynchronous traffic throughout the ring for the duration of the dialogue, but will not affect Synchronous traffic.

To ensure that the Restricted traffic is operating properly, it

is possible to monitor the use of Restricted Tokens on the

ring. When a Restricted Token is received, the event is

latched and, under program control, may generate an interrupt. In addition, a request to begin a Restricted dialogue

will only be honored if both the previous transmitted Token

and the current received Token were Non-Restricted tokens. This is to ensure that the upper bound on the presence of a Restricted dialogue in the ring is limited to a single

dialogue.

As suggested by the MAC-2 standard, to help ensure that

only one Restricted dialogue will be in progress at any given

time, Restricted Requests are not serviced after a MAC

frame is received until Restricted Requests are explicitly enabled by management software. Since the Claim process

results in the generation of a Non-restricted Token, this prevents stations from initiating another restricted dialogue

without the intervention of management software.

4.5.4 Immediate Service Class

The Immediate Service Class facilitates several non-standard applications and is useful in ring failure recovery (e.g.,

Transmission of Directed Beacons). Certain ring failures

may cause the ring to be unusable for normal traffic, until

the failure is remedied.

Immediate requests are only serviced when the ring is nonoperational. Immediate requests may be serviced from the

Transmitter Data, Claim, and Beacon States. Options are

available to force the Ring Engine to enter the Claim or

Beacon State, to prohibit it from entering the Claim State, or

to remain in the Claim State when receiving MyÐClaim.

On the completion of an Immediate request, a Token (Nonrestricted or Restricted) may optionally be issued. Immediate requests may also be used in non-standard applications

such as a full duplex point to point link.

5.0 Functional Description

(Ring Engine)

5.1 TOKEN HANDLING

5.1.1 Token Timing Logic

The FDDI Ring operates based on the Timed Token Rotation protocol where all stations on the ring negotiate for the

maximum time that the stations have to wait before being

able to transmit frames. This value is termed the Negotiated

Target Token Rotation Time (TTRT). The TTRT value is

stored in the TNEG Register.

Stations negotiate for TTRT based on their TREQ that is

assigned to them upon initialization.

Each station keeps track of the token arrival by setting the

Token Rotation Timer (TRT) to the TTRT value. If the token

18

5.0 Functional Description (Continued)

is not received within TTRT (the token is late), the event is

recorded by setting the LateÐFlag. If the token is not received within twice TTRT (TRT expires and LateÐFlag is

set), there is a potential problem in the ring and the recovery

process is invoked.

Furthermore, the Token Holding Timer (THT) is used to limit