NSC CLC020ACQ Datasheet

CLC020

SMPTE 259M Digital Video Serializer with Integrated

Cable Driver

General Description

The CLC020 SMPTE 259M Digital Video Serializer with Integrated Cable Driver is a monolithic integrated circuit that encodes, serializes and transmits bit-parallel digital data conforming to SMPTE 125M and SMPTE 267M component

video and SMPTE 244M composite video standards. The

CLC020 can also serialize other 8 or 10-bitparalleldata.The

CLC020 operates at data rates from below 100 Mbps to over

400 Mbps. The serial data clock frequency is internally generated and requires no external frequency setting components, trimming or filtering

*

. Functions performed by the

CLC020 include: parallel-to-serial data conversion, data encoding using the polynomial (X

9+X4

+1), data format conversion from NRZ to NRZI, parallel data clock frequency multiplication and encoding with the serial data, and coaxial cable

driving. Input for sync (TRS) detection disabling and a PLL

lock detect output are provided. The CLC020 has an exclusive built-in self-test (BIST) and video test pattern generator

(TPG) with 4 component video test patterns, reference

black, PLLandEQpathologicals and modified colour bars, in

4:3 and 16:9 raster and both NTSC and PALformats

*

. Separate power pins for the output driver, VCO and the digital

logic improve power supply rejection, output jitter and noise

performance.

The CLC020 is the ideal complement to the CLC011B

SMPTE 259M Serial Digital Video Decoder, CLC014 Active

Cable Equalizer, CLC016 Data Retiming PLL (clock-data

separator), CLC018 8X8 Digital Crosspoint Switch and

CLC006 or CLC007 Cable Drivers, for a complete

parallel-serial-parallel, high-speed data processing and

transmission system.

The CLC020 is powered from a single 5V supply. Power dissipation is typically 235 mW including two 75Ω

back-matched output loads. The device is packaged in a

JEDEC 28-lead PLCC.

Features

n SMPTE 259M serial digital video standard compliant

n No external serial data rate setting or VCO filtering

components required

*

n Built-in self-test (BIST) and video test pattern generator

(TPG) with 16 internal patterns

*

n Supports all NTSC and PAL standard component and

composite serial video data rates

n HCMOS/TTL-compatible data and control inputs and

outputs

n 75Ω ECL-compatible, differential, serial cable-driver

outputs

n Fast VCO lock time:

<

75 µs

n Single +5V TTL or −5V ECL supply operation

n Low power: 235 mW typical

n 28-lead PLCC package

n Commercial temperature range 0˚C to +70˚C

Applications

n SMPTE 259M parallel-to-serial digital video interfaces

for:

— Video cameras

— VTRs

— Telecines

— Video test pattern generators and digital video test

equipment

n Non-SMPTE video applications

n Other high data rate parallel/serial video and data

systems

*

Patents applications made or pending.

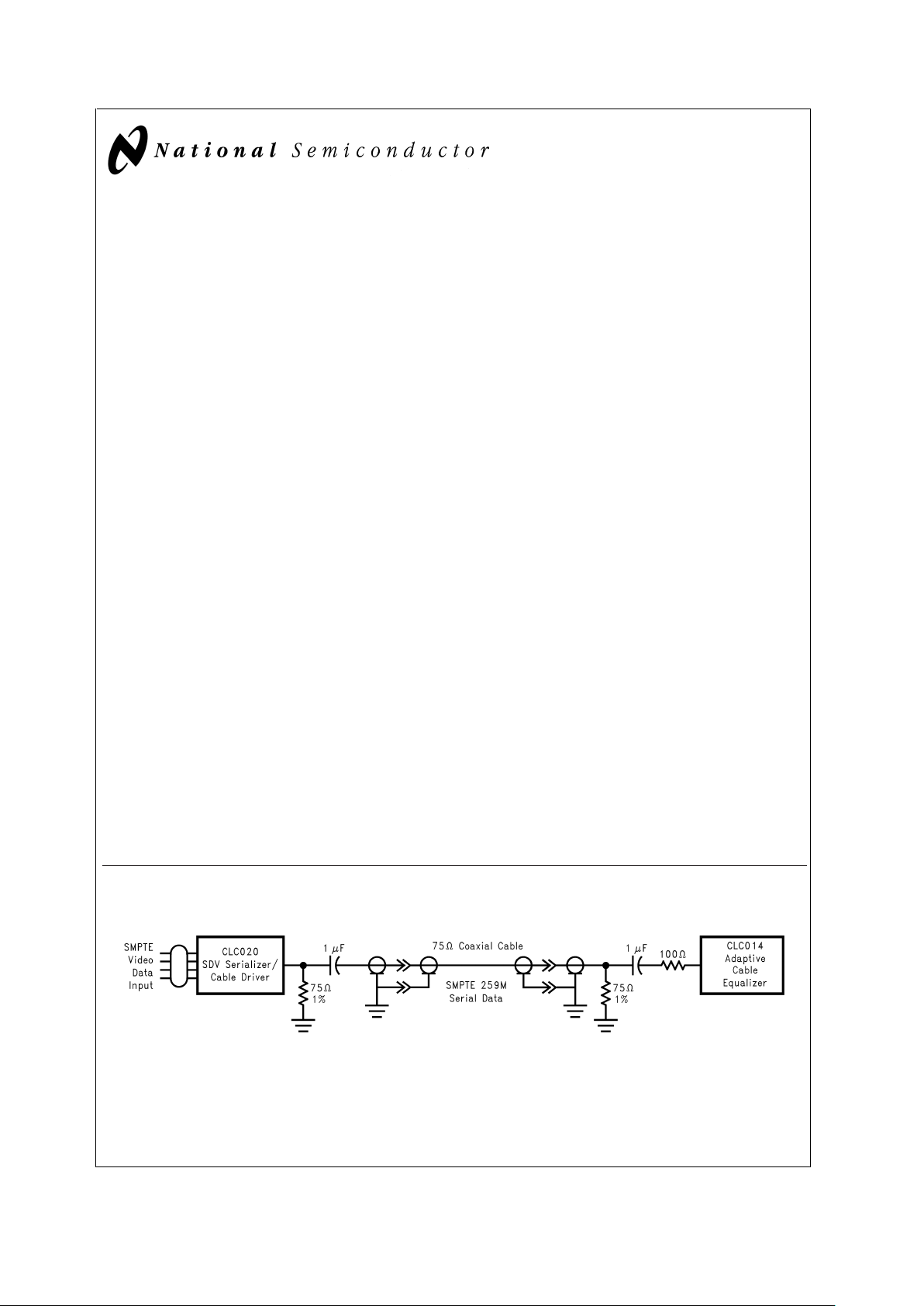

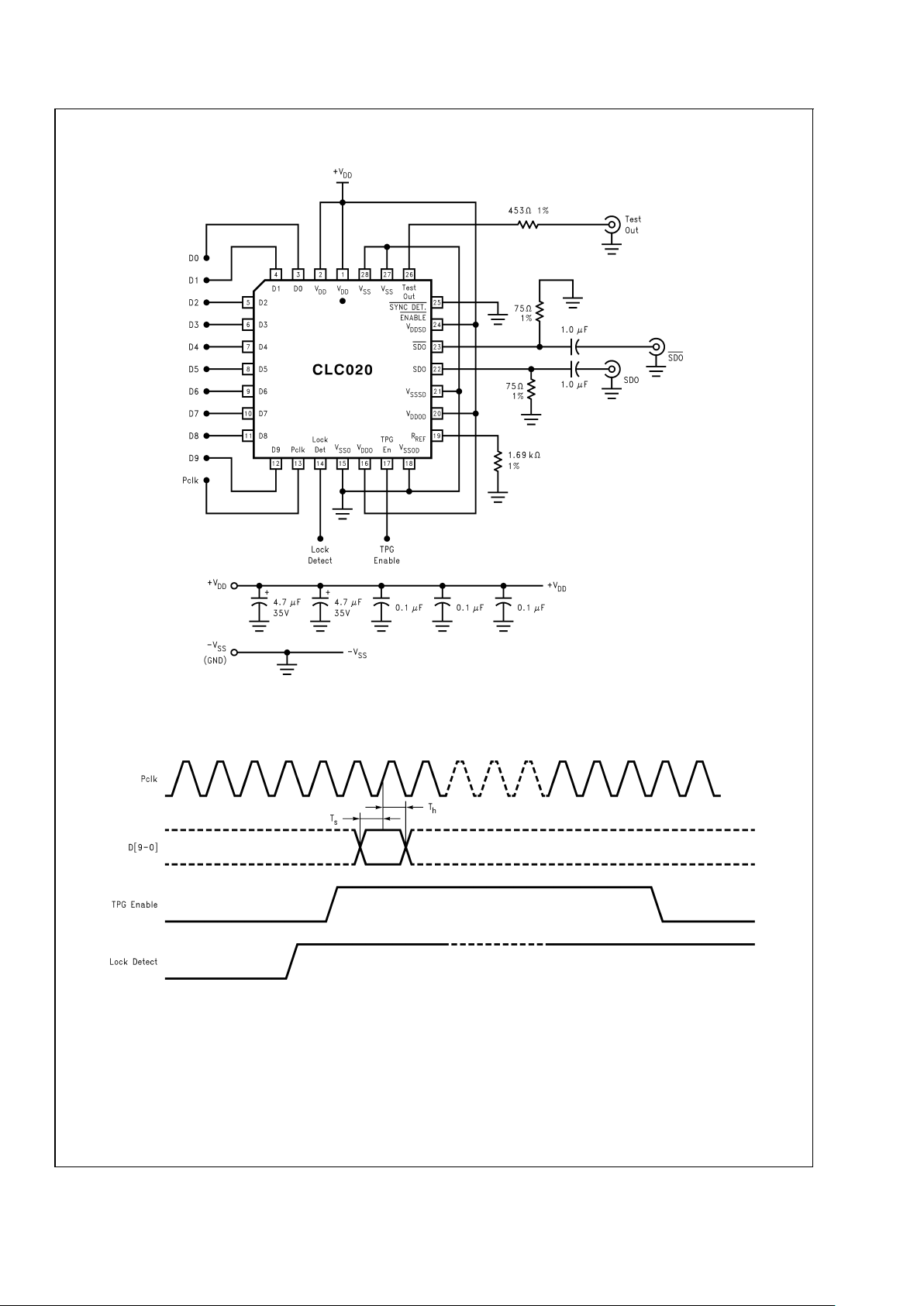

Typical Application

DS100917-12

February 2000

CLC020 SMPTE 259M Digital Video Serializer with Integrated Cable Driver

© 2000 National Semiconductor Corporation DS100917 www.national.com

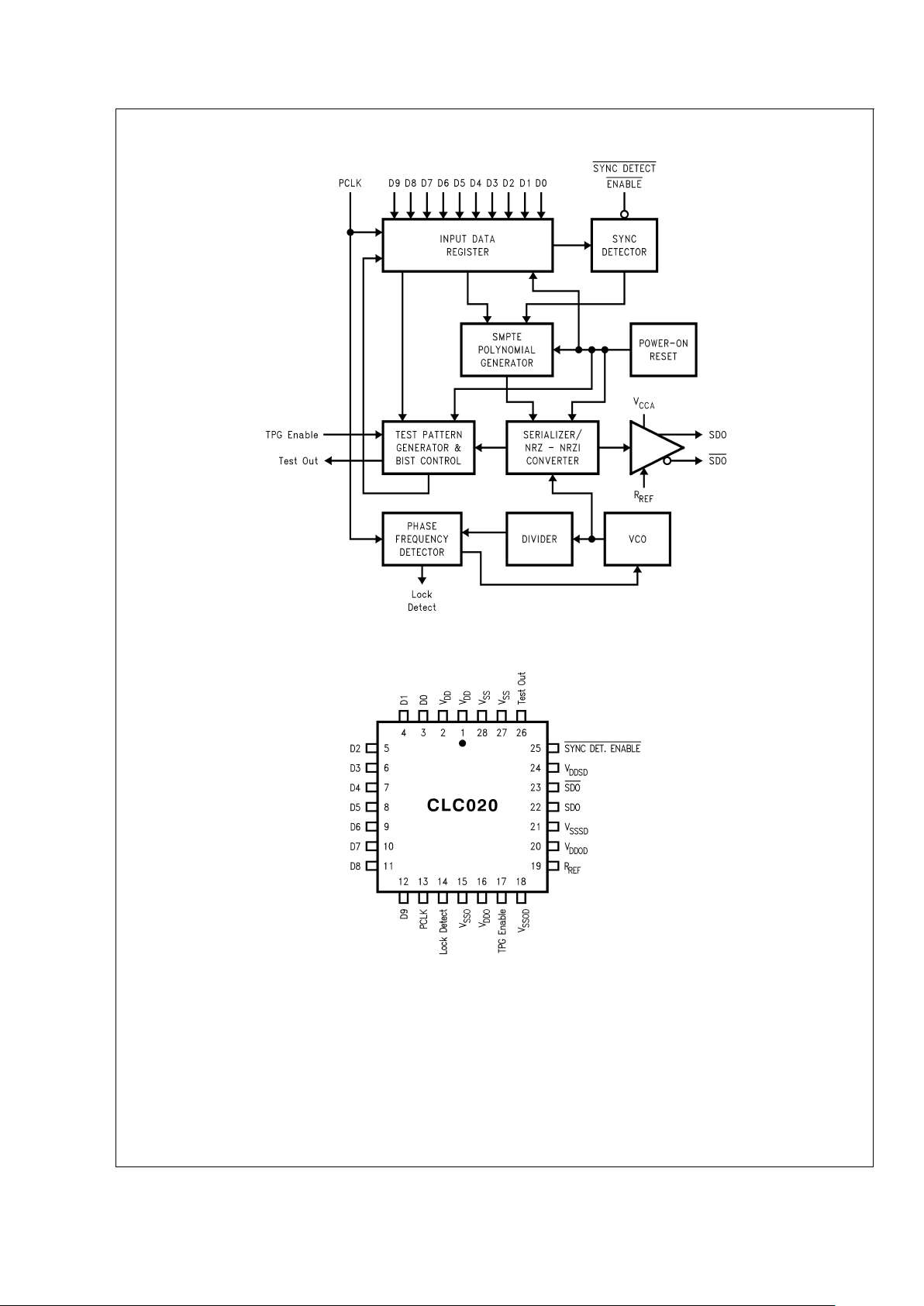

Block Diagram

Connection Diagram

DS100917-1

DS100917-2

28-Pin PLCC

Order Number CLC020ACQ

See NS Package Number V28A

CLC020

www.national.com 2

Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required,

please contact the National Semiconductor Sales Office/

Distributors for availability and specifications.

Supply Voltage (V

DD−VSS

) 6.0V

CMOS/TTL Input Voltage (V

I

) −0.5V to (VDD+ 0.5V)

CMOS/TTL Output Voltage (V

O

) −0.5V to (VDD+ 0.5V)

CMOS/TTL Input Current (single input)

V

I=VSS

−0.5V −5 mA

V

I=VDD

+0.5V +5 mA

Input Current, Other Inputs

±

1mA

CMOS/TTL Output Source/Sink Current

±

10 mA

SDO Output Source Current 20 mA

Package Thermal Resistance

θ

JA

28-lead PLCC 85˚C/W

θ

JC

28-lead PLCC 35˚C/W

Storage Temp. Range −65˚C to +150˚C

Junction Temperature +150˚C

Lead Temperature (Soldering 4 Sec) +260˚C

ESD Rating (HBM)

>

2.5 kV

ESD Rating (MM)

>

300 V

Transistor Count 33,400

Recommended Operating

Conditions

Supply Voltage (VDD−VSS) 5.0V±10%

CMOS/TTL Input Voltage V

SS

to V

DD

Maximum DC Bias on SDO pins 3.0V±10%

Operating Free Air Temperature (T

A

) 0˚C to +70˚C

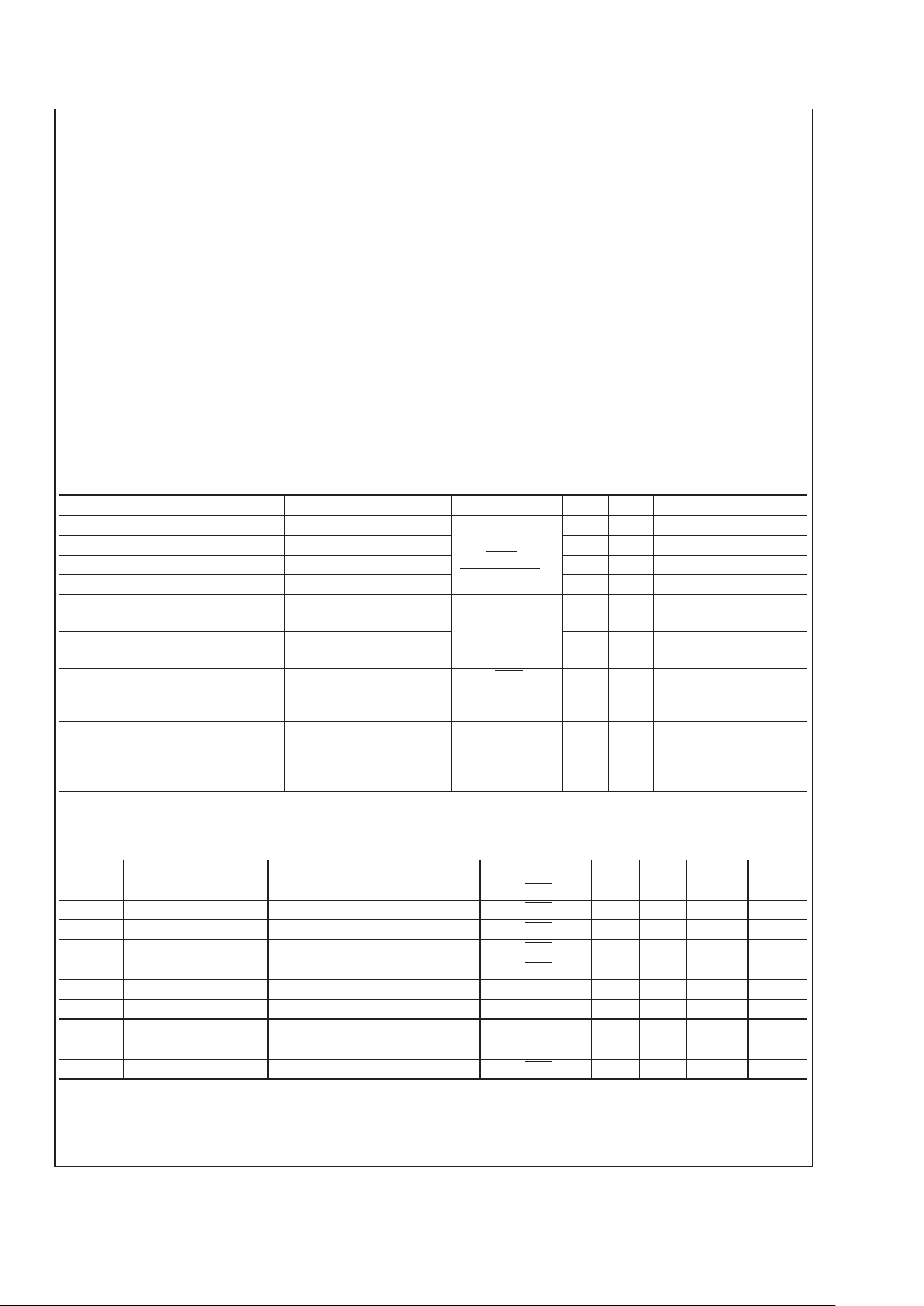

DC Electrical Characteristics

Over Supply Voltage and Operating Temperature ranges, unless otherwise specified (Notes 2, 3).

Symbol Parameter Conditions Reference Min Typ Max Units

V

IH

Input Voltage High Level D0 through D9,

P

CLK

, TPG_EN

and Sync.

Detect Enable

2.0 V

DD

V

V

IL

Input Voltage Low Level V

SS

0.8 V

I

IH

Input Current High Level VIH=V

DD

+40 +60 µA

I

IL

Input Current Low Level VIL=V

SS

-1 -20 µA

V

OH

CMOS Output Voltage

High Level

IOH= −10 mA Lock Detect,

Test Out

2.4 4.7 V

DD

V

V

OL

CMOS Output Voltage

Low Level

IOL= +10 mA 0.0 0.3 VSS+ 0.5V V

V

SDO

Serial Driver Output

Voltage

RL=75Ω1%,

R

REF

= 1.69 kΩ 1%,

Figure 2

SDO, SDO 700 800 900 mV

P-P

I

DD

Power Supply Current,

Total

RL=75Ω1%,

R

REF

= 1.69 kΩ 1%,

P

CLK

= 27 MHz,

Figure 2

,

NTSC Colour Bar Pattern

47 60 mA

AC Electrical Characteristics

Over Supply Voltage and Operating Temperature ranges, unless otherwise specified (Note 3).

Symbol Parameter Conditions Reference Min Typ Max Units

BR

SDO

Serial data rate RL=75Ω, AC coupled, (Note 5) SDO, SDO 100 400 Mbps

t

j

Serial output jitter 270 Mbps,

Figure 2

, (Note 6) SDO, SDO 220 ps

P-P

t

jit

Serial output jitter (Notes 4, 5) SDO, SDO 100 200 ps

P-P

tr,t

f

Rise time, Fall time 20%–80%, (Notes 4, 5) SDO, SDO 500 800 1500 ps

Output overshoot SDO, SDO

1%

t

LOCK

Lock time 270 Mbps, (Notes 5, 7) 75 µs

t

SU

Setup time

Figure 3

DNto P

CLK

32 ns

t

HLD

Hold time

Figure 3

DNfrom P

CLK

1.5 1 ns

L

GEN

Output inductance (Note 4) SDO, SDO 6nH

R

GEN

Output resistance (Note 4) SDO, SDO 25k Ω

CLC020

www.national.com3

AC Electrical Characteristics (Continued)

Note 1: “Absolute Maximum Ratings” are those parameter values beyond which the life and operation of the device cannot be guaranteed. The stating herein of

these maximums shall not be construed to imply that the device can or should be operated at or beyond these values. The table of “Electrical Characteristics” specifies acceptable device operating conditions.

Note 2: Current flow into device pins is defined as positive. Current flow out of device pins is defined as negative. All voltages are stated referenced to V

SS

=0V.

Note 3: Typical values are stated for V

DD

= +5.0V and TA= +25˚C.

Note 4: Specification is guaranteed by design.

Note 5: R

L

=75Ω, AC-coupled@270 M

bps,RREF

= 1.69 kΩ 1%, See

Test Loads

and

Figure 2

.

Note 6: CLC020 mounted in the SD020EVK board, configured in BIST mode (NTSC color bars) with P

CLK

= 27MHz derived from Tektronix TG2000 black-burst ref-

erence. Timing jitter measured with Tektronix VM700T using jitter measurement FFT mode, frame rate, 1kHz filter bandwidth, Hanning window.

Note 7: Measured from rising-edge of first P

CLK

cycle until Lock Detect output goes high (true).

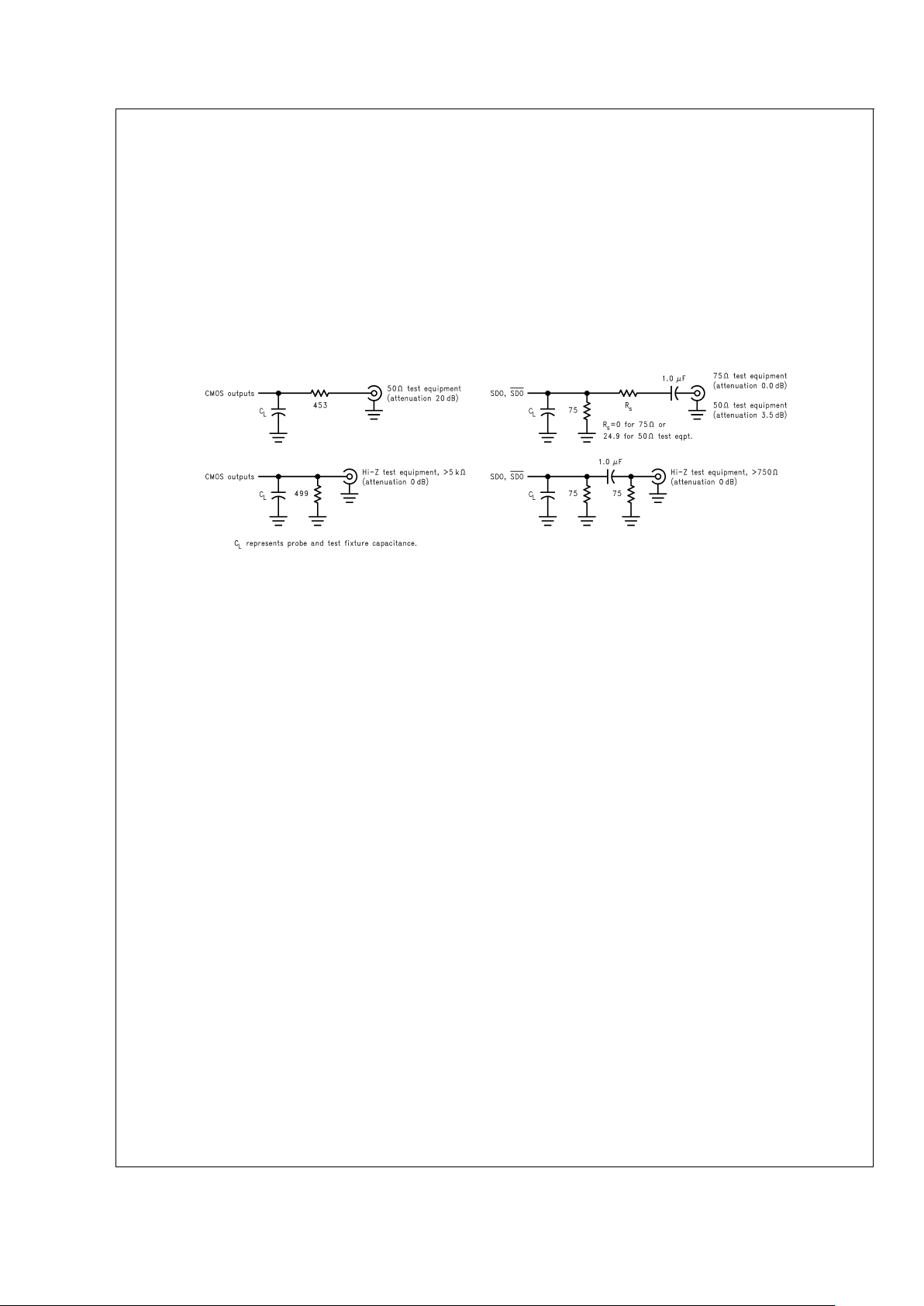

Test Loads

DS100917-3

All resistors in Ohms, 1% tolerance.

FIGURE 1. Test Loads

CLC020

www.national.com 4

Test Loads (Continued)

Timing Diagram

Device Operation

The CLC020 SMPTE 259M Digital Video Serializer is used in

digital video signal origination and processing equipment:

cameras, video tape recorders, telecines, video test equipment and others. It converts parallel component or composite digital video signals into serial format. Logic levels within

this equipment are normally TTL-compatible as produced by

CMOS or bipolar logic devices. The encoder outputs

ECL-compatible serial digital video (SDV) signals conforming to SMPTE 259M-1997. The CLC020 operates at all standard SMPTE and ITU-R parallel data rates.

DS100917-4

FIGURE 2. Test Circuit

DS100917-5

FIGURE 3. Setup and Hold Timing

CLC020

www.national.com5

Loading...

Loading...