NSC ADC16061CCVT Datasheet

January 2000

ADC16061

Self-Calibrating 16-Bit, 2.5 MSPS, 390 mW A/D Converter

ADC16061 Self-Calibrating 16-Bit, 2.5 MSPS, 390 mW A/D Converter

General Description

The ADC16061 is a self-calibrating 16-bit, 2.5 Megasample

per secondanalog to digital converter. It operates on a single

+5V supply, consuming just 390mW (typical).

The ADC16061 provides an easy and affordable upgrade

from 12 bit and 14 bit converters. The ADC16061 may also

be used to replace many hybrid converters with a resultant

saving of space, power and cost.

The ADC16061 operates with excellent dynamic performance at input frequencies up to

calibration feature of theADC16061 can be used to get more

consistent and repeatable results over the entire operating

temperature range. On-command self-calibration reduces

many of the effects of temperature-induced drift, resulting in

more repeatable conversions.

The Power Down feature reduces power consumption to

less than 2mW.

TheADC16061 comes in aTQFP and is designed to operate

over the commercial temperature range of 0˚C to +70˚C.

1

⁄2the clock frequency.The

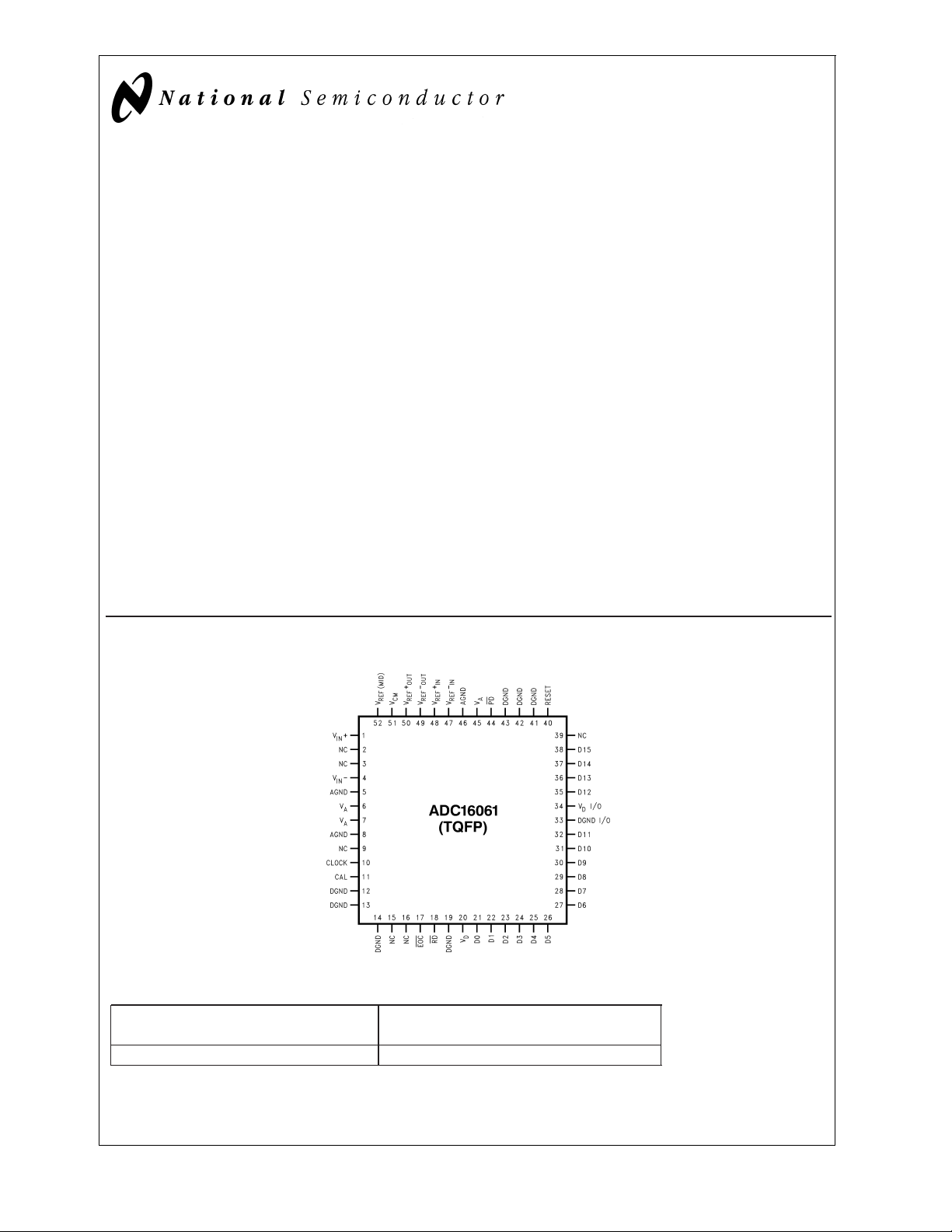

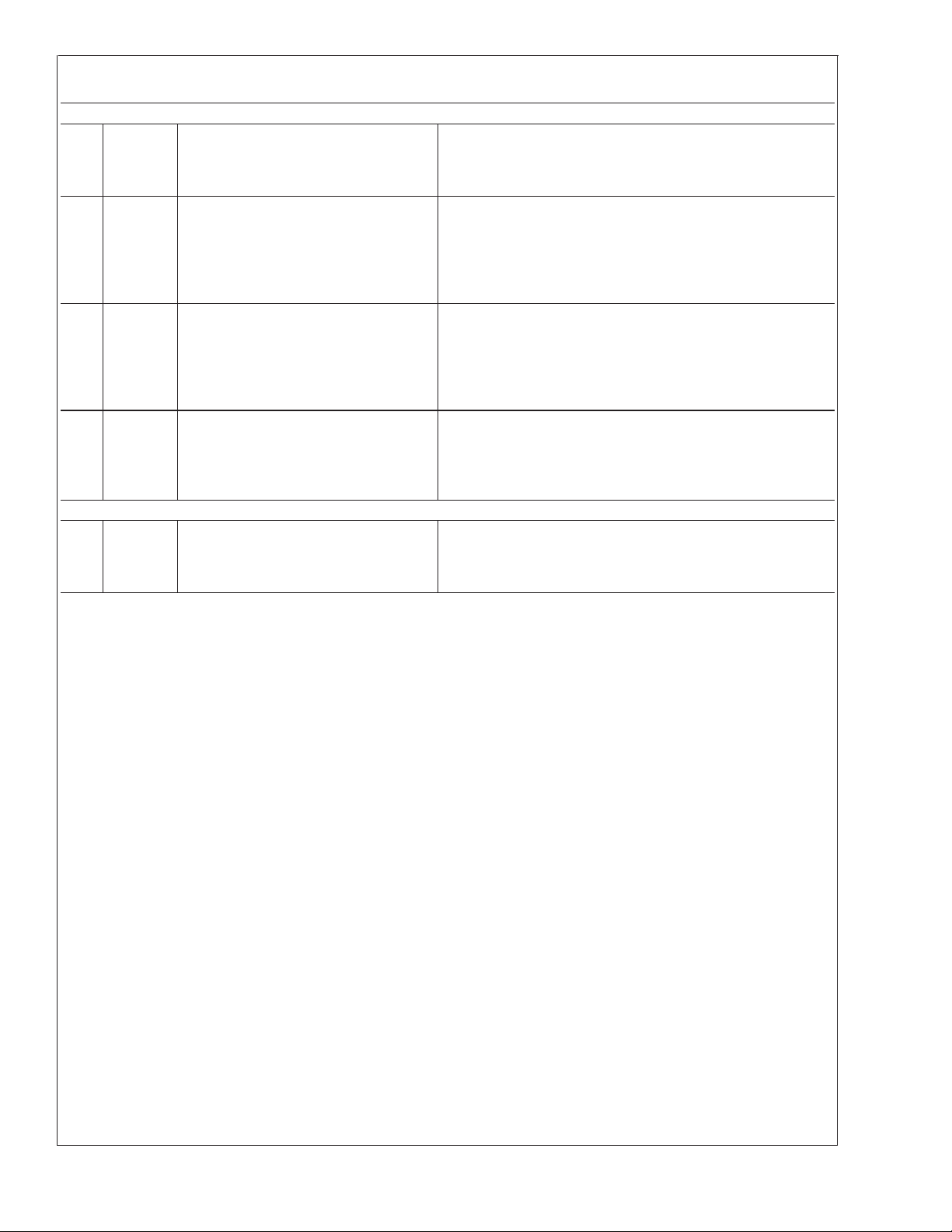

Connection Diagram

Features

n Single +5V Operation

n Self Calibration

n Power Down Mode

Key Specifications

n Resolution 16 Bits

n Conversion Rate 2.5 Msps (min)

n DNL 1.0 LSB (typ)

n SNR (f

n Supply Voltage +5V

n Power Consumption 390mW (typ)

= 500 kHz) 80 dB (typ)

IN

±

Applications

n PC-Based Data Acquisition

n Document Scanners

n Digital Copiers

n Film Scanners

n Blood Analyzers

n Sonar/Radar

%

5

DS100889-1

Ordering Information

Commercial

(0˚C ≤ TA ≤ +70˚C)

ADC16061CCVT VEG52A 52 Pin Thin Quad Flat Pack

© 2000 National Semiconductor Corporation DS100889 www.national.com

Package

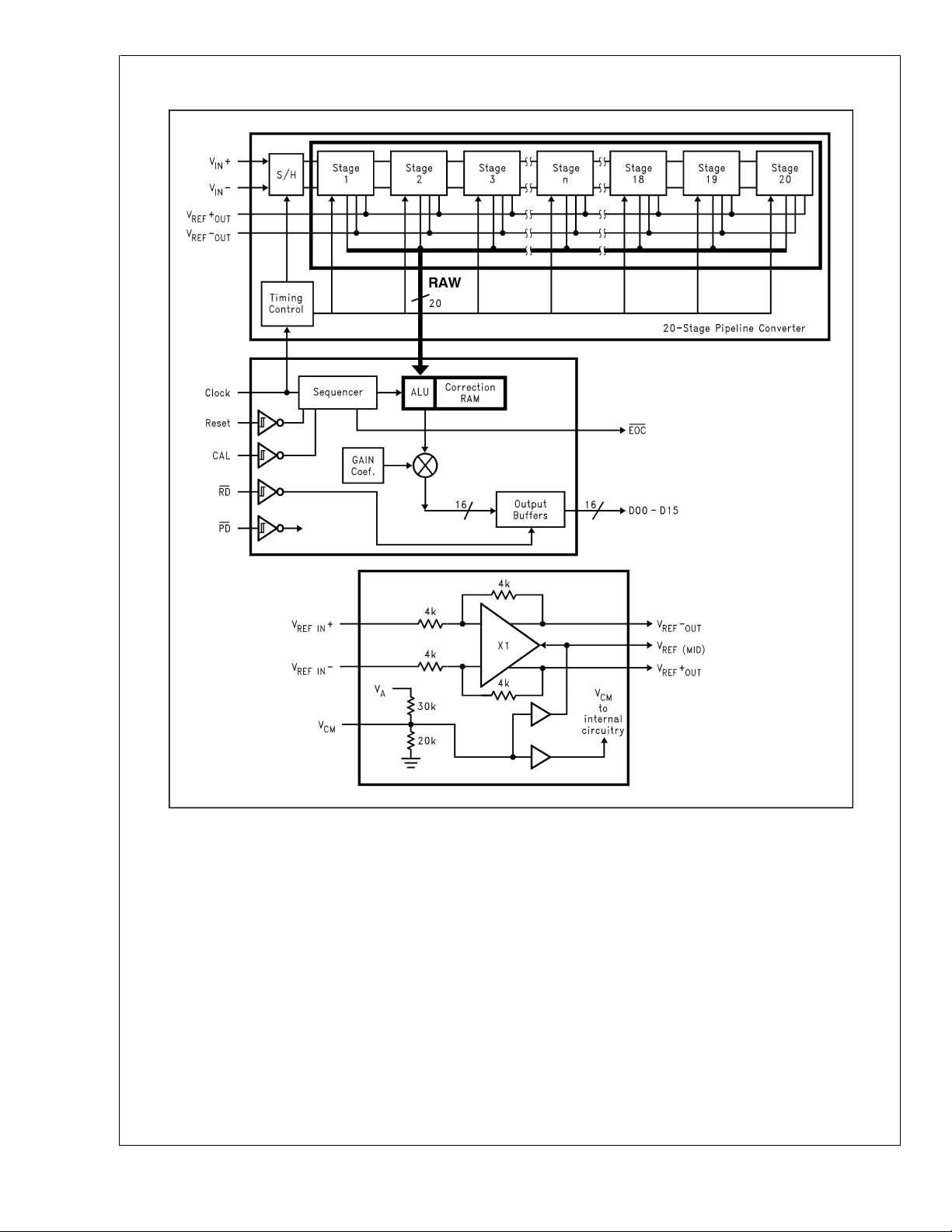

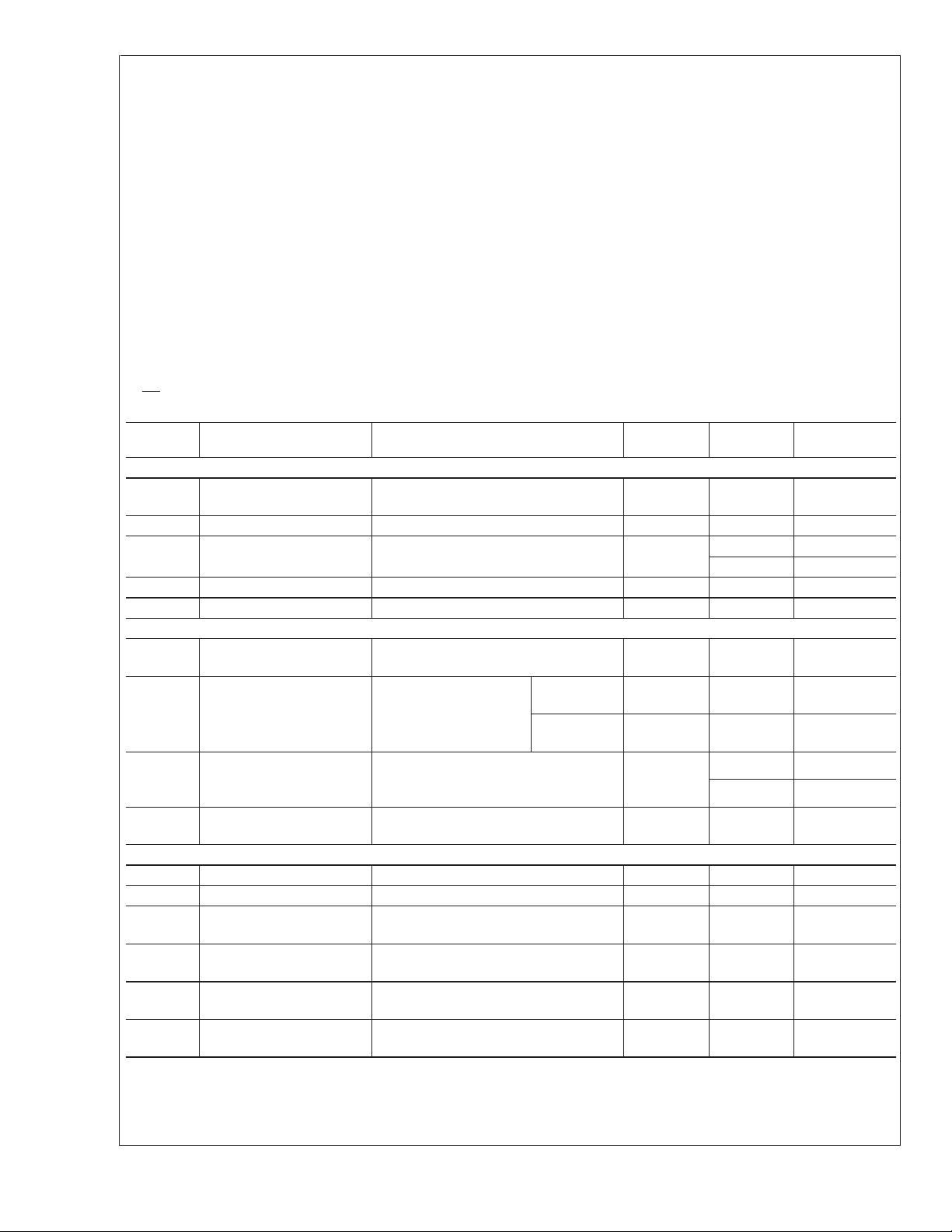

Block Diagram

ADC16061

www.national.com 2

DS100889-2

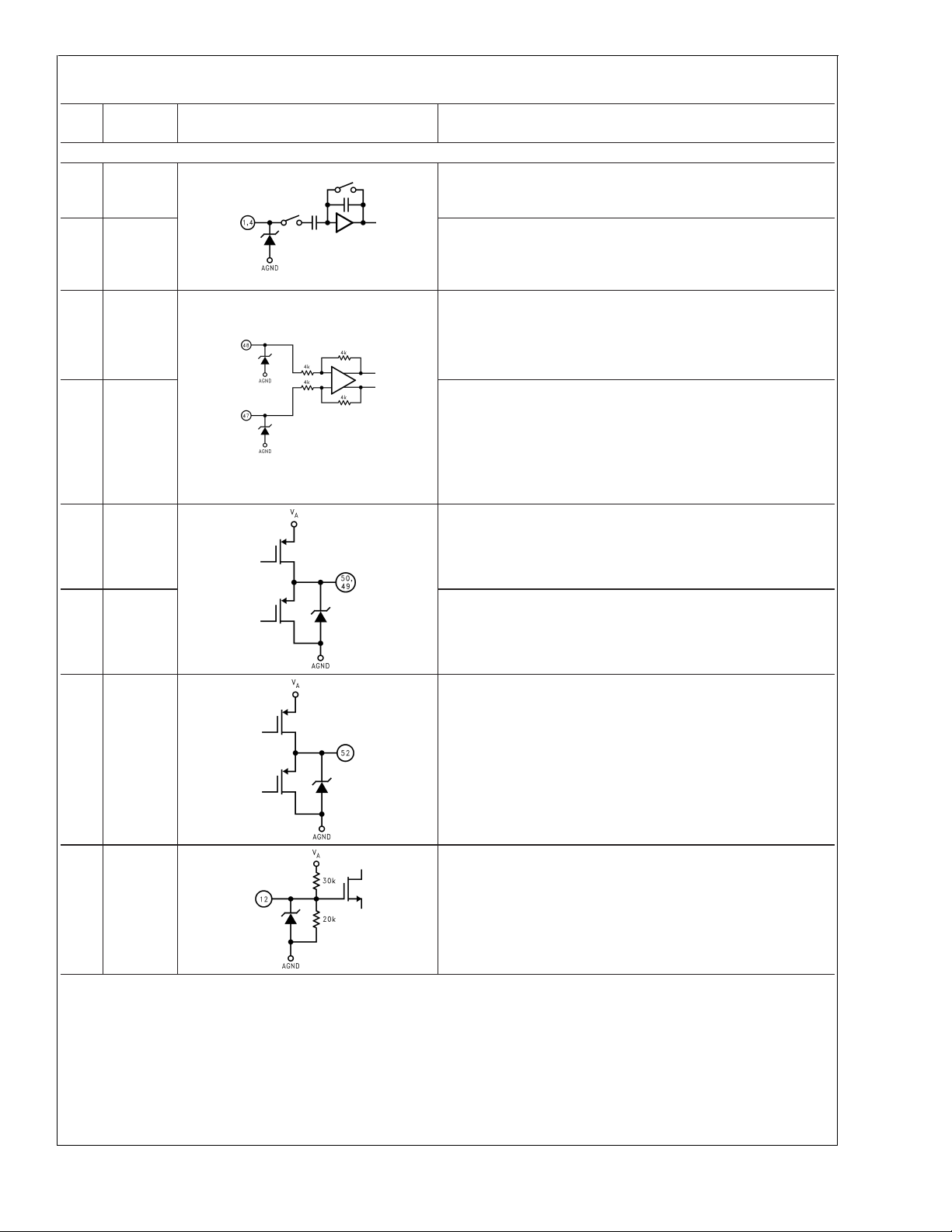

Pin Descriptions and Equivalent Circuits

ADC16061

Pin

Symbol Equivalent Circuit

No.

Analog I/O

1V

4V

48 V

47 V

50 V

IN

IN

REF+IN

REF−IN

REF+OUT

Description

Non-Inverting analog signal Input. With a 2.0V reference voltage

+

and a 2.0V common mode voltage, V

, the input signal voltage

CM

range is from 1.0 volt to 3.0 Volts.

Inverting analog signal Input. With a 2.0V reference voltage and a

−

2.0V common mode voltage, V

from 1.0 Volt to 3.0 Volts. The input signal should be balanced for

, the input signal voltage range is

CM

best performance.

Positive reference input. This pin should be bypassed to AGND

with a 0.1 µF monolithic capacitor.

+ minus V

V

REF

maximum of 2.2V. The full-scale input voltage is equal to V

minus V

REF−IN

should be a minimum of 1.8V and a

REF− IN

.

REF+IN

Negative reference input. In most applications this pin should be

connected to AGND and the full reference voltage applied to

V

REF+IN

. If the application requires that V

REF−IN

be offset from

AGND, this pin should be bypassed to AGND with a 0.1 µF

monolithic capacitor. V

REF+IN

minus V

REF− IN

should be a

minimum of 1.8V and a maximum of 2.2V. The full-scale input

voltage is equal to V

REF+IN

minus V

REF−IN

.

Output of the high impedance positive reference buffer. With a

2.0V reference input, and with a V

of 2.0V, this pin will have a

CM

3.0V output voltage. This pin should be bypassed to AGND with a

0.1 µF monolithic capacitor in parallel with a 10 µF capacitor.

49 V

REF−OUT

52 V

REF (MID)

51 V

CM

The output of the negative reference buffer. With a 2.0V reference

andaV

of 2.0V, this pin will have a 1.0V output voltage. This

CM

pin should be bypassed to AGND with a 0.1 µF monolithic

capacitor in parallel with a 10 µF capacitor.

Output of the reference mid-point, nominally equal to 0.4 V

A

(2.0V). This pin should be bypassed to AGND with a 0.1 µF

monolithic capacitor. This voltage is derived from V

CM

.

Input to the common mode buffer, nominally equal to 40%of the

supply voltage (2.0V). This pin should be bypassed to AGND with

a 0.1 µF monolithic capacitor. Best performance is obtained if this

pin is driven with a low impedance source of 2.0V.

www.national.com3

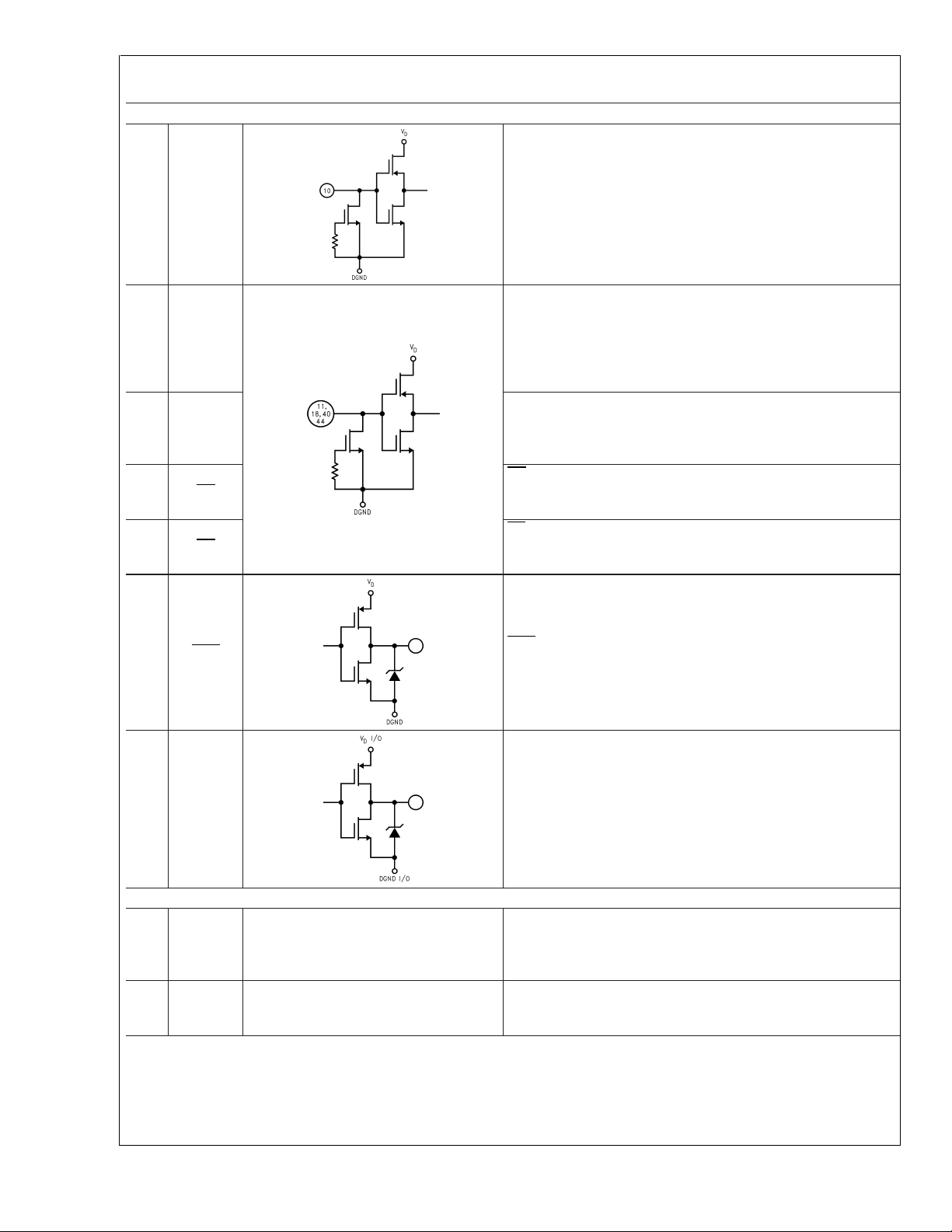

Pin Descriptions and Equivalent Circuits (Continued)

Digital I/O

ADC16061

Digital clock input. The input voltage is captured tADafter the fall of

10 CLOCK

11 CAL

40 RESET

18 RD

44 PD

the clock signal. The range of frequencies for this input is 300 kHz

to 2.5 MHz. The clock frequency should not be changed or

interrupted during conversion or while reading data output.

CAL is a level-sensitive digital input that, when pulsed high for at

least two clock cycles, puts the ADC into the CALIBRATE mode.

Calibration should be performed upon ADC power-up (after

asserting a reset) and each time the temperature changes by more

than 50˚C since the ADC16061 was last calibrated. See Section

2.3 for more information.

RESET is a level-sensitive digital input that, when pulsed high for

at least 2 CLOCK cycles, results in the resetting of the ADC. This

reset pulse must be applied after ADC power-up, before

calibration.

RD is the (READ) digital input that, when low, enables the output

data buffers. When this input pin is high, the output data bus is in

a high impedance state.

PD is the Power Down input that, when low, puts the converter

into the power down mode. When this pin is high, the converter is

in the active mode.

17 EOC

21-32

35-38

Analog Power

6, 7,

5, 8,

45

46

D00-15

V

AGND

EOC is a digital output that, when low, indicates the availability of

new conversion results at the data output pins.

Digital data outputs that make up the 16-bit TRI-STATE conversion

results. D00 is the LSB, while D15 is the MSB (SIGN bit) of the

two’s complement output word.

Positive analog supply pins. These pins should be connected to a

A

clean, quiet +5V source and bypassed to AGND with 0.1 µF

monolithic capacitors in parallel with 10 µF capacitors, both located

within 1 cm of these power pins.

The ground return for the analog supply. AGND and DGND should

be connected together directly beneath the ADC16061 package.

See Section 5 (Layout and grounding) for more details).

www.national.com 4

Pin Descriptions and Equivalent Circuits (Continued)

Digital Power

Positive digital supply pin. This pin should be connected to the

20 V

12,

13,

14,

19,

DGND

41,

42, 43

34 V

D

33 DGND I/O

NC

2, 3,

9, 15,

NC

16, 39

D

I/O

same clean, quiet +5V source as is V

with a 0.1 µF monolithic capacitor in parallel with a 10µF capacitor,

both located within 1 cm of the power pin.

The ground return for the digital supply. AGND and DGND should

be connected together directly beneath the ADC16061 package.

See Section 5 (Layout and Grounding) for more details.

Positive digital supply pin for the ADC16061’s output drivers. This

pin should be connected to a +3V to +5V source and bypassed to

DGND I/O with a 0.1 µF monolithic capacitor. If the supply for this

pin is different from the supply used for V

be bypassed with a 10 µF capacitor. All bypass capacitors should

be located within 1 cm of the supply pin.

The ground return for the digital supply for the ADC16061’s output

drivers. This pin should be connected to the system digital ground,

but not be connected in close proximity to the ADC16061’s DGND

or AGND pins. See Section 5.0 (Layout and Grounding) for more

details.

All pins marked NC (no connect) should be left floating. Do not

connect the NC pins to ground, power supplies, or any other

potential or signal. These pins are used for test in the

manufacturing process.

and bypassed to DGND

A

and VD, it should also

A

ADC16061

www.national.com5

Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required,

please contact the National Semiconductor Sales Office/

ADC16061

Distributors for availability and specifications.

Supply Voltage (V

A,VD,VD

Voltage on Any I/O Pin −0.3V to V

Input Current at Any Pin (Note 3)

Package Input Current (Note 3)

Power Dissipation at T

ESD Susceptibility (Note 5)

Human Body Model 1500V

Machine Model 200V

Soldering Temp., Infrared, 10 sec. (Note 6) 300˚C

I/O) 6.5V

=

25˚C (Note 4)

A

+

+0.3V

±

25mA

±

50mA

Storage Temperature −65˚C to +150˚C

Operating Ratings(Notes 1, 2)

Operating Temperature

Range

V

A,VD

V

I/O 2.7V to V

D

V

− IN 1.0V to 3.0V

REF

V

− IN AGND to 0.1V

REF

Digital Inputs −0.05V to V

|V

| ≤100 mV

A−VD

|AGND - DGND | 0V to 100 mV

0˚C ≤ T

≤ +70˚C

A

+4.75V to +5.25V

+ 0.05V

D

D

Converter Electrical Characteristics

+

=

=

The following specifications apply for AGND=DGND=DGND I/O=0V, V

PD=+5V, V

=

T

=

T

A

T

J

MIN

REF+ IN

to T

=

+2.0V, V

MAX

REF− IN

: all other limits T

=

AGND, f

A

CLK

=

=

T

25˚C(Notes 7, 8, 9)

J

=

2.5 MHz, C

=

L

V

50 pF/pin. After Auto-Cal. Boldface limits apply for

Symbol Parameter Conditions

Static Converter Characteristics

Resolution with No

Missing Codes

INL Integral Non Linearity At 16 Bits

DNL Differential Non Linearity At 16 Bits

Full-Scale Error

Zero Offset Error +0.1

Reference and Analog Input Characteristics

V

IN

Input Voltage Range

(V

IN+−VIN−

)

(CLK

C

IN

Input Capacitance V

=

1.0V + 0.7Vrms

IN

LOW)

(CLK

HIGH)

Reference Voltage

V

REF

Range [( V

(V

REF−IN

)] (Note 14)

REF+IN

)−

Reference Input

Resistance

Dynamic Converter Characteristics

BW Full Power Bandwidth 8 MHz

SNR Signal-to-Noise Ratio f

SINAD

THD

SFDR

IMD

Signal-to-Noise &

Distortion

Total Harmonic

Distortion

Spurious Free Dynamic

Range

Intermodulation

Distortion

=

500 kHz 80 dB

IN

=

500 kHz 79 dB

f

IN

=

f

500 kHz

IN

=

f

500 kHz

IN

=

f

95 kHz

IN1

=

105 kHz

f

IN2

A

=

V

+5.0V, V

D

Typical

(Note 10)

I/O=3.0V or 5.0V,

D

Limits

(Note 11)

15 Bits(min)

±

3

±

1

±

0.6 3.0

2.0

±

9 LSB(max)

+3 LSB(max)

−2 LSB(min)

±

0.7

1.8

2.2

12 pF

28 pF

1.8 V(min)

2.00

2.2 V(max)

3.5 KΩ

−88 dB

91 dB

−97 dB

Units

%

FS(max)

%

FS(max)

V(min)

V(max)

www.national.com 6

Loading...

Loading...