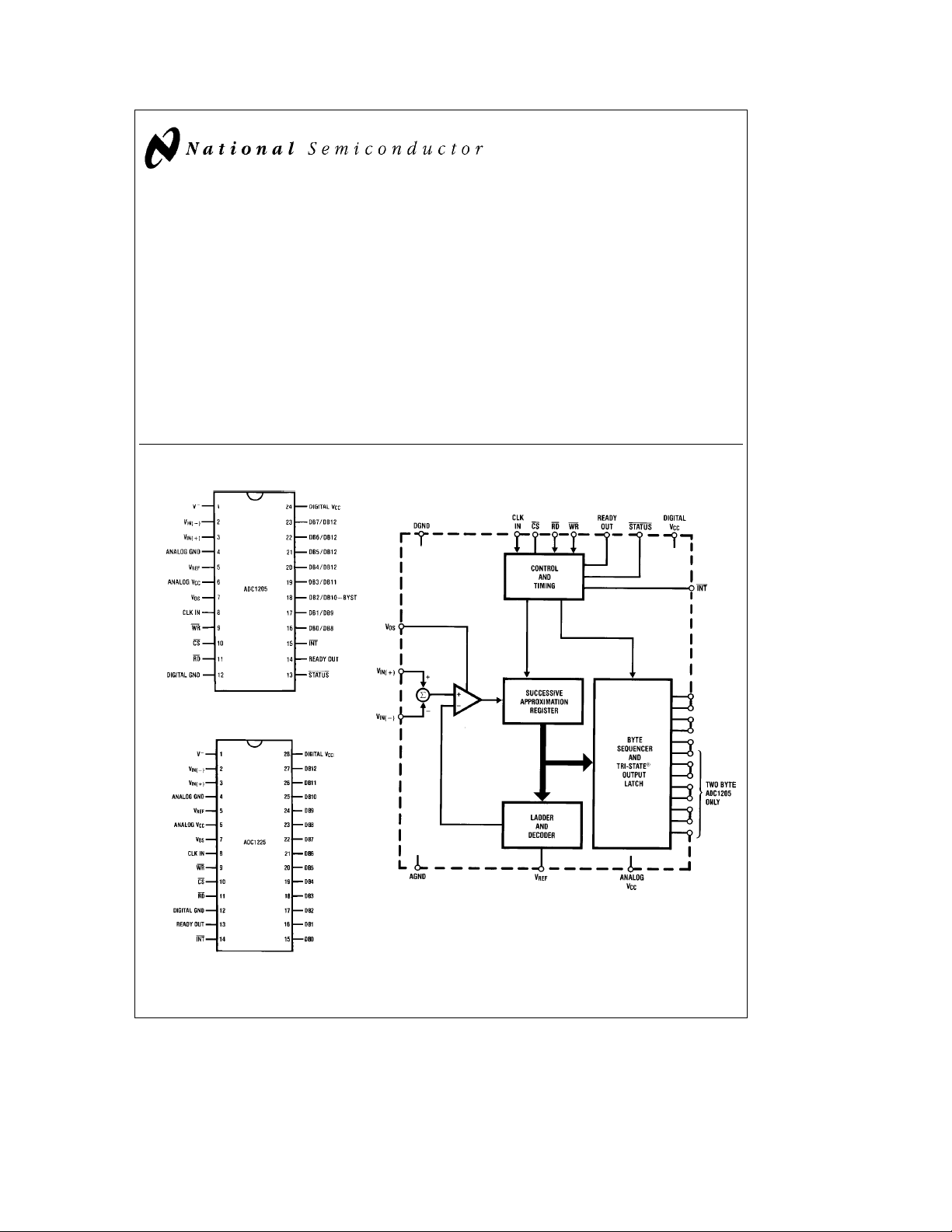

ADC1205/ADC1225 12-Bit Plus Sign

mP Compatible A/D Converters

General Description

The ADC1205 and ADC1225 are CMOS, 12-bit plus sign

successive approximation A/D converters. The 24-pin

ADC1205 outputs the 13-bit data result in two 8-bit bytes,

formatted high-byte first with sign extended. The 28-pin

ADC1225 outputs a 13-bit word in parallel for direct interface to a 16-bit data bus.

Negative numbers are represented in 2’s complement data

format. All digital signals are fully TTL and MOS compatible.

A unipolar input (0V to 5V) can be accommodated with a

single 5V supply, while a bipolar input (

b

5V toa5V) re-

quires the addition of a 5V negative supply.

The ADC1205C and ADC1225C have a maximum non-linearity of 0.0224% of Full Scale.

Connection and Functional Diagrams

Dual-In-Line Package

Key Specifications

Y

ResolutionÐ12 bits plus sign

Y

Linearity ErrorÐg1 LSB

Y

Conversion TimeÐ100 ms

Features

Y

Compatible with all mPs

Y

True differential analog voltage inputs

Y

0V to 5V analog voltage range with single 5V supply

Y

TTL/MOS input/output compatible

Y

Low powerÐ25 mW max

Y

Standard 24-pin or 28-pin DIP

ADC1205/ADC1225 12-Bit Plus Sign mP Compatible A/D Converters

June 1994

Top View

TL/H/5676– 1

Dual-In-Line Package

TL/H/5676– 3

See Ordering Information

Top View

TRI-STATEÉis a registered trademark of National Semiconductor Corporation.

C

1995 National Semiconductor Corporation RRD-B30M115/Printed in U. S. A.

TL/H/5676– 2

TL/H/5676

Absolute Maximum Ratings (Notes1&2)

If Military/Aerospace specified devices are required,

please contact the National Semiconductor Sales

Office/Distributors for availability and specifications.

Supply Voltage (DV

Negative Supply Voltage (V

Logic Control Inputs

Voltage at Analog Inputs

[

V

IN(a),VIN(b)

Voltage at All Outputs, V

Input Current per Pin

Input Current per Package

Storage Temperature Range

Package Dissipation at T

Lead Temp. (Soldering, 10 seconds) 300

and AVCC) 6.5V

CC

b

)

]

REF,VOS

(V

e

25§C 875 mW

A

b

b

)b0.3V to V

b

0.3V to (V

b

65§Ctoa150§C

b

0.3V toa15V

15V to GND

a

0.3V

CC

a

0.3)V

CC

g

5mA

g

20mA

§

Operating Conditions (Notes1&2)

Temperature Range T

ADC1205CCJ, ADC1225CCD

ADC1205CCJ-1, ADC1225CCD-1 0

Supply Voltage (DV

Negative Supply Voltage (Vb)

C

and AVCC) 4.5 VDCto 6.0 V

CC

b

40§CsT

s

T

MIN

A

CsT

§

b

15V to GND

s

T

A

MAX

s

a

85§C

s

70§C

A

DC

ESD Susceptibility (Note 12) 800V

Electrical Characteristics

MIN

Typ

(Note 8)

b

eb

5V for bipolar input range, or

to T

; all other limits T

MAX

Tested Design

Limit Limit

g

1

g

2

g

30

g

2

g

2

g

30

g

2

s

IN(a)

s

IN(a)

A

g

1 LSB

g

2 LSB

g

30 LSB

g

(/2 LSB

g

2 LSB

g

2 LSB

g

30 LSB

g

2 LSB

5.05V;

5.05V;

e

Limit

Units

T

J

e

The following specifications apply for DV

b

e

V

GND for unipolar input range unless otherwise specified. Bipolar input range is defined asb5.05VsV

b

5.05VsV

b

0.05VsV

e

25§C (Notes 3, 4, 5, 6, 7).

IN(b)

IN(b)

s

5.05V andlV

s

5.05V andlV

IN(a)

IN(a)

CC

b

b

V

e

AV

5V, V

CC

s

V

IN(b)

5.05V. Unipolar input range is defined asb0.05VsV

l

IN(b)

s

5.05V. Boldface limits apply from T

l

REF

e

5V, f

CLK

e

1.0 MHz, V

ADC1205CCJ, ADC1225CCD ADC1205CCJ-1, ADC1225CCD-1

Parameter Conditions

Typ

(Note 8)

Tested Design

Limit Limit

(Note 9) (Note 10) (Note 9) (Note 10)

CONVERTER CHARACTERISTICS

Linearity Error Unipolar Input

ADC1205CCJ, ADC1225CCD Range

ADC1205CCJ-1, ADC1225CCD-1 (Note 11)

Unadjusted Zero Error Unipolar Input

Unadjusted Positive and Negative Unipolar Input

Full-Scale Error Range

Negative Full-Scale Error Unipolar Input

Linearity Error Bipolar Input

ADC1205CCJ, ADC1225CCD Range

ADC1205CCJ-1, ADC1225CCD-1 (Note 11)

Unadjusted Zero Error Bipolar Input

Unadjusted Positive and Negative Bipolar Input

Full-Scale Error Range

Negative Full-Scale Error Bipolar Input

Maximum Gain Temperature 6 15 6 15 ppm/§C

Coefficient

Maximum Offset Temperature 0.5 1.5 0.5 1.5 ppm/§C

Coefficient

Minimum V

Maximum V

Input Resistance 4.0 2 4.0 2 2 kX

REF

Input Resistance 4.0 8 4.0 8 8 kX

REF

Range

Range, Full

Scale Adj. to

Zero

Range

Range, Full

Scale Adj. to

Zero

g

1 LSB

g

2

g

30

g

(/2

g

2 LSB

g

2

g

30

g

2

2

Electrical Characteristics (Continued)

e

e

AV

The following specifications apply for DV

b

e

V

GND for unipolar input range unless otherwise specified. Bipolar input range is defined asb5.05VsV

b

5.05VsV

b

0.05VsV

e

25§C (Notes 3, 4, 5, 6, 7).

IN(b)

IN(b)

s

5.05V andlV

s

5.05V andlV

IN(a)

IN(a)

CC

b

V

IN(b)

b

V

IN(b)

5V, V

CC

s

5.05V. Unipolar input range is defined asb0.05VsV

l

s

5.05V. Boldface limits apply from T

l

REF

e

5V, f

CLK

e

1.0 MHz, V

ADC1205CCJ, ADC1225CCD ADC1205CCJ-1, ADC1225CCD-1

Parameter Conditions

Typ

(Note 8)

Tested Design

Limit Limit

(Note 9) (Note 10) (Note 9) (Note 10)

CONVERTER CHARACTERISTICS (Continued)

Minimum Analog Input Unipolar Input GND-0.05 GND-0.05 GND-0.05 V

Voltage Range

b

Bipolar Input

Range

Maximum Analog Input Unipolar Input V

Voltage Range

Bipolar Input V

Range

DC Common-Mode Error

Power Supply Sensitivity AV

5Vg5%,

V

b

CC

eb

e

DV

5Vg5%

CC

a

0.05 V

CC

g

(/8

e

Zero Error

Positive and Negative

b

V

0.05

CC

a

0.05 V

CC

g

(/2

g

*/4

g

*/4

Full-Scale Error

Linearity Error

g

(/4

DIGITAL AND DC CHARACTERISTICS

V

, Logical ‘‘1’’ Input V

IN(1)

Voltage (Min) All Inputs except

e

5.25V, 2.0 2.0 2.0 V

CC

CLK IN

V

, Logical ‘‘0’’ Input V

IN(0)

Voltage (Max) All Inputs except

e

4.75V, 0.8 0.8 0.8 V

CC

CLK IN

I

, Logical ‘‘1’’ Input V

IN(1)

Current (Max)

I

, Logical ‘‘0’’ Input V

IN(0)

Current (Max)

a

V

(Min), Minimum Positive- CLK IN 3.1 2.7 3.1 2.7 2.7 V

T

Going Threshold Voltage

a

V

(Max), Maximum Positive- CLK IN 3.1 3.5 3.1 3.5 3.5 V

T

Going Threshold Voltage

b

V

(Min), Minimum Negative- CLK IN 1.8 1.4 1.8 1.4 1.4 V

T

Going Threshold Voltage

b

V

(Max), Maximum Negative- CLK IN 1.8 2.1 1.8 2.1 2.1 V

T

Going Threshold Voltage

VH(Min), Minimum Hysteresis CLK IN 1.3 0.6 1.3 0.6 0.6 V

a

[

V

(Min)bV

T

VH(Max), Maximum Hysteresis CLK IN 1.3 2.1 1.3 2.1 2.1 V

a

[

V

(Max)bV

T

T

b

T

(Max)

b

(Min)

]

]

e

5V 0.005 1 0.005 1 mA

IN

e

0V

IN

b

0.005

b

1

b

MIN

Typ

(Note 8)

g

(/8

b

0.005

eb

5V for bipolar input range, or

to T

MAX

IN(a)

IN(a)

; all other limits T

Tested Design

Limit Limit

b

b

V

0.05bV

CC

CC

C

a

a

g

(/2

g

*/4

g

*/4

g

(/4

0.05 V

0.05 V

CC

CC

CC

g

g

g

g

s

5.05V;

s

5.05V;

e

A

b

0.05 V

a

0.05 V

a

0.05 V

(/2 LSB

*/4 LSB

*/4 LSB

(/4 LSB

b

1 mA

T

Limit

Units

J

3

Electrical Characteristics (Continued)

e

e

AV

The following specifications apply for DV

b

e

V

GND for unipolar input range unless otherwise specified. Bipolar input range is defined asb5.05VsV

b

5.05VsV

b

0.05VsV

e

25§C (Notes 3, 4, 5, 6, 7).

IN(b)

IN(b)

s

5.05V andlV

s

5.05V andlV

IN(a)

IN(a)

CC

b

V

b

V

IN(b)

5V, V

CC

s

5.05V. Unipolar input range is defined asb0.05VsV

l

IN(b)

s

5.05V. Boldface limits apply from T

l

ADC1205CCJ, ADC1225CCD ADC1205CCJ-1, ADC1225CCD-1

Parameter Conditions

(Note 8)

DIGITAL AND DC CHARACTERISTICS (Continued)

V

, Logical ‘‘1’’ Output V

OUT(1)

Voltage (Min) I

V

, Logical ‘‘0’’ Output V

OUT(0)

Voltage (Max) I

I

, TRI-STATE Output Leakage V

OUT

Current (Max) V

I

, Output Source Current V

SOURCE

(Min)

I

, Output Sink Current (Min) V

SINK

DICC,DVCCSupply Current (Max) f

AICC,AVCCSupply Current (Max) f

Ib,VbSupply Current (Max) f

e

4.75V

CC

eb

360 mA 2.4 2.4 2.4 V

OUT

eb

I

10 mA 4.5 4.5 4.5 V

OUT

e

4.75V 0.4 0.4 0.4 V

CC

e

1.6 mA

OUT

e

0V

OUT

e

5V 0.01 3 0.01 0.3 3 mA

OUT

e

0V

OUT

e

5V 16 8.0 16 9.0 8.0 mA

OUT

e

1 MHz, CSe11 3 1 2.5 3 mA

CLK

e

1 MHz, CSe11 3 1 2.5 3 mA

CLK

e

1 MHz, CSe110 100 10 100 100 mA

CLK

b

e

REF

Tested Design

Typ

(Note 9) (Note 10) (Note 9) (Note 10)

0.01

b

12

e

5V, f

CLK

1.0 MHz, V

Limit Limit

b

3

b

6.0

MIN

(Note 8)

b

b

eb

5V for bipolar input range, or

to T

; all other limits T

MAX

0.01

12

Tested Design

Limit Limit

b

0.3

b

7.0

Typ

b

IN(a)

IN(a)

b

b

6.0 mA

s

5.05V;

s

5.05V;

e

T

A

Limit

Units

3 mA

J

AC Electrical Characteristics

e

e

e

The following specifications apply for DV

CC

AV

CC

5.0V, t

Parameter Conditions

f

, Clock Frequency MIN 1.0 0.3 MHz

CLK

Clock Duty Cycle MIN 40 %

TC, Conversion Time MIN 108 1/f

t

,WRPulse Width MAX 220 350 ns

W(WR)L

t

, Access Time (Delay from C

ACC

Falling Edge of RD

Output Data Valid) (Max)

t1H,t0H, TRI-STATE Control (Delay R

from Rising Edge of RD

Hi-Z State) (Max)

t

PD(READYOUT)

READYOUT Delay (Max)

t

RD or WR to Reset of INT 250 400 ns

PD(INT),

(Max)

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. DC and AC electrical specifications do not apply when operating

the device beyond its specified operating ratings.

Note 2: All voltages are measured with respect to ground, unless otherwise specified.

Note 3: A parasitic zener diode exists internally from AV

to

,RDor WR to 250 400 ns

MAX 1.0 1.5 MHz

MAX 60 %

MAX 109 1/f

MIN f

MAX f

to

e

1.0 MHz 108 ms

CLK

e

1.0 MHz 109 ms

CLK

e

100 pF 210 340 ns

L

e

e

2k, C

L

L

and DVCCto ground. This parasitic zener has a typical breakdown voltage of 7 VDC.

CC

e

t

20 ns and T

r

f

(Note 8)

100 pF 170 290 ns

Typ

e

25§C unless otherwise specified.

A

Tested Design

Limit Limit

(Note 9) (Note 10)

Limit

Units

CLK

CLK

4

AC Electrical Characteristics (Continued)

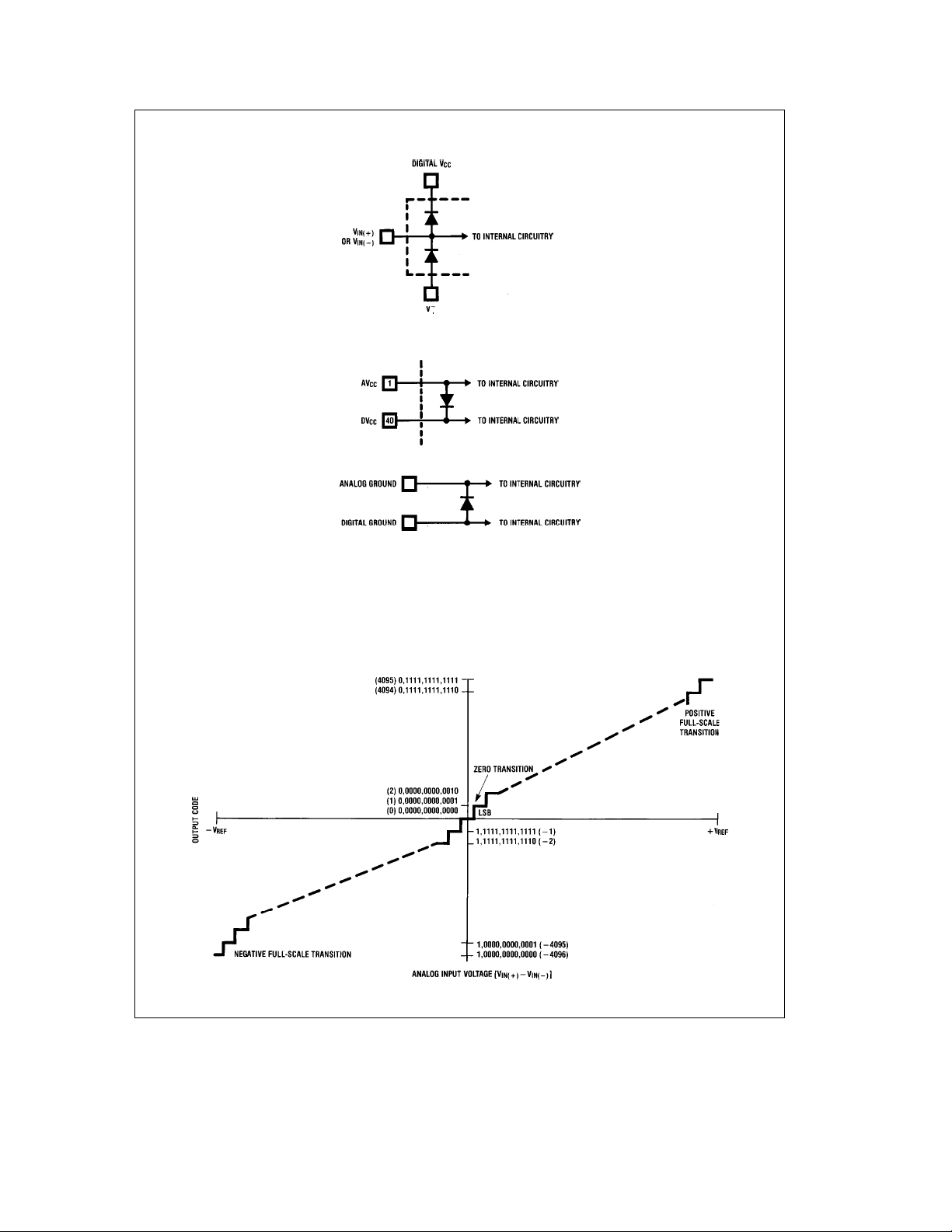

Note 4: Two on-chip diodes are tied to each analog input as shown below.

Errors in the A/D conversion can occur if these diodes are forward biased more than 50 mV. This means that if AVCCand DVCCare minimum (4.75 VDC) and Vbis

b

minimum (

Note 5: A diode exists between analog V

To guarantee accuracy, it is required that the AVCCand DVCCbe connected together to a power supply with separate bypass filters at each VCCpin.

Note 6: A diode exists between analog ground and digital ground.

To guarantee accuracy, it is required that the analog ground and digital ground be connected together externally.

Note 7: Accuracy is guaranteed at f

Note 8: Typicals are at 25

Note 9: Tested and guaranteed to National’s AOQL (Average Outgoing Quality Level).

Note 10: Guaranteed, but not 100% production tested. These limits are not used to calculate outgoing quality levels.

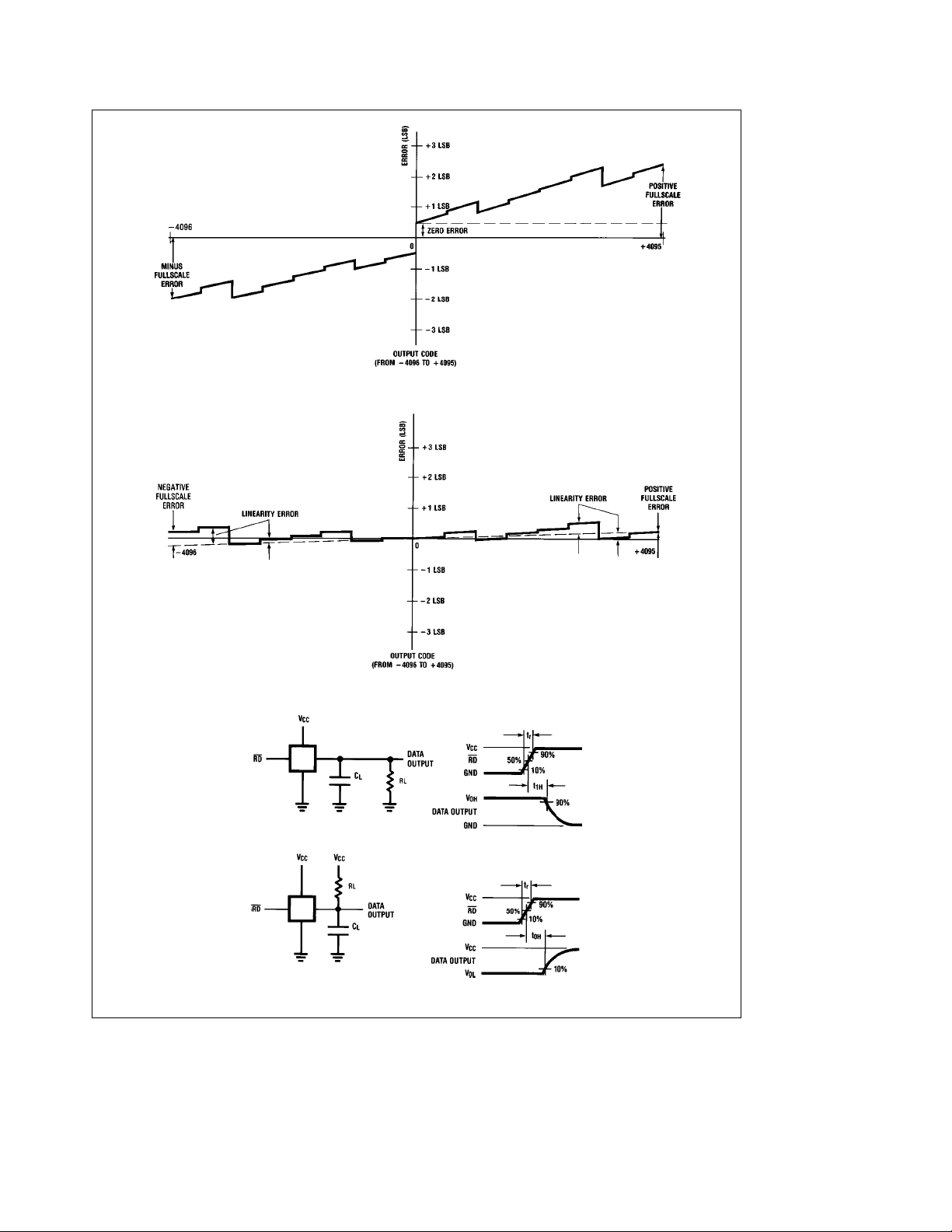

Note 11: Linearity error is defined as the deviation of the analog value, expressed in LSBs, from the straight line which passes through positive full scale and zero,

after adjusting zero error. (See

Note 12: Human body model; 100 pF discharged through a 1.5 kX resistor.

4.75VDC), full-scale must bes4.8VDC.

C and represent most likely parametric norm.

§

Figures 1b

and digital VC.

CC

e

1.0 MHz. At higher clock frequencies accuracy may degrade.

CLK

and1c).

TL/H/5676– 4

TL/H/5676– 20

TL/H/5676– 21

FIGURE 1a. Transfer Characteristic

5

TL/H/5676– 8

FIGURE 1b. Simplified Error Curve vs. Output Code Without Zero and Fullscale Adjustment

TL/H/5676– 22

FIGURE 1c. Simplified Error Curve vs. Output Code after Zero/Fullscale Adjustment

TL/H/5676– 7

FIGURE 2. TRI-STATE Test Circuits and Waveforms

6

TL/H/5676– 23

Loading...

Loading...