NSC ADC12062CIVF, ADC12062CIV, ADC12062BIVF, ADC12062BIV Datasheet

ADC12062

12-Bit, 1 MHz, 75 mW A/D Converter

with Input Multiplexer and Sample/Hold

December 1994

ADC12062 12-Bit, 1 MHz, 75 mW A/D Converter

with Input Multiplexer and Sample/Hold

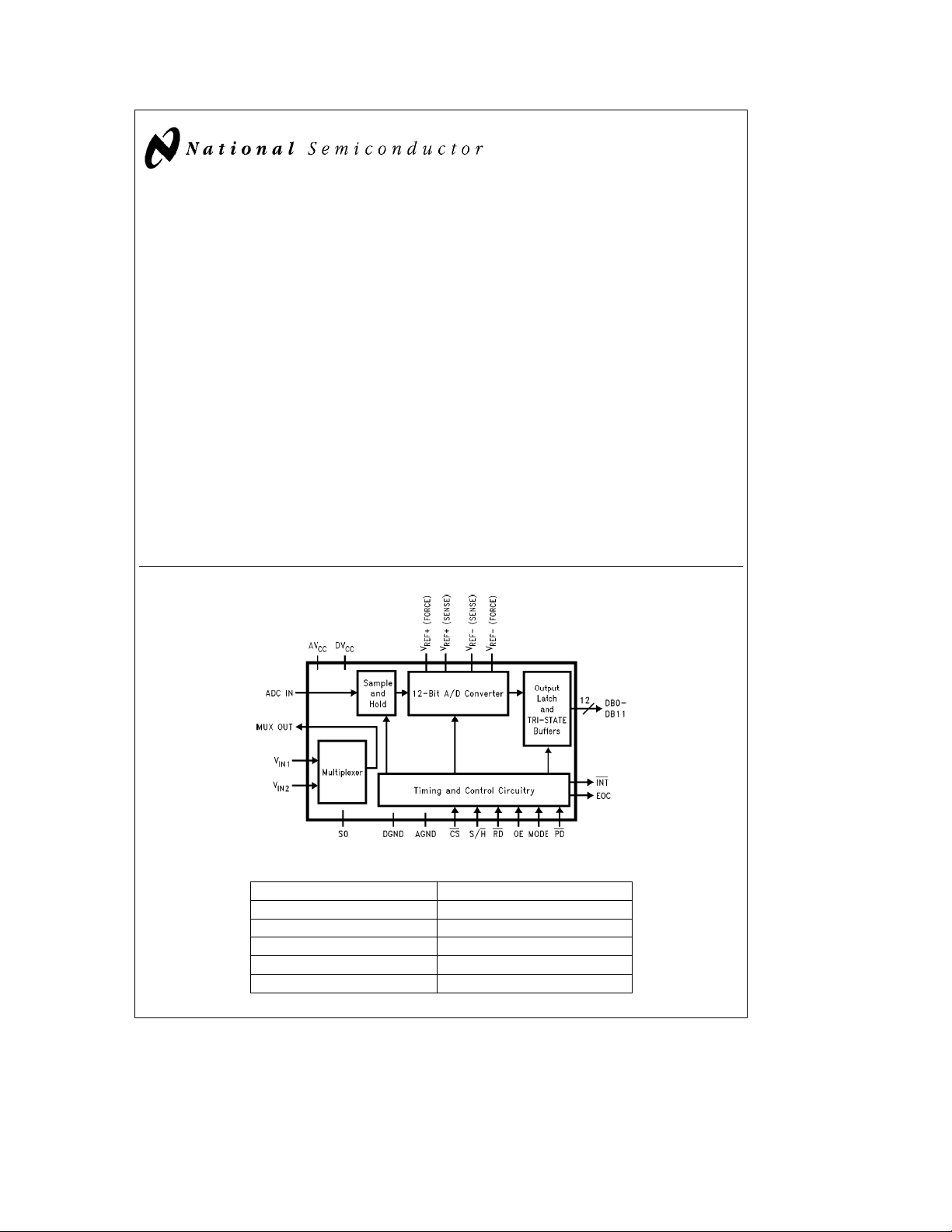

General Description

Using an innovative multistep conversion technique, the

12-bit ADC12062 CMOS analog-to-digital converter digitizes

signals at a 1 MHz sampling rate while consuming a maximum of only 75 mW on a single

a

5V supply. The

ADC12062 performs a 12-bit conversion in three lower-resolution ‘‘flash’’ conversions, yielding a fast A/D without the

cost and power dissipation associated with true flash approaches.

The analog input voltage to the ADC12062 is tracked and

held by an internal sampling circuit, allowing high frequency

input signals to be accurately digitized without the need for

an external sample-and-hold circuit. The multiplexer output

is available to the user in order to perform additional external signal processing before the signal is digitized.

When the converter is not digitizing signals, it can be placed

in the Standby mode; typical power consumption in this

mode is 100 mW.

Block Diagram

Features

Y

Built-in sample-and-hold

Y

Singlea5V supply

Y

Single channel or 2 channel multiplexer operation

Y

Low Power Standby mode

Key Specifications

Y

Sampling rate 1 MHz (min)

Y

Conversion time 740 ns (typ)

Y

Signal-to-Noise Ratio, f

Y

Power dissipation (f

Y

No missing codes over temperature Guaranteed

e

100 kHz 69.5 dB (min)

IN

e

1 MHz) 75 mW (max)

s

Applications

Y

Digital signal processor front ends

Y

Instrumentation

Y

Disk drives

Y

Mobile telecommunications

Y

Waveform digitizers

TL/H/11490– 1

Ordering Information

s

Industrial (b40§CsT

ADC12062BIV V44 Plastic Leaded Chip Carrier

ADC12062BIVF VGZ44A Plastic Quad Flat Package

ADC12062CIV V44 Plastic Leaded Chip Carrier

ADC12062CIVF VGZ44A Plastic Quad Flat Package

ADC12062EVAL Evaluation Board

TRI-STATEÉis a registered trademark of National Semiconductor Corporation.

C

1995 National Semiconductor Corporation RRD-B30M75/Printed in U. S. A.

TL/H/11490

a

85§) Package

A

Absolute Maximum Ratings (Notes 1, 2)

If Military/Aerospace specified devices are required,

please contact the National Semiconductor Sales

Office/Distributors for availability and specifications.

Supply Voltage (V

CC

DV

CC

Voltage at Any Input or Output

e

AVCC)

b

0.3V to V

b

0.3V toa6V

a

CC

0.3V

e

Input Current at Any Pin (Note 3) 25 mA

Package Input Current (Note 3) 50 mA

Power Dissipation (Note 4) 875 mW

ESD Susceptibility (Note 5) 2000V

Converter Characteristics The following specifications apply for DV

a

4.096V, V

T

MIN

to T

MAX

REFb(SENSE)

; all other limits T

e

AGND, and f

A

e

1 MHz, unless otherwise specified. Boldface limits apply for T

s

e

ea

T

25§C.

J

Symbol Parameter Conditions

Resolution 12 Bits

Differential Linearity Error T

Integral Linearity Error T

(Note 9)

Offset Error T

Full Scale Error T

Power Supply Sensitivity DV

(Note 15)

R

REF

V

REF(a)VREFa(SENSE)

V

REF(b)VREFb(SENSE)

V

IN

Reference Resistance

Input Voltage Range To V

Input Voltage AV

Input Voltage AGND V (min)

A

T

MIN

MIN

T

A

T

MIN

MIN

T

A

T

MIN

MIN

T

A

T

MIN

e

ea

ea

ea

CC

IN1,VIN2

25§C

to T

MAX

to T

MAX

25§C (CIV Suffix)

to T

MAX

to T

MAX

25§C (CIV Suffix)

to T

MAX

to T

MAX

25§C (CIV Suffix)

to T

MAX

e

AV

ADC IN Input Leakage AGND to AV

C

ADC

ADC IN Input Capacitance 25 pF

MUX On-Channel Leakage AGND to AV

MUX Off-Channel Leakage AGND to AV

C

MUX

Multiplexer Input Cap 7 pF

MUX Off Isolation f

e

100 kHz 92 dB

IN

Soldering Information (Note 6)

V Package, Infrared, 15 seconds

VF Package

Vapor Phase (60 seconds)

Infrared (15 seconds)

Storage Temperature Range

Maximum Junction Temperature (T

Operating Ratings (Notes 1, 2)

Temperature Range T

ADC12062BIV, ADC12062CIV,

ADC12062BIVF, ADC12062CIVF

Supply Voltage Range (DV

(Note 7) (Note 8) (Limit)

g

(BIV Suffix)

(CIV Suffix)

(BIV Suffix)

(CIV Suffix)

(BIV Suffix)

(CIV Suffix)

e

5Vg10%

CC

, or ADC IN AV

b

0.3V 0.1 3 mA (max)

CC

b

0.3V 0.1 3 mA (max)

CC

b

0.3V 0.1 3 mA (max)

CC

g

g

g

g

g

g

a

300§C

a

215§C

a

s

A

T

A

s

A

e

TJfrom

s

a

220§C

T

85§C

CC

b

65§Ctoa150§C

) 150§C

JMAX

MIN

b

40§CsT

e

AVCC) 4.5V to 5.5V

CC

e

ea

AV

CC

5V, V

REFa(SENSE)

Typ Limit Units

0.4

0.4

0.4

0.3

0.3

0.2

0.2

750

g

0.8 LSB (max)

g

0.95 LSB (max)

g

1.0 LSB (max)

g

1.0 LSB (max)

g

1.5 LSB (max)

g

1.25 LSB (max)

g

1.25 LSB (max)

g

2.0 LSB (max)

g

1.0 LSB (max)

g

1.0 LSB (max)

g

1.5 LSB (max)

g

1.0 LSB (max)

500 X (min)

1000 X (max)

CC

a

0.05V V (max)

CC

b

AGND

0.05V V (min)

V (max)

MAX

e

2

Dynamic Characteristics (Note 10) The following specifications apply for DV

V

REFa(SENSE)

otherwise specified. Boldface limits apply for T

Symbol Parameter Conditions

SINAD Signal-to-Noise Plus T

SNR Signal-to-Noise Ratio T

THD Total Harmonic Distortion T

ENOB Effective Number of Bits T

IMD Intermodulation Distortion f

ea

4.096V, V

REFb(SENSE)

e

Distortion Ratio

(Note 11)

(Note 12) T

(Note 13)

AGND, R

S

e

TJfrom T

A

to T

MIN

to T

MIN

ea

25§C

A

to T

MIN

to T

MIN

e

102.3 kHz, 102.7 kHz

IN

e

MAX

MAX

MAX

MAX

25X,f

e

100 kHz, 0 dB from fullscale, and f

IN

to T

MIN

; all other limits T

MAX

Typ Limit Units

(Note 7) (Note 8) (Limit)

71 68.0 dB (min)

72 69.5 dB (min)

b

82

11.5 11.0 Bits (min)

b

80 dBc

e

CC

e

T

A

J

b

74 dBc (max)

b

70 dBc (max)

AV

CC

e

1 MHz, unless

s

ea

25§C.

ea

5V,

DC Electrical Characteristics The following specifications apply for DV

V

REFa(SENSE)

for T

A

Symbol Parameter Conditions

V

IN(1)

V

IN(0)

I

IN(1)

I

IN(0)

V

OUT(1)

V

OUT(0)

I

OUT

C

OUT

C

IN

DI

CC

AI

CC

I

STANDBY

e

TJfrom T

ea

4.096V, V

to T

MIN

REFb(SENSE)

MAX

e

AGND, and f

; all other limits T

e

1 MHz, unless otherwise specified. Boldface limits apply

s

e

ea

T

A

25§C.

J

Typ Limit Units

(Note 7) (Note 8) (Limit)

e

Logical ‘‘1’’ Input Voltage DV

Logical ‘‘0’’ Input Voltage DV

CC

CC

ea

AV

e

AV

5.5V 2.0 V (min)

CC

ea

4.5V 0.8 V (max)

CC

Logical ‘‘1’’ Input Current 0.1 1.0 mA (max)

Logical ‘‘0’’ Input Current 0.1 1.0 mA (max)

e

Logical ‘‘1’’ Output Voltage DV

Logical ‘‘0’’ Output Voltage DV

I

I

I

OUT

OUT

OUT

CC

CC

eb

eb

e

TRI-STATEÉOutput Pins DB0 – DB11

Leakage Current

ea

AV

360 mA 2.4 V (min)

CC

4.5V,

100 mA 4.25 V (min)

e

ea

AV

1.6 mA

CC

4.5V,

0.1 3 mA (max)

TRI-STATE Output Capacitance Pins DB0–DB11 5 pF

Digital Input Capacitance 4 pF

DVCCSupply Current 2 3 mA (max)

AVCCSupply Current 10 12 mA (max)

Standby Current (DI

a

AICC)PD

CC

e

0V 20 mA

e

AV

CC

CC

0.4 V (max)

ea

5V,

3

AC Electrical Characteristics The following specifications apply for DV

V

REFa(SENSE)

for T

A

Symbol Parameter Conditions

f

s

t

CONV

t

AD

t

S/H

t

EOC

t

ACC

t1H,t

0H

t

INTH

t

INTL

t

UPDATE

t

MS

t

MH

t

CSS

t

CSH

t

WU

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is

functional. These ratings do not guarantee specific performance limits, however. For guaranteed specifications and test conditions, see the Electrical Characteristics. The guaranteed specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under

the listed test conditions.

Note 2: All voltages are measured with respect to GND (GND

Note 3: When the input voltage (V

limited to 25 mA or less. The 50 mA package input current limits the number of pins that can safely exceed the power supplies with an input current of 25 mA to

two.

Note 4: The maximum power dissipation must be derated at elevated temperatures and is dictated by T

allowable power dissipation at any temperature is P

(PLCC) package is 55

conditions.

e

TJfrom T

ea

4.096V, V

to T

MIN

REFb(SENSE)

MAX

e

AGND, and f

; all other limits T

e

1 MHz, unless otherwise specified. Boldface limits apply

s

e

ea

T

A

25§C.

J

Typ Limit Units

(Note 7) (Note 8) (Limits)

Maximum Sampling Rate

(1/t

THROUGHPUT

)

Conversion Time 740 600 ns (min)

(S/H

Low to EOC High) 980 ns (max)

Aperture Delay

(S/H

Low to Input Voltage Held)

20 ns

S/H Pulse Width 5 ns (min)

S/H Low to EOC Low

Access Time C

(RD

Low or OE High to Data Valid)

TRI-STATE Control

High or OE Low to Databus TRI-STATE)

(RD

Delay from RD Low to INT High C

Delay from EOC High to INT Low C

e

100 pF

L

e

R

L

e

L

e

L

e

1k, C

10 pF 25 40 ns (max)

L

100 pF 35 60 ns (max)

100 pF

95

10 20 ns (max)

b

25

EOC High to New Data Valid 5 15 ns (max)

Multiplexer Address Setup Time

(MUX Address Valid to EOC Low)

Multiplexer Address Hold Time

(EOC Low to MUX Address Invalid)

CS Setup Time

(CS Low to RD Low, S/H Low, or OE High)

CS Hold Time

(CS

High after RD High, S/H High, or OE Low)

Wake-Up Time

(PD

High to First S/H Low)

e

) at any pin exceeds the power supply rails (V

IN

e

C/W. iJAfor the VF (PQFP) package is 62§C/W. In most cases the maximum derated power dissipation will be reached only during fault

§

D

AGNDeDGND), unless otherwise specified.

b

(T

TA)/iJAor the number given in the Absolute Maximum Ratings, whichever is lower. iJAfor the V

JMAX

IN

k

GND or V

l

VCC) the absolute value of current at that pin should be

IN

JMAX

1 ms

, iJAand the ambient temperature TA. The maximum

e

CC

1 MHz (min)

550 ns (max)

60 ns (min)

125 ns (max)

b

b

50 ns (min)

50 ns (min)

20 ns (min)

20 ns (min)

ea

AV

CC

35 ns (min)

10 ns (max)

5V,

4

Note 5: Human body model, 100 pF discharged through a 1.5 kX resistor. Machine model ESD rating is 200V.

Note 6: See AN-450 ‘‘Surface Mounting Methods and Their Effect on Product Reliability’’ or the section titled ‘‘Surface Mount’’ found in a current National

Semiconductor Linear Data Book for other methods of soldering surface mount devices.

Note 7: Typicals are at

Note 8: Tested limits are guaranteed to National’s AOQL (Average Outgoing Quality Level).

Note 9: Integral Linearity Error is the maximum deviation from a straight line between the

Note 10: Dynamic testing of the ADC12062 is done using the ADC IN input. The input multiplexer adds harmonic distortion at high frequencies. See the graph in the

Typical Performance Characteristics section for a typical graph of THD performance vs input frequency with and without the input multiplexer.

Note 11: The signal-to-noise ratio is the ratio of the signal amplitude to the background noise level. Harmonics of the input signal are not included in its calculation.

Note 12: The contributions from the first nine harmonics are used in the calculation of the THD.

Note 13: Effective Number of Bits (ENOB) is calculated from the measured signal-to-noise plus distortion ratio (SINAD) using the equation ENOB

1.76)/6.02.

Note 14: The digital power supply current takes up to 10 seconds to decay to its final value after PD is pulled low. This prohibits production testing of the standby

current. Some parts may exhibit significantly higher standby currents than the 20 mA typical.

Note 15: Power Supply Sensitivity is defined as the change in the Offset Error or the Full Scale Error due to a change in the supply voltage.

a

25§C and represent most likely parametric norm.

measured

offset and full scale endpoints.

e

(SINAD

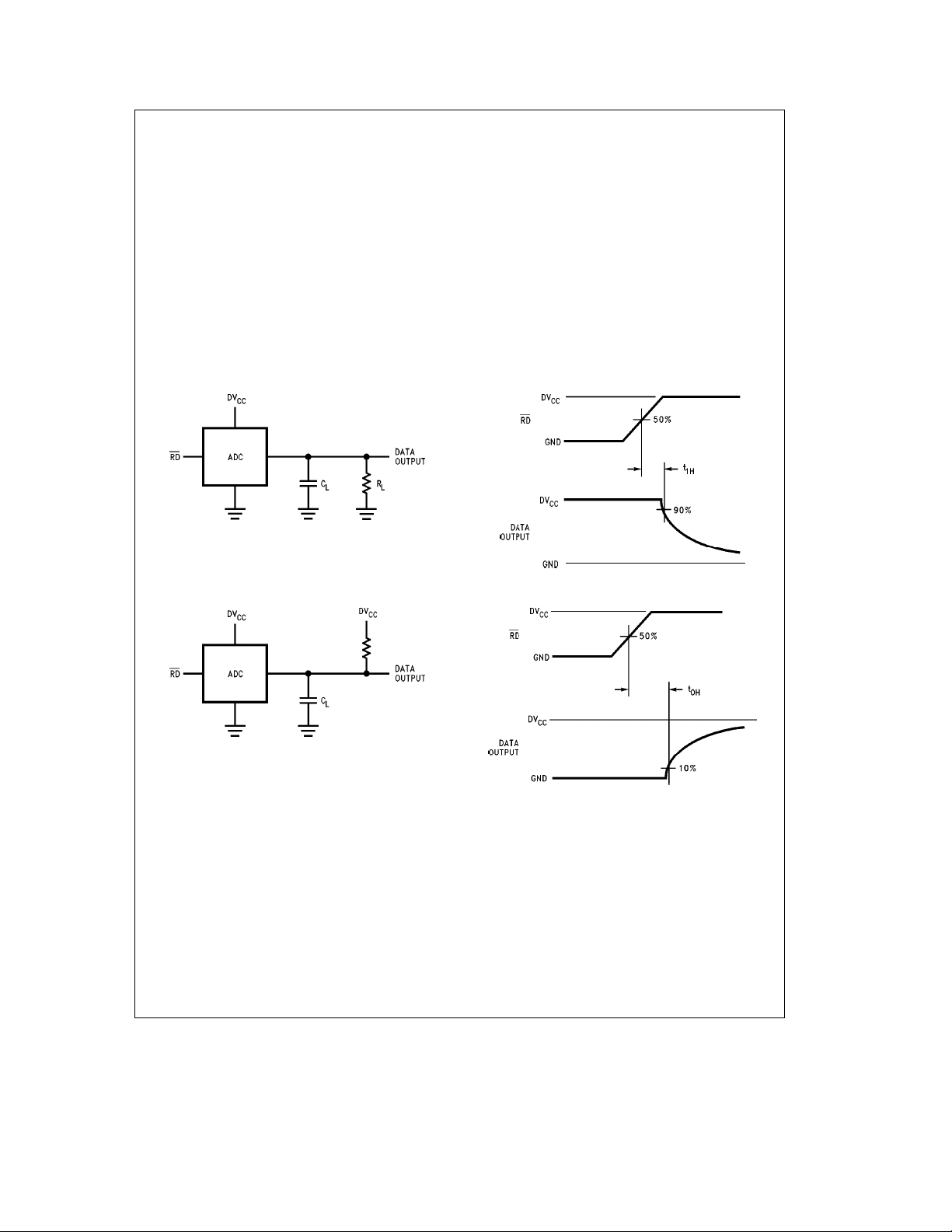

TRI-STATE Test Circuit and Waveforms

TL/H/11490– 2

TL/H/11490– 3

b

TL/H/11490– 4

TL/H/11490– 5

5

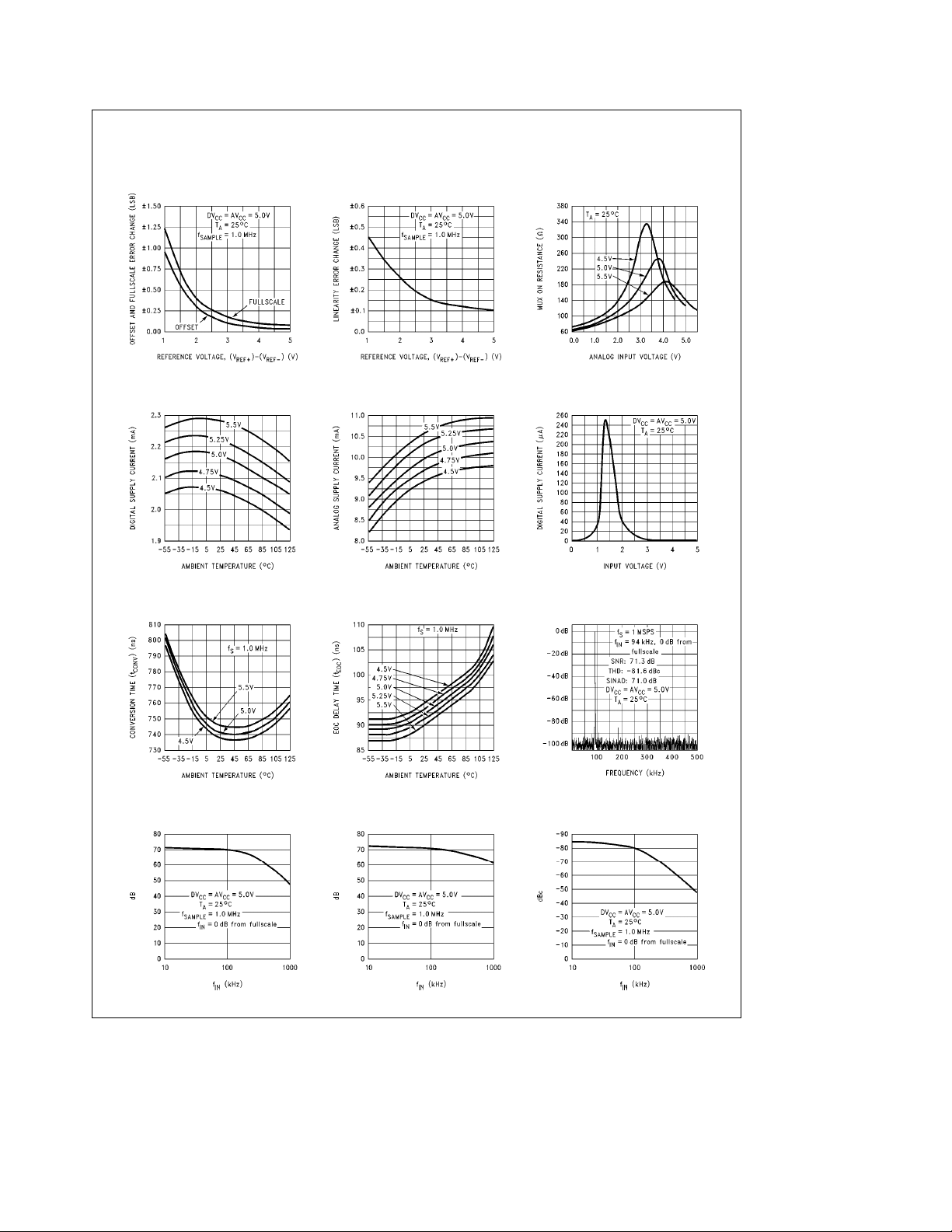

Typical Performance Characteristics

Offset and Fullscale

Error Change vs

Reference Voltage

Linearity Error Change

vs Reference Voltage

Mux ON Resistance vs

Input Voltage

Digital Supply Current

vs Temperature

Conversion Time (t

vs Temperature

SINAD vs Input Frequency

(ADC IN)

CONV

Analog Supply Current

vs Temperature

)

EOC Delay Time (t

vs Temperature

SNR vs Input Frequency

(ADC IN)

EOC

)

Current Consumption in

Standby Mode vs Voltage

on Digital Input Pins

Spectral Response

THD vs Input Frequency

(ADC IN)

TL/H/11490– 27

6

Loading...

Loading...