NSC ADC12048CIVF, ADC12048CIV Datasheet

ADC12048

12-Bit Plus Sign 216 kHz 8-Channel Sampling

Analog-to-Digital Converter

ADC12048 12-Bit Plus Sign 216 kHz 8-Channel Sampling Analog-to-Digital Converter

April 2000

General Description

Operating from a single 5V power supply,theADC12048 is a

12 bit + sign, parallel I/O, self-calibrating, sampling

analog-to-digital converter (ADC) with an eight input fully differential analog multiplexer. The maximum sampling rate is

216 kHz. On request, the ADC goes through a

self-calibration process that adjusts linearity, zero and

full-scale errors.

TheADC12048’s8-channelmultiplexer is software programmable to operate in a variety of combinations of

single-ended, differential, or pseudo-differential modes. The

fully differentialMUXandthe 12-bit + sign ADC allowsforthe

difference between two signals to be digitized.

TheADC12048 can be configured to work with many popular

microprocessors/microcontrollers and DSPs including National’s HPC family, Intel386 and 8051, TMS320C25, Motorola MC68HC11/16, Hitachi 64180 and Analog Devices

ADSP21xx.

For complementary voltage references see the LM4040,

LM4041 or LM9140.

Features

n 8-channel programmable Differential or Single-Ended

multiplexer

n Programmable Acquisition Times and user-controllable

Throughput Rates

n Programmable data bus width (8/13 bits)

n Built-in Sample-and-Hold

n Programmable Auto-Calibration and Auto-Zero cycles

n Low power standby mode

n No missing codes

Key Specifications

(f

= 12 MHz)

CLK

n Resolution 12-bits + sign

n 13-bit conversion time 3.6 µs, max

n 13-bit throughput rate 216 ksamples/s, min

n Integral Linearity Error (ILE)

n Single Supply +5V

n V

Range GND to VA+

IN

n Power consumption

— Normal operation 34 mW, max

— Stand-by mode 75 µw, max

±

1 LSB, max

±

10%

Applications

n Medical instrumentation

n Process control systems

n Test equipment

n Data logging

n Inertial guidance

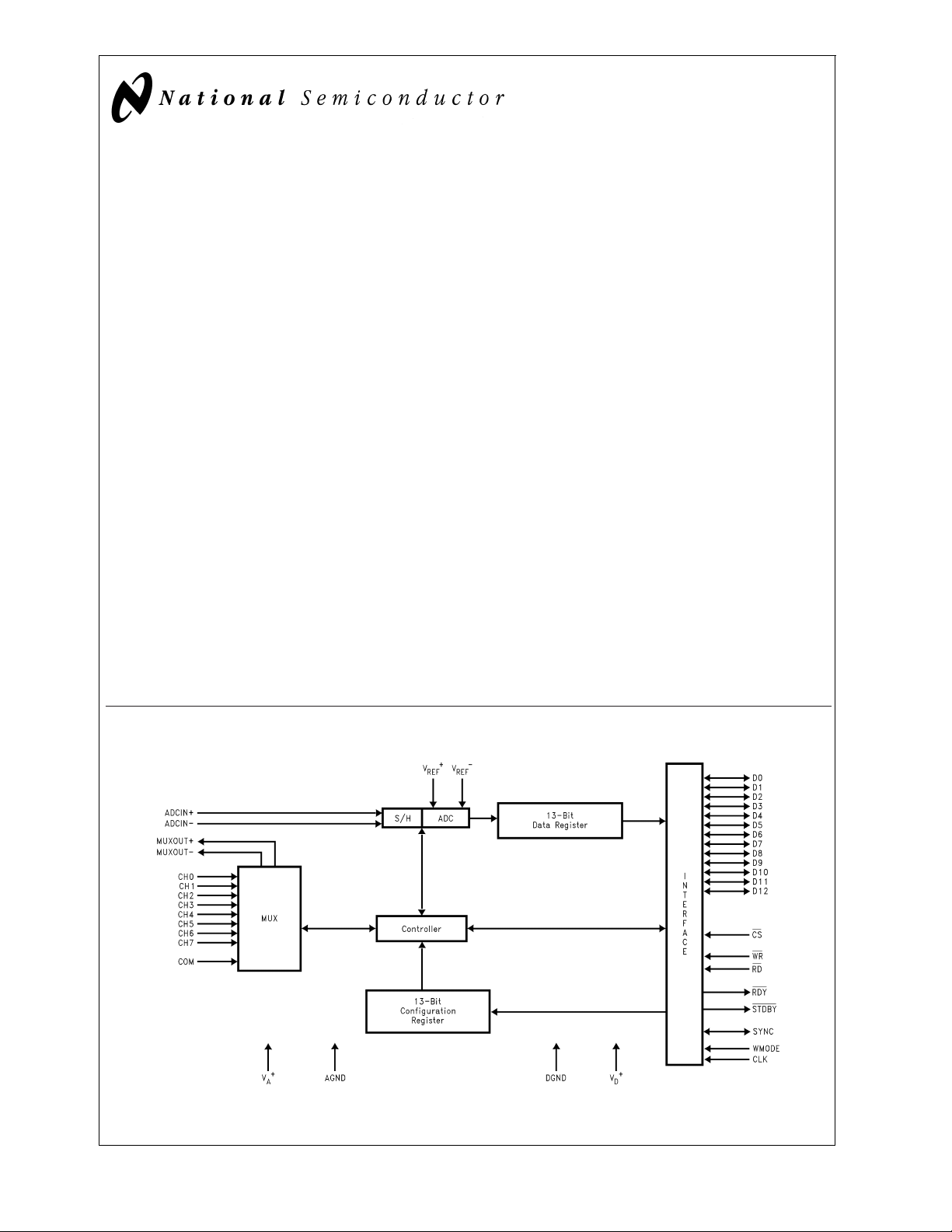

Block Diagram

DS012387-1

TRI-STATE®is a registered trademark of National Semiconductor Corporation.

© 2000 National Semiconductor Corporation DS012387 www.national.com

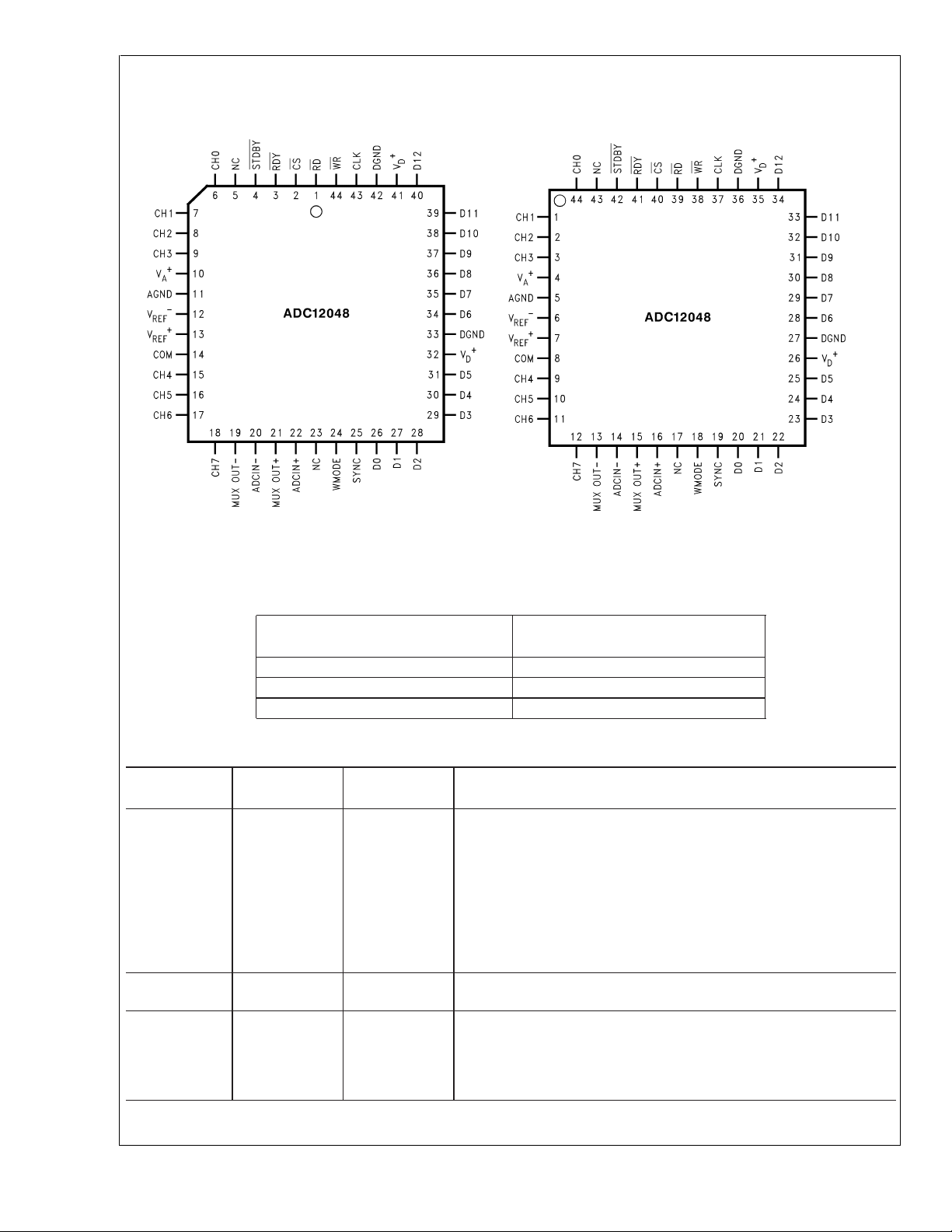

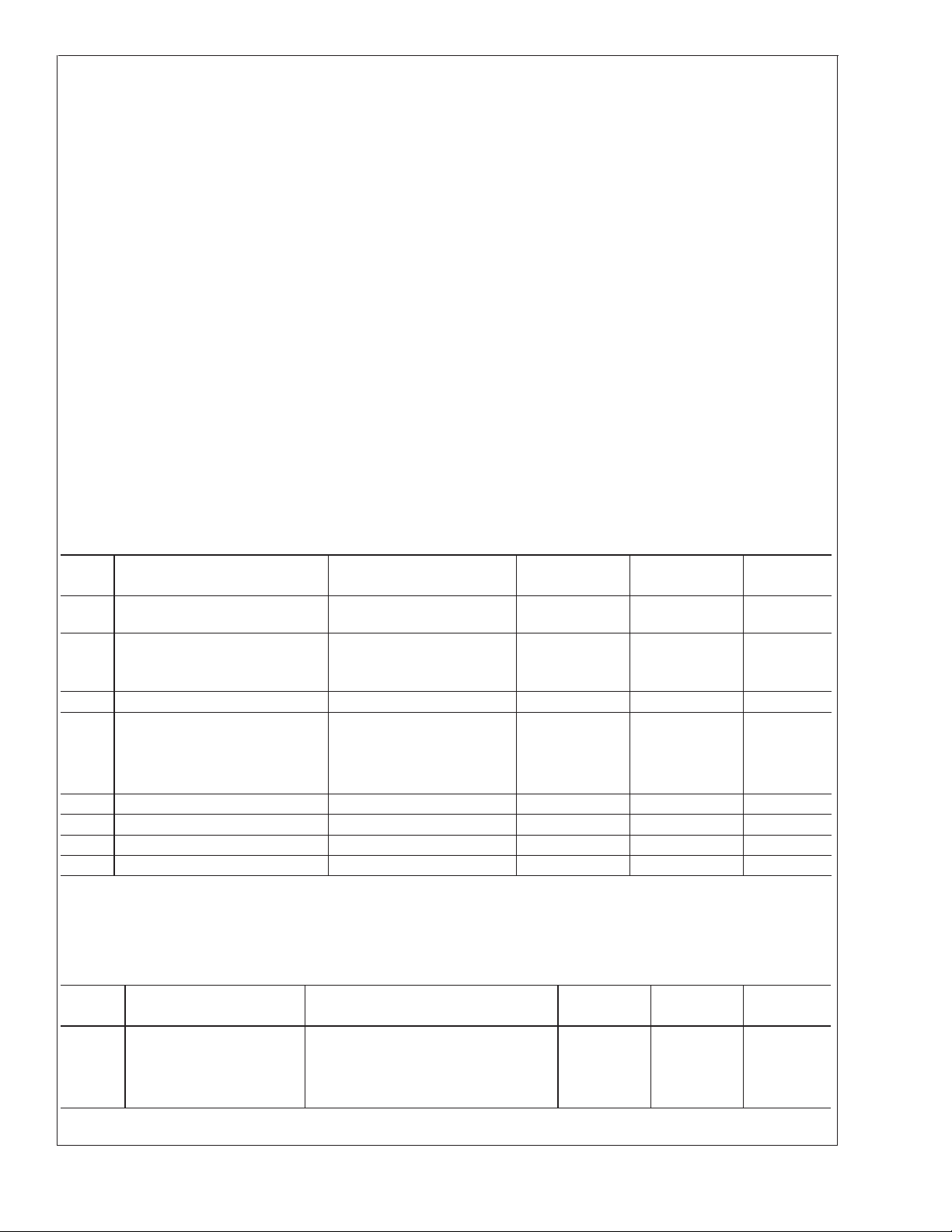

Connection Diagrams

ADC12048

PLCC Package

Order Number ADC12048CIV

See NS Package Number V44A

DS012387-2

PQFP Package

DS012387-3

Order Number ADC12048CIVF

See NS Package Number VGZ44A

Ordering Information

Industrial Temperature Range Package

−40˚C ≤ T

≤ +85˚C

A

ADC12048CIV PLCC

ADC12048CIVF PQFP

ADC12048EVAL Evaluation board

Pin Description

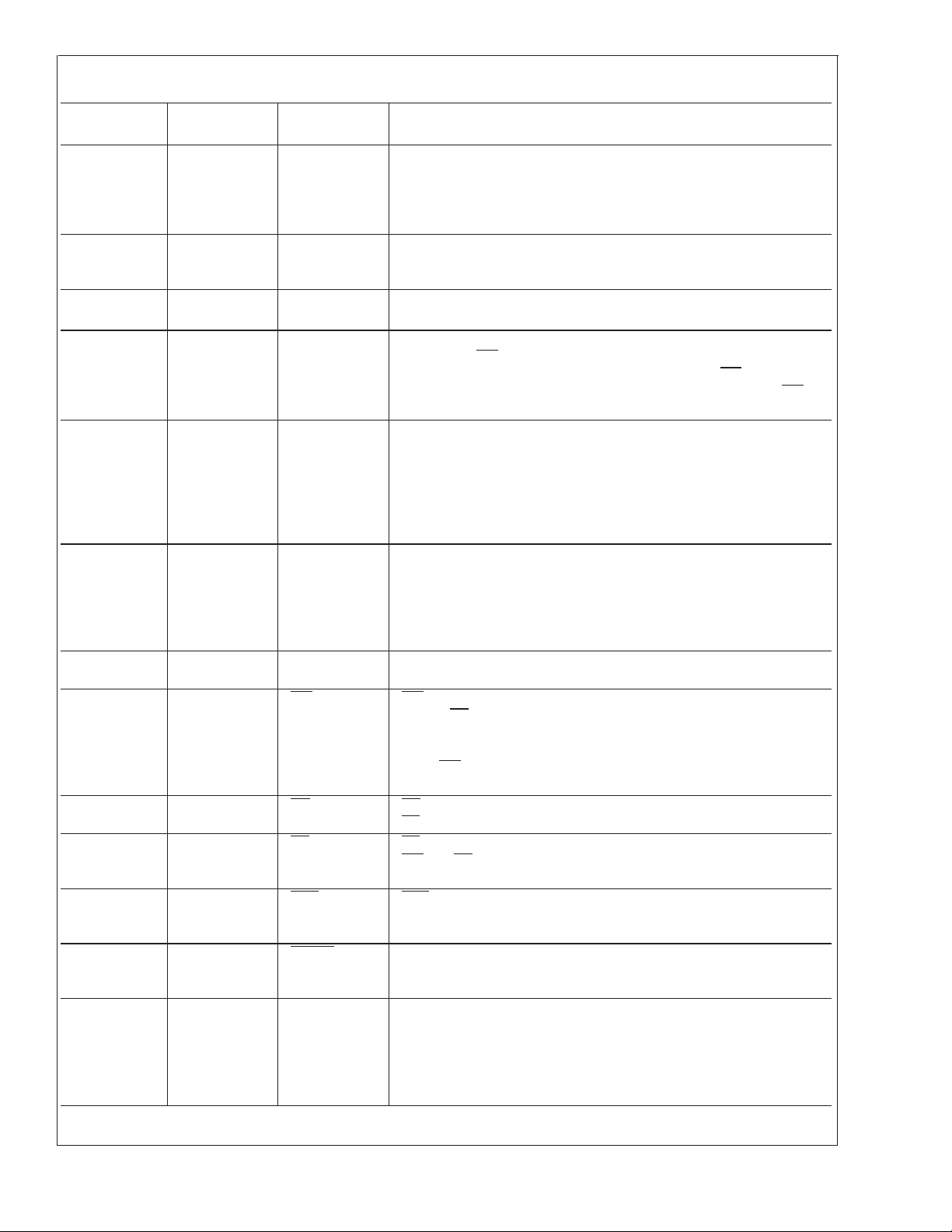

PLCC Pkg. PQFP Pkg. Pin Name Description

Pin Number Pin Number

6 44 CH0 The eight analog inputs to the Multiplexer. Active channels are selected

7 1 CH1

8 2 CH2

9 3 CH3

15 9 CH4

16 10 CH5

17 11 CH6

18 12 CH7

14 8 COM This pin is another analog input pin used as a pseudo ground when the

13 7 V

+ Positive reference input. The operating voltage range for this input is

REF

based on the contents of bits b3–b0 of the Configuration register. Refer

to section titled MUX for more details.

multiplexer is configured in single-ended mode.

1V ≤ V

+ ≤ VA+ (see

REF

Figure 3

and4). This pin should be bypassed

to AGND at least with a parallel combination of a 10 µF and a 0.1 µF

(ceramic) capacitors. The capacitors should be placed as close to the

part as possible.

www.national.com 2

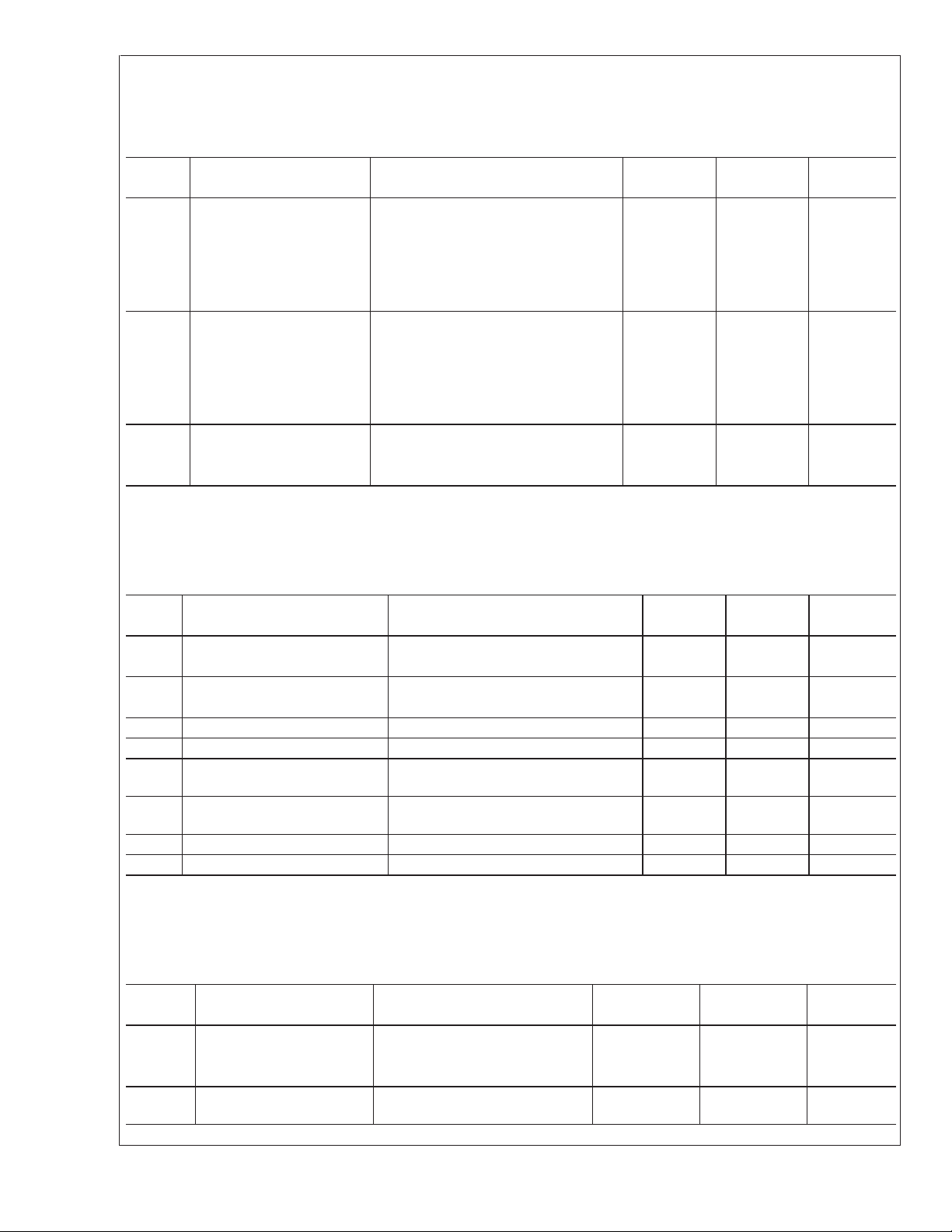

Pin Description (Continued)

PLCC Pkg. PQFP Pkg. Pin Name Description

Pin Number Pin Number

12 6 V

19 13 MUX OUT− The inverting (negative) and non-inverting (positive) outputs of the

21 15 MUX OUT+

20 14 ADCIN− ADC inputs. The inverting (negative) and non-inverting (positive) inputs

22 16 ADCIN+

24 18 WMODE The logic state of this pin at power-up determines which edge of the

25 19 SYNC The SYNC pin can be programmed as an input or an output. The

26–31 20–25 D0–D5 13-bit Data bus of the ADC12048. D12 is the most significant bit and

34–40 29–34 D6–D12

43 37 CLK The clock input pin used to drive the ADC12048. The operating range

44 38 WR

139RD

240CSCS is the active low Chip Select input pin. Used in conjunction with the

3 41 RDY

4 42 STDBY

10 4 V

− Negative reference input. The operating voltage range for this input is

REF

0V ≤ V

REF

− ≤ V

+ −1 (see

REF

Figure 3

and4). This pin should be

bypassed to AGND at least with a parallel combination of a 10 µF and

a 0.1 µF (ceramic) capacitor. The capacitors should be placed as close

to the part as possible.

multiplexer. The analog inputs to the MUX selected by bits b3–b0 of

the Configuration register appear at these pins.

into the ADC.

write signal (WR) will latch in data from the data bus. If tied low, the

ADC12048 will latch in data on the rising edge of the WR signal. If tied

to a logic high, data will he latched in on the falling edge of the WR

signal. The state of this pin should not be changed after power-up.

Configuration register’s bit b8 controls the function of this pin. When

programmed as an input pin (b8 = 1), a rising edge on this pin causes

the ADC’s sample-and-hold to hold the analog input signal and begin

conversion. When programmed as an output pin (b8 = 0), the SYNC

pin goes high when a conversion begins and returns low when

completed.

D0 is the least significant. The BW (bus width) bit of the Configuration

register (b12) selects between an 8-bit or 13-bit data bus width. When

the BW bit is cleared (BW = 0), D7–D0 are active and D12–D8 are

always in TRI-STATE. When the BW bit is set (BW = 1), D12–D0 are

active.

is 0.05 MHz to 12 MHz.

WR is the active low WRITE control input pin. A logic low on this pin

and the CS will enable the input buffers of the data pins D12–D0. The

signal at this pin is used by the ADC12048 to latch in data on D12–D0.

The sense of the WMODE pin at power-up will determine which edge

of the WR signal the ADC12048 will latch in data. See WMODE pin

description.

RD is the active low read control input pin. A logic low on this pin and

CS will enable the active output buffers to drive the data bus.

WR and RD signals to control the active data bus input/output buffers

of the data bus.

RDY is an active low output pin. The signal at this pin indicates when a

requested function has begun or ended. Refer to section Functional

Description and the digital timing diagrams for more detail.

This is the standby active low output pin. This pin is low when the

ADC12048 is in the standby mode and high when the ADC12048 is out

of the standby mode or has been requested to leave the standby mode.

+ Analog supply input pin. The device operating supply voltage range is

A

±

10%. Accuracy is guaranteed only if the VA+ and VD+ are

+5V

connected to the same potential. This pin should be bypassed to AGND

with a parallel combination of a 10 µF and a 0.1 µF (ceramic) capacitor.

The capacitors should be placed as close to the supply pins of the part

as possible.

ADC12048

www.national.com3

Pin Description (Continued)

PLCC Pkg. PQFP Pkg. Pin Name Description

ADC12048

Pin Number Pin Number

11 5 AGND Analog ground pin. This is the device’s analog supply ground

connection. It should be connected through a low resistance and low

inductance ground return to the system power supply.

32 and 41 26 and 35 V

33 and 42 27 and 36 DGND Digital ground pin. This is the device’s digital supply ground connection.

+ Digital supply input pins. The device operating supply voltage range is

D

±

10%. Accuracy is guaranteed only if the VA+ and VD+ are

+5V

connected to the same potential. This pin should be bypassed to

DGND with a parallel combination of a 10 µF and a 0.1 µF (ceramic)

capacitor. The capacitors should be placed as close to the supply pins

of the part as possible.

It should be connected through a low resistance and low inductance

ground return to the system power supply.

www.national.com 4

ADC12048

Absolute Maximum Ratings (Notes 1, 2)

If Military/Aerospace specified devices are required,

please contact the National Semiconductor Sales Office/

Distributors for availability and specifications.

Supply Voltage (V

Voltage at all Inputs −0.3V to V

+−VD+| 300 mV

|V

A

|AGND − DGND| 300 mV

Input Current at Any Pin (Note 3)

Package Input Current (Note 3)

Power Dissipation (Note 4)

= 25˚C 875 mW

at T

A

Storage Temperature −65˚C to +150˚C

+ and VD+) 6.0V

A

+

+ 0.3V

±

30 mA

±

120 mA

Lead Temperature

VF Package

Vapor Phase (60 sec.) 210˚C

Infared (15 sec.) 220˚C

V Package, Infared (15 sec.) 300˚C

ESD Susceptibility (Note 5) 3.0 kV

Operating Ratings (Notes 1, 2, 6, 7, 8, 9)

Temperature Range

(T

≤ TA≤ T

min

Supply Voltage

+, VD+ 4.5V to 5.5V

V

A

+−VD+| ≤100 mV

|V

A

) −40˚C ≤ TA≤ 85˚C

max

|AGND − DGND| ≤100 mV

Voltage Range

V

IN

at all Inputs GND ≤ V

+ Input Voltage 1V ≤ V

V

REF

− Input Voltage 0 ≤ V

V

REF

+−V

V

REF

Common Mode

V

REF

(Note 16) 0.1 V

−1V≤V

REF

+ ≤ V

A

REF

− ≤ V

REFCM

≤ VA+

IN

+ ≤ VA+

REF

+−1V

REF

≤ VA+

REF

≤ 0.6 VA+

Converter DC Characteristics

The following specifications apply to the ADC12048 for VA+=VD+ = 5V, V

sion mode, f

common-mode voltage (V

=T

to T

MIN

= 12.0 MHz, RS=25Ω, source impedance for V

CLK

; all other limits TA=TJ= 25˚C

MAX

), and minimum acquisition time, unless otherwise specified. Boldface limits apply for TA=T

INCM

REF

+ and V

Symbol Parameter Conditions Typical Limits Unit

Resolution with No Missing

After Auto-Cal 13 Bits (max)

Codes

ILE Integral Linearity Error After Auto-Cal

(Notes 12, 17)

+ = 4.096V, V

REF

− ≤ 1Ω, fully differential input with fixed 2.048V

REF

− = 0.0V, 12-bit + sign conver-

REF

(Note 10) (Note 11) (Limit)

±

0.6

±

1 LSB (max)

J

DNL Differential Non-Linearity After Auto-Cal

±

1 LSB (max)

Zero Error After Auto-Cal (Notes 13, 17)

V

= 5.0V

INCM

V

= 2.048V

INCM

V

=0V

INCM

Positive Full-Scale Error After Auto-Cal (Notes 12, 17)

Negative Full-Scale Error After Auto-Cal (Notes 12, 17)

DC Common Mode Error After Auto-Cal (Note 14)

TUE Total Unadjusted Error After Auto-Cal (Note 18)

±

1.0

±

1.0

±

2

±

1 LSB

±

5.5 LSB (max)

±

2.5 LSB (max)

±

5.5 LSB (max)

±

2.5 LSB (max)

±

2.5 LSB (max)

±

5.5 LSB (max)

Power Supply Characteristics

The following specifications apply to the ADC12048 for VA+=VD+ = 5V, V

sion mode, f

common-mode voltage, and minimum acquisition time, unless otherwise specified. Boldface limits apply for T

to T

; all other limits TA=TJ= 25˚C

MAX

= 12.0 MHz, RS=25Ω, source impedance for V

CLK

REF

+ and V

Symbol Parameter Conditions Typical Limits Unit

PSS Power Supply Sensitivity V

Zero Error V

Full-Scale Error V

+=VA+ = 5.0V±10% (Note 15)

D

+ = 4.096V

REF

−=0V

REF

Linearity Error

+ = 4.096V, V

REF

− ≤ 1Ω, fully differential input with fixed 2.048V

REF

− = 0.0V, 12-bit + sign conver-

REF

A=TJ=TMIN

(Note 10) (Note 11) (Limit)

±

0.1 LSB

±

0.5 LSB

±

0.1 LSB

www.national.com5

Power Supply Characteristics (Continued)

The following specifications apply to the ADC12048 for VA+=VD+ = 5V, V

sion mode, f

ADC12048

common-mode voltage, and minimum acquisition time, unless otherwise specified. Boldface limits apply for T

to T

; all other limits TA=TJ= 25˚C

MAX

= 12.0 MHz, RS=25Ω, source impedance for V

CLK

REF

+ and V

Symbol Parameter Conditions Typical Limits Unit

I

+V

D

+ Digital Supply Current Start Command (Performing a

D

conversion) with SYNC configured as

an input and driven with a 214 kHz

signal. Bus width set to 13.

= 12.0 MHz, Reset Mode 850 µA

f

CLK

f

= 12.0 MHz, Conversion 2.45 2.8 mA (max)

CLK

I

+V

A

+ Analog Supply Current Start Command (Performing a

A

conversion) with SYNC configured as

an input and driven with a 214 kHz

signal. Bus width set to 13.

= 12.0 MHz, Reset Mode 2.3 mA

f

CLK

f

= 12.0 MHz, Conversion 2.3 4.0 mA (max)

CLK

I

ST

Standby Supply Current Standby Mode

(I

++IA+) f

D

= Stopped 5 15 µA (max)

CLK

f

= 12.0 MHz 100 120 µA (max)

CLK

+ = 4.096V, V

REF

− ≤ 1Ω, fully differential input with fixed 2.048V

REF

− = 0.0V, 12-bit + sign conver-

REF

A=TJ=TMIN

(Note 10) (Note 11) (Limit)

Analog MUX Inputs Characteristics

The following specifications apply to the ADC12048 for VA+=VD+= 5V, V

sion mode, f

common-mode voltage, and minimum acquisition time, unless otherwise specified. Boldface limits apply for T

to T

; all other limits TA=TJ= 25˚C

MAX

= 12.0 MHz, RS=25Ω, source impedance for V

CLK

REF

+ and V

Symbol Parameter Conditions Typical Limits Unit

I

ON

I

OFF

I

ADCIN

R

ON

C

MUX

MUX ON Channel Leakage

Current

MUX OFF Channel Leakage

Current

ON Channel = 5V, OFF Channel = 0V 0.05 1.0 µA (min)

ON Channel = 0V, OFF Channel = 5V −0.05 −1.0 µA (max)

ON Channel = 5V, OFF Channel = 0V 0.05 1.0 µA (min)

ON Channel = 0V, OFF Channel = 5V −0.05 −1.0 µA (max)

ADCIN Input Leakage Current 0.05 2.0 µA (max)

MUX On Resistance VIN= 2.5V 310 500 Ω (max)

MUX Channel-to-Channel R

Matching

ON

V

IN

= 2.5V

MUX Channel and COM Input

Capacitance

C

ADC

C

MUXOUT

ADCIN Input Capacitance 70 pF

MUX Output Capacitance 20 pF

+ = 4.096V, V

REF

+ ≤ 1Ω, fully differential input with fixed 2.048V

REF

− = 0.0V, 12-Bit + sign conver-

REF

A=TJ=TMIN

(Note 10) (Note 11) (Limit)

±

20% Ω

10 pF

Reference Inputs

The following specifications apply to the ADC12048 for VA+=VD+ = 5V, V

version mode, f

2.048V common-mode voltage, and minimum acquisition time, unless otherwise specified. Boldface limits apply for T

=T

to T

MIN

MAX

= 12.0 MHz, RS=25Ω, source impedance for V

CLK

; all other limits TA=TJ= 25˚C

REF

Symbol Parameter Conditions Typical Limits Unit

I

REF

Reference Input Current V

+ 4.096V, V

REF

REF−

=0V

Analog Input Signal: 1 kHz 145 µA

(Note 20) 80 kHz 136 µA

C

REF

Reference Input

Capacitance

www.national.com 6

REF

+ and V

+ = 4.096V, V

− ≤ 1Ω, fully differential input with fixed

REF

− = 0.0V, 12-bit + sign con-

REF

(Note 10) (Note 11) (Limit)

85 pF

A=TJ

Digital Logic Input/Output Characteristics

The following specifications apply to the ADC12048 for VA+=VD+ = 5V, V

version mode, f

2.048V common-mode voltage, and minimum acquisition time, unless otherwise specified. Boldface limits apply for T

=T

to T

MIN

MAX

= 12.0 MHz, RS=25Ω, source impedance for V

CLK

; all other limits TA=TJ= 25˚C

REF

Symbol Parameter Conditions Typical Limits Unit

V

V

I

I

V

V

I

C

IH

IL

IH

IL

OH

OL

OFF

IN

Logic High Input Voltage VA+=VD+ = 5.5V 2.0 V (min)

Logic Low Input Voltage VA+=VD+ = 4.5V 0.8 V (max)

Logic High Input Current VIN= 5V 0.035 2.0 µA (max)

Logic Low Input Current VIN= 0V −0.035 −2.0 µA (max)

Logic High Output Voltage VA+=VD+ = 4.5V

= −1.6 mA

I

OUT

Logic Low Output Voltage VA+=VD+ = 4.5V

= 1.6 mA

I

OUT

TRI-STATE®Output

Leakage Current

V

V

OUT

OUT

=0V

=5V

D12–D0 Input

Capacitance

REF

+ and V

+ = 4.096V, V

− ≤ 1Ω, fully differential input with fixed

REF

− = 0.0V, 12-bit + sign con-

REF

(Note 10) (Note 11) (Limit)

2.4 V (min)

0.4 V (max)

±

2.0 µA (max)

10 pF

A=TJ

Converter AC Characteristics

The following specifications apply to the ADC12048 for VS+=VD+ = 5V, V

version mode, f

2.048V common-mode voltage, and minimum acquisition time, unless otherwise specified. Boldface limits apply for T

TJ=T

MIN

to T

= 12.0 MHz, RS=25Ω, source impedance for V

CLK

; all other limits TA=TJ= 25˚C

MAX

REF

Symbol Parameter Conditions Typical Limits Unit

t

t

Z

CAL

Auto Zero Time 78 78 clks + 120 ns clks (max)

Full Calibration Time 4946 4946 clks + 120 ns clks (max)

CLK Duty Cycle 50 %

t

CONV

t

AcqSYNCOUT

Conversion Time Sync-Out Mode 44 44 clks (max)

Acquisition Time

(Programmable)

Minimum for 13 Bits 9 9 clks + 120 ns clks (max)

Maximum for 13 Bits 79 79 clks + 120 ns clks (max)

REF

+ and V

+ = 4.096V, V

− ≤ 1Ω, fully differential input with fixed

REF

− = 0.0V, 12-bit + sign con-

REF

(Note 10) (Note 11) (Limit)

40 % (min)

60 % (max)

A

ADC12048

=

Digital Timing Characteristics

The following specifications apply to the ADC12048, 13-bit data bus width, VA+=VD+ = 5V, f

= 50 pF on data I/O lines

Symbol Parameter Conditions Typical Limits Units

t

TPR

Throughput Rate Sync-Out Mode (SYNC Bit

= “0”) 9 Clock Cycles of

Acquisition Time

t

CSWR

t

WRCS

t

WR

t

WRSETFalling

t

WRHOLDFalling

t

WRSETRising

t

WRHOLDRising

t

CSRD

t

RDCS

t

RDDATA

Falling Edge of CS to Falling Edge of WR 0ns

Active Edge of WR to Rising Edge of CS 0ns

WR Pulse Width 20 30 ns (min)

Write Setup Time WMODE = “1” 20 ns (min)

Write Hold Time WMODE = “1” 5 ns (min)

Write Setup Time WMODE = “0” 20 ns (min)

Write Hold Time WMODE = “0” 5 ns (min)

Falling Edge of CS to Falling Edge of RD 0ns

Rising Edge of RD to Rising Edge of CS 0ns

Falling Edge of RD to Valid Data 8-Bit Mode (BW Bit = “0”) 40 58 ns (max)

= 12 MHz, tf= 3 ns and C

CLK

(Note 10) (Note 11) (Limit)

222 kHz

www.national.com7

L

Digital Timing Characteristics (Continued)

The following specifications apply to the ADC12048, 13-bit data bus width, VA+=VD+ = 5V, f

= 50 pF on data I/O lines

ADC12048

Symbol Parameter Conditions Typical Limits Units

t

RDDATA

t

RDHOLD

t

RDRDY

Falling Edge of RD to Valid Data 13-Bit Mode (BW Bit = “1”) 26 44 ns (max)

Read Hold Time 23 32 ns (max)

Rising Edge of RD to Rising Edge of

RDY

t

WRRDY

Active Edge of WR to Rising Edge of

WMODE = “1”

RDY

t

STNDBY

Active Edge of WR to Falling Edge of

STDBY

WMODE = “0”. Writing the

Standby Command into the

Configuration Register

t

STDONE

Active Edge of WR to Rising Edge of

STDBY

WMODE = “0”. Writing the

RESET Command into the

Configuration Register

t

STDRDY

Active Edge of WR to Falling Edge of

RDY

WMODE = “0”. Writing the

RESET Command into the

Configuration Register

t

SYNC

Minimum SYNC Pulse Width 5 10 ns (min)

= 12 MHz, tf= 3 ns and C

CLK

(Note 10) (Note 11) (Limit)

24 38 ns (max)

42 65 ns (max)

200 230 ns (max)

30 45 ns (max)

1.4 2.5 ms (max)

Notes on Specifications

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is

functional, but do not guarantee specific performance limits. For guaranteed specifications and test conditions, see the Electrical Characteristics. The guaranteed

specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions.

Note 2: All voltages are measured with respect to GND, unless otherwise specified.

Note 3: When the input voltage (V

30 mA. The 120 mA maximum package input current limits the number of pins that can safely exceed the power supplies with an input current of 30 mA to four.

Note 4: The maximum power dissipation must he derated at elevated temperatures and is dictated by T

tion to ambient thermal resistance), and T

the number given in theAbsolute Maximum Ratings, whichever is lower. For this device, T

in the V package, when board mounted, is 55˚C/W, and in the VF package, when board mounted, is 67.8˚C/W.

Note 5: Human body model, 100 pF discharged through 1.5 kΩ resistor.

Note 6: Each input and output is protected by a nominal 6.5V breakdown voltage zener diode to GND; as shown below, input voltage magnitude up to 0.3V above

V

+ or 0.3V below GND will not damage the ADC12048. There are parasitic diodes that exist between the inputs and the power supply rails and errors in the A/D

A

conversion can occur if these diodes are forward biased by more than 50 mV.As an example, if V

accurate conversions.

) at any pin exceeds the power supply rails (V

IN

(ambient temperature). The maximum allowable power dissipation at any temperature is P

A

IN

<

GND or V

Jmax

>

(VA+orVD+)), the current at that pin should be limited to

IN

, (maximum junction temperature), θJA(package junc-

Jmax

= 150˚C, and the typical thermal resistance (θJA) of the ADC12048

+ is 4.50 VDC, full-scale input voltage must be ≤ 4.55 VDCto ensure

A

Dmax

=(T

Jmax−TA

L

)/θJAor

DS012387-4

Note 7: V

comparison accuracy. Refer to the Power Supply Considerations section for a detailed discussion.

Note 8: Accuracy is guaranteed when operating at f

Note 9: With the test condition for V

Note 10: Typicals are at T

Note 11: Limits are guaranteed to National’s AOQL (Average Outgoing Quality Level).

Note 12: Positive integral linearity error is defined as the deviation of the analog value, expressed in LSBs, from the straight line that passes through positive

full-scale and zero. For negative integral linearity error, the straight line passes through negative full-scale and zero.

+ and VD+ must be connected together to the same power supply voltage and bypassed with separate capacitors at each V+pin to assure conversion/

A

= 12 MHz.

CLK

+−V

REF(VREF

= 25˚C and represent most likely parametric norm.

A

−) given as +4.096V, the 12-bit LSB is 1.000 mV.

REF

www.national.com 8

Notes on Specifications (Continued)

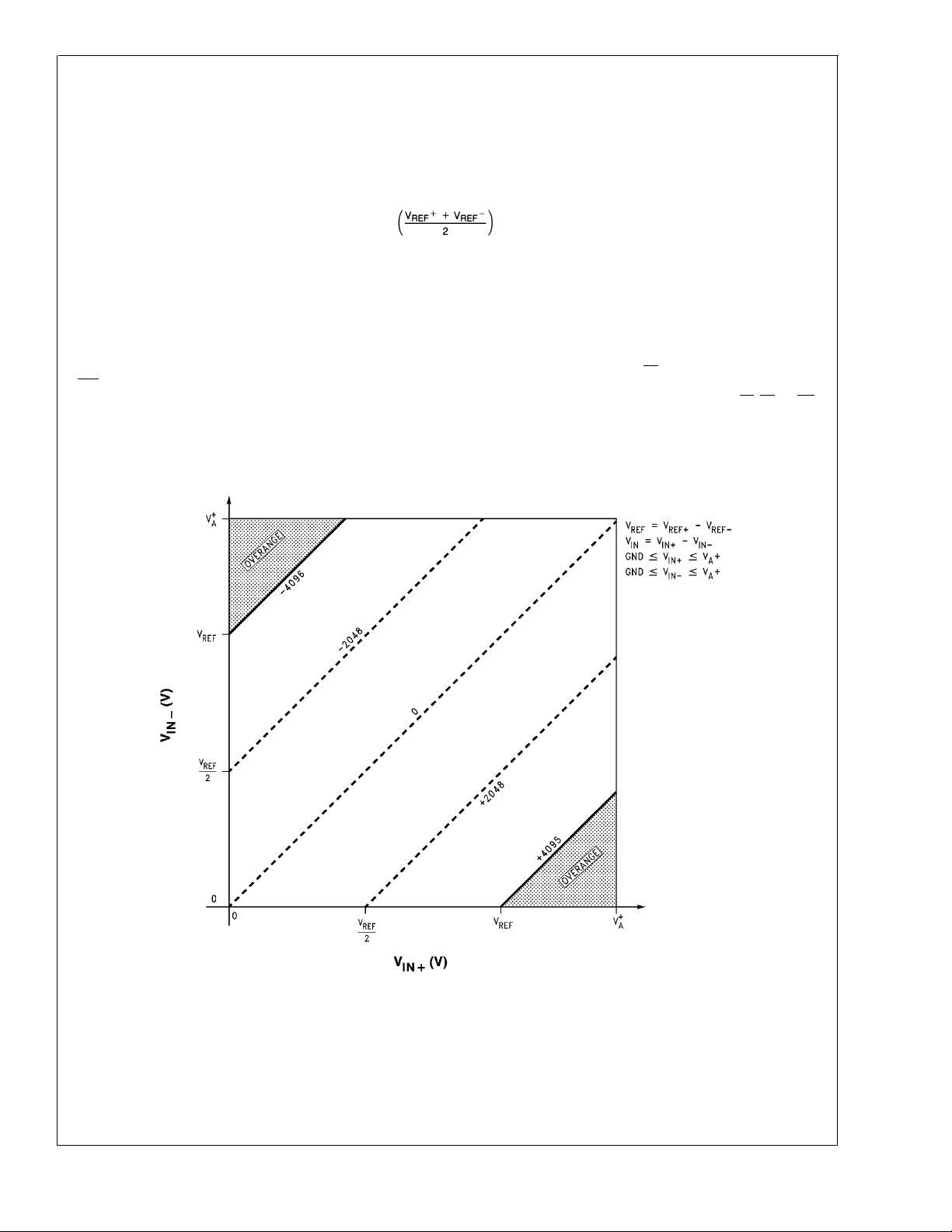

Note 13: Zero error is a measure of the deviation from the mid-scale voltage (a code of zero), expressed in LSB. It is the average value of the code transitions be-

tween −1 to 0 and 0 to +1 (see

Note 14: The DC common-mode error is measured with both inputs shorted together and driven from0V to 5V. The measured value is referred to the resulting out-

put value when the inputs are driven with a 2.5V input.

Note 15: Power Supply Sensitivity is measured after an Auto-Zero and Auto Calibration cycle has been completed with V

Note 16: V

(Reference Voltage Common Mode Range) is defined as

REFCM

Figure 8

).

+ and VD+ at the specified extremes.

A

ADC12048

Note 17: The ADC12048’s self-calibration technique ensures linearity and offset errors as specified, but noise inherent in the self-calibration process will result in

a repeatability uncertainly of

Note 18: Total Unadjusted Error (TUE) includes offset, full scale linearity and MUX errors.

Note 19: The ADC12048 parts used to gather the information for these curves were auto-calibrated prior to taking the measurements at each test condition. The

auto-calibration cycle cancels any first order drifts due to test conditions. However, each measurement has a repeatability uncertainty error of 0.2 LSB. See (Note

17).

Note 20: The reference input current is a DC average current drawn by the reference input with a full-scale sinewave input. The ADC12048 is continuously con-

verting with a throughput rate of 206 kHz.

Note 21: These typical curves were measured during continuous conversions with a positive half-scale DC input. A 240 ns RD pulse was applied 25 ns after the

RDY signal went low. The data bus lines were loaded with 2 HC family CMOS inputs (CL∼ 20 pF).

Note 22: Any other values placed in the command field are meaningless. However, if a code of 101 or 110is placed in the command field and the CS, RD and WR

go low at the same time, theADC12048 will enter a test mode. These test modes are only to be used by the manufacturer of this device. A hardware power-off and

power-on reset must be done to get out of these test modes.

±

0.20 LSB.

Electrical Characteristics

DS012387-5

FIGURE 1. Output Digital Code vs the Operating Input Voltage Range (General Case)

www.national.com9

Loading...

Loading...