ADC08L060

8-Bit, 10 MSPS to 60 MSPS, 0.65 mW/MSPS A/D

Converter with Internal Sample-and-Hold

General Description

The ADC08L060 is a low-power, 8-bit, monolithic analog-todigital converter with an on-chip track-and-hold circuit. Optimized for low cost, low power, small size and ease of use,

this product operates at conversion rates of 10 MSPS to

60 MSPS while consuming just 0.65 mW per MHz of clock

frequency, or 39 mW at 60 MSPS. Raising the PD pin puts

the ADC08L060 into a Power Down mode where it con-

<

sumes

The unique architecture achieves 7.6 Effective Bits. The

ADC08L060 is resistant to latch-up and the outputs are

short-circuit proof. The top and bottom of the ADC08L060’s

reference ladder are available for connections, enabling a

wide range of input possibilities. The digital outputs are

TTL/CMOS compatible with a separate output power supply

pin to support interfacing with 1.8V to 3V logic. The digital

inputs (CLK and PD) are TTL/CMOS compatible.

The ADC08L060 is offered in a 24-lead plastic package

(TSSOP) and is specified over the industrial temperature

range of −40˚C to +85˚C.

1.0 mW.

Features

n Single-ended input

n Internal sample-and-hold function

n Low voltage (single +3V) operation

n Small package

n Power-down feature

Key Specifications

n Resolution 8 bits

n Conversion rate 60 MSPS

n DNL

n INL +0.5/−0.2 LSB (typ)

n SNR (10.1 MHz) 48 dB (typ)

n ENOB (10.1 MHz) 7.6 bits (typ)

n THD (10.1 MHz) −57 dB (typ)

n Latency 5 Clock Cycles

n No missing codes Guaranteed

n Power Consumption

n Operating 0.65 mW/MSPS (typ)

n Power down

Applications

n Digital Imaging

n Set-top boxes

n Portable Instrumentation

n Communication Systems

n X-ray imaging

n Viterbi decoders

November 2002

±

0.25 LSB (typ)

<

1.0 mW (typ)

ADC08L060 8-Bit, 10 MSPS to 60 MSPS, 0.65 mW/MSPS A/D Converter with Internal

Sample-and-Hold

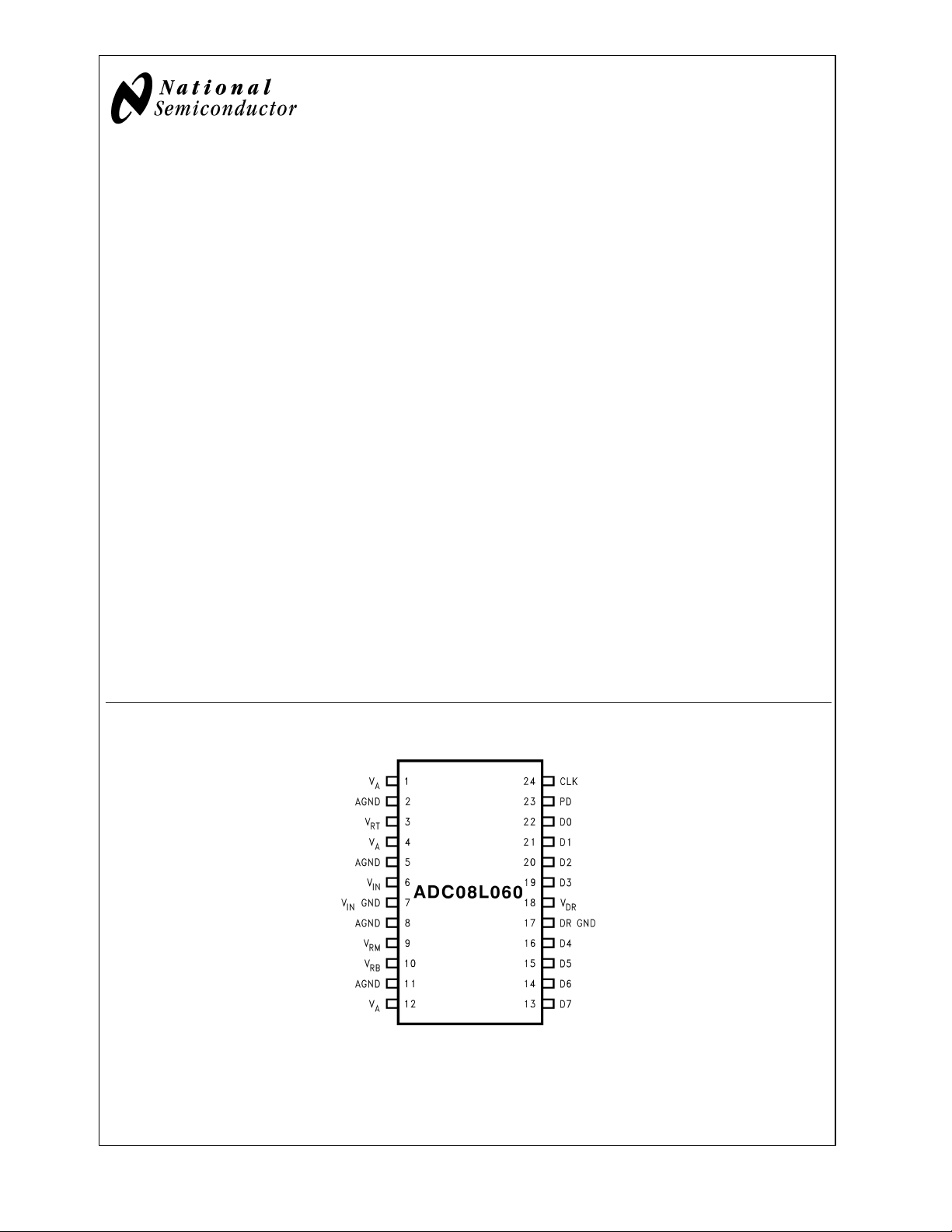

Pin Configuration

20041701

© 2002 National Semiconductor Corporation DS200417 www.national.com

Ordering Information

ADC08L060

Block Diagram

ADC08L060CIMT TSSOP

ADC08L060CIMTX TSSOP (tape and reel)

ADC08L060EVAL Evaluation Board

Pin Descriptions and Equivalent Circuits

Pin No. Symbol Equivalent Circuit Description

6V

3V

9V

10 V

IN

RT

RM

RB

Analog signal input. Conversion range is VRBto VRT.

Analog Input that is the high (top) side of the reference

ladder of the ADC. Nominal range is 0.5V to V

and VRBinputs define the VINconversion range.

on V

RT

Bypass well. See Section 2.0 for more information.

Mid-point of the reference ladder. This pin should be

bypassed to a quiet point in the analog ground plane with

a 0.1 µF capacitor.

Analog Input that is the low side (bottom) of the

reference ladder of the ADC. Nominal range is 0.0V to

– 0.5V). Voltage on VRTand VRBinputs define the

(V

RT

conversion range. Bypass well. See Section 2.0 for

V

IN

more information.

20041702

. Voltage

A

www.national.com 2

Pin Descriptions and Equivalent Circuits (Continued)

Pin No. Symbol Equivalent Circuit Description

Power Down input. When this pin is high, the converter is

23 PD

in the Power Down mode and the data output pins hold

the last conversion result.

ADC08L060

24 CLK

13 thru 16

and

D0–D7

19 thru 22

7V

IN

GND Reference ground for the single-ended analog input, VIN.

CMOS/TTL compatible digital clock Input. V

on the rising edge of CLK input.

Conversion data digital Output pins. D0 is the LSB, D7 is

the MSB. Valid data is output after the rising edge of the

CLK input.

Positive analog supply pin. Connect to a quiet voltage

1, 4, 12 V

A

source of +3V. V

ceramic chip capacitor for each pin, plus one

should be bypassed with a 0.1 µF

A

10 µF capacitor. See Section 3.0 for more information.

18 V

DR

Power supply for the output drivers. If connected to VA,

decouple well from V

.

A

17 DR GND The ground return for the output driver supply.

2, 5, 8, 11 AGND The ground return for the analog supply.

is sampled

IN

www.national.com3

Absolute Maximum Ratings (Notes 1,

2)

If Military/Aerospace specified devices are required,

ADC08L060

please contact the National Semiconductor Sales Office/

Distributors for availability and specifications.

Supply Voltage (V

Driver Supply Voltage (V

Voltage on Any Input or Output Pin −0.3V to V

Reference Voltage (VRT,VRB)V

CLK, PD Voltage Range −0.05V to

Input Current at Any Pin (Note 3)

Package Input Current (Note 3)

Power Dissipation at T

ESD Susceptibility (Note 5)

Human Body Model

Machine Model

) 3.8V

A

)V

DR

A

(V

= 25˚C See (Note 4)

A

+0.3V

A

to AGND

+ 0.05V)

A

±

25 mA

±

50 mA

2500V

A

200V

Soldering Temperature, Infrared,

10 seconds (Note 6) 235˚C

Storage Temperature −65˚C to +150˚C

Operating Ratings (Notes 1, 2)

Operating Temperature Range −40˚C ≤ T

Supply Voltage, V

Driver Supply Voltage, V

Output Driver Voltage, V

A

DR

DR

Ground Difference |GND - DR GND| 0V to 300 mV

Upper Reference Voltage (V

Lower Reference Voltage (V

V

Voltage Range VRBto V

IN

) 0.5V to (VA−0.3V)

RT

) 0Vto(VRT−0.5V)

RB

+2.4V to +3.6V

Converter Electrical Characteristics

The following specifications apply for VA=VDR= +3.0VDC,VRT= +1.9V, VRB= 0.3V, CL= 10 pF, f

cycle. Boldface limits apply for T

A=TMIN

to T

Symbol Parameter Conditions

: all other limits TA= 25˚C (Notes 7, 8)

MAX

Typical

(Note 9)

DC ACCURACY

INL Integral Non-Linearity

DNL Differential Non-Linearity

+0.5

−0.2

±

0.25

Missing Codes 0 (max)

FSE Full Scale Error 3.0

V

OFF

Zero Scale Offset Error 19 27 mV (max)

ANALOG INPUT AND REFERENCE CHARACTERISTICS

V

IN

C

IN

R

IN

Input Voltage 1.6

VINInput Capacitance

RINInput Resistance

V

= 0.75V +0.5

IN

Vrms

(CLK LOW) 3 pF

(CLK HIGH) 4 pF

>

1MΩ

BW Full Power Bandwidth 270 MHz

V

RT

V

RB

R

REF

I

ref

Top Reference Voltage 1.9

Bottom Reference Voltage 0.3

Reference Ladder Resistance VRTto V

RB

720

Reference Ladder Current VRT to VRB 2.2

CLK, PD DIGITAL INPUT CHARACTERISTICS

V

IH

V

IL

I

IH

I

IL

C

IN

Logical High Input Voltage VDR=VA= 3.6V 2.0 V (min)

Logical Low Input Voltage VDR=VA= 2.7V 0.8 V (max)

Logical High Input Current VIH=VDR=VA= 3.6V 10 nA

Logical Low Input Current VIL= 0V, VDR=VA= 2.7V −50 nA

Logic Input Capacitance 3 pF

DIGITAL OUTPUT CHARACTERISTICS

= 60 MHz at 50% duty

CLK

Limits

(Note 9)

+1.9

−1.35

±

0.90 LSB (max)

±

13 mV (max)

V

RB

V

RT

V

A

0.5 V (min)

− 0.5 V (max)

V

RT

0 V (min)

590 Ω (min)

1070 Ω (max)

1.5 mA

2.7 mA

+85˚C

+2.4V to V

1.8V to V

Units

(Limits)

LSB (max)

LSB (min)

V (min)

V (max)

V (max)

≤

A

A

A

RT

www.national.com 4

Converter Electrical Characteristics (Continued)

The following specifications apply for VA=VDR= +3.0VDC,VRT= +1.9V, VRB= 0.3V, CL= 10 pF, f

cycle. Boldface limits apply for T

A=TMIN

to T

Symbol Parameter Conditions

V

OH

V

OL

High Level Output Voltage VA=VDR= 2.7V, IOH= −400 µA 2.6 2.4 V (min)

Low Level Output Voltage VA=VDR= 2.7V, IOL= 1.0 mA 0.4 0.5 V (max)

DYNAMIC PERFORMANCE

ENOB Effective Number of Bits

SINAD Signal-to-Noise & Distortion

SNR Signal-to-Noise Ratio

SFDR Spurious Free Dynamic Range

THD Total Harmonic Distortion

HD2 2nd Harmonic Distortion

HD3 3rd Harmonic Distortion

IMD Intermodulation Distortion

POWER SUPPLY CHARACTERISTICS

I

A

DRI

I

A

DRI

+

Analog Supply Current

Output Driver Supply Current

D

Total Operating Current

D

PC Power Consumption

PSRR

PSRR

Power Supply Rejection Ratio

1

Power Supply Rejection Ratio SNR with 200 mW at 1MHz on supply 45 dB

2

AC ELECTRICAL CHARACTERISTICS

f

C1

f

C2

t

CL

t

CH

Maximum Conversion Rate 80 60 MHz (min)

Minimum Conversion Rate 10 MHz

Minimum Clock Low Time 0.62 ns (min)

Minimum Clock High Time 0.62 ns (min)

DC Clock Duty Cycle

t

OH

t

OD

Output Hold Time CLK to Data Invalid 5.2 ns

Output Delay CLK to Data Transition 7.1

Pipeline Delay (Latency) 5 Clock Cycles

t

AD

Sampling (Aperture) Delay CLK Rise to Acquisition of Data 2.6 ns

: all other limits TA= 25˚C (Notes 7, 8)

MAX

Typical

(Note 9)

f

= 10.1 MHz, VIN= FS − 0.25 dB 7.6 6.9 Bits

IN

f

= 29 MHz, VIN= FS − 0.25 dB 7.4 Bits (min)

IN

f

= 10.1 MHz, VIN= FS − 0.25 dB 47.4 43.3 dB

IN

f

= 29 MHz, VIN= FS − 0.25 dB 46.1 dB (min)

IN

f

= 10.1 MHz, VIN= FS − 0.25 dB 48 44.5 dB

IN

f

= 29 MHz, VIN= FS − 0.25 dB 47.2 dB (min)

IN

f

= 10.1 MHz, VIN= FS − 0.25 dB 59.1 dBc

IN

f

= 29 MHz, VIN= FS − 0.25 dB 54.5 dBc

IN

f

= 10.1 MHz, VIN= FS − 0.25 dB −56.9 dBc

IN

f

= 29 MHz, VIN= FS − 0.25 dB −53.3 dBc

IN

f

= 10.1 MHz, VIN= FS − 0.25 dB -61.1 dBc

IN

f

= 29 MHz, VIN= FS − 0.25 dB −54.9 dBc

IN

f

= 10.1 MHz, VIN= FS − 0.25 dB −64.2 dBc

IN

f

= 29 MHz, VIN= FS − 0.25 dB −63.1 dBc

IN

f

= 11 MHz, VIN= FS − 6.25 dB

1

= 12 MHz, VIN= FS − 6.25 dB

f

2

−55 dBc

DC Input 13 15.9 mA (max)

f

= 10 MHz, VIN=FS−3dB 14 mA

IN

DC Input 0.04 0.2 mA (max)

f

= 10 MHz, VIN=FS−3dB 4.2 mA

IN

DC Input 13 16.1

f

= 10 MHz, VIN= FS − 3 dB, PD =

IN

Low

18.2

CLK Low, PD = Hi 0.33

DC Input 39 48.3 mW (max)

f

= 10 MHz, VIN= FS − 3 dB, PD =

IN

Low

53

CLK Low, PD = Hi 0.3 mW

FSE change with 2.7V to 3.3V change

in V

A

−51 dB

5

95

= 60 MHz at 50% duty

CLK

Limits

(Note 9)

(Limits)

mA (max)

5.0 ns (min)

9.4 ns (max)

ADC08L060

Units

mW

%(min)

%(max)

www.national.com5

Converter Electrical Characteristics (Continued)

The following specifications apply for VA=VDR= +3.0VDC,VRT= +1.9V, VRB= 0.3V, CL= 10 pF, f

cycle. Boldface limits apply for T

A=TMIN

to T

ADC08L060

Symbol Parameter Conditions

: all other limits TA= 25˚C (Notes 7, 8)

MAX

Typical

(Note 9)

DYNAMIC PERFORMANCE

t

AJ

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is

functional, but do not guarantee specific performance limits. For guaranteed specifications and test conditions, see the Electrical Characteristics. The guaranteed

specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test

conditions.

Note 2: All voltages are measured with respect to GND = AGND = DR GND = 0V, unless otherwise specified.

Note 3: When the input voltage at any pin exceeds the power supplies (that is, less thanAGND or DR GND, or greater than V

be limited to 25 mA. The 50 mA maximum package input current rating limits the number of pins that can safely exceed the power supplies with an input current of

25 mA to two.

Note 4: The absolute maximum junction temperature (T

junction-to-ambient thermal resistance (θ

TSSOP, θ

this device under normal operation will typically be about 49 mW (40 mW quiescent power + 4 mW reference ladder power+5mWtodrive the output bus

capacitance). The values for maximum power dissipation listed above will be reached only when the ADC08L060 is operated in a severe fault condition (e.g., when

input or output pins are driven beyond the power supply voltages, or the power supply polarity is reversed). Obviously, such conditions should always be avoided.

Note 5: Human body model is 100 pF capacitor discharged through a 1.5 kΩ resistor. Machine model is 220 pF discharged through ZERO Ohms.

Note 6: See AN-450, “Surface Mounting Methods and Their Effect on Product Reliability”.

Note 7: The analog inputs are protected as shown below. Input voltage magnitudes up to V

However, errors in the A/D conversion can occur if the input goes above V

voltage must be ≤2.8V

Aperture Jitter 2 ps rms

A

max) for this device is 150˚C. The maximum allowable power dissipation is dictated by TJmax, the

), and the ambient temperature (TA), and can be calculated using the formula PDMAX=(TJmax − TA)/θJA. In the 24-pin

is 92˚C/W, so PDMAX = 1,358 mW at 25˚C and 706 mW at the maximum operating ambient temperature of 85˚C. Note that the power consumption of

JA

to ensure accurate conversions.

DC

JA

J

+ 300 mV or to 300 mV below GND will not damage this device.

or below GND by more than 100 mV. For example, if VAis 2.7VDCthe full-scale input

DR

A

= 60 MHz at 50% duty

CLK

Limits

(Note 9)

or VDR), the current at that pin should

Units

(Limits)

20041707

Note 8: To guarantee accuracy, it is required that VAand VDRbe well bypassed. Each supply pin must be decoupled with separate bypass capacitors.

Note 9: Typical figures are at T

Level).

Note 10: I

voltage, V

driver power supply voltage, C

is the current consumed by the switching of the output drivers and is primarily determined by the load capacitance on the output pins, the supply

DR

, and the rate at which the outputs are switching (which is signal dependent), IDR=VDR(COxfO+C1xf1+…+C71xf7) where VDRis the output

DR

= 25˚C, and represent most likely parametric norms. Test limits are guaranteed to National’s AOQL (Average Outgoing Quality

J

is the total capacitance on any given output pin, and fnis the average frequency at which that pin is toggling.

n

www.national.com 6

Loading...

Loading...