TL/F/9492

54F/74F182 Carry Lookahead Generator

December 1994

54F/74F182

Carry Lookahead Generator

General Description

The ’F182 is a high-speed carry lookahead generator. It is

generally used with the ’F181 or ’F381 4-bit arithmetic logic

units to provide high-speed lookahead over word lengths of

more than four bits.

Features

Y

Provides lookahead carries across a group of four

ALUs

Y

Multi-level lookahead high-speed arithmetic operation

over long word lengths

Y

Guaranteed 4000V minimum ESD protection

Commercial Military

Package

Package Description

Number

74F182PC N16E 16-Lead (0.300×Wide) Molded Dual-In-Line

54F182DM (Note 2) J16A 16-Lead Ceramic Dual-In-Line

74F182SJ (Note 1) M16D 16-Lead (0.300×Wide) Molded Small Outline, EIAJ

54F182FM (Note 2) W16A 16-Lead Cerpack

54F182LM (Note 2) E20A 20-Lead Ceramic Leadless Chip Carrier, Type C

Note 1: Devices also available in 13×reel. Use suffixeSCX and SJX.

Note 2: Military grade device with environmental and burn-in processing. Use suffix

e

DMQB, FMQB and LMQB

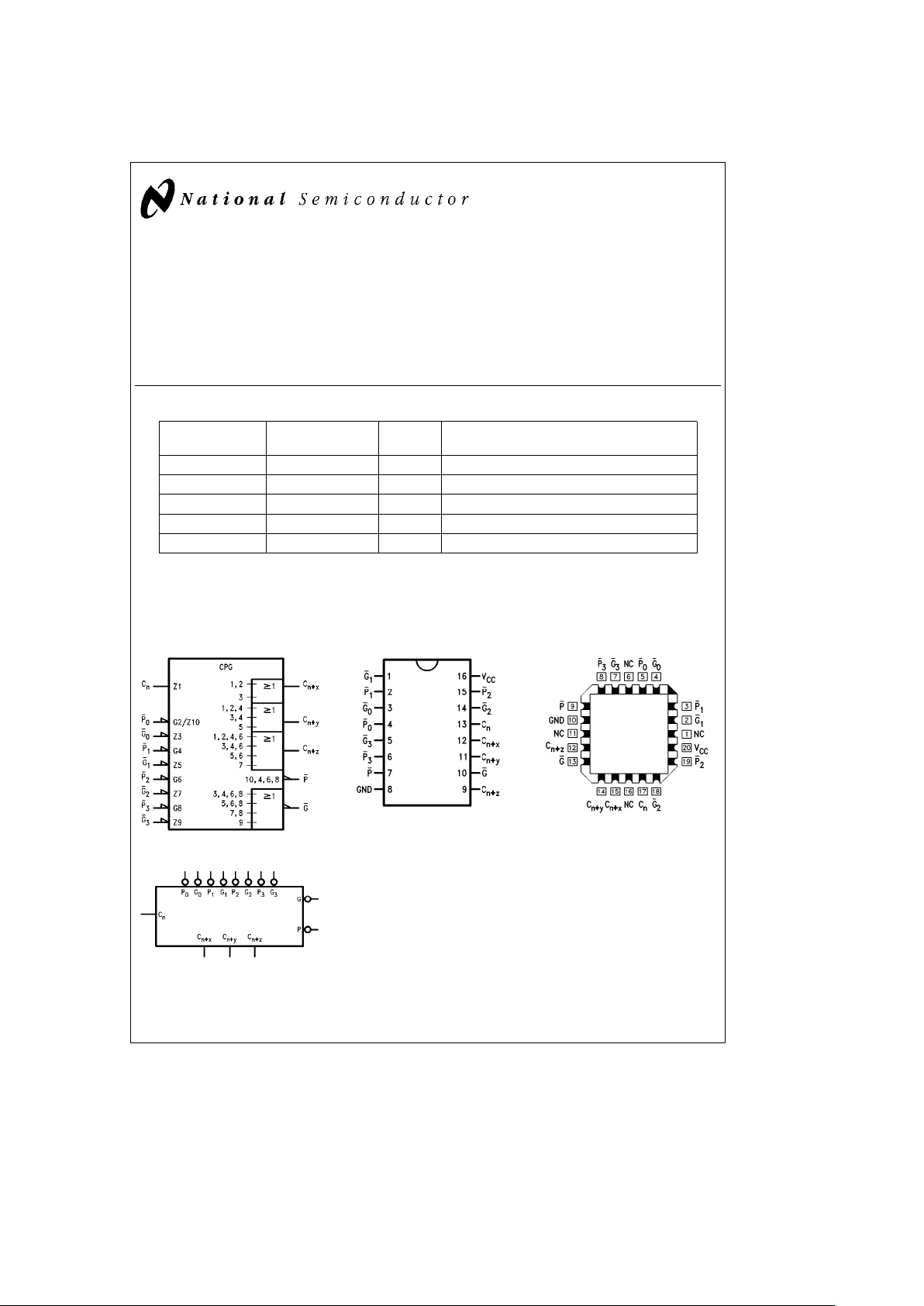

Logic Symbols Connection Diagrams

IEEE/IEC

TL/F/9492– 6

TL/F/9492– 3

Pin Assignment for

DIP, SOIC and Flatpak

TL/F/9492– 1

Pin Assignment

for LCC

TL/F/9492– 2

TRI-STATEÉis a registered trademark of National Semiconductor Corporation.

C

1995 National Semiconductor Corporation RRD-B30M105/Printed in U. S. A.

Unit Loading/Fan Out

54F/74F

Pin Names Description

U.L. Input I

IH/IIL

HIGH/LOW Output IOH/I

OL

C

n

Carry Input 1.0/2.0 20 mA/b1.2 mA

G

0,G2

Carry Generate Inputs (Active LOW) 1.0/14.0 20 mA/b8.4 mA

G

1

Carry Generate Input (Active LOW) 1.0/16.0 20 mA/b9.6 mA

G

3

Carry Generate Input (Active LOW) 1.0/8.0 20 mA/b4.8 mA

P

0,P1

Carry Propagate Inputs (Active LOW) 1.0/8.0 20 m A/b4.8 mA

P

2

Carry Propagate Input (Active LOW) 1.0/6.0 20 mA/b3.6 mA

P

3

Carry Propagate Input (Active LOW) 1.0/4.0 20 mA/b2.4 mA

C

nax

b

C

naz

Carry Outputs 50/33.3

b

1 mA/20 mA

G

Carry Generate Output (Active LOW) 50/33.3

b

1 mA/20 mA

P

Carry Propagate Output (Active LOW) 50/33.3

b

1 mA/20 mA

Functional Description

The ’F182 carry lookahead generator accepts up to four

pairs of Active LOW Carry Propagate (P

0–P3

) and Carry

Generate (G

0–G3

) signals and an Active HIGH Carry input

(C

n

) and provides anticipated Active HIGH carries (C

nax

,

C

nay,Cnaz

) across four groups of binary adders. The

’F182 also has Active LOW Carry Propagate (P

) and Carry

Generate (G

) outputs which may be used for further levels

of lookahead. The logic equations provided at the outputs

are:

C

nax

e

G

0

a

P0C

n

C

nay

e

G

1

a

P1G

0

a

P1P0C

n

C

naz

e

G

2

a

P2G

1

a

P2P1G

0

a

P2P1P0C

n

G

e

G

3

a

P3G

2

a

P3P2G

1

a

P3P2P1G

0

P

e

P2P2P1P

0

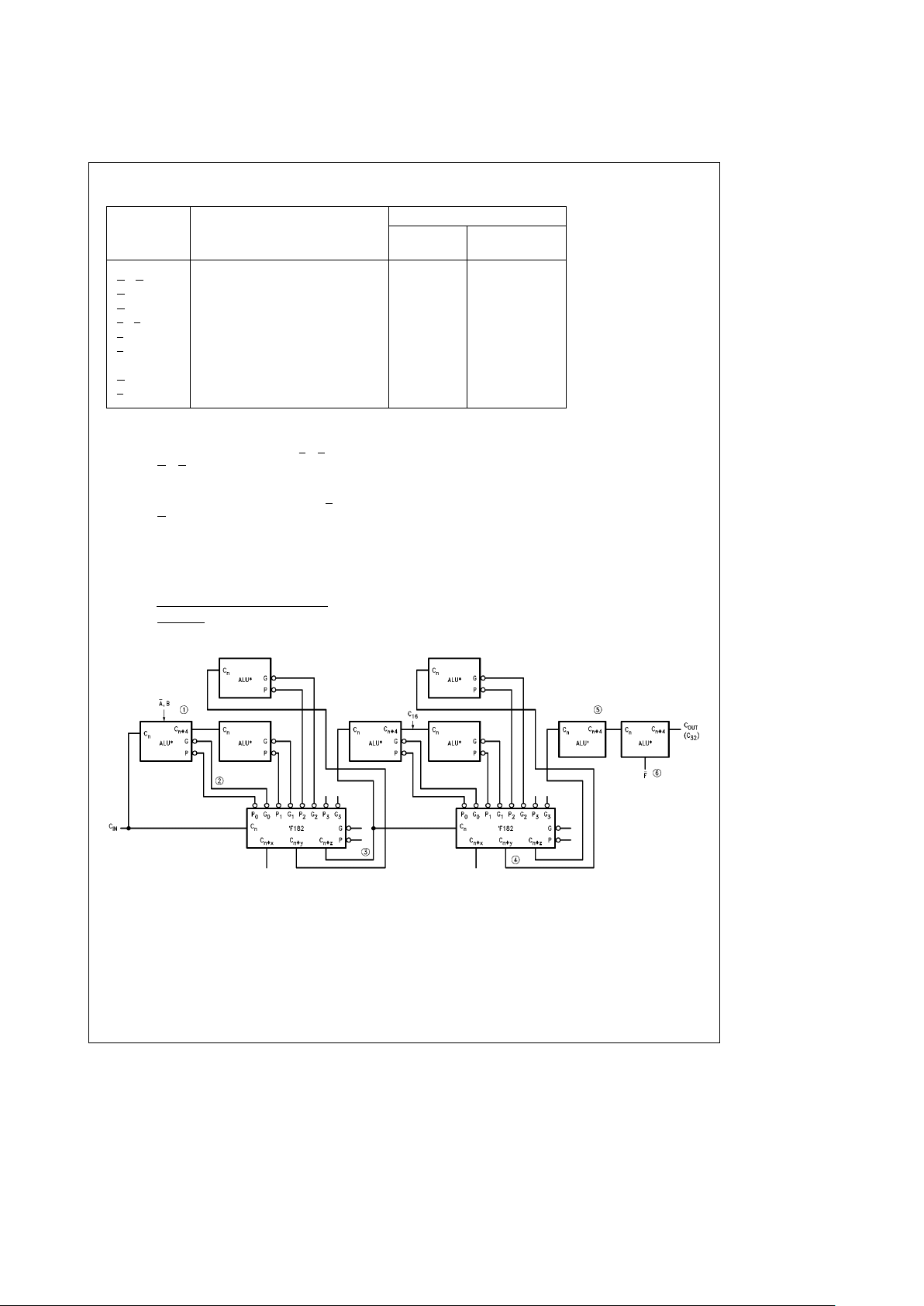

Also, the ’F182 can be used with binary ALUs in an active

LOW or active HIGH input operand mode. The connections

(Figure 1)

to and from the ALU to the carry lookahead generator are identical in both cases. Carries are rippled between lookahead blocks. The critical speed path follows the

circled numbers. There are several possible arrangements

for the carry interconnects, but all achieve about the same

speed. A 28-bit ALU is formed by dropping the last ’F181 or

’F381.

TL/F/9492– 5

FIGURE 1. 32-Bit ALU with Rippled Carry between 16-Bit Lookahead ALUs

*ALUs may be either ’F181 or ’F381

2

Truth Table

Inputs Outputs

CnG0P0G1P1G2P2G3P3C

naxCnayCnaz

G P

XHH L

LHX L

XLX H

HXL H

XXXHH L

XHHH X L

LHXHX L

XXXLX H

XLXXL H

HXLXL H

XXXXXHH L

X XXHHHX L

XHHHXHX L

LHXHXHX L

XXXXXL X H

XXXLXXL H

XLXXLXL H

HXLXLXL H

X XXXXHH H

XXXHHHX H

X HHHXHX H

H HXHXHX H

X XXXXLX L

X XXLXXL L

XLXXLXL L

L XLXLXL L

HXXX H

XHXX H

XXHX H

XXXH H

LLLL L

H

e

HIGH Voltage Level

L

e

LOW Voltage Level

X

e

Immaterial

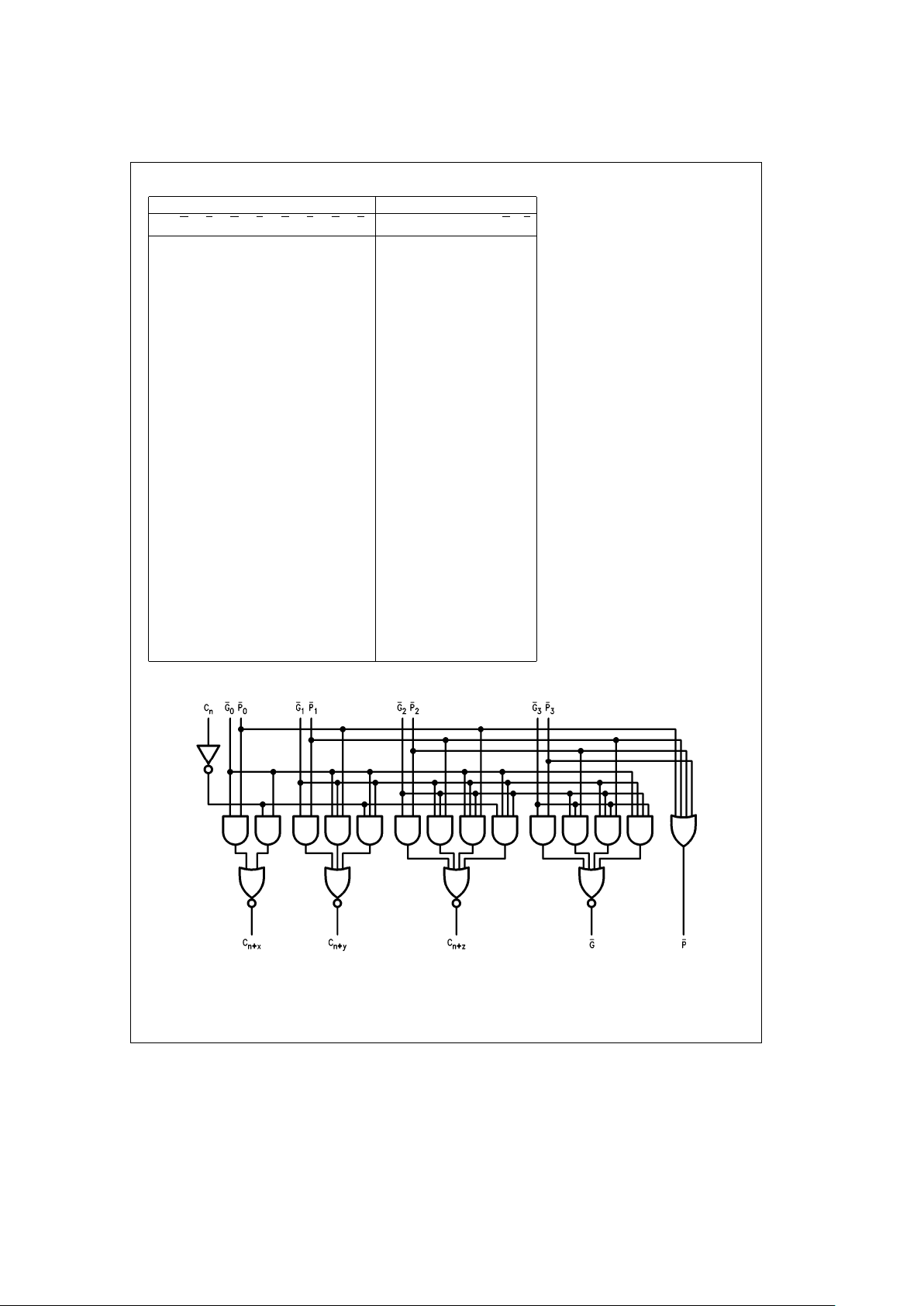

Logic Diagram

TL/F/9492– 4

Please note that this diagram is provided only for the understanding of logic operations and should not be used to estimate propagation delays.

3

Loading...

Loading...