NIPPON PRECISION CIRCUITS INC.

NIPPON PRECISION CIRCUITS-1

SM5004 Series

Quartz Crystal Oscillator IC

OVERVIEW

The SM5004 Series crystal oscillator module ICs fabricated in NPC’s Molybdenum-gate CMOS. They comprise

low-voltage low-current consumption oscillator circuits

and output buffers. They incorporate built-in oscillation

capacitance with superior frequency response to realize

without any external components.

FEATURES

⋅ Oscillation frequency up to 30MHz

⋅ Fundamentally oscillation

⋅ 4.5 to 5.5 V supply voltage

⋅ Inverter amplifier feedback resistance built-in (Rf )

⋅ Oscillation capacitances built-in (CG and CD)

⋅ Output drive capability : 8 mA (VDD=4.5V)

⋅ Output frequency : fo, fo/2, fo/4, fo/8

⋅ Output duty level

CMOS, TTL, CMOS & TTL

⋅ Input level : TTL

⋅ 3 state function

⋅ Chip form (CF5004××)

⋅ 6 pin SOT (SM5004××H)

DEVICE LIST

Device Output duty level Output frequency Output (standby)

SM5004A1H CMOS f

0 Hi-Z (Stop oscillation)

SM5004A3H CMOS f

0/2 Hi-Z (Stop oscillation)

SM5004A5H CMOS, TTL f

0/4 Hi-Z (Stop oscillation)

SM5004A7H CMOS, TTL f

0/8 Hi-Z (Stop oscillation)

SM5004B1H TTL f

0 Hi-Z (Stop oscillation)

SM5004B3H TTL f

0/2 Hi-Z (Stop oscillation)

Notes:

CF5004×× is Chip form.

SM5004××H is 6 pin SOT.

NIPPON PRECISION CIRCUITS-2

SM5004 Series

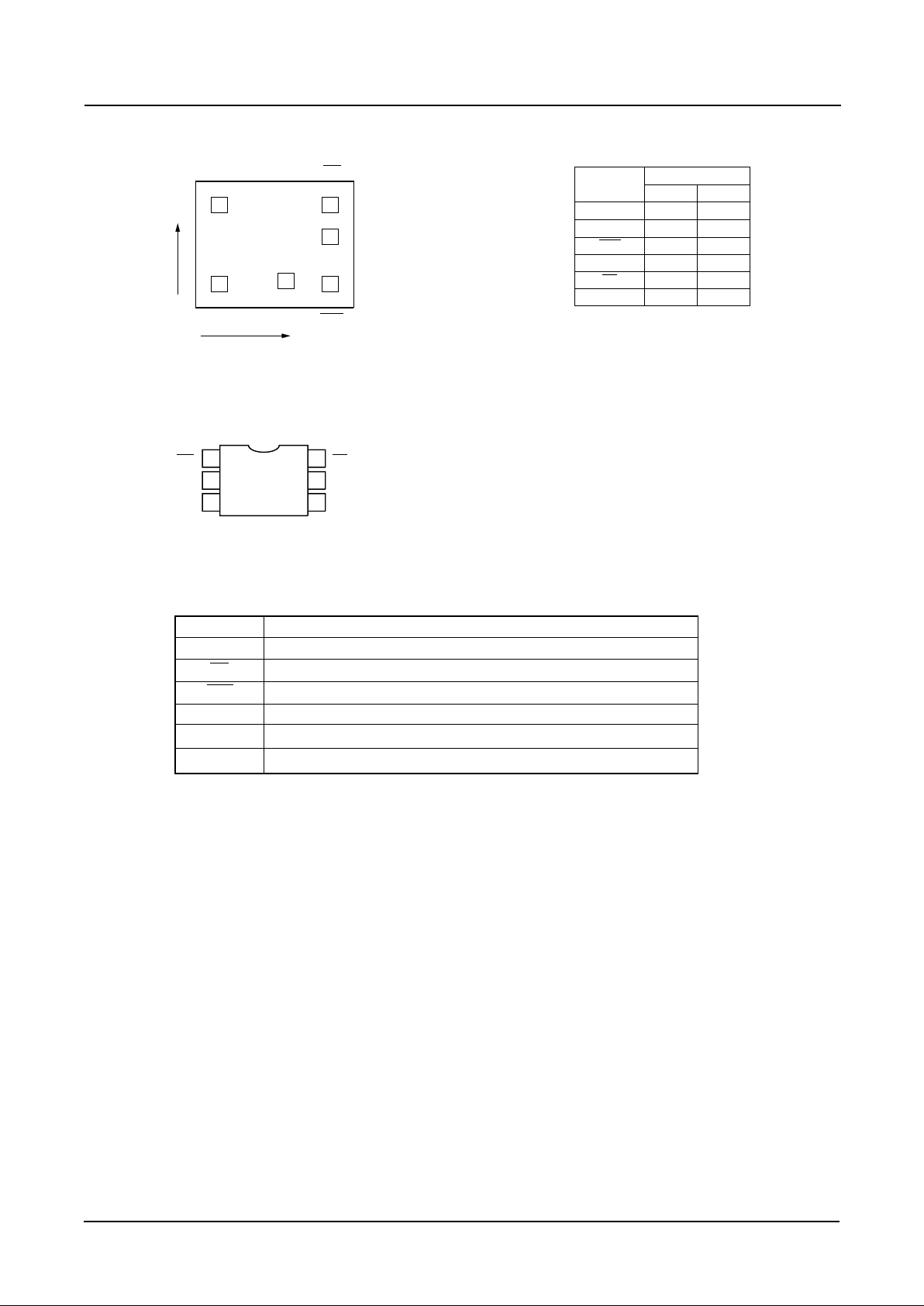

PAD DIMENSIONS

Q

XT

(1000,800)

VDD

INHXTVSS

(0,0)

X

Y

PAD COORDINATES

Name Coordinates (µm)

XY

VSS 150 150

XT 570 170

INH 850 150

VDD 850 450

XT 850 650

Q 150 650

Chip size : 1.00×0.80 mm

Chip thickness : 250 ± 30 µm

Chip reverse side : VDD level

PIN CONFIGURATION

(Top view)

1INH

2XT

3VSS 4 Q

5 VDD

6XT

TERMINAL DESCRIPTIONS

Name Descriptions

XT

XT

INH

VDD

VSS

Q

Oscillator input pin

Oscillator output pin

Output state control input pin (with buit-in pull-up resistance)

Supply voltage

Ground

Output pin

NIPPON PRECISION CIRCUITS-3

SM5004 Series

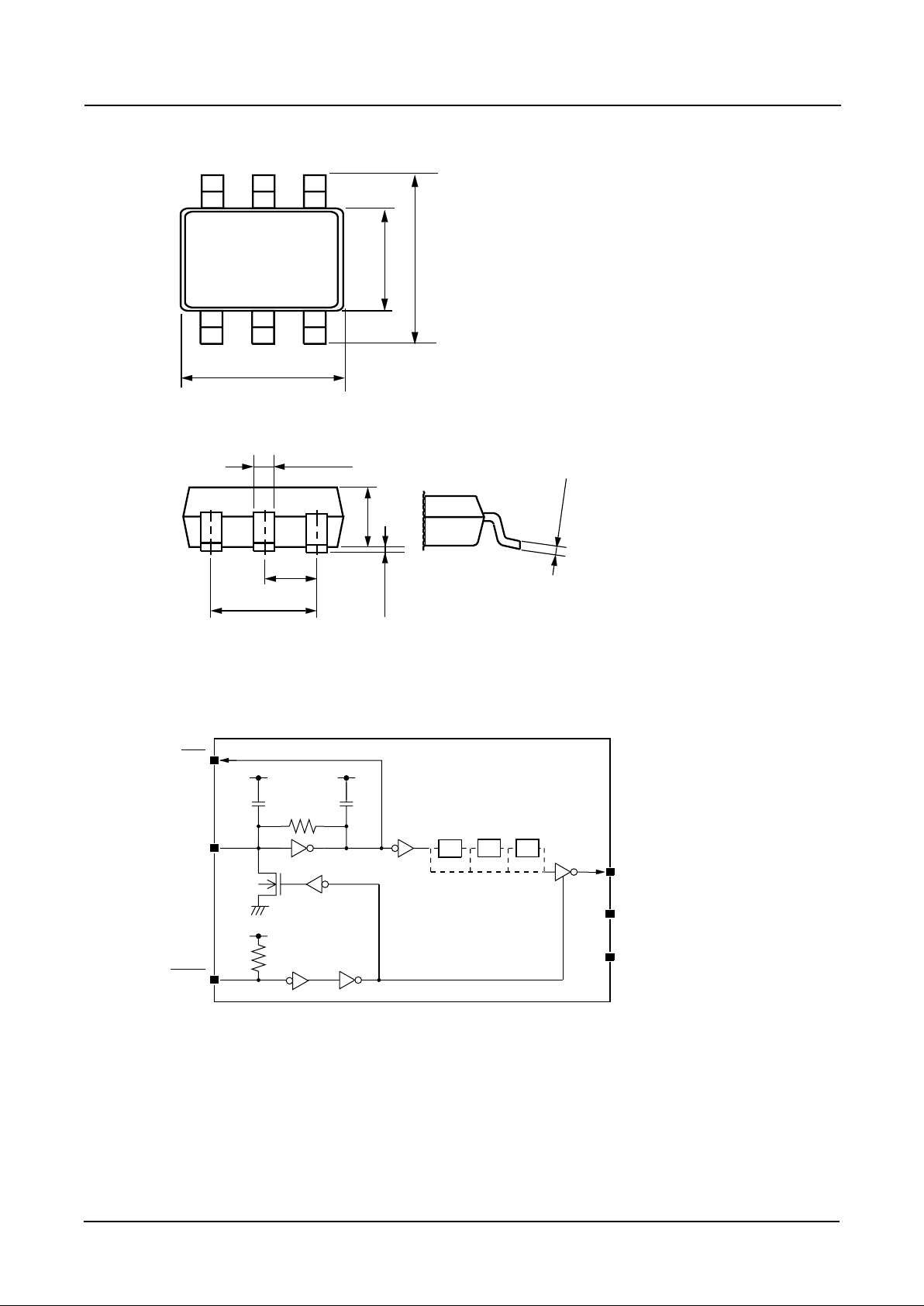

BLOCK DIAGRAM

XT

XT

INH

VSS

VDD

Q

CG CD

Rf

1/2

1/2 1/2

PACKAGE DIMENSIONS

(6 pin SOT)

2.9±0.2

0.95

2.8

0.40±0.1

0.15

+0.1

−0.05

1.60

1.1±0.1

+2.0

−0.1

+2.0

−0.3

0 to 0.15

1.9±0.2

(Unit:mm)

NIPPON PRECISION CIRCUITS-4

SM5004 Series

SPECIFICATIONS

Absolute Maximum Ratings

Parameter Symbol Condition Rating Unit

Supply voltage range V

DD -0.5 to 7.0 V

Input voltage range V

IN -0.5 to VDD + 0.5 V

Output voltage range V

OUT -0.5 to VDD + 0.5 V

Strage temperature ranges T

STG Chip form -65 to 150 °C

6 pin SOT -55 to 125 °C

Power dissipation P

W 6 pin SOT 250 mW

Output current I

OUT 13 mA

Soldering temperture T

SLD 6 pin SOT 255 °C

Soldering time t

SLD 6 pin SOT 10 sec

(VSS = 0V unless otherwise noted)

Recommended Operating Conditions

(VSS= 0V unless otherwise noted)

Limit

Parameter Symbol Condition MIN TYP MAX Unit

Supply Voltage V

DD 4.5 5.5 V

Input voltage V

IN VSS VDD V

Operating temperature T

OPR -20 +80 °C

Electrical Characteristics

Limit

Parameter

Symbol Condition MIN TYP MAX Unit

HIGH-level output voltage VOH Q pin, test circuit 1, VDD= 4.5V, IOH= 8mA 3.9 4.2 V

LOW-level output voltage VOL Q pin, test circuit 2, VDD= 4.5V, IOL= 8mA 0.3 0.4 V

Output leakage current IZ Q pin, test circuit 2, VOH= VDD 10 µA

INH= Low, V

DD= 5.5V VOL= VSS 10 µA

HIGH-level input voltage VIH INH pin 2.0 V

LOW-level input voltage VIL INH pin 0.8 V

Current consumption IDD INH= OPEN, SM5004A×H 9 14 mA

test circuit 3, load circuit 1

C

L= 15pF, SM5004B×H 9 14 mA

f= 30MHz load circuit 2

Pull-up resistance RUP INH pin, test circuit 4 25 100 250 kΩ

AC feedback resistance Rf test circuit 5 100 200 400 kΩ

Internal capacitance C

G Design value, determined by the internal 17 20 23 pF

C

D wafer pattern. 17 20 23 pF

(VDD= 4.5 to 5.5V, VSS = 0V, Ta= -20 to 80°C, unless otherwise noted )

NIPPON PRECISION CIRCUITS-5

SM5004 Series

Switching Characteristics

Limit

Parameter Symbol Condition MIN TYP MAX Unit

Output rise time tr Test circuit 6, load circuit 1, C

L= 15pF 3.5 7 ns

0.1V

DD to 0.9VDD

Output fall time tf Test circuit 6, load circuit 1, CL= 15pF 3.5 7 ns

0.9V

DD to 0.1VDD

Output duty cycle DUTY Test circuit 6, Ta= 25˚C, VDD=5.0V 45 55 %

load circuit 1, C

L= 15pF, f= 30MHz (*1)

Output disable delay time t

PLZ Test circuit 6, Ta= 25˚C, VDD= 5.0V 100 ns

Output enable delay time t

PZL load circuit 1, CL= 15pF 100 ns

Duty level CMOS (VDD= 4.5 to 5.5V, VSS = 0V, Ta= -20 to 80°C, unless otherwise noted)

Duty level TTL (V

DD= 4.5 to 5.5V, VSS = 0V, Ta= -20 to 80 C, unless otherwise noted)

Limit

Parameter Symbol Condition MIN TYP MAX Unit

Output rise time tr Test circuit 6, load circuit 2, C

L= 15pF 2.5 7 ns

0.4V

DD to 2.4VDD

Output fall time tf Test circuit 6, load circuit 2, CL= 15pF 2.5 7 ns

2.4V

DD to 0.4VDD

Output duty cycle DUTY Test circuit 6, Ta= 25˚C, VDD=5.0V 45 55 %

load circuit 2, C

L= 15pF, f= 30MHz (*1)

Output disable delay time t

PLZ Test circuit 6, Ta= 25˚C, VDD= 5.0V 100 ns

Output enable delay time t

PZL load circuit 2, CL= 15pF 100 ns

Note:

(*1) Determined by the lot monitor.

NIPPON PRECISION CIRCUITS-6

SM5004 Series

TEST CIRCUITS

Signal

Generator

VDD

VSS

XT Q

R1 R2

C1

C1: 0.001µF

R1: 50

Ω

R2: 490 Ω

VOH

0V

Q output

Test Circuit 1

3.5 VP-P, 10MHz sine wave input signal

Test Circuit 3

3.5 VP-P, 30MHz sine wave input signal

Test Circuit 2

Test Circuit 4

Test Circuit 5

Test Circuit 6

Load Circuit 1

Load Circuit 2

VDD

VSS

Q

A

V

IOL, IZ

IZ

VOL

VOH

INH

Signal

Generator

VDD

VSS

XT Q

R1

I

DD

C1

C1: 0.001µF

R1: 50

Ω

A

VDD

VSS

INH

IPR

RUP=

V

DD

IPR

A

VDD

VSS

XT

XT

A

IRf

Rf=

V

DD

IRf

VDD

VSS

INH

XT

Q

R1

10kΩ

R2

10kΩ

Notes

R1 : SM5004 3H

R2 : SM5004 1H

SM5004 5H

SM5004 7H

C

L : 15pF(Including

proove capacity)

CL

Q output

C

L

CL=15pF(Including

proove capacity)

Q output

VDD

C

L

R

CL=15pF(Including

proove capacity)

R=800Ω

Output Disable/Enable Delay Times

Q output

INH

VIH

VIL

tPLZ

tPZL

INH inputwaveform tr = tf 10ns

NIPPON PRECISION CIRCUITS-7

SM5004 Series

Switching Time Test Waveforms

Duty level CMOS

tr,tf DUTY

Output duty cycle time

0.9VDD

0.1VDD

0.9VDD

0.1VDD

tr tf

Q output

DUTY measuring

voltage

(0.5VDD)

DUTY measuring

voltage

(0.5VDD)

Q output

TW

T

DUTY= (T

W/ T) 100 (%)

Duty level TTL

tr,tf DUTY

Output duty cycle time

2.4V

0.4V

2.4V

0.4V

tr

tf

Q output

DUTY measuring

voltage

(1.4V)

DUTY measuring

voltage

(1.4V)

Q output

TW

T

DUTY= (T

W/ T) 100 (%)

Note :

This waveform is provided by oscillating.

NIPPON PRECISION CIRCUITS-8

SM5004 Series

NC9512BE 1996 10

NIPPON PRECISION CIRCUITS INC.

NIPPON PRECISION CIRCUITS INC. reserves the right to make changes to the products described in this data sheet in order to

improve the design or performance and to supply the best possible products. Nippon Precision Circuits Inc. assumes no responsibility for

the use of any circuits shown in this data sheet, conveys no license under any patent or other rights, and makes no claim that the circuits

are free from patent infringement. Applications for any devices shown in this data sheet are for illustration only and Nippon Precision

Circuits Inc. makes no claim or warranty that such applications will be suitable for the use specified without further testing or modification. The products described in this data sheet are not intended to use for the apparatus which influence human lives due to the failure or

malfunction of the products. Customers are requested to comply with applicable laws and regulations in effect now and hereinafter, including compliance with export controls on the distribution or dissemination of the products. Customers shall not export, directly or indirectly, any products without first obtaining required licenses and approvals from appropriate government agencies.

NIPPON PRECISION CIRCUITS INC.

4-3, 2-chome Fukuzumi, Koto-ku

Tokyo, 135 -8430, JAPAN

Telephon: 03-3642-6661

Facsimile: 03-3642-6698

Loading...

Loading...