Page 1

Gals

Iban

Service

SaO2/ETCO2

Model

Part

This

manual

based

July

20,

Number

on

Version

Manual

Monitor

7000

1989

5007-90-P3

5.7

-

CPU

|

software.

Wallingford,

No

part

of

permission

Novametrix

Connecticut,

this

manual

of

Novametrix

Medical

may

Preliminary

Systems

U.S.A:

be

reproduced

Medical

Systems

Inc.,

06492.

Documentation

©1988.

All

rights

without

Inc.

Printed

reserved.

the

written

in

U.S.A.

_

Page 2

Spor

fose-

Fl"

"BSV;

Gama

5/5065

+

SOF

|

-

Saca

é

Cea

Span

GO

par

Truscbeer

Saoz

-

pré

PQ

~

+498

49776

ISO

ua

/

19500

A

65001-

JÍ

과

4

3

#

TİJ

Ab?

pee

750

1395)

exchenge

-01

9/8

—

coed

一

|

cred

ão

CET

delay

7

ömer

<7

Pyle

T.

asan

een

070"

591%

y

ete

bf

Va

so

TT

PRED

À

CRT

ponny

É

—

pÉs

pel

BASS

WS

BIS

|

Ga?

93550.00

GE)

4

ο...

#36

-

ced

CET

-/

8

бое

<8

-

/

ann,

ATİ

ン

yi

LAR

PARO

~

Page 3

Service

Manual:

Model

7000

Guarantee

Equipment

is

fully

guaranteed,

from

year

products

right

tion,

Novametrix’

Novametrix’

except

occur

Claims

portation

both

equipment.

Improper

out

release

with

to

perform

the

at

or

fuses,

during

for

company.

the

model

use,

following

Novametrix

manufactured

covering

of

date

the

stated

customer’s

obligations

option,

batteries,

normal

damages

mishandling,

guarantees

guarantee

replacement

service.

during

All

correspondence

name

specific

and

from

and

Guarantee

or

distributed

materials

shipment,

service(s)

installation.

under

calibration

number,

tampering

operating

further

any

except

other

this

of

shipment

and

instructions

guarantee

by

Novametrix

and

workmanship,

certain

for

than

one

at

its

factory,

guarantee

defective

any

gasses,

must

be

concerning

the

serial

with,

or

operation

obligations.

year.

at

are

limited

parts

without

filed

promptly

the

number

will

void

Coz

Medical

disposable

Novametrix

an

charge,

equipment

of

colt.

for

a

authorized

to

our

of

if

with

as

it

appears

the

equipment

this

guarantee

Systems

period

products

repairs,

of

reserves

repair

equipment,

said

defects

the

must

specify

on

Inc.,

one

and

the

sta-

or

at

trans-

the

with-

and

'

For

Caution:

by

or

This

Novametrix

retrieval

means,

Systems

Federal

on

the

document

system,

without

Inc.

Novametrix’

In

Connecticut,

(U.S.A.)

order

of a physician.

contains

Medical

Systems

translated,

prior

Service

factory

1-800-243-3444

call

Telex

Facsimile

law

restricts

information

Inc.,

transcribed,

explicit

written

Department

repair

Collect

956-054

(203)

which

and

service,

(203)

284-0753

this

device

is

proprietary

may

not

be

or

transmitted,

permission

265-7701

to

from

call

toll

free

sale,

distribution,

and

the

reproduced,

in

any

form,

Novametrix

or

use

property

stored

or

by

in

any

Medical

of

a

Novametrix

5007-90-P3

20-Jul-89

Page 4

Page 5

Service

Manual:

Model

7000

Table

of

Contents:

10

2.0

3.0

4.0

4.0

5.0

6.0

7.0

80

Table

Theory

11

1.2

1.3

1.4

1.5

1.6

1.7

1.8

19

110

Maintenance

21

2.2

2.3

2.4

。

Operational

3.1

3.2

3.3

3.4

Calibration

4.1

4.2

4.3

44

Assembly

4.1

42

|

Specifications..

5.1

5.2

5.3

5.4

55

Connecting

6.1

6.2

Troubleshooting

7.1

Partslists...............

8.1

8.2

of

Operation

Introduction.............

Power

CPU

MainCPUBoard#2403....................

VideoController#2404............................

CO2

Saturation

Motherboard,

SaO2

CO2

Supply

Memory

Front

Front

Sensors

Senmsor

..

#

2401.

#

2402................

End + 2418

End $ 2267, # 2268

CRT

nee

иьненииииолиизлинильзмишиниитоталили

Schedule..........

General....................

Battery

Fuses

Cleaning

OvervieW

Equipment

Monitor

Safety

A

Calibration

Adjustment

Software

Disassembly

Assembly

General........................

The

Oxygen

The

Optonst..........................

RS-232outputs..................

AnalogIn/Out........

20007

ASSY:

ASSY:

Maintenance

and

Line

Cord

the

Model

TeSS

Required

Tests.......

Checks.....................

and

Adjustments

Procedure

Updates...

and

Disassembly

CapnostatTM

Saturation

Monitor...

External

Guide

746668865.0.000

5007-00

5007-01

инь

Procedure.

ue

Sensor

SaO2

Equipment.

06

MODEL

06

MAIN

of

Contents

..

eserse

(2409), # 2421

Assembly,

and

(2407)

..............

Front

Panel..

ити

000

rennes

7000...

оноюонеиньзиононоьовавонотвотиниивиоиоини

ee

лилии

ee

ee

шииты,

ee

излить

scan

τος

cod

…

…

…

…

…

…

„8

9

38

40

42

42

42

43

44

44

44

44

51

...52

52

dre.

Instructions.

AN

…

52

.

58

.

64

70

.

70

72

73

…

73

...........

Sensor...

iii

.............asesesesesemes

아

나

아

이

아

아

아

아

아

아

아

아

이

아

7000

-

SAO2

AND

ASSY,

METAL

BOX,

아

아

마

ETCO2

eric

라

라

여

라

MODEL

erezioni

ee

아

아

아

아

어

MONITOR

7000

마

아

아

마

아

.

...........................

마

이

…

…

…

…

ninni

아

아

이

아

이

...

73

.

73

.74

74

73

75

76

78

이

78

81

..

81

81

5007-90-P3

Preliminary

Documentation

20-Jul-89

(Rev.P3)

Page

1

Page 6

Table

of

Contents:

Service

Manual:

Model

7000

9.0

8.3

84

8.5

8.6

8.7

8.8

8.9

8.10

8.11

8.12

8.13

8.14

8.15

8.16

8.17

8.18

8.19

8.20

8.21

8.22

8.23

8.24

8.25

ASSY:

ASSY:

ASSY:

ASSY:

ASSY:

ASSY:

ASSY:

ASSY:

ASSY:

ASSY:

ASSY:

ASSY:

ASSY:

ASSY:

ASSY:

ASSY:

ASSY:

ASSY:

ASSY:

ASSY:

ASSY:

ASSY:

ASSY:

Schematics

4977-13

2400-01

2402-01

2403-01

2404-01

2405-01

2407-01

2409-01

2418-01

2421-01

5006-01

5055-01

2267-01

2267-17

2268-01

2268-17

5088-01

5062-01

5007-06

4998-01

5013-01

4959-01

5218-01

and

Assembly

02

TOP

06

MOTHER

04

CPU

04

MAIN

04

VIDEO

05

RAM

03

FRONT

02

PIGGYBACK

04

PIGGYBACK

01

FRONT

03

POWER

04

REAR

03

Sa02

00

FNT

03

FRONT

00

FNT

06

BEZEL

00

SAO2

XX

OPTION

02

CO2

02

REGULATOR

03

SENSOR

02

SENSOR

COVER

MEMORY

SIMM

FRONT

END

END

INPUT

SCREENED,

BOARD

CPU

BOARD

CONTROLLER

BOARD

END

BD

BD

BOARD

END

BOARD

HARNESS

PANEL

ASSY,

INPUT

DIGITAL

END

ANALOG

LIST,

HARNESS,

CAL

CAL

ASSY,

END

ANALOG

MODEL,

HARNESS,

HARNESS

RCPT

RECEPTACLE

ASSY,

BOARD

ASSY,

ASSY,

ASSEMBLY

ASSY

ASSEMBLY,

ASSY,

ASSY,

MODEL

BD

ASSY,

BD

BD

MODEL

ASSY,

MODEL

MODEL

ASSY,

MODEL

BD

ASSY,

(CTC),

MODEL

ASSY...........................

BD

ASSY,

ASSY

7000

MOD

7000

MODEL

ASSY,

7000..

7000...

MODEL

MODEL

MODEL

(CTC),

1260......

MODEL

7000

7000...

MODEL

MODEL

......

7000.

........

7000

MODEL

1260...

ASSY,

7000

7000...

7000..........

MODEL

MO!

7000

....

7000.

7

7000..

7000.

MODEL

7000..

Drawing6s...........cseccscssssecscecsssceeseceees

Page

2

Preliminary

Documentation

20-Jul-89

(Rev.P3)

5007-90-P3

Page 7

Service

Manual:

Model

7000

Theory

of

Operation:Introduction

1.0

11

Theory

of

Introduction

The

Model

reliable

rate,

infra-red

A

requirements,

after

sent

the

five

along

panel

used

connections

ease

changing

backup

possible

continuous

expired

light

user

friendly

the

unit

is

There

monitor’s

The

are

Status

softkeys,

for

of

or

with

the

jacks

the

“SaO2

system,

are

disassembly.

unit

can

a

programming

will

supply

battery

Operation

7000

is a

non-invasive

measurement,

CO2,

and

respiratory

sources

once

turned

five

menu

operation.

power

Cal

damage.

and

menu

display

programmed

off.

“softkeys”

displayed,

The

switch

Cell

used

INPUT”

The

jacks

run

through

operate

from

key

approximately

monitoring,

rate.

computing

system

any

which

front

and

and

found

perform

this

panel

indicators,

in

calibrating

“CO2

are

different

the

system’s

any

voltage

in

1

hour

portable

This

the

assists

changes

eliminates

is

Sa02/ETCO2

is

results

different

a

membrane

the

the

INPUT”

to

avoid

Motherboard

and

the

power

of

operation

and

display

performed

to

acquire

in

programming

are

permanently

commands

large

are

confusing

switch

ALERT

Capnostat™

for

the

connection

frequency

entry

module

with

monitor

of

by

the

overlay

RESET

(202

designed

oxygen

analyzing

correct

the

stored

depending

keypanels

and

sensor.

connection

of

the

via

removable

found

protection

on

in

the

the

rear

to

saturation,

the

changes

parameter

unit

for

in

memory

upon

and

which

of

circuitry

contains

AUDIO

The

the

two

wrong

world

sensor.

connectors

panel.

produce

pulse

in

results.

individual

even

the

pre-

simplifies

the

buttons,

two

front

sensors

All

for

by

simply

A

battery

to

prevent

The

monitor

to

as

the

functions

nicates

lines

The

tions,

Manual.

with

are

CRT

Various

The

different

*

2401

*

2402

*

2403

*

2404

*

2421

*

2418

*

2267

+

2268

+

Motherboard

is

“host”.

through

external

run

through

displays

displays

assemblies

Power

CPU

Main

Video

Digital

Analog

Digital

Analog

controlled

Consider

communication

equipment

the

the

by

the

Motherboard

waveforms

are

found

Supply

Memory

CPU

Board

Board

Board

Controller

CO2

Front

CO2

Front

SaO2

Front

SaO2

Front

the

Motorola

host

as

the

with

each

through

where

as

selected

available,

in

the

Model

-

End

Board

End

Board

End

Board

End

Board

MC68000

“brains”

board,

the

each

runs

rear

panel

all

the

by

the

is

described

7000

are

(previously

(previously

Microprocessor

of

the

system,

the

system

connectors.

individual

user

along

thoroughly

listed

below:

2407)

2409)

it

controls

software,

All

circuit

boards

with

which

the

in

is

referred

all

internal

and

commu-

communication

are

housed.

softkey

the

Operating

func-

5007-90-P3

Preliminary

Documentation

20-Jul-89

(Rev.P3)

Page

3

Page 8

¿Theory

of

Operation:Power

+

*

Supply

CRT

Front

#

2401

Assembly

Panel

Membrane

Switch

Overlay

Service

Manual:

Model

7000

1.2

Power

1.2.1

There

supply.

they

are

the

monitor.

or

even

it

is

used

used

to

within

1.22

AC

acceptable

AC/DC

The

power

AC

Plugged

*

Supply # 2401

Output

Three

charge

1260/7000

operation

level.

Both

voltages

are

four

used

to

Even

device

to

power

line

the

low

of

these

power

small

failure.

the

the

battery.

limits

operation

monitor

or

in

DC

mode

into

a

line

cord and

level

DC

voltages

critical

deviations

The

CRT

so

fourth

picture

While

that

the

digital

can

mode

occurs

properly

with

when

fuses

voltages

(+5V,

and

from

voltage

tube

this

voltage

components

operate

wired

either

its

internal

the

monitor

AC

are

in

supplied

+15V,

analog

their

(V

BAT)

and

operate

in

battery.

line

good

condition,

as

-15V)

components

nominal

need

the

fan,

may

be

properly.

AC

mode

is:

with

outputs

need

to

values

not

and

under

less

regulated

by

an

acceptable

and

from

be

closely

which

may

lead

be

as

tightly

AC

an

external

the

1260/7000

regulated

make

up

to

erroneous

regulated

operation

it

must

connection

operating

power

the

heart

mode

still

be

voltage

since

of

data

since

is

kept

to

an

+

the

rear

DC

operating

*

unit

is

operating

*

Power

*

AC

line

*

the

rear

While

operating

charged.

ating

operating

introduced

information

panel

1.2.3

The

battery

the

mode

As

level,

mode

into

occurs

indicates

DC

power

power

from

panel

mode

unplugged

level.

cord

and/or

power

panel

monitor

are

soon

as

or

the

is

the

monitor,

when

that

AC

source

source

being

power

power

met,

the

unit

automatically

entry

occurs

from

fuse

is

lost,

or

entry

is

connected

the

AC

line

is

turned

AC

switch

when

the

are

bad.

switch

monitor

voltage

initiated.

operating

switching

power

for

ruined

is

present.

the

DC

by a deep

is

set

either:

AC

line

is

set

to

an

acceptable

operates

into

on

while

mode

between

mode

is

discharge

ON

or

the

to

OFF

in

the

not

When

is

AC

and

the

internal

(|).

AC

voltage

(0).

AC

source

AC

mode

monitor

falls

connected

an

acceptable

restored.

DC

modes.

lead

under

DC

is

below

and

the

and

the

below

to

an

AC

AC

No

loss

of

The

AC

acid

battery.

operation,

an

acceptable

conditions

internal

the

acceptable

line

source,

line

is

once

monitor

LED

the

function

on

To

prevent

power

for

AC

battery

oper-

DC

again

the

front

the

supply

is

or

Page

4

Preliminary

Documentation

20-Jul-89

(Rev.P3)

5007-90-P3

Page 9

Service

Manual:

turns

warning

provide

up

volts

Model

7000

the

the

power,

when

monitor

is

provided

battery

a

constant

it

is

fully

of

when

to

alert

with

voltage

charged

battery

a

quick

down

voltage

the

user

charge

charging

to

before

while

method

the

turn

falls

to

a

the

turn

off

maintaining

is

used.

off

threshold

Theory

preset

of

threshold.

threshold

stand-by

The

battery

of

10.5

Operation:Power

A

“Low

is

actually

float

current

delivers

VDC.

between

Supply

#

2401

Battery”

reached.

for

To

back-

13.8

1.24

how

users.

changing

also

normal

erated

120

1.2.5

RAW

from

DC/BATTERY

SWITCH

MONITOR

whether

CONVERTER.

the

front

SIGNAL

ER,

and

DC

POWER

AC

AC

power

well

the

The

the

required

power

by

the

-

10%

Block

The

AC

DC

is

the

+BAT

is

the

processor

The

POWER

membrane

is

turning

to

the

supplies.

ON/OFF

power

1260/7000

source

input

power

voltage

when

line

system.

=

108

VAC

diagram

INPUT/RAW

fed

into

GENERATOR

SWITCH

sent

into

senses

RAW

The

as

well

ON/OFF

the

DC/BATTERY

RAW

keypanel

used

to

the

monitor

fan,.while

The

SIGNAL

depends

company

can

selector

going

conditions

For

and

operation

the

and

the

voltage

as

on

switch

from

example,

the

DC

block

+BAT

the

input

DC/BATTERY

controls

LATCH

and

control

+5V

on

the

DC-DC

output

for

the

the

and

not

only

can

regulate

its

primary

on

the

rear

100/120

in

excess

with

high-line

converts

GENERATOR

is

used

to

CRT/FAN

of

the

level

on

both

SWITCH

MONITOR.

the

AC

ON

is

activated

generates

outputs

off.

from

POWER

of

The

CONVERTER

the

ON

the

country

their

input

panel

VAC

to

of

10%

120

VAC

value

is

AC

and

charge

SWITCH.

DC-DC

the

should

LED

by

a

POWER

the

CRT/FAN

DC-DC

LED

on

in

which

power

given

between

power

200/240

of

the

nominal

nominal

120

+

10%

line

input

the

RAW

the

battery,

The

CONVERTER.

RAW

DC

send

RAW

also

sends

on

the

front

the

POWER

ON/OFF

CRT/FAN

SWITCH

SWITCH

provides

CONVERTER

the

front

the

monitor

the

varying

100,

entry

VAC.

DC/BATTERY

output

module.

Voltage

value

input,

=

132

VAC.

into

an

unregulated

and

is

of

The

and

BATTERY

DC

or

a

BATTERY

membrane

ON/OFF

RAW

SIGNAL.

and

provides

power

for

is

also

membrane

is

demands

120,

200,

A

fuse

fluctuations

are

expected

the

low

SWITCH.

also

sent

the

RAW

DC/BATTERY

lines

BATTERY

ON/OFF

keypanel.

SWITCH

The

POWER

the

DC-DC

power

the

to

+5V

used

to

keypanel.

used

but

of

240

VAC

change

due

and

line

voltage

DC

voltage.

The

output

to

the

DC/BATTERY

and

decides

to

the

DC-DC

signal

located

on

ON/OFF

CONVERT-

the

CRT

and

the

generate

also

their

by

is

to

tol-

is

RAW

LINE

to

the

tube

+15V

the

5007-90-P3

Preliminary

Documentation

20-Jul-89

(Rev.P3)

Page

5

Page 10

>

Theory

of

Operation:Power

Supply

#

2401

Service

Manual:

Mode!

7000

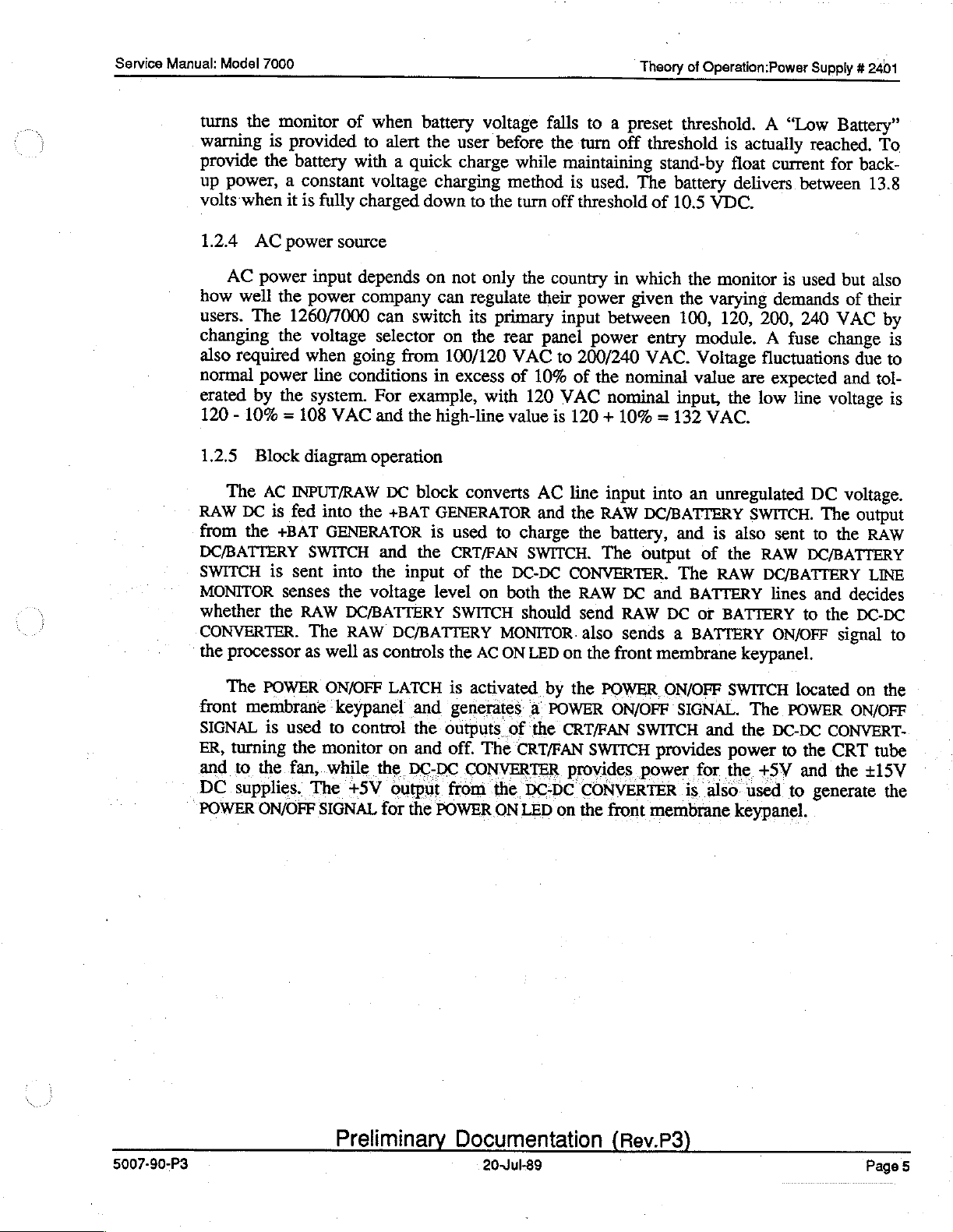

INPUT/RAW

POWER

ON/OFF.

FRONT

1.2.6

former,

integral

provides

the

ondary

D1

tors

following

DC

ACINPUT/RAW

The

AC

a

bridge

power

a

desired

during

to

produce

Cl,

C2,

equations,

varies

AC

D1,

ON

PANEL

INPUT/RAW

receptacle

voltage

and

according

DC

C1,

C2,

2400

C3

BOARD

———>

rectifier,

switch,

low-line

a

full

C3

+BAT

GENERÁTOR

REAR

PANEL

ON/OFF

>

07.

1024, IC2B,

DC

DC

and

voltage

for

the

selected

input

wave

rectified

on

the

Motherboard

an

AC

to

the

AC

RAW

MONITOR

ca,

RAWDC/BATTERY|__

02,

12V

BATTERY

POWER:

|

LATCH

+

IC1

block

block

several

selector

line

into

conditions.

line

line

capacitors.

cord.

the

output,

input

voltage

input

DC/BAT

G8,

СЧА

”|

VAL,

Y

SWITCH

2

08,

04

consists

switch,

The

dual

primary

The

which

to

make

of

and

the

——1——_—_———,

:

y]

of

The

fuse

primary

induces

secondary

120

monitor

CRT/

>|

FAN

SWITCH

06,

a

power

power

holder

is

filtered

UNREGULATED

VAC

DC.DC

CONVERTER

PS1

O1

entry

entry

and

transformer,

at

least

AC

voltage

and

is

power

—*

module,

module

RFI/

15

smoothed

assumed.

requirements:

ACLED

BATTERYON

Lo

==»

pa

+5v

ONLED

+15V

-15V

CRTÆAN

EMI

filter,

T1,

is

VAC

is

rectified

RAW

The

a

incorporates

wound

across

out

DC.

value

power

as

the

by

by

For

of

trans-

an

well

as

so

that

sec-

bridge

capaci-

all

the

RAW

“Page

6

RAW

The

maximum

imum

rectifier)

12.7

the

device

its

DC

THE

To

generate

CRT

is

input

current

and

Vripple

+BAT

and

located

the

put. A power

drop

in

voltage

DC

(VDC)

magnitude

draw

of

the

value

of

the

(VAC)

GENERATOR

the

voltage

the

fan,

an

adjustable

on

the

back

UNREGULATED

diode,

D2,

across

protects

the

Preliminary

=

Secondary

=

15

VAC

=21

VDC

of

ripple

the

system,

filter

=

=4A/(0.03

=

required

(AC

capacitors:

Current / (Capacitance * Frequency)

1.11

to

linear

panel

RAW

the

of

DC

IC

diode, a constant

AC

(min)

fluctuation)

the

frequency

F *

VAC

charge

voltage

the

monitor

and

during

voltage

Documentation

20-Jul-89

voltage

(Vrms) / .707

/.707

on

120

Hz)

the

battery

regulator

which

of

RAW

the

during

it

DC

ripple

AC

integrated

uses

as a heatsink.

produces a regulated

battery

operation,

charge

of

and

13.8

(Rev.P3)

is

related

(120

Hz

operation

circuit

14.5

is

VDC

allowing

VDC

(2.3

to

the

max-

for

a

bridge

and

power

used.

It

takes

at

its

for a 0.7

volts per

5007-90-P3

This

as

out-

V

Page 11

Service

Manual:

Modei

7000

Theory

of

Operation:Power

Supply

#

2401

battery

the

1.2.8

tion

volt

voltage

mary

switches

provided

also

from

lower

itor

that.

Taking

cell)

condition

AC/BATTERY

A

dual

of

both

reference.

divider

power

If

AC

sensed

becoming

trip

is

automatically

must:

the

ints

0f10.5

is

present

of

the

under/over

RAW

When

consisting

source

RAW

power

over

it

DC

declines

to

has

an

through

deeply

point

sets

be.

present’

diode

and

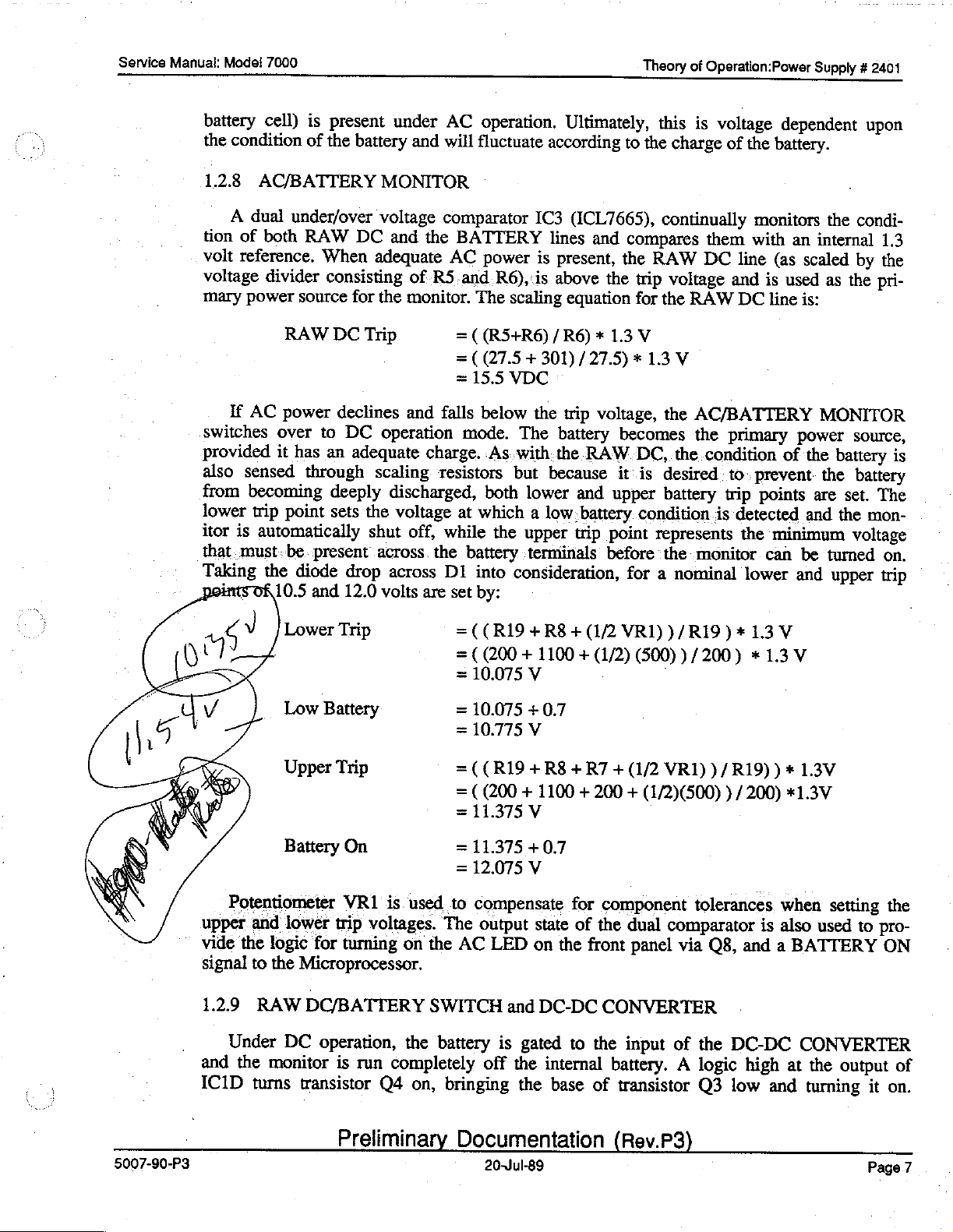

Lower

Trip

under

battery

MONITOR

voltage

DC

and

adequate

for

the

Trip

DC

operation

adequate

scaling

discharged,

the

voltage

shut

across.

drop

across

12.0

volts

AC

operation.

and

will

fluctuate

comparator

the

BATTERY

AC

power

of

R5.and-R6),:is

monitor.

The

= ( (R5+R6) / R6) * 1.3

=((27.5+

=

15.5

and

falls

below

mode.

charge.

resistors

As.with.the

both

at

which

off,

while

the

D1

are

the

battery

into

set

by:

=((R19+R8+(1/2VR1))/R19)+13V

= ( (200 + 1100 + (1/2)

=

10.075

Ultimately,

according

IC3

(ICL7665),

lines

and

is

present,

above

scaling

301)

the

equation

/27.5)*

VDC

the

trip

voltage,

The

battery

but

because

lower

a

low

upper

-terminals

consideration,

becomes

RAW

it

and

upper

battery

trip

point

before

V

this

is

voltage

to

the

charge

continually

compares

the

RAW

trip

voltage

for

the

V

1.3

V

the

DC,.the.condition

is

desired

battery

condition.

represents

the

for

a

nominal

(500)

)/

of

the

them

DC

line

and

RAW

DC

AC/BATTERY

the

primary

to-

trip

is

detected

the

monitor

lower

200) * 1.3

|

dependent

battery.

monitors

with

an

(as

scaled

is

used

line

is:

power

of

the

prevent

points

can

are

and

minimum

be

and

V

upon

the

condi-

internal

by

the

as

the

pri-

MONITOR

source,

battery

the

battery

set.

The

the

mon-

voltage

turned

upper

trip

1.3

is

on.

5007-90-P3

Low

Upper

Battery

Potentiometer

upper

vide

signal

1.2.9

and

ICID

and

the

logic

to

the

RAW

Under

the

monitor

turns

lower

DC

Battery

Trip

Оп

VR1

is

used

trip

voltages.

for

tuming

Microprocessor.

DC/BATTERY

operation,

is

run

transistor

Preliminary

on

the

SWITCH

the

completely

Q4

on,

=

10.075 + 0.7

=

10.775

=

(CR19

V

+R8 + R7 + (1/2

VR1)

= ( (200 + 1100 + 200 + (1/2)(500) ) /

=

11.375

=

11.375

=

12.075

to

compensate

The

output

AC

battery

bringing

Documentation

У

+07

У

state

LED

on

and

DC-DC

is

gated

off

the

the

20-Jul-89

for

component

of

the

the

front

CONVERTER

to

the

internal

base

battery.

of

(Rev.P3)

tolerances

dual

comparator

panel

input

transistor

via

of

A

the

logic

Q3

}/

R19) ) *

Q8,

and

DC-DC

high

low

200)

is

also

a

and

1.3V

*1.3V

when

setting

used

BATTERY

CONVERTER

at

the

output

turning

to

pro-

it

Page

the

ON

of

on.

7

Page 12

Theory

of

Operation:CPU

Memory # 2402

Service

Manual:

Model

7000

Transistor

switch

power

transistor

VERTER.

convert a 9

efficiency

from

nal

1.2.10

the

associated

line.

in

sideration

directly

1.2.11

closure

whose

flip-flop

this

the

tion

ON/OFF

Capacitor

for

from

ICIC,

the

monitor

CRT/FAN

To

avoid

CRT

Because

the

switch

off

POWER

The

POWER

ofthe

width

(IC2A),

pulse

present

is

detected

switch

of

and

LATCH

power-up.

Q3

then

the

battery

leaking

Q2

The

DC-DC

to

24

volt

about

the

75%.

POWER

is

on

SWITCH

the

loss

the

fan

circuitry

given

of

the

FET

and

the

IC1B

is

wasted

of

ON/OFF

ON/OFF

front

is

controlled

and a short

causes

state

the

until

by

will

C2

and

resistor

turns

into

back

is

off

CONVERTER

input

The

ON / OFF

via

the

of

require

used

has

high

the

panel

output

the

the

be

power

into

efficiency

to

when

POWER

transistor

the

CONVERTER.

the

and

D3

into

tightly

outputs

ON LED

only loosely

supply

very

low

the

power

ON/OFF

LATCH

LATCH

POWER

by

capacitor

pulse

of

the

next

positive

RAW

DC/BATTERY

forced

R17

cause

Q2

fully

on,

Back

RAW

LATCH.

when

CRT

requirements

DC

line.

is

forward-biased,

is a 50

regulated

of

the

located

going

the

CRT

resistance

tube

Watt

converter

The

on

the

through

regulated

display

when

and

of the

When

switching

+5,

are

+5v

supply

front

input

and

fan

LATCH.

receives

key,

is

generated

second D flip-flop

to

the

its

‘which:

Cl

and

clock

OFF

the

LATCH

control

appears

resistor

at

the Q not

edge.

MONITOR,

state

In

by

to

and

it

acts

biased

sending

+15,

panel.

turned

are

from a pulse

at

(IC2B)

the

diode

adequate

RAW

and

-15

enabled

line

the

DC-DC

power,

the

fan

on,

on,

which

CRT.

‘the

R3,

The

‘colle¢tor

is

debounced

output.

to

event

the

power

directly

with

very

toggle

that.a

transistor

be

reset

in

as a low

D3

prevents

RAW

DC

onto

supply

VDC

FET

directly

output

Q5

outputs

by

R25

Converter

switch

from

little

is

an

switch

generated

of

The

positive

and

low

of

and

the

OFF’

impedance

DC

is

present,

the

which

with

an

ON

is

used

and

Ol

the

power

important

is

controlled

during

Q7.

This

by

the

edge

to

latch

battery

the

POWER

resistor

state

battery

CON-

can

an

signal

to

sig-

since

and

its

+BAT

is

lost

con-

the

pulse,

first

D

of

onto

condi-

R13.

during

13

Page

8

CPU

1.3.1

age,

information.

per

(128K X 8)

up

low

1.3.2

inputs

transition

Memory

Memory

Two

types

and

SRAM

The

byte

(128K X 8)

and

in a similar

and

high).

Analog

The

analog

at a time.

of the

#

2402

of

memory

(SIMM

SRAM

is

and

is

enabled

manner.

to

Digital

to

When

LBWE

U2

Converter

digital

converter IC35

the

line.

Preliminary

devices

are

boards)

contained

is

enabled

by

the

which

CS11

Data

consists

line

lines

Documentation

used,

EPROM

for

temporary

on

two

2405-01

by

the

UBRE

LBRE

line.

of

two

The

has a multiplexed

is

low

IC49

D@-D3

20-Jul-89

feed

(IC2,

storage

SIMM

line,

EPROM

chips

(low

will

IC49

(Rev.P3)

3,

the

other

and

input

be

enabled

which

4,

and

5)

of

variables

boards,

handles

devices

high),

which

on

transfers

for

program

and

one

handles

the

IC2-IC5

and

U3

reads

the

positive

the

trending

the

lower

are

broken

(two

chips,

one

of

data

to

5007-90-P3

stor-

up-

byte

four

going

the

Page 13

Service

Manual:

Model

7000

Theory

of

Operation:Main

CPU

Board

#

2403

1.4

multiplexor

amplified

monitoring

IC35.

and

Main

1.4.1

The

MHz

program

peripheral

the

rest

packets

bits

16

Mbytes

protocol.

The

external

tions

by

CPU

The

heart

for

earlier

instruction

affected

of

the

that

of

the

MC68000

hardware

are

conducted

R/W

data

W=Write,

device.

1C34

is

(which

IC28A

handled

pin

by

1

IC28C

Board # 2403

Microprocessor

if

the

system

units).

system

are

either

word)

of

continuous

(Read/Write)

to

and

by

in

length

has

and

in

be

The

interpreting

the

via

one

various

the

a

smooth

sent

data

selects

and

instruction

a

word

memory

one

IC28B

pin

is

the

MC68000

16-bit

and

data

(the

a

24-bit

of

pin

8.

Motorola

oversees

it

to

of

full

space.

control

microprocessor

and

orderly

indicates

external

be

the

sent

from

from

to

four

7,

IC28D

IC41

deciding

its

task.

bus,

which

16-bits)

address

The

lines

to

manner:

the

direction

the

analog

develops

MC68000

Front

which

ensure

inputs).

pin

14

a

all

aspects

what

The

microprocessor

allows

or

one

bus

that

End

provide

that

of

device

microprocessor

to

The

is

a

spare

-10

volts

MPU

which

of

the

action

to

information

byte

(either

allows

Boards

“handshaking”

data

transfer

data

transfer.

microprocessor.

the

to

two

analog

input.

VREF

system,

take

the

communicate

the

Battery

for

runs

at

from

and

informing

communicates

to

be

the

high

processor

and

R=Read,

external

inputs

are

voltage

use

by

IC28

10

MHz

fetching

transferred

or

to

by

between

system

(8

the

with

in

low

8-

access

serial

the

func-

a

AS

(Address

placed

start

of a data

UDS,

LDS

length

ed

along

the

LBWE

DTACK

device

by

the

microprocessor

Strobe)

on

the

address

transfer

are

Upper

of

the

packet

with

R/W

by

(Lower

LDS:

information,

UDS:

ignore

UDS

information.

(Data

addressed

only

only

the

and

Byte

the

the

the

lower

LDS

Transfer

by

indicates

bus

by

the

cycle.

and

Lower

of

data

to

be

IC31,

Write

lower

upper

Enable),

byte

8-bits

upper

IC32B,

8-bits

8-bits.

together:

the

microprocessor

has

been

the

ACKnowledge),

received

that a valid

microprocessor

Data

Strobes,

transferred.

IC30C,

UBWE

of

the

data

should

contain

full

data

by

These

and

word

be

ignored.

valid

word

sent from

to

signal

the

device.

address

and

they

has

signals

indicate

signals

IC36F

contains

to

valid

information,

contains

the

that

the

data

been

the

the

are gat-

develop

valid

external

sent

5007-90-P3

Preliminary

Documentation

20-Jul-89

(Rev.P3)

Page

9

Page 14

Theory

of

Operation:Main

CPU

Board # 2403

Service

Manual:

Model

7000

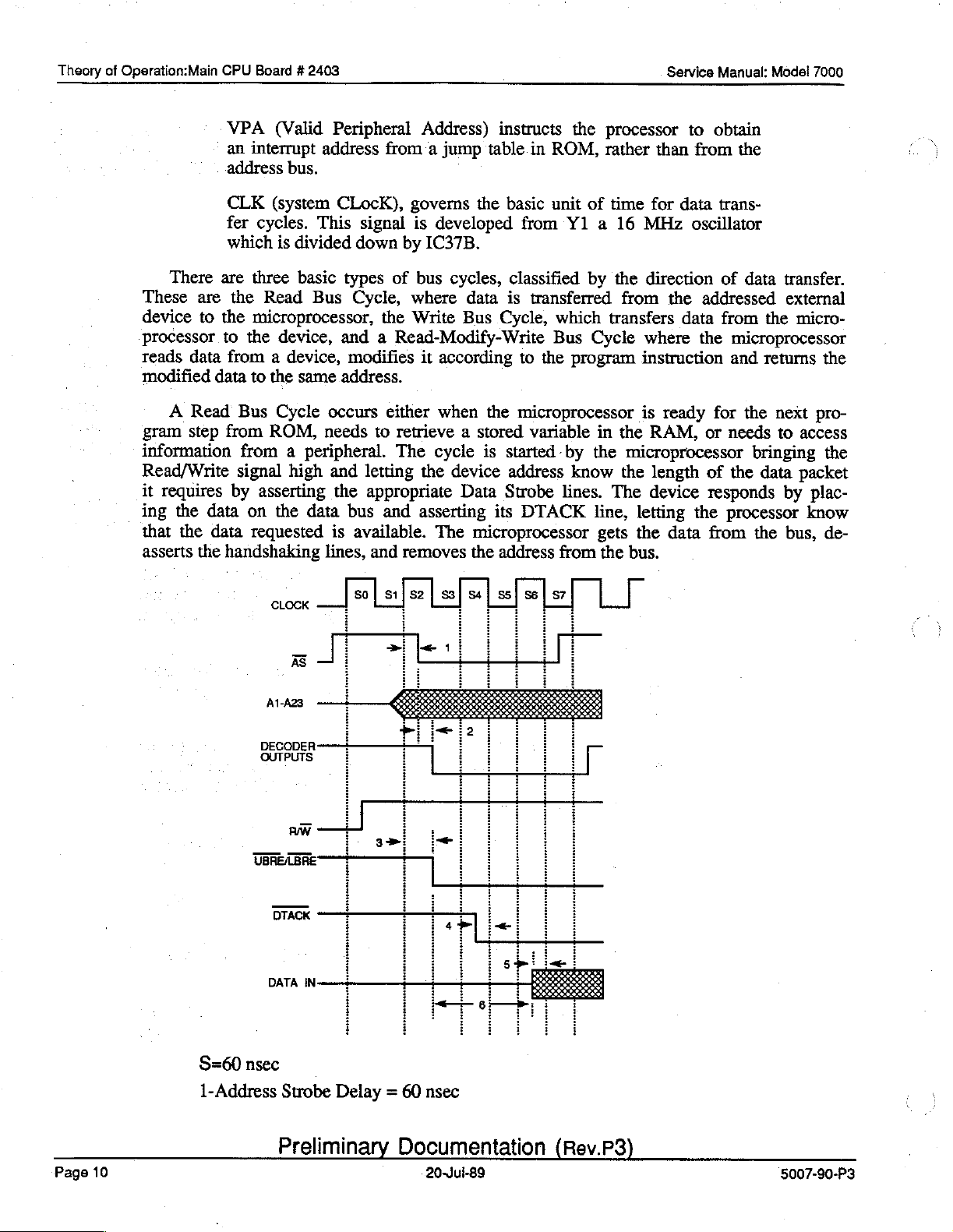

VPA

an

address

CLK

fer

which

There

These

device

processor

reads

modified

A

gram

information

Read/Write

it

requires

ing

that

asserts

are

to

data

Read

step

the

the

the

are

the

the

to

from a device,

data

Bus

from

from a peripheral.

signal

by

data

data

handshaking

(Valid

interrupt

(system

cycles.

is

three

Read

microprocessor,

the

device,

to

the

Cycle

ROM,

asserting

on

the

requested

CLOCK

Peripheral

address

bus.

This

divided

basic

Bus

same

occurs

needs

high

and

the

data

is

lines,

CLocK),

signal

down

types

Cycle,

and a Read-Modify-Write

modifies

address.

letting

appropriate

bus

available.

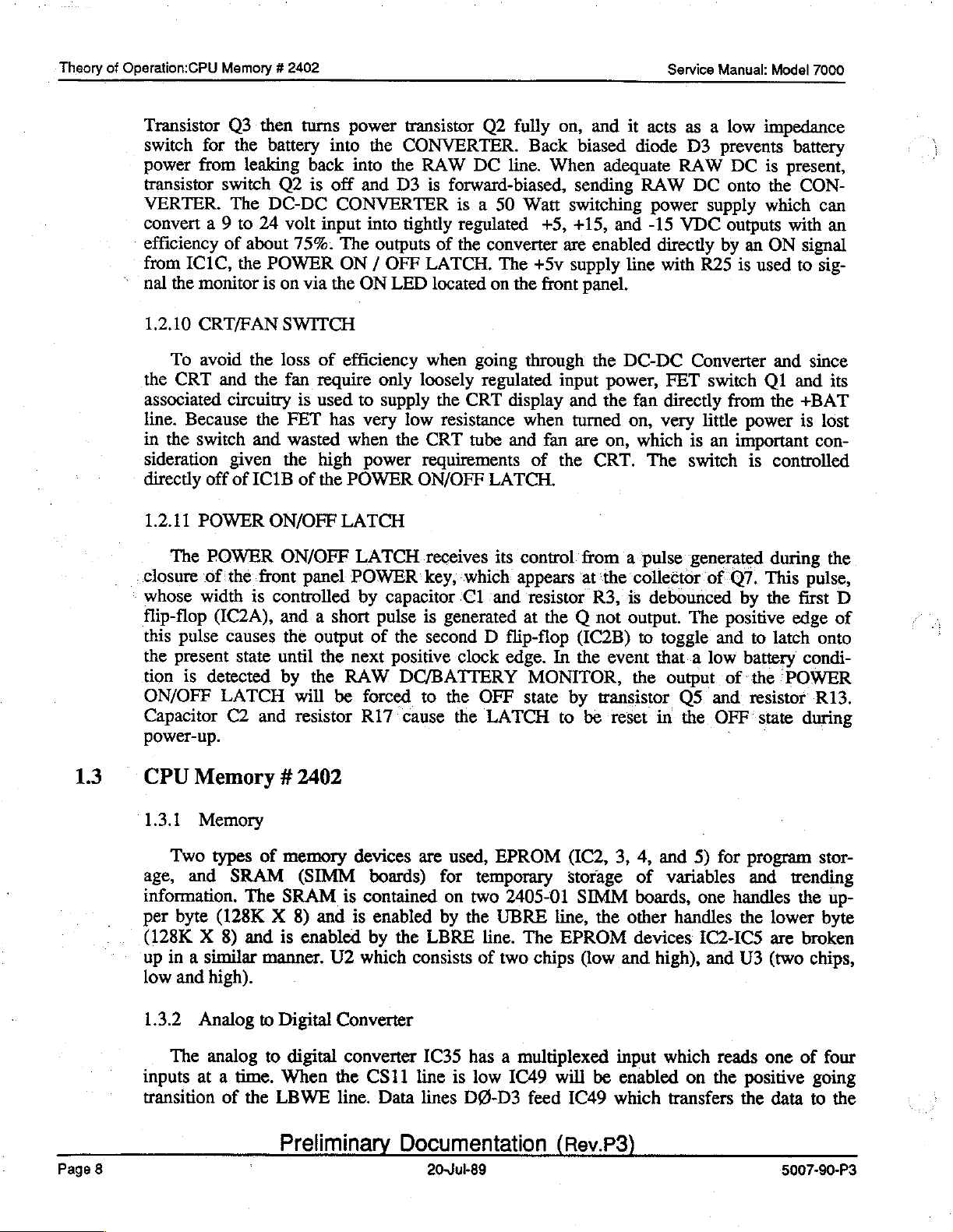

$0 | $1|

Address)

from a jump

governs

is

developed

by

IC37B.

of

bus

cycles,

where

the

Write

either

to

retrieve a stored

The

and

asserting

and

removes

52 | S3|

data

Bus

it

according

when

cycle

the

device

Data

The

microprocessor

the

S4 | 55]

instructs

table

in

ROM,

the

basic

unit

from

classified

is

transferred

Cycle,

to

the

the

microprocessor

variable

is

started-by

address

Strobe

its

DTACK

address

S6 | S7

the

of

Y1 a 16

by

which

Bus

Cycle

program

in

the

know

lines.

line,

gets

from

the

processor

rather

time

the

from

transfers

the

microprocessor

the

The

letting

the

bus.

|

to

than

from

for

data

MHz

where

instruction and

is

oscillator

direction

the

addressed

data

the

ready

RAM,

length

device

the

data

or

of

responds

from

obtain

the

trans-

of

data

transfer.

external

from

the

micro-

microprocessor

returns

for

the

next

needs

the

processor

to

access

bringing

data

packet

by

plac-

know

the

bus,

the

pro-

the

de-

DATA

S=60

nsec

1-Address

IN

Strobe

Delay = 60

nsec

Page

10

Preliminary

Documentation

20-Jul-89

(Rev.P3)

5007-90-P3

Page 15

Sarvice

Manual: Model

7000

Theory

of

Operation:Main

CPU

Board

#

2403

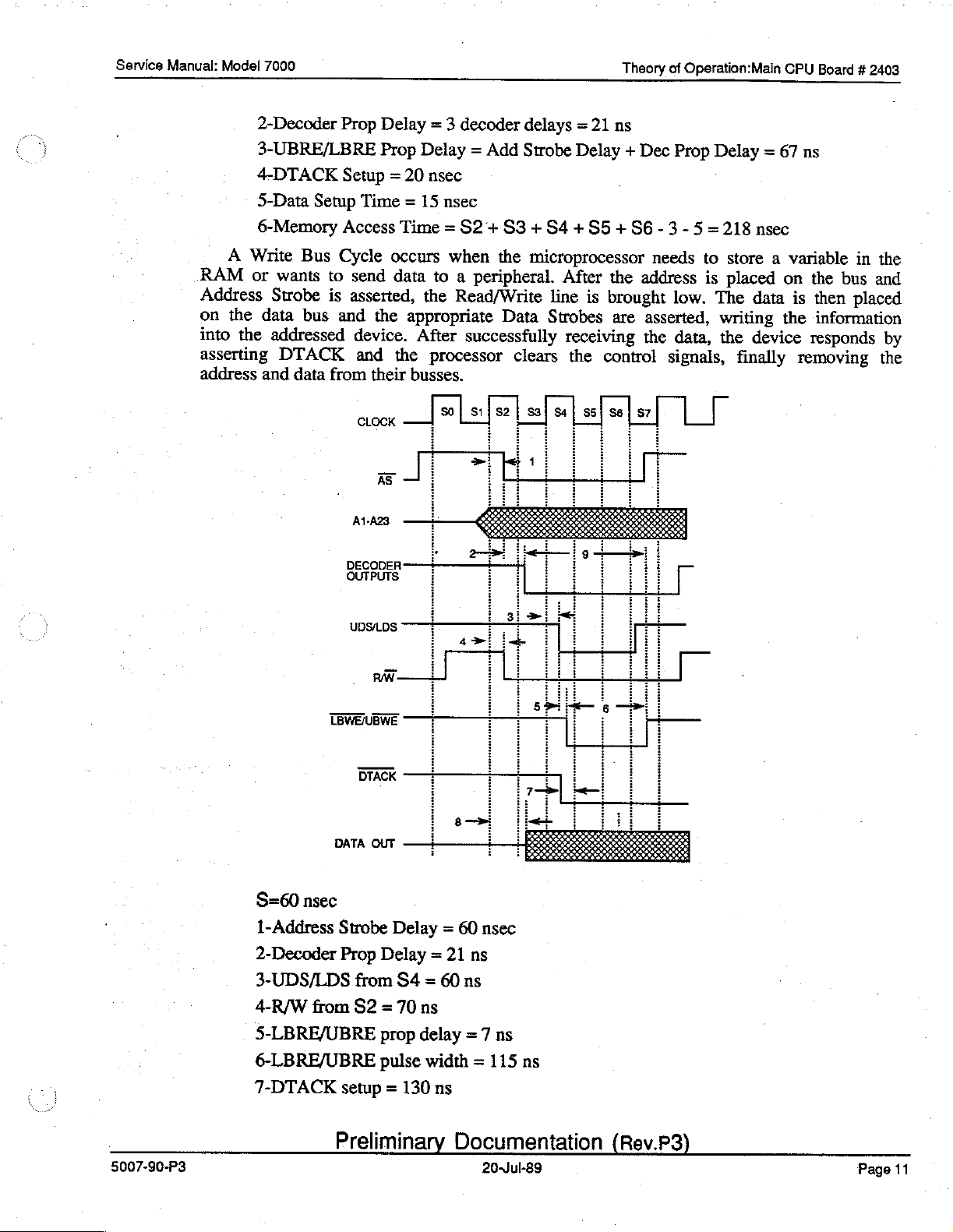

2-Decoder

3-UBRE/LBRE

4-DTACK

5-Data

6-Memory

A

Write

RAM

Address

on

into

asserting

address

or

the

the

Strobe

data

addressed

and

Setup

Bus

wants

bus

DTACK

data

Prop

Delay = 3

Prop

Setup = 20

Time = 15

Access

Cycle

to

send

is

asserted,

and

the

device.

and

from

their

CLOCK

AS

A1-A23

DECODER

OUTPUTS

decoder

Delay = Add

nsec

nsec

Time

=

S2+

occurs

data

the

when

to

a

the

Read/Write

appropriate

After

processor

busses.

So | $11

|

—

delays = 21

Strobe

53

+

54

the

microprocessor

peripheral.

Data

successfully

clears

52 | $3]

1

ke

È

a

line

Strobes

1

After

$4 | $5]

ns

Delay + Dec

+

55

+

56

the

is

brought

are

receiving

the

control

$6157

9

>

Prop

-

3

-

5

=

needs

address

asserted,

the

to

is

low.

data,

signals,

—

Delay = 67

218

ㅁ

560

store

a

variable

placed

The

writing

the

Г

on

data

the

device

finally

ns

in

the

bus

is

then

placed

information

responds

removing

the

and

by

the

UDS/LDS

LBWE/UBWE

DATA

S=60

nsec

1-Address

2-Decoder

3-UDS/LDS

4-R/W

5-LBRE/UBRE

6-LBRE/UBRE

Strobe

Prop

from

S2 = 70

ΒΑΝ.

DTACK

OUT

Delay = 60

Delay = 21

from

S4 = 60

prop

pulse

3İ

mİ

Fe

4>

8—>

ns

delay = 7

width = 115

ns

ns

~

5

7—>|

ei

nsec

ns

ns

6

—

5007-90-P3

7-DTACK

setup = 130

Preliminary

ns

Documentation

20-Jul-89

(Rev.P3)

Page

11

Page 16

Theory

of

Operation:Main

CPU

Board

#

2403

Service

Manual:

Model

7000

8-Data

9-CE

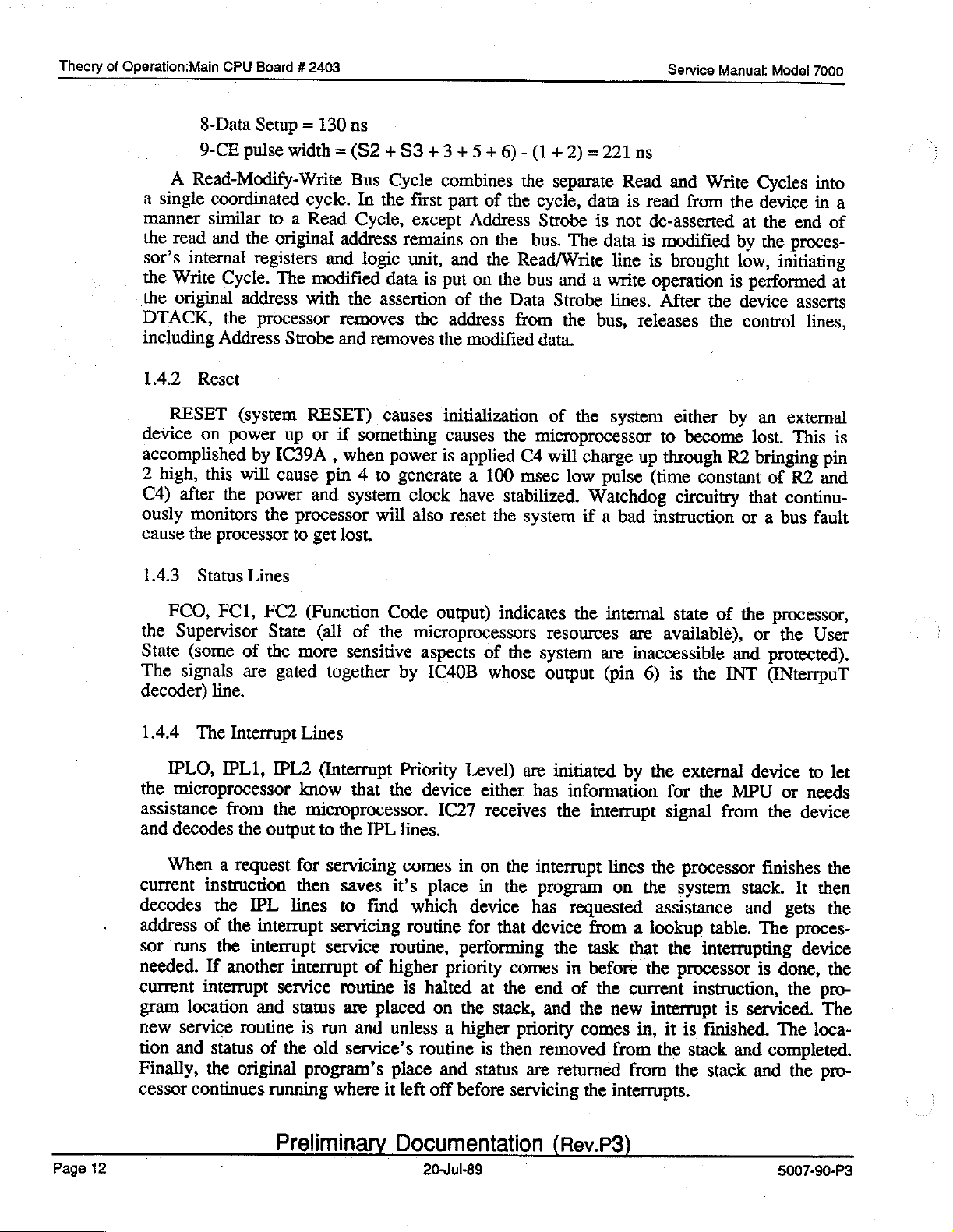

A

Read-Modify-Write

a

single

manner

the

sor’s

the

the

DTACK,

including

1.4.2

device

accomplished

2

high,

C4)

ously

cause

143

coordinated

similar

read

and

internal

Write

original

RESET

Cycle.

the

Address

Reset

on

power

this

after

the

monitors

the

processor

Status

(system

will

Setup = 130

pulse

width = (S2 + S3.+3+5+6)-(1+2)=221

to

a

the

original

registers

The

address

processor

Strobe

up

by

IC39A

cause

power

the

processor

to

Lines

ns

Bus

cycle.

Read

In

Cycle,

address

and

logic

modified

with

the

removes

and

RESET)

or

if

something

,

when

pin

4

and

system

get

lost.

Cycle

the

first

except

remains

unit,

data

is

assertion

the

removes

causes

power

to

generate

clock

will

also

combines

part

Address

on

and

put

on

of

address

the

modified

initialization

causes

is

applied

a

have

reset

the

of

the

cycle,

Strobe

the

bus.

the

Read/Write

the

bus

the

Data

from

data.

the

microprocessor

C4

100

msec

stabilized.

the

system

separate

data

is

The

data

and

a

write

Strobe

the

bus,

of

the

will

charge

low

pulse

Watchdog

if

a

ns

Read

is

read

not

de-asserted

is

modified

line

is

operation

lines.

system

After

releases

to

up

through

(time

bad

instruction

and

Write

from

the

by

brought

either

become

low,

is

the

the

by

R2

constant

circuitry

Cycles

device

at

the

end

the

proces-

initiating

performed

device

control

that

or

asserts

an

external

lost.

This

bringing

of

R2

continu-

a

bus

into

in

a

of

at

lines,

is

pin

and

fault

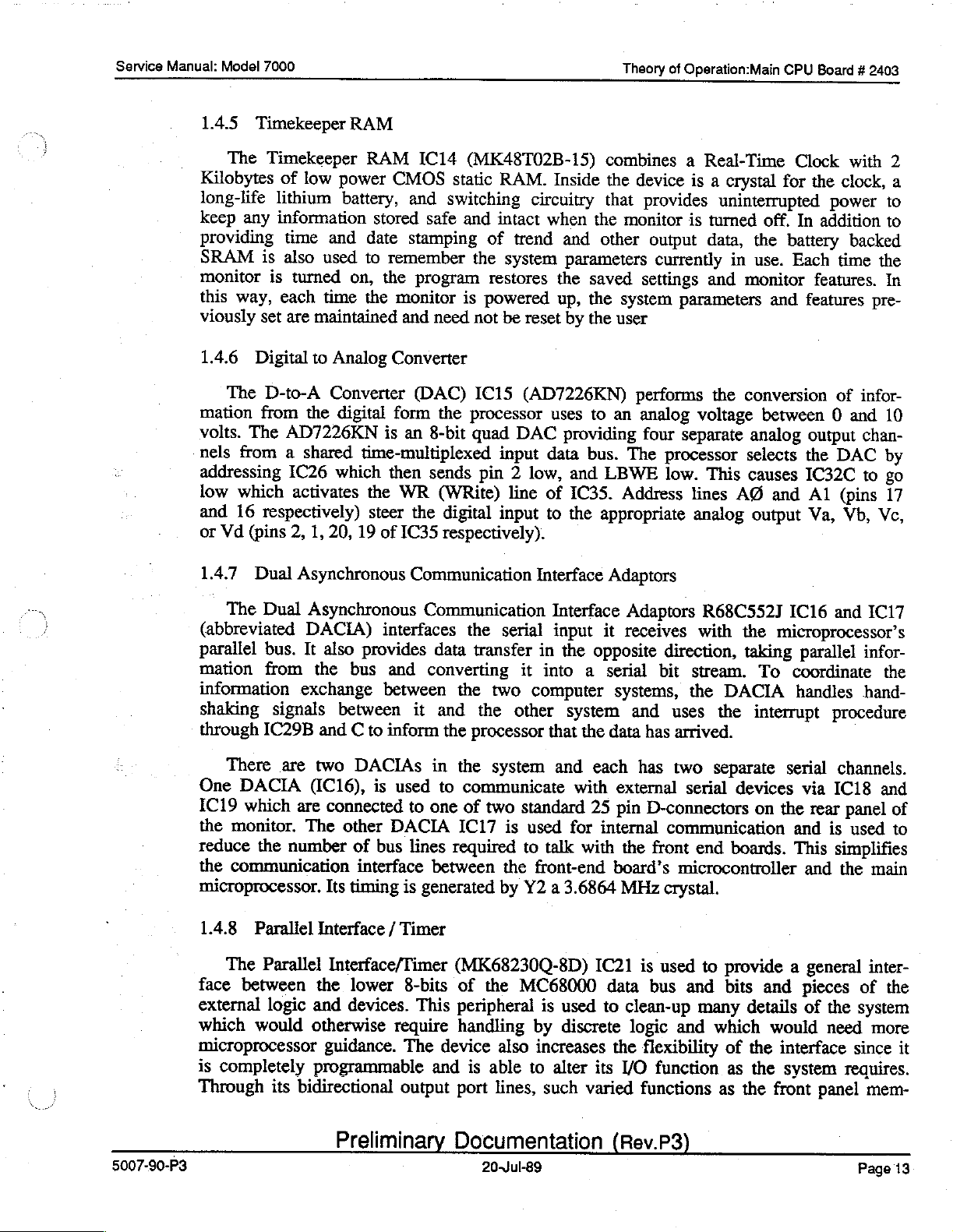

FCO,

the

State

The

decoder)

1.4.4

IPLO,

the

assistance

and

When

current

decodes

address

sor

needed.

current

gram

new

tion

Finally,

cessor

FC1,

Supervisor

(some

signals

line.

The

IPL1,

microprocessor

from

decodes

a

instruction

the

of

runs

the

If

interrupt

location

service

and

status

the

continues

FC2

State

of

the

are

gated

Interrupt

IPL2

the

the

output

request

for

then

IPL

lines

the

interrupt

interrupt

another

interrupt

service

and

status

routine

of

the

original

running

(Function

(all

more

together

Lines

(interrupt

know

Code

of

the

microprocessors

sensitive

by

Priority

that

the

aspects

device

microprocessor.

to

the

IPL

lines.

servicing

saves

to

servicing

service

routine

are

is

run

and

old

service’s

program’s

where

comes

it’s

find

which

routine

routine,

of

higher

is

placed

unless

place

it

left

halted

routine

output)

of

IC40B

IC27

place

whose

Level)

either

receives

in

on

in

device

for

performing

priority

at

on

the

a

higher

is

and

status

off

before

indicates

resources

the

system

output

are

initiated

has

the

the

interrupt

the

program

has

that

device

the

comes

the

end

stack,

and

priority

then

removed

are

returned

servicing

the

internal

are

are

inaccessible

(pin

6)

by

the

information

interrupt

lines

the

on

the

requested

from

a

lookup

task

that

in

before

of

the

the

comes

the

current

new

interrupt

in,

from

from

the

interrupts.

state

of the

available),

and

is

the

INT

external

for

the

MPU

signal

from

processor

system

assistance

stack.

and

table.

the

interrupting

processor

instruction,

is

it

is

finished.

the

stack

and

the

stack

processor,

or

the

User

protected).

(INterrpuT

device

finishes

The

or

the

device

It

gets

proces-

to

needs

the

then

the

device

is

done,

serviced.

The

the

the

pro-

The

loca-

completed.

and

the

pro-

let

Page

12

Preliminary

Documentation

20-Jul-89

(Rev.P3)

5007-90-P3

Page 17

Service

Manual:

Model

7000

Theory

of

Operation:Main

CPU

Board # 2403

1.4.5

Kilobytes

long-life

keep

providing

SRAM

monitor

this

viously

1.4.6

mation

volts.

nels

addressing

low

and

or

1.4.7

Timekeeper

The

Timekeeper

of

lithium

any

information

is

is

way,

each

set

Digital

The

D-to-A

from

The

from

which

16

respectively)

Vd

(pins

Dual

RAM

RAM

low

power

battery,

stored

time

and

date

also

used

to

turned

are

AD7226KN

a

IC26

activates

2,

on,

time

the

maintained

to

Analog

Converter

the

digital

shared

1,

time-multiplexed

which

the

steer

20,

19

Asynchronous

IC14

CMOS

and

stamping

remember

the

program

monitor

and

Converter

(DAC)

form

is

an

then

WR

the

of

IC35

(MK48T02B-15)

static

switching

safe

and

is

need

the

8-bit

sends

(WRite)

digital

respectively).

Communication

RAM.

circuitry

intact

of

trend

the

system

restores

powered

not

be

reset

IC15

processor

quad

input

pin

input

(AD7226KN)

DAC

2

low,

line

Interface

combines

Inside

when

the

up,

uses

data

of

to

the

that

the

and

other

parameters

saved

the

by

the

to

providing

bus.

and

LBWE

1C35.

the

appropriate

Adaptors

device

provides

monitor

output

currently

settings

system

user

performs

an

analog

four

The

Address

a

Real-Time

is

a

crystal

uninterrupted

is

turned

data,

in

and

parameters

the

voltage

separate

processor

low.

This

lines

A@

analog

Clock

for

the

off.

In

the

battery

use.

Each

monitor

conversion

between

analog

selects

causes

output

and

and

features.

features

output

the

IC32C

Al

Va,

with

clock,

power

addition

backed

time

the

pre-

of

infor-

0

and

chan-

DAC

to

(pins

Vb,

Vc,

2

a

to

to

In

10

by

go

17

The

Dual

Asynchronous

(abbreviated

parallel

mation

information

shaking

through

There

One

DACIA

IC19

which

the

monitor.

reduce

the

the

communication

microprocessor.

1.4.8

face

Parallel

The

between

external

which

would

microprocessor

is

completely

Through

DACIA)

bus.

It

also

from

the

exchange

signals

IC29B

are

are

The

and C to

two

(IC16),

connected

number

Its

Interface / Timer

Parallel

Interface/Timer

the

logic

and

otherwise

guidance.

programmable

its

bidirectional

interfaces

provides

bus

and

between

between

inform

DACIAs

is

used

other

DACIA

of

bus

interface

timing

lower

devices.

require

Communication

the

data

transfer

converting

the

it

and

the

the

processor

in

the

to

communicate

to

one

of

two

IC17

lines

required

between

is

generated

(MK68230Q-8D)

8-bits

of

This

peripheral

the

handling

The

device

and

is

output

port

serial

it

two

computer

other

system

standard

is

used

to

the

front-end

by

Y2

MC68000

by

also

increases

able

to

lines,

Interface

input

in

the

opposite

into

a

system

that

the

and

each

with

25

for

internal

talk

with

a

3.6864

IC21

is

used

discrete

alter

its

such

varied

Adaptors

it

receives

direction,

serial

bit

systems,

and

data

has

has

external

pin

D-connectors

communication

the

front

board’s

MHz

crystal.

is

used

data

bus

to

clean-up

logic

the

flexibility

I/O

function

functions

R68C552J

with

the

microprocessor’s

taking

stream.

the

uses

To

DACIA

the

interrupt

arrived.

two

separate

serial

microcontroller

and

end

to

devices

boards.

provide

bits

many

and

which

of

as

as

serial

on

the

and

details

would

the

interface

the

system

the

front

IC16

and

parallel

coordinate

handles

infor-

hand-

procedure

channels.

via

IC18

rear

panel

and

is

used

This

simplifies

and

the

a

general

pieces

of

the

of

system

need

since

requires.

panel

mem-

IC17

the

and

of

to

main

inter-

the

more

it

5007-90-P3

Preliminary

Documentation

20-Jul-89

(Rev.P3)

Page

13

Page 18

Theory

of

Operation:Main

CPU

Board

#

2403

Service

Manual:

Model

7000

brane

generated

which

events

1.4.9

tem

configurations

ding

and

switches

1.4.10

ties

the

pin

sound.

4.15

goes.low

speaker.

GEN

line

keys,

that

The

parameters.

on

the

The

in

addition

LBWE

7

drives

volt

the

if

activity

the

microprocessor

are

Cal

switches

four

DIP

the

system

LBRE

are

then

Sound

SN76476N

line

IC50A

threshold

(after

The

CS

line

for

the

processor.

controlled

Generator

IC50B

READY

by

battery

is

switches

These

and

alter

hardware

lines

are

present

programmable

to

the

video

is

low,

pin

prevents

on

time

constant

line

IC40C,

state,

detected

uses

by

software:

(S1)

switches

the

program

which

low,

this

on

D@-D7

output

IC46

is

5,

which

audio

pin

3

it

output

of

of

of

IC46

is

then

and

the

on

the

as

a

on

the

allow

causes

to

sound

of

enabled

in

IC50A

R49

pin

inverted

I/O

lines.

time

base

CPU

the

if

needed

is

present.

IC33D

be

read

generator

the

CRT

and

turn

drives

until

the

(junction

and

C65)

4

drives

by

mux

lines

Also

generated

for

board

by

receives

are

processor

so

the

IC48

pin

the

processor.

IC46

display.

O1,

junction

of

R51

O2

is

IC43D

IC43A

are

monitored

is

the

marking

used

to

appropriate

is

enabled

11

to

gives

When

input

if

of

and

turned

which

which

the

to

define

recognize

go

low.

the

pin

from

O1

is

R49

and

R52).

on

and

is

develops

and

timer

occurrence

and

different

actions

when

The

system

8

of

IC26

data

lines

enabled

C65

When

audio

gated

the

interrupts

output

of

set

certain

are

taken

IC26

pin

condition

audio

goes

DG-D7.

the

speaker

charges

pin

1

may

pass

with

the

TONE

are

(TOUT),

certain

sys-

hardware

depen-

6

(CS6)

of

S1's

capabili-

low,

and

IC46

may

past

the

of

IC50A

to

the

SOUND

DTACK

1.4.11

and

to

When

goes

this

1.4.12

The

then

the

low

data

LED

LED

LEDs

the

is

Wait

Running

in

a

normal

problem,

sor

know

when

ensures

this

this

to

it

that

system

a

circuit

satisfy

latch

latch

IC44

maintains

processor

which

then

State

at

bus

peripherals

when

is

ready

only

are

called

the

requirements

that

is

limited

enables

latched

Generator

8

MHz,

cycle

some

for

valid

of

the

a

addresses

in

extra

programmable

lets

the

microprocessor

state

without

by

R32-R41

IC26

IC44.

by

the

to

collect,

the

the

The

IC44

until

MC68000

convert

MC68000

time

is

processor

information

MC68000

of

family

the

individual

further

and

switched

pin

9

(LATCHES)

processor

written

does

to

not

and

family

required

is

to

proceed.

given

and

and

Wait

State

control

input

from

by

then

writes

again.

allow

present

have

a

DTACK

that

it

This

to

the

processor.

do

not

provide

Generator

devices.

If

the

state

the

microprocessor.

5

transistor

and

LBWE

to

IC44

some

of

its

the

requested

control

should

wait

synchronizes

Not

a

DTACK

takes

a

device

of

the

front

array

go

on

Q3

low,

data

peripherals

data.

To

line

to

for

the

device

data

all

of

the

signal.

control

has

its

and

own

panel

The

LEDs

current

(CA3046).

IC24C

lines

enough

alleviate

let

transfer

DO-D7,

the

proces-

to

pin

time

this

signal

and

peripherals

To

correct

can

be

varied

DTACK

line,

8

in

Page

14

Preliminary

Documentation

20-Jul-89

(Rev.P3)

5007-90-P3

Page 19

Service

Manual:

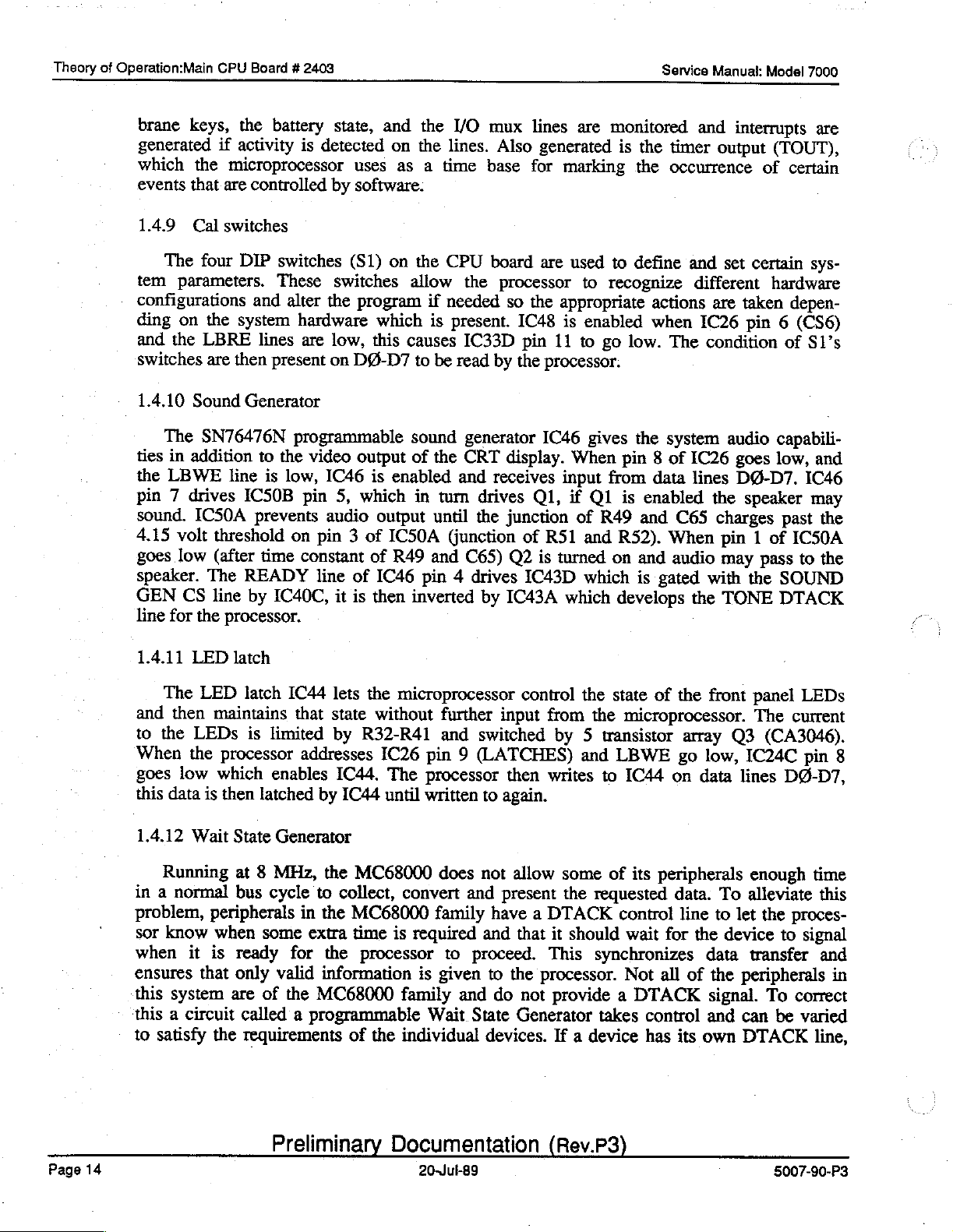

then

the

Model

that

data

7000

supersedes

as

soon

as

the

it

is

available.

S0j

81]

Wait

S2|

83]

State

S4

|SW|

generated

Sw]

sw|sw]

Theory

signal

$51

56 | $7

so

of

Operation:Video

that

the

Controller

processor

can

#

2404

process

1.5

Video

A1-A23 一 一

LOAD

RPC

Mt

OCP

DECODER

OUTPUTS

=

DTACK

Controller # 2404

HE

OC

e

CDH

ОЕ

ОЕ

5007-90-P3

1.5.1

play

HD63484

distance

history

en.

1.5.2

(Host)

MEMORY)

Buffer

the

CHANNEL,

horizontal

the

Introduction

The

video

for

a

medical

Advanced

viewing

of

stored

Block

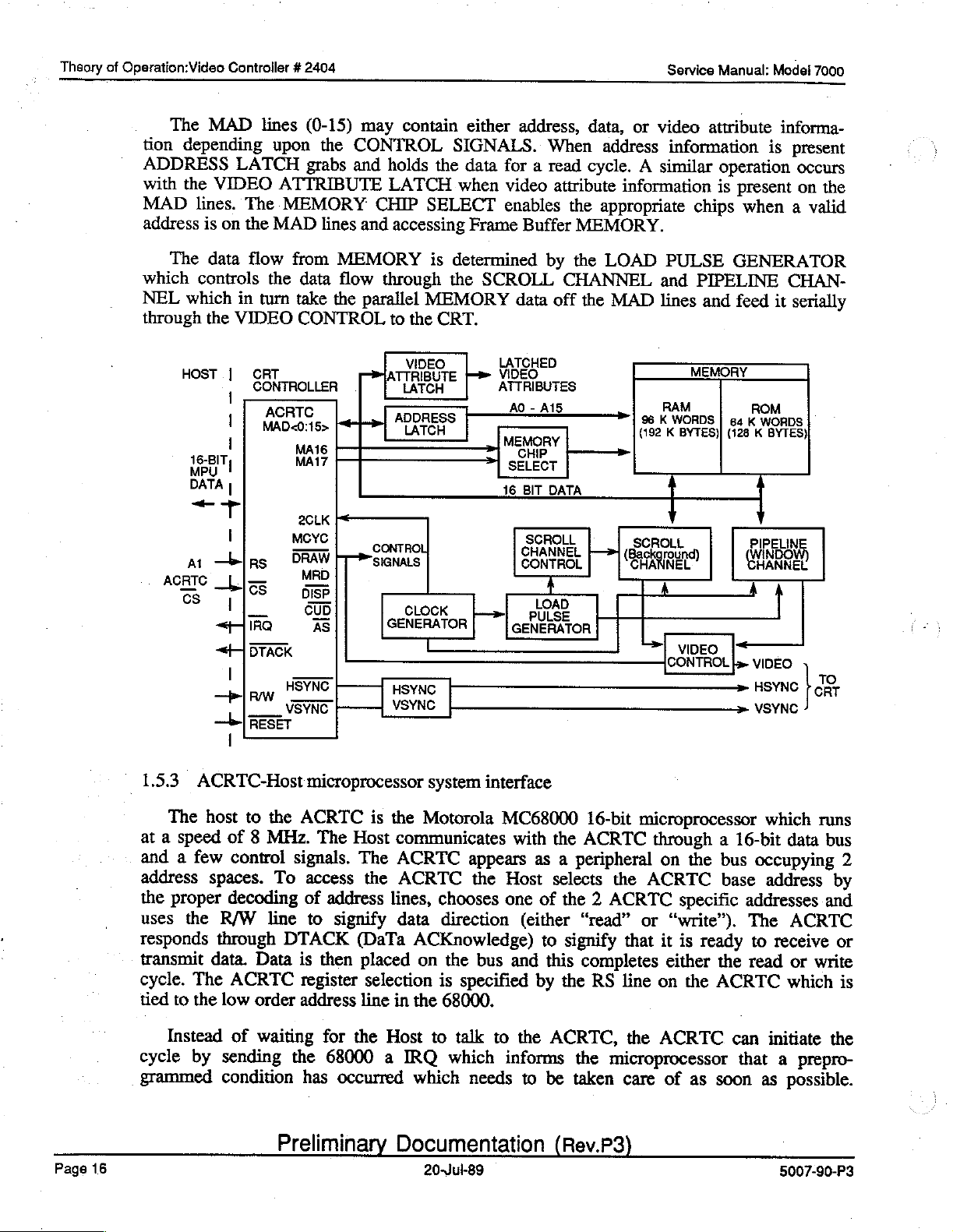

The

ACRTC

and

data.

5

MHz

sync

CRT.

display

monitoring

of

waveforms.

diagram

handles

the

CRT.

manages

The

system

2CLK

and

PIPELINE

pulses,

Preliminary

system

CRT

important