Page 1

Freescale Semiconductor, Inc.

nc...

I

MOTOROLA

Metrowerks

SW/HW Dept

cale Semiconductor,

Frees

MSC8101 ADS

User’s Manual

Revision B

(Revision Release 1.2)

Dragilev Lev

SW/HW Dept

Motorola Semiconductor Israel

1 Shenkar Street,

Herzlia 46120, Israel

TEL

: 972-9-522-579

email: Lev.Dragilev@motorola.com

FAX: 972-9-9562990

For More Information On This Product,

Go to: www.freescale.com

25/1/2004

Page 2

Freescale Semiconductor, Inc.

nc...

I

cale Semiconductor,

Frees

MSC8101ADS RevB User’s Manual

For More Information On This Product,

Go to: www.freescale.com

Page 3

nc...

I

cale Semiconductor,

Frees

Freescale Semiconductor, Inc.

CONTENTS

1•1 Introduction 11

1•2 Abbreviations’ List 11

1•3 Related Documentation 11

1•4 Specification 12

1•5 ADS Features 13

2•1 INTRODUCTION 16

2•2 UNPACKING INSTRUCTIONS 16

2•3 HARDWARE PREPARATION 16

2•3•1 Setting The Core Supply Voltage Level 18

2•3•2 Setting MODCK(1:3) For Initial PLLs’ Multiplication Factor - SW9 18

2•3•3 Setting HReset Configuration Source 18

3•1 OnCE Connection Scheme 19

3•2 Host I/F Operation 19

3•3 Stand Alone Operation 20

3•4 +5V Power Supply Connection 21

3•5 JTAG/OnCE Connector - P6 21

3•6 HOST I/F Connector - P4 22

3•7 Terminal to MSC8101ADS RS-232 Connection 23

3•8 10/100-Base-T Ethernet Port Connection 24

3•9 Flash Memory SIMM Installation 24

4•1 INTRODUCTION 26

4•2 SWITCHES 26

4•2•1 Host I/F Setting - SW1 26

4•2•2 Emulator Enable (EE) - SW2 26

4•2•3 ABORT Switch - SW3 27

4•2•4 SOFT RESET (SRESET) Switch - SW4 27

4•2•5 DATA Bus Width Setting - SW5 & SW6. 27

4•2•6 HARD RESET (HRESET) - Switch - SW7 28

4•2•7 Power-On RESET Switch (PRESET) - SW8 28

4•2•8 Configuration Switch - SW9 28

4•2•9 Boot Mode Select - SW10 29

4•2•10 Software Options Switch - SW11 30

4•3 Jumpers 30

4•3•1 JP1 - DLL Disable. 30

4•3•2 JP2 - Clock Buffer Set. 30

4•3•3 JP3 - 50 Ohm Enable. 31

4•3•4 JP4 - VPP Source Selector 31

4•3•5 JP5,JP8 - 600 Ohm Termination. 31

4•3•6 JP6,JP7 - MIC Enable. 31

4•3•7 JP9 - 5V power supply for CODEC 31

4•3•8 JS1-5 - Current Consumption Measurement 32

4•3•9 JG1-6 GND Bridges 32

4•3•10 Solder Bridges 32

4•4 LEDs 32

4•4•1 Fast Ethernet Indicator - LD1 32

4•4•2 Fast Ethernet RX Indicator - LD2 32

4•4•3 Ethernet TX Indicator - LD3 32

MOTOROLA MSC8101ADS RevB User’s Manual III

For More Information On This Product,

Go to: www.freescale.com

Page 4

nc...

I

cale Semiconductor,

Frees

Freescale Semiconductor, Inc.

4•4•4 Ethernet LINK Indicator - LD4 33

4•4•5 Fast Ethernet CLSN Indicator - LD5 33

4•4•6 ATM RX Indicator - LD6 33

4•4•7 ATM TX Indicator - LD7 33

4•4•8 TEXP Indicator - LD8 33

4•4•9 Signaling Indicator 1 - LD9 33

4•4•10 Signaling Indicator 0 - LD10 33

4•4•11 RS232 Port 2 ON - LD11 33

4•4•12 RS232 Port 1 ON - LD12 33

4•4•13 Fast Ethernet Port Initially Enabled - LD13 33

4•4•14 ATM ON - LD14 34

4•4•15 T1-1 TDM Port 1 Enable - LD15 34

4•4•16 T1-234 TDM Ports 2,3,4 Enable - LD16 34

4•4•17 CODEC Enable - LD17 34

4•4•18 RUN Indicator - LD18 34

4•4•19 Host I/F Enable - LD19 34

4•4•20 1.5V Indicator - LD20 34

4•4•21 3.3V Indicator - LD21 34

4•4•22 5V Indicator - LD22 34

4•5 The MSC8101’s Registers’ Programming 34

4•5•1 System Initialization 35

5•1 Reset & Reset - Configuration 39

5•1•1 Power- On Reset 39

5•1•2 Manual Hard Reset 39

5•1•3 Hard Reset Configuration 39

5•1•4 Manual Soft Reset 41

5•1•5 MSC8101 Internal Hard Reset Sources 42

5•2 Local Interrupter 42

5•2•1 ABORT Interrupt 42

5•2•2 ATM UNI Interrupt 42

5•2•3 QFALC Interrupt 42

5•3 Clock Generator 42

5•4 Bus Buffering 43

5•5 Chip - Select Generator 43

5•6 Synchronous DRAM Bank 44

5•6•1 SDRAM Programming 45

5•6•2 SDRAM Refresh 46

5•7 Flash Memory SIMM 46

5•7•1 Flash Programming Voltage 47

5•8 Communication Ports 48

5•8•1 ATM Port 50

5•8•2 100/10 Base - T Port 50

5•8•3 Audio CODEC 51

5•8•4 T1/E1 Ports 52

5•8•5 RS232 Ports 52

5•9 Host I/F 53

5•10 DMA off-board tool 54

5•11 Board Control & Status Register - BCSR 54

IV MSC8101ADS RevB User’s Manual MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Page 5

Freescale Semiconductor, Inc.

5•11•1 BCSR0 - Board Control / Status Register 0 55

5•11•2 BCSR1 - Board Control / Status Register 1 56

5•11•3 BCSR2 - Board Control / Status Register 2 58

5•11•4 BCSR3 - Board Status Register 3 59

7•1 Power rails. 65

7•1•1 5V Bus 66

7•1•2 3.3V Bus 66

7•1•3 1.5V Bus 66

A•1 BOM 68

B•1 Interconnect Signals 76

B•1•1 MSC8101ADS’s P1- System Expansion Connector 76

B•1•2 MSC8101ADS’s P2 - CPM Expansion Connector 82

B•1•3 P3 - Altera’s In System Programming (ISP) 90

B•1•4 P4 - Host Interface Connector 90

nc...

I

B•1•5 P5, P7, P8, P9, P10, P13, P14 - Logic Analyzer Connectors 92

B•1•6 P6 - JTAG/OnCE Port Connector 92

B•1•7 P12 - Ethernet Port Connector 93

B•1•8 P15,P16 - SMB Connectors 93

B•1•9 P17,P18 - Double RJ45 T1/E1 Line Connectors 93

B•1•10 P19,P21,P24 - Stereo Phone Jack Connectors 94

B•1•11 P20,P22,P23,P25 - RCA Jack Connectors 94

B•1•12 P26 - 5V Power Supply Connectors 95

B•1•13 P27A,B - RS232 Ports’ Connectors 95

C•1 Logic Equations 99

C•1•1 First Include File 99

C•1•2 Second Include file 100

C•1•3 Main File 101

cale Semiconductor,

Frees

MOTOROLA MSC8101ADS RevB User’s Manual V

For More Information On This Product,

Go to: www.freescale.com

Page 6

Freescale Semiconductor, Inc.

nc...

I

cale Semiconductor,

Frees

VI MSC8101ADS RevB User’s Manual MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Page 7

Freescale Semiconductor, Inc.

LIST OF FIGURES

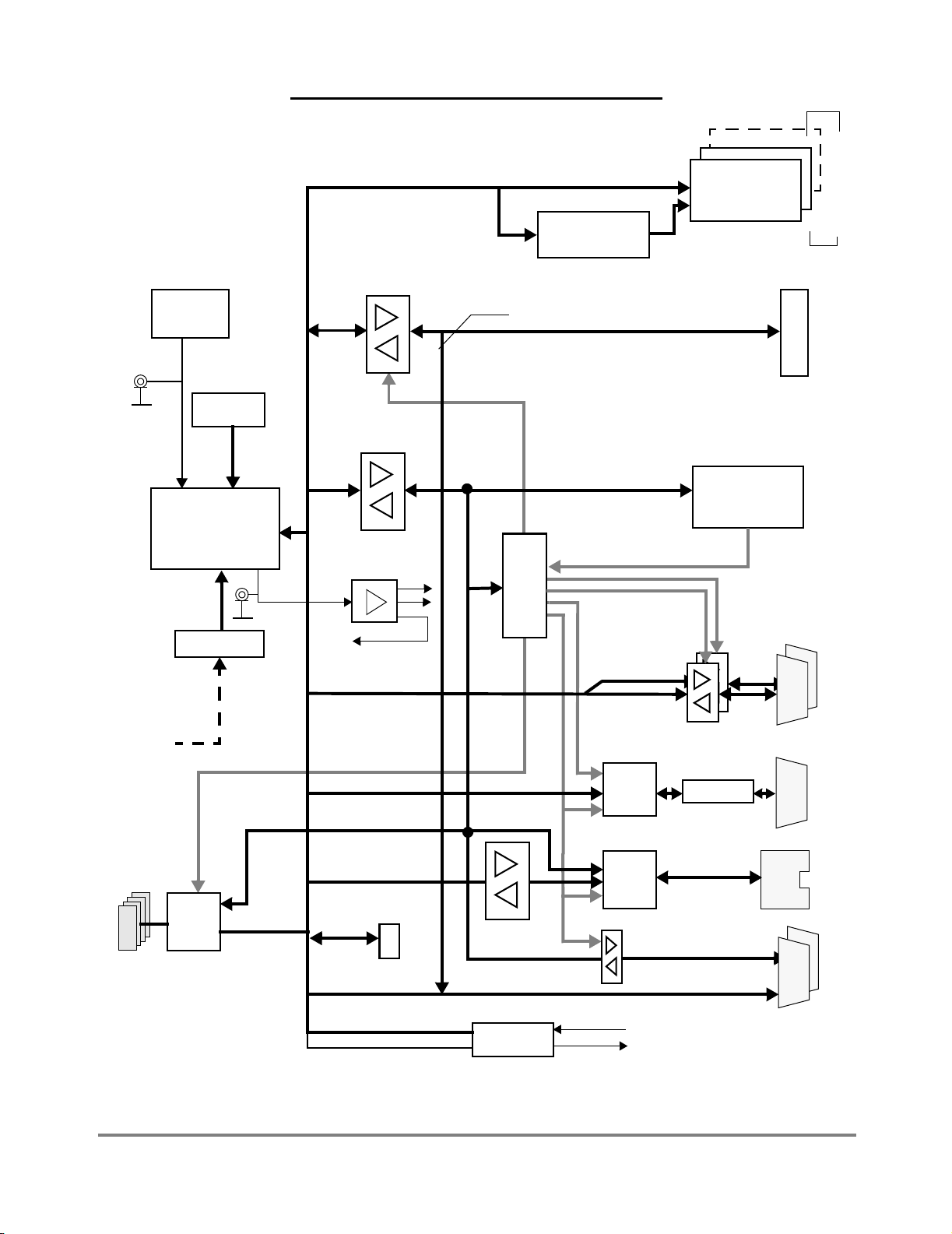

FIGURE 1-1 MSC8101ADS Block Diagram 15

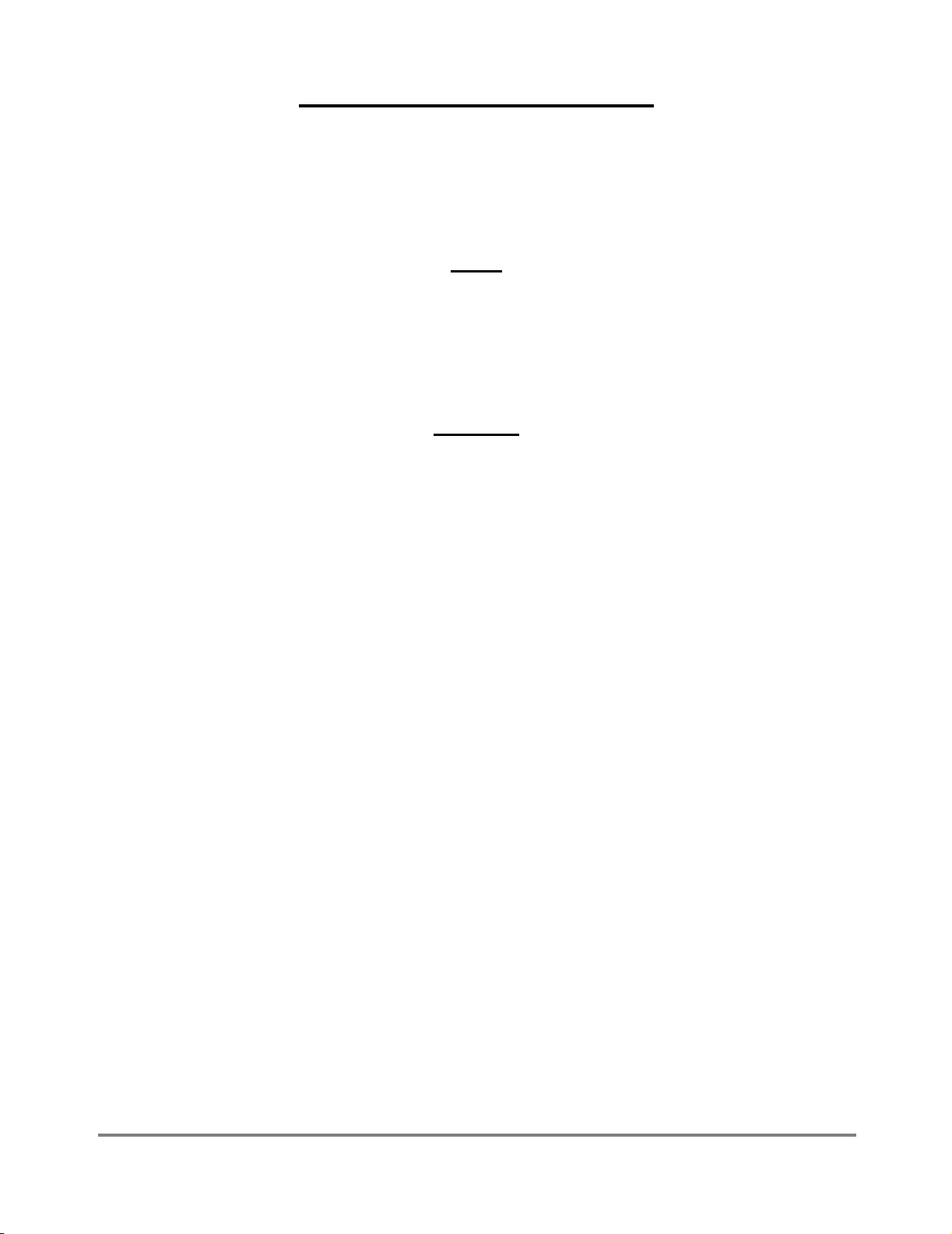

FIGURE 2-1 MSC8101ADS Top Side Part Location diagram 17

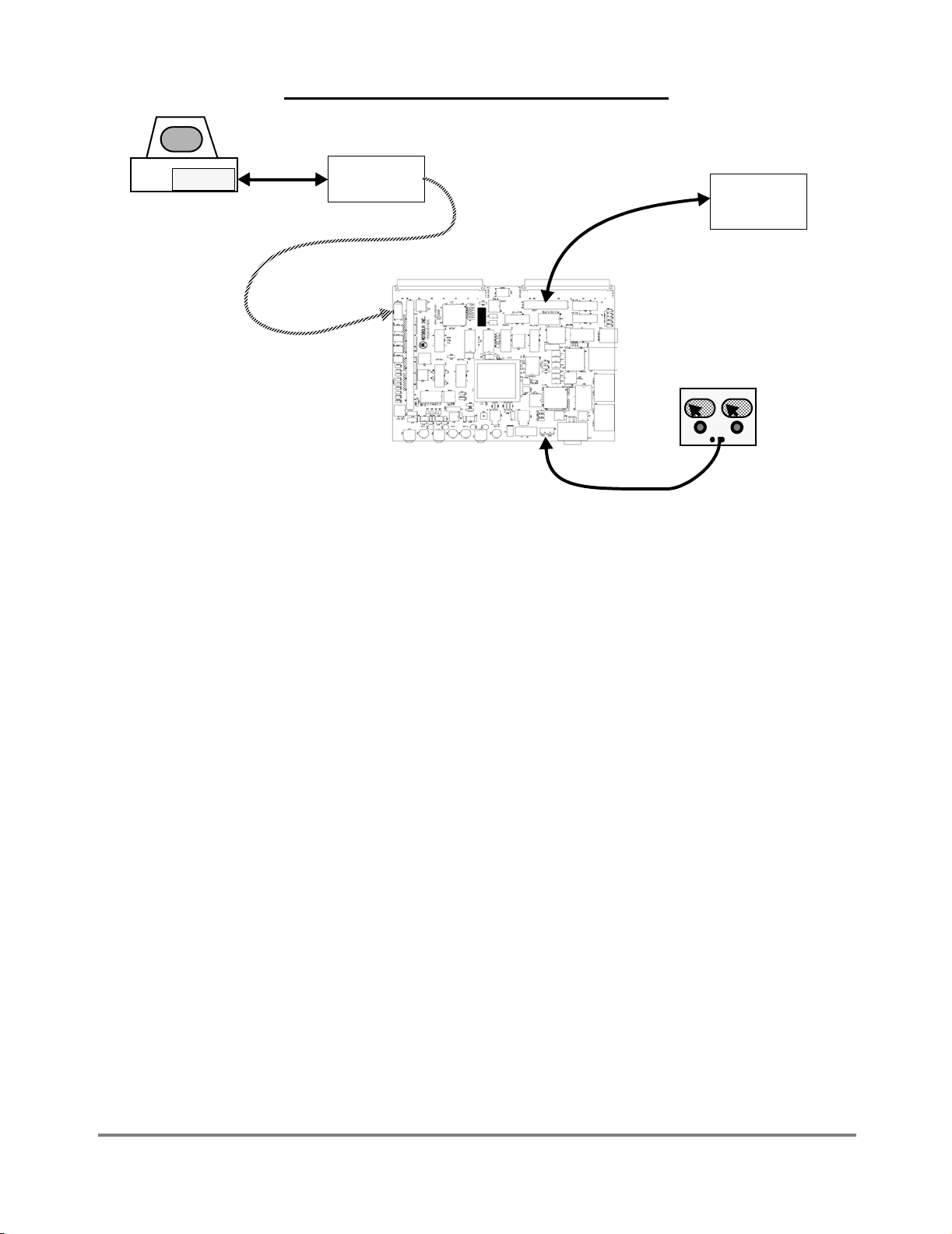

FIGURE 3-1 Host System Debug Scheme A 19

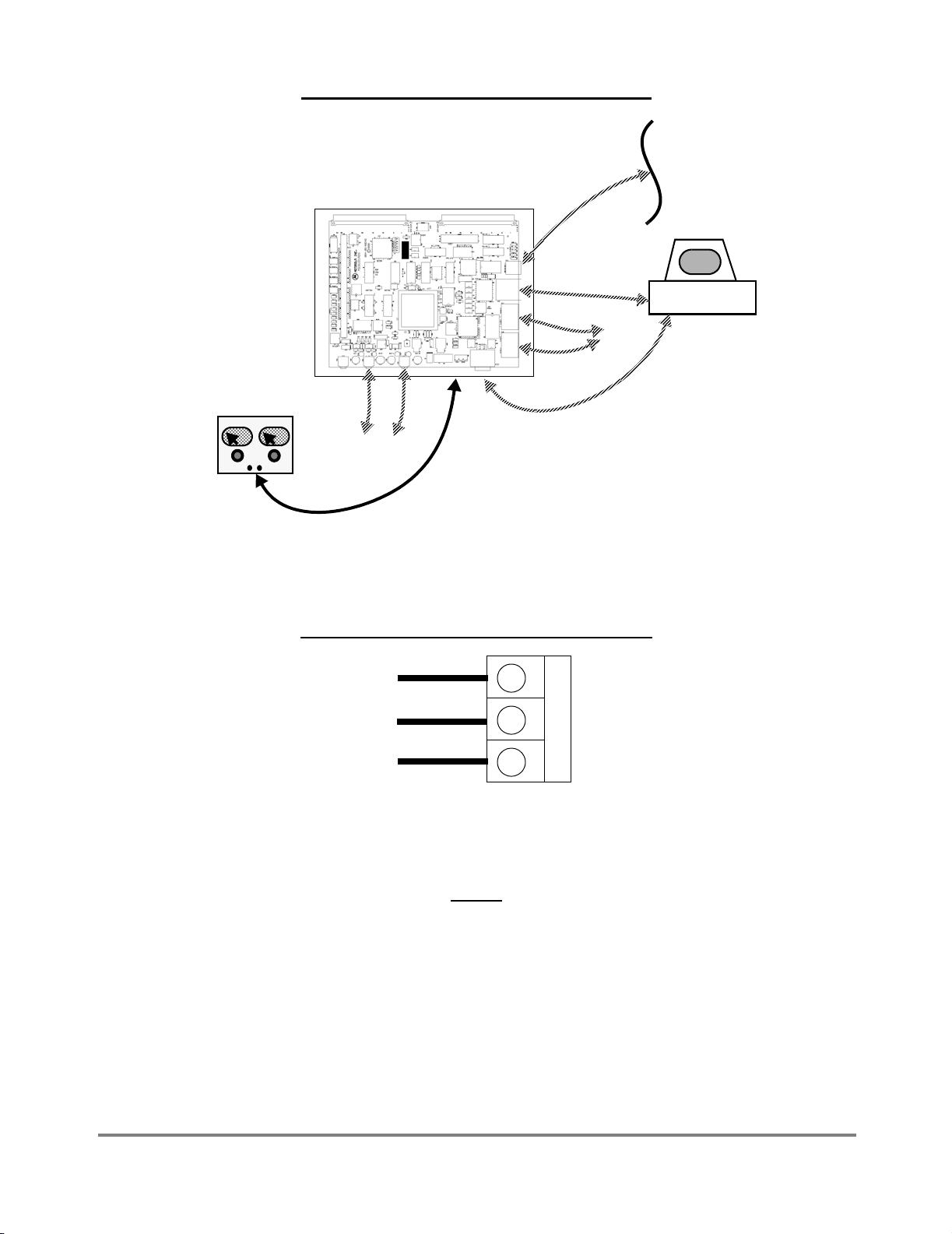

FIGURE 3-2 Host System Debug Scheme B 20

FIGURE 3-3 Stand Alone Configuration 21

FIGURE 3-4 P26: +5V Power Connector 21

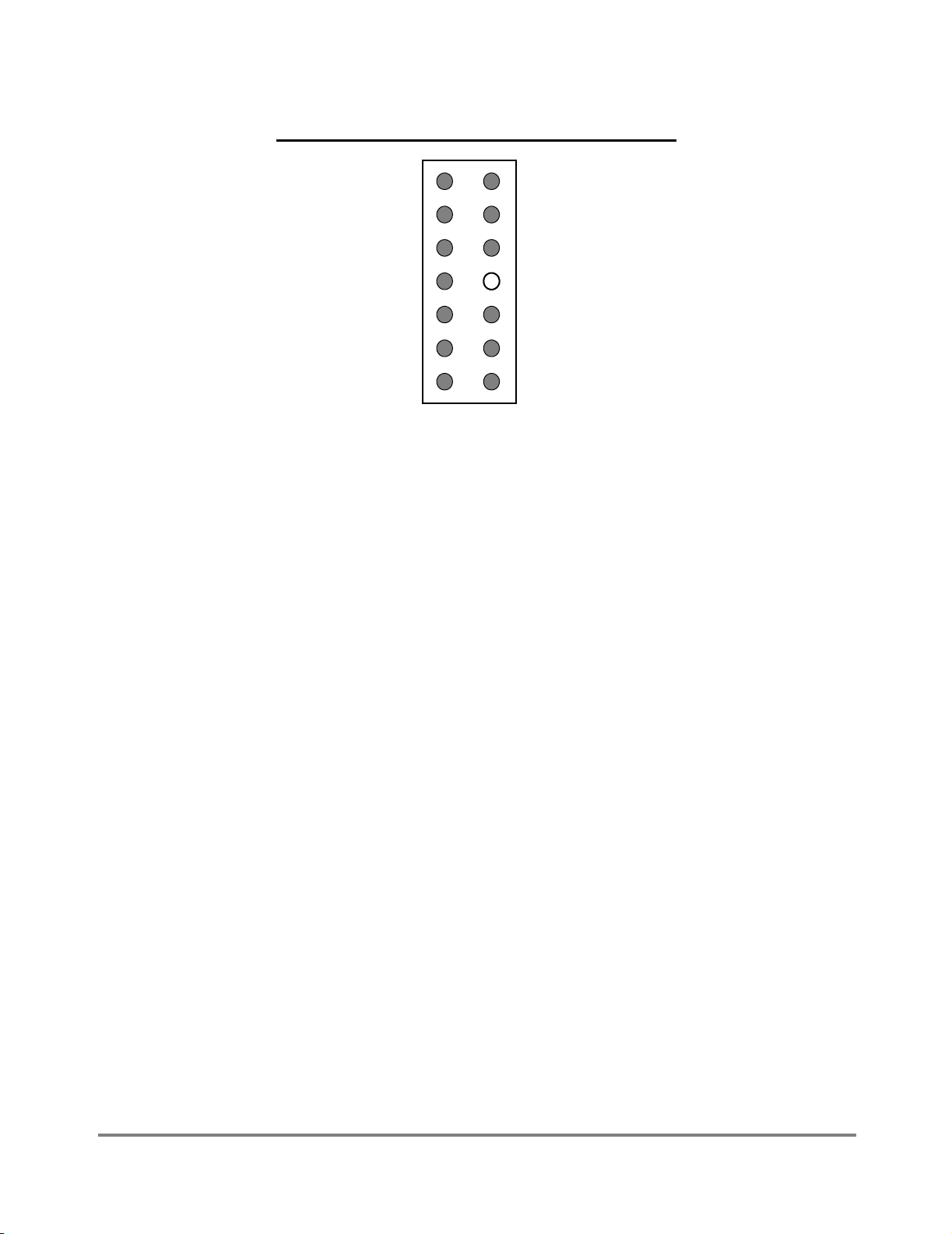

FIGURE 3-5 P6 - JTAG/OnCE Port Connector 22

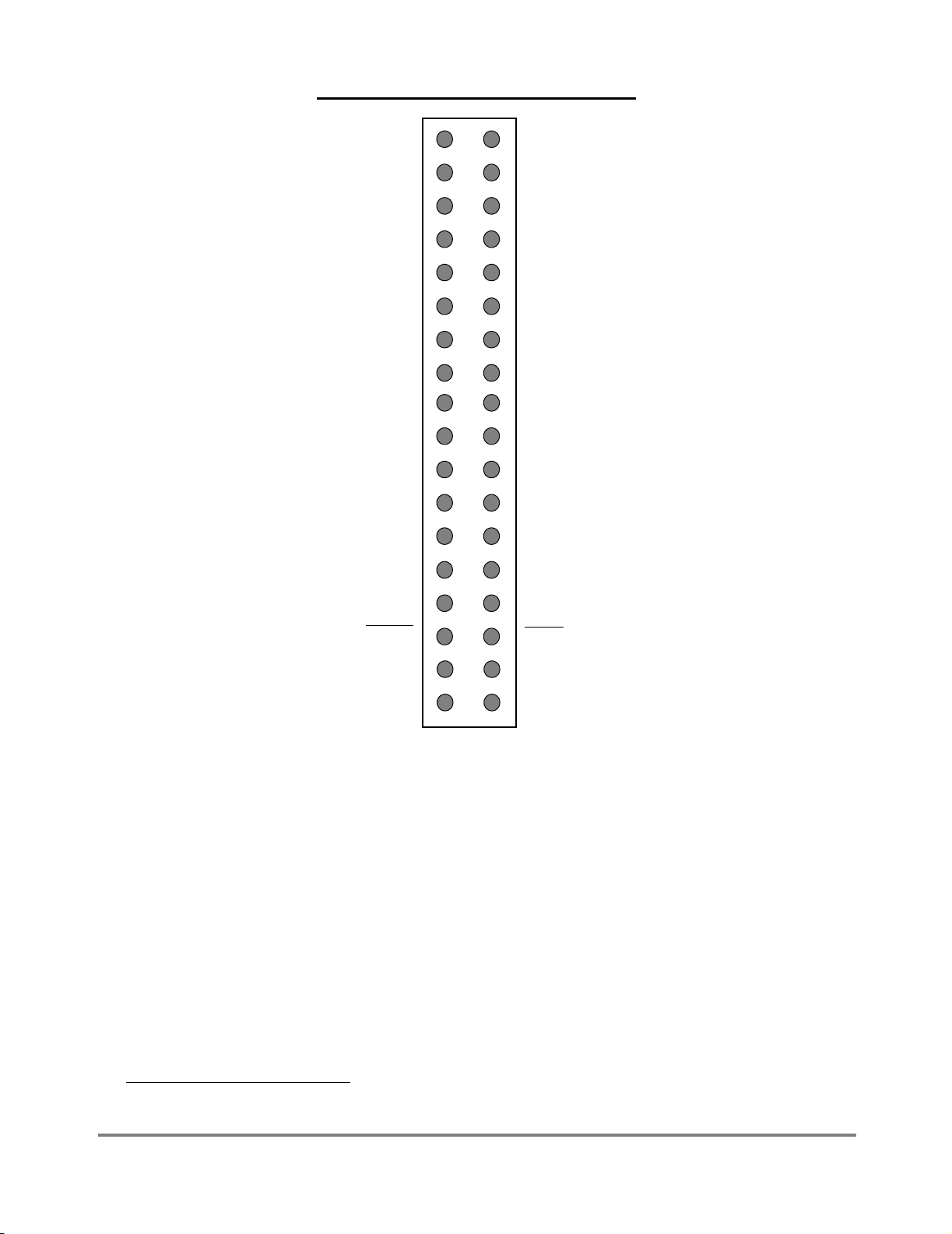

FIGURE 3-6 P4 - Host I/F Connector 23

FIGURE 3-7 P27A - Upper RS-232 Serial Port Connector 24

FIGURE 3-8 P27B - Lower RS-232 Serial Port Connector 24

FIGURE 3-9 Flash Memory SIMM Insertion 25

FIGURE 4-1 Switch SW1 HOST - Description 26

nc...

I

cale Semiconductor,

FIGURE 4-2 Switch SW2 - Description 27

FIGURE 4-3 DIP-Switch 64/32 Bit Setting 28

FIGURE 4-4 Switch SW9 MODCK - Description 29

FIGURE 4-5 Switch SW10 BOOT MODE - Description 30

FIGURE 4-6 Switch SW11 S/W Option - Description 30

FIGURE 4-7 JP4 - FLASH Programming Source Selection 31

FIGURE 4-8 JP9 - 5V CODEC Source Selection 32

FIGURE 5-1 Clock Distribution Scheme 43

FIGURE 5-2 SDRAM Connection Scheme 45

FIGURE 5-3 FLASH SIMM Connection Scheme 47

FIGURE 5-4 MSC8101 to CODEC connection. 51

FIGURE 5-5 RS232 Serial Ports’ Connector 52

FIGURE 5-6 Host Interface Diagram 53

FIGURE 7-1 ADS Power Scheme 65

Frees

MOTOROLA MSC8101ADS RevB User’s Manual VII

For More Information On This Product,

Go to: www.freescale.com

Page 8

Freescale Semiconductor, Inc.

nc...

I

cale Semiconductor,

Frees

VIII MSC8101ADS RevB User’s Manual MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Page 9

nc...

I

cale Semiconductor,

Frees

Freescale Semiconductor, Inc.

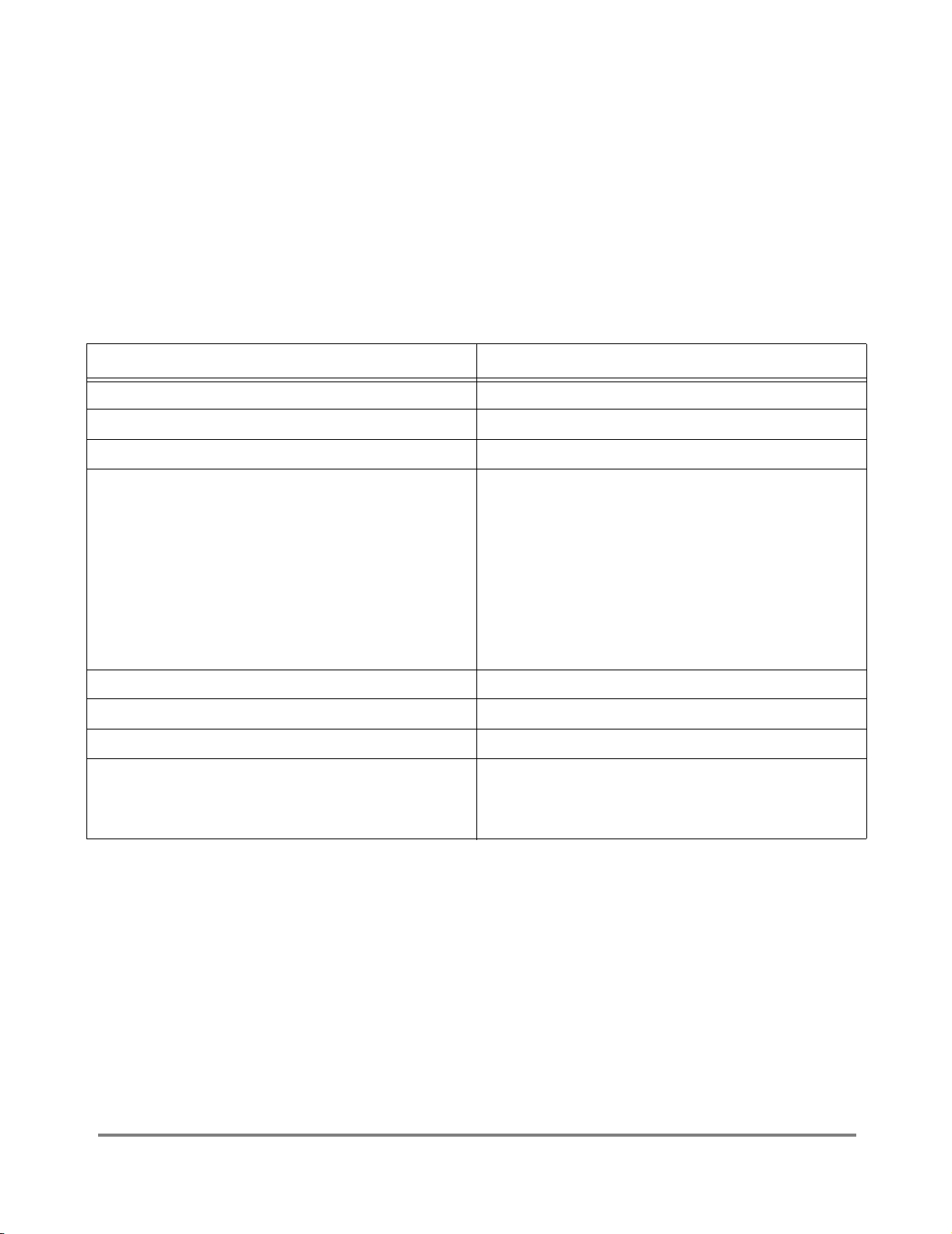

LIST OF TABLES

TABLE 1-1. MSC8101ADS Specifications 12

TABLE 4-1. Available Clock Mode Setting 29

TABLE 4-2. JP1/JP2 Settings 31

TABLE 4-3. SIU Registers’ Programming 35

TABLE 4-4. Memory Controller Initialization for 100(50) MHz 36

TABLE 5-1 Summary Reset Configuration Schemes. 40

TABLE 5-2. Hard Reset Configuration Word 40

TABLE 5-3. MSC8101ADS Chip Select Assignments 44

TABLE 5-4. 100 MHz SDRAM Mode Register Programming 45

TABLE 5-5. Flash Memory Projected Performance Figures 46

TABLE 5-6. Ports Function Enable 49

TABLE 5-7. CS4221 Programming 51

TABLE 5-8. Host I/F Interconnect signals 54

TABLE 5-9. BCSR0 Description 55

TABLE 5-10. BCSR1 Description 56

TABLE 5-11. Peripheral’s Availability Decoding. 58

TABLE 5-12. BCSR2 Description 58

TABLE 5-13. Flash Presence Detect (7:5) Encoding 59

TABLE 5-14. Flash Presence Detect (4:1) Encoding 59

TABLE 5-15. BCSR3 Description 60

TABLE 5-16. EXTOOLI(0:3) Assignment 61

TABLE 5-17. External Tool Revision Encoding 61

TABLE 5-18. ADS Revision Encoding 61

TABLE 6-1. MSC8101ADS Memory Map 63

TABLE 7-1. Off-Board Application Maximum Current Consumption 66

TABLE A-1. MSC8101ADS Bill Of Material 68

TABLE B1-2. P1 - System Expansion - Interconnect Signals 77

TABLE B1-3. P2 - CPM Expansion - Interconnect Signals 82

TABLE B1-4. P3 - ISP Connector - Interconnect Signals 90

TABLE B1-5. P4 - Host Interface Connector - Interconnect Signals 90

TABLE B1-6. P6 - JTAG/ONCE Connector - Interconnect Signals 92

TABLE B1-7. P12 - Ethernet Port Interconnect Signals 93

TABLE B1-8. P17,P18 - T1/E1 Line Connectors Interconnect Signals 94

TABLE B1-9. P19,P21,P24 - Stereo Phone Connectors Interconnect Signals 94

TABLE B1-10. P27A Interconnect Signals 95

TABLE B1-11. P27B Interconnect Signals 95

MOTOROLA MSC8101ADS RevB User’s Manual IX

For More Information On This Product,

Go to: www.freescale.com

Page 10

Freescale Semiconductor, Inc.

nc...

I

cale Semiconductor,

Frees

T-X MSC8101ADS RevB User’s Manual MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Page 11

Freescale Semiconductor, Inc.

General Information

1 - General Information

1•1 Introduction

This document describes the engineering specifications of the MSC8101ADS board based on the

MSC8101- first member of the family of programmable DSP based around the SC100 DSP cores.

It integrates a high-performance Star*Core SC140 DSP is four ALU DSP Core, large on-chip

memory (1/2 MByte), Communication Processor Module compatible with PowerQUICCII

(MPC8260) CPM, a very flexible system integration unit (SIU) and a 16-channel DMA engine.

This board is meant to serve as a platform for s/w and h/w development around the MSC8101 processor. Using its on-board resources and its associated debugger, a developer is able to download

code, run it, set breakpoints, display memory and registers and connect proprietary h/w via the expansion and host interface connectors, to be incorporated into a desired system with the MSC8101

processor.

This board could also be used as a demonstration tool, i.e., application s/w may be burned

its flash memory and ran in exhibitions etc.

A

into

nc...

I

cale Semiconductor,

Frees

1•2 Abbreviations’ List

• Processor - The MSC8101

• ADS - The MSC8101ADS, the subject of this document

• SDRAM Machine - Synchronous Dynamic RAM Machine

• UPM - User Programmable Machine

• GPCM - General Purpose Chip-select Machine

• CPM - Communication Processor Module

• FCC - Fast communications controller

• SCC - Serial communications controller

• SMC - Serial management controller

• TDMA(B,C,D) - One of four A(B,C,D) time-division multiplexed interfaces

• HID16 - Host Parallel Interface 16 bit-wide

• GPL - General Purpose Line (associated with a UPM)

• EOnCE - Enhanced On-Chip Emulation (debug port)

• EE - EOnCE Event Signal

• BCSR - Board Control & Status Register

• ZIF - Zero Input Force

• BGA - Ball Grid Array

• SIMM - Single In-line Memory Module

• MII - Media Independent Interface

1•3 Related Documentation

[1] StarCore 140 Architecture Functional Specification

[2] SC140 DSP Core Reference Manual

[3] MSC8101 Reference Manual

[4] MSC8101 Hardware Specification

A. Either on or off-board.

MOTOROLA MSC8101ADS RevB User’s Manual 11

For More Information On This Product,

Go to: www.freescale.com

Page 12

Freescale Semiconductor, Inc.

PMC-SIERRA 5350 Long Form Data Sheet

[5]

[6] PMC-SIERRA 5350 Errata Notice

[7] PMC-SIERA 5350 Reference Design

[8] LXT970A (by Level One) Data Sheet

[9] LXT970 Demo Board User’s Guide

General Information

1•4 Specification

The MSC8101ADS specifications are given in TABLE 1-1. "MSC8101ADS Specifications" below

TABLE 1-1. MSC8101ADS Specifications

CHARACTERISTICS SPECIFICATIONS

Power requirements (no other boards attached) +5V DC @ 2A (Typ.), 3A (Max.)

nc...

I

cale Semiconductor,

Frees

MSC8101 Internal clock up to 300MHz @ 1.5V

PowerPC(60x) Bus Running up to 100 MHz Bus Clock Frequency.

PowerPC (60x) bus:

Total address range:

Data Bus width:

Flash memory mounted on SIMM

Synchronous DRAM 100MHz soldered (non-buffered)

Operating temperature 0

Storage temperature -25

Relative humidity 5% to 90% (non-condensing)

Dimensions:

Length

Width

PCB Thickness

4 Giga Bytes (32 address lines)

256 KBytes External (18 address lines)

64 bit without Host Interface(HID16)/32bit with HID16

8 MByte, 32 bits wide expandable to 32 MBytes.

16MBytes, organized as 2x8Megx32 bit. May be reconfiged

to 32bits wide with 8MByte (expansion to 16MByte is

optional)

O

C - 30OC (room temperature)

O

C to 85OC

9.549" (240 mm)

7.480" (190 mm)

0.063" (1.6 mm)

12 MSC8101ADS RevB User’s Manual MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Page 13

Freescale Semiconductor, Inc.

General Information

1•5 ADS Features

o 64-bit MSC8101, running up to @ 100MHz external bus frequency.

o 8 MByte, 80 pin Flash SIMM reside after buffer. Support for up to 32 MByte, con-

trolled by GPCM, 5V Programmable, with Automatic Flash SIMM identification, via

BCSR.

o 16 MByte unbuffered SDRAM on PPC bus, controlled by SDRAM machine, sol-

dered directly on the board. Data bus width 64/32 bits is controlled by Jumper Array. The narrow data bus configuration is supported with 8MByte SDRAM memory

space.

o 256 KBit serial EEPROM on I2C bus.

o Board Control & Status Register - BCSR, controlling Board’s Operation on PPC

bus. Access via GPCM.

o Programmable Hard-Reset Configuration via Flash memory or Host Interface.

nc...

I

Also may be forced from BCSR.

o High density (MICTOR) Logic Analyzer connectors, carrying all MSC8101 signals,

for fast logic analyzer connection.

cale Semiconductor,

Frees

o 155 Mbps ATM UNI on FCC1 with Optical I/F, connected to the MSC8101 via

UTOPIA, using the PMC-SIERA 5350.

o 10/100-Base-T Port on FCC2 with T.P. I/F, MII controlled, using Level-One

LXT970.

o Four channels T1/E1 on TDMs using Infeneon Quad FALC PEB22554.

o 24-bit audio-CODEC CS4221 connected to the CPM’s TDMA1 channel with

gained stereo audio Input/Output.

o Dual RS232 port residing on SCC1 & SMC1.

o Module disable (i.e., low-power mode) option for all communication transceivers -

BCSR controlled, enabling use of communication ports, off-board via expansion

connectors.

o Dedicated MSC8101’s communication ports expansion connectors for convenient

tools’ connection, carrying also necessary bus signals, for transceivers’ M/P I/F

connection. Use is done with 2 X 128 pin DIN 41612 receptacle connectors.

o Host I/F, providing through expansion connectors or dedicated header.

o External Tools’ Identification & status read Capability, via BCSR.

o SMB-connectors for external pulse generator and clock output

o Configuration setting via DIP switches.

o Power-On Reset Push, Soft - Hard Reset Push, ABORT Push - Buttons.

o Ext. Single 5V DC Supply with Reverse / Over Voltage Protection for Power Input

and Power-On sequence.

MOTOROLA MSC8101ADS RevB User’s Manual 13

For More Information On This Product,

Go to: www.freescale.com

Page 14

Freescale Semiconductor, Inc.

o On-board 1.2V - 2.2V adjustable for MSC8101 Internal Logic Operation and

3.3V±10% fixed Voltage Regulators for other circuits. May be bypassed in case of

external power supplying.

o Software Option Switch provides 8 S/W options via BCSR.

o LED’s for power supply, module enables, timer expired and SW indications.

nc...

I

General Information

cale Semiconductor,

Frees

14 MSC8101ADS RevB User’s Manual MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Page 15

Freescale Semiconductor, Inc.

General Information

FIGURE 1-1 MSC8101ADS Block Diagram

nc...

I

cale Semiconductor,

Frees

Ext CLK

14pin

To

Command

Converter

RJ45

Clock

16.4/25MHz

Reset,Config

Interrupts

MSC8101

332 pin

19x19 matrix

(3M Socket)

JTAG/OnCE

QFALC

4xT1/E1

0.8mm

3.3V

TDMA,B,C,D

ClkOut

HOST Buffers

D[32:59]

DATA Transceivers &

Address Buffers

D[0:31]

3.3V<->5V

3ns

Clock Buffer

1

7

DLLIN

SCC1,SMC1

FCC2

MIIctrl.

FCC1

EEPROM

I2C

PPC (non-buffered)

28

Control &

Status Register

3.3V<->5V

D[0:59]

Address Mux

for variable

Port Size 64/32

HOST I/F

PPC Bus (buffered)

Flash Detect

Altera

3.3V

LXT970

PM5350

SDRAM

2Megx32

Flash SIMM.

8 - 32MByte

32 - Bit

MC145583

3.3V

Magnetics

5V

Buffered Exp. System Bus

3.3V

*

2

1

36pin

Host PORT

5V

D-9RJ45-8

OPTICAL

2

3

2

S

R

T

e

s

a

B

0

0

1

/

0

1

ATM-155

16Mbyte @ 64bit

S

T

R

O

P

T

R

O

P

PORT

CPM

DIN 41612

TDMA1

SPI

cnt

CODEC

CS4221

From MIC/LINE STEREO

To STEREO AUDIO AMP

* - Additional memory part is optional

MOTOROLA MSC8101ADS RevB User’s Manual 15

For More Information On This Product,

Go to: www.freescale.com

CPM EXPANSION

Page 16

Freescale Semiconductor, Inc.

Hardware Preparation

2 - Hardware Preparation

2•1 INTRODUCTION

This chapter provides unpacking instructions, hardware preparation, and installation instructions

for the

2•2 UNPACKING INSTRUCTIONS

Unpack equipment from shipping carton. Refer to packing list and verify that all items are present.

Save packing material for storing and reshipping of equipment.

nc...

I

MSC8101ADS.

NOTE

If the shipping carton is damaged upon

receipt, request carrier’s agent to be

present during unpacking and inspection of

equipment.

CAUTION

AVOID TOUCHING AREAS OF

INTEGRATED CIRCUITRY; STATIC

DISCHARGE CAN DAMAGE CIRCUITS.

cale Semiconductor,

Frees

2•3 HARDWARE PREPARATION

To select the desired configuration and ensure proper operation of the MSC8101-ADS board,

changes of the DIP-Switch settings may be required before installation. The location of the

switches, indicators, DIP-Switches, and connectors is illustrated in FIGURE 2-1 "MSC8101-ADS

Top Side Part Location diagram" on page 17. The board has been factory tested and is shipped

with DIP-Switch settings as described in the following paragraphs. Parameters can be changed for

the following conditions:

• The Processor Internal Logic and PLLs Supply Level (1.6V) via potentiometer RP2.

• The Processor I/O Supply Voltage (3.3V) via potentiometer RP1 (be careful since this

power supply feeds another logic devices on the ADS and tool boards).

• The Processor Clocking:

o MODCK(1:3). Determining Core’s and CPM’s PLLs multiplication factor via the

DIP Switch SW9.

o MODCKH(4:6) for the Flash Memory Config. Word/Host Config Word (Power-On

Reset Source Dependent) or from the DIP Switch SW9 for FPGA Config. Setting

(Safe Mode).

o Clock mode update requires power up operation.

• Hard Reset Configuration Word source is selected by the DIP Switch SW9/7.

• Normal (64-bit wide) or Narrow (32-bit wide) Data bus width for Host I/F mode is

selected by the DIP Switches SW5,6.

16 MSC8101ADS RevB User’s Manual MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Page 17

Freescale Semiconductor, Inc.

FIGURE 2-1 MSC8101ADS Top Side Part Location diagram

nc...

I

Hardware Preparation

cale Semiconductor,

Frees

Host SW

EE SW

64/32 Select

Boot Mode SW

Config SW

S/W Opt

MOTOROLA MSC8101ADS RevB User’s Manual 17

For More Information On This Product,

Go to: www.freescale.com

Page 18

Freescale Semiconductor, Inc.

2•3•1 Setting The Core Supply Voltage Level

The internal Logic & PLL’s of the MSC8101 is powered separately through a supply bus named

1V5. The voltage level over this power bus may vary between 0.9V - 2.1V. In the lower voltage

level, the Processor will operate at lower frequency range, consuming a smaller amount of power

and vice-versa for the higher voltage level.

1V5 power level is factory set for 1.5V, but may be changed by RP2.

2•3•2 Setting MODCK(1:3) For Initial PLLs’ Multiplication Factor - SW9

During Power On reset sequence the Processor samples the three MODCK(1:3) lines which are

driven by Altera FPGA device in accordance with SW9/1-3 setting. MODCK_HI field (MODCK[4–

6]), taken from the reset configuration word, are read from the Flash memory (default value from

Altera FPGA for non-programmed Flash is read from SW9/4-6) or from Host Interface to establish

with the multiplication factors of the CPM’s and Core’s PLLs. SW9 is shown in FIGURE 4-4 "Switch

SW9 MODCK - Description" on page 29:

Some Clock Configuration can see in FIGURE 5-1 on page 43:

2•3•3 Setting HReset Configuration Source

The HReset Configuration WordA, read by the Processor while HRESET~ is asserted, may be

nc...

I

taken from three sources:

1) Flash Memory SIMM.

2) Altera FPGA (Safe Mode).

Hardware Preparation

cale Semiconductor,

Frees

3) Host I/F.

When SW9/7 is OFF, the Hard Reset Configuration Word is taken from Altera FPGA, when it is

ON, the Hard Reset Configuration Word is taken from the Flash SIMM. If SW9/8 (Configuration)

set OFF the Processor will be configured from Host, independent of SW9/7 (Flash Configuration

Enable) position. For correct operation for Host Config. Mode Data bus width will be set to 32-bit

wide.

A. In fact 8 Hard-Reset configuration words are read by a configuration master, however only the first is rel-

evant for a single MSC8101.

18 MSC8101ADS RevB User’s Manual MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Page 19

Freescale Semiconductor, Inc.

Installation Instructions

3 - Installation Instructions

The MSC8101ADS may be configured according to the required working environment as follows:

• Host Controlled Operation through OnCE Port

• Host Interface Operation through HDI16 Port

• Stand-Alone Mode

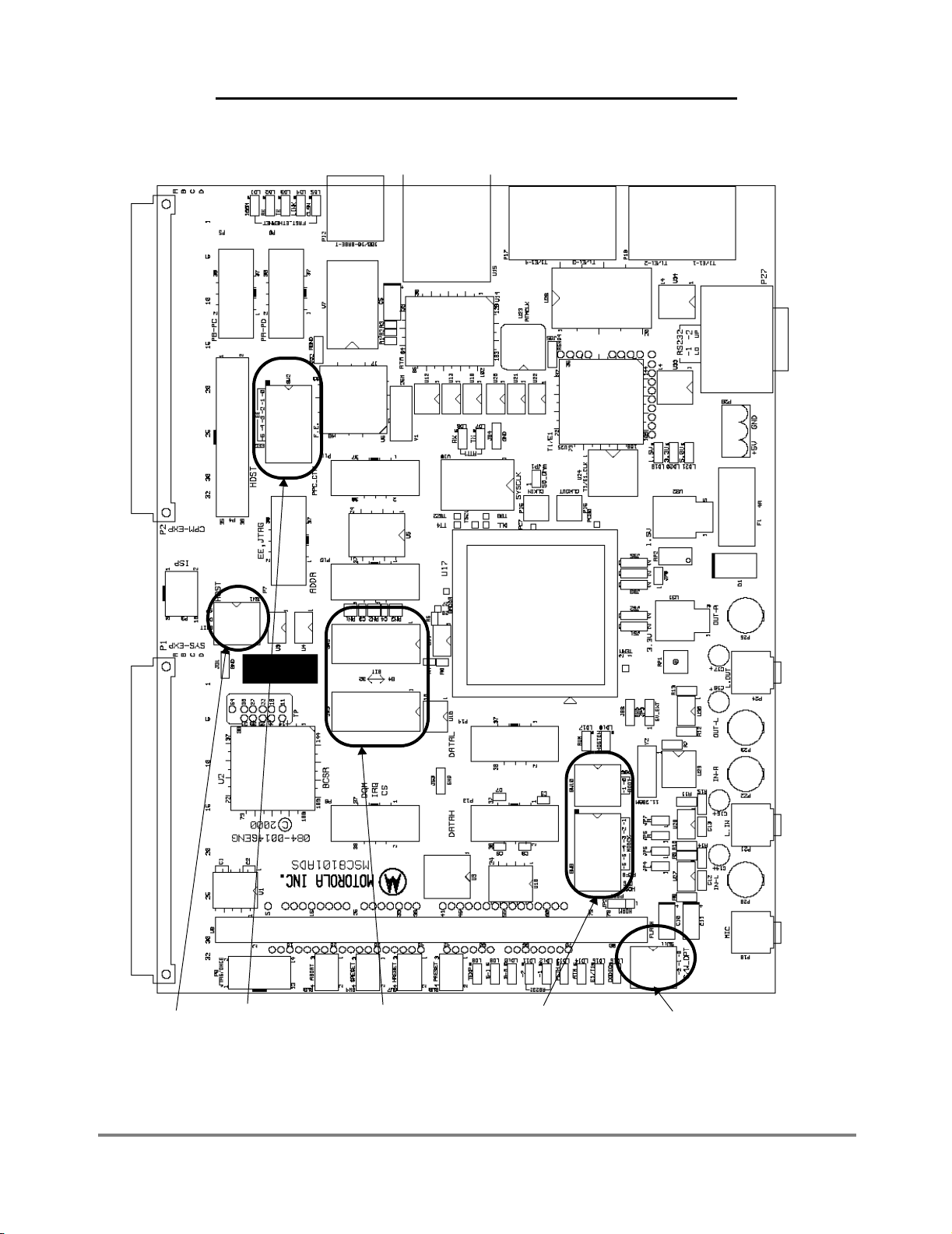

3•1 OnCE Connection Scheme

In this configuration the MSC8101ADS is controlled by a host computer via the OnCE Port, which

is a subset of the JTAG port. This configuration allows for extensive debugging using on-host debugger. The host is connected to the ADS by a Command Converter provided by a third party

(Macraigor Systems).

FIGURE 3-1 Host System Debug Scheme A

Host

Computer

nc...

I

Media I/F

Command

Converter

14 Wire

Flat Cable

cale Semiconductor,

Frees

5V Power Supply

3•2 Host I/F Operation

In this configuration the MSC8101ADS is using HDI16 I/F that provide 16-bit wide, full-duplex,

double-buffered, parallel port to connect directly to the data bus of a host processor. The HDI16

supports two classes of interfaces:

• Host processor/Microcontroller (MCU) connection interface

• DMA controller interface

A Host Device may be connected to the ADS via dedicated 36pin two rows header or via 128pin

DIN - connector P2.

MOTOROLA MSC8101ADS RevB User’s Manual 19

For More Information On This Product,

Go to: www.freescale.com

Page 20

Freescale Semiconductor, Inc.

Installation Instructions

FIGURE 3-2 Host System Debug Scheme B

Host

Computer

Media I/F

nc...

I

Command

Converter

14 Wire

Flat Cable

To JTAG/OnCE

36Wire

Flat Cable

Host

Device

5V Power Supply

cale Semiconductor,

Frees

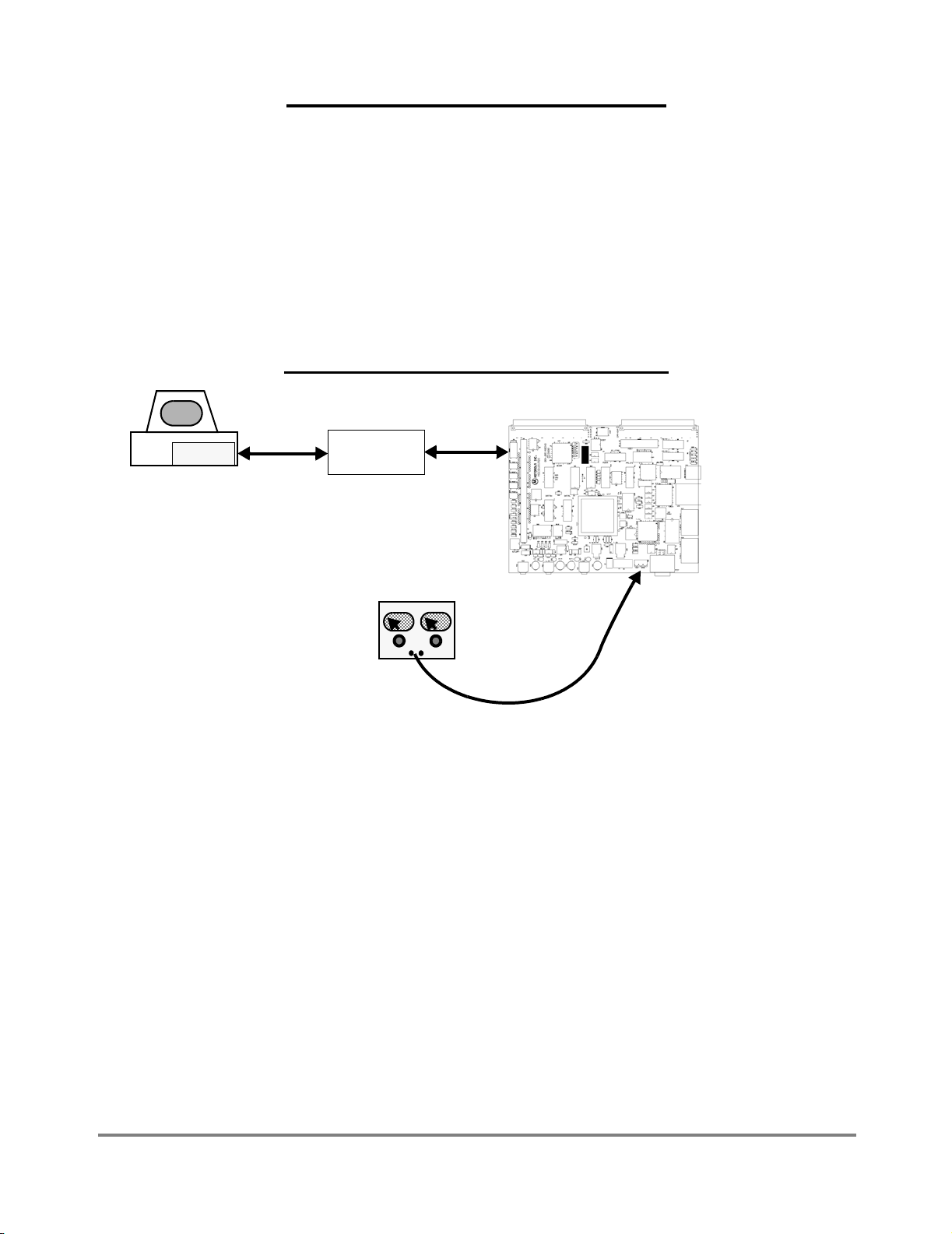

3•3 Stand Alone Operation

In this mode, the ADS is not controlled by the host via the OnCE port. It may connect to host via

one of its other ports, e.g., RS232 port, Fast Ethernet port, ATM155 port etc. Operating in this

mode requires an application program to be programmed into the board’s Flash memory.

20 MSC8101ADS RevB User’s Manual MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Page 21

5V Power Supply

Freescale Semiconductor, Inc.

Installation Instructions

FIGURE 3-3 Stand Alone Configuration

t

e

n

r

k

e

r

h

o

t

w

E

t

e

N

A

T

M

1

5

5

(

O

p

t

i

c)

T1/E1

four ch.

2

3

2

S

R

Host

Computer

nc...

I

cale Semiconductor,

Frees

Audio

Stereo

3•4 +5V Power Supply Connection

The MSC8101 requires +5V DC @ 4A max, power supply for operation. Connect the +5V power

supply to connector P26 as shown below:

FIGURE 3-4 P26: +5V Power Connector

+5V

GND

GND

P26 is a 3 terminal block power connector with power plug. The plug is designed to accept 14 to

22 AWG wires. It is recommended to use 14 to 18 AWG wires. To provide solid ground, two GND

terminals are supplied. It is recommended to connect both GND wires to the common of the power

supply, while “Hot” line is connected with a single wire.

Since hardware applications may be connected

to the MSC8101ADS via the expansion connectors P1 and P2, the additional power consumption should be taken into consideration when a

power supply is connected to the MSC8101ADS.

1

2

3

NOTE

3•5 JTAG/OnCE Connector - P6

The MSC8101ADS JTAG/OnCE connector, P6, is a 14 pin, two rows, header connector with key.

The connection between the MSC8101ADS and the Command Converter is by a 14 line flat cable,

MOTOROLA MSC8101ADS RevB User’s Manual 21

For More Information On This Product,

Go to: www.freescale.com

Page 22

Freescale Semiconductor, Inc.

supplied with the Command Converter obtained from Macraigor Systems. FIGURE 3-5 "P6 -

JTAG/OnCE Port Connector" below shows the pin configuration of the connector.

Installation Instructions

FIGURE 3-5 P6 - JTAG/OnCE Port Connector

1

TDI

3

TDO

5

TCK

7

N.C.

RESET

nc...

I

9

11

3.3V

13 14

N.C.

2

GND

4

GND

6

GND

8

KEY (NO PIN)

10

TMS

12

N.C.

TRST

3•6 HOST I/F Connector - P4

The MSC8101ADS HOST I/F connector, P4, is a 36 pin, two rows, header connector. The

connection between the MSC8101-ADS and the Host Board is by a 36 line flat cable, not shipped

with the ADS. FIGURE 3-6 "P4 - Host I/F Connector" below shows the pin configuration of the

connector.

cale Semiconductor,

Frees

22 MSC8101ADS RevB User’s Manual MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Page 23

Freescale Semiconductor, Inc.

Installation Instructions

FIGURE 3-6 P4 - Host I/F Connector

nc...

I

cale Semiconductor,

Frees

GND

HD0

HD2

HD4

HD6

HD8

HD10

HD12

HD14

GND

HA0

HA2

HCS1

HRRQACK

HRDRW

HRESET

3.3V

GND

1

3

5

7

9

11

13 14

15 16

17

19

21

23

25

27

29

31

35

26

28

30

32

3433

36

2

4

6

8

10

12

18

20

22

24

GND

HD1

HD3

HD5

HD7

HD9

HD11

HD13

HD15

GND

HA1

HA3

HCS2

HREQ

HDS

PORST

N.C.

GND

3•7 Terminal to MSC8101ADS RS-232 Connection

A serial (RS232) terminal or any other RS232 equipment, may be connected to both connectors

P27/A-B (Upper and Lower). This connectors are a 9 pin, female, D-type connectors, arranged in

a stacked configuration. P27A connected to SCC1 of the MSC8101 is the lower and P27B,

connected to SMC1 of the MSC8101, is the upper in the stack.

The connectors are arranged in a manner that allows for 1:1 connection with the serial port of an

IBM-AT

to DCE connection unlike it the P27B supports Null Modem connection (DTE to DTE). The

difference is shown in FIGURE 3-7 and FIGURE 3-8.

A

or compatibles, i.e. via a flat cable. The pinout which is not identical - P27A supports DTE

A. IBM-AT is a trademark of International Business Machines Inc.

MOTOROLA MSC8101ADS RevB User’s Manual 23

For More Information On This Product,

Go to: www.freescale.com

Page 24

Freescale Semiconductor, Inc.

Installation Instructions

FIGURE 3-7 P27A - Upper RS-232 Serial Port Connector

CD

TX 2

RX 3

DTR

GND

1

4

5

DSR6

N.C.

7

CTS

8

9N.C.

FIGURE 3-8 P27B - Lower RS-232 Serial Port Connector

N.C.

N.C.

nc...

I

GND

TX 2

RX 3

1

4

5

N.C.6

N.C.

7

N.C.

8

9N.C.

3•8 10/100-Base-T Ethernet Port Connection

The 10/100-Base-T port connector - P12, is an 8-pin, 90o, receptacle RJ45 connector. The connection between the 10/100-Base-T port to the network is done by a standard cable, having two

RJ45/8 jacks on its ends.

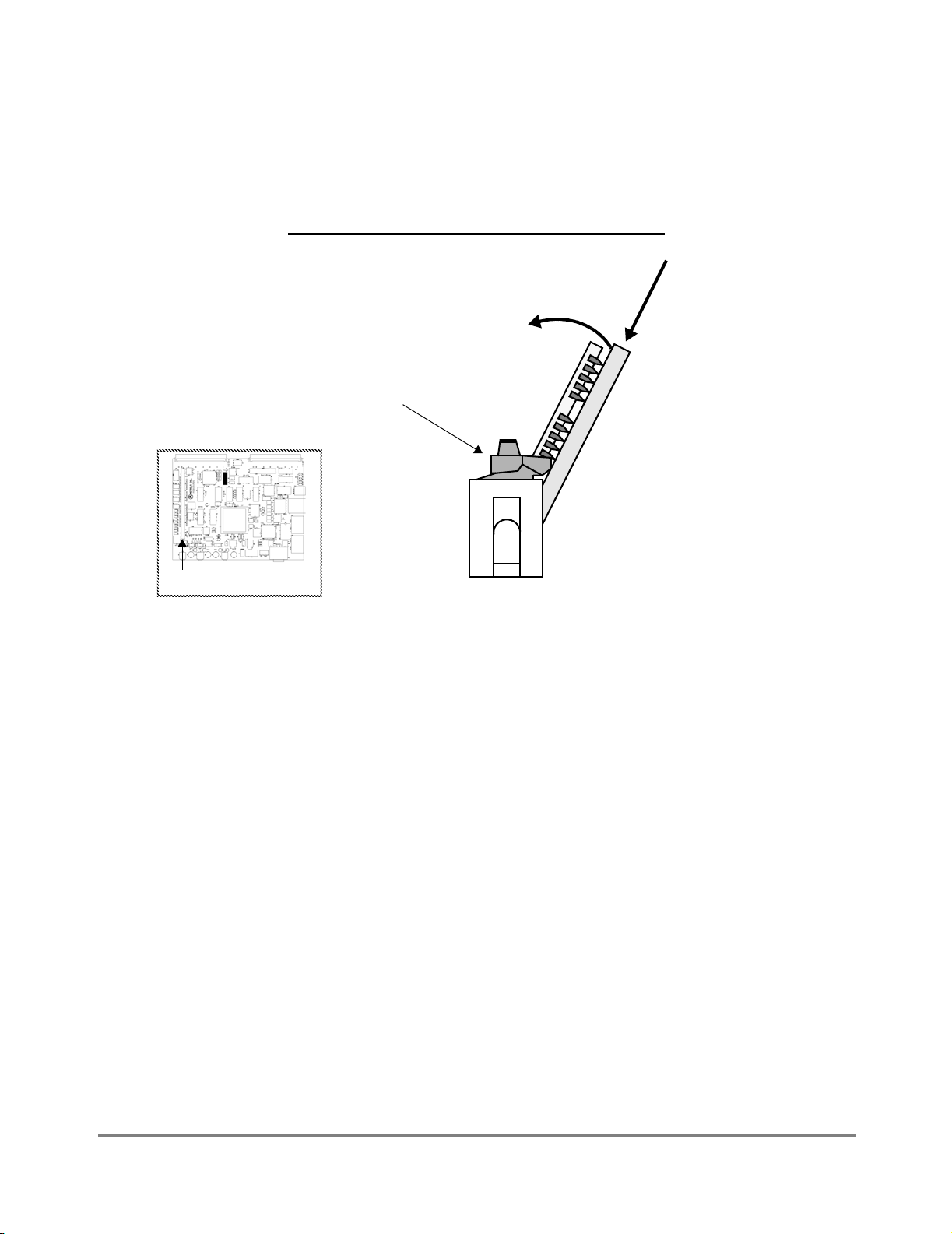

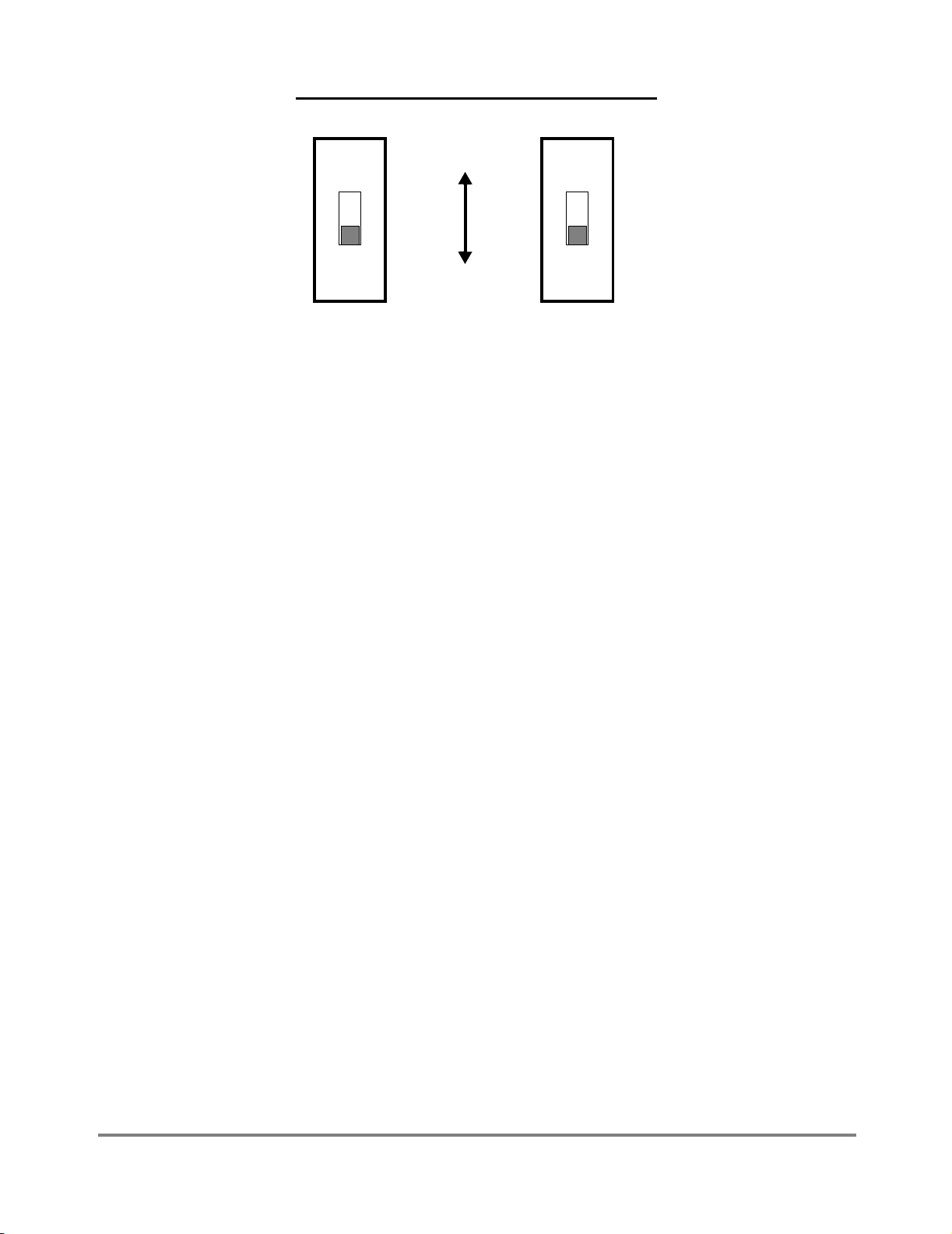

3•9 Flash Memory SIMM Installation

To install a memory SIMM, it should be taken out of its package, put diagonally in its socket - U8

and then raised to a vertical position until the metal lock clips are locked. See FIGURE 3-9 "Flash

Memory SIMM Insertion" on page 25.

cale Semiconductor,

Frees

24 MSC8101ADS RevB User’s Manual MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Page 25

Freescale Semiconductor, Inc.

Installation Instructions

CAUTION

The memory SIMMs have alignment nibble

near their # 1 pin. It is important to align the

memory correctly before it is twisted, otherwise damage might be inflicted to both the

memory SIMM and its socket.

FIGURE 3-9 Flash Memory SIMM Insertion

(1)

Insert

(2)

Turn

Flash

Metal Lock Clip

nc...

I

SIMM

cale Semiconductor,

Frees

SIMM

SIMM Socket

MOTOROLA MSC8101ADS RevB User’s Manual 25

For More Information On This Product,

Go to: www.freescale.com

Page 26

Freescale Semiconductor, Inc.

Operating Instructions

4 - Operating Instructions

4•1 INTRODUCTION

This chapter provides necessary information to use the MSC8101-ADS in host-controlled and

stand-alone configurations. This includes controls and indicators, memory map details, and

software initialization of the board.

4•2 SWITCHES

The MSC8101ADS has the following switches:

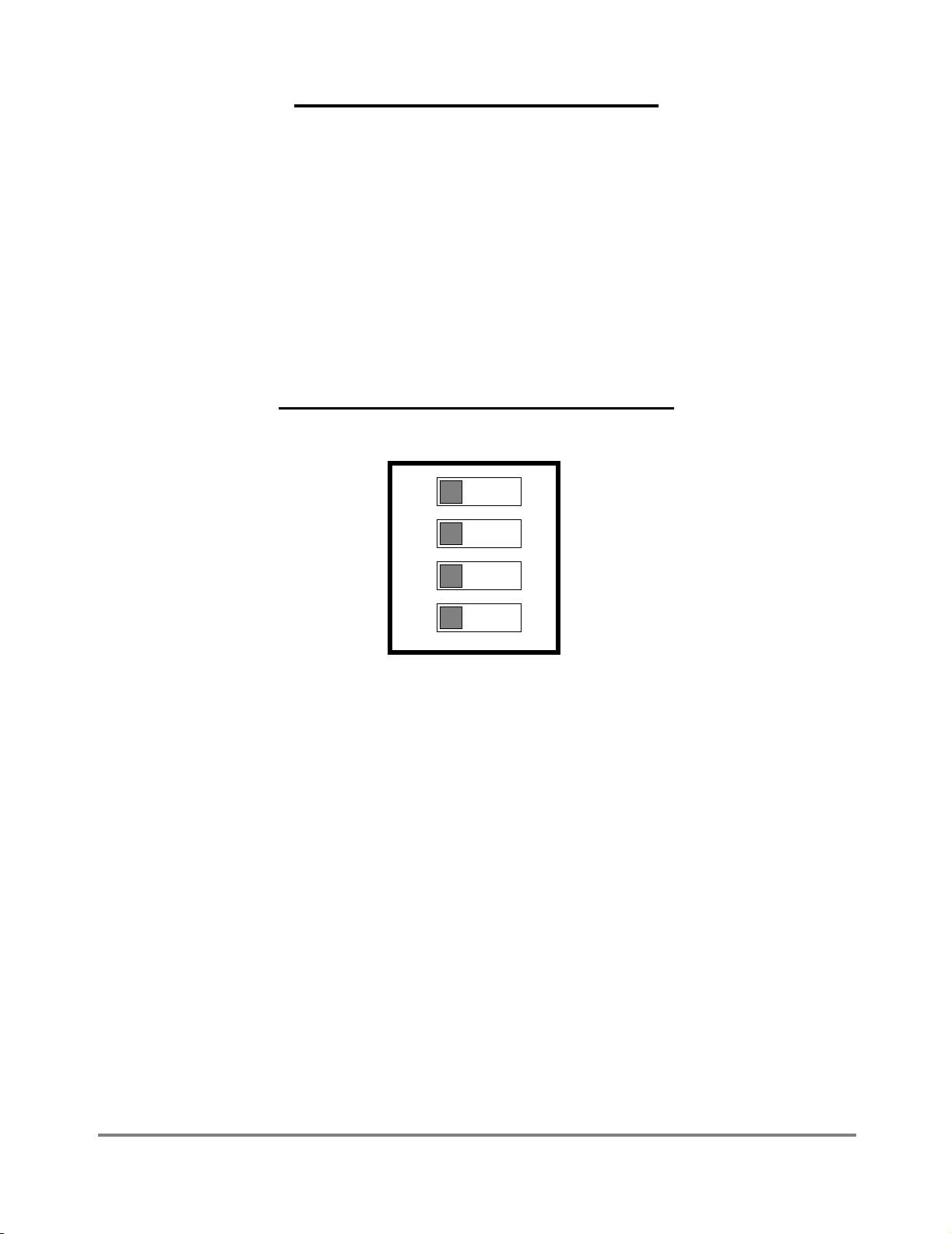

4•2•1 Host I/F Setting - SW1

This switch is using for manually set a Host Bus parameters. When Host Configuration is enable

the DIP switch SW1/1-3 will be connected to Data Bus through tri-state buffers and sampled by the

Processor. The SW1 factory set is all ON.

FIGURE 4-1 Switch SW1 HOST - Description

nc...

I

SW1

cale Semiconductor,

Frees

RESERVED

8/16BIT

DualSingleStrobe

StrobePolarity

Set to ‘0’

ON

<=

4

3

2

1

=> Set to ’1’

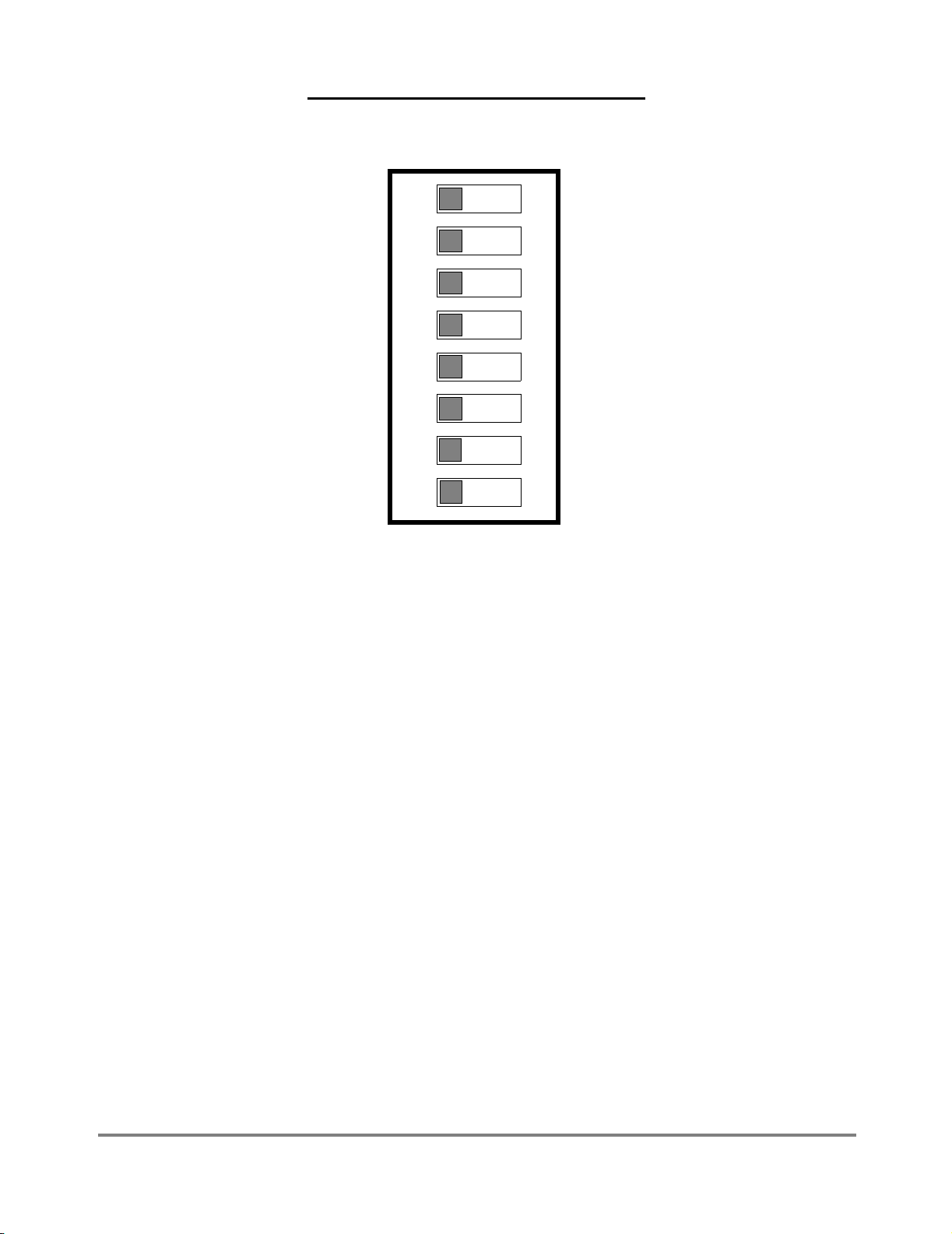

4•2•2 Emulator Enable (EE) - SW2

This switch controls lines EE0-EE7,EED, connected to appropriate pins of the Processor. When

Reset Configuration executed, EEs lines, involved in one, are driven by FPGA. In fact, they are

EE0, EE1, EE4 and EE5 which sampled at the rising edge of PORESET~. After configuration is

done level of all EE-signals is set by the switch SW2/1-7. Their status may be read out via

BCSR3/0-6. SW2 is factory set to all ON.

26 MSC8101ADS RevB User’s Manual MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Page 27

Freescale Semiconductor, Inc.

Operating Instructions

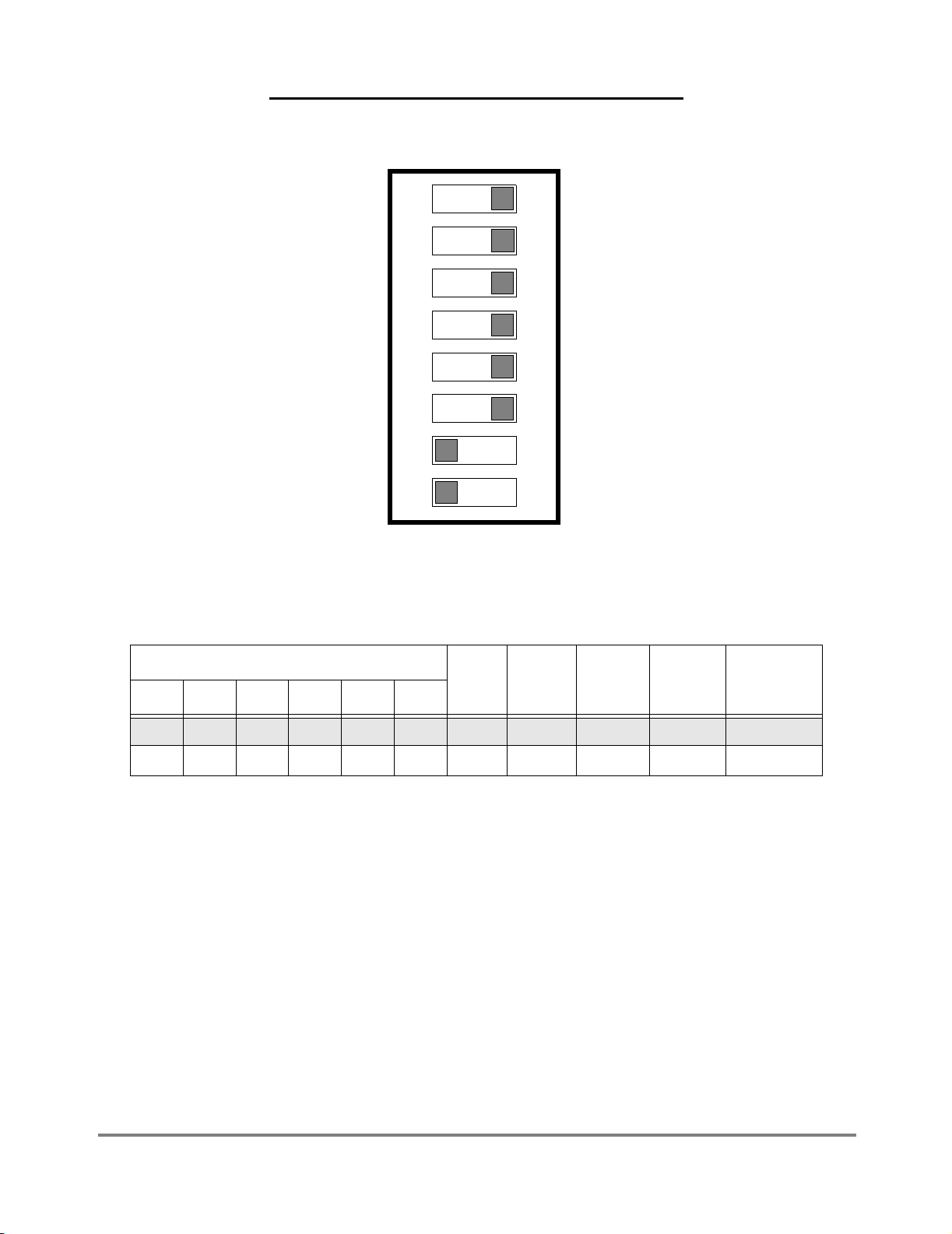

FIGURE 4-2 Switch SW2 - Description

SW2

nc...

I

cale Semiconductor,

Frees

RESERVED

EED

EE5

EE4

EE3

EE2

EE1

EE0

Set to ‘0’

ON

<=

8

7

6

5

4

3

2

1

=> Set to ’1’

4•2•3 ABORT Switch - SW3

The ABORT switch is normally used to abort program execution, this by issuing a level 0 nonmaskable interrupt to the Processor. If the ADS is in stand alone mode, it is the responsibility of

the user to provide means of handling the interrupt, since there is no resident debugger with the

MSC8101-ADS. The ABORT switch signal is denounced, and can not be disabled by software.

4•2•4 SOFT RESET (SRESET) Switch - SW4

The SOFT reset switch SW4 performs Soft Reset to the Processor internal modules, maintaining

it’s configuration (clocks & chip-selects) and SDRAMs’ contents. The switch signal is debounced,

and it is not possible to disable it by software.

4•2•5 DATA Bus Width Setting - SW5 & SW6.

Two switches SW5 & SW6 are using together for preparing the SDRAM Memory Banks for Host

Interface Mode when HDI16 interface is provided over Data Bus lines D32-D63. They should be

set in “32bit” position when DIP-Switch SW9/8 HOST CFG set ON (PPC bus supports Host I/F)

and vice versa - “64bit” when Host I/F disable.

MOTOROLA MSC8101ADS RevB User’s Manual 27

For More Information On This Product,

Go to: www.freescale.com

Page 28

Freescale Semiconductor, Inc.

Operating Instructions

FIGURE 4-3 DIP-Switch 64/32 Bit Setting

SW5 SW6

32

BIT

64

4•2•6 HARD RESET (HRESET) - Switch - SW7

HARD reset is generated when switch SW7 is pressed. When the Processor executes HARD reset

sequence, all its configuration is lost, including data stored in the SDRAMs and the Processor has

nc...

I

to be re-initialized.

4•2•7 Power-On RESET Switch (PRESET) - SW8

The Power-On reset switch SW8 performs Power-On reset to the MSC8101, as if the power was

re-applied to the ADS. When the Processor is reset that way, all configuration and all data residing

in volatile memories are lost. After PORST~ signal is negated, the Processor re-acquires the

power-on reset configuration data from the Flash (Altera) or Host I/F.

cale Semiconductor,

Frees

4•2•8 Configuration Switch - SW9

SW9 is a 8-switch DIP-Switch. This switch is connected over Altera device to MODCK(1:6) lines

of the Processor. The combination of the switches composing SW9, sets, during Power-On reset

sequence, the MODCK(1:6) field for the MSC8101. The switch SW9/7 establishes Configuration

Word Source. If SW9/7 is set to ON position Configuration Word will be loaded from the Flash, otherwise from Altera device (default). The Host Configuration will be chosen with SW9/8 set ON,

when SW9/8 is OFF - PPC bus has 64-bit width.

The Switch SW9 is factory set to (1 - OFF, 2 - ON, 3 - OFF, 4 - OFF (X), 5 - ON, 6 - OFF, 7,8 OFF).

28 MSC8101ADS RevB User’s Manual MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Page 29

Freescale Semiconductor, Inc.

Operating Instructions

FIGURE 4-4 Switch SW9 MODCK - Description

SW9

HOST

CFG

FCFG

MODCK6

MODCK5

MODCK4

MODCK3

nc...

I

MODCK2

MODCK1

Set to ‘0’

ON

<=

TABLE 4-1. Available Clock Mode Setting

MODCK-

-1 -2 -3 -4 -5 -6

0 0 1 1 1 1 57

0010019

Clock

Mode

a

b

cale Semiconductor,

a. Factory setting.

b. Alternative clock mode for 100MHz bus frequency requires clock oscillator 20MHz

8

7

6

5

4

3

2

1

=> Set to ’1’

Clock In

MHz

55 137.5 55

20 200 100 300

CPM

MHz

PPC Bus

MHz

a

SC140 Core

MHz

275

Frees

4•2•9 Boot Mode Select - SW10

SW10 is a 4-switch Dip-Switch with three poles in use. This switch selects Boot Mode over Altera

FPGA on the Processor inputs EE0, EE4, EE5 during Power-On reset sequence. Setting SW10/1

(DBG) to ON brings holding EE0 at logic 1 during reset that puts the SC140 core into DEBUG

MODE. In doing so BTM’s switch position will be ignored. See TABLE 5-1 on page 40 for more

explanation. SW10 is factory set to all ON.

MOTOROLA MSC8101ADS RevB User’s Manual 29

For More Information On This Product,

Go to: www.freescale.com

Page 30

Freescale Semiconductor, Inc.

Operating Instructions

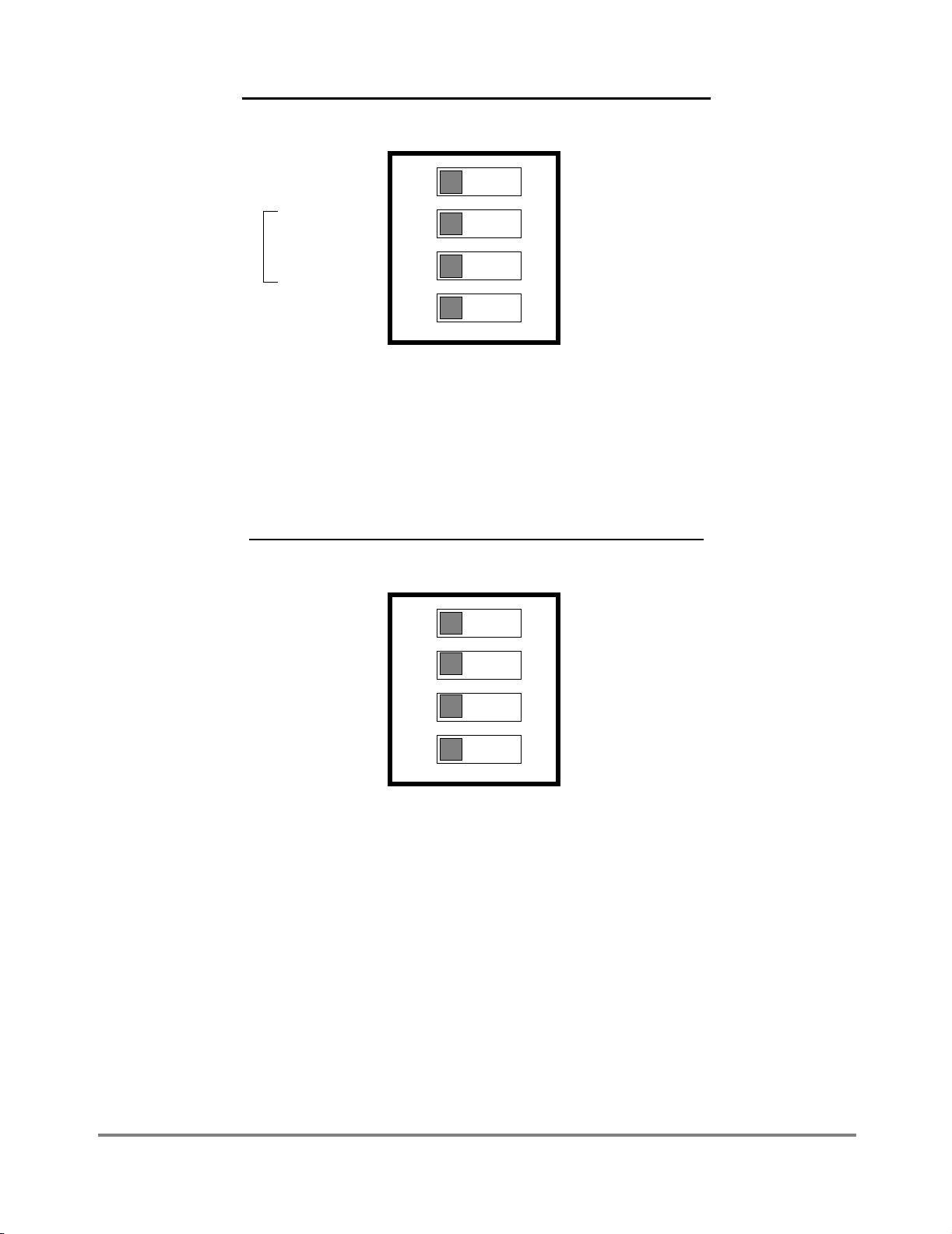

FIGURE 4-5 Switch SW10 BOOT MODE - Description

SW10

RESERVED

BTM1

BOOT

BTM0

DBG

Set to ‘0’

nc...

I

4•2•10 Software Options Switch - SW11

SW11 is a 4-switch Dip-Switch with three poles in use. This switch is connected over SWOPT(0:2)

lines which are available at BCSR2 via bus driver U16, S/W options may be manually selected,

according to SW11 state. SW11 is factory set to all ON.

ON

<=

4

3

2

1

=> Set to ’1’

FIGURE 4-6 Switch SW11 S/W Option - Description

SW11

RESERVED

SWOPT2

SWOPT1

SWOPT0

ON

4

3

2

1

cale Semiconductor,

Set to ‘0’

<=

=> Set to ’1’

Frees

4•3 Jumpers

The MSC8101-ADS has the following jumpers:

4•3•1 JP1 - DLL Disable.

J1 set DLLDIS bit 27 in the HCW loaded from BCSR. When Jumper JP1 is open MSC8101 will be

configured without DLL. If JP3 will closed the DLL is ON. Setting of JP3 is depended on jumper

JP2 (see JP2 description). Default set is JP3-OPEN (DLL disable).

4•3•2 JP2 - Clock Buffer Set.

Jumper J2 allows to change mode of Zero-Delay Buffer JP2. When Jumper JP2 is open ZD buffer

operates in normal mode and require DLL disable setting (JP1 is open). For U44 buffer mode (internal PLL is disable) JP2 should be close. If JP2 is close MSC8101 will be configured without

30 MSC8101ADS RevB User’s Manual MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Page 31

Freescale Semiconductor, Inc.

DLL. See TABLE 4-2. summarized available modes. . Default set is JP3-OPEN (DLL disable).

Operating Instructions

TABLE 4-2. JP1/JP2 Settings

J1 J2

OPEN OPEN PLL Mode DLL disable

CLOSE CLOSE Buffer Mode DLL enable

Clock Driver

U44

MSC8101

Mode

4•3•3 JP3 - 50 Ohm Enable.

JP3 provides 50 Ohm resistance termination in case when using an external clock source via

coaxial cable connected to the SMB CLOCKIN. In so doing the on-board clock oscillator U18 must

be removed from the socket. Default set is JP3-OPEN (termination disable).

4•3•4 JP4 - VPP Source Selector

JP4 selects the source for VPP - programming voltage for the Flash SIMM. When a jumper is

nc...

I

located between pins 1 - 2 of JP4 (Factory Set), the VPP is connected to the 5V0 plane of the ADS.

For 12V programming set VPP will be drawn from external power supply 12V connected to pins

JP4/2,3.

NOTE

Should be taken into consideration that 12V

external power input for Flash SIMM have

no protection.

FIGURE 4-7 JP4 - FLASH Programming Source Selection

JP4

JP4

-

+

12V Ext.

5V

cale Semiconductor,

1

Factory Set

1

Frees

4•3•5 JP5,JP8 - 600 Ohm Termination.

Set for audio measurements. Factory set - JP5,JP8 are OPEN.

4•3•6 JP6,JP7 - MIC Enable.

Set if using external microphone audio source. Factory set - JP6,JP7 are CLOSE.

4•3•7 JP9 - 5V power supply for CODEC

JP9 selects the source for CODEC Power Rail. When a jumper is located between pins 1 - 2 of

JP9 (Factory Set), the CODEC feeds from the 5V0 plane of the ADS. When a jumper is removed

external low noise power supply 5V @ 200 mA might be connected to JP9 pins 2,3. See figure

below:

MOTOROLA MSC8101ADS RevB User’s Manual 31

For More Information On This Product,

Go to: www.freescale.com

Page 32

Freescale Semiconductor, Inc.

Operating Instructions

FIGURE 4-8 JP9 - 5V CODEC Source Selection

JP9 JP9

1

1

5V Internal

+5V

Factory Set

GND

External

4•3•8 JS1-5 - Current Consumption Measurement

JS1-5 reside on I/O-pins, core & PLL main flow. To measure current consumption, the corresponding JS should be removed using a solder tool and a current meter (shunt) should be connected

instead, with as shorted and thicker wires as possible.

Warning

nc...

I

4•3•9 JG1-6 GND Bridges

There are 6 GND bridges on the MSC8101-ADS, 4, designated as GND reside on digital ground

and 2, designated as AGND3 and AGND4 resides on analog ground plane. They are meant to

assist general measurements and logic-analyzer connection.

cale Semiconductor,

4•3•10 Solder Bridges

The job of removing JS1-5 and soldering current

meter connections instead is very delicate and

should be done by a skilled technician.

If this process is done by unskilled hand or repeated more than 3 times, permanent damage

might be inflicted to the MSC8101ADS.

Warning

When connecting to a GND bridge, use only INSULATED GND clips. Otherwise, un-insulated

clips may cause short- circuits, touching "HOT"

points around them. Failure in doing so, might

result in permanent damage to the

MSC8101ADS.

Frees

All the solder bridges should be shorted while additional SDRAM device has been assembled on

the ADS board (special requirement).

4•4 LEDs

The MSC8101-ADS has the following indicators:

4•4•1 Fast Ethernet Indicator - LD1

When the LXT970 is enabled and is in 100 Mbps operation mode, the yellow LED - LD1 lights.

4•4•2 Fast Ethernet RX Indicator - LD2

The green Ethernet Receive LED indicator blinks whenever the LXT970 is receiving data from one

of the 10/100-Base-T port.

4•4•3 Ethernet TX Indicator - LD3

32 MSC8101ADS RevB User’s Manual MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Page 33

Freescale Semiconductor, Inc.

The green Ethernet Receive LED indicator blinks whenever the LXT970 is transmitting data via the

10/100-Base-T port.

Operating Instructions

4•4•4 Ethernet LINK Indicator - LD4

The yellow Ethernet Twisted Pair Link Integrity LED indicator - LINK, lights to indicate good link

integrity on the 10/100-Base-T port. LD4 is off when the link integrity fails.

4•4•5 Fast Ethernet CLSN Indicator - LD5

The red Ethernet Collision LED indicator CLSN, lights whenever a collision condition is detected

on the 10/100-Base-T port, i.e., simultaneous receive and transmit. This led functions in this duty

provided that bits 7:6) of LXT970’s register 19, are cleared.

4•4•6 ATM RX Indicator - LD6

The green ATM Receive LED indicator blinks whenever the PM5350 ATM-UNI is receiving cells

via the ATM port.

4•4•7 ATM TX Indicator - LD7

The green ATM Receive LED indicator blinks whenever the PM5350 ATM-UNI is transmitting cells

via the ATM port.

nc...

I

4•4•8 TEXP Indicator - LD8

The green Timer Expired LED indicates status of Timer 4 output and lights when it’s low.

cale Semiconductor,

Frees

4•4•9 Signaling Indicator 1 - LD9

This red indication LED has no dedicated function over the ADS. It is meant to provide additional

visibility for program behavior. Its different color from LD9 provides additional information. It is controlled by BCSR0/7. When either of HRESET

well.

or Power-On-Reset is asserted the LED lights as

4•4•10 Signaling Indicator 0 - LD10

This green indication LED has no dedicated function over the ADS. It is meant to provide some

visibility for program behavior. It is controlled by BCSR0/6. When either of SRESET

Reset is asserted the LED lights as well.

or Power-On-

4•4•11 RS232 Port 2 ON - LD11

When the yellow RS232 Port 2 ON LED is lit, it designates that the RS232 transceiver connected

to P27B, is active and communication via that medium is allowed. When darkened, it designates,

that the transceiver is in shutdown mode and its associated SMC1 pins may be used off-board via

the expansion connectors.

4•4•12 RS232 Port 1 ON - LD12

When the yellow RS232 Port 1 ON LED is lit, it designates, that the RS232 transceiver connected

to P27A, is active and communication via that medium is allowed. When darkened, it designates

that the transceiver is in shutdown mode and its associated SCC1 pins may be used off-board via

the expansion connectors.

4•4•13 Fast Ethernet Port Initially Enabled - LD13

When the yellow FETH ON LED is lit, it indicates that the fast ethernet port transceiver - the

LXT970, is initially active. When it is dark, it indicates that the LXT970 is initially in power down

mode, enabling the use of its associated FCC2 pins off-board via the expansion connectors. The

state of LD13 is controlled by bit BCSR1/4.

This is a soft-indication, i.e., since the LXT970 may be controlled via the MII port, it is possible that

the state of LD13 does not reflect correctly the status of the LXT970.

MOTOROLA MSC8101ADS RevB User’s Manual 33

For More Information On This Product,

Go to: www.freescale.com

Page 34

Freescale Semiconductor, Inc.

Operating Instructions

Note

Application S/W should always seek to match

the state of LD13 to the status of the LXT970, so

that, this indication is made reliable as to the

correct status of the LXT970.

4•4•14 ATM ON - LD14

When the yellow ATM ON LED is lit, it indicates that the ATM-UNI transceiver - the PM5350, is

active and enables communication via that medium. When it is dark, the ATM-UNI transceiver is

disconnected from the MSC8101, enabling the use of its associated FCC1 pins off-board via the

expansion connectors.

ATM ON LED is controlled by BCSR1/2.

4•4•15 T1-1 TDM Port 1 Enable - LD15

When the yellow T1-1 LED is lit, it indicates that T1/E1 QFALC port 1 is connected to the CPM

TDMA1 port. When darkened, it designates that associated CPM TDMA1 lines may be used for

nc...

I

the CODEC application, in case when CODEC LED is lit. The LD15 reflects the bit BCSR0/3

T1_1EN.

cale Semiconductor,

Frees

4•4•16 T1-234 TDM Ports 2,3,4 Enable - LD16

When the yellow T1-234 LED is lit, it indicates that T1/E1 QFALC ports 2-4 are available. When

darkened, it designates that associated CPM’s TDMB2,TDMC2,TDMD2 lines may be used for the

other application, e.g. Fast Ethernet. The LD16 reflects the bit BCSR0/4 T1_234EN.

4•4•17 CODEC Enable - LD17

When the yellow CODEC LED is lit, it indicates that CODEC lines are connected to the CPM

TDMA1 port instead of T1/E1 QFALC port 1. When darkened, the CODEC device is isolated from

the bus by tri-state buffers. The LD17 reflects the bit BCSR1/1 CODEC_EN.

4•4•18 RUN Indicator - LD18

When the green RUN LED - LD18 is lit, it indicates that the MSC8101 is performing cycles on the

PPC Bus. When dark, the Processor is either running internally or stuck.

4•4•19 Host I/F Enable - LD19

When the yellow Host I/F ON LED is lit, it indicates that the Processor implementes HDI16 port.

It’s is available on the Host connector P4 and expansion connectors P1, P2. When darkened, PPC

Data Bus becomes 64-bit width with no Host I/F support.

4•4•20 1.5V Indicator - LD20

The green 1.5V LED - LD20, indicates the presence of the +1.5V supply with output voltage no

less than 0.9V.

4•4•21 3.3V Indicator - LD21

The green 3.3V LED - LD21, indicates the presence of the +3.3V supply on the ADS.

4•4•22 5V Indicator - LD22

The green 5V LED - LD22, indicates the presence of the +5V external supply on the ADS.

4•5 The MSC8101’s Registers’ Programming

The MSC8101 provides the following functions on the MSC8101ADS:

1) System functions which include:

34 MSC8101ADS RevB User’s Manual MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Page 35

Freescale Semiconductor, Inc.

• PPC Bus SDRAM Controller

• GPCM (Flash, BCSR, ATM, Ext. Tools)

• UPM (QFALC, Ext. Tools)

2) Communication functions which include:

• ATM SAR

• Fast Ethernet controller.

• TDMs for T1/E1 and CODEC support

• UART for terminal or host computer connection.

The internal registers of the MPC must be programmed after Hard reset as described in the

following paragraphs. The addresses and programming values are in Hexadecimal base.

For better understanding the of the following initialization refer to the

4•5•1 System Initialization

Hard Reset Config. Word is programmed in Flash according to TABLE 5-2. "Hard Reset Configu-

ration Word" on page 40.

nc...

I

TABLE 4-3. SIU Registers’ Programming

Operating Instructions

cale Semiconductor,

Frees

Register Init Value[hex] Description

RMR 0001 Check-Stop Reset enabled.

IMMR 14700000 Internal space begins from 0x1470_0000

SYPCR FFFFFFC3 Software watchdog timer count - FFFF, Bus-monitor timing FF, PPC Bus-monitor -

Enabled, Local Bus-monitor - Enabled, S/W watch-dog - disabled, S/W watch-dog

(if enabled) causes reset, S/W watch-dog (if enabled) - prescaled.

BCR 0000_0000 Single MSC8101, 0 wait-states on address tenure, 1-level Pipeline depth,

Extended transfer mode disabled for PCC & Local Buses, Odd parity for PPC &

Local Buses (not relevant for this application, External Master delay enabled,

Internal space responds as 64 bit slave for external master (not relevant for this

application).

4•5•1•1 Memory Controller Registers Programming

The memory controller on the MSC8101ADS is initialized to 50/100 MHz operation. I.e., registers’

programming is based on 50/100 MHz timing calculation.

MOTOROLA MSC8101ADS RevB User’s Manual 35

For More Information On This Product,

Go to: www.freescale.com

Page 36

Freescale Semiconductor, Inc.

Operating Instructions

Warning

The initialization in TABLE 4-4. "Memory Control-

ler Initialization for 100(50) MHz" below are based

on design and are not verified yet, due to silicon

availability problems.

TABLE 4-4. Memory Controller Initialization for 100(50)a MHz

nc...

I

cale Semiconductor,

Frees

Reg. Device Type Bus

BR0 SM73228XG1JHBG0 by

Smart Modular Tech.

SM73248XG2JHBG0 by

Smart Modular Tech.

SM73288XG4JHBG0 by

Smart Modular Tech.

OR0 SM73228XG1JHBG0 by

Smart Modular Tech.

SM73248XG2JHBG0 by

Smart Modular Tech.

SM73288XG4JHBG0 by

Smart Modular Tech.

BR1

BCSR0-3

OR1 FFFF8010

BR2 SDRAM 64bit Supported Non-buffered

OR2 MT48LC2M32B2T6-8x2

by Micron

b

BR2

OR2

BR3

OR3

SDRAM 32bit Supported Non-buffered

b

MT48LC2M32B2T6-8 by

Micron

c

SDRAM 32bit Supported Non-buffered

c

MT48LC2M32B2T6-8 by

Micron

Buffered

PPC

Buffered

PPC

PPC

PPC with

Host support

PPC with

Host support

Init Value

[hex]

FF801801 Base at FF800000, 32 bit port size, no parity,

FF001801 Base at FF00000, 32 bit port size, no parity,

FE001801 Base at FE00000, 32 bit port size, no parity,

FF800866

(FF800836)

FF000866

(FF000836)

FE000866

(FE000836)

14501801 Base at 14500000, 32 bit port size, no parity,

(FFFF8020)

20000041 Base at 20000000, 64 bit port size, no parity,

FF003080 16MByte block size, 4 banks per device, row starts

20001841 Base at 20000000, 32 bit port size, no parity,

FF803280 8MByte block size, 4 banks per device, row starts

20801841 Base at 20800000, 32 bit port size, no parity,

FF803280 8MByte block size, 4 banks per device, row starts

Description

GPCM

GPCM

GPCM

8MByte block size, CS early negate, 12(6) w.s.,

Timing relax

16MByte block size, CS early negate, 12(6) w.s.,

Timing relax

32MByte block size, CS early negate, 12(6) w.s.,

Timing relax

GPCM

32 KByte block size, all types access, 1 w.s.

(32 KByte block size, all types access, 2 w.s.)

SDRAM machine 1

at A8, 11 row lines, internal bank interleaving

allowed

SDRAM machine 1

at A9, 11 row lines, internal bank interleaving

allowed

SDRAM machine 1

at A9, 11 row lines, internal bank interleaving

allowed

BR4 QFALC - 4ch. T1/E1 Buffered

PPC

OR4 FFFF8106 32K Byte block size, burst inhibit, eight idle cycle

36 MSC8101ADS RevB User’s Manual MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

146088A1 Base at 14608000, 8 bit port size, no parity, UPMB

on PPC bus

are inserted before next access

Page 37

Freescale Semiconductor, Inc.

Operating Instructions

TABLE 4-4. Memory Controller Initialization for 100(50)a MHz

nc...

I

cale Semiconductor,

Frees

Reg. Device Type Bus

BR5 PM5350 - ATM UNI Buffered

PPC

OR5 FFFF8E36 32K Byte block size, delayed CS assertion, early

BR6 User’s peripheral Buffered

OR6 - -

BR7 User’s peripheral Buffered

OR7 - -

BR10 DSPRAM Local PPC 020000C1 Base at 200000, 64 bit port size, no parity,UPMC

OR10 FFF80000 512K Byte block size

BR11 DSP Peripherals Local PPC 01F00021 Base at 1F00000, 64 bit port size, no parity, GPCM

OR11 FFFF0000 64K Byte block size

PSDMR SDRAM 64bit Non-buffered

SDRAM 32bit Non-buffered

PSRT SDRAM Supported

PPC

PPC

PPC

PPC with

Host support

All PPC Bus

Config.

Init Value

[hex]

14600801 Base at 14600000, 8 bit port size, no parity, GPCM

on PPC bus.

CS and WE negation for write cycle, relaxed

timing, 7 w.s. for read, 8 for write, extended hold

time after read.

--

--

on local PPC bus.

C26B36A3

(C2692452)

C28737A3

(C2432552)

22 Generates refresh every 14 µsec, while 15.6 µsec

Page interleaving, Refresh enabled, normal

operation, address muxing mode SDAM=2, A(15-

17) on BNKSEL(0:2), A8 on PSDA10, 8(4) clocks

refresh recovery, 3(2) clocks precharge to activate

delay, 3(2) clocks activate to read/write delay, 4

beat burst length, 2(1) clock last data out to

precharge, 2(1) clock write recovery time, Internal

address muxing, normal timing, 3(2) clocks CAS

latency.

Page interleaving, Refresh enabled, normal

operation, address muxing mode 1, A(13-15) on

BNKSEL(0:2), A9 on PSDA10, 8(4) clocks refresh

recovery, 3(2) clocks precharge to activate delay,

3(2) clocks activate to read/write delay, 8 beat

burst length, 2(1) clock last data out to precharge,

2(1) clock write recovery time, Internal address

muxing, normal timing, 3(2) clocks CAS latency.

required. Therefore is refresh redundancy of 6.6

msec throughout full SDRAM refresh cycle which

completes in 64 msec. I.e., Application s/w may

withhold the bus upto app. 6.6 msec in a 57.3

msec period, without jeopardizing the contents of

the PPC bus SDRAM.

Description

MPTPR SDRAM Supported 2800(1300) Divide Bus clock by 40D (20D)

MOTOROLA MSC8101ADS RevB User’s Manual 37

For More Information On This Product,

Go to: www.freescale.com

Page 38

Freescale Semiconductor, Inc.

Operating Instructions

TABLE 4-4. Memory Controller Initialization for 100(50)a MHz

Reg. Device Type Bus

MBMR QFALC - 4ch. T1/E1

Read Access

Write Access 10015418 60x bus select, refresh disable, write to UPM

Exception Access 1001543c RAM address begins at 0x3c.

Normal Operation 00015400 Execute at 0x0.

a. Table values in parentheses reflect the lower frequency bus.

b. With Host Enable.

c. If additional SDRAM device U38SP will be assembled on the ADS (special requirement).

nc...

I

Buffered

PPC

cale Semiconductor,

Init Value

[hex]

10015400 60x bus select, refresh disable, write to UPM

RAM, Read loop execute 5 times, first RAM

address.

RAM, Write loop execute 5 times, RAM address

begins at 18H.

Description

Frees

38 MSC8101ADS RevB User’s Manual MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Page 39

Freescale Semiconductor, Inc.

Functional Description

5 - Functional Description

In this chapter the ADS block diagram is described in detail.

5•1 Reset & Reset - Configuration

There are available reset sources on the MSC8101ADS:

1) Power-On-Reset and manual

2) Manual Hard-Reset

3) Manual Soft-Reset

4) JTAG/ONCE - Reset

5) MSC8101 internal Resets. See [4].

5•1•1 Power- On Reset

The power on reset to the MSC8101ADS initializes the processor state after power up. A dedicated

logic, using Seiko S-80808AN, which is a voltage detector of 1.0V +/- 2.0% keeps nominal core

nc...

I

power supplying. Its open-drain output scheme allows off-board RESET sources e.g. pulse generator. PORESET

period is long enough to cover also the Core and I/O supply stabilization, powered by a different

voltage regulator. Power-On-Reset may be generated manually as well by a dedicated pushbutton.

is asserted to the MSC8101ADS for a period of ~300 msec and keeps.This time

cale Semiconductor,

Frees

5•1•1•1 Power - On Reset Configuration

At the end of Power - On reset sequence, MODCK(1:3) are sampled by the MSC8101 and together

with two additional clock configuration bits and set the various clock modes of the MSC8101

system (dsp core, cpm, 60x bus). Selection between the MODCK(1:3) combination options is done

by means of DIP-switches. See TABLE 4-1. "Available Clock Mode Setting" on page 29.

Following Power-on reset sequence is the hard-reset sequence, within which, many other different

options are configured (see TABLE 5-2. "Hard Reset Configuration Word" on page 40). MODCKs

bits are sampled at hard-reset configuration, whenever hard-reset sequence is entered, they are

influential only once - after power-on reset. If a hard reset sequence is entered later on, these bits

although sampled, are don’t care.

5•1•2 Manual Hard Reset

To allow run-time Hard-reset, when the Command Converter is disconnected from the

MSC8101ADS and to support resident debuggers, manual Hard is facilitated. Depressing both

Soft-Reset and ABORT buttons asserts the HRESET

RESET sequence.

Since the HRESET

MSC8101 with an open-drain gate. If off-board H/W connected to the MSC8101ADS is to drive

HRESET

When Hard Reset is generated, the MSC8101 is reset in a destructive manner, i.e., the hard reset

configuration is re-sampled and all registers (except for the PLL’s) are reset, including memory

controller registers - reset of which results in a loss of dynamic memory contents.

To save on board’s real-estate, this button is not a dedicated one, but is shared with the Soft-Reset

button and the ABORT button - when both are depressed, Hard Reset is generated. The Soft

Reset is action achieved by using one dedicated button and provides DSP core reset only as well

as JTAG reset without sampling reset configuration word.

line, then it should do so with an open-drain gate, this, to avoid contention over this line.

line may be driven internally by the MSC8101, it must be driven to the

pin of the MSC8101, generating a HARD

5•1•3 Hard Reset Configuration

When Hard-Reset is applied to the MSC8101ADS (externally as well as internally), it samples the

MOTOROLA MSC8101ADS RevB User’s Manual 39

For More Information On This Product,

Go to: www.freescale.com

Page 40

Freescale Semiconductor, Inc.

Hard-Reset configuration word. This configuration may be taken from an internal default, in case

RSTCONF

data bus) or Altera device

Hardware Reset Configuration in different of Host Reset Configuration that available while HPEHost Port Enable input of the MSC8101 is sampled high at the rising edge of PORESET

Port is enabled and a Configuration Word is got from Host I/F. The default configuration word can

be taken from the Flash or from the Altera device in case the Flash has been tampered with. The

selection between the Flash and the Altera device as the source of the default configuration word

is determined by a dedicated jumper.

During hard reset sequence while Host Port Disable (HPE is low) the configuration master reads

the Flash (or Altera device) memory at addresses 0, 8, 0x18, 0x20,... a byte each time, to assemble

the 32 bit configuration word. If the HPE pin and RSTCONF

enable by Slave Configuration Reset mode. The Host device which must not be MSC8101 write

two 16-bit words to program 32-bit Reset Conf. Word. See a table below including the several boot

mode.

is negated during HRESET asserted or taken from the Flash memory (MS 8 bits of the

A

Functional Description

in case RSTCONF signal is asserted along with HRESET. Its meant

the Host

are sampled high the Host Port is

TABLE 5-1 Summary Reset Configuration Schemes.

nc...

I

cale Semiconductor,

Frees

Signal/

Config. Mode

MASTER 0 0 0 - Debug Mode

HOST 1 1

For Debug and Boot Mode setting will be used separate DIP switch array. EEs and EED pins are

controlled from another DIP switch and may be read out from status register of the BCSR3.

The following table describes The Hard Reset Config. Word field values:

RSTCONF

HPE/EE1 EE0/DBG

Enable

1- Debug Mode

Disable

EE[4-5]/BTM[1-0]

Boot Mode

00-From ext. memory

01-From HOST

10-From EEPROM

11- Reserved

TABLE 5-2. Hard Reset Configuration Word

Data

Field

EARB 0 ’0’ Internal Arbitration Selected. 0 2C

EXMC 1 ’0’ Internal Memory Controller. CS0

IRQ7INT

EBM 3 ’0’ Single Quartz001 bus mode is assumed

Bus

Bits

2’1’INT_OUT function is active

Prog

Val ue

[Bin]

system boot.

Implication

active at

Offset In

Flash

[Hex]

Value

[Hex]

BPS 4:5 ’11’ 32 Bit Boot Port Size for both Flash memory

and BCSR

SCDIS 6 ’0’ SC140 enabled

ISPS 7 ‘0’ Internal space port size for ext. master access

is 64 bit. Don’t care since this feature is not

supported for the current board configuration.

A. In general, from any device residing on CS0.

40 MSC8101ADS RevB User’s Manual MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Page 41

Freescale Semiconductor, Inc.

Functional Description

TABLE 5-2. Hard Reset Configuration Word

Data

Field

IRPC 8:9 ’00’ Interrupt pin configuration. NC/BADDR(29)/

DPPC 10:11 ‘00’ Data Parity Pin configuration as IRQ

NMIOUT 12 ’0’ NMI interrupt is serviced by the core.

ISB 13:15 ’000’ IMMR initial value 0x0, i.e., the internal space

BMS 16 ’0’ Non-functional cleared bit. 10 02

BBD 17 ’0’ Bus busy pins set: ABB

nc...

I

cale Semiconductor,

Reserved 18:21 ‘0000’ Must be cleared

TCPC 22:23 ’10’ Transfer code pins are configured following

BC1PC 24:25 ’00’ Buffer control 1-pin configuration BCTL1/

Reserved 26 ’0’ Reserved. Should be cleared.

DLLDIS

MODCK_HI 28:30 ‘111’ High-order bits of the MODCK array i.e.

Reserved 31 ’0’ Reserved. Should be cleared.

a

a. Applies only ONCE after power-up reset.

When HCW is applied from Flash (SW9/7 is ON) DLLDIS and MODCK_HI bits have value shown in table. In case of HCW source will be from BCSR (SW9/7 is OFF) those bits set up manually - DLLDIS is

controlled by JP1 and MODCK_HI - by DIP-switch SW9/4-6.

Bus

Bits

27 ’1’ No DLL bypass when value is zero. Controlled

Prog

Val ue

[Bin]

Implication

IRQ2,NC/BADDR(30)/IRQ3,NC/BADDR(31)/

are selected as NC (not connect)

IRQ5

[1:7].

resides initially at address 0xF0000000

/IRQ2 pin is ABB

DBB/IRQ3 pin is DBB

way after PONRESET

MODCK1/BNKSEL(0)/TC(0) as BKSEL0

MODCK2/BNKSEL(1)/TC(1) as BKSEL1

MODCK3/BNKSEL(2)/TC(2) as BKSEL2

DBG_DIS~ functions as BCTL1

with jumper JP1

MODCK[4-6]. Set Clock Mode 57. See [4].

:

Offset In

Flash

[Hex]

800

18 1E

Value

[Hex]

Frees

5•1•4 Manual Soft Reset

To allow run-time Soft-reset, when the Command Converter is disconnected from the JTAG/ONCE

connector and to support resident debuggers, a Soft Reset push-button is provided. When the Soft

Reset push-button is depressed, the SRESET

Reset sequence.

Since the SRESET

drain gate, to avoid contention over that line. If off-board H/W connected to the MSC8101ADS is

to drive SRESET

this line.

MOTOROLA MSC8101ADS RevB User’s Manual 41

line may be driven internally by the MSC8101, it must be driven by an open-

line, then, it should do so with an open-drain gate, this, to avoid contention over

For More Information On This Product,

Go to: www.freescale.com

line is asserted to the MSC8101, generating a Soft

Page 42

nc...

I

cale Semiconductor,

Frees

Freescale Semiconductor, Inc.

5•1•5 MSC8101 Internal Hard Reset Sources

The MSC8101 has internal sources which generate Hard / Soft Resets. Among these sources are:

1) Loss of Lock Reset (Hard)

2) S/W Watch Dog Reset (Hard)

3) Bus Monitor (Hard)

4) JTAG/ONCE Reset (Hard)

In general, the MSC8101 asserts a reset line HARD or SOFT for a period 512 clock cycles after

the reset source has been identified. A hard reset sequence is followed by a soft reset sequence

that released three bus clocks later than hard reset is negated.

Functional Description

5•2 Local Interrupter

There are external interrupts which are applied to the MSC8101ADS via its interrupt controller:

1) ABORT (NMI)

2) ATM UNI interrupt

5•2•1 ABORT Interrupt

The ABORT (NMI), is generated by a push-button. When this button is depressed, the IRQ0 input

to the MSC8101 is asserted. The purpose of this type of interrupt, is to support the use of resident

debugger if any is made available to the MSC8101ADS. To support external (off-board) generation

of an NMI, the IRQ0

drive this line. If an external h/w indeed does so, it is compulsory that IRQ0

drain (or open-collector) gate.

5•2•2 ATM UNI Interrupt

To support ATM UNI (User Network I/F) event report by means of interrupt, the interrupt output of

the UNI (INTB) is connected to IRQ6

Since INTB of the UNI is an open-drain output, it is possible to connect additional (off-board) interrupt requesters on the same IRQ6

5•2•3 QFALC Interrupt

Interrupt of T1/E1 Frame are served by IRQ7. The QFALC has an open-drain output, therefore it

is possible to connect additional (off-board) interrupt requesters on the IRQ7

as IRQ6

.

line, is driven by an open-drain gate. This allows for an external h/w, to also

is driven by an open-

line of the MSC8101.

, provided that they drive IRQ6 with open-drain gate as well.

line, the same way

5•3 Clock Generator

The MSC8101 requires a single clock source for the main clock oscillator. Use is done with 25MHz

(16.38MHz) 3.3V clock generator mounted on the 14-pin DIP socket for simpler changing. Also

clock may be provided from external clock generator (reference) via SMB-connector. All MSC8101

PPC bus timings are referenced to the clock output of the DSP. The CLKOUT is connected to a

low inter-skew buffer to split the load between all various clock consumers on the board. One of

the channel intends for the MSC8101 DLL input to eliminate buffer and path propagation delay.

Special care is taken to isolate and terminate the clock route between the on-board devices and

the MSC8101, this to provide a "clean" clock for proper operation. The main clock scheme is

shown in figure below:

42 MSC8101ADS RevB User’s Manual MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Page 43

Freescale Semiconductor, Inc.

Functional Description

FIGURE 5-1 Clock Distribution Scheme

CY2309

MSC8101

CLOCK OSC.

55MHz/

20MHz

The Zero Delay Buffer CY2309 distributes high speed clock with skew less 250ps when internal

PLL is ON. Select inputs S1,S2 allow to the input clock be directly applied to the output with propogation delay of regular clock buffer about 5ns. See available working modes in TABLE 4-2. "JP1/

JP2 Settings".

nc...

I

CLKIN

DLL_IN

CLKOUT

JP2

VCC

VCC/

GND

S2

S1

Zero

Delay

Buffer

U44

A1

A2

B1

B2

B3

A4

SDRAM1

SDRAM2

BCSR

MICTOR

EXPANSION

5•4 Bus Buffering

In order to achieve best performance, it is necessary to reduce the capacitive load over the PPC

bus as much as possible. Therefore, the slower devices on the bus, i.e., the Flash SIMM, ATM UNI

M/P interface, BCSR and the external tool bus are buffered, while the SDRAM devices are not

buffered from the bus.

Buffers are provided over address and strobe (when necessary) lines while transceivers are

provided for data. Use is done with 74ALVT buffers (by Philips) which are 3.3V operated and 5V

tolerant

MSC8101). This type of buffers reduces noise on board due to reduced transition’s amplitude.

To further reduce noise and reflections, serial damping resistors may be added are placed over

SDRAM address and all MSC8101 strobe lines.

The data transceivers are open only if there is an access to a valid

during Hard - Reset configuration

cale Semiconductor,

memory read or off-board memory is read - provided that it is not mapped to an address valid on

board. It is the users’ responsibility to avoid such errors.

A

and provide bus hold to reduce pull-up/pull-down resistors count (as required by the

B

C

. That way data conflicts are avoided in case an unbuffered

buffered board address or

5•5 Chip - Select Generator

Frees

The memory controller of the MSC8101 is used as a chip-select generator to access on-board (and

off-board) memories, saving board’s area, reducing cost, power consumption and increasing flexibility. To enhance off-board application development, memory modules (including the BCSRx)

may be disabled via BCSR

tors. That way, a CS line may be used off-board via the expansion connectors, while its associated

local memory is disabled.

When a CS region, assigned to a buffered

A. Required for Flash SIMM and BCSR

B. An address which is covered in a Chip-Select region, that controls a buffered device by BCSR logic.

C. To allow a configuration word stored in the Flash memory or BCSR to become active.

D. After the BCSR is removed from the local memory map, there is no way to access it but to re-apply

power to the MSC8101ADS.

MOTOROLA MSC8101ADS RevB User’s Manual 43

D

in favor of an external memory connected via the expansion connec-

E

memory, is disabled via BCSR, the local data trans-

For More Information On This Product,

Go to: www.freescale.com

Page 44

Freescale Semiconductor, Inc.

ceivers are disabled during access to that region, avoiding possible

The MSC8101 chip-selects assignment to the various memories / registers on the MSC8101ADS

are shown in TABLE 5-3.

Functional Description

A

contention over data lines.

TABLE 5-3. MSC8101ADS Chip Select Assignments

nc...

I

cale Semiconductor,

Frees

Chip

Select

CS0 Flash SIMM /BCSR Config Word PPC (Buffered) GPCM

CS1

CS2

CS3

CS4

CS5

CS6

CS7

CS10 DPSRAM Internal Local PPC UPMC

CS

11 DSP Peripherals Internal Local PPC GPCM

a. User defined.

SDRAM(soldered on the board) PPC (Unbuffered) SDRAM Machine 1

SDRAM spare (soldered on the

Communication Tool M/P Interface

Communication Tool M/P Interface

Assignment Bus

BCSR PPC (Buffered) GPCM

PPC (Unbuffered) SDRAM Machine 1

board)

QFALC T1/E1 PPC (Buffered) UPMB

ATM UNI Microprocessor I/F PPC (Buffered) GPCM

PPC (Buffered)

CS1

PPC (Buffered)

CS2

Timing

Machine

GPCM/UPMA

GPCM/UPMA

a

a

5•6 Synchronous DRAM Bank

To enhance MSC8101ADS performance, 16MBytes of SDRAM is provided on the Unbuffered

PPC Bus for storage and fast data exchange. The SDRAM is configured as 2 X 2Meg X 32. Use

is done with two MT48LC2M32B2 chips by Micron or compatibles (Samsung). The part data sheet

may be obtained on the Internet at URL: http://www.micron.com/mti/msp/htm/datasheet.html.

Since it includes only 2 memory chips, the SDRAM is unbuffered from the MSC8101, avoiding the

delay associated with address and data buffers. As the volume of this sdram is far beyond any