Page 1

After Sales Technical Documentation

NHE–5 Series Transceiver

Chapter 4

SYSTEM MODULE GT8

Original 02/97

Page 2

NHE–5

After Sales

System Module GT8

CHAPTER 4 – SYSTEM MODULE

Contents

Introduction Page 4–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

External and Internal Connections Page 4–4. . . . . . . . . . . . . . . . . . . . . . . .

System Connector X103 Page 4–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

UI Connector X101 Page 4–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Flash Connector X103 Page 4–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

SIM Connector X102 Page 4–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Baseband Block Page 4–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Introduction Page 4–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Modes of Operation Page 4–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Circuit Description Page 4–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Power Supply Page 4–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

MCU Page 4–17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

MCU Flash Loading Page 4–18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Flash Prommer Connection Using Dummy Battery Page 4–21. . . . . .

Flash, D400 Page 4–21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

SRAM D402, D403 Page 4–21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

MCU and Peripherals Page 4–22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Baseband A/D Converter Channels usage in N450 and D150 Page 4–22

Keyboard Interface Page 4–26. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Keyboard and Display Light Page 4–27. . . . . . . . . . . . . . . . . . . . . . . . .

Audio Control Page 4–27. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Internal Audio Page 4–28. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

External Audio Page 4–29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

DSP Page 4–30. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

RFI2, N450 Operation Page 4–33. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

SIM Interface Page 4–36. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

BART ASIC Page 4–37. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

RF Block Page 4–39. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Technical Documentation

Introduction Page 4–39. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Receiver Page 4–39. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Duplex Filter Page 4–39. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Pre–Amplifier Page 4–40. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

RF Interstage Filter Page 4–40. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

First Mixer Page 4–41. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

First IF Amplifier Page 4–41. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

First IF Filter Page 4–41. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Receiver IF Circuit, RX part of CRFRT Page 4–42. . . . . . . . . . . . . . . .

Last IF Filter Page 4–42. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Transmitter Page 4–42. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Modulator Circuit, TX part of CRFRT Page 4–43. . . . . . . . . . . . . . . . . .

Page 4–2

Original 02/97

Page 3

After Sales

NHE–5

Technical Documentation

Up–conversion Mixer Page 4–44. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

TX Interstage Filters Page 4–44. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1st TX Buffer Page 4–45. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2nd TX Buffer Page 4–45. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Power Amplifier Page 4–45. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Power Control Circuitry Page 4–46. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Frequency Synthesizers Page 4–47. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Reference Oscillator Page 4–47. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

VHF PLL Page 4–48. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

VHF VCO + Buffer Page 4–48. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

UHF PLL Page 4–49. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

UHF VCO + Buffer Page 4–49. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

UHF VCO Buffers Page 4–49. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

PLL Circuit Page 4–50. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

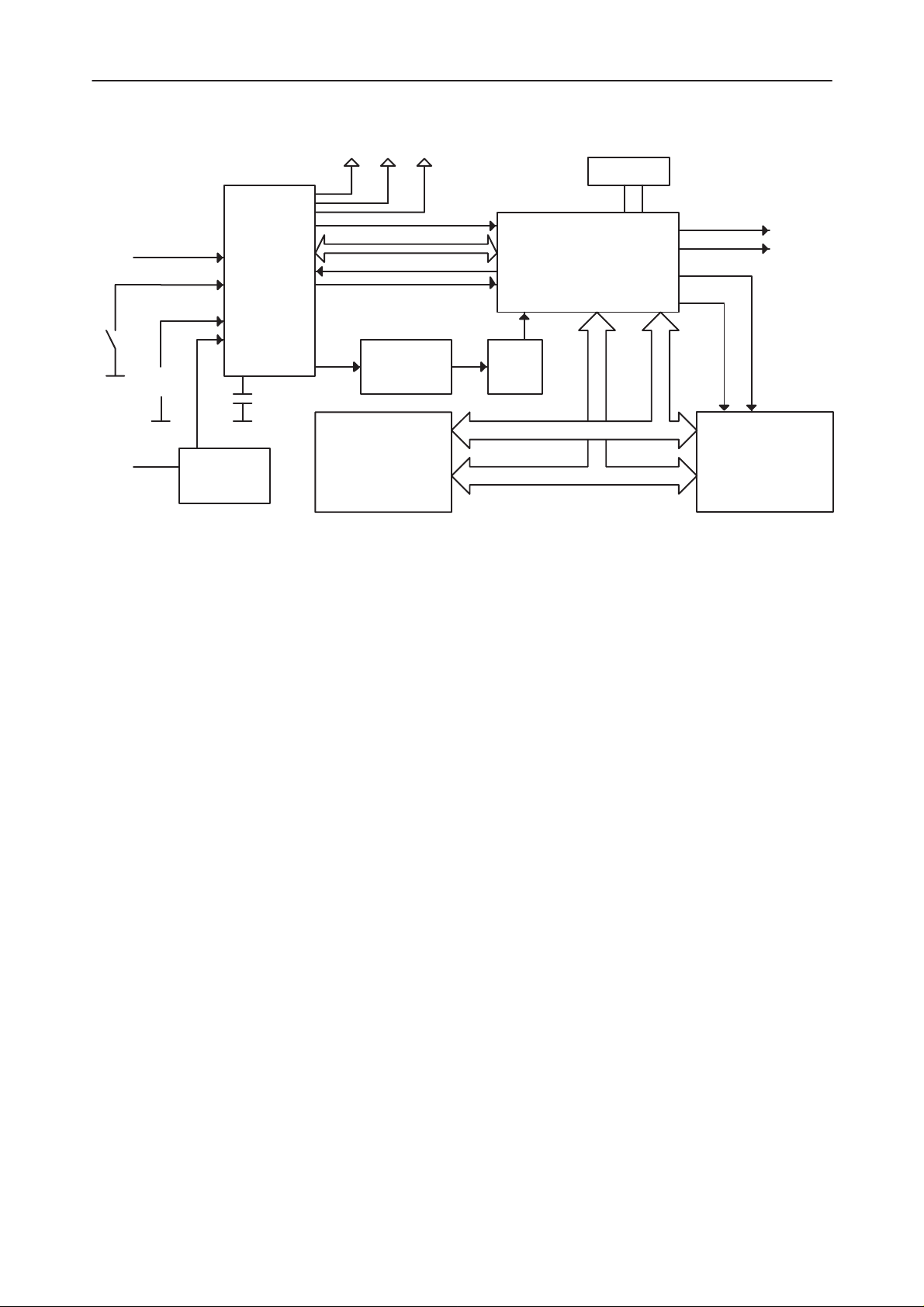

Interconnection Diagram of Baseband Page 4–51. . . . . . . . . . . . . . . . . . . . .

Block Diagram of RF Page 4–52. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

RF Frequency Plan Page 4–53. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Power Distribution Diagram of RF Page 4–54. . . . . . . . . . . . . . . . . . . . . . . . .

Circuit Diagram of 4 MBit Flash Memory (Version 5.0/5.4 ; Edit 44) Page 4–55

Circuit Diagram of Baseband (Version 5.0 ; Edit 155) Page 4–56

Circuit Diagram of Power Supply and Charging (V. 5.0 ; Edit 207) Page 4–57

Circuit Diagram of Charger Control (Version 5.0 ; Edit 41) Page 4–58

Circuit Diagram of Central Processing Unit (Version 5.0 ; Edit 172) Page 4–59

Circuit Diagram of MCU Memory Block (Version 5.0 ; Edit 110) Page 4–60

Circuit Diagram of Keyboard Display Interface (Version 5.0 ; Edit 85) Page 4–61

Circuit Diagram of Audio (Version 5.0 ; Edit 136) Page 4–62

Circuit Diagram of DSP Memory Block (Version 5.0 ; Edit 68) Page 4–63

Circuit Diagram of RFI (Version 5.0 ; Edit 90) Page 4–64

Circuit Diagram of Receiver (Version 5.0 ; Edit 209) Page 4–65

Circuit Diagram of Transceiver (Version 5.0 ; Edit 249) Page 4–66

Layout Diagrams of GT8 (Version: 30) Page 4–67

Circuit Diagram of Baseband (Version 5.4 ; Edit 167) Page 4–69

Circuit Diagram of Power Supply and Charging (V. 5.4 ; Edit 214) Page 4–70

Circuit Diagram of Charger Control (Version 5.4 ; Edit 47) Page 4–71

Circuit Diagram of Central Processing Unit (Version 5.4 ; Edit 180) Page 4–72

Circuit Diagram of MCU Memory Block (Version 5.4 ; Edit 116) Page 4–73

Circuit Diagram of Keyboard Display Interface (Version 5.4 ; Edit 92) Page 4–74

Circuit Diagram of Audio (Version 5.4 ; Edit 144) Page 4–75

Circuit Diagram of DSP Memory Block (Version 5.4 ; Edit 2) Page 4–76

Circuit Diagram of RFI (Version 5.4 ; Edit 99) Page 4–77

Circuit Diagram of Receiver (Version 5.4 ; Edit 209) Page 4–78

Circuit Diagram of Transceiver (Version 5.4 ; Edit 251) Page 4–79

Layout Diagrams of GT8 (Version: 34) Page 4–80

Parts list of GT8 (EDMS Issue 5.4) for layout version 30 Page 4–81

Parts list of GT8 (EDMS Issue 6.2) for layout version 34 Page 4–94

System Module GT8

Original 02/97

Page 4–3

Page 4

NHE–5

After Sales

System Module GT8

Introduction

GT8 is the baseband/RF module NHE–5 cellular transceiver. The GT8 module

carries out all the system and RF functions of the transceiver. System module

GT8 is designed for a handportable phone, that operate in GSM system.

Technical Section

All functional blocks of the system module are mounted on a single multi layer

printed circuit board. The chassis of the radio unit has separating walls for

baseband and RF. All components of the baseband section are surface mountable. They are soldered using reflow. The connections to accessories are taken

through the bottom connector of the radio unit. The connections to the User Interface module (UIF) are fed through a connector. There is no physical connector between the RF and baseband sections.

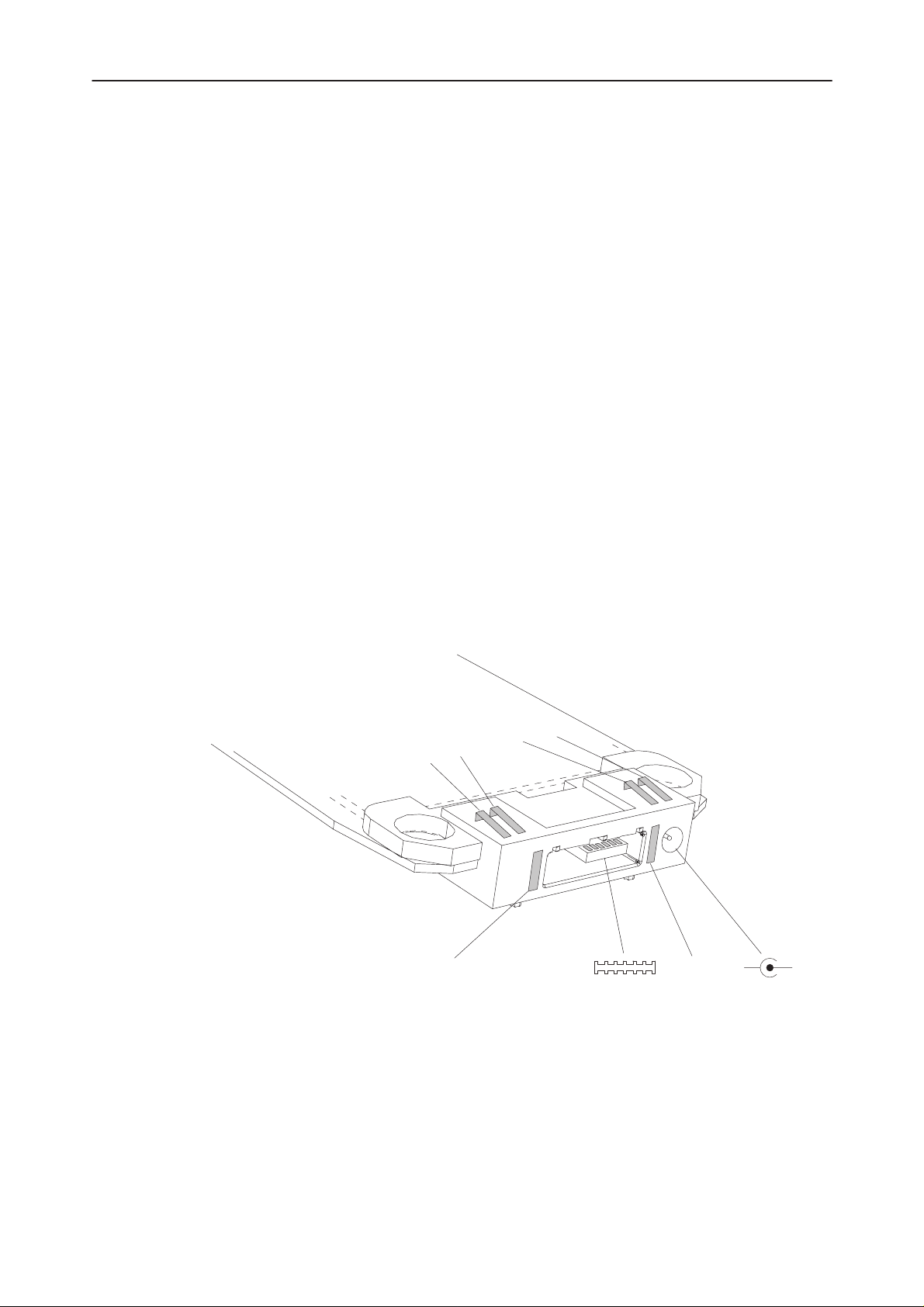

External and Internal Connections

The system module has two connector, external bottom connector and internal

display module connector.

Technical Documentation

System Connector X103

S0001130

13

18

15

14

16

7

12

16

17 20

19

Page 4–4

Original 02/97

Page 5

After Sales

NHE–5

Technical Documentation

Accessory Connector

Pin: Name: Description:

1 GND Digital ground

2 V_OUT Accessory output supply

3 XMIC External microphone input and accessory

ID Accessory identification

4 NC No connection

System Module GT8

• min/typ/max: 3.25...10 V

(output current 50 mA)

identification

• nom/max: 8...50 mV (the maximum value

corresponds to 0 dBm network level with input

amplifier gain set to 20 dB, typical value is

maximum value –16 dB)

• 1.7...2.05 V headset adapter connected

• 1.15...1.4 V compact handsfree unit connected

5 NC No connection

6 MBUS Serial control bus

• logic low level: 0...0.5 V

• logic high level: 2.4...3.2 V

7 NC No connection

8 SGND Signal ground

9 XEAR External audio output and mute control

• min/nom/max: 0...32...500 mV (typical level

corresponds to –16 dBm0 network level with

volume control in nominal position 8 dB below

maximum. Maximum 0 dBm0 max. volume

codec gain –6 dB)

• mute on (HF speaker mute): 0...0.5 V d.c.

• mute off (HF speaker active): 1.0...1.7 V d.c.

10 HOOK Hook control, accessory connection detect

• hook off (handset in use) : 0...0.5 V

• hook on, (handset not in use): 2.4...3.2 V

11 NC No connection

12 V_IN Charging supply voltage

• max: 16 V

Original 02/97

Page 4–5

Page 6

NHE–5

After Sales

System Module GT8

Battery Connector

Pin: Name: Description:

13 BGND Battery ground

14 BSI Battery size indicator

15 BTEMP Battery temperature

16 VB Battery voltage

Charging connectors

Pin: Name: Description:

17, 19 V_IN Charging voltage input

Technical Documentation

(used also for SIM card detection)

• R2=47k pull–up resistor in

(used also for vibration alert)

• 47 kΩ NTC in battery to gnd,

47 kΩ pull–up in module

• min/typ/max: 5.3...6...8.6 V

• ACH–6 min/nom/max: 9.8...10.3...10.8 V

• ACH–8 min/nom/max: 12...14...16 V

module

18, 20 GND Charger ground

UI Connector X101

Pin: Name: Description:

1 EARP Earphone positive signal

2 EARN Earphone negative signal

3 VBKEY Battery supply

4 BUZZER Alert buzzer (audio codec PWM controlled)

5–7 ROW(0–2) Input

8–10 GND Shield ground

• min/typ/max: 0...14...220 mV (typical level

corresponds to –16 dBm0 network level with

volume control giving nominal RLR (=+2 dB)

8 dB below maximum. Maximum 0 dBm0

with max. volume (codec gain –11 dB)

• min/typ/max: 0...14...220 mV (see above)

• min/max: 5.3...8.5 V

Page 4–6

11–13 ROW(3–5) Input

Original 02/97

Page 7

After Sales

NHE–5

Technical Documentation

Pin: Name: Description:

14 LIGHTC Keyboard light

15–18 COL(0–3) Output

19 PWRKEY Power on/off

20 GND Digital ground

Flash Connector X103

Pin: Name: Description:

1 WDDIS Watchdog disable, signal pulled down to

2 FCLK Flash serial clock, test point J303

3 VPP Flash programming voltage

System Module GT8

disable watchdog, test point J300

• min/typ/max: 11.4...12...12.6 V

(values when VPP active), test point J304

4 FTX Flash acknowledge transmit, test point J302

5 FRX Flash data receive, test point J301

SIM Connector X102

Pin: Name: Description:

1 GND Ground for SIM

2 VSIM SIM voltage supply

3 SDATA Serial data for SIM

4 SRES Reset for SIM

5 CLK Clock for SIM data (clock frequency minimum

• min/typ/max: 4.8...4.9...5.0 V

1 MHz if clock stopping not allowed)

Original 02/97

Page 4–7

Page 8

NHE–5

After Sales

System Module GT8

Baseband Block

Introduction

The GT8 module is used in NHE–5 products. The baseband is built around one

DSP, System ASIC and the MCU. The DSP performs all speech and GSM/PCN

related signal processing tasks. The baseband power supply is 3V except for

the A/D and D/A converters that are the interface to the RF section. The A/D

converters used for battery monitoring are integrated into the same device as

the signal processing converters.

The audio codec is a separate device which is connected to both the DSP and

the MCU. The audio codec support the internal and external microphone/earpiece functions. External audio is connected in a dual ended fashion to improve

audio quality together with accessories.

The baseband implementation support a 32 kHz sleep clock function for power

saving. The 32 kHz clock is used for timing purposes during inactive periods

between paging blocks. This arrangement allows the reference clock, derived

from RF to be switched off.

Technical Documentation

The baseband clock reference is derived from the RF section and the reference

frequency is 13 MHz. a low level sinusoidal wave form is fed to the ASIC which

acts as the clock distribution circuit. The DSP is running at 39 MHz using an internal PLL. The clock frequency supplied to the DSP is 13 MHz. The MCU bus

frequency is the same as the input frequency. The system ASIC provides both

13 MHz and 6.5 MHz as alternative frequencies. The MCU clock frequency is

programmable by the MCU. The baseband uses 6.5 MHz as the MCU operating frequency. The RF A/D, D/A converters are operated using the 13 MHz

clock supplied from the system ASIC

The power supply and charging section supplies several types of battery

technologies. such as , NiCd, NiMH and Lithium. The battery charging unit is

designed to accept constant current type chargers, that are approved by NMP.

The power supply IC contains three different regulators. The output voltage

from each regulator is 3.15V nominal. One of the regulator uses an external

transistor as the boost transistor.

Page 4–8

Original 02/97

Page 9

After Sales

NHE–5

Technical Documentation

Modes of Operation

The baseband in operates in the following Modes

– Active, as during a call or when baseband circuitry is operating

– Sleep, in this mode the clock to the baseband is stopped and timing is kept

by the 32 KHz oscillator. All Baseband circuits are powered

– Acting dead, in this mode the battery is charged but only necessary func-

tions for charging are running

– Power off, in this mode all baseband circuits are powered off. The regulator

IC N301 is powered

Circuit Description

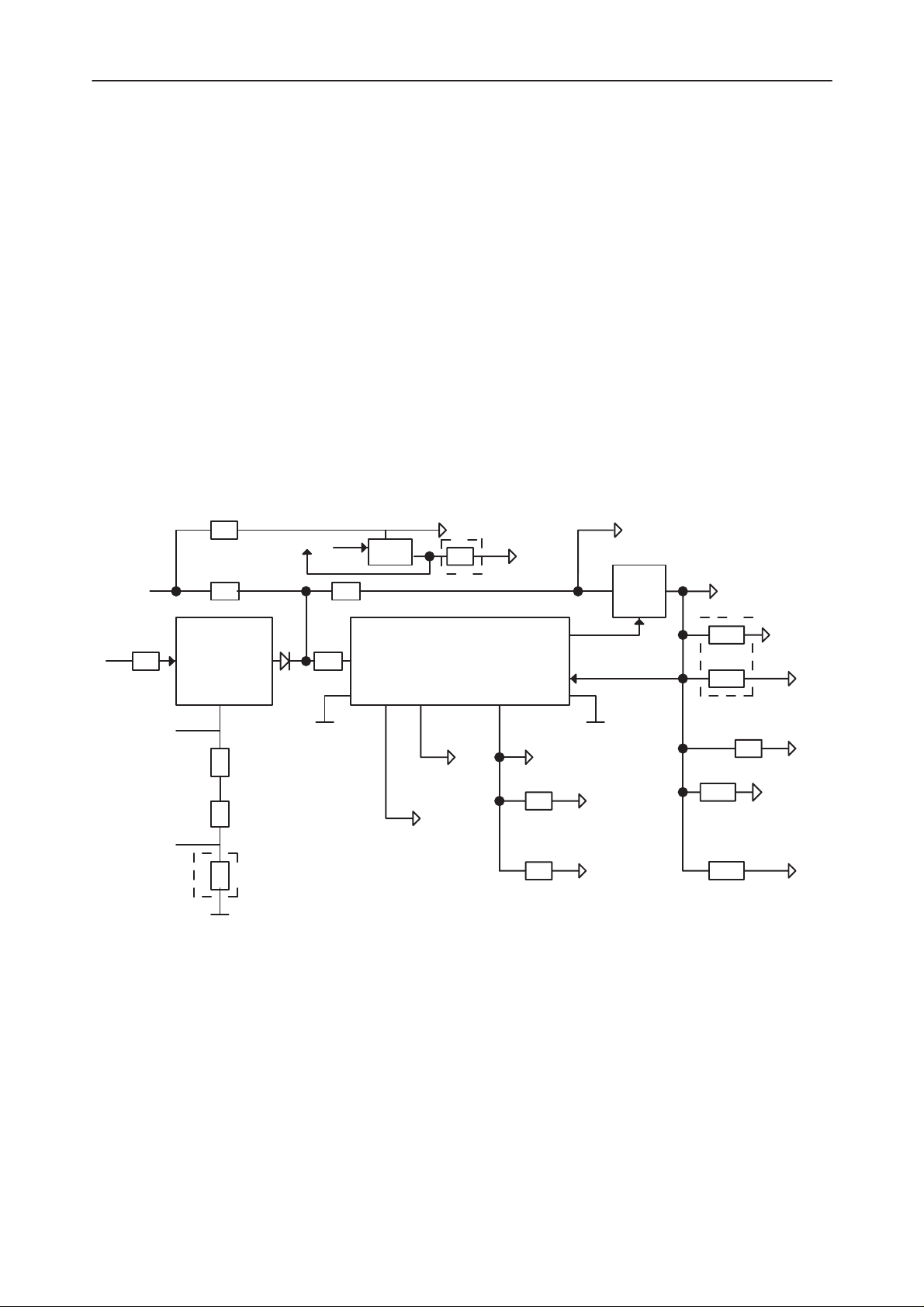

Power Supply

L308

CRFCONT

VBAT

5.3 ... 8.6 V

CHARGER

16.5 V max.

L301

CHARGND

BATGND

Not Assembled

L300

CHARGER

UNIT

N601

V305

AGND

L302

L304

L309

BGND

L310

L311

5,21,37

39,44

6,32

V450

41

VBAT to RF

Not Assembled

PSCLD

N301

35

VA

3.16 V

N200

VSIM

L451

4.50 V

40

VRF

N450

4,20,38

VSL

L152

L151

43

42

VSLRC

3.16 V

D151; pin 124

VSLC

D151

D402

D404

System Module GT8

VB (to illumination leds)

V306

GND

3.16 V

VL

L306

L150

Not Assembled

L410

L153

VLDSP

D152

L450

VLCD

3.16 V3.16 V

VLC

3.16 V

D150

D400

VLCRAM

3.16 V

D410

D411

VLRFI

3.16 V

N450

The power supply for the baseband is the main battery. The main battery consists of 5 NiCd or NiMH cells with a nominal voltage of 6.0V. A charger input is

used to charge the battery. Two different chargers can be used for charging the

battery. A switch mode type fast charger that can deliver 780 mA and a standard charger that can deliver 265 mA. The idle voltage for the fast and standard

charger see NO TAG. Both chargers are of constant current type.

Original 02/97

Page 4–9

Page 10

NHE–5

After Sales

System Module GT8

The baseband has one power supply circuit, N301 delivering power to the different parts in the baseband. There are two logic power supply and one analog

power supply. The analog power supply VA is used for analog circuits such as

audio codec, N200 and microphone bias circuitry. Due to the current consumption and the baseband architecture the digital supply is divided into to parts.

Both digital power supply rails from the N301, PSCLD is used to distribute the

power dissipation inside N301, PSCLD. The main logic power supply VL has an

external power transistor, V306 to handle the power dissipation that will occur

when the battery is fully charged or during charging.

D151, ASIC and the MCU SRAM, D402/D403 are connected to the same logic

supply voltage. All other digital circuits are connected to the main digital supply.

The analog voltage supply is connected to the audio codec.

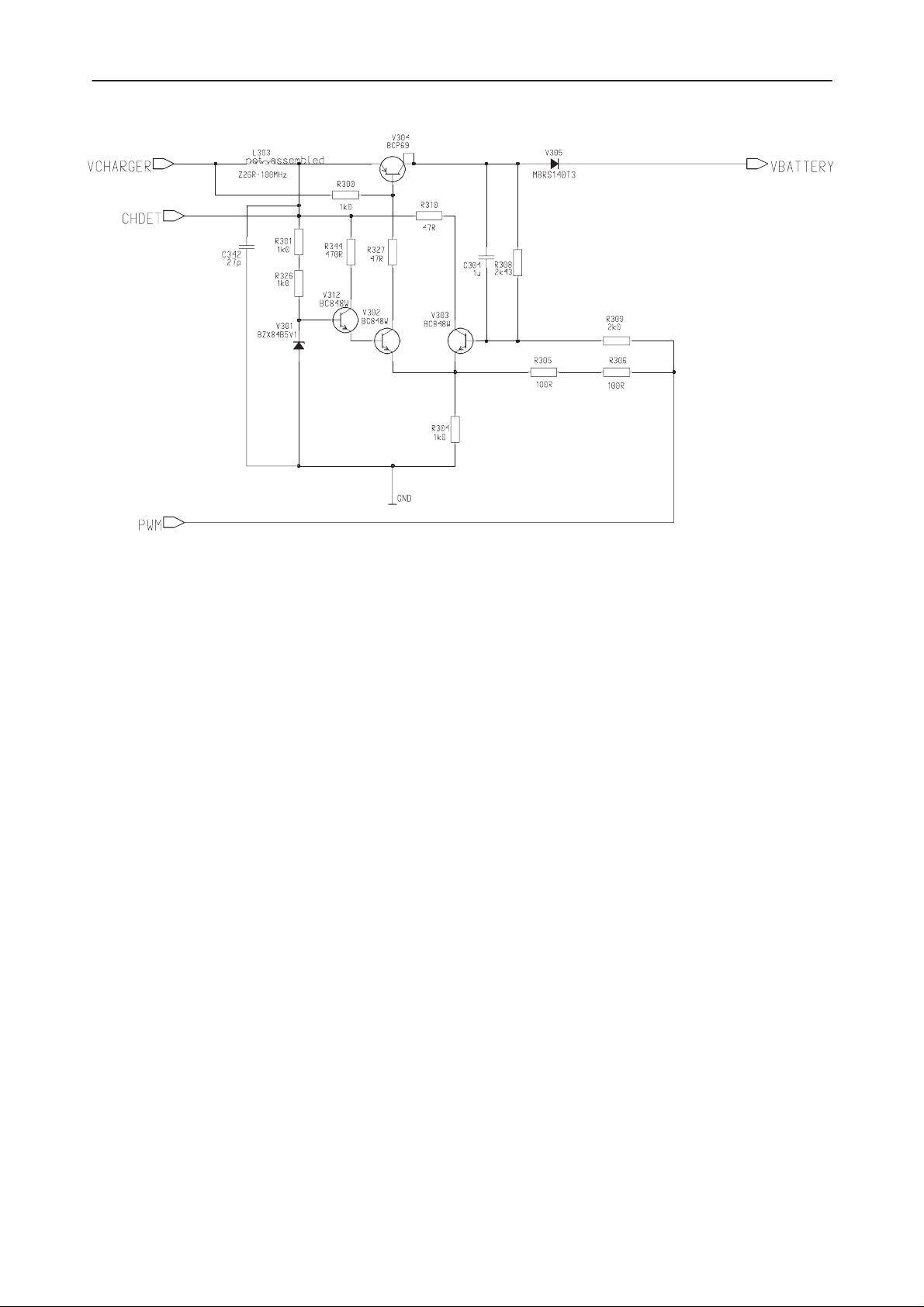

Charging Control Switch Functional Description

The charging switch transistor V304 controls the charging current from the

charger input to the battery. During charging the transistor is forced in saturation and the voltage drop over the transistor is 0.2–0.4V depending upon the

current delivered by the charger. Transistor V304 is controlled by the PWM output from N301, pin 23 via resistors R309, R308 and transistor V303. The output

from N301 is of open drain type. When transistor V304 is conducting the output

from N301 pin is low. In this case resistors R305 and R306 are connected in

parallel with R304. This arrangement increases the base current through V304

to put it into saturation.

Technical Documentation

Transistors V304, V302, V303 and V312 forms a simple voltage regulator circuitry. The reference voltage for this circuitry is taken from zener diode V301.

The feedback for the regulator is taken from the collector of V304. When the

PWM output from N301 is active, low, the feedback voltage is determined by

resistors R308 and R309. This arrangement makes the charger control switch

circuitry to act as a programmable voltage regulator with two output voltages

depending upon the state of the PWM output from N301. When the PWM is inactive, in high impedance the feedback voltage is almost the same as on the

collector of V304. Due to the connection the voltage on V303 and V302 emitters are the same. The influence of the current thru R305 and R306 can be neglected in this case.

The charging switch circuit diagram is shown in following figure. The figure is

for reference only.

Page 4–10

Original 02/97

Page 11

After Sales

NHE–5

Technical Documentation

System Module GT8

This feedback means that the system regulates the output voltage from V304 in

such a way that the base of V303 and V302 are at the same voltage. The voltage on V302 is determined by the V301 zener voltage. The darlington connection of V312 and V302 service two purposes 1 the load on the voltage reference V301 is decreased, 2 the output voltage on V304 is decreased by the

VBE voltage on V312 which is a wanted feature. The voltage reduction allows a

relative temperature stable zener diode to be used and the output voltage from

V304 is at a suitable level when the PWM output from N301 is not active.

The circuitry is self starting which means that an empty battery is initially

charged by the regulator circuitry around the charging switch transistor. The

battery is charged to a voltage of maximum 8.4V. This charging switch circuit

allows for both NiCd, NiMH and Lithium type of batteries to be used.

When the PWM output from N301 is active the feedback voltage is changed

due to the presence of R308 and R309. When the PWM is active the charging

switch regulator voltage is set to 10.5V maximum. This means that even if the

voltage on the charger input exceeds 11.5V the battery voltage will not exceed

10.5 V. This protects N301 from over voltage even if the battery was to be detached while charging.

V305 is a schottky diode that prevents the battery voltage from reverse bias

V304 when the charger is not connected. The leakage current for V305 is increasing with increasing temperature and the leakage current is passed to

ground via R308, V303 and R304. This arrangement prevents V304 from being

reversed biased as the leakage current increases at high temperatures.

V300 is a 16V transient suppressor. V300 protects the charger input and in particular V304 for over voltage. The cut off voltage is 16V with a maximum surge

voltage up to 25V. V300 also protects the input for wrong polarity since the transient suppressor is bipolar.

Original 02/97

Page 4–11

Page 12

NHE–5

After Sales

System Module GT8

Power Supply Regulator PSCLD, N301

The power supply regulators are integrated into the same circuit N301. The

power supply IC contains three different regulators. The main digital power supply regulator is implemented using an external power transistor V306. The other two regulators are completely integrated into N301.

Technical Documentation

PSCLD, N301 External Components

N301 performs the required power on timing. The PSCLD, N301 internal power on and reset timing is defined by the external capacitor C330. This capacitor

determines the internal reset delay, which is applied when the PSCLD, N301 is

initially powered by applying the battery. The baseband power on delay is determined by C311. With a value of 10 nF the power on delay after a power on

request has been active is in the range of 50–150 ms. C310 determines the

PSCLD, N301 internal oscillator frequency and the minimum power off time

when power is switched off.

The sleep control signal from the ASIC, D151 is connected via PSCLD, N301.

During normal operation the baseband sleep function is controlled by the ASIC,

D151 but since the ASIC is not power up during the startup phase the sleep

signal is controlled by PSCLD, N301 as long as the PURX signal is active. This

arrangement ensures that the 13 MHz clock provided from RF to the ASIC,

Page 4–12

Original 02/97

Page 13

After Sales

NHE–5

Technical Documentation

D151 is started and stable before the PURX signal is released and the baseband exits reset. When PURX is inactive, high, sleep control signal is controlled

by the ASIC D151.

N301 requires capacitors on the input power supply as well as on the output

from each regulator to keep each regulator stable during different load and temperature conditions. C305 and C335 are the input filtering capacitors. Due to

EMC precautions a filter using C337, L310, C335, L311, C338 and C339 has

been inserted into the supply rail. This filter reduces the high frequency components present at the battery supply from exiting the baseband into the battery

pack. The regulator outputs also have filter capacitors for power supply filtering

and regulator stability. A set of different capacitors are used to achieve a high

bandwidth in the suppression filter.

PSCLD, N301 Control Bus

The PSCLD, N301 is connected to the baseband common serial control bus,

SCONB(5:0). This bus is a serial control bus from the ASIC, D151 to several

devices on the baseband. This bus is used by the MCU to control the operation

of N301 and other devices connected to the bus. N301 has two internal 8 bit

registers and the PWM register used for charging control. The registers contain

information for controlling reset levels, charging HW limits, watchdog timer

length and watchdog acknowledge.

System Module GT8

The control bus is a three wire bus with chip select for each device on the bus

and serial clock and data. From PSCLD, N301 point of view the bus can be

used for writing only. It is not possible to read data from PSCLD, N301 by using

this bus.

The MCU can program the HW reset levels when the baseband exits/enters reset. The programmed values remains until PSCLD is powered off, the battery is

removed. At initial PSCLD, N301 power on the default reset level is used. The

default value is 5.1 V with the default hysteresis of 400 mV. This means that reset is exit at 5.5 V when the PSCLD, N301 is powered for the first time.

The watchdog timer length can be programmed by the MCU using the serial

control bus. The default watchdog time is 32 s with a 50 % tolerance. The complete baseband is powered off if the watchdog is not acknowledged within the

specified time. The watchdog is running while PSCLD, N301 is powering up the

system but PURX is active. This arrangement ensures that if for any reason the

battery voltage doesn’t increase above the reset level within the watchdog time

the system is powered off by the watchdog. This prevents a faulty battery from

being charged continuously even if the voltage never exceeds the reset limit.

As the time PURX is active is not exactly known, depends upon startup condition, the watchdog is internally acknowledged in PSCLD when PURX is released. This gives the MCU always the same time to respond to the first watchdog acknowledge.

Baseband power off is initiated by the MCU and power off is performed by writing the smallest value to the watchdog timer register. This will power off the

baseband within 0.5 ms after the watchdog write operation.

Original 02/97

Page 4–13

Page 14

NHE–5

After Sales

System Module GT8

The PSCLD, N301 also contains switches for connecting the charger voltage

and the battery voltage to the baseband A/D converters. Since the battery voltage is present and the charger voltage might be present in power off the A/D

converter signals must be connected using switches. The switch state can be

changed by the MCU via the serial control bus. When PURX is active both

switches are open to prevent battery/charger voltage from being applied to the

baseband measurement circuitry which is powered off. Before any measurement can be performed both switches must be closed by MCU.

Charger Detection

A charger is detected if the voltage on N301 pin 28 is higher than 0.5V. The

charger voltage is scaled externally to PSCLD, N301 using resistors R302 and

R303. With the implemented resistor values the corresponding voltage at the

charger input is 2.8V. Due to the multi–function of the charger detection signal

from PSCLD, N301 to ASIC, D151 the charger detection line is not forced ,active high until PURX is inactive. In case PURX is inactive the charger detection

signal is directly passed to D151. The active high on pin 14 generates and interrupt to MCU which then starts the charger detection task in SW.

Technical Documentation

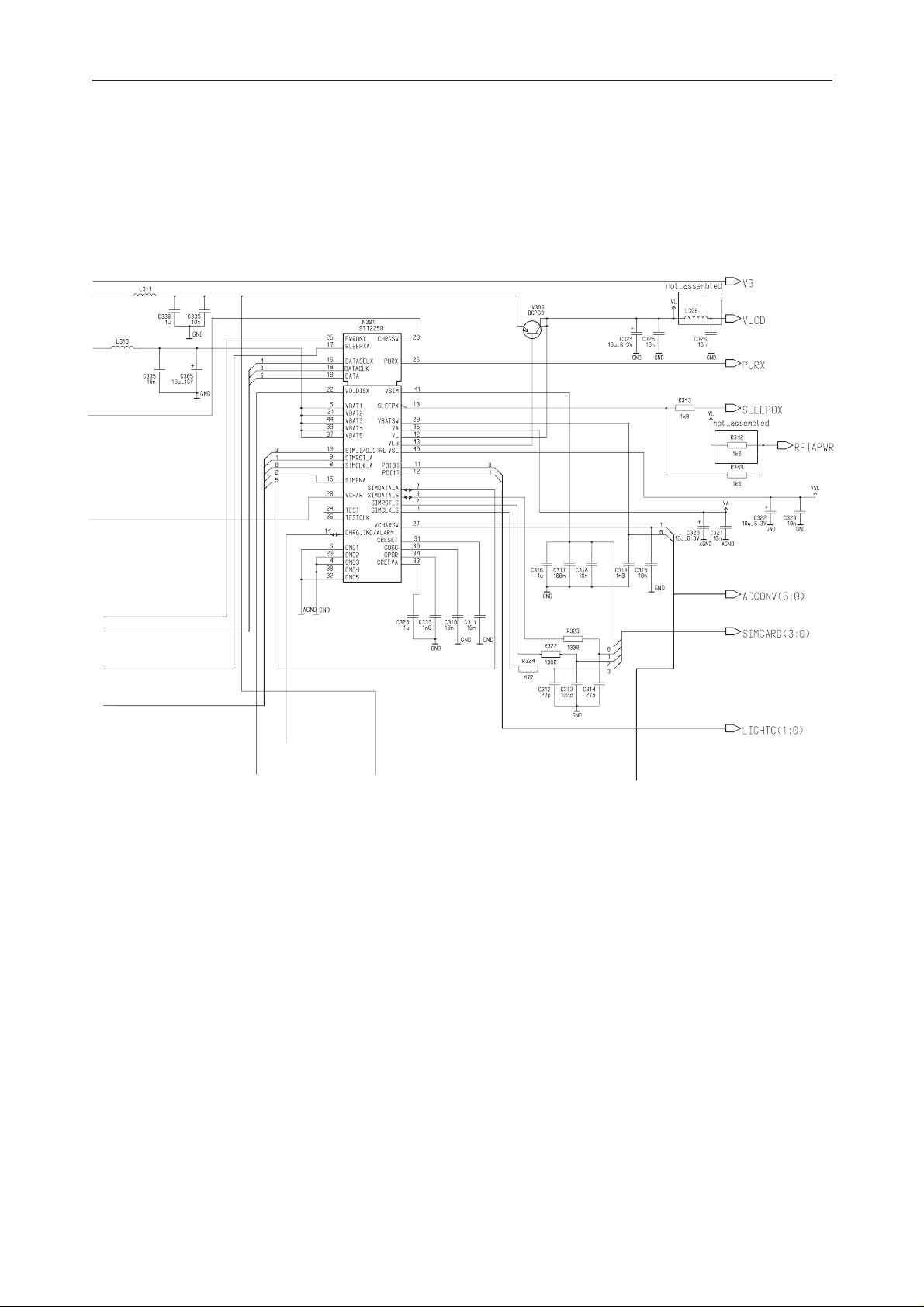

SIM Interface and Regulator in N301

The SIM card regulator and interface circuitry is integrated into PSCLD, N301.

The benefit from this is that the interface circuits are operating from the same

supply voltage as the card, avoiding the voltage drop caused by the external

switch used in previous designs. The PSCLD, N301 SIM interface also acts as

voltage level shifting between the SIM interface in the ASIC, D151 operating at

3V and the card operating at 5V. Interface control in PSCLD is direct from

ASIC, D151 SIM interface using SIMI(5:0) bus. The MCU can select the power

supply voltage for the SIM using the serial control bus. The default value is 3V

which needs to be changed to 5V before power up the SIM interface in ASIC,

D151. Regulator enable and disable is controlled by the ASIC via SIMI(2). For

further operation of the SIM interface see section NO TAG.

Power Up Sequence

The baseband can be powered up in three different ways.

– When the power switch is pressed input pin 25 to PSCLD, N301 is con-

nected to ground and this switches on the regulators inside PSCLD.

– An other way to power up is to connect the charger. Connecting the charger

causes the baseband to power up and start charging the battery.

Page 4–14

– The third way to power the system up is to attach the battery.

Original 02/97

Page 15

After Sales

NHE–5

Technical Documentation

PSCLD

N301

VBAT

Pwr

Switch

Watchdog

disable

CHARGER

UNITCHARGER

5,21,37

39,44

25

23

28

30

16,18,19

C310

VL VSL VA

40

35

26 120

17 130

14

13

CRFCONT

N601

Purx

Serial Bus

VCXO Enable

CHARGAlarm

1415

129

VCXO

SRAM, FLASH

D403 D400

22

13 MHz

Address Bus

ASIC

D151

Watchdog

Register

32 kHz

125 126

Data Bus

System Module GT8

83

84

82

81

MCU Clock

MCU Reset

48 51

DSP Reset

DSP Clock

MCU

D150

Power up using Power on Button

This is the most common way to power the system up. This power up is successful if the battery voltage is higher than power on reset level set by the

MCU, default value 5.5V in PSCLD, N301. The power up sequence is started

when the power on input pin 25 at PSCLD is activated, low. The PSCLD then

internally enters the reset state where the regulators are switched on. At this

state the PWM output from PSCLD is forced active to support additional power

from any charger connected. The sleep control output signal is forced high enabling the regulator to supply the VCO and startup the clock. After the power on

reset delay of 50–150 ms PURX is released and the system exits reset. The

PWM output is still active until the MCU writes the first value to the PWM register. The watchdog has to be acknowledged within 16 s after that PURX has

changed to inactive state

Power Up with Empty Battery using Charger

When the charger is inserted into the DC jack or charger voltage is supplied at

the system connector surface contacts/pins PSCLD , N301 powers up the

baseband. The charging control switch is operating as a linear regulator, the

output voltage is 4.5V–5V. This allows the battery to be charged immediately

when the charger is connected. This way of operation guarantees successful

power up procedure with empty battery. In case of empty battery the only power source is the charger. When the battery has been initially charged and the

voltage is higher than the PSCLD, N301 switch on voltage the sleep control signal which is connected to the PSCLD for power saving function sleep mode,

enters inactive state, high, to enable the regulator that controls the power supply to the VCO to be started. The ASIC, D151 which normally controls the sleep

control line has the sleep output inactive, low as long as the system reset,

PURX is active, low, from PSCLD. After a delay of about 5–10 ms the system

Original 02/97

Page 4–15

Page 16

NHE–5

After Sales

System Module GT8

reset output PURX from PSCLD enters high state. This delay is to ensure that

the clock is stable when the ASIC exits reset. The sleep control output from the

PSCLD that has been driving an output until now, returns the control to the

sleep signal from the ASIC as the PURX signal goes inactive. When the PURX

signal goes inactive, high, the charge detection output at PSCLD, that is in input mode when PURX is active, switches to output and goes high indicating

that a charger is present. When the system reset, PURX, goes high the sleep

control line is forced inactive, high, by the ASIC, D151 via PSCLD, N301.

Once the system has exited reset the battery is initially charged until the MCU

writes a new value to the PWM in PSCLD. If the watchdog is not acknowledged

the battery charging is switched off when the PSCLD shuts off the power to the

baseband. The PSCLD will not enter the power on mode again until the charger

has been extracted and inserted again or the power switch has been pressed.

The battery is charged as long as the power on line, PWRONX is active low.

This is done to allow the phone to be started manually from the power button

with the charger inserted not having to extract the charger to get a power up if

the battery is empty.

Power On Reset Operation

Technical Documentation

The system power up reset is generated by the regulator IC, N301. The reset is

connected to the ASIC, D151 that is put into reset whenever the reset signal,

PURX is low. The ASIC, D151 then resets the DSP, D152 the MCU, D150 and

the digital parts in N450. When reset is removed the clock supplied to the ASIC,

D151 is enabled inside the ASIC. At this point the 32 kHz oscillator signal is not

enabled inside the ASIC, since the oscillator is still in the startup phase. To start

up the block requiring 32 kHz clock the MCU must enable the 32 kHz clock.

The MCU reset counter is now started and the MCU reset is still kept active,

low. 6.5 MHz clock is started to MCU in order to put the MCU, D150 into reset,

MCU is a synchronous reset device and needs clock to reset. The reset to

MCU is put inactive after 128 MCU clock cycles and MCU is started.

DSP, D152 and N450 reset is kept is kept active when the clock inside the

ASIC, D151 is started. 13 MHz clock is started to DSP, D152 and puts it into reset, D152 is a synchronous reset device and requires clock to enter reset.

N450 digital parts are reset asynchronously and do not need clock to be supported to enter reset.

As both the MCU, D151 and DSP, D152 are synchronous reset devices all interface signals connected between these devices and ASIC D151 which are

used as I/O are set into input mode on the ASIC, D151 side during reset. This

avoids bus conflicts to occur before the MCU, D150 and the DSP, D152 are actually reset.

Page 4–16

The DSP, D152 and N450 reset signal remains active after that the MCU has

exited reset. The MCU writes to the ASIC register to disable the DSP reset.

This arrangement allows the MCU to reset the DSP, D152 and N450 when ever

needed. The MCU can put DSP into reset by writing the reset active in the

ASIC, D151 register

Original 02/97

Page 17

After Sales

NHE–5

Technical Documentation

MCU

The baseband uses a Hitachi H3001 type of MCU. This is a 16–bit internal

MCU with 8–bit external data bus. The MCU is capable of addressing up to 16

MByte of memory space linearly depending upon the mode of operation. The

MCU has a non multiplexed address/data bus which means that memory access can be done using less clock cycles thus improving the performance but

also tightening up memory access requirements. The MCU is used in mode 3

which means 8–bit external data bus and 16 Mbyte of address space. The

MCU operating frequency is equal to the supplied clock frequency. The MCU

has 512 bytes of internal SRAM. The MCU has one serial channel, USART that

can operate in synchronous and asynchronous mode. The USART is used in

the MBUS implementation. Clock required for the USART is generated by the

internal baud rate generator. The MCU has 5 internal timers that can be used

for timing generation. Timer TIOCA0 input pin 71 is used for generation of netfree signal from the MBUS receive signal which is connected to the MCU

USART receiver input on pin 2.

The MCU contains 4 10–bit A/D converters channels that are used for baseband monitoring. For A/D converter channel usage see section NO TAG.

System Module GT8

The MCU, D150 has several programmable I/O ports which can be configured

by SW. Port 4 which multiplexed with the LSB part of the data bus is used

baseband control. In the mode the MCU is operating this port can be used as

an I/O port and not as part of the data bus, D0–D7.

MCU Access and Wait State Generation

The MCU can access external devices in 2 state access or 3 state access. In

two state access the MCU uses two clock cycles to access data from the external device In 3 state access the MCU uses 3 clock cycles to access the external device or more if wait states are enabled. The wait state controller can operate in different modes. In this case the programmable wait mode is used.

This means that the programmed amount of wait states in the wait control register are inserted when an access is performed to a device located in that area.

For area split see NO TAG. The complete address space is divided into 8 areas

each area covering 2 MByte of address space. The access type for each area

can be set by bits in the access state control register. Further more the wait

state function can be enabled separately for each area by the wait state controller enable register.

This means that in 3 state access two types of access can be performed with a

fixed setting:

– 3 state access without wait states

– 3 state access with the amount of wait states inserted determined by the

Original 02/97

wait control register

Page 4–17

Page 18

NHE–5

After Sales

System Module GT8

If the wait state controller is not enabled for a 3 state access area no waits

states are inserted when accessing that area even if the wait control register

contains a value that differs from 0 states.

MCU Flash Loading

The flash loading equipment is connected to the baseband by means of the test

connector before the module is cut out from the frame. Updating SW on a final

product is done by removing the battery and connect a special battery that contains the necessary contacting elements. The contacts on the baseband board

are test points that are accessible when the battery is detached. The power

supply for the base band is supplied via the adapter and controlled by the flash

programming equipment. The base band module is powered up when the power is connected to the battery contact pins.

Five signals are required for the flash programming, with the addition of the battery supply. The baseband MCU will automatically wait for flash down loading to

be performed if one of the two following criteria are met.

– The flash is found to be empty when tested by the MCU

Technical Documentation

– The serial clock line at the baseband MCU is forced low when the MCU is

exiting reset

The second alternative is used for reprogramming as the flash is not empty in

this case. To allow the serial clock line to be forced low during MCU initial boot

there is a requirement that the flash prommer can control the power on of the

baseband module. This is done by controlling the switching of the battery power supply. This arrangement allows the baseband module to operate in normal

mode even if the flash prommer is connected but not active. The flash prommer

also disables the power supply watchdog during flash programming to prevent

unwanted power off of the baseband. The programming voltage to the flash is

applied when the flash prommer has detected that the baseband module is

powered. This detection is performed by monitoring the serial interface RX line

from the baseband. The RX line is pulled high by a pull–up resistor in idle. The

VPP voltage is set to 5V as it is not known at this point what type of device is

used.

The following diagram shows the block diagram for the baseband flash programming circuitry.

Page 4–18

Original 02/97

Page 19

After Sales

NHE–5

Technical Documentation

X300

VPP

FRX

FTX

FCLK

WDDis

GND

VBAT

1

2

3

4

5

6

Flash Prommer

5... 22

26

PSCLD

N301

40

FLASH pin11 Vpp

PSCLD pin 22 WDDis

GND

Programming Voltage Vpp

ASIC pin 120

PurX

VL,VSL

ASIC pin 130 PwrDown

VLC

R315

11

FLASH

D400

ASIC pin 51 CSelX

2,71

1

MCU

D150

Internal

3

MCU pin 55 RdX

RAM

38(9)37(24)9(24)12(10)

MCU pin 56 WrX

PSCLD pin 26 PurX

Master Reset

56

55

MCUResX

51 82

MCUClk

MCUAdrress

MCUData

WrX

RdX

SRAM

D403

System Module GT8

120

55

ASIC

56

D151

8148

BOOT

ROM

49

RAMCSelX

30

5

32

MCU pin 56 WrX

MCU pin 55 RdX

The following picture shows the location of the flash programming contact pads

on the PCB. These pads are used for SW updating at after sales locations. A

special battery pack is used for this purpose. The battery pack contains contacting elements that can access these pads without having to disassemble the

phone.

WDDIS FCLK VPP FTX FRX

D152

The interface lines between the flash prommer and the baseband are in low

state when power is not connected by the flash prommer. The data transfer between the flash programming equipment and the base band is synchronous

and the clock is generated by the flash prommer. The same MCU USART that

is used for MBUS communication is used for the serial synchronous communication. The PSCLD watchdog is disabled when the flash loading battery pack

and cable is connected.

Original 02/97

Page 4–19

Page 20

NHE–5

After Sales

System Module GT8

After the flash battery pack adapter has been mounted or the test connector

has been connected to the board the power to the baseband module is connected by the flash prommer or the test equipment. All interface lines are kept

low except for the data transmit from the baseband that is in reception mode on

the flash prommer side, this signal is called TXF. The MCU boots from ASIC

and investigates the status of the synchronous clock line. If the clock input line

from the flash prommer is low or no valid SW is located in the flash MCU forces

the initially high TXF line low acknowledging to the flash prommer that it is

ready to accept data.

The flash prommer sends data length, 2 bytes, on the RXF data line to the

baseband. The MCU acknowledges the 2 data byte reception by pulling the

TXF line high. The flash prommer now transmits the data on the RXF line to the

MCU. The MCU loads the data into the internal SRAM. After having received

the transferred data correctly MCU puts the TXF line low and jumps into internal SRAM and starts to execute the code. After a guard time of 1 ms the TXF

line is put high by the MCU. After 1 ms the TXF is put low indicating that the

external SRAM test is going on. After further 1 ms the TXF is put high indicating

that external SRAM test has passed. The MCU performs the flash memory

identification based upon the identifiers specified in the Flash Programming

Specifications. In case of an empty device, identifier locations shows FFH, the

flash device code is read and transmitted to the Flash Prommer.

Technical Documentation

TXF

Boot OK

Reset

External SRAM

Internal SRAM

execution begin External SRAM

Length OK

After that the device mounted on base band has been identified the Flash

Prommer down loads the appropriate algorithm to the baseband. The programming algorithm is stored in the external SRAM on the baseband module and

after having down loaded the algorithm and data transfer SW, MCU jumps to

the external SRAM and starts to execute the code.

The MCU now asks the prommer to connect the flash programming power supply. This SW loads the data to be programmed into the flash and implements

the programming algorithm that has been down loaded.

test going on

test passed

1 ms

Ready to send

Flash ID

Page 4–20

Original 02/97

Page 21

After Sales

NHE–5

Technical Documentation

Flash Prommer Connection Using Dummy Battery

For MCU SW updating in the field a special battery adapter can be used to connect to the test points which are accessible through 5 holes in the chassis, located behind the battery. Supply voltage must be connected to this dummy battery as well as the flash programming equipment

Flash, D400

A 4 MBit Boot Block flash is used as the main program memory, D400 the device is 3 V read/program with external 12V VPP for programming. The device

has a lockable boot sector. This function is not used since the complete code is

reprogrammed. The Boot sector is located at the ”bottom”, definition by Intel,

address 00000H–03FFFH. The block is unlocked by a logic high state on pin

12. This logic high level is generated from VPP. The device can be programmed by a VPP of 5V but the programming procedure takes longer. To improve programming the programming voltage used is 12V. The speed of the

device is 110 ns although the requirement is 150 ns. The MCU operating at 6.5

MHz will access the flash in 2 state access, requiring 150 ns access time from

the memory.

System Module GT8

SRAM D402, D403

The baseband is designed to take two different size of SRAMs, 32kx8 and

128kx8, not at the same time. The required speed is 150 ns as the MCU will

operate at 6.5 MHz and the SRAM will be accessed in 2 state access. The

SRAM has no battery backup which means that the content is lost even during

short power supply disconnections. As shown in the memory map the SRAM is

not accessible after boot until the MCU has enabled the SRAM access by writing to the ASIC register.

EEPROM D401

The baseband is designed to take an 8kx8 parallel EEPROM. In addition to that

a serial 2kx8 device using I2C bus is also designed on the baseband. HD842

will use the 2kx8 serial device over the I2C bus. The I2C bus protocol is implemented in SW and the physical implementation is performed on MCU Port 4.

The parallel device is connected to the MCU data and address bus. The ASIC

generates chip select for the EERPROM. To avoid unwanted EEPROM access

there is an EERPOM access bit in the ASIC MCU interface. This bit mus be set

to allow for EERPOM access. This bit is cleared by default after reset. After

each access this bit should be cleared to prevent unwanted EEPROM access.

The parallel device used support page mode writing, 64 byte page. One page

can be written by the MCU and after that the internal programming procedure is

started. The page write operation is internally timed in the device and consecutive bytes must be written within 100 us. During this operation all interrupts

must be disabled.

Original 02/97

Page 4–21

Page 22

NHE–5

After Sales

System Module GT8

Technical Documentation

MCU and Peripherals

MCU Port P4 Usage

MCU, D150 port 4 is used for baseband control.

Port Pin MCU pin Control Function Remark

P40 5 Display driver reset Active low

P41 6

P42 7

P43 8

P44 9 EEPROM SCK

P45 10 EEPROM SDA

P46 11 EEPROM write enable Active low

P47 12 Headset mic amplifier bias Active low

Baseband A/D Converter Channels usage in N450 and D150

The auxiliary A/D converter channels inside RFI2, N450 are used by MCU to

measure battery voltage. The A/D converters are accessed by the DSP, D152

via the ASIC, D151. The required resolution is 10 bit.

The MCU has 4 10 bit A/D channels which are used for baseband voltage monitoring. The MCU can measure charger voltage, battery size, battery temperature and accessory detection by using it’s own converters.

Page 4–22

Original 02/97

Page 23

After Sales

NHE–5

Technical Documentation

Baseband N450 A/D Converter Channel Usage

Name: Usage: Input volt. range Remark

Chan 0 Battery voltage 5...9 V Battery voltage when

Chan 1 Charger voltage 5...16 V

Chan 2 Battery size indic. 0...3.2 V

Chan 3 Battery temperature 0...3.2 V

Chan 4 System board temp. 0...3.2 V Not used

Chan 5 Accessory detection 0...3.2 V

Chan 6 0...3.2 V Not used

Chan 7 Battery voltage 5...9 V Battery volt. TX inactive

MCU Baseband A/D Converter Channel Usage

Name: Usage: Input volt. range Remark

System Module GT8

TX is active

Chan 0 Battery temperature 0...3.2 V

Chan 1 Charger voltage 5...16 V

Chan 2 Accessory detection 0...3.2 V

Chan 3 Battery size indicator0...3.2 V

Battery Voltage Measurement

The battery voltage is measured using RFI2, N450 A/D converter channel 0

and 7. The converter value supplied from channel 7 is measured when the

transmitter is active. This measurement gives the minimum battery voltage. The

value from channel 0 is measured when the transmitter is inactive. The battery

voltage supplied to the A/D converter input is switched off when the baseband

is in power off. The battery voltage measurement voltage is supplied by

PSCLD, N301 which performs scaling, the scaling factor is R1(R1+R2), and

switch off. The measurement voltage is filtered by a capacitor to achieve an average value that is not depending upon the current consumption behavior of the

baseband. To be able to measure the battery voltage during transmission pulse

the time constant must be short. The value for the filtering capacitor is set to

1 nF, C319. The scaling factor used to scale the battery voltage must be 1:3,

which means that 9V battery voltage will give 3V A/D converter input voltage.

The A/D converter value in decimal can be calculated using the following formula:

A/D = 1023xR1xU

where K is the scaling factor. K = R1/((R1+R2)xU

Original 02/97

/((R1+R2)xU

BAT

) = 1023xU

ref

BAT

ref).

xK

Page 4–23

Page 24

NHE–5

After Sales

System Module GT8

Charger Voltage Measurement

The charger voltage is measured to determine the type of charger used. MCU

A/D converter channel 1 is used for this purpose. The input circuitry to the charger measurement A/D channel implements an LP–filter. The input voltage must

be scaled before it is fed to the A/D converter input. Due to the high input voltage range scaling is performed outside PSCLD, N301. The scaling factor required is 22/(22+100) = 0.18. The charger voltage measurement switch is integrated into PSCLD, N301. Charger voltage is not supplied to the A/D converter

input in power off mode. This is done to protect the A/D converter input in case

power is switched off and the charger remains connected to the baseband. The

charger A/D converter value can be calculated using the same formula as described in above section. The resistor values are different since the scaling factor is larger.

Battery Size Resistor Measurement

The battery size, capacity is determined by measuring the voltage on the BSI

pin on the battery pack when the battery is attached to the phone. The MCU

A/D converter channel 3 is used for this purpose. The BSI signal is pulled up on

the base band using a 47 kohm resistor and the resistor inside the battery pack

is reflecting the capacity of the battery. There are two special cases to be detected by the MCU. The first case is the Lithium battery. The Lithium battery

has reserved values in the battery size table. Lithium type batteries are all the

same from charging point of view. Lithium batteries are charged to a constant

voltage and charging is aborted when the predefined voltage is reached. The

Lithium battery capacity is a function of the battery voltage. The battery voltage

drops linearly as the battery is discharged. The other case that has to be handled is the dummy battery. This battery is used for A/D converter field calibration at service centers and together with a defined voltage on the BTEMP pin

on the battery pack to put the baseband into Local mode in production. Battery

sizes below 250 mAh will be treated as dummy battery. The different battery

size values are shown in the table below . The battery size A/D converter value

can be calculated using the following formula:

Technical Documentation

Page 4–24

A/D = RSI/(RSI+47 kΩ)x1023

where RSI is the value of the resistor inside the battery pack.

Original 02/97

Page 25

After Sales

NHE–5

Technical Documentation

Battery Size and A/D Converter Value

Battery Type Battery pack resistor Capacity BSI volt. A/D conv value

Dummy 1 kΩ 2 % <250 mAh0.07 21 (83)

Standard battery 6.19 kΩ 2 % 900 mAh 0.37 119 (467)

Extended battery 9.09 kΩ 2 % 1200 mAh0.52 166 (664)

Slim 3.3 kΩ 2 % 500 mAh 0.21 67 (268)

Lithium 68 kΩ 2 % 400 mAh 1.86 605 (2420)

Lithium 82 kΩ 2 % 8.6 V 2 650 (2601)

Battery Temperature Measurement

The battery temperature is measured during charging. The BTEMP pin to the

battery is pulled up on baseband by a 47 kohm resistor to logic supply voltage,

3.2V. The voltage on the BTEMP pin is a function of the battery pack temperature. Auxiliary A/D channel 3 is used for this purpose. Inside the battery pack

there is a 47 kohm NTC resistor to ground. The A/D converter value can be calculated from the following formula:

System Module GT8

A/D = RNTC/(RNTC+47 kohm)x1023

where RNTC is the value of the NTC resistor inside the battery pack.

The relation ship between different battery temperature, BTEMP voltage and

A/D converter values are shown in following table.

A/D Converter Values for Different Battery Temperatures

Bat. temp.NTC value BTEMP voltage A/D conv. value

Dummy 1 kΩ 0.06 V 21

–25 745.60 kΩ 2.96 V 962

0 164.96 kΩ 2.45 V 796

25 47 kΩ 1.58 V 512

50 16.26 kΩ 0.81 V 263

70 7.78 kΩ 0.45 V 145

Compact HF & Headset Detection

Auxiliary A/D channel 4 is used to detect accessories connected to the system

connector using the XMIC. To be able to determine which accessory has been

connected MCU measures the DC voltage on the XMIC input. The accessory is

detected in accordance with the CAP Accessory specifications. Not all accessories are supported by the HD842 base band that are specified in the CAP Accessory specification.

Original 02/97

Page 4–25

Page 26

NHE–5

After Sales

System Module GT8

The base band has a pull–up resistor network of 32 kohm to VA. The accessory

has a pull down. The A/D converter value can be calculated using the following

formula:

A/D = (ACCI+10 kΩ)/(ACCI+32 kΩ)x1023

where ACCI is the d.c. input impedance of the accessory device connected to

the system connector.

The different values for acceptable accessories are given in the following table.

The values in below table are calculated using 5 % resistor values and power

supply range 3–3.3 V. Due to that the pull up resistor in the XMIC line is divided

into two resistors the voltage at the A/D converter input is different from that on

the XMIC.

Accessory Detection Voltage

Acc. type Acc. resistance Voltage on A/D converter A/D converter

Headset 47 kΩ 2.1...2.3...2.45 717...758

Compact 22 kΩ 1.7...1.9...2.05 581...631

HF

Technical Documentation

channel 5 (min/typ/max) value(min/max)

Keyboard Interface

The keypad matrix is located on a PCB and the interface to the base band is by

using connector X101. The electrical specifications are shown in NO TAG. The

power on key is also connected to the PSCLD to switch power on. Due to the

internal pull up inside PSCLD, N301 to a high voltage, a rectifier, V203 is required in the keypad matrix for the power on keypad to prevent the high voltage

to interfere with the keypad matrix.

Series resistors, R261–R264 are implemented in the Column output to reduce

the EMI radiation to the UI PCB. Capacitors C257–C260 reduces the EMC radiation and absorbs any ESD produced over an air gap to the keymat. As the serial display driver interface uses ROW5 for data transmission series resistors

are needed to prevent keypad or double keypad pressing from interfering with

the display communication. In a similar way R265–R269 in the ROW lines reduces the EMI to the UI board. Capacitors C251–C256 implements a LP–filter

together with each resistor in the ROW line. The capacitors also absorbs ESD

pulses over an air gap to the keymat.

During idle when no keyboard activity is present the MCU sets the column outputs to ”0” and enables the keyboard interrupt. An interrupt is generated when

a ROW input is pulled low. Each ROW input on the ASIC, D151 has an internal

pull–up. The keyboard interrupt starts up the MCU and the MCU starts the

scanning procedure. As there are keypads to be detected outside the matrix

the MCU sets all columns to ”1” and reads the ROW inputs if a logic ”0” is read

on any ROW this means that one of the 6 possible non matrix keypads has

been pressed. If the result was a ”1” on each ROW the MCU writes a ”0” on

Page 4–26

Original 02/97

Page 27

After Sales

NHE–5

Technical Documentation

each column consecutively while the rest of the column outputs are kept in tri–

state to allow dual keypad activation to be detected. After that the keyboard

scanning is completed and no activity is found the MCU writes ”0” to all columns, enables the keyboard interrupt and enters sleep mode where the clock

to the MCU is stopped. A key press will again start up the MCU.

Keyboard and Display Light

The display and keyboard are illuminated by LED’s. The light is normally

switched on when a keypad is pressed. The rules for light switching are defined

in the SW UI specifications. The display and keyboard light is controlled by the

MCU. The LED’s are connected two in series to reduce the power consumption. Due to the amount of LED’s required for the keyboard and display light

they are divided into three groups. Each group has it’s own control transistor.

The LED switch transistor is connected as a constant current source, which

means that the current limiting resistor is put in the emitter circuitry. This arrangement will reduce LED flickering depending upon battery voltage and momentary power consumption of the phone. The LED’s are connected straight to

the battery voltage. This connection allows two LED’s to connected in series.

The battery voltage varies a lot depending upon if the battery is charged, full or

empty. The switching transistor circuitry is designed to improve this as mentioned earlier.

System Module GT8

The LED transistor control lines are coming from PSCLD. The MCU controls

these lines by writing to PSCLD using the serial control bus. There are two LED

control lines provided by the PSCLD. The display light control is connected to a

separate control line. The keyboard light control is common to the two transistors. This means that the keyboard and display light can be controlled separately. The advantage of this is that the power dissipation and heating of the

phone can be reduced by only having the required lights switched on.

Audio Control

The audio codec N200 is controlled by the MCU, D150. Digital audio is transferred on the CODECB(5:0). PCM data is clock at 512 kHz from the ASIC and

the ASIC also generates 8 kHz synchronization signal for the bus. Data is put

out on the bus at the rising edge of the clock and read in at the falling edge.

Data from the DSP, D152 to the audio codec, N200 is transmitted as a separate

signal from data transmitted from the audio codec, N200 to the DSP, D152. The

communication is full duplex synchronous. The transmission is started at the

falling edge of the synchronization pulse. 16 bits of data is transmitted after

each synchronization pulse.

Original 02/97

Page 4–27

Page 28

NHE–5

After Sales

System Module GT8

VB

BUZZER

BUZZER DRIVER

V201,V202

R209, 210, 211 ...

EARP

EARN

L205

XEAR

MIC BIAS

R201,V200..

MICP

R203L201 C203

MICN

R204L202

R205

L204

R214L206

C206

14

8

9

6

21

25

24

CODEC

N200

CLK

CSX

DATA

11

12

13,16

23

22

5

20

19

10

17

VA

BRIDGE

CIRCUIT

R207,R216,R217

R219,R220

C213,C216

C213,C216

Serial Bus

AUDIO DATA IN

AUDIO DATA OUT

X103

SYSTEM

CONNECTOR

10

R218

CLK 512 kHz

SYNC 8 kHz

VLC

R168

Technical Documentation

R215

R206

C218

C220 L200

MCU

D150

293727

31

DSP

D152

EXT AUDIO EQUIPM. INDICATION

R208

L208

IRQ1X

68

3341

MCU pin 64

A/D Converters

XMIC

X103

pin 8

SGND

Data, Addr Bus

78

42,44,46

40

41

ASIC

D151

Data, Addr Bus

R161

122

The 512 kHz clock is generated form 13 MHz using a PLL type of approach

which means that the output frequency is not 512 kHz at any moment. The frequency varies as the PLL adjusts the frequency. The average frequency is 512

kHz. The clock is not supplied to the codec when it is not needed. The clock is

controlled by both MCU and DSP. DTMF tones are generated by the audio codec and for that purposes the 512 kHz clock is needed. The MCU must switch

on the clock before the DTMF generation control data is transmitted on the serial control bus.

The serial control bus uses clock, data and chip select to address the device on

the bus. This interface is built in to the ASIC and the MCU writes the destination

and data to the ASIC registers. The serial communication is then initiated by

the ASIC. Data can be read form the audio codec, N200 via this bus.

Internal Audio

The bias for the internal microphone is generated from the PSCLD, N301 analog output, VA using a bias generator. The bias generation is designed in such

a way that common mode signals induced into the microphone capsule wires

are suppressed by the input amplifier in the audio codec. The bias generator is

controlled by the MCU to save power, the control signal is taken from the audio

codec, N200 output latch, pin 21, when the microphone is not used, in idle the

bias generator is switched off. The microphone amplifier gain is set by the MCU

to match with the used microphone, 35 dB. The microphone amplifier input to

the audio codec is a symmetrical input.

Page 4–28

The microphone signal is connected to the baseband using filtering to prevent

EMC radiation and RF PA signal to interfere with the microphone signal. L201

Original 02/97

Page 29

After Sales

NHE–5

Technical Documentation

and C201 forms the first part of this filter. R203 and C202 forms the second

part of this filter. A similar filter is used in the negative signal path of the microphone signal. R205 is connected in the ground path for the microphone bias

current. R202 supplies the bias current to the microphone from the generator

circuitry R201, C200 and V200. A transient suppressor, V204, is connected

across the microphone terminals to protect the microphone against ESD.

The earpiece amplifier used for the internal earpiece is of differential type and

is designed as a bridge amplifier to give the output swing for the required sound

pressure. Since the power supply is only 3V a dynamic type ear piece has to be

used to achieve the sound pressure. This means that the ear piece is a low impedance type and represents a significant load to the output amplifier. Series

inductors are implemented to prevent EMC radiation from the connection on

baseband to the earpiece. The same filter also prevents the PA RF field from

causing interference in the audio codec, N200 output stage to the earpiece.

The buzzer is controlled by the PWM output provided by the audio codec,

N200. Transistors V201 and V202 acts as amplifier and, impedance conversion

for the low impedance buzzer. The buzzer is driven directly from the battery

voltage. As the buzzer is connected to the baseband via the keyboard the battery voltage provided by VBKEY and the buzzer driving signal BUZZER are

EMC protected. As the buzzer is a dynamic one the impedance shows a clear

inductance. Therefore a free running diode V203 is used to clip the voltage

spikes induced in the buzzer line when the buzzer is switched off.

System Module GT8

The buzzer frequency is determined by the internal setup of N200. The frequency is determined by the MCU via the serial control bus. The output level

can be adjusted by the PWM function which is attached to the buzzer output in

N200.

External Audio

The external microphone audio signal is applied to the baseband system connector and connected to the audio block using signals XMIC and SGND. In order to improve the external audio performance the input circuitry is arranged in

a sort of dual ended. A wheatstone type of bridge configuration is created by

resistors R216, R217, R219 and R220. The signal is attenuated around 20 dB

to not cause distortion in the microphone amplifier. The microphone signal is

attenuated by resistors R216, R207 and R217. Two allow the external earpiece

to be driven dual ended the external microphone signal ground is connected to

the negative output of the external audio earpiece amplifier. This means that

with reference to audio codec, N200 ground there is a signal level on the SGND

line. This arrangement requires that the external microphone amplifier supplies

the signal on the SGND line to the XMIC line. With this arrangement the differential voltage over R207 caused by the signal in the SGND line is canceled.

There is however a common mode component which is relatively high presented at both the external microphone input pins at the audio codec input, pins

22 and 23. The microphone amplifier has a good common mode rejection ratio

but a slight phase shift in the signals will remove the balance. To compensate

Original 02/97

Page 4–29

Page 30

NHE–5

After Sales

System Module GT8

for this the signal from the external earpiece amplifier positive output, which

also feeds the external audio output from the baseband is feed to the remaining

resistors in the bridge, R219 and R220. This arrangement will attenuate the

common mode signal presented to the microphone amplifier caused by the audio signal in the SGND line. Since the positive output from the audio codec,

XEAR signal introduces a DC signal to the microphone amplifier the DC signal

on the XMIC and SGND lines are blocked by capacitors C218 and C220.

XMIC

R216

R207

Technical Documentation

XEAR

R219

Microphone +

Microphone –

R220R217

DSP

SGND

The external audio output is the XEAR signal on the system connector pin. The

XEAR signal is taken from audio codec N200 pin 6. The output impedance is

increased to 32 ohms by resistors R222 and R214. This resistors prevents the

output amplifier from being short circuited even if the pin at the system connector is short circuited. An ESD capacitor, C225, is connected to ground at the

connection point of R222 and R214. R222 is added to N200 pin 6 output as the

output amplifier can not be loaded directly with the ESD capacitor. The DC voltage at the XEAR output is used to control the mute function of the accessory.

When internal audio is selected the XEAR amplifier in N200 is switched off and

the DC voltage at the output on pin 5 is removed. External audio output level is

adjusted by the variable gain amplifier in the N200 by MCU via the serial control

bus from the ASIC, D151. L206 and C 214 is EMC protection for the XEAR signal at the system connector. This filter also prevents RF signals induced in the

external cables from creating interference in the audio codec output stage.

The DSP used in NHE–5 is the TI 320C541. This is a 16 bit DSP that can use

external and/or internal memory access. The DSP can operate in two modes

microprocessor mode or micro–controller mode. The difference between the

two modes are that in microprocessor mode the DSP boots from external

memory while in the micro–controller mode the DSP boots from internal ROM.

The DSP external memory access is divided into data, program and I/O access.

The type of access is indicated on three control pins that can be used for

memory control.

XEAR

Page 4–30

Original 02/97

Page 31

After Sales

NHE–5

Technical Documentation

The DSP, D152 executes code from the internal ROM. The baseband also provides external memories for the DSP, D410, D411. The DSP is capable of addressing 64 kword of memory. The memory area is divided into a code execution area and a data storage area. The code execution area is located at

address 8000H–FFFFH in the internal ROM. The external memories are arranged in such a way that the DSP can access the external memories both as

data storage and code execution. The memory chip select is taken from the

memory access strobe signal from the DSP. This means that the memory is active during any memory access. The SRAMs are configured in chip select controlled write mode. This means that both the write signal and the output enable

signal are active at the same time, and the actual write occurs at the rising

edge of the chip select signal. This implementation is required since the DSP

supports only one signal for write/read control. The DSP, D152 executes code

from the internal ROM. The baseband also provides external memories for the

DSP, D410, D411. The DSP is capable of addressing 64 kword of memory. The

memory area is divided into a code execution area and a data storage area.

The code execution area is located at address 8000H–FFFFH in the internal

ROM. The external memories are arranged in such a way that the DSP can access the external memories both as data storage and code execution. The

memory chip select is taken from the memory access strobe signal from the

DSP. This means that the memory is active during any memory access. The

memories are connected in such a way that the write control is CE controlled

write. This means that both the write signal and the output enable signal are

active at the same time. This implementation is required since the DSP supports only one signal for write/read control.

System Module GT8

The DSP is operating from the 13 MHz clock. In order to get the required performance the frequency is internally increased by a PLL by a factor of 3. The

PLL requires a settling time of 50 us after that the clock has been supplied before proper operation is established. This settling counter is inside the DSP although the ASIC, D151 contains a counter that will delay the interrupt with a

programmable amount of clock cycles before the interrupt causing the clock to

be switched on is presented to the DSP. The DSP has full control over the clock

supplied to it. When the DSP is to enter the sleep mode the clock is switched

off by setting a bit in the ASIC register. The clock is automatically switched on

when an interrupt is generated.

The DSP also has two synchronous serial channels for communication. One

channel is used for data transmission between the DSP and the audio codec.

This channel is operating at 512 kbits and clock and synchronization signal is

provided by the ASIC, D151. The other channel is used for debugging purposes and uses the same clock and synchronization signals. The DSP has an

interrupt controller servicing four interrupts and one non maskable interrupt,

NMI. The interrupts have fixed priority which can only be changed by changing

the interconnection between the interrupt sources by HW

.

The ASIC contains DSP support functions as modulator,encryption/decryption

using algorithms A5/A51, RF power ramp generation/AGC control, AFC control,

Synthesizer serial interface, frame counters, timer, RFI2 interface, RX and TX

Original 02/97

Page 4–31

Page 32

NHE–5

After Sales

System Module GT8

power control timing. RF power ramp timing/AGC control, AFC control, synthesizer control are timed to the value of the frame counter. This means that data

is loaded into the registers and transferred when the frame counter and the reference value matches. This allows timing of synthesizer control power ramp

and start of TX data to be controlled very precisely.

As the receiver and the transmitter is not operating at the same time the TX

power ramp function is used to control the AGC in the receiver during the reception. This requires the DSP to continuously modify the values in the TX

ramp SRAM to fit the ramp during TX and the AGC value during reception.

DSP ASIC Access

The DSP is accessing the ASIC in the DSP I/O area. 2 wait states are required

for the ASIC access. Some of the DSP registers located in the ASIC are retimed to the internal ASIC clock and requires special handling with respect to

consecutive writing. This means that the same register can not be written again

until a specified time has passed. To cope with this DSP is inserting NOP

instructions to satisfy this requirement.

Technical Documentation

DSP Interrupts

The DSP supports 4 external interrupts. Three interrupts are used. The ASIC,

D151 generates two of the interrupts. One interrupt is generated by RFI2, N450

auxiliary A/D converter. This interrupt is generated when a baseband measurement A/D conversion is completed. The interrupts to the DSP are active low.

INT0 which is the highest priority interrupt is used for data reception from the

receiver and is generated by the ASIC. INT1 signal is used for auxiliary A/D

channel conversions generated by the RFI2. This interrupt is generated by

RFI2 and is a result of measurement requests from the DSP. There are 8 auxiliary channels supported by the RFI2, not all are used in HD842 even if most of

the channels are connected. INT3 is a low priority interrupt generated by the

ASIC timer. The DSP programs the timer value and an interrupt is given when

the timer expires. The interrupt must be active at least 1 ??? DSP clock cycle

as it is sampled on the rising/falling edge by the DSP. All interrupts are active

low.

INT0 is used for the receiver A/D converter in RFI2. The ASIC reads the data

from the receiver path A/D converter in RFI2 at every data available signal activation from the RFI2. After the data transfer when the data is stored in the

ASIC the ASIC generates a receiver interrupt to the DSP using INT1 signal.

The DSP enters the interrupt routine and services the interrupt and reads the

data from the ASIC.

Page 4–32

INT1 signal is used for the auxiliary A/D converter channels in RFI2. These A/D

channels are used for baseband battery voltage monitoring. Two channels are