Page 1

PAMS Technical Documentation

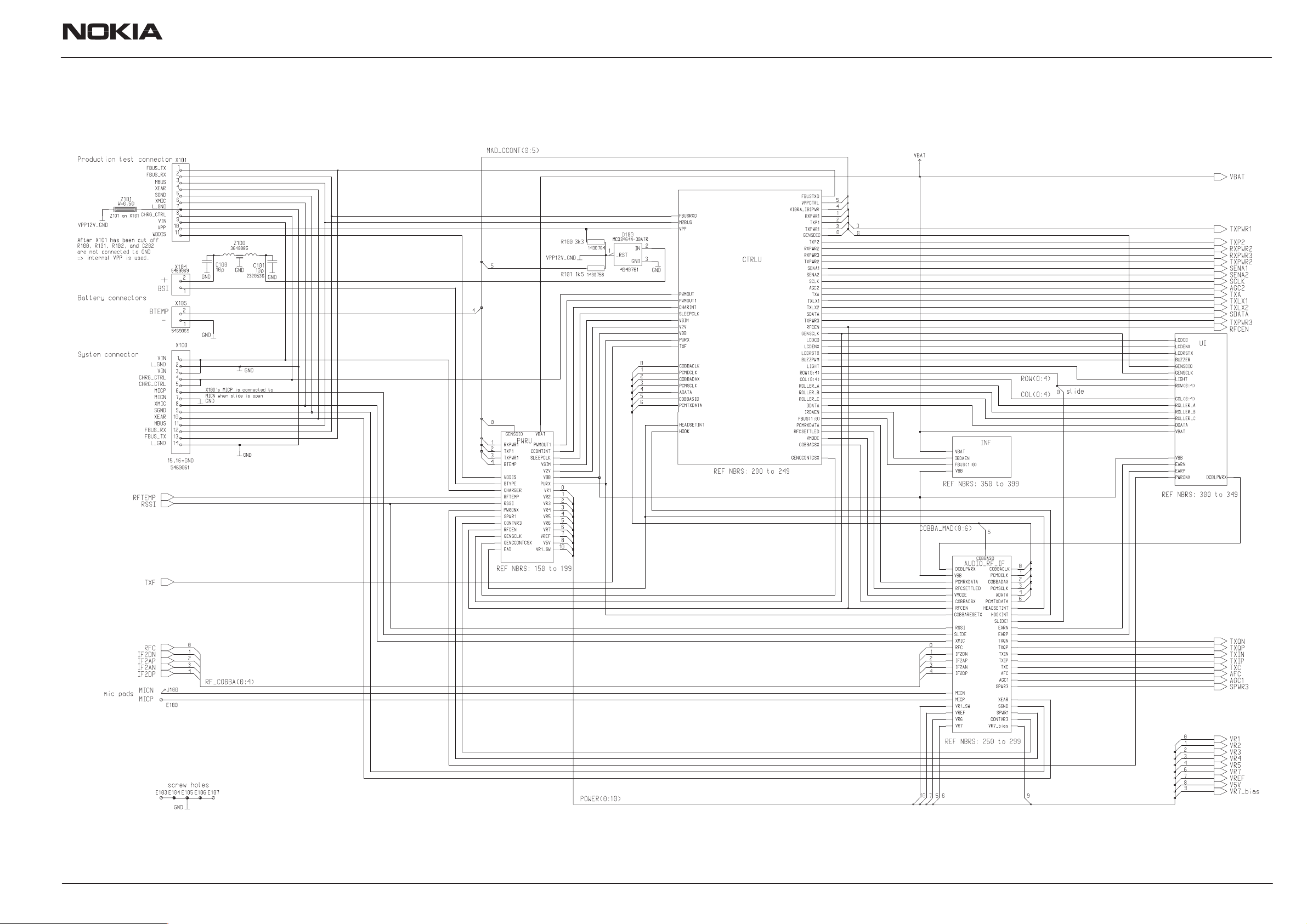

Block Diagram of UT5 (Version 17.4 Edit 40)

NSW-5

System Module UT5U

Issue 1 10/00

Nokia Mobile Phones Ltd.

A–1

Page 2

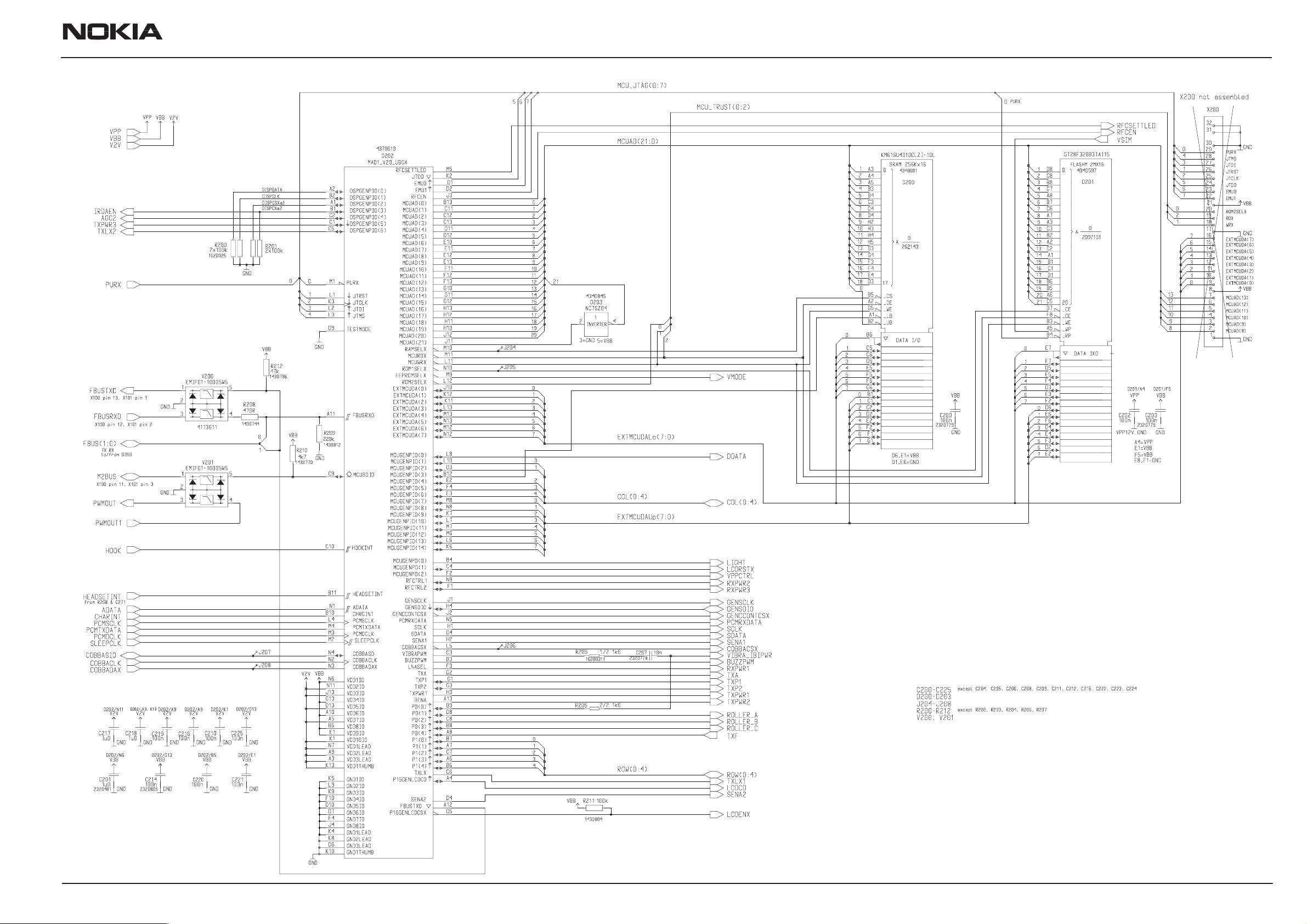

PAMS Technical Documentation

Circuit Diagram of CTRLU Block (Version 17.4 Edit 441)

NSW-5

System Module UT5U

Issue 1 10/00

Nokia Mobile Phones Ltd.

A–2

Page 3

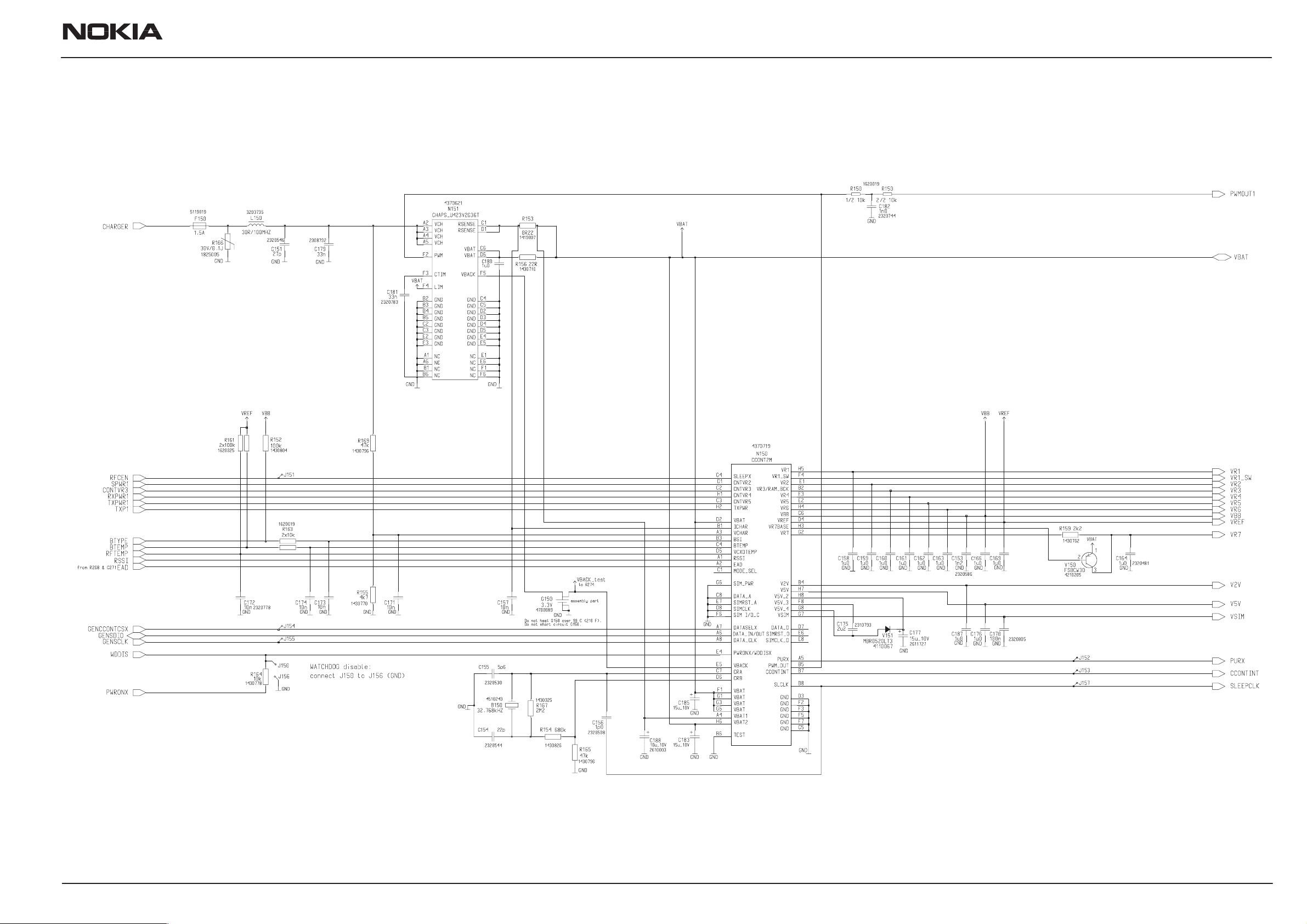

PAMS Technical Documentation

Circuit Diagram of PWRU (Version 17.4 Edit 474 )

NSW-5

System Module UT5U

Issue 1 10/00

Nokia Mobile Phones Ltd.

A–3

Page 4

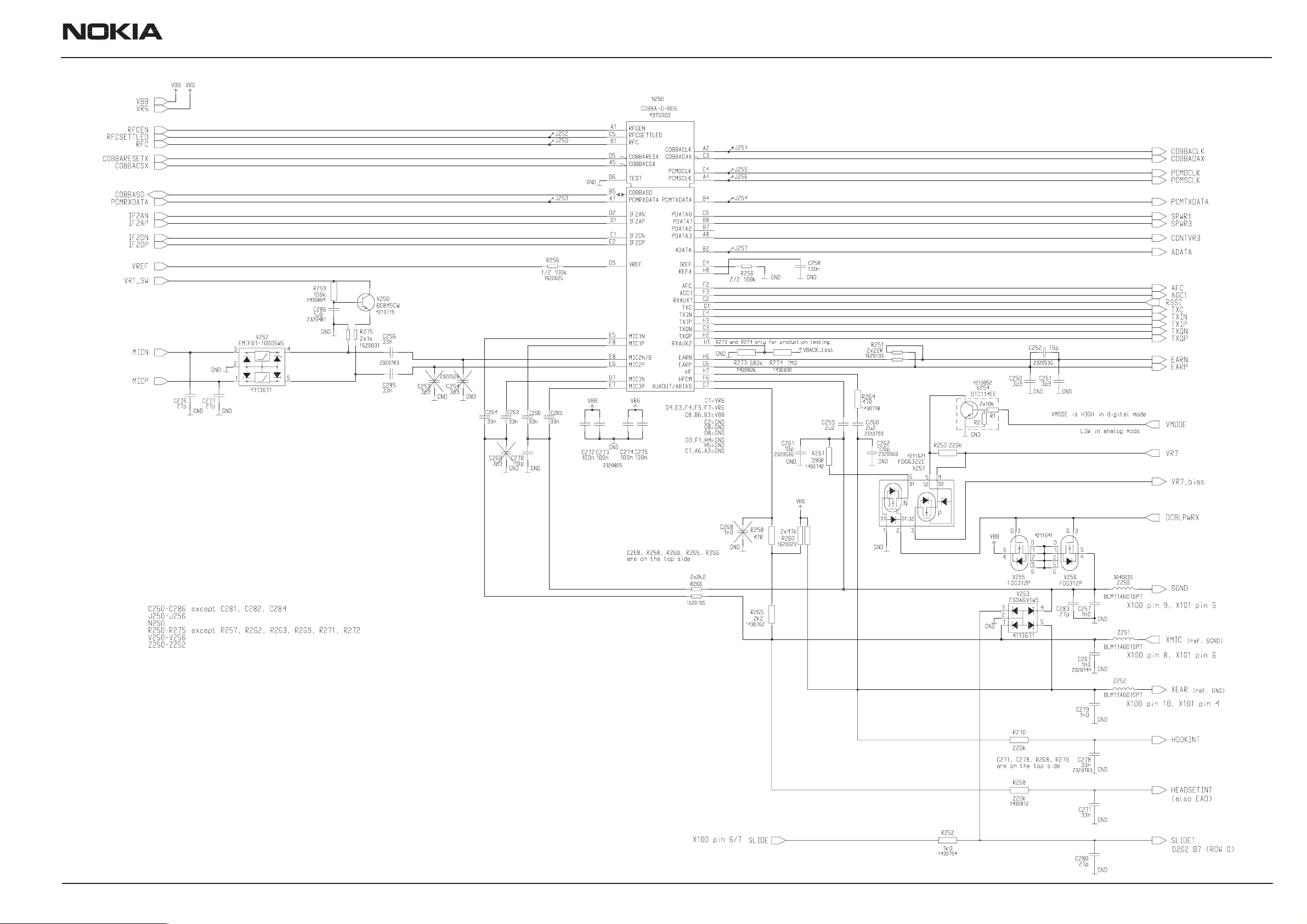

PAMS Technical Documentation

Circuit Diagram of Audio (Version 17.4 Edit 391)

NSW-5

System Module UT5U

Issue 1 10/00

Nokia Mobile Phones Ltd.

A–4

Page 5

PAMS Technical Documentation

Circuit Diagram of Receiver (Version 17.4.0 Edit 39)

NSW-5

System Module UT5U

TP

Issue 1 10/00

Nokia Mobile Phones Ltd.

A–5

Page 6

PAMS Technical Documentation

Circuit Diagram of Synthesiser Block (Version 17.4 Edit 17)

NSW-5

System Module UT5U

TP

TP

TP

Issue 1 10/00

Nokia Mobile Phones Ltd.

A–6

Page 7

PAMS Technical Documentation

Circuit Diagram of Transmitter (Version 13.0 Edit 51)

NSW-5

System Module UT5U

TP

Issue 1 10/00

Nokia Mobile Phones Ltd.

A–7

Page 8

PAMS Technical Documentation

Circuit Diagram of UI (Version 17.4 Edit 179)

NSW-5

System Module UT5U

Issue 1 10/00

Nokia Mobile Phones Ltd.

A–8

Page 9

PAMS Technical Documentation

Circuit Diagram of IR (Version 17.4 Edit 99) and BB_RF interface (Version 17.4 Edit 96)

NSW-5

System Module UT5U

Issue 1 10/00

Nokia Mobile Phones Ltd.

A–9

Page 10

PAMS Technical Documentation

Diagram of Dualband RF (Version 17.4 Edit 10)

NSW-5

System Module UT5U

Issue 1 10/00

Nokia Mobile Phones Ltd.

A–10

Page 11

PAMS Technical Documentation

Layout Diagram of UT5U v.17_4 side 1/2

NSW-5

System Module UT5U

Issue 1 10/00

Nokia Mobile Phones Ltd.

A–11

Page 12

PAMS Technical Documentation

Layout Diagram of UT5U v.17_4 2/2

NSW-5

System Module UT5U

Table 1. Test point description

Test

point

J150 WDDIS/PWRONX X101–CCONT E4 Pulse active 0V,

J156 GND J156–GND Ground for WDDIS

J151 RFCEN MAD J3– D201 A5, CCONT

J152 PURX CCONT A5–MAD M1, D201

J153 CCONTINT CCONT B7–MAD B10 Pulse active 2.8V,

J154 DATASELX MAD J2– CCONT A7 Read/write enable

J155 DATA_CLK CCONT A8– MAD J1

J157 SLEEPCLK CCONT B8– MAD M2 Pulsed DC <

J204 RAMSELX MAD M10– D200 B5

J205 ROM1SELX MAD N10– D201 D7

Name From–to Level Description

Watchdog disable

non–active 2.8V

G4

B4, COBBA D5

Pulse active 2.8V,

non–active 0V

Reset state 0V,

normal state 2.8V

non–active 0V

0.8V/>2.4V

Active state

RESET power up/down

Charger interrupt

32.768 kHz, power on

Issue 1 10/00

J206 COBBACSX MAD L5– COBBA A5 Chip select

J207 COBBASIO MAD N4– COBBA B5 Bidirectional data line

J208 COBBADAX MAD N3– COBBA C3 Data ready flag

J250 RFC EROTUS 25– COBBA B1 0.7 Vpp sinewave 19.44 MHz clock

J251 COBBACLK COBBA A2– MAD N2 Pulsed DC

J252 RFCSETTLED MAD M5– COBBA C5 Pulse active 2.8V,

J253 PCMRXDAT A MAD N5– COBBA A7 Receive data line

J254 PCMTXDAT A COBBA B4– MAD M4 Transmit data line

J255 PCMDCLK COBBA C4– MAD M3 1.08 MHz (digital), 1.215

J256 PCMSCLK COBBA A4– MAD L4 8.0 kHz (digital), 8.1 kHz

J257 ADATA COBBA B2– MAD N1

Nokia Mobile Phones Ltd.

COBBA system clock

(<0.5V/>2.15V)

Active state

non–active 0 V

MHz (analog)

(analog)

A–12

Loading...

Loading...