Page 1

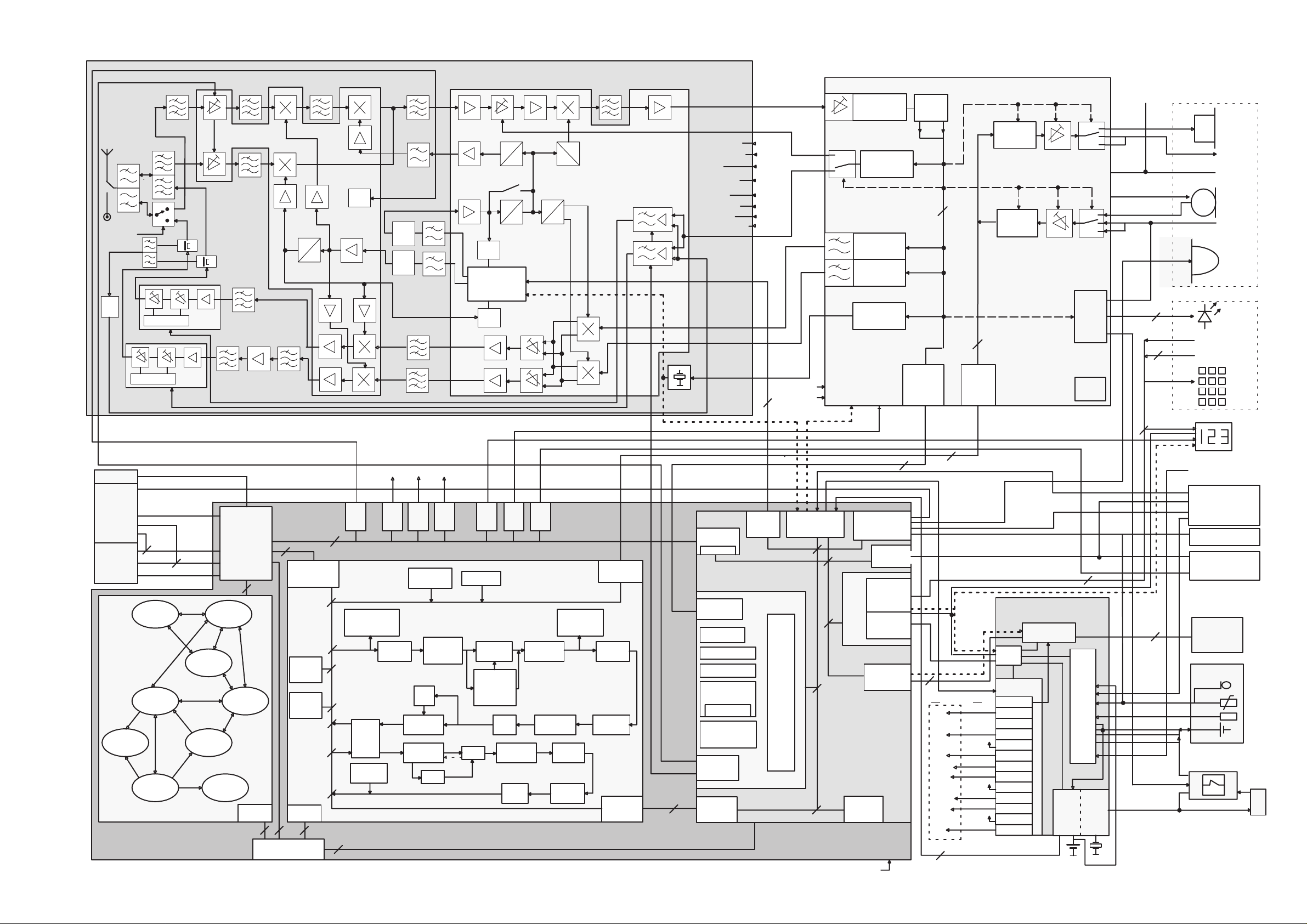

System Block Diagram

1880

..

MHZ

1805

GSM Duplex

GSM/PCN

Diplex

EXT. RF

Vtx

Diplexer

Det

BIAS

BIAS

DET_FB

BAND_SEL

PCN

Rx/Tx

PA

PCN

PA

GSM

Couplers

915

890

1785

..

MHZ

1710

1880

1805

960

935

..

..

..

MHZ

MHZ

MHZ

1031

1006

..

187 MHz

f

f/2

MHZ

CRFU3

Band

Select

2067

..

MHZ

1992

2017

..

MHZ

1942

71 MHz

116 MHz

464 MHz

VHF

VCO

UHF

VCO

2067

..

1942

116 MHz

232 MHz

MHz

PCN Tx

Rx + GSM Tx

16/17

PLL

LOGIC

64/65

NSE–5Schematics/Layouts (V13)

13 MHz

58 MHz

f/

232 MHz

2

f

f

f/2

f

f/2

232 MHz

PCN

f/4

f

116 MHz

GSM

SUMMA

Summa, Crfu3

Summa Charge.

Vctcxo

Crfu3, lo_buff

Rx, Tx, Synth.

Crfu3, Rx

Summa, VCO’s Vsyn_2

Summa, Rx Vrx_2

Crfu3, Summa, Tx

Vref

Vcp

Vxo

Vsyn_1

Vrx_1

Vtx

SYNTH

–ENA1

–CLK

–DATA

RXINP/

RXINN

RXC

TXC

TXIP/

TXIN

TXQP/

TXQN

AFC

RX

ADC 12bit

TxC/AGC

DAC10bit

TXI

DAC 8bit

TXQ

DAC 8bit

AFC

DAC 1 1bit

I+

modulato

Q

r

541.6

kS/S

1.083kS/S

1.083kS/S

1

kS/S

RX

8kS/S

AUDIO

DAC 13bit

TX

8kS/S

AUDIO

ADC 13bit

COBBA _GJP

st 64 BGA

PDATA

register

13MHz

VCTCXO

RFCLK

Vcobba

Vbb

COBBACLK

13MHz

COBBA

RESET

SERIEL

RF/CTR

IF

SERRFI(3:0) PCM(3:0)

SERIAL

AUDIO

IF

IMEI–

register

LCDRSTX

DLR–3 Supply

(MCUGENIO0)

Headset

mic bias

Headset

2

3

UI

AUDIO

KEYBOARD

slide position

roller input

Earpiece

XEar

SGnd

slide

MIC

XMIC

Buzzer

Keyb.–

lights

KEYB.

FrACtrl

Vpp ctr.

ROM

(FLASH)

2M*16

SRAM

512k*8

MCU

HW

HW

DRIVERS

MCUDA

(15:8)

ROM1SELX

MCUDA

RAMSELX

USER

INTERFACE

DEV

DEVICE

CONTROL

LOCAL

NETWORK

UI

LN

(7:0)

MCUAD

(21:0)

MCUWRX

MCURDX

DDI

DATA DEVICE

INTERFACE

LOC

LOCALS

CONTROL

BUSC

CS

CELLULAR

SYSTEM

CONTROL

OS

OPERATING

SYSTEM

MAD2PR1

ti 144 BGA

MCUGENIO3

DSP

DSP

JTAG

API RAM

ROM

68kx16

RAM

10kx16

JTAG

TEST IF

2kx16

DSP

GEN

Out4

RSS–

Measurement

and AGC

8kHz

HF

AEC

8kHz

Transmit

Control

NC NC

NC

DSP

RX

GEN

PwrTXPwr

Out2

T one–

Generator

RX–

Filtering

Phase–

Demodu–

lation

RX–

DTX

Speech

Decoding

Speech

Encoding

VAD

Transmit–burst every 4.615 ms

Synth

Pwr

Sidetone

Matched

Filter

Channel

Estimation

Symbol

Sync.

DTX

DSP

GEN

Out5

BFI

CRC

Convol.

Encoding

Burst

Build

DSP

GEN

Out3

DSP

Bit–

Detection

Convol.

Decoding

En–

cryption

SNR–

Calculation

and AFC

Inter–

leaving

PCMSIO

De–

cryption

Deinter–

leaving

DSP IO

TXP

MCU–If

boot rom

COBBA–

IF

RX RAM

TXC RAM

TXC Ramp

GMSK–

modulator

TXIQ RAM

Offset

Counter &

Comparator

FrACtrl

TXP

DSP IF

SCU

MFI

FSM

MFI

CTSI

PUP

ACC IF

LCD–

driver IF

Keyb. IF

CCONT

UIF

IF

SIM IF

SYSTEM

LOGIC

Coder

Vbb

HOOKDET, HEADDET

VCXOPWR

ROW(5:0), Col(4:0), LCDCS,

ROLLER_A, ROLLER_B, ROLLER_C

GENSCLK

GENSDIO

SIMCard

CLK

BUZZER

MBUS

VIBRA

FBUS Rx/Tx

CCONT

st 64 BGA

SIO

CCONTCSX

Voltage

RF

Vref

Vcp

Vxo

Vsyn_1

Vrx_1

Vsyn_2

Vrx_2

Vtx

SLEEPCLK, PURX, CCONTINT

BB

Vbb

Ram_

bck

Vcobba

Regulators

VSIM 3/5

Vref

V2V

V5V

VBB

VR1

VR1_SW

VR2

VR3

VR4

VR5

VR6

VR7

IRON

SIM IF

back–up

battery

RTC

Mux/

ADC

RSSI

EAD

BTEMP

BSI

VBAT

ICHAR

VCHAR

VCXOT

PWM

OSC

32

kHz

wd

Display/Driver

Temp.–sense (LCD)

SYSTEM

CONNECTOR

INTERN

VIBRA

IR–MODULE

TFDU4100

5

LCD–

Temp.

CharLim

PWM

HD945

SIM

CARD

READER

BATTERY

VIBRA

BTEMP

BSI

CHAPS SO16

CHARGER CONTROL

Block Diagram

Draft v. 2.1+ 13

Aug 98

CHARG

Draft 05

A –1Page

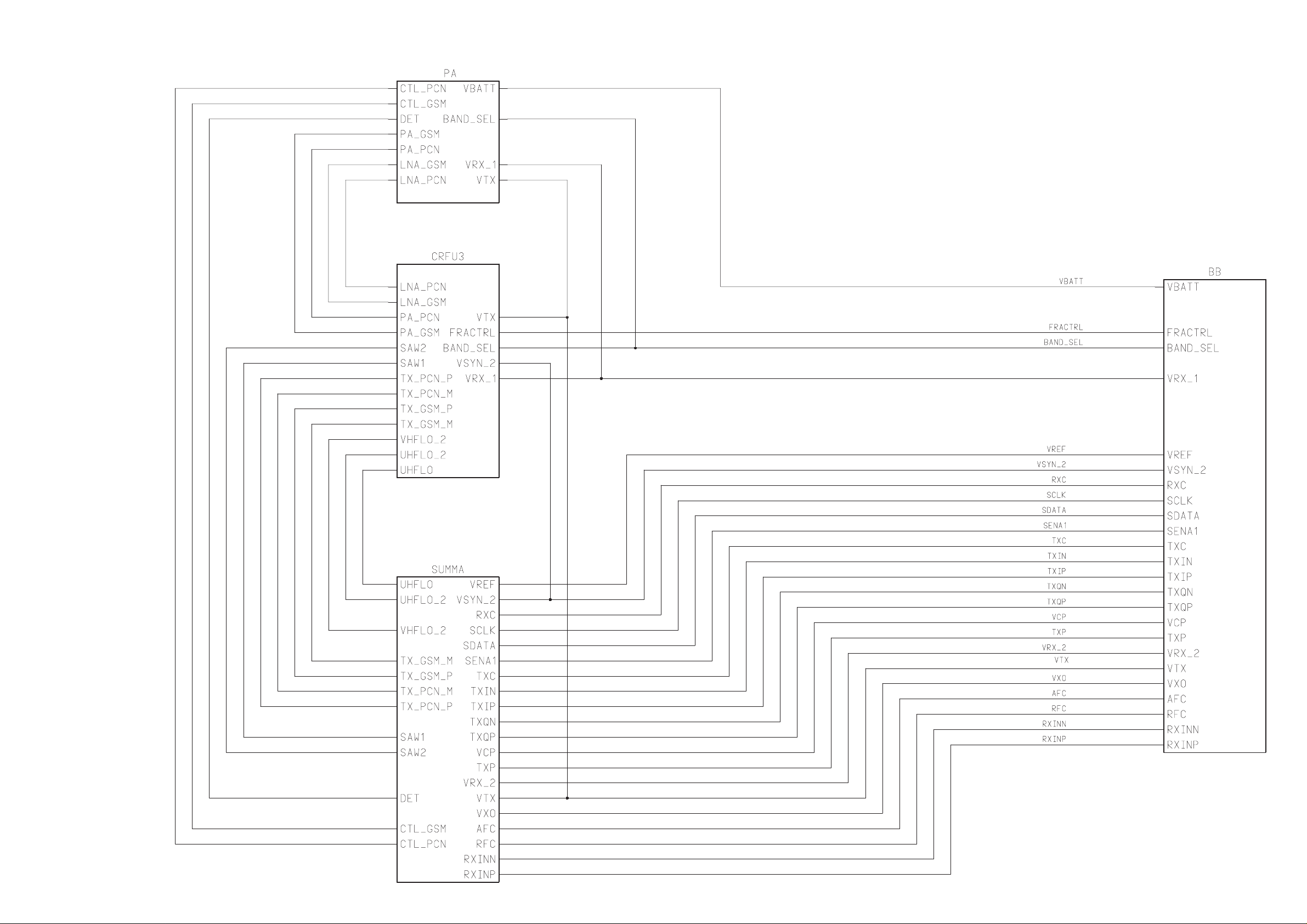

Page 2

RF and BB Interconnections

NSE–5Schematics/Layouts (V13)

Draft 05

A –2Page

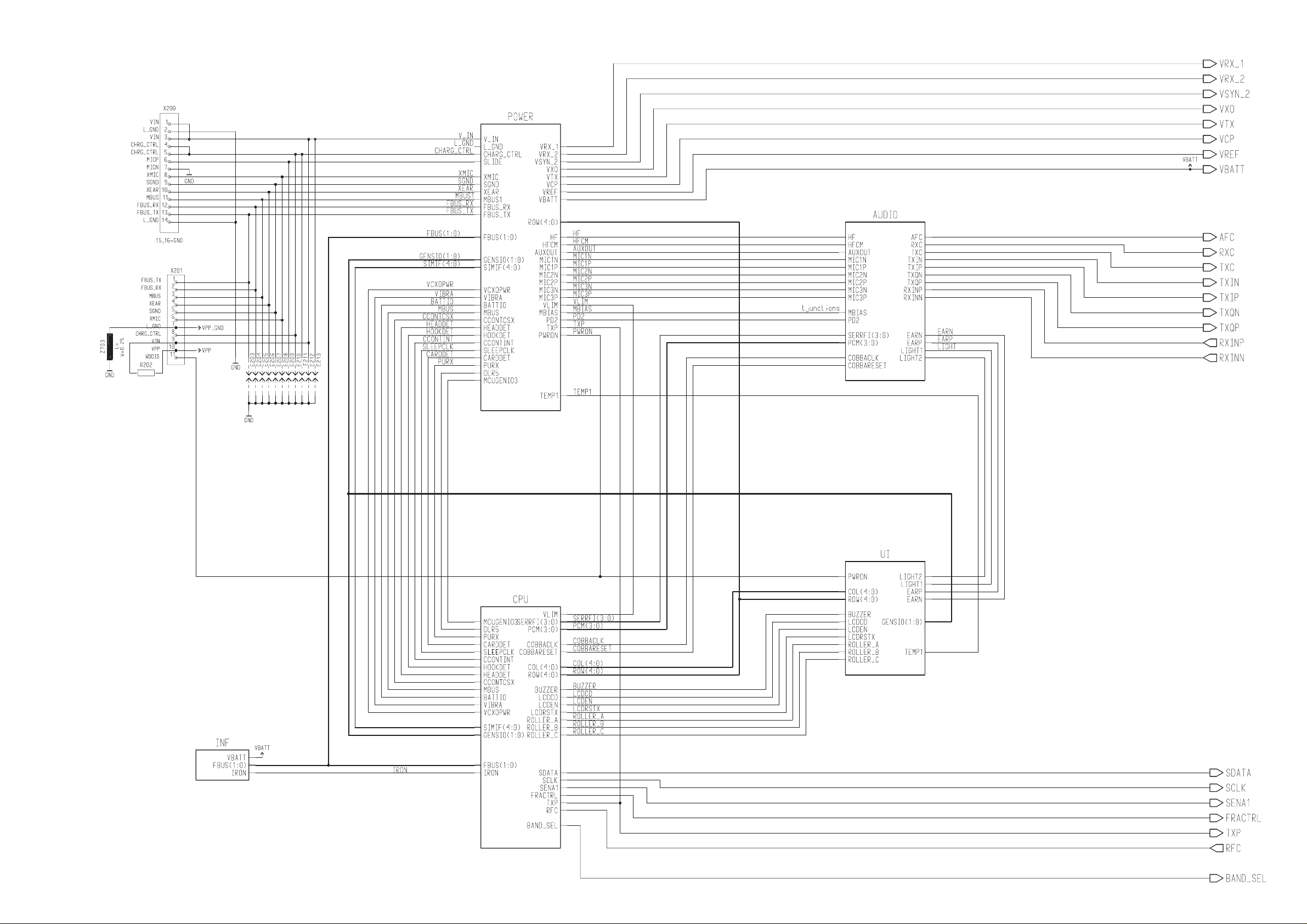

Page 3

Baseband Block

NSE–5Schematics/Layouts (V13)

Draft 05

A –3Page

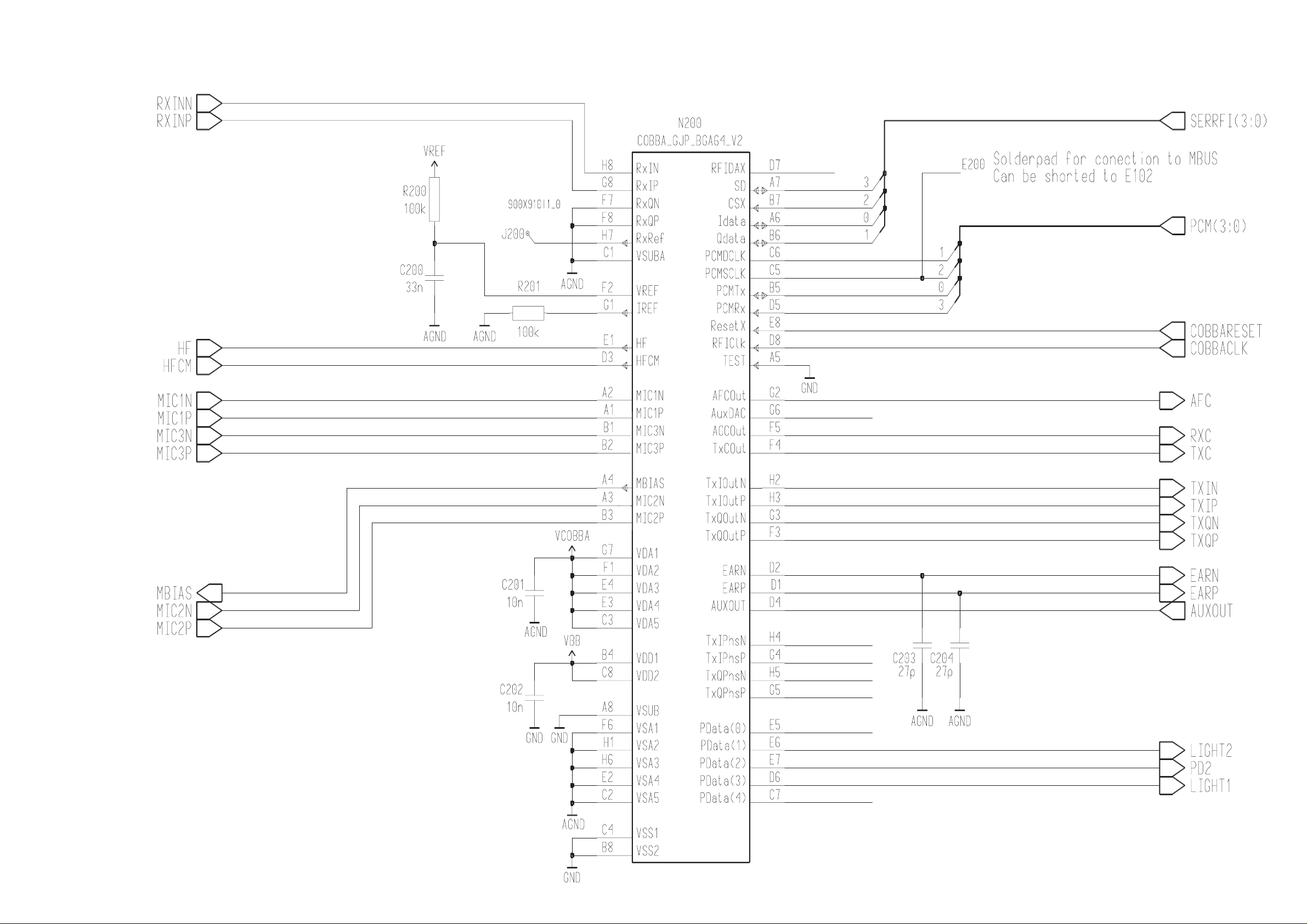

Page 4

Audio

NSE–5Schematics/Layouts (V13)

Draft 05

A –4Page

Page 5

CPU

NSE–5Schematics/Layouts (V13)

Draft 05

A –5Page

Page 6

Infrared Module

NSE–5Schematics/Layouts (V13)

Draft 05

A –6Page

Page 7

Power

NSE–5Schematics/Layouts (V13)

Draft 05

A –7Page

Page 8

User Interface

End 31

NSE–5Schematics/Layouts (V13)

2Send

0

5Soft l e ft

## 84Soft ri ght

69

7*

Draft 05

A –8Page

Page 9

CRFU3

NSE–5Schematics/Layouts (V13)

Draft 05

A –9Page

Page 10

PA

NSE–5Schematics/Layouts (V13)

Draft 05

A –10Page

Page 11

SUMMA

NSE–5Schematics/Layouts (V13)

Draft 05

A –1 1Page

Page 12

Component Layout – Top

NSE–5Schematics/Layouts (V13)

Draft 05

A –12Page

Page 13

Component Layout – Bottom

NSE–5Schematics/Layouts (V13)

Draft 05

A –13Page

Loading...

Loading...