Page 1

Preliminary User’s Manual

V850ES/HG2

32-Bit Single-Chip Microcontrollers

Hardware

µ

PD70F3706

µ

PD70F3707

Document No. U17718EJ1V0UD00 (1st edition)

Date Published December 2005 N CP(K)

Printed in Japan

2005

Page 2

[MEMO]

2

Preliminary User’s Manual U17718EJ1V0UD

Page 3

NOTES FOR CMOS DEVICES

1

VOLTAGE APPLICATION WAVEFORM AT INPUT PIN

Waveform distortion due to input noise or a reflected wave may cause malfunction. If the input of the

CMOS device stays in the area between V

malfunction. Take care to prevent chattering noise from entering the device when the input level is fixed,

and also in the transition period when the input level passes through the area between V

V

IH

(MIN).

HANDLING OF UNUSED INPUT PINS

2

Unconnected CMOS device inputs can be cause of malfunction. If an input pin is unconnected, it is

possible that an internal input level may be generated due to noise, etc., causing malfunction. CMOS

devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed

high or low by using pull-up or pull-down circuitry. Each unused pin should be connected to V

via a resistor if there is a possibility that it will be an output pin. All handling related to unused pins must

be judged separately for each device and according to related specifications governing the device.

3

PRECAUTION AGAINST ESD

A strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and

ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as

much as possible, and quickly dissipate it when it has occurred. Environmental control must be

adequate. When it is dry, a humidifier should be used. It is recommended to avoid using insulators that

easily build up static electricity. Semiconductor devices must be stored and transported in an anti-static

container, static shielding bag or conductive material. All test and measurement tools including work

benches and floors should be grounded. The operator should be grounded using a wrist strap.

Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for

PW boards with mounted semiconductor devices.

IL

(MAX) and VIH (MIN) due to noise, etc., the device may

IL

(MAX) and

DD

or GND

4

STATUS BEFORE INITIALIZATION

Power-on does not necessarily define the initial status of a MOS device. Immediately after the power

source is turned ON, devices with reset functions have not yet been initialized. Hence, power-on does

not guarantee output pin levels, I/O settings or contents of registers. A device is not initialized until the

reset signal is received. A reset operation must be executed immediately after power-on for devices

with reset functions.

5

POWER ON/OFF SEQUENCE

In the case of a device that uses different power supplies for the internal operation and external

interface, as a rule, switch on the external power supply after switching on the internal power supply.

When switching the power supply off, as a rule, switch off the external power supply and then the

internal power supply. Use of the reverse power on/off sequences may result in the application of an

overvoltage to the internal elements of the device, causing malfunction and degradation of internal

elements due to the passage of an abnormal current.

The correct power on/off sequence must be judged separately for each device and according to related

specifications governing the device.

6

INPUT OF SIGNAL DURING POWER OFF STATE

Do not input signals or an I/O pull-up power supply while the device is not powered. The current

injection that results from input of such a signal or I/O pull-up power supply may cause malfunction and

the abnormal current that passes in the device at this time may cause degradation of internal elements.

Input of signals during the power off state must be judged separately for each device and according to

related specifications governing the device.

Preliminary User’s Manual U17718EJ1V0UD

3

Page 4

MINICUBE is a registered trademark of NEC Electronics Corporation in Japan and Germany.

•

The information contained in this document is being issued in advance of the production cycle for the

product. The parameters for the product may change before final production or NEC Electronics

Corporation, at its own discretion, may withdraw the product prior to its production.

•

Not all products and/or types are available in every country. Please check with an NEC Electronics sales

representative for availability and additional information.

No part of this document may be copied or reproduced in any form or by any means without the prior written consent

•

of NEC Electronics. NEC Electronics assumes no responsibility for any errors that may appear in this document.

NEC Electronics does not assume any liability for infringement of patents, copyrights or other intellectual property

•

rights of third parties by or arising from the use of NEC Electronics products listed in this document or any other

liability arising from the use of such products. No license, express, implied or otherwise, is granted under any

patents, copyrights or other intellectual property rights of NEC Electronics or others.

Descriptions of circuits, software and other related information in this document are provided for illustrative purposes

•

in semiconductor product operation and application examples. The incorporation of these circuits, software and

information in the design of a customer's equipment shall be done under the full responsibility of the customer. NEC

Electronics assumes no responsibility for any losses incurred by customers or third parties arising from the use of

these circuits, software and information.

While NEC Electronics endeavors to enhance the quality, reliability and safety of NEC Electronics products,

•

customers agree and acknowledge that the possibility of defects thereof cannot be eliminated entirely. To minimize

risks of damage to property or injury (including death) to persons arising from defects in NEC Electronics products,

customers must incorporate sufficient safety measures in their design, such as redundancy, fire-containment and

anti-failure features.

NEC Electronics products are classified into the following three quality grades: "Standard", "Special" and "Specific".

•

The "Specific" quality grade applies only to NEC Electronics products developed based on a customer-designated

"quality assurance program" for a specific application. The recommended applications of an NEC Electronics

products depend on its quality grade, as indicated below. Customers must check the quality grade of each NEC

Electronics product before using it in a particular application.

"Standard":

"Special":

"Specific":

Computers, office equipment, communications equipment, test and measurement equipment, audio and

visual equipment, home electronic appliances, machine tools, personal electronic equipment and

industrial robots.

Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster

systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life

support).

Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support

systems and medical equipment for life support, etc.

The quality grade of NEC Electronics products is "Standard" unless otherwise expressly specified in NEC

Electronics data sheets or data books, etc. If customers wish to use NEC Electronics products in applications

not intended by NEC Electronics, they must contact an NEC Electronics sales representative in advance to

determine NEC Electronics' willingness to support a given application.

(Note)

(1)

"NEC Electronics" as used in this statement means NEC Electronics Corporation and also includes its

majority-owned subsidiaries.

(2)

"NEC Electronics products" means any product developed or manufactured by or for NEC Electronics (as

defined above).

M5 D 02 . 11-1

4

Preliminary User’s Manual U17718EJ1V0UD

Page 5

PREFACE

Readers This manual is intended for users who wish to understand the functions of the

V850ES/HG2 and design application systems using the V850ES/HG2.

Purpose This manual is intended to give users an understanding of the hardware functions of

the V850ES/HG2 shown in the Organization below.

Organization This manual is divided into two parts: Hardware (this manual) and Architecture

(V850ES Architecture User’s Manual).

Hardware Architecture

• Pin functions • Data types

• CPU function • Register set

• On-chip peripheral functions • Instruction format and instruction set

• Flash memory programming • Interrupts and exceptions

• Electrical specifications (target) • Pipeline operation

How to Read This Manual It is assumed that the readers of this manual have general knowledge in the fields of

electrical engineering, logic circuits, and microcontrollers.

To understand the overall functions of the V850ES/HG2

→ Read this manual according to the CONTENTS.

To find the details of a register where the name is known

→ Use APPENDIX A REGISTER INDEX.

To understand the details of an instruction function

→ Refer to the V850ES Architecture User’s Manual available separately.

To know the electrical specifications of the V850ES/HG2

→ See CHAPTER 26 ELECTRICAL SPECIFICATIONS (TARGET).

Register format

→ The name of the bit whose number is in angle brackets (<>) in the figure of the

register format of each register is defined as a reserved word in the device file.

The “yyy bit of the xxx register” is described as the “xxx.yyy bit” in this manual. Note

with caution that if “xxx.yyy” is described as is in a program, however, the

compiler/assembler cannot recognize it correctly.

Preliminary User’s Manual U17718EJ1V0UD

5

Page 6

Conventions Data significance: Higher digits on the left and lower digits on the right

Active low representation: xxx (overscore over pin or signal name)

Memory map address: Higher addresses on the top and lower addresses on

the bottom

Note: Footnote for item marked with Note in the text

Caution: Information requiring particular attention

Remark: Supplementary information

Numeric representation: Binary ... xxxx or xxxxB

Decimal ... xxxx

Hexadecimal ... xxxxH

Prefix indicating power of 2

(address space, memory

capacity): K (kilo): 2

M (mega): 2

G (giga): 2

10

= 1,024

20

= 1,0242

30

= 1,0243

6

Preliminary User’s Manual U17718EJ1V0UD

Page 7

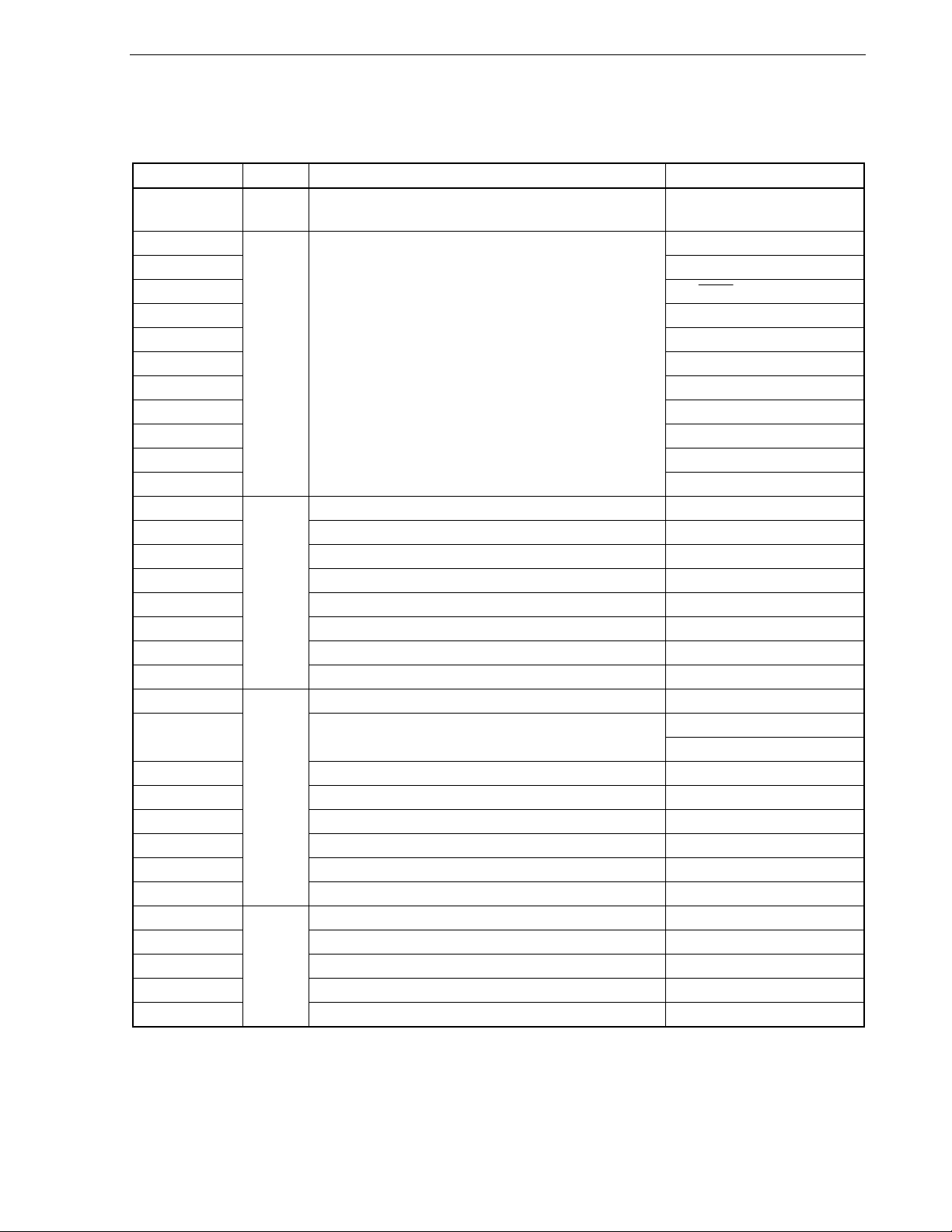

Related Documents The related documents indicated in this publication may include preliminary versions.

However, preliminary versions are not marked as such.

Documents related to V850ES/HG2

Document Name Document No.

V850ES Architecture User’s Manual U15943E

V850ES/HG2 Hardware User’s Manual This manual

Documents related to development tools

Document Name Document No.

CA850 Ver. 3.00 C Compiler Package

PM+ Ver. 6.00 Project Manager U17178E

ID850QB Ver. 3.10 Integrated Debugger Operation U17435E

SM850 Ver. 2.50 System Simulator Operation U16218E

SM850 Ver. 2.00 or Later System Simulator External Part User Open

RX850 Ver. 3.20 or Later Real-Time OS

RX850 Pro Ver. 3.20 Real-Time OS

AZ850 Ver. 3.30 System Performance Analyzer U17423E

PG-FP4 Flash Memory Programmer U15260E

Operation U17293E

C Language U17291E

Assembly Language U17292E

Link Directives U17294E

U14873E

Interface Specification

Basics U13430E

Installation U17419E

Technical U13431E

Task Debugger U17420E

Basics U13773E

Installation U17421E

Technical U13772E

Task Debugger U17422E

Preliminary User’s Manual U17718EJ1V0UD

7

Page 8

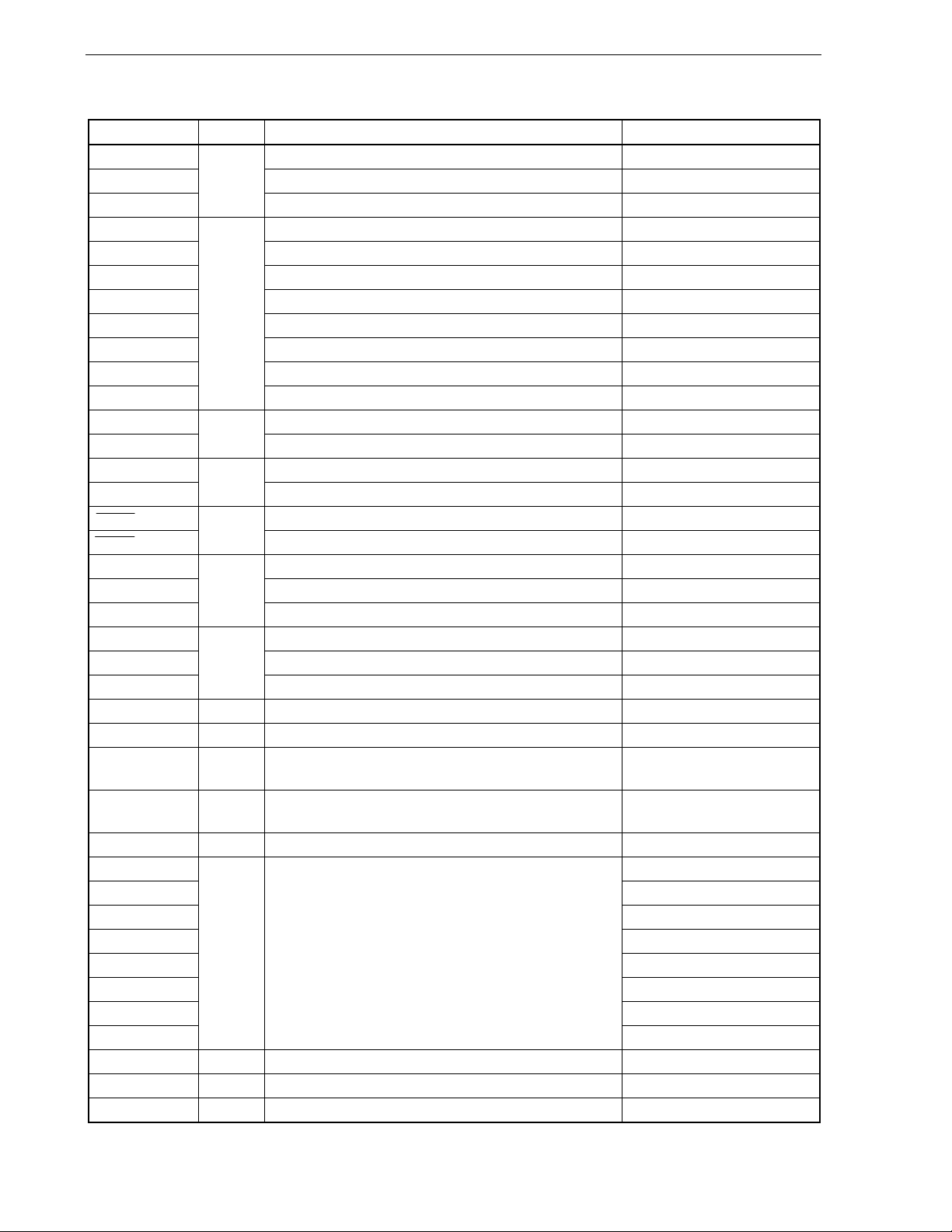

CONTENTS

CHAPTER 1 INTRODUCTION..................................................................................................................16

1.1 General .....................................................................................................................................16

1.2 Features....................................................................................................................................18

1.3 Application Fields....................................................................................................................18

1.4 Ordering Information...............................................................................................................19

1.5 Pin Configuration (Top View) .................................................................................................20

1.6 Function Block Configuration ................................................................................................22

1.6.1 Internal block diagram................................................................................................................ 22

1.6.2 Internal units ..............................................................................................................................23

CHAPTER 2 PIN FUNCTIONS ................................................................................................................25

2.1 Pin Function List......................................................................................................................25

2.2 Description of Pin Functions..................................................................................................30

2.3 Pin I/O Circuit Types and Recommended Connection of Unused Pins.............................37

2.4 Pin I/O Circuits .........................................................................................................................39

2.5 Cautions ...................................................................................................................................40

CHAPTER 3 CPU FUNCTION .................................................................................................................41

3.1 Features....................................................................................................................................41

3.2 CPU Register Set .....................................................................................................................42

3.2.1 Program register set ..................................................................................................................43

3.2.2 System register set ....................................................................................................................44

3.3 Operation Modes .....................................................................................................................50

3.3.1 Specifying operation mode ........................................................................................................50

3.4 Address Space.........................................................................................................................51

3.4.1 CPU address space ...................................................................................................................51

3.4.2 Wraparound of CPU address space ..........................................................................................52

3.4.3 Memory map .............................................................................................................................. 53

3.4.4 Areas .........................................................................................................................................55

3.4.5 Recommended use of address space........................................................................................57

3.4.6 Peripheral I/O registers ..............................................................................................................60

3.4.7 Special registers ........................................................................................................................69

3.4.8 Cautions..................................................................................................................................... 73

CHAPTER 4 PORT FUNCTIONS ............................................................................................................76

4.1 Features....................................................................................................................................76

4.2 Basic Configuration of Ports..................................................................................................76

4.3 Port Functions .........................................................................................................................78

4.3.1 Operation of port function ..........................................................................................................78

4.3.2 Notes on setting port pins ..........................................................................................................79

4.3.3 Port 0 .........................................................................................................................................80

4.3.4 Port 1 .........................................................................................................................................86

4.3.5 Port 3 .........................................................................................................................................90

4.3.6 Port 4 .........................................................................................................................................97

4.3.7 Port 5 .......................................................................................................................................100

8

Preliminary User’s Manual U17718EJ1V0UD

Page 9

4.3.8 Port 7 ....................................................................................................................................... 106

4.3.9 Port 9 ....................................................................................................................................... 108

4.3.10 Port CM ................................................................................................................................... 117

4.3.11 Port CS.................................................................................................................................... 119

4.3.12 Port CT .................................................................................................................................... 121

4.3.13 Port DL .................................................................................................................................... 123

4.3.14 Port pins that function alternately as on-chip debug function................................................... 125

4.3.15 Register settings to use port pins as alternate-function pins.................................................... 126

4.4 Block Diagrams of Port.........................................................................................................131

4.5 Cautions .................................................................................................................................157

4.5.1 Cautions on setting port pins ................................................................................................... 157

CHAPTER 5 CLOCK GENERATION FUNCTION ...............................................................................158

5.1 Overview.................................................................................................................................158

5.2 Configuration.........................................................................................................................159

5.3 Registers ................................................................................................................................161

5.4 Operation................................................................................................................................166

5.4.1 Operation of each clock ........................................................................................................... 166

5.4.2 Clock output function ............................................................................................................... 166

5.5 PLL Function..........................................................................................................................167

5.5.1 Overview ................................................................................................................................. 167

5.5.2 Registers ................................................................................................................................. 167

5.5.3 Usage ......................................................................................................................................171

CHAPTER 6 16-BIT TIMER/EVENT COUNTER P (TMP) .................................................................172

6.1 Overview.................................................................................................................................172

6.2 Functions ...............................................................................................................................172

6.3 Configuration.........................................................................................................................173

6.4 Registers ................................................................................................................................175

6.5 Operation................................................................................................................................189

6.5.1 Interval timer mode (TPnMD2 to TPnMD0 bits = 000) ............................................................. 190

6.5.2 External event count mode (TPnMD2 to TPnMD0 bits = 001) ................................................. 200

6.5.3 External trigger pulse output mode (TPnMD2 to TPnMD0 bits = 010) ..................................... 208

6.5.4 One-shot pulse output mode (TPnMD2 to TPnMD0 bits = 011) .............................................. 220

6.5.5 PWM output mode (TPnMD2 to TPnMD0 bits = 100).............................................................. 227

6.5.6 Free-running timer mode (TPnMD2 to TPnMD0 bits = 101) .................................................... 236

6.5.7 Pulse width measurement mode (TPnMD2 to TPnMD0 bits = 110) ........................................ 253

6.5.8 Timer output operations........................................................................................................... 259

6.6 Timer Tuned Operation Function ........................................................................................260

6.7 Selector Function ..................................................................................................................264

6.8 Cautions .................................................................................................................................266

CHAPTER 7 16-BIT TIMER/EVENT COUNTER Q (TMQ) ................................................................267

7.1 Overview.................................................................................................................................267

7.2 Functions ...............................................................................................................................267

7.3 Configuration.........................................................................................................................268

7.4 Registers ................................................................................................................................271

7.5 Operation................................................................................................................................289

Preliminary User’s Manual U17718EJ1V0UD

9

Page 10

7.5.1 Interval timer mode (TQnMD2 to TQnMD0 bits = 000) ............................................................290

7.5.2 External event count mode (TQnMD2 to TQnMD0 bits = 001) ................................................299

7.5.3 External trigger pulse output mode (TQnMD2 to TQnMD0 bits = 010) ....................................308

7.5.4 One-shot pulse output mode (TQnMD2 to TQnMD0 bits = 011).............................................. 321

7.5.5 PWM output mode (TQnMD2 to TQnMD0 bits = 100) .............................................................330

7.5.6 Free-running timer mode (TQnMD2 to TQnMD0 bits = 101) ...................................................341

7.5.7 Pulse width measurement mode (TQnMD2 to TQnMD0 bits = 110) ........................................ 361

7.5.8 Triangular wave PWM mode (TQnMD2 to TQnMD0 = 111) ....................................................367

7.5.9 Timer output operations ...........................................................................................................368

7.6 Timer Tuned Operation Function........................................................................................ 369

7.7 Cautions ................................................................................................................................ 373

CHAPTER 8 16-BIT INTERVAL TIMER M (TMM) ............................................................................ 374

8.1 Overview................................................................................................................................ 374

8.2 Configuration ........................................................................................................................ 375

8.3 Register ................................................................................................................................. 376

8.4 Operation............................................................................................................................... 377

8.4.1 Interval timer mode ..................................................................................................................377

8.4.2 Cautions................................................................................................................................... 381

CHAPTER 9 WATCH TIMER FUNCTIONS ........................................................................................ 382

9.1 Functions............................................................................................................................... 382

9.2 Configuration ........................................................................................................................ 383

9.3 Registers ............................................................................................................................... 385

9.4 Operation............................................................................................................................... 389

9.4.1 Operation as watch timer .........................................................................................................389

9.4.2 Operation as interval timer ....................................................................................................... 390

9.4.3 Cautions................................................................................................................................... 391

CHAPTER 10 FUNCTIONS OF WATCHDOG TIMER 2 ................................................................... 392

10.1 Functions............................................................................................................................... 392

10.2 Configuration ........................................................................................................................ 393

10.3 Registers ............................................................................................................................... 394

10.4 Operation............................................................................................................................... 397

CHAPTER 11 A/D CONVERTER ......................................................................................................... 398

11.1 Overview................................................................................................................................ 398

11.2 Functions............................................................................................................................... 398

11.3 Configuration ........................................................................................................................ 399

11.4 Registers ............................................................................................................................... 402

11.5 Operation............................................................................................................................... 410

11.5.1 Basic operation ........................................................................................................................ 410

11.5.2 Trigger mode ...........................................................................................................................411

11.5.3 Operation mode ....................................................................................................................... 413

11.5.4 Power-fail compare mode ........................................................................................................ 417

11.6 Cautions ................................................................................................................................ 422

11.7 How to Read A/D Converter Characteristics Table........................................................... 426

10

Preliminary User’s Manual U17718EJ1V0UD

Page 11

CHAPTER 12 ASYNCHRONOUS SERIAL INTERFACE A (UARTA) ..............................................430

12.1 Features..................................................................................................................................430

12.2 Configuration.........................................................................................................................431

12.3 Registers ................................................................................................................................433

12.4 Interrupt Request Signals.....................................................................................................439

12.5 Operation................................................................................................................................440

12.5.1 Data format.............................................................................................................................. 440

12.5.2 SBF transmission/reception format.......................................................................................... 442

12.5.3 SBF transmission .................................................................................................................... 444

12.5.4 SBF reception.......................................................................................................................... 445

12.5.5 UART transmission.................................................................................................................. 446

12.5.6 Continuous transmission procedure ........................................................................................447

12.5.7 UART reception....................................................................................................................... 449

12.5.8 Reception errors ...................................................................................................................... 450

12.5.9 Parity types and operations ..................................................................................................... 452

12.5.10 Receive data noise filter ..........................................................................................................453

12.6 Dedicated Baud Rate Generator .......................................................................................... 454

12.7 Cautions .................................................................................................................................462

CHAPTER 13 3-WIRE VARIABLE-LENGTH SERIAL I/O (CSIB) ....................................................463

13.1 Features..................................................................................................................................463

13.2 Configuration.........................................................................................................................464

13.3 Registers ................................................................................................................................466

13.4 Interrupt Request Signals.....................................................................................................473

13.5 Operation................................................................................................................................474

13.5.1 Single transfer mode (master mode, transmission/reception mode)........................................ 474

13.5.2 Single transfer mode (master mode, reception mode)............................................................. 475

13.5.3 Continuous mode (master mode, transmission/reception mode)............................................. 476

13.5.4 Continuous mode (master mode, reception mode).................................................................. 477

13.5.5 Continuous reception mode (error).......................................................................................... 478

13.5.6 Continuous mode (slave mode, transmission/reception mode) ............................................... 479

13.5.7 Continuous mode (slave mode, reception mode) ....................................................................480

13.5.8 Clock timing............................................................................................................................. 481

13.6 Output Pin Status with Operation Disabled .......................................................................483

13.7 Operation Flow ......................................................................................................................484

13.8 Baud Rate Generator ............................................................................................................490

13.8.1 Baud rate generation ............................................................................................................... 491

13.9 Cautions .................................................................................................................................492

CHAPTER 14 DMA FUNCTION (DMA CONTROLLER) ....................................................................493

14.1 Features..................................................................................................................................493

14.2 Configuration.........................................................................................................................494

14.3 Registers ................................................................................................................................495

14.4 Transfer Targets .................................................................................................................... 503

14.5 Transfer Modes......................................................................................................................503

14.6 Transfer Types.......................................................................................................................504

14.7 DMA Channel Priorities ........................................................................................................505

14.8 Time Related to DMA Transfer.............................................................................................505

Preliminary User’s Manual U17718EJ1V0UD

11

Page 12

DMA Transfer Start Factors................................................................................................. 506

14.9

14.10 DMA Abort Factors ............................................................................................................... 507

14.11 End of DMA Transfer ............................................................................................................ 507

14.12 Operation Timing .................................................................................................................. 507

14.13 Cautions ................................................................................................................................ 512

CHAPTER 15 INTERRUPT/EXCEPTION PROCESSING FUNCTION............................................... 516

15.1 Features................................................................................................................................. 516

15.2 Non-Maskable Interrupts ..................................................................................................... 520

15.2.1 Operation................................................................................................................................. 522

15.2.2 Restore ....................................................................................................................................523

15.2.3 NP flag.....................................................................................................................................524

15.3 Maskable Interrupts.............................................................................................................. 525

15.3.1 Operation................................................................................................................................. 525

15.3.2 Restore ....................................................................................................................................527

15.3.3 Priorities of maskable interrupts...............................................................................................528

15.3.4 Interrupt control register (xxICn) ..............................................................................................532

15.3.5 Interrupt mask registers 0 to 3 (IMR0 to IMR3)........................................................................ 534

15.3.6 In-service priority register (ISPR).............................................................................................536

15.3.7 ID flag ......................................................................................................................................537

15.3.8 Watchdog timer mode register 2 (WDTM2) .............................................................................537

15.4 Software Exception .............................................................................................................. 538

15.4.1 Operation................................................................................................................................. 538

15.4.2 Restore ....................................................................................................................................539

15.4.3 EP flag ..................................................................................................................................... 540

15.5 Exception Trap...................................................................................................................... 541

15.5.1 Illegal opcode definition ...........................................................................................................541

15.5.2 Debug trap ............................................................................................................................... 543

15.6 External Interrupt Request Input Pins (NMI and INTP0 to INTP10) ................................. 545

15.6.1 Noise elimination .....................................................................................................................545

15.6.2 Edge detection.........................................................................................................................545

15.7 Interrupt Acknowledge Time of CPU .................................................................................. 552

15.8 Periods in Which Interrupts Are Not Acknowledged by CPU.......................................... 553

15.9 Cautions ................................................................................................................................ 553

CHAPTER 16 KEY INTERRUPT FUNCTION ..................................................................................... 554

16.1 Function................................................................................................................................. 554

16.2 Register ................................................................................................................................. 555

16.3 Cautions ................................................................................................................................ 555

CHAPTER 17 STANDBY FUNCTION .................................................................................................. 556

17.1 Overview................................................................................................................................ 556

17.2 Registers ............................................................................................................................... 558

17.3 HALT Mode............................................................................................................................ 561

17.3.1 Setting and operation status ....................................................................................................561

17.3.2 Releasing HALT mode............................................................................................................. 561

17.4 IDLE1 Mode ........................................................................................................................... 563

17.4.1 Setting and operation status ....................................................................................................563

12

Preliminary User’s Manual U17718EJ1V0UD

Page 13

17.4.2 Releasing IDLE1 mode............................................................................................................ 563

17.5 IDLE2 Mode............................................................................................................................565

17.5.1 Setting and operation status .................................................................................................... 565

17.5.2 Releasing IDLE2 mode............................................................................................................ 565

17.5.3 Securing setup time when releasing IDLE2 mode ................................................................... 567

17.6 STOP Mode ............................................................................................................................568

17.6.1 Setting and operation status .................................................................................................... 568

17.6.2 Releasing STOP mode............................................................................................................ 568

17.6.3 Securing oscillation stabilization time when releasing STOP mode......................................... 570

17.7 Subclock Operation Mode....................................................................................................571

17.7.1 Setting and operation status .................................................................................................... 571

17.7.2 Releasing subclock operation mode........................................................................................ 571

17.8 Sub-IDLE Mode......................................................................................................................573

17.8.1 Setting and operation status .................................................................................................... 573

17.8.2 Releasing sub-IDLE mode....................................................................................................... 574

CHAPTER 18 RESET FUNCTIONS......................................................................................................576

18.1 Overview.................................................................................................................................576

18.2 Registers to Check Reset Source........................................................................................577

18.3 Operation................................................................................................................................578

18.3.1 Reset operation via RESET pin ............................................................................................... 578

18.3.2 Reset operation by watchdog timer 2 ...................................................................................... 580

18.3.3 Reset operation by power-on clear circuit................................................................................ 581

18.3.4 Reset operation by low-voltage detector.................................................................................. 581

18.3.5 Reset operation by clock monitor ............................................................................................ 581

CHAPTER 19 CLOCK MONITOR ......................................................................................................... 582

19.1 Functions ...............................................................................................................................582

19.2 Configuration.........................................................................................................................582

19.3 Register ..................................................................................................................................583

19.4 Operation................................................................................................................................584

CHAPTER 20 POWER-ON CLEAR CIRCUIT .....................................................................................587

20.1 Function .................................................................................................................................587

20.2 Configuration.........................................................................................................................587

20.3 Operation................................................................................................................................588

CHAPTER 21 LOW-VOLTAGE DETECTOR........................................................................................589

21.1 Functions ...............................................................................................................................589

21.2 Configuration.........................................................................................................................589

21.3 Registers ................................................................................................................................590

21.4 Operation................................................................................................................................592

21.4.1 To use for internal reset signal ................................................................................................592

21.4.2 To use for interrupt .................................................................................................................. 594

21.5 RAM Retention Voltage Detection Operation.....................................................................595

21.6 Emulation Function...............................................................................................................596

CHAPTER 22 REGULATOR ..................................................................................................................597

Preliminary User’s Manual U17718EJ1V0UD

13

Page 14

Overview................................................................................................................................ 597

22.1

22.2 Operation............................................................................................................................... 598

CHAPTER 23 FLASH MEMORY.......................................................................................................... 599

23.1 Features................................................................................................................................. 599

23.1.1 Erasure unit .............................................................................................................................600

23.2 Rewriting by Dedicated Flash Programmer....................................................................... 601

23.2.1 Programming environment....................................................................................................... 601

23.2.2 Communication mode..............................................................................................................602

23.2.3 Flash memory control ..............................................................................................................607

23.2.4 Selection of communication mode ...........................................................................................608

23.2.5 Communication commands .....................................................................................................609

23.2.6 Pin connection .........................................................................................................................610

23.2.7 Recommended circuit example for writing ...............................................................................614

23.3 Rewriting by Self Programming.......................................................................................... 615

23.3.1 Overview.................................................................................................................................. 615

23.3.2 Features...................................................................................................................................616

23.3.3 Standard self programming flow ..............................................................................................617

23.3.4 Flash functions.........................................................................................................................618

23.3.5 Pin processing .........................................................................................................................618

23.3.6 Internal resources used ...........................................................................................................619

CHAPTER 24 OPTION BYTE FUNCTION .......................................................................................... 620

CHAPTER 25 ON-CHIP DEBUG FUNCTION ..................................................................................... 621

25.1 Features................................................................................................................................. 621

25.2 Connection Circuit Example................................................................................................ 622

25.3 Interface Signals................................................................................................................... 623

25.4 Register ................................................................................................................................. 625

25.5 Operation............................................................................................................................... 626

25.6 ROM Security Function........................................................................................................ 627

25.6.1 Security ID ...............................................................................................................................627

25.6.2 Setting .....................................................................................................................................628

25.7 Cautions ................................................................................................................................ 629

CHAPTER 26 ELECTRICAL SPECIFICATIONS (TARGET).............................................................. 630

26.1 Absolute Maximum Ratings ................................................................................................ 630

26.2 Capacitance........................................................................................................................... 632

26.3 Operating Conditions........................................................................................................... 632

26.4 Oscillator Characteristics.................................................................................................... 633

26.4.1 Main clock oscillator characteristics.........................................................................................633

26.4.2 Subclock oscillator characteristics ...........................................................................................634

26.4.3 PLL characteristics ..................................................................................................................635

26.4.4 Internal oscillator characteristics..............................................................................................635

26.5 Voltage Regulator Characteristics...................................................................................... 635

26.6 DC Characteristics ............................................................................................................... 636

26.6.1 I/O level ...................................................................................................................................636

26.6.2 Pin leakage current..................................................................................................................637

14

Preliminary User’s Manual U17718EJ1V0UD

Page 15

26.6.3 Supply current .........................................................................................................................638

26.7 Data Retention Characteristics............................................................................................639

26.8 AC Characteristics ................................................................................................................640

26.8.1 CLKOUT output timing ............................................................................................................ 641

26.9 Basic Operation.....................................................................................................................642

26.10 Flash Memory Programming Characteristics ....................................................................649

CHAPTER 27 PACKAGE DRAWING ...................................................................................................650

APPENDIX A REGISTER INDEX ..........................................................................................................651

APPENDIX B INSTRUCTION SET LIST..............................................................................................660

B.1 Conventions........................................................................................................................... 660

B.2 Instruction Set (in Alphabetical Order) ...............................................................................663

Preliminary User’s Manual U17718EJ1V0UD

15

Page 16

CHAPTER 1 INTRODUCTION

The V850ES/HG2 is one of the products in the NEC Electronics V850 Series of single-chip microcontrollers

designed for low-power operation for real-time control applications.

1.1 General

The V850ES/HG2 is a 32-bit single-chip microcontroller that includes the V850ES CPU core and peripheral

functions such as ROM/RAM, a timer/counter, serial interfaces, and an A/D converter.

In addition to high real-time response characteristics and 1-clock-pitch basic instructions, the V850ES/HG2 features

multiply instructions, saturated operation instructions, bit manipulation instructions, etc., realized by a hardware

multiplier, as optimum instructions for digital servo control applications.

Table 1-1 lists the products of the V850ES/HG2.

16

Preliminary User’s Manual U17718EJ1V0UD

Page 17

CHAPTER 1 INTRODUCTION

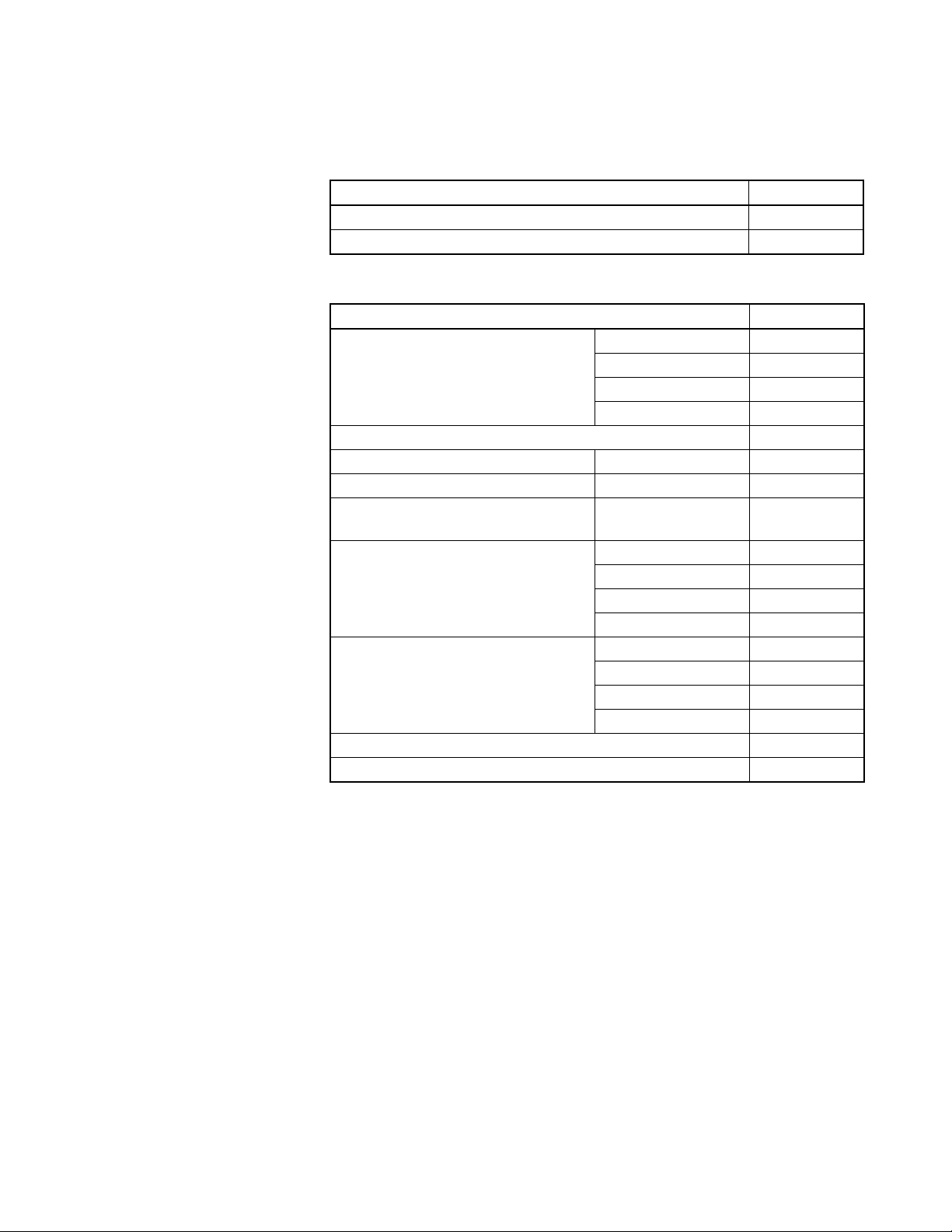

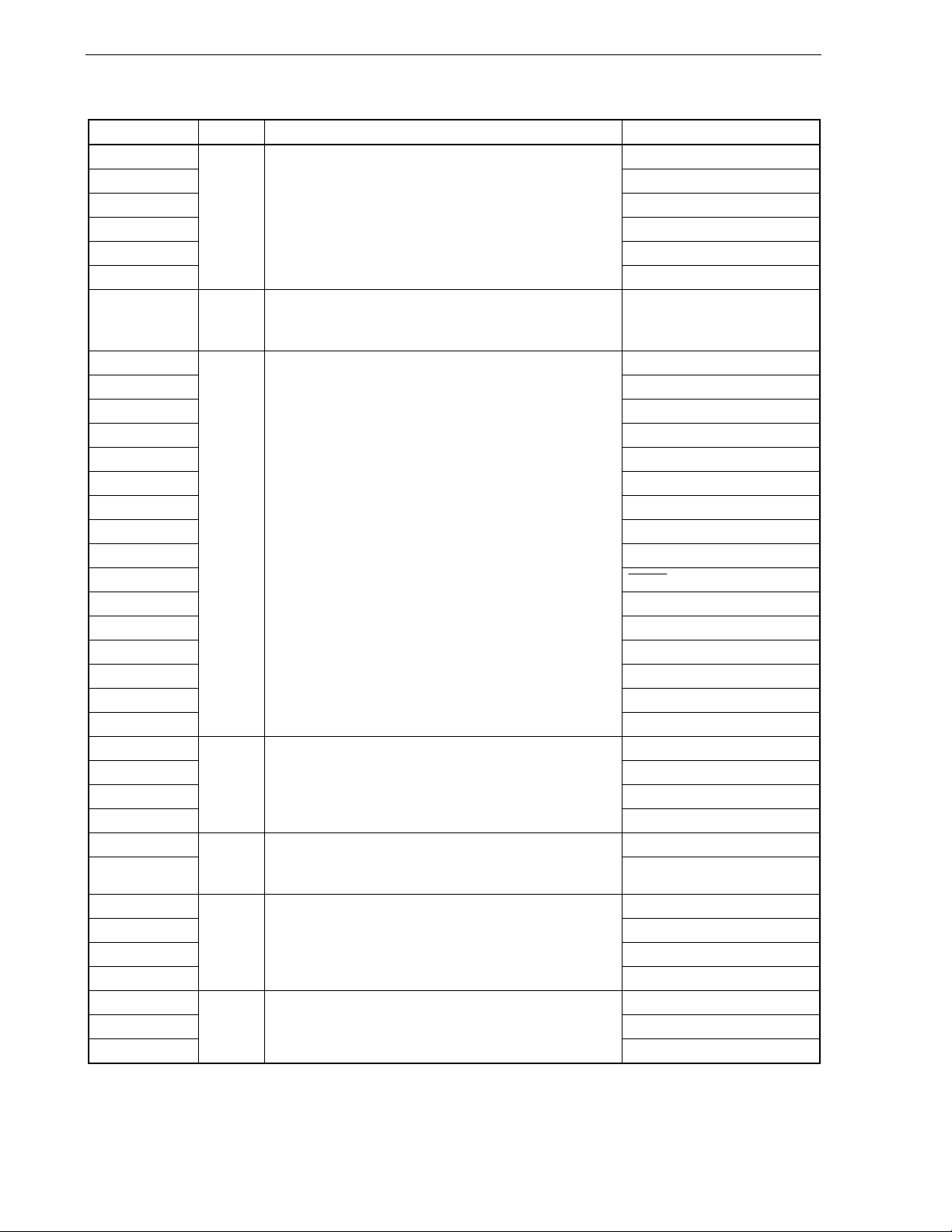

Table 1-1. V850ES/HG2 Product List

Part Number

µ

PD70F3706

µ

PD70F3707

Flash memory 128 KB 256 KB Internal memory

RAM 12 KB

Memory space Logical space 64 MB

General-purpose register 32 bits × 32 registers

Main clock (oscillation frequency)

Subclock (oscillation frequency)

Ceramic/crystal/external clock

• In PLL mode: f

• In clock through mode: f

X = 4 to 5 MHz

X = 4 to 5 MHz

Crystal/external clock: f

XT = 32.768 kHz

RC oscillation: 20 kHz

Internal oscillator fR = 200 kHz (TYP.)

Minimum instruction execution time 50 ns (main clock (fXX) = 20 MHz operation)

DSP function

32 × 32 = 64: 200 to 250 ns (at 20 MHz)

32 × 32 + 32 = 32: 300 ns (at 20 MHz)

16 × 16 = 32: 50 to 100 ns (at 20 MHz)

16 × 16 + 32 = 32: 150 ns (at 20 MHz)

I/O port I/O: 84

Timer

16-bit timer/event counter P: 4 channels

16-bit timer/event counter Q: 2 channels

16-bit interval timer M: 1 channel

Watchdog timer 2: 1 channel

Watch timer: 1 channel

A/D converter 10-bit resolution × 16 channels

Serial interface

CSIB: 2 channels

UARTA (for LIN): 3 channels

DMA controller 4 channels (transfer target: on-chip peripheral I/O, internal RAM)

Interrupt source External: 12 (12)

Note

, internal: 43

Power save function HALT/IDLE1/IDLE2/STOP/subclock/sub-IDLE mode

Reset

RESET pin input, watchdog timer 2 (WDT2), clock monitor (CLM), POC circuit, low-voltage

detector (LVI)

On-chip debug function Provided (RUN/break)

Operating power supply voltage 3.5 to 5.5 V (A/D converter: 4.0 to 5.5 V)

Operating ambient temperature −40 to +85°C

Package 100-pin plastic LQFP (fine pitch) (14 × 14 mm)

Note The figure in parentheses indicates the number of external interrupts that can release STOP mode.

Preliminary User’s Manual U17718EJ1V0UD

17

Page 18

CHAPTER 1 INTRODUCTION

1.2 Features

Minimum instruction execution time: 50 ns (operating with main clock (fXX) of 20 MHz)

General-purpose registers: 32 bits × 32 registers

CPU features: Signed multiplication (16 × 16 → 32): 1 to 2 clocks

Signed multiplication (32 × 32 → 64): 1 to 5 clocks

Saturated operations (overflow and underflow detection functions included)

32-bit shift instruction: 1 clock

Bit manipulation instructions

Load/store instructions with long/short format

Memory space: 64 MB of linear address space (for programs and data)

• Internal memory: RAM: 12 KB

Flash memory: 128 KB/256 KB (see Ta ble 1-1)

Interrupts and exceptions: Non-maskable interrupts: 2 sources

Maskable interrupts: 53 sources

Software exceptions: 32 sources

Exception trap: 2 sources

I/O lines: I/O ports: 84

Timer function: 16-bit interval timer M (TMM): 1 channel

16-bit timer/event counter P (TMP): 4 channels

16-bit timer/event counter Q (TMQ): 2 channels

Watch timer: 1 channel

Watchdog timer 2: 1 channel

Serial interface: Asynchronous serial interface A (UARTA)

3-wire variable-length serial interface B (CSIB)

UARTA (supporting LIN): 3 channels

CSIB: 2 channels

A/D converter: 10-bit resolution: 16 channels

DMA controller: 4 channels

On-chip debug function: JTAG interface

Clock generator: During main clock or subclock operation

7-level CPU clock (f

XX, fXX/2, fXX/4, fXX/8, fXX/16, fXX/32, fXT)

Clock-through mode/PLL mode selectable

Internal oscillation clock: 200 kHz (TYP.)

Power-save functions: HALT/IDLE1/IDLE2/STOP/subclock/sub-IDLE mode

Package: 100-pin plastic LQFP (fine pitch) (14 × 14)

1.3 Application Fields

Consumer devices

18

Preliminary User’s Manual U17718EJ1V0UD

Page 19

CHAPTER 1 INTRODUCTION

1.4 Ordering Information

Part Number Package On-Chip Flash Memory

µ

PD70F3706GC-8EA-A

µ

PD70F3707GC-8EA-A

Remark Products with -A at the end of the part number are lead-free products.

100-pin plastic LQFP (fine pitch) (14 × 14)

100-pin plastic LQFP (fine pitch) (14 × 14)

128 KB

256 KB

Preliminary User’s Manual U17718EJ1V0UD

19

Page 20

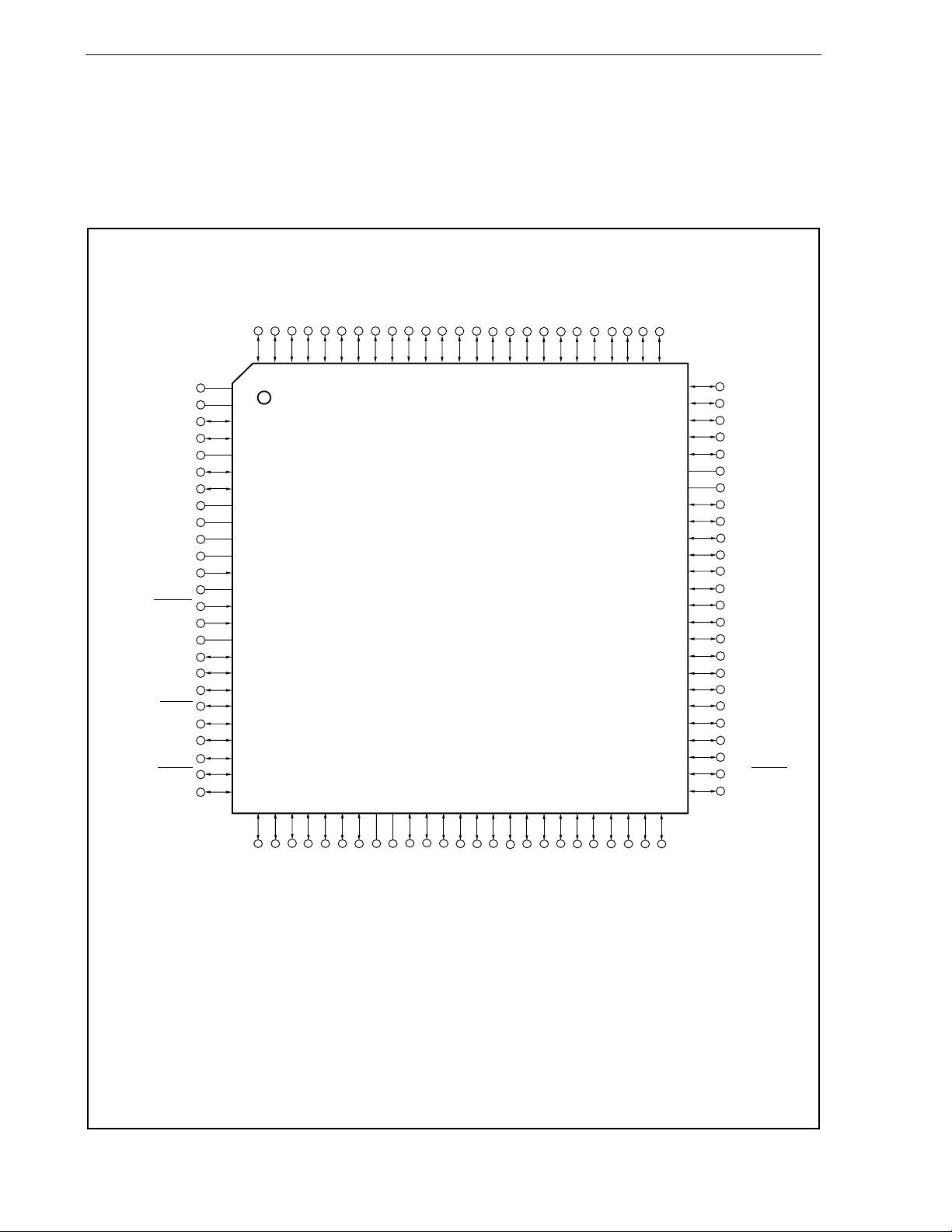

1.5 Pin Configuration (Top View)

100-pin plastic LQFP (fine pitch) (14 × 14)

µ

PD70F3706GC-8EA-A

µ

PD70F3707GC-8EA-A

P70/ANI0

P71/ANI1

P72/ANI2

P73/ANI3

P74/ANI4

CHAPTER 1 INTRODUCTION

P75/ANI5

P76/ANI6

P77/ANI7

P78/ANI8

P79/ANI9

P710/ANI10

P711/ANI11

P712/ANI12

P713/ANI13

P714/ANI14

P715/ANI15

PDL13

PDL12

PDL11

PDL10

PDL9

PDL8

PDL7

PDL6

PDL5/FLMD1

AV

REF0

AV

P10/INTP9

P11/INTP10

EV

P00/TIP31/TOP31

P01/TIP30/TOP30

Note 1

FLMD0

V

Note 2

REGC

V

X1

X2

RESET

XT1

XT2

P02/NMI

P03/INTP0/ADTRG

P04/INTP1

P05/INTP2/DRST

P06/INTP3

P40/SIB0

P41/SOB0

P42/SCKB0

P30/TXDA0

100 99 98 97 96 95 94 93 92 91 90 89 88 87 86

1

SS

2

3

4

DD

5

6

7

8

DD

9

10

SS

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26 27 28 29 30 31 32 33 34 35 36 37 38 39 40

85

84 8283 81

41

43 4442 45

7780 7879 76

4946 4847 50

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

PDL4

PDL3

PDL2

PDL1

PDL0

DD

BV

BV

SS

PCT6

PCT4

PCT1

PCT0

PCM3

PCM2

PCM1/CLKOUT

PCM0

PCS1

PCS0

P915/INTP6

P914/INTP5

P913/INTP4/PCL

P912

P911

P910

P99/SCKB1

P98/SOB1

P31/RXDA0/INTP7

P32/ASCKA0/TOP01/TIP00/TOP00

Notes 1. Connect this pin to V

2. Connect the REGC pin to V

20

SS

P37

EV

DD

EV

P36

P38/TXDA2

P33/TIP01/TOP01

P34/TIP10/TOP10

P35/TIP11/TOP11

SS in the normal mode.

SS via a 4.7

Preliminary User’s Manual U17718EJ1V0UD

µ

P54/KR4/DCK

P55/KR5/DMS

P90/KR6/TXDA1

P91/KR7/RXDA1

P92/TIQ11/TOQ11

P39/RXDA2/INTP8

P50/KR0/TIQ01/TOQ01

P51/KR1/TIQ02/TOQ02

P52/KR2/TIQ03/TOQ03/DDI

P53/KR3/TIQ00/TOQ00/DDO

P93/TIQ12/TOQ12

F (preliminary value) capacitor.

P96/TIP21/TOP21

P94/TIQ13/TOQ13

P95/TIQ10/TOQ10

P97/SIB1/TIP20/TOP20

Page 21

Pin identification

ADTRG:

ANI0 to ANI15:

ASCKA0:

AV

REF0:

AV

SS:

BV

DD:

BVSS:

CLKOUT:

DCK:

DDI:

DDO:

DMS:

DRST:

EV

DD:

EV

SS:

FLMD0, FLMD1:

INTP0 to INTP10:

KR0 to KR7:

NMI:

P00 to P06:

P10, P11:

P30 to P39:

P40 to P42:

P50 to P55:

P70 to P715:

P90 to P915:

PCL:

PCM0 to PCM3:

CHAPTER 1 INTRODUCTION

A/D trigger input

Analog input

Asynchronous serial clock

Analog reference voltage

Analog V

SS

Power supply for bus interface

Ground for bus interface

Clock output

Debug clock

Debug data input

Debug data output

Debug mode select

Debug reset

Power supply for port

Ground for port

Flash programming mode

External interrupt input

Key return

Non-maskable interrupt request

Port 0

Port 1

Port 3

Port 4

Port 5

Port 7

Port 9

Programmable clock output

Port CM

PCS0, PCS1:

PCT0, PCT1,

PCT4, PCT6:

PDL0 to PDL13:

REGC:

RESET:

RXDA0 to RXDA2:

SCKB0, SCKB1:

SIB0, SIB1:

SOB0, SOB1:

TIP00, TIP01,

TIP10, TIP11,

TIP20, TIP21,

TIP30, TIP31,

TIQ00 to TIQ03,

TIQ10 to TIQ13:

TOP00, TOP01,

TOP10, TOP11,

TOP20, TOP21,

TOP30, TOP31,

TOQ00 to TOQ03,

TOQ10 to TOQ13:

TXDA0 to TXDA2:

V

DD:

VSS:

X1, X2:

XT1, XT2:

Port CS

Port CT

Port DL

Regulator control

Reset

Receive data

Serial clock

Serial input

Serial output

Timer input

Timer output

Transmit data

Power supply

Ground

Crystal for main clock

Crystal for subclock

Preliminary User’s Manual U17718EJ1V0UD

21

Page 22

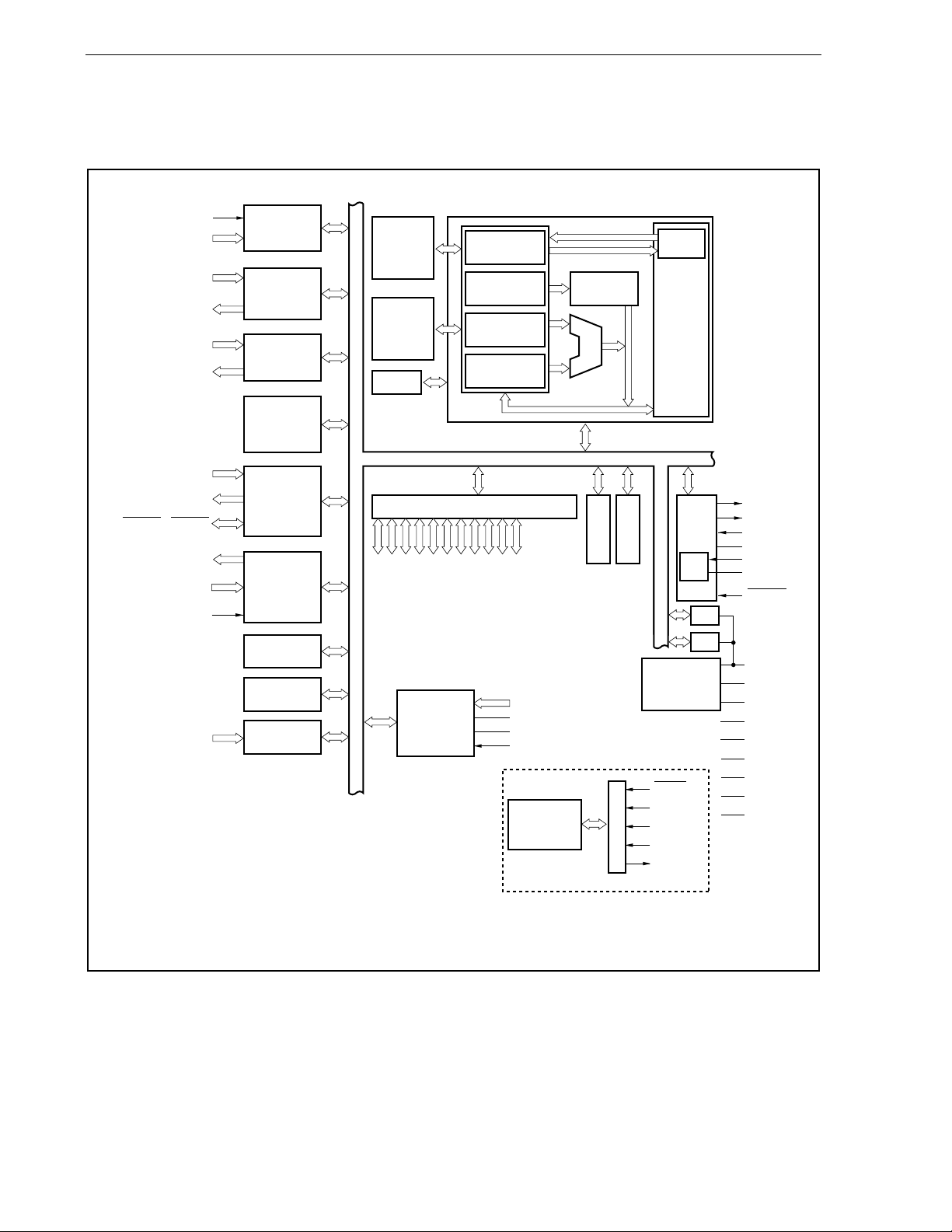

1.6 Function Block Configuration

1.6.1 Internal block diagram

INTP0 to INTP10

TIQ00 to TIQ03

TIQ10 to TIQ13

TOQ00 to TOQ03

TOQ10 to TOQ13

TIP00 to TIP30,

TIP01 to TIP31

TOP00 to TOP30,

TOP01 to TOP31

SIB0, SIB1

SOB0, SOB1

SCKB0, SCKB1

TXDA0 to TXDA2

RXDA0 to RXDA2

KR0 to KR7

µ

Note

µ

NMI

ASCK0

PD70F3706: 128 KB

PD70F3707: 256 KB

INTC

16-bit timer/

counter Q:

2 ch

16-bit timer/

counter P:

4 ch

16-bit

interval

timer M:

1 ch

CSIB: 2 ch

UARTA:

3 ch

Watchdog

timer 2

Watch timer

Key return

function

CHAPTER 1 INTRODUCTION

Flash

memory

Note 1

RAM

12 KB

DMAC

PC

32-bit barrel

shifter

System

registers

General-purpose

registers 32 bits × 32

Port

P10, P11

P50 to P55

P40 to P42

P30 to P39

PCS0, PCS1

P90 to P915

PCM0 to PCM3

PDL0 to PDL13

P70 to P715

P00 to P06

PCT0, PCT1, PCT4, PCT6

ANI0 to ANI15

SS

A/D

converter

AV

AV

REF0

ADTRG

On-chip

debug

function

CPU

Multiplier

16 × 16 → 32

ALU

Internal

oscillator

CLM

Instruction

queue

BCU

CG

PLL

POC

Regulator

DRST

DMS

DDI

DCK

DDO

LVI

PCL

CLKOUT

XT1

XT2

X1

X2

RESET

V

DD

V

SS

REGC

FLMD0

FLMD1

BV

DD

BV

SS

EV

DD

EV

SS

22

Preliminary User’s Manual U17718EJ1V0UD

Page 23

CHAPTER 1 INTRODUCTION

1.6.2 Internal units

(1) CPU

The CPU uses five-stage pipeline control to enable single-clock execution of address calculations, arithmetic

logic operations, data transfers, and almost all other instruction processing.

Other dedicated on-chip hardware, such as a multiplier (16 bits × 16 bits → 32 bits) and a barrel shifter (32

bits) contribute to faster complex processing.

(2) Bus control unit (BCU)

The BCU controls the internal buses.

(3) ROM

This is a 256 KB/128 KB flash memory mapped to addresses 0000000H to 003FFFFH/0000000H to

001FFFFH. It can be accessed from the CPU in one clock during instruction fetch.

(4) RAM

This is a 12 KB RAM mapped to addresses 3FFC000H to 3FFEFFFH. It can be accessed from the CPU in

one clock during data access.

(5) Interrupt controller (INTC)

This controller handles hardware interrupt requests (NMI, INTP0 to INTP10) from on-chip peripheral hardware

and external hardware. Eight levels of interrupt priorities can be specified for these interrupt requests, and

multiple servicing control can be performed.

(6) Clock generator (CG)

A main clock oscillator that generates the main clock oscillation frequency (f

X) and a subclock oscillator that

generates the subclock oscillation frequency (fXT) are available. As the main clock frequency (fXX), fX is used as

is in the clock-through mode and is multiplied by four in the PLL mode.

The CPU clock frequency (f

CPU) can be selected from seven types: fXX, fXX/2, fXX/4, fXX/8, fXX/16, fXX/32, and fXT.

(7) Internal oscillator

An internal oscillator is provided on chip. The oscillation frequency is 200 kHz (TYP.). An internal oscillator

supplies the clock for watchdog timer 2 and timer M.

(8) Timer/counter

Four-channel 16-bit timer/event counter P (TMP), two-channel 16-bit timer/event counter Q (TMQ), and one-

channel 16-bit interval timer M (TMM) are provided on chip.

(9) Watch timer

This timer counts the reference time period (0.5 s) for counting the clock (the 32.768 kHz from the subclock or

the 32.768 kHz f

BRG from prescaler 3). The watch timer can also be used as an interval timer for the main

clock.

Preliminary User’s Manual U17718EJ1V0UD

23

Page 24

(10) Watchdog timer 2

A watchdog timer is provided on chip to detect inadvertent program loops, system abnormalities, etc.

Either the internal oscillation clock or the main clock can be selected as the source clock.

Watchdog timer 2 generates a non-maskable interrupt request signal (INTWDT2) or a system reset signal

(WDT2RES) after an overflow occurs.

(11) Serial interface

The V850ES/HG2 includes three kinds of serial interfaces: asynchronous serial interface A (UARTA) and 3-

wire variable-length serial interface B (CSIB).

In the case of UARTA, data is transferred via the TXDA0 to TXDA2 and RXDA0 to RXDA2 pins.

In the case of CSIB, data is transferred via the SOB0, SOB1, SIB0, SIB1, SCKB0, and SCKB1 pins.

(12) A/D converter

This 10-bit A/D converter includes 16 analog input pins. Conversion is performed using the successive

approximation method.

(13) DMA controller

A 4-channel DMA controller is provided on chip. This controller transfers data between the internal RAM and

on-chip peripheral I/O devices in response to interrupt requests sent by on-chip peripheral I/O.

(14) Key interrupt function

A key interrupt request signal (INTKR) can be generated by inputting a falling edge to key input pins (8

channels).

(15) On-chip debug function

An on-chip debug function that uses the JTAG (Joint Test Action Group) communication specifications is

provided. Switching between the normal port function and on-chip debugging function is done with the

control pin input level and the on-chip debug mode register (OCDM).

(16) Ports

The general-purpose port functions and control pin functions are provided. For details, see CHAPTER 4

PORT FUNCTIONS.

CHAPTER 1 INTRODUCTION

24

Preliminary User’s Manual U17718EJ1V0UD

Page 25

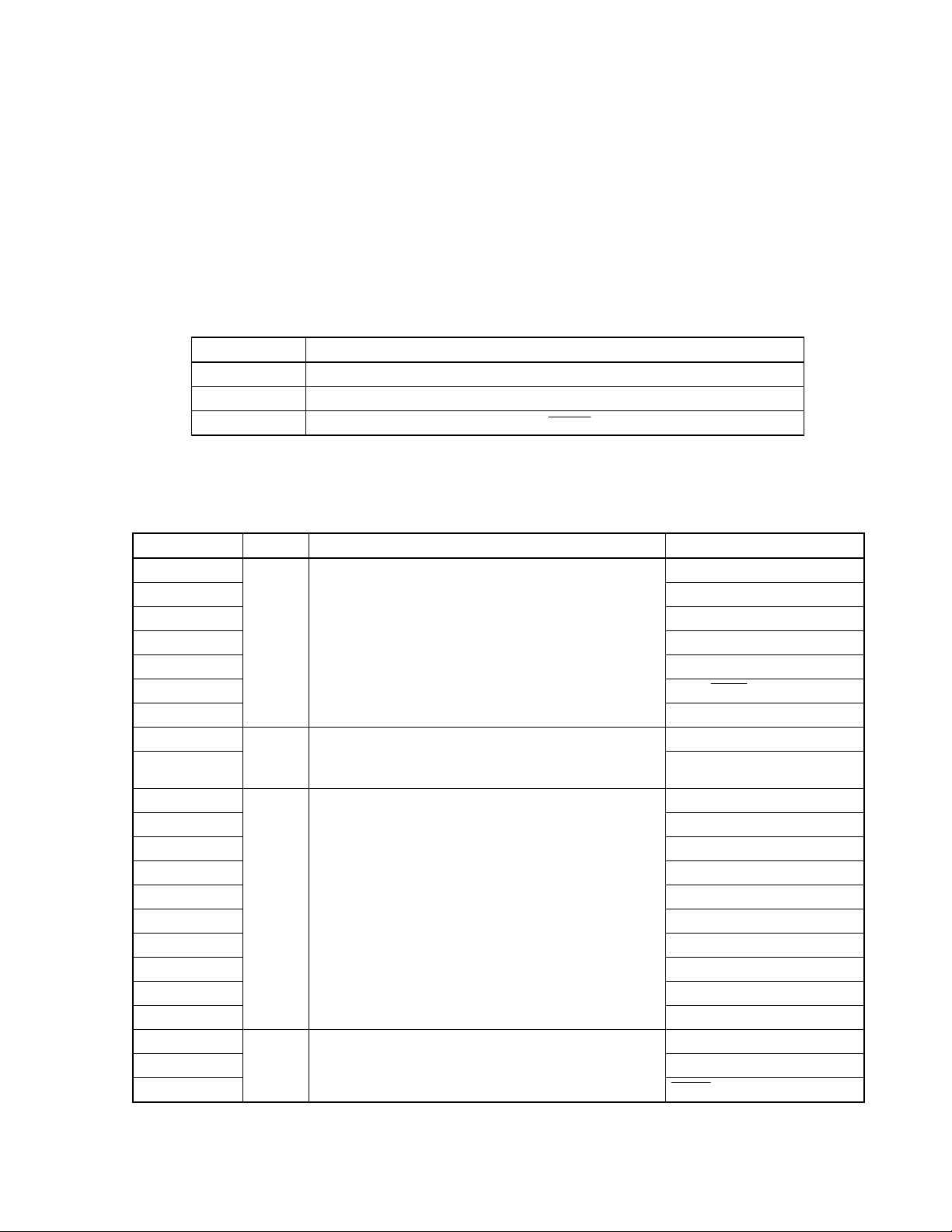

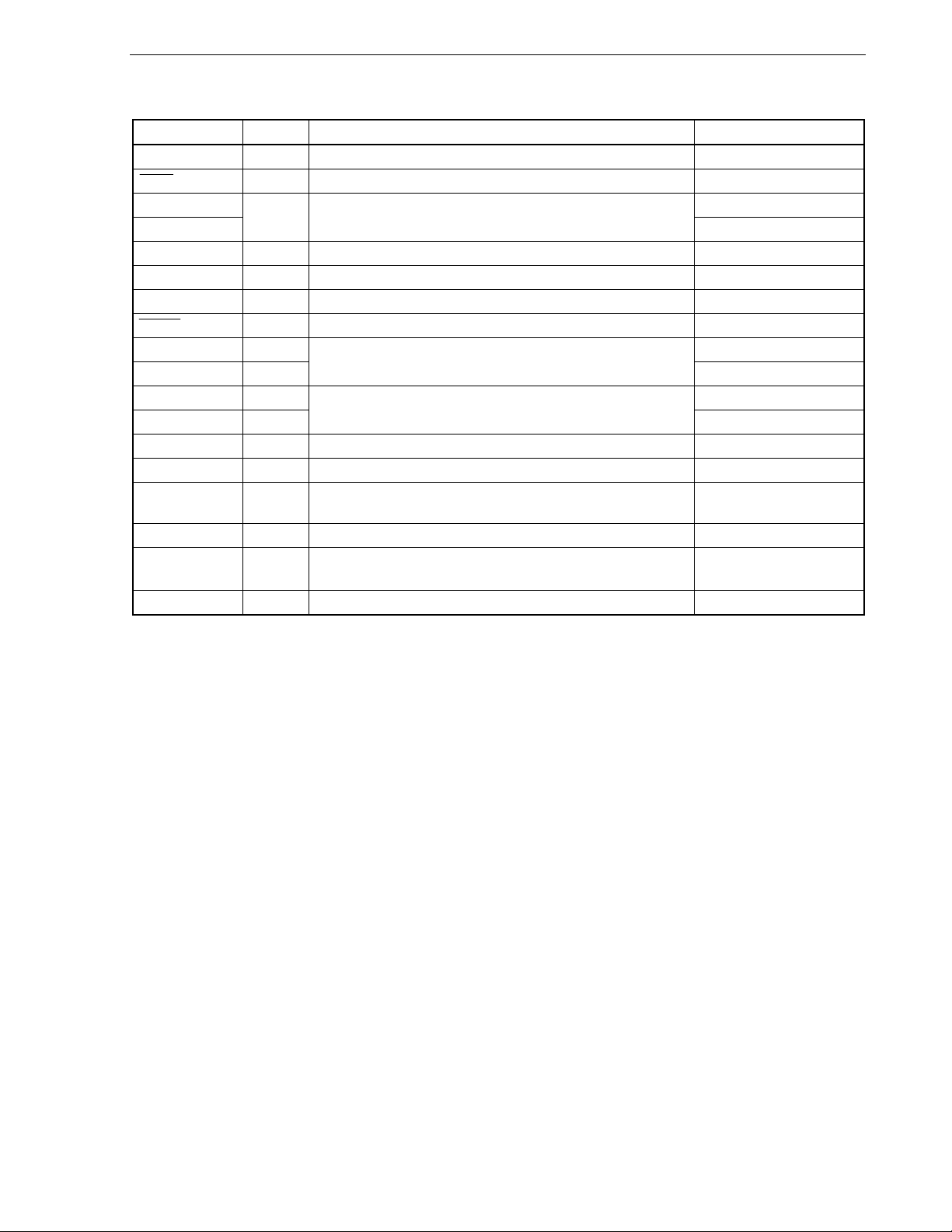

CHAPTER 2 PIN FUNCTIONS

This section explains the names and functions of the pins of the V850ES/HG2.

2.1 Pin Function List

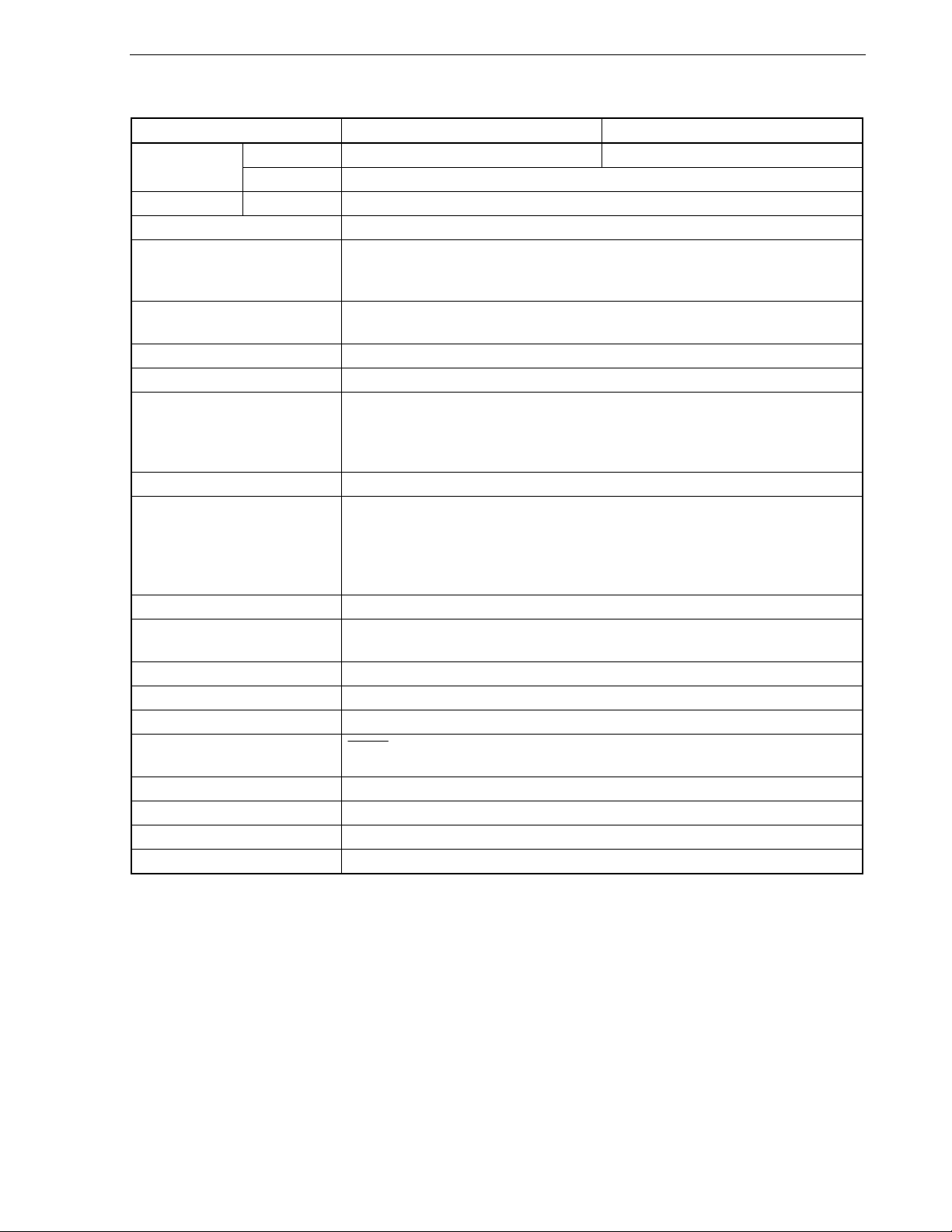

Three I/O buffer power supplies, AV

supplies and the pins is shown below.

Power Supply Corresponding Pin

AVREF0 Port 7

BVDD Port CM, port CS, port CT, port DL

EVDD Port 0, port 1, port 3, port 4, port 5, port 9, RESET

(1) Port pins

REF0, BVDD, and EVDD, are available. The relationship between the power

Table 2-1. Pin I/O Buffer Power Supplies

Table 2-2. List of Pins (Port Pins) (1/2)

Pin Name I/O Function Alternate Function

P00 TIP31/TOP31

P01 TIP30/TOP30

P02 NMI

P03 INTP0/ADTRG

P04 INTP1

P05 INTP2/D RST

P06

P10 INTP9

P11

P30 TXDA0

P31 RXDA0/INTP7

P32 ASCKA0/TIP00/TOP00/TOP01

P33 TIP01/TOP01

P34 TIP10/TOP10

P35 TIP11/TOP11

P36

P37

P38 TXDA2

P39

P40 SIB0

P41 SOB0

P42

I/O

I/O

I/O

I/O

Port 0

7-bit I/O port

Input/output can be specified in 1-bit units.

Port 1

2-bit I/O port

Input/output can be specified in 1-bit units.

Port 3

10-bit I/O port

Input/output can be specified in 1-bit units.

Port 4

3-bit I/O port

Input/output can be specified in 1-bit units.

INTP3

INTP10

−

−

RXDA2/INTP8

SCKB0

Preliminary User’s Manual U17718EJ1V0UD

25

Page 26

CHAPTER 2 PIN FUNCTIONS

Table 2-2. List of Pins (Port Pins) (2/2)

Pin Name I/O Function Alternate Function

P50 KR0/TIQ01/TOQ01

P51 KR1/TIQ02/TOQ02

P52 KR2/TIQ03/TOQ03/DDI

P53 KR3/TIQ00/TOQ00/DDO

P54 KR4/DCK

P55

P70 to P715 I/O

P90 KR6/TXDA1

P91 KR7/RXDA1

P92 TIQ11/TOQ11

P93 TIQ12/TOQ12

P94 TIQ13/TOQ13

P95 TIQ10/TOQ10

P96 TIP21/TOP21

P97 SIB1/TIP20/TOP20

P98 SOB1

P99 SCKB1

P910

P911

P912

P913 INTP4/PCL

P914 INTP5

P915

PCM0

PCM1 CLKOUT

PCM2

PCM3

PCS0

PCS1

PCT0

PCT1

PCT4

PCT6

PDL0 to PDL4

PDL5 FLMD1

PDL6 to PDL13

I/O

I/O

I/O

I/O

I/O

I/O

Port 5

6-bit I/O port

Input/output can be specified in 1-bit units.

Port 7

16-bit I/O port

Input/output can be specified in 1-bit units.

Port 9

16-bit I/O port

Input/output can be specified in 1-bit units.

Port CM

4-bit I/O port

Input/output can be specified in 1-bit units.

Port CS

2-bit I/O port

Input/output can be specified in 1-bit units.

Port CT

4-bit I/O port

Input/output can be specified in 1-bit units.

Port DL

14-bit I/O port

Input/output can be specified in 1-bit units.

KR5/DMS

ANI0 to ANI15

−

−

−

INTP6

−

−

−

−

–

−

−

−

−

−

−

26

Preliminary User’s Manual U17718EJ1V0UD

Page 27

CHAPTER 2 PIN FUNCTIONS

(2) Non-port pins

Table 2-3. List of Pins (Non-Port Pins) (1/3)

Pin Name I/O Function Alternate Function

Note

NMI

Input

INTP0 P03/ADTRG

INTP1 P04

INTP2 P05/DR ST

INTP3 P06

INTP4 P913/PCL

INTP5 P914

INTP6 P915

INTP7 P31/RXDA0

INTP8 P39/RXDA2

INTP9 P10

INTP10

TIP00 External event/clock input (TMP00) P32/ASCKA0/TOP00/TOP01

TIP01 External event input (TMP01) P33/TOP01

TIP10 External event/clock input (TMP10) P34/TOP10

TIP11 External event input (TMP11) P35/TOP11

TIP20 External event/clock input (TMP20) P97/SIB1/TOP20

TIP21 External event input (TMP21) P96/TOP21