Page 1

PRELIMINARY PRODUCT INFORMATION

MOS INTEGRATED CIRCUIT

µµµµ

PD78F9328

8-BIT SINGLE-CHIP MICROCONTROLLER

The µPD78F9328 is a µPD789327 Subseries (designed for remote controller with on-chip LCD) product in the

78K/0S Series, featuring expanded flash memory in place of the internal ROM of the µPD789322, 789324, 789326,

and 789327.

Because flash memory allows the program to be written and erased with the device mounted on the target board,

this product is ideal for development trials, small-scale production, or for applications that require frequent upgrades.

Detailed function descriptions are provided in the following user’s manuals. Be sure to read them before

designing.

µµµµ

PD789327, 789467 Subseries User’s Manual: To be prepared

78K/0S Series User’s Manual Instructions: U11047E

FEATURES

• Pin-compatible with mask ROM product (except VPP)

• Flash memory: 32 Kbytes

• Internal high-speed RAM: 512 bytes

• LCD display RAM: 24 bytes

• Variable minimum instruction execution time: High speed (0.4 µs: @5.0-MHz operation with main system clock),

low speed (1.6 µs: @5.0-MHz operation with main system clock), and ultra low speed (122 µs: @32.768-kHz

operation with subsystem clock)

• I/O ports: 21

• Serial interface (3-wire serial I/O mode): 1 channel

• LCD controller/driver

Segment signals: 24

Common signals: 4

• Timer: 4 channels

• Supply voltage: VDD = 1.8 to 5.5 V

APPLICATIONS

Remote-control devices, healthcare equipment, etc.

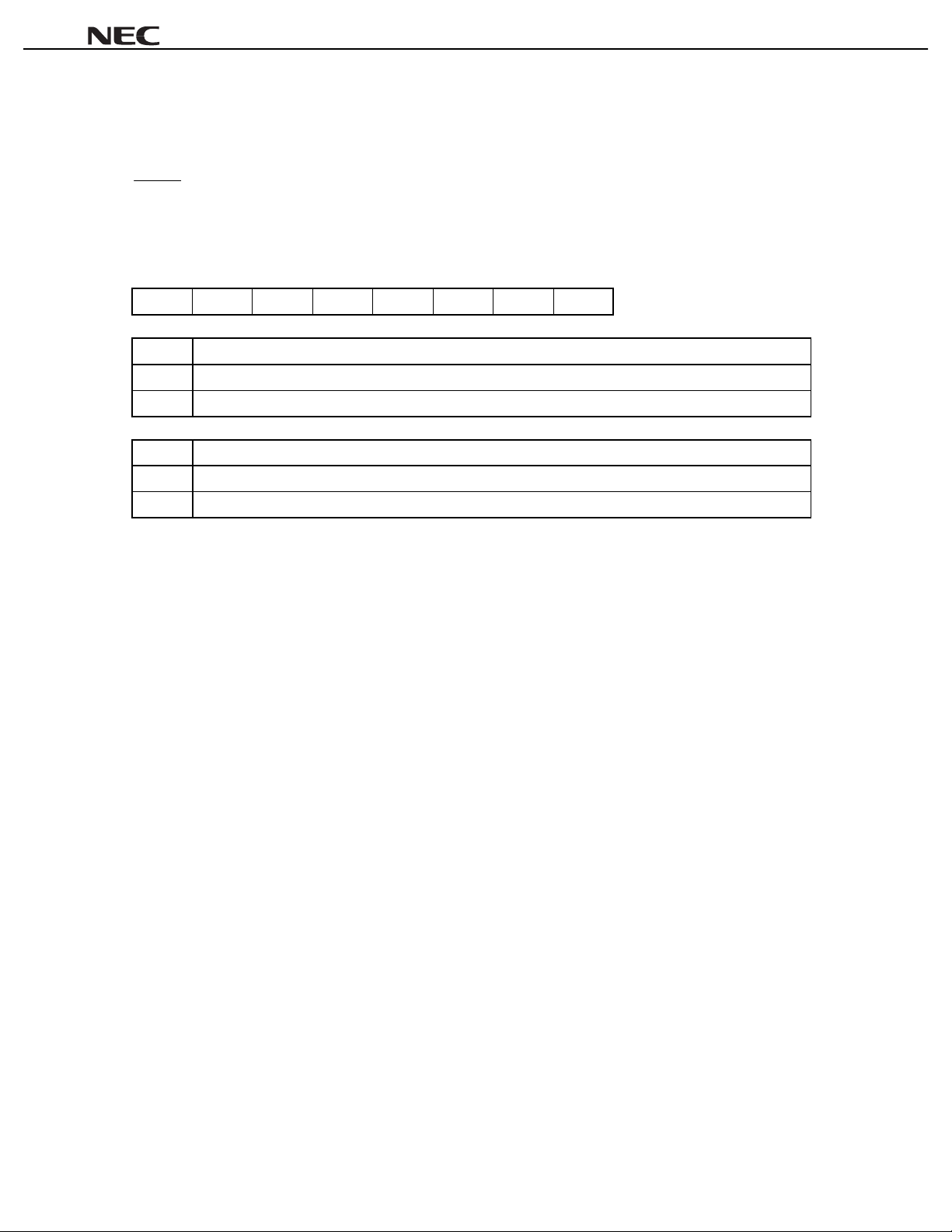

ORDERING INFORMATION

Part Number Package

PD78F9328GB-8ET 52-pin plastic LQFP (10 mm × 10 mm)

µ

The information contained in this document is being issued in advance of the production cycle for the

device. The parameters for the device may change before final production or NEC Corporation, at its own

discretion, may withdraw the device prior to its production.

Not all devices/types available in every country. Please check with local NEC representative for

availability and additional information.

Document No. U14411EJ1V0PM00 (1st edition)

Date Published November 1999 N CP(K)

Printed in Japan

Page 2

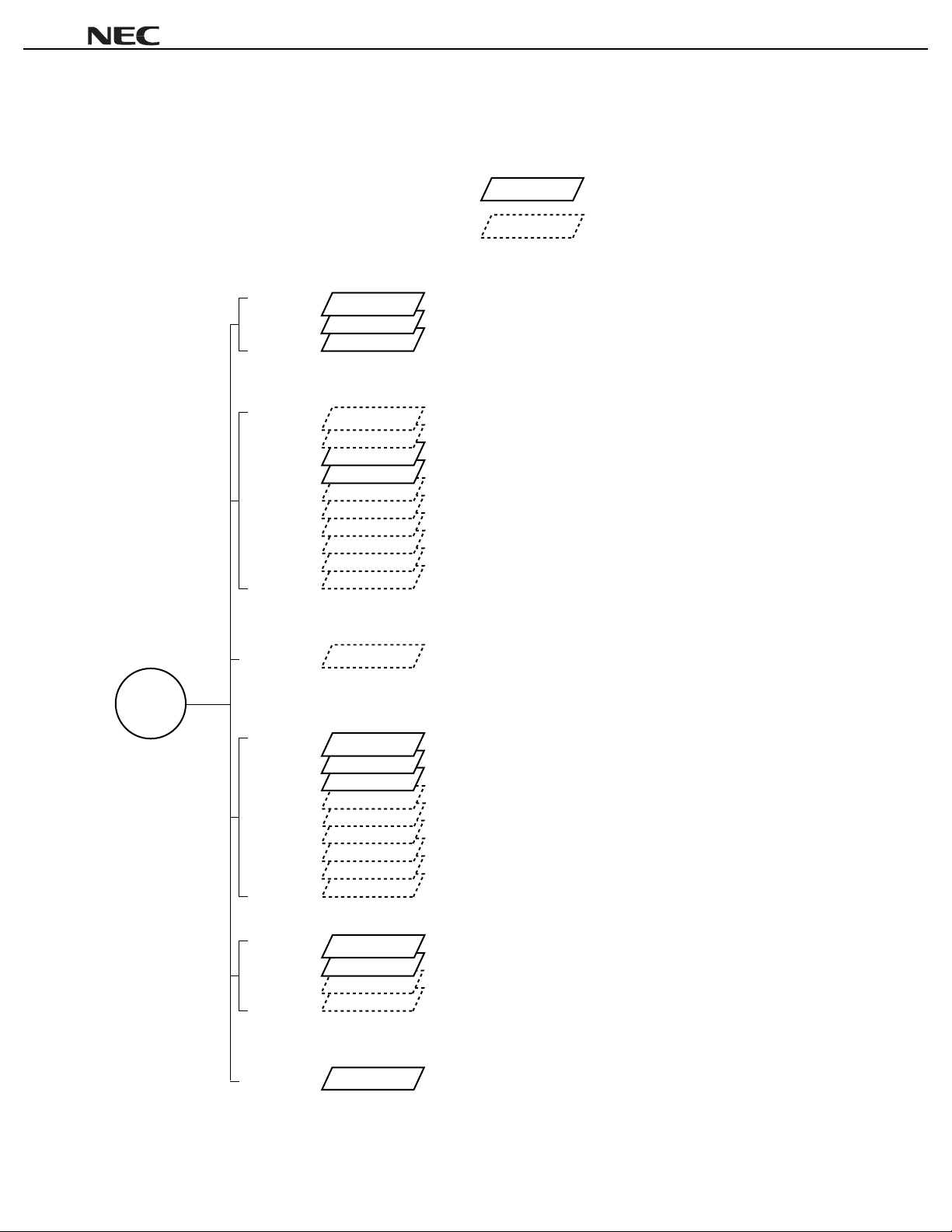

78K/0S SERIES LINEUP

The products in the 78K/0S Series are listed below. The names enclosed in boxes are subseries names.

Products in mass production

Products under development

Small-scale, general-purpose applications

µ

44-pin

42-/44-pin

28-pin

µ

PD789046

µ

PD789026

PD789014

µ

Small-scale, general-purpose applications + A/D

PD789026 with internal subsystem clock

PD789014 with enhanced timer and expanded ROM, RAM

µ

On-chip UART. Capable of low-voltage (1.8 V) operation

µµµµ

PD78F9328

78K/0S

Series

44-/48-pin

44-/48-pin

44-pin

44-pin

30-pin

30-pin

30-pin

30-pin

30-pin

30-pin

44-pin

88-pin

80-pin

80-pin

64-pin

64-pin

64-pin

64-pin

64-pin

64-pin

PD789

PD789

PD789177

PD789167

PD789156

PD789146

PD789134A

PD789124A

PD789114A

PD789104A

Inverter control

PD789842

LCD drive

PD789830

PD789417A

PD789407A

PD789457

PD789447

PD789437

PD789427

PD789316

PD789306

217AY

µ

197AY

µ

µ

µ

µ

µ

µ

µ

µ

µ

µ

µ

µ

µ

µ

µ

µ

µ

µ

µ

RC oscillation version of the PD789197AY

PD789177 with on-chip EEPROM

µ

PD789167 with enhanced A/D converter

µ

µ

PD789104A with enhanced timer

µ

PD789146 with enhanced A/D converter

PD789104A with EEPROM

µ

PD789124A with enhanced A/D converter

µ

RC oscillation version of the PD789104A

PD789104A with enhanced A/D converter

µ

PD789026 with added A/D, multiplier

µ

On-chip inverter control circuit and UART

On-chip UART and dot LCD

µ

PD789407A with enhanced A/D converter

µ

PD789457 with enhanced I/O

µ

PD789447 with enhanced A/D converter

RC oscillation version of the PD789427

µ

PD789427 with enhanced A/D converter

µ

PD789306 with A/D converter

RC oscillation version of the PD789306

Basic subseries for LCD drive

µ

TM

and SMB

µ

µ

µ

ASSP

44-pin

44-pin

20-pin

20-pin

5-pin

2

PD789800

µ

µ

PD789840

µ

PD789861

µ

PD789860

IC card

PD789810

µ

Preliminary Product Information U14411EJ1V0PM00

For PC keyboard, on-chip USB function

For key pad, on-chip POC

RC oscillation version of the PD789860

For keyless entry, on-chip POC and key return circuit

On-chip EEPROM, security circuit

µ

Page 3

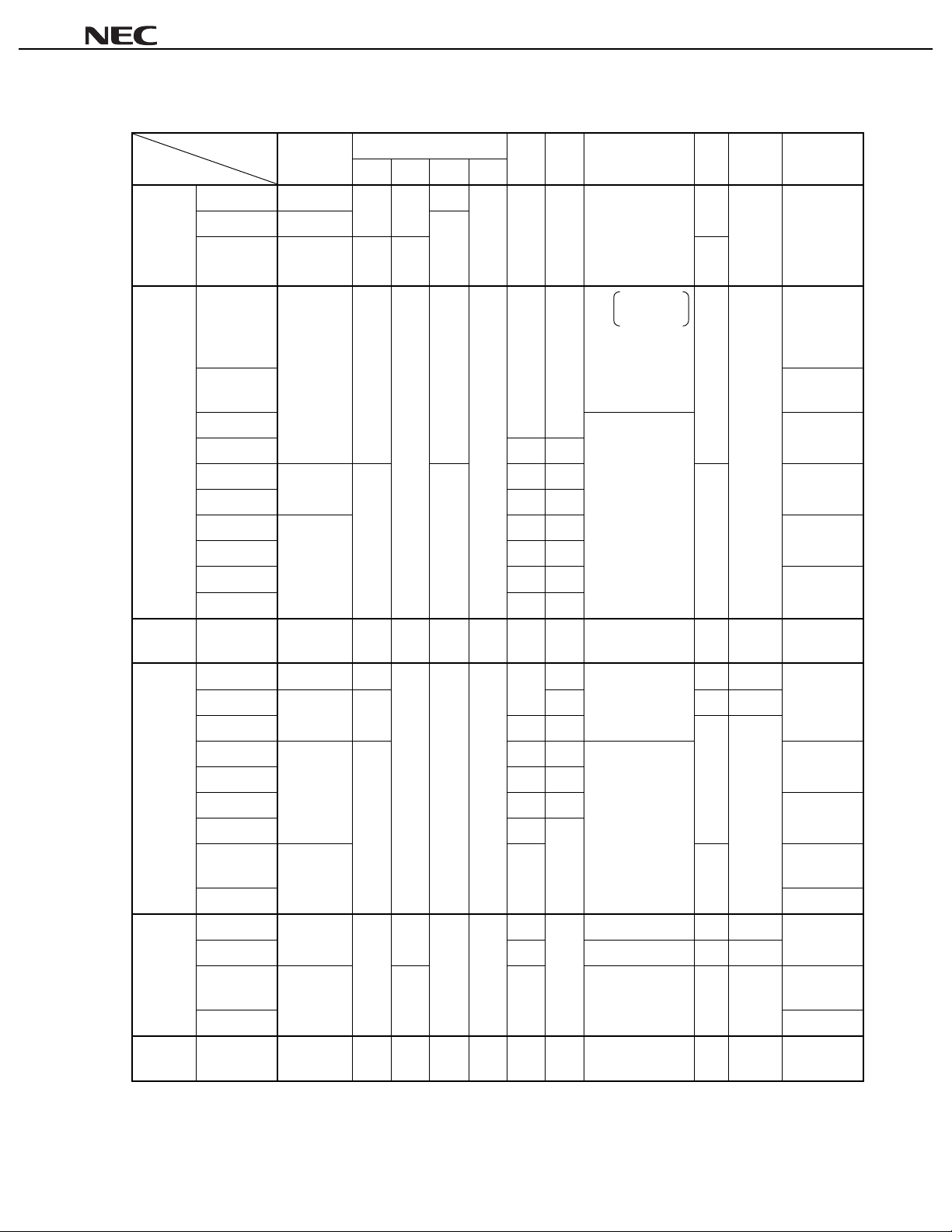

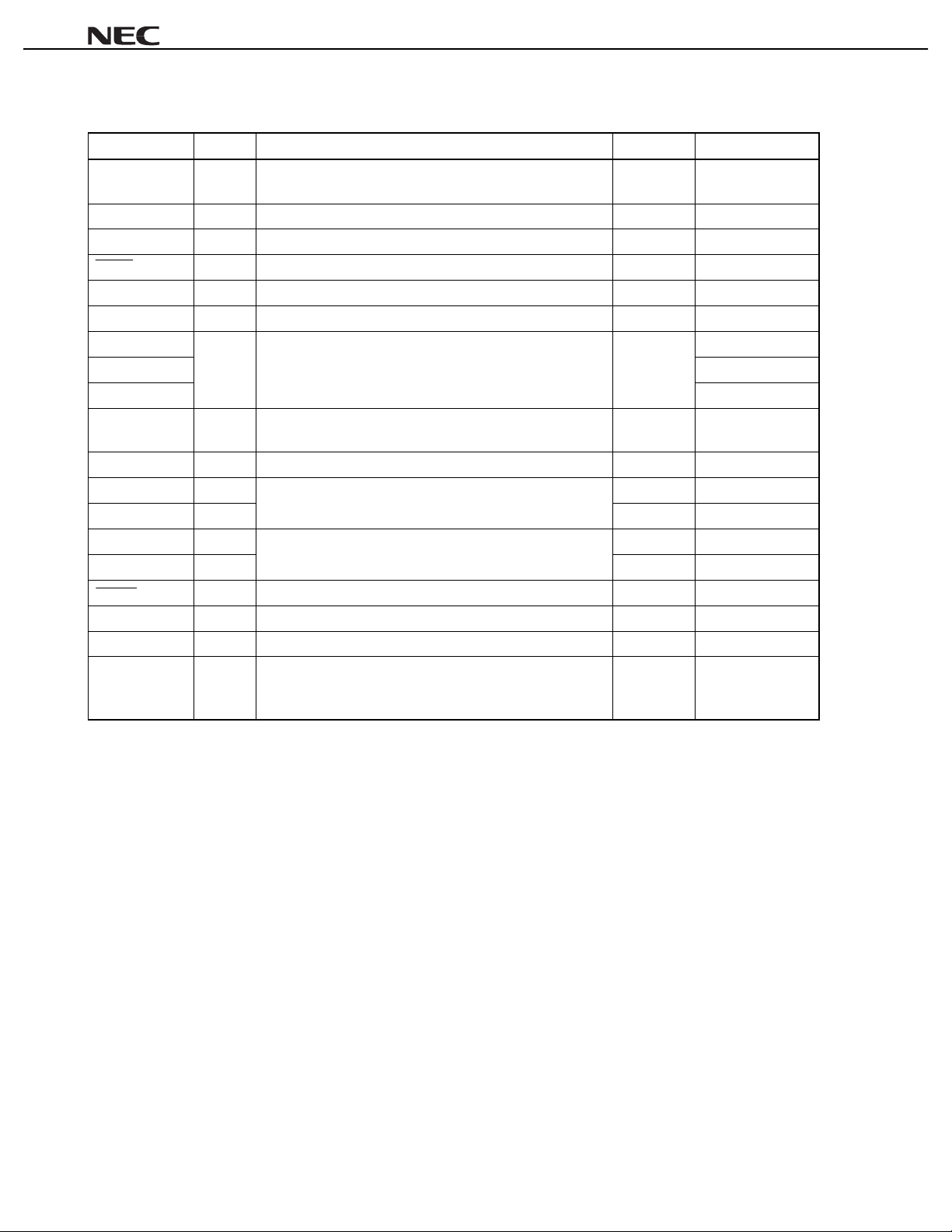

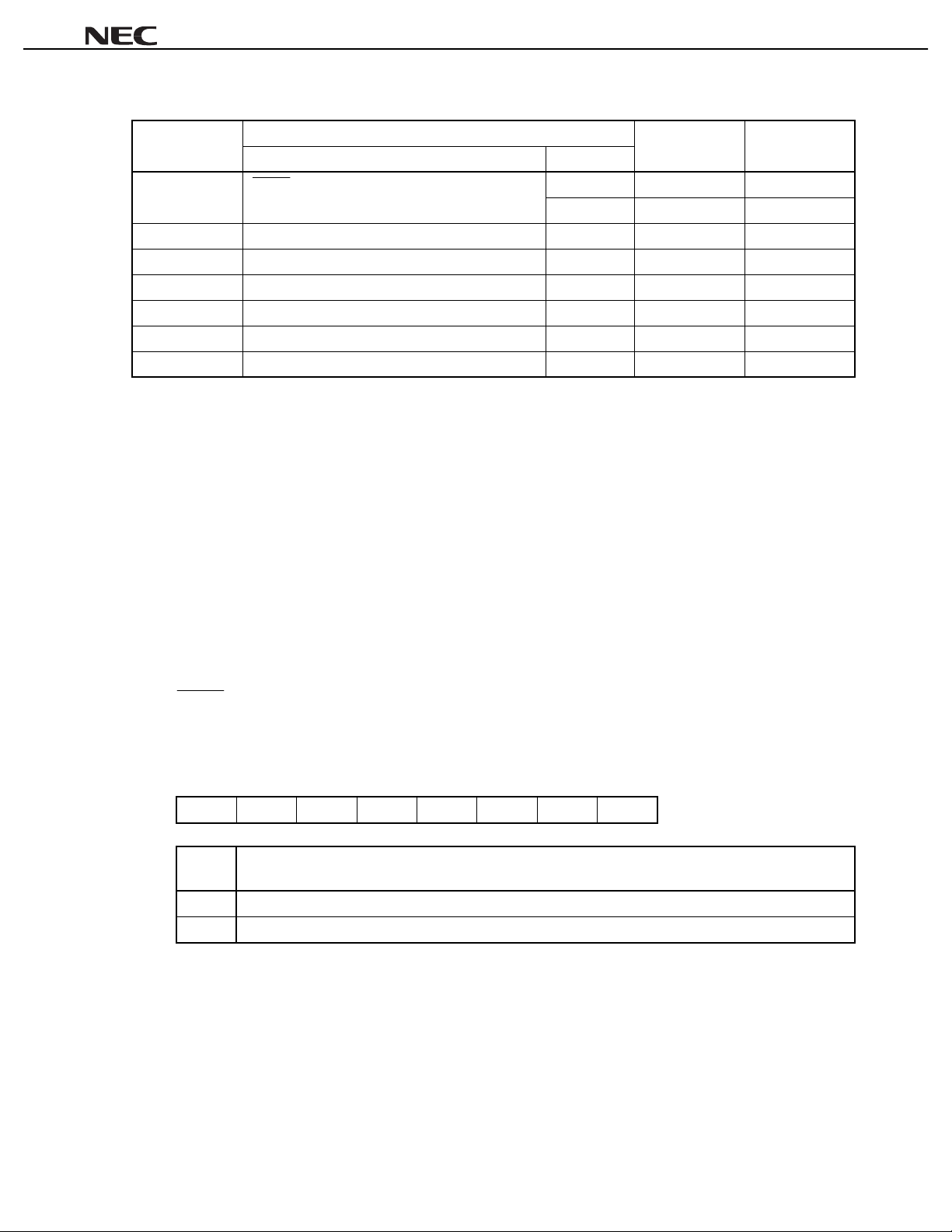

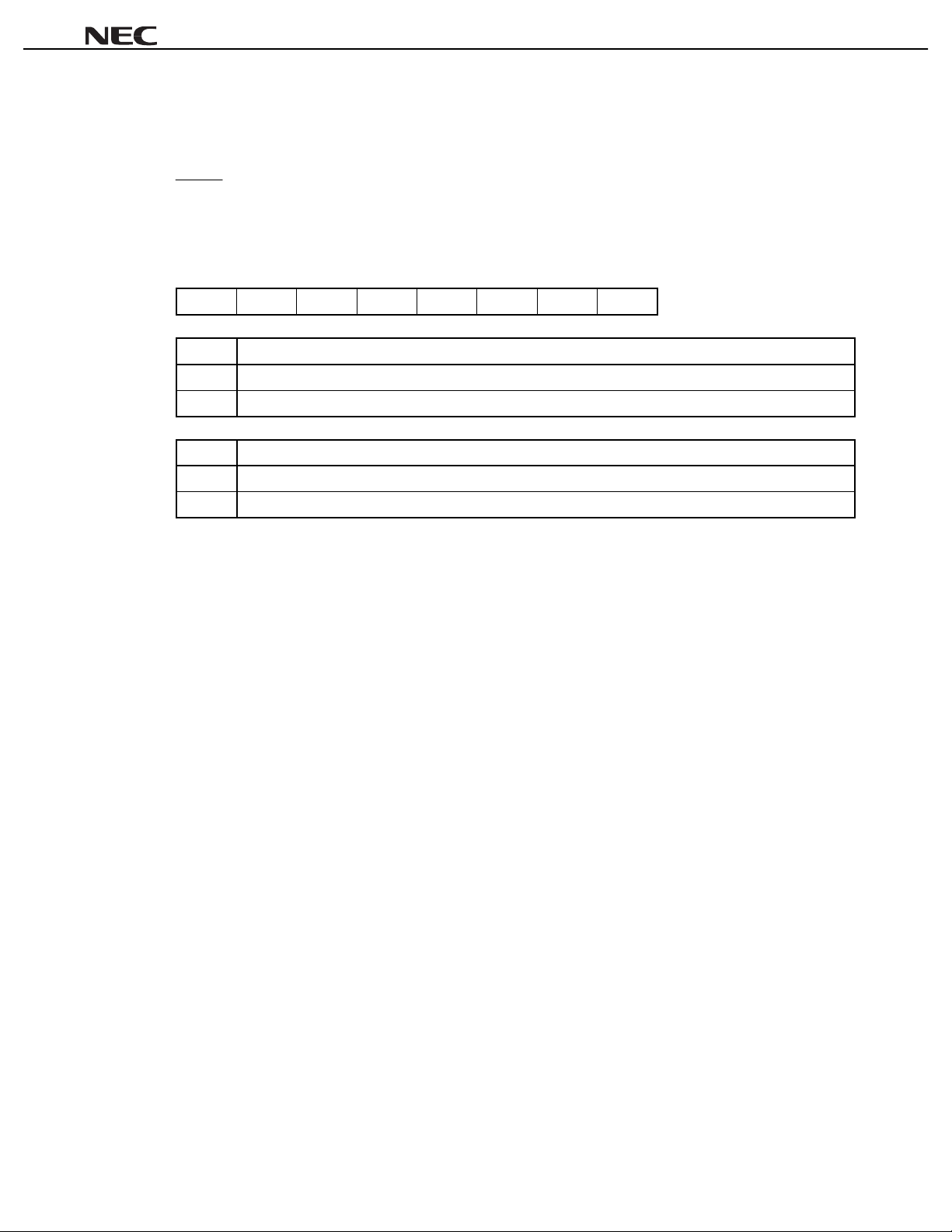

The major functional differences among the subseries are listed below.

µµµµ

PD78F9328

Subseries Name

PD789046 16 K 1 ch

Smallscale,

generalpurpose

applications

Smallscale,

generalpurpose

applications

+ A/D

Inverter

µ

PD789026 4 K to 16 K

µ

PD789014 2 K to 4 K 2 ch

µ

µ

PD789217AY

µ

PD789197AY

PD789177

µ

PD789167

µ

PD789156

µ

PD789146

µ

PD789134A

µ

µ

PD789124A

µ

PD789114A

PD789104A

µ

PD789842 8 K to 16 K 3 ch

µ

control

LCD drive

PD789830 24 K 1 ch

µ

PD789417A

µ

PD789407A

µ

PD789457

µ

PD789447 4 ch

µ

PD789437

µ

PD789427

µ

PD789316

µ

PD789306

µ

ROM

Capacity

8-Bit 16-Bit

TimerFunction

Watch

1 ch 1 ch 34

−

−

16 K to 24 K 3 ch 1 ch

8 K to 16 K

1 ch

1 ch

−

2 K to 8 K

Note

1 ch 1 ch 8 ch

1 ch 1 ch 1 ch

12 K to 24 K 3 ch

16 K to 24 K

2 ch

8 K to 16 K

WDT

1 ch

1 ch

8-Bit

10-Bit

A/D

−−

−

Serial Interface I/O V

A/D

1 ch (UART: 1 ch)

2 ch UART: 1ch

8 ch

SMB : 1ch

1 ch (UART: 1 ch)

8 ch

4 ch

4 ch

4 ch

−

4 ch

−

−

4 ch

−

−

4 ch

−

−

1 ch (UART: 1 ch) 30 4.0 V

−

1 ch (UART: 1 ch)

−

−

7 ch 43 1.8 V

7 ch

−

4 ch

−

2 ch (UART: 1 ch)

−

4 ch

−

4 ch

−

−

DD

Min.

Value

1.8 V

22

31

1.8 V

20

30 2.7 V

25

23

Remarks

−

RC oscillation

version,

on-chip

EEPROM

On-chip

EEPROM

−

On-chip

EEPROM

RC oscillation

version

−

−

−

RC oscillation

version

−

RC oscillation

version

−

ASSP

PD789800

µ

PD789840

µ

PD789861

µ

PD789860

µ

IC cardµPD789810 6 K

10-bit timer: 1 channel

Note

8 K 1 ch

4 K

2 ch

−

−−−

Preliminary Product Information U14411EJ1V0PM00

1 ch

−

−

2 ch (USB: 1 ch) 31 4.0 V

−

−

4 ch 1 ch 29 2.8 V

−

−

14 1.8 V

RC oscillation

version

−

1 ch

−− −

1 2.7 V

On-chip

EEPROM

3

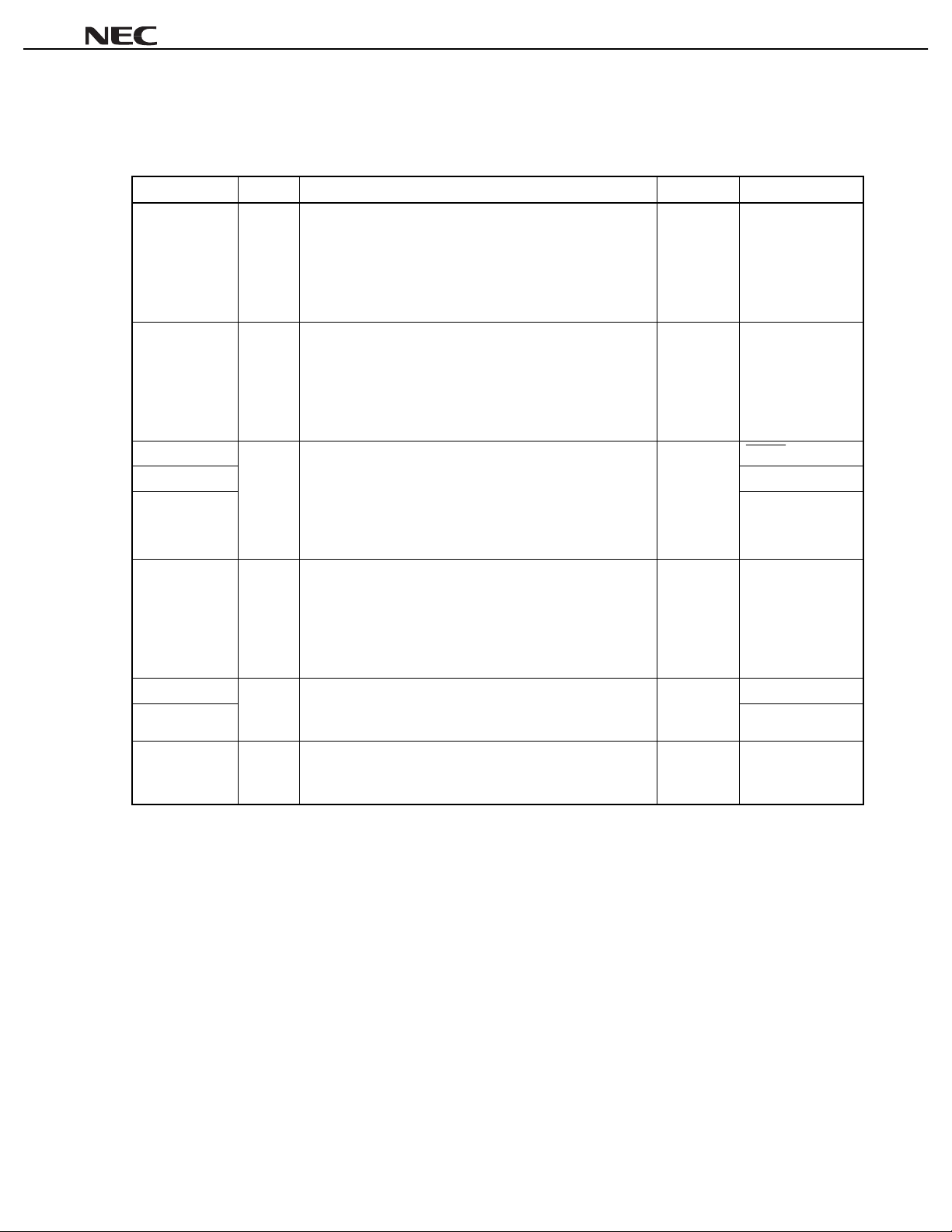

Page 4

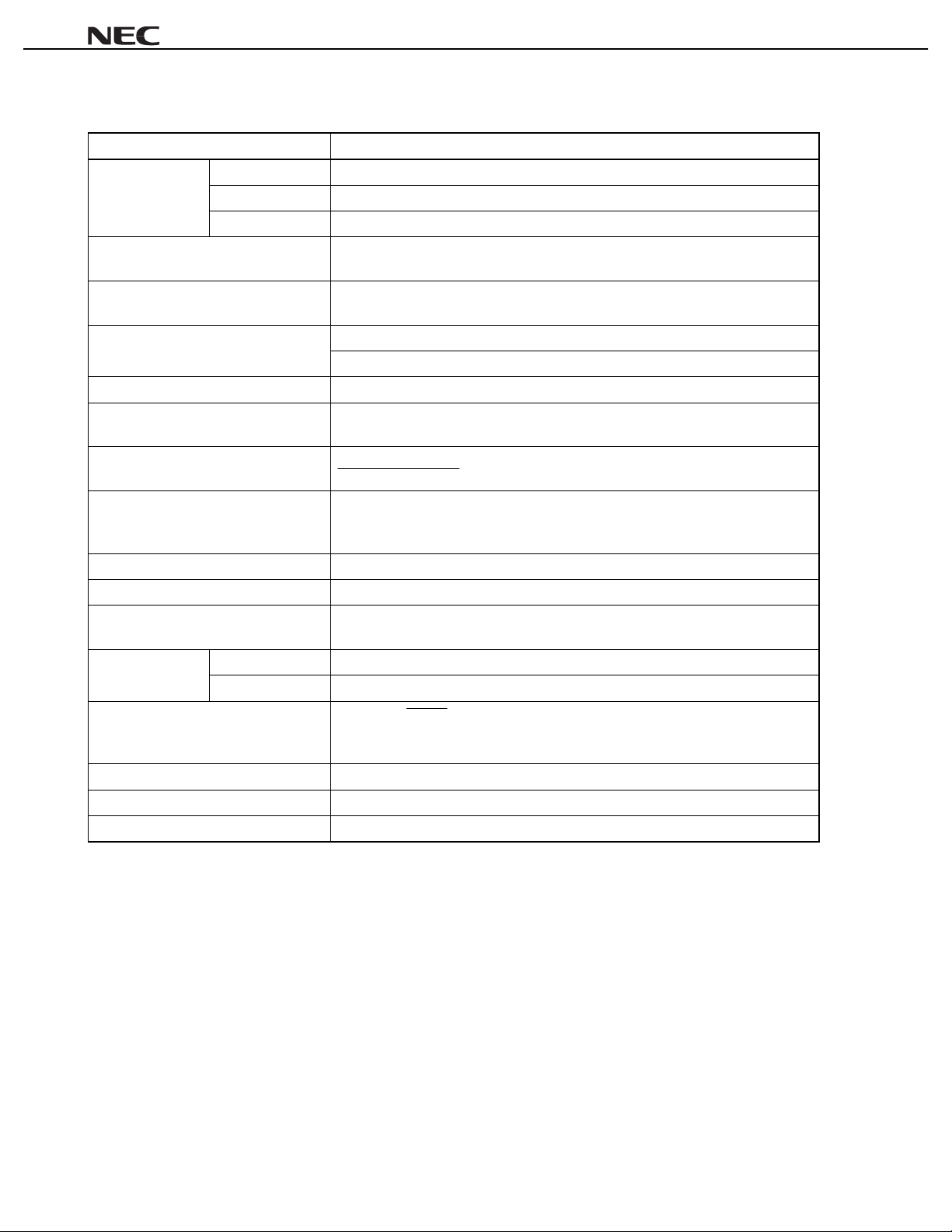

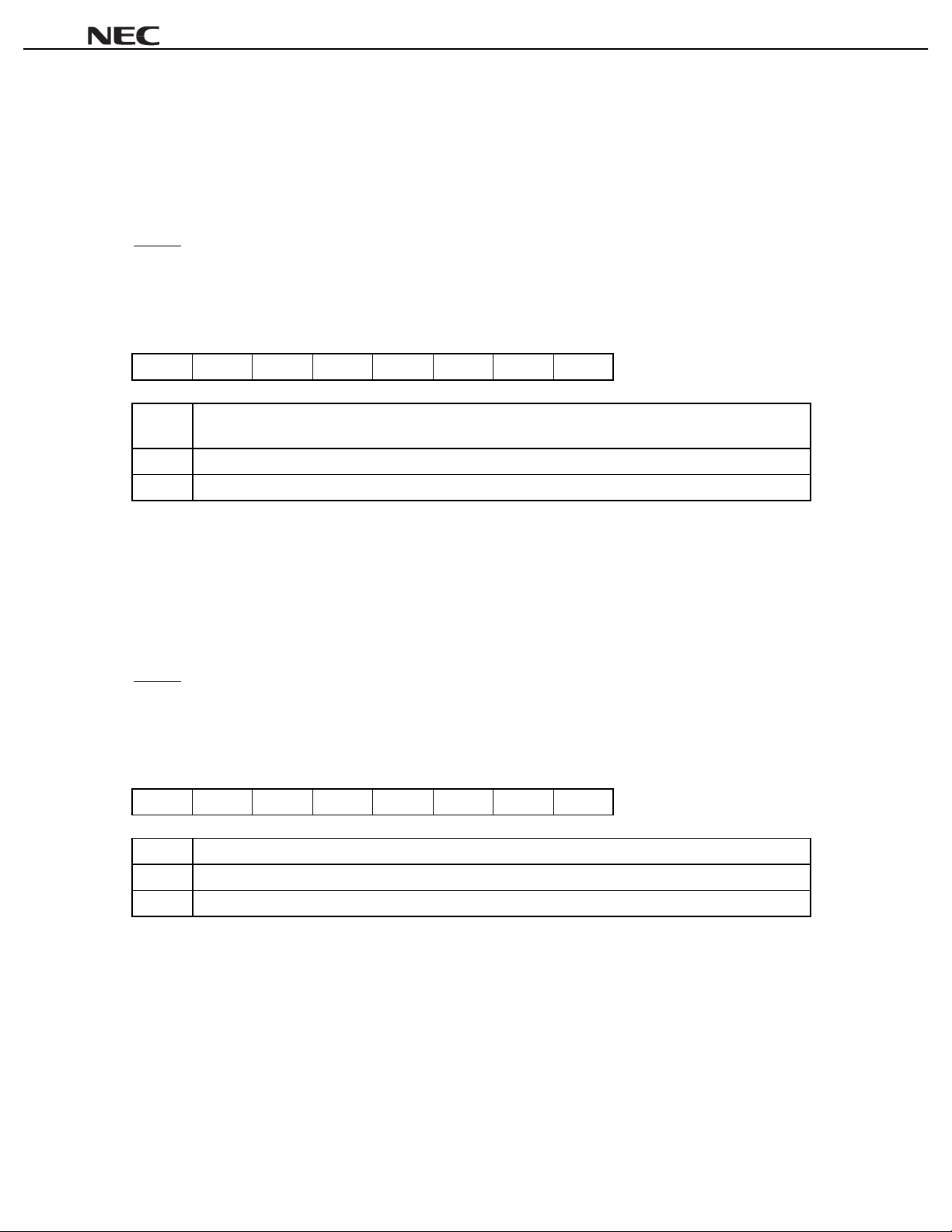

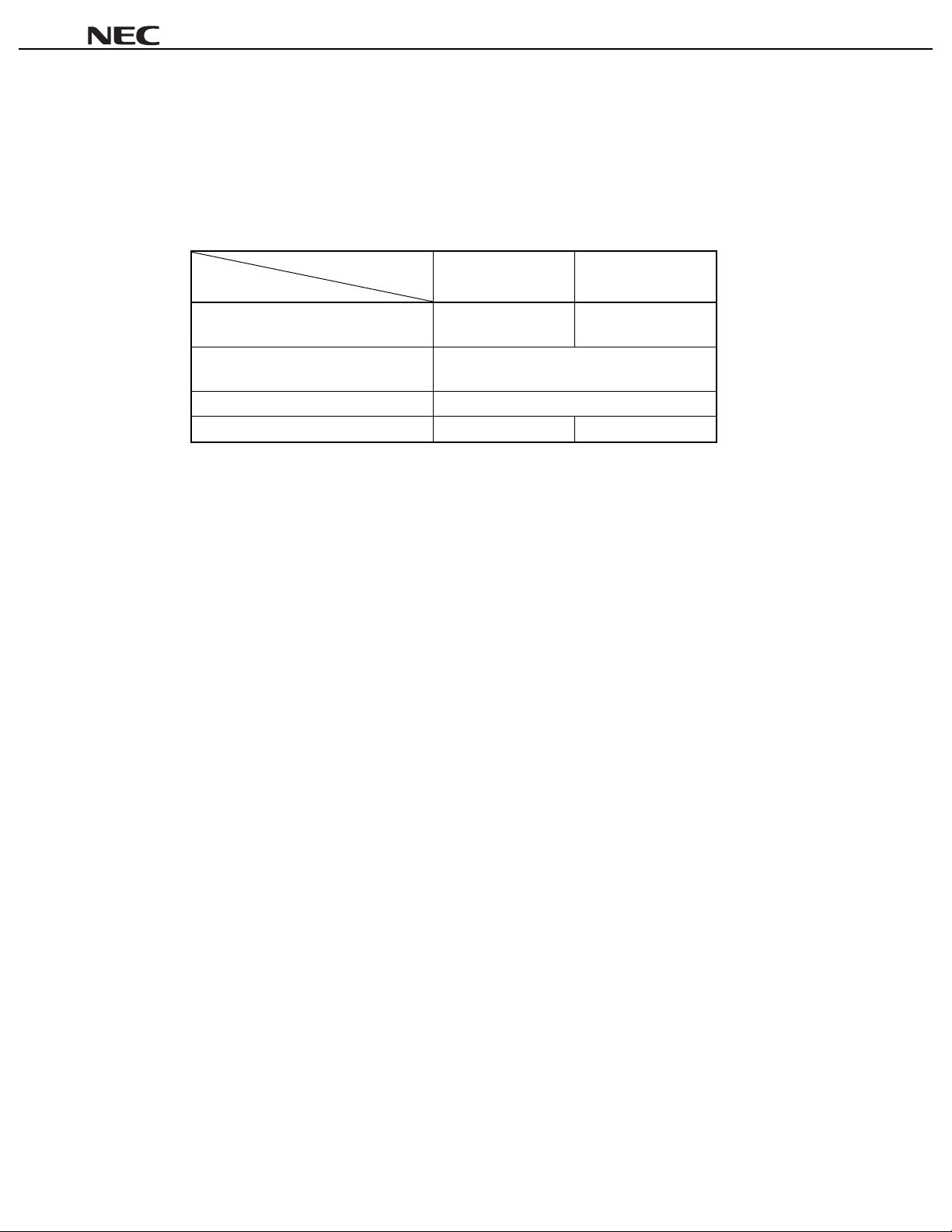

OVERVIEW OF FUNCTIONS

Item Description

µµµµ

PD78F9328

Internal memory

Main system clock

(oscillation frequency)

Subsystem clock

(oscillation frequency)

General-purpose registers 8 bits × 8 registers

Instruction set

I/O ports Total: 21

Timers

Timer outputs 1

Serial interface 3-wire serial I/O mode: 1 channel

LCD controller/driver

sources

Reset

Supply voltage VDD = 1.8 to 5.5 V

Operating ambient temperature TA = −40 to +85°C

Package 52-pin plastic LQFP (10 m m × 10 mm)

Flash memory 32 Kbytes

High-speed RAM 512 bytes

LCD display RAM 24 bytes

Ceramic/crystal resonator (1.0 to 5.0 MHz)

Crystal resonator (32.768 kHz)

0.4 µs/1.6 µs (@5.0-MHz operation with main system clock)Minimum instructi on execution time

122

s (@32.768-kHz operation with s ubsystem clock)

µ

16-bit operations

•

Bit manipulation (set, reset, test) etc.

•

CMOS I/O: 21

8-bit timer: 2 channels

•

Watch timer: 1 c hannel

•

Watchdog timer: 1 channel

•

Segment signal outputs: 24

•

Common signal outputs: 4

•

Maskable Internal: 6, External: 2Vectored interrupt

Non-maskable Internal: 1

Reset by RESET signal input

•

Internal reset by watchdog timer

•

Reset via power-on-clear circuit

•

4

Preliminary Product Information U14411EJ1V0PM00

Page 5

µµµµ

PD78F9328

CONTENTS

1. PIN CONFIGURATION (TOP VIEW) .................................................................................................... 7

2. BLOCK DIAGRAM.................................................................................................................................8

3. PIN FUNCTIONS....................................................................................................................................9

3.1 Port Pins......................................................................................................................................... 9

3.2 Non-Port Pins .............................................................................................................................. 10

3.3 Pin I/O Circuits and Recommended Connection of Unused Pins.......................................... 11

4. CPU ARCHITECTURE.........................................................................................................................13

4.1 Memory Space............................................................................................................................. 13

4.2 Data Memory Addressing........................................................................................................... 14

4.3 Processor Registers ................................................................................................................... 15

4.3.1 Control registers...............................................................................................................................15

4.3.2 General-purpose registers................................................................................................................16

4.3.3 Special function registers (SFRs).....................................................................................................17

5. PERIPHERAL HARDWARE FUNCTIONS ......................................................................................... 19

5.1 Ports.............................................................................................................................................19

5.1.1 Port functions....................................................................................................................................19

5.1.2 Port configuration .............................................................................................................................21

5.1.3 Port function control registers...........................................................................................................22

5.2 Clock Generator .......................................................................................................................... 25

5.2.1 Clock generator function...................................................................................................................25

5.2.2 Clock generator configuration...........................................................................................................25

5.2.3 Clock generator control registers......................................................................................................27

5.3 8-Bit Timer 30, 40 ........................................................................................................................ 30

5.3.1 Functions of 8-bit timer 30, 40..........................................................................................................30

5.3.2 Configuration of 8-bit timer 30, 40....................................................................................................31

5.3.3 8-bit timer 30, 40 control registers....................................................................................................36

5.4 Watch Timer.................................................................................................................................40

5.4.1 Watch timer functions.......................................................................................................................40

5.4.2 Watch timer configuration.................................................................................................................41

5.4.3 Watch timer control register..............................................................................................................42

5.5 Watchdog Timer.......................................................................................................................... 43

5.5.1 Watchdog timer functions.................................................................................................................43

5.5.2 Watchdog timer configuration...........................................................................................................43

5.5.3 Watchdog timer control register........................................................................................................44

5.6 Serial Interface 10........................................................................................................................ 45

5.6.1 Functions of serial interface 10 ........................................................................................................45

5.6.2 Configuration of serial interface 10...................................................................................................45

5.6.3 Control register for serial interface 10 ..............................................................................................47

5.7 LCD Controller/Driver ................................................................................................................. 49

5.7.1 LCD controller/driver functions.........................................................................................................49

5.7.2 LCD controller/driver configuration...................................................................................................49

Preliminary Product Information U14411EJ1V0PM00

5

Page 6

µµµµ

PD78F9328

5.7.3 LCD controller/driver control registers..............................................................................................52

6. INTERRUPT FUNCTION......................................................................................................................55

6.1 Interrupt Types ............................................................................................................................55

6.2 Interrupt Sources and Configuration ........................................................................................55

6.3 Interrupt Function Control Registers........................................................................................58

7. STANDBY FUNCTION.........................................................................................................................64

7.1 Standby Function........................................................................................................................64

7.2 Standby Function Control Register...........................................................................................66

8. RESET FUNCTION...............................................................................................................................67

8.1 Reset Function ............................................................................................................................67

8.2 Power Failure Detection Function.............................................................................................69

9. FLASH MEMORY PROGRAMMING...................................................................................................70

9.1 Selection of Communication Mode ...........................................................................................70

9.2 Flash Memory Programming Functions....................................................................................71

9.3 Flashpro III Connection Example...............................................................................................71

9.4 Setting Example Using Flashpro III (PG-FP3)...........................................................................72

10. INSTRUCTION SET OVERVIEW......................................................................................................73

10.1 Conventions...............................................................................................................................73

10.1.1 Operand formats and descriptions..................................................................................................73

10.1.2 Operation field definitions...............................................................................................................74

10.1.3 Flag operation field definitions........................................................................................................74

10.2 Operations..................................................................................................................................75

11. ELECTRICAL SPECIFICATIONS ......................................................................................................80

APPENDIX A. DIFFERENCES BETWEEN

APPENDIX B. DEVELOPMENT TOOLS ................................................................................................92

APPENDIX C. RELATED DOCUMENTS................................................................................................94

PD78F9328 AND MASK ROM VERSIONS................91

µµµµ

6

Preliminary Product Information U14411EJ1V0PM00

Page 7

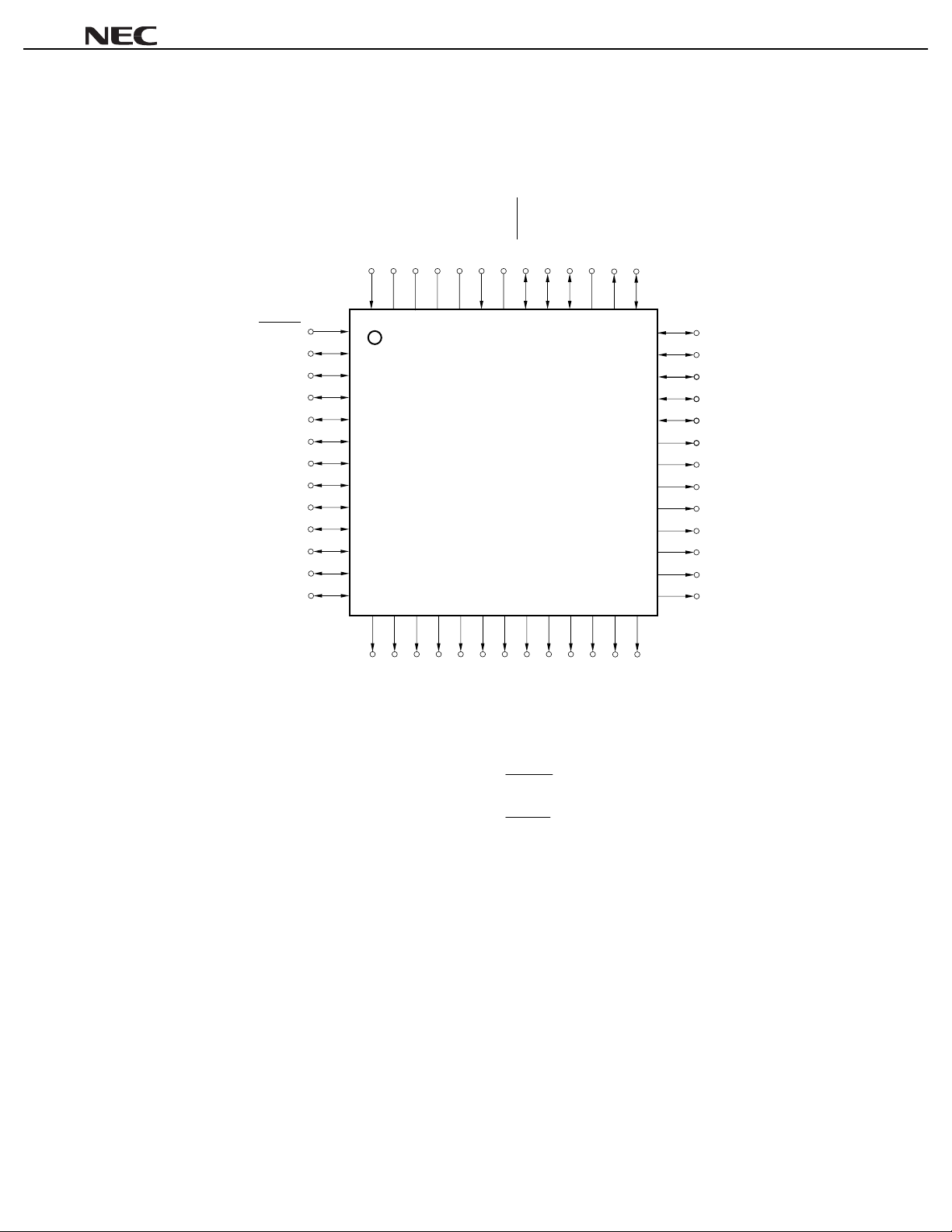

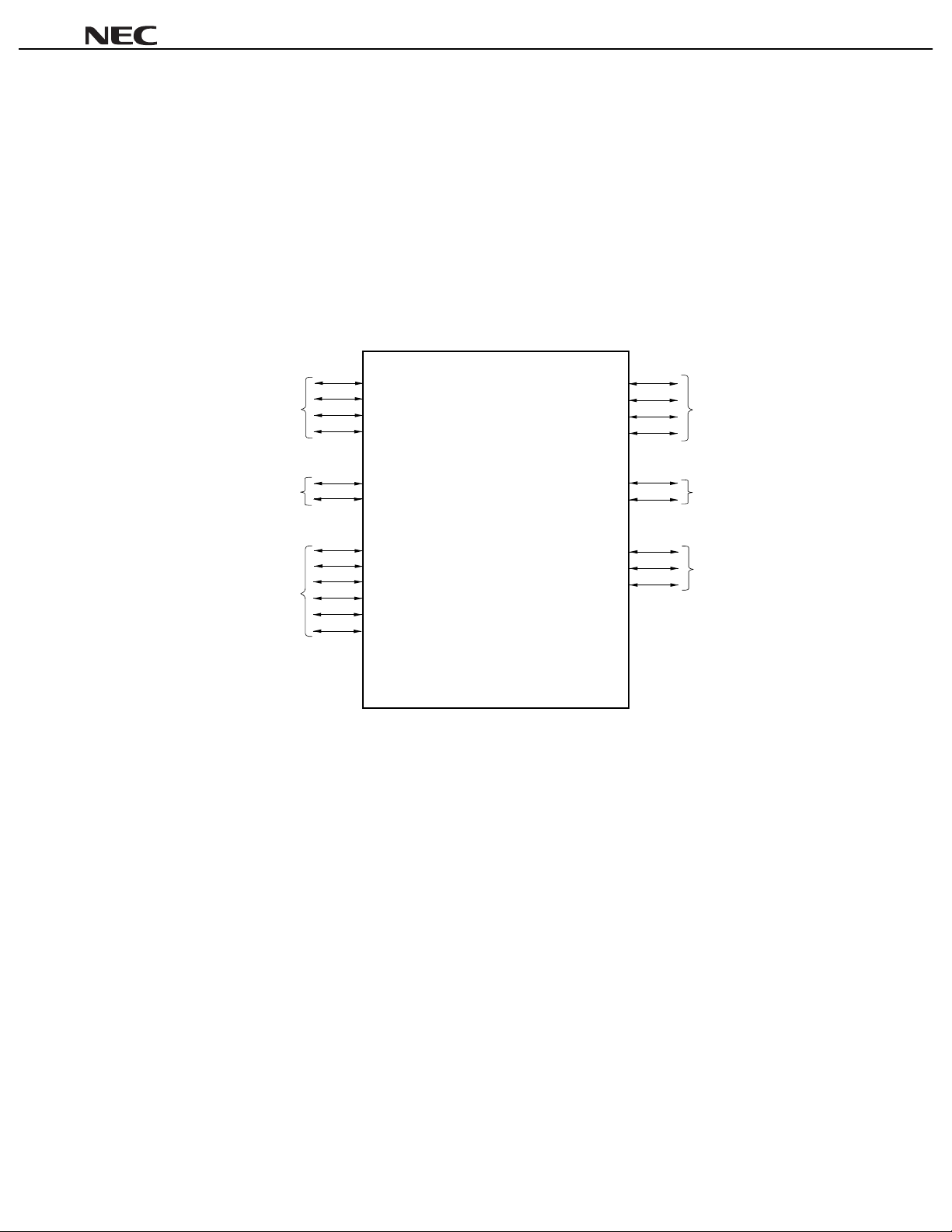

1. PIN CONFIGURATION (TOP VIEW)

µµµµ

PD78F9328

52-pin plastic LQFP (10 mm

PD78F9328GB-8ET

µµµµ

RESET

P60/TO40

P43/KR03

P42/KR02

P41/KR01

P40/KR00

P03

P02

P01

P00

INT/P61

P11

P10

10 mm)

××××

X1X2VDD

52 51 50 49 48 47 46 45 44 43 42

1

2

3

4

5

6

7

8

9

10

11

12

13

14 15 16 17 18 19 20 21 21 23 24

VSS

XT2

XT1

VPP

P20/SCK10

LC0

P21/SO10

P22/SI10

V

S23

41 40

26

25

P80/S22

39

38

37

36

35

34

33

32

31

30

29

28

27

P81/S21

P82/S20

P83/S19

P84/S18

P85/S17

S16

S15

S14

S13

S12

S11

S10

S9

COM0

COM1

COM2

COM3

S0

S1S2S3S4S5

S6

S7

S8

Caution In normal operation mode, directly connect the VPP pin to VSS.

COM0 to COM3: Common Output RESET: Reset

INT: Interrupt from Peripherals S0 to S23: Segment Output

KR00 to KR03: Key Return SCK10: Serial Clock Input/Output

P00 to P03: Port 0 SI10: Serial Data Input

P10, P11: Port 1 SO10: Serial Data Output

DD

P20 to P22: Port 2 V

P40 to P43: Port 4 V

: Power Supply

LC0

: Power Supply for LCD

P60, P61: Port 6 VPP: Programming Power Supply

P80 to P85: Port 8 VSS: Ground

TO40: Timer Output X1, X2: Crystal (Main system clock)

XT1, XT2: Crystal (Sabsystem clock)

Preliminary Product Information U14411EJ1V0PM00

7

Page 8

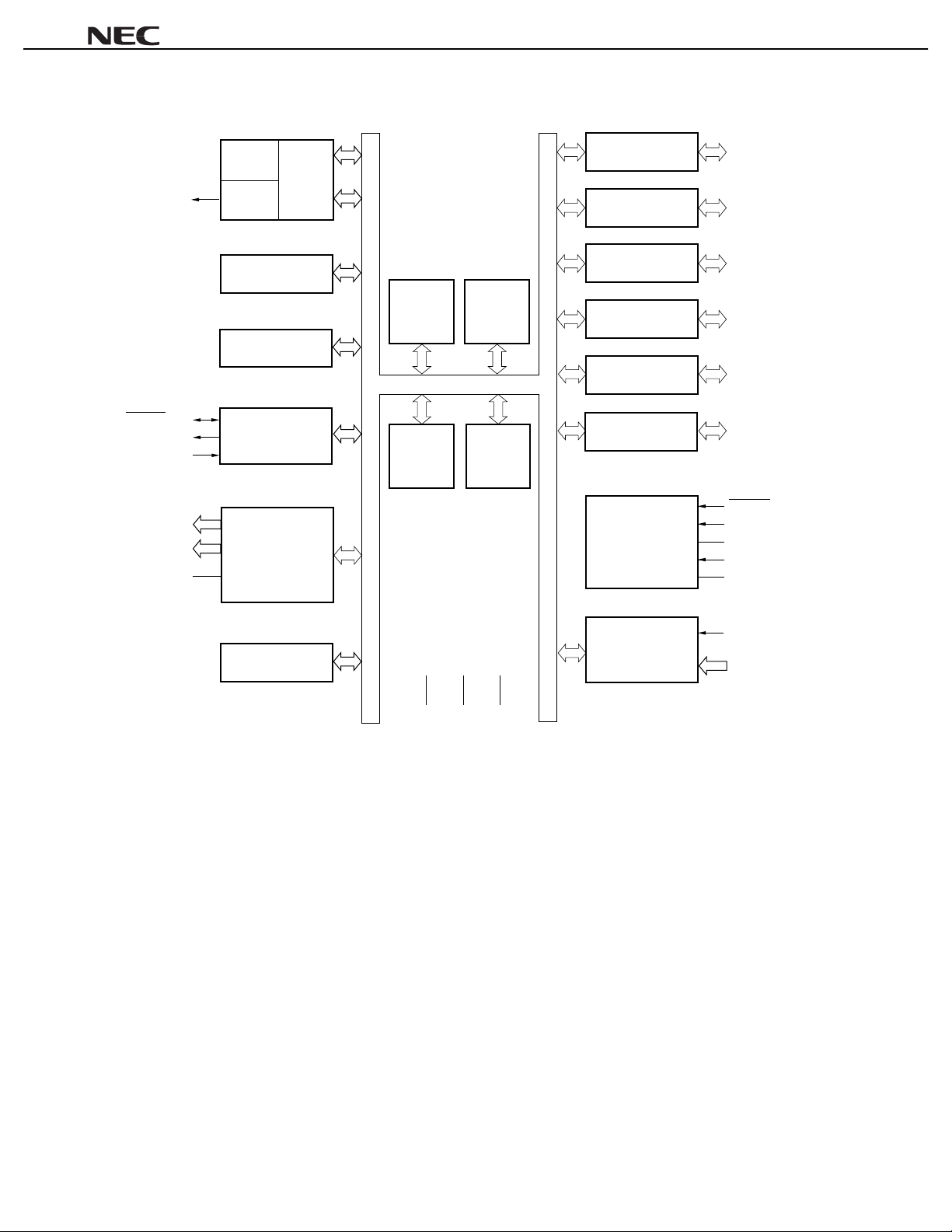

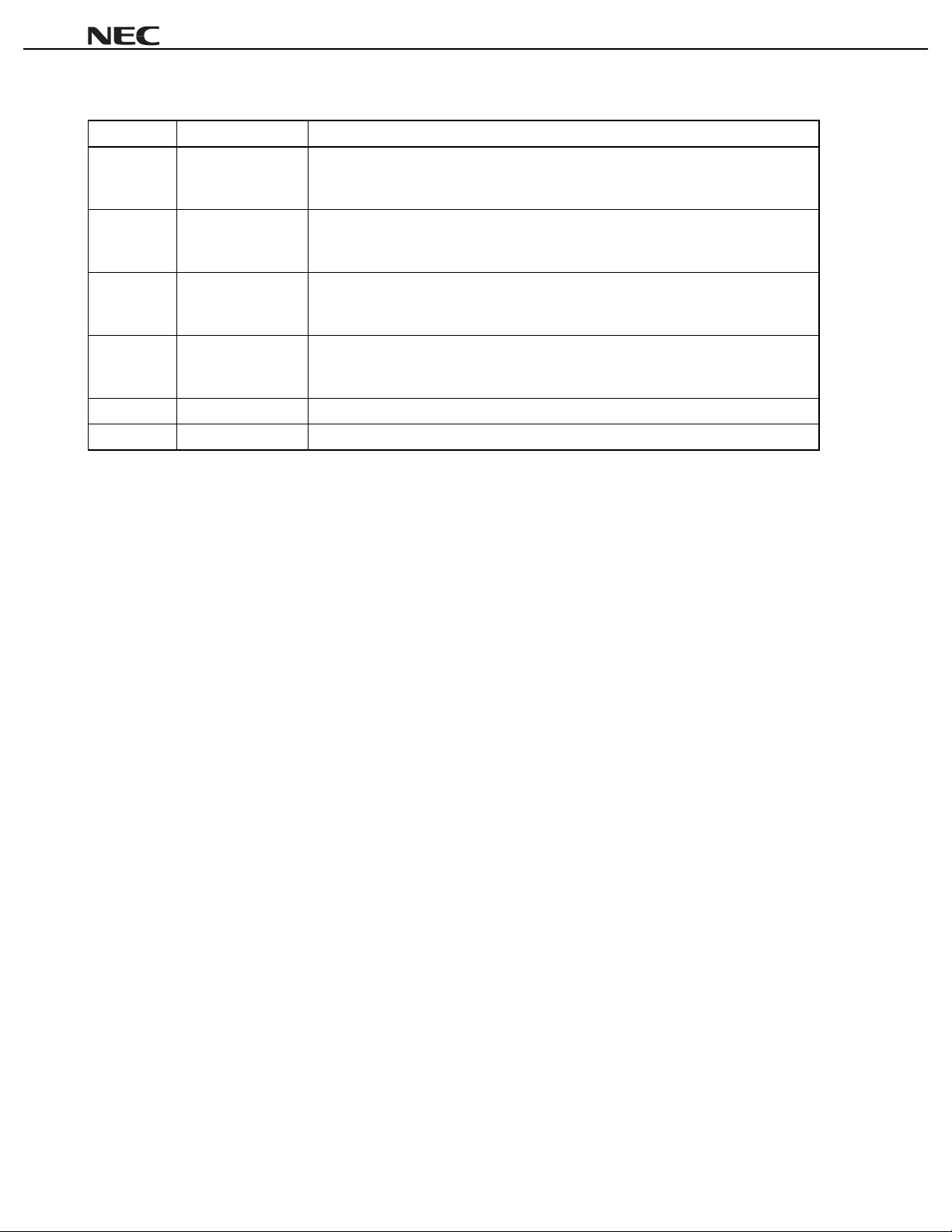

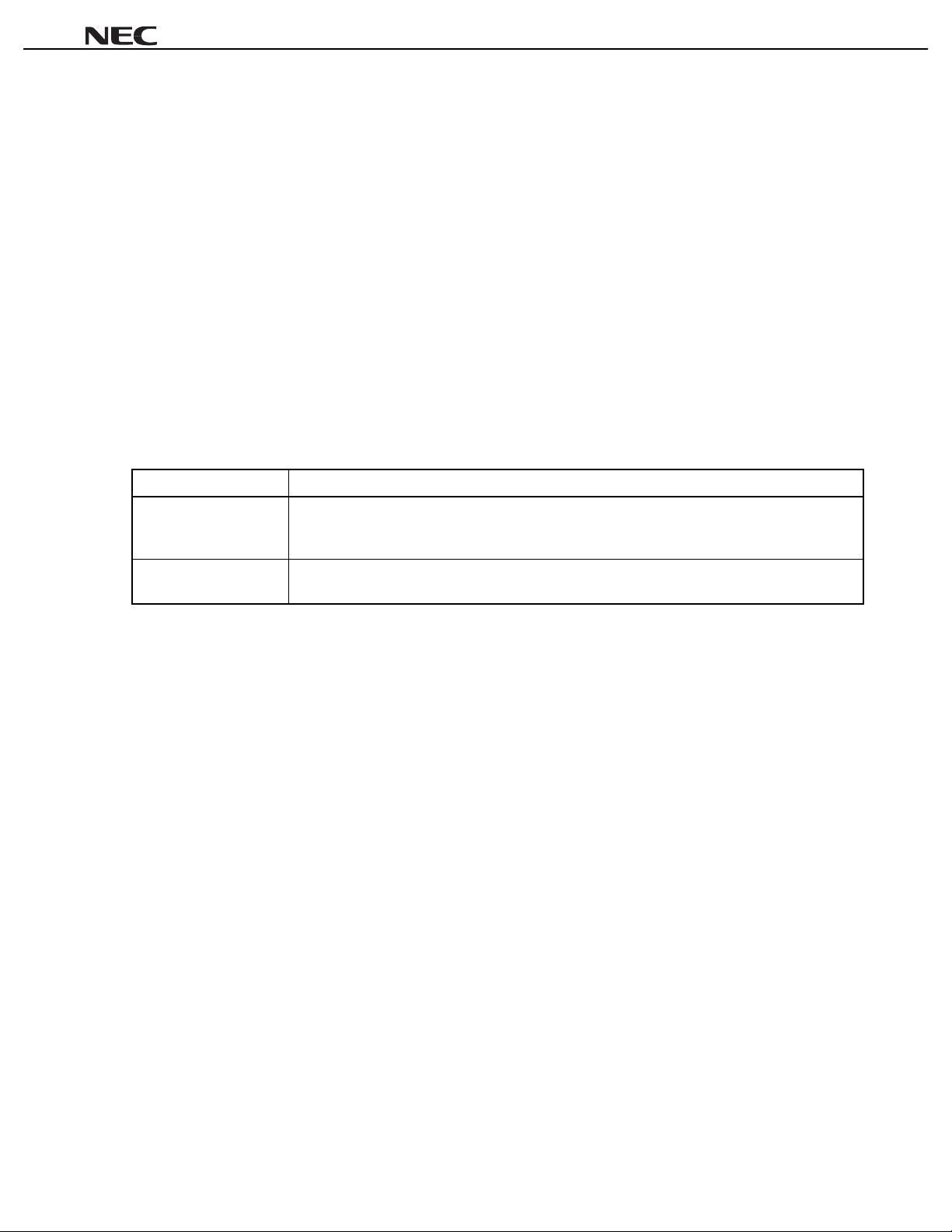

2. BLOCK DIAGRAM

µµµµ

PD78F9328

TO40/P60

SCK10/P20

SO10/P21

SI10/P22

S0 to S23

COM0 to COM3

V

LC0

8-bit

timer 30

8-bit

timer 40

Watchdog timer

Serial interface 10

Cascaded

16-bit

timer

Watch timer

LCD

controller/driver

78K/0S

CPU core

RAM

Flash

memory

RAM

space for

LCD data

Port 0

Port 1

Port 2

Port 4

Port 6

Port 8

System control

P00 to P03

P10, P11

P20 to P22

P40 to P43

P60, P61

P80 to P85

RESET

X1

X2

XT1

XT2

Power-on clear

VDDVSSV

INT/P61

Interrupt control

PP

KR00/P40 to

KR03/P43

8

Preliminary Product Information U14411EJ1V0PM00

Page 9

µµµµ

PD78F9328

3. PIN FUNCTIONS

3.1 Port Pins

Pin Name I/O Function Af ter Reset Alternate Function

P00 to P03 I/O Port 0.

This is a 4-bit I/O port.

Input/output can be spec i f i ed i n 1-bi t units.

When used as an input port, on-chip pull -up resistors can be

specified for the whole port using pull-up resistor option

register 0 (PU0).

P10, P11 I/O Port 1.

This is a 2-bit I/O port.

Input/output can be spec i f i ed i n 1-bi t units.

When used as an input port, on-chip pull -up resistors can be

specified for the whole port using pull-up resistor option

register 0 (PU0).

P20 SCK10

P21 SO10

P22

P40 to P43 I/O Port 4.

P60 TO40

P61

P80 to P85 I/O Port 8.

I/O Port 2.

This is a 3-bit I/O port.

Input/output can be spec i f i ed i n 1-bi t units.

When used as an input port, on-chip pull -up resistors can be

specified in 1-bit units using pull-up resistor option regi s ter 2

(PUB2).

This is a 4-bit I/O port.

Input/output can be spec i f i ed i n 1-bi t units.

When used as an input port, on-chip pull -up resistors can be

specified for the whole port using pull-up resistor option

register 0 (PU0), or key ret urn mode register 00 (KRM00).

I/O Port 6.

This is a 2-bit I/O port.

Input/output can be spec i f i ed i n 1-bi t units.

This is a 6-bit I/O port.

Input/output can be spec i f i ed i n 1-bi t units.

Input

Input

Input

SI10

Input KR00 to KR03

Input

INT

Low-level

output

S22 to S17

−

−

Preliminary Product Information U14411EJ1V0PM00

9

Page 10

µµµµ

PD78F9328

3.2

Non-Port Pins

Pin Name I/O Function Af ter Reset Alternate Function

INT Input External interrupt input f or whi ch the valid edge (rising edge,

falling edge, or both rising and falling edges) can be specified.

KR00 to KR03 Input Key return signal detection Input P40 to P43

TO40 Output 8-bit timer 40 output Input P60

SCK10 I/O Serial cl ock input/output of serial i nterface 10 Input P20

SI10 Input Serial data input of serial i nt erface 10 Input P22

SO10 Output Serial data out put of serial interface 10 Input P21

S0 to S16

S17 to S22 P85 to P80

S23

COM0 to COM3 Output LCD controller/driver common si gnal out puts Low-level

LC0

V

X1 Input

X2

XT1 Input

XT2

RESET Input System reset input Input

DD

V

SS

V

PP

V

Output LCD controller/driver segment signal outputs Low-level

LCD drive voltage

−

Connecting crystal res onator for main system clock oscillation

−

Connecting crystal res onator for subsystem clock oscillation

−

Positive power supply

−

Ground potential

−

Flash memory programming mode setting.

−

High-voltage application for program write/verify.

In normal operation mode, connect di rectly to V

SS

.

Input P61

output

output

−−

−−

−−

−−

−−

−−

−−

−−

−

−

−

−

10

Preliminary Product Information U14411EJ1V0PM00

Page 11

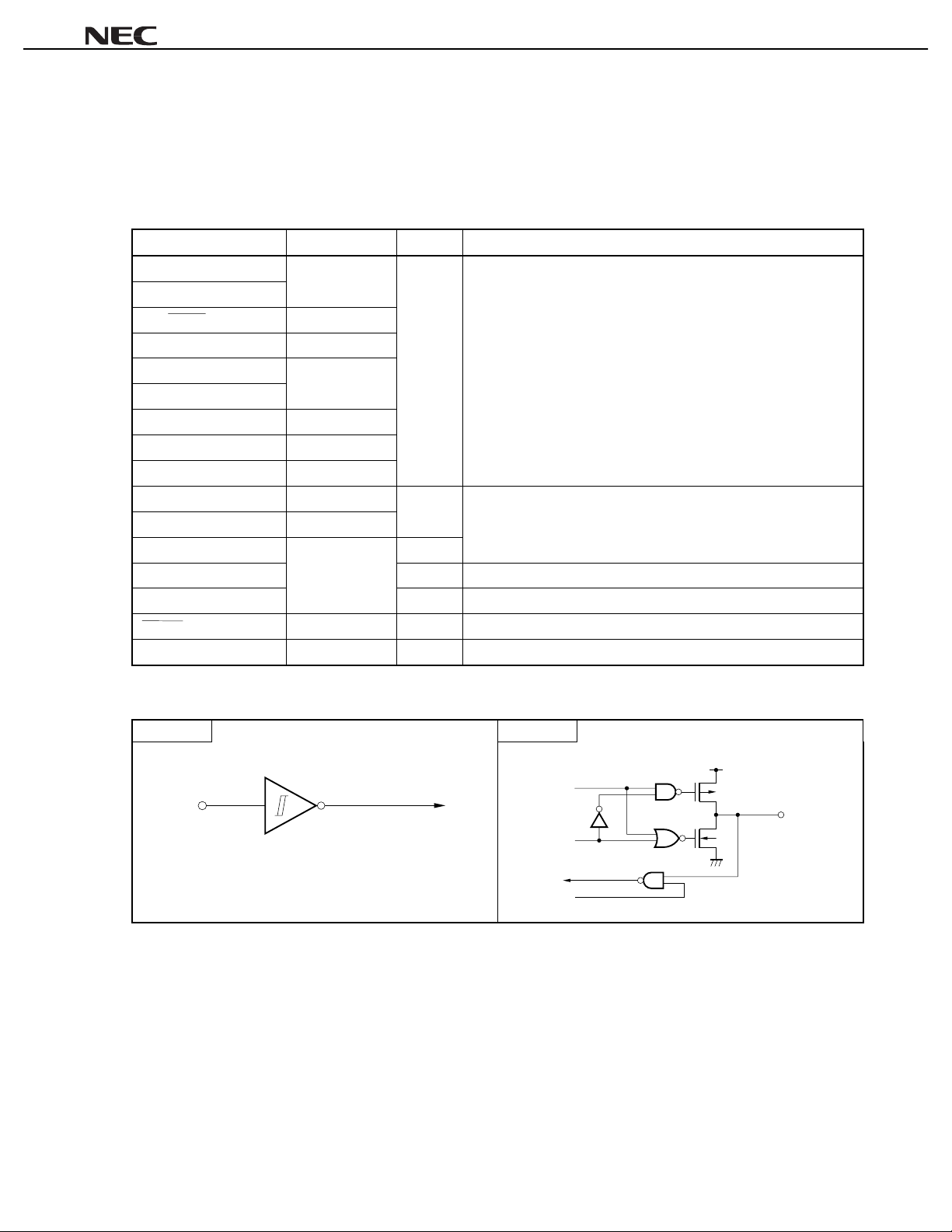

3.3 Pin I/O Circuits and Recommended Connection of Unused Pins

The I/O circuit type of each pin and recommended connection of unused pins is shown in Table 3-1.

For the input/output circuit configuration of each type, refer to Figure 3-1.

Table 3-1. Types of Pin I/O Circuits and Recommended Connection of Unused Pins

Pin Name I/O Ci rcuit Type I/O Recommend Connection of Unused Pi ns

P00 to P03

P10, P11

5-A

I/O Input: Independently connec t to V

Output: Leave open.

P20/SCK10 8-A

P21/SO10 5-A

P22/SI10

8-A

P40/KR00 to P43/KR03

P60/TO40 5

P61/INT 8

P80/S22 to P85/S17 17-G

S0 to S16, S23 17-D

Output

Leave open.

COM0 to COM3 18-B

LC0

V

−

−

XT1 Input Connect to VSS.

XT2

−

Leave open.

RESET 2 Input

PP

V

−−

Connect directly to V

SS

.

DD

or VSS via a resistor.

−

µµµµ

PD78F9328

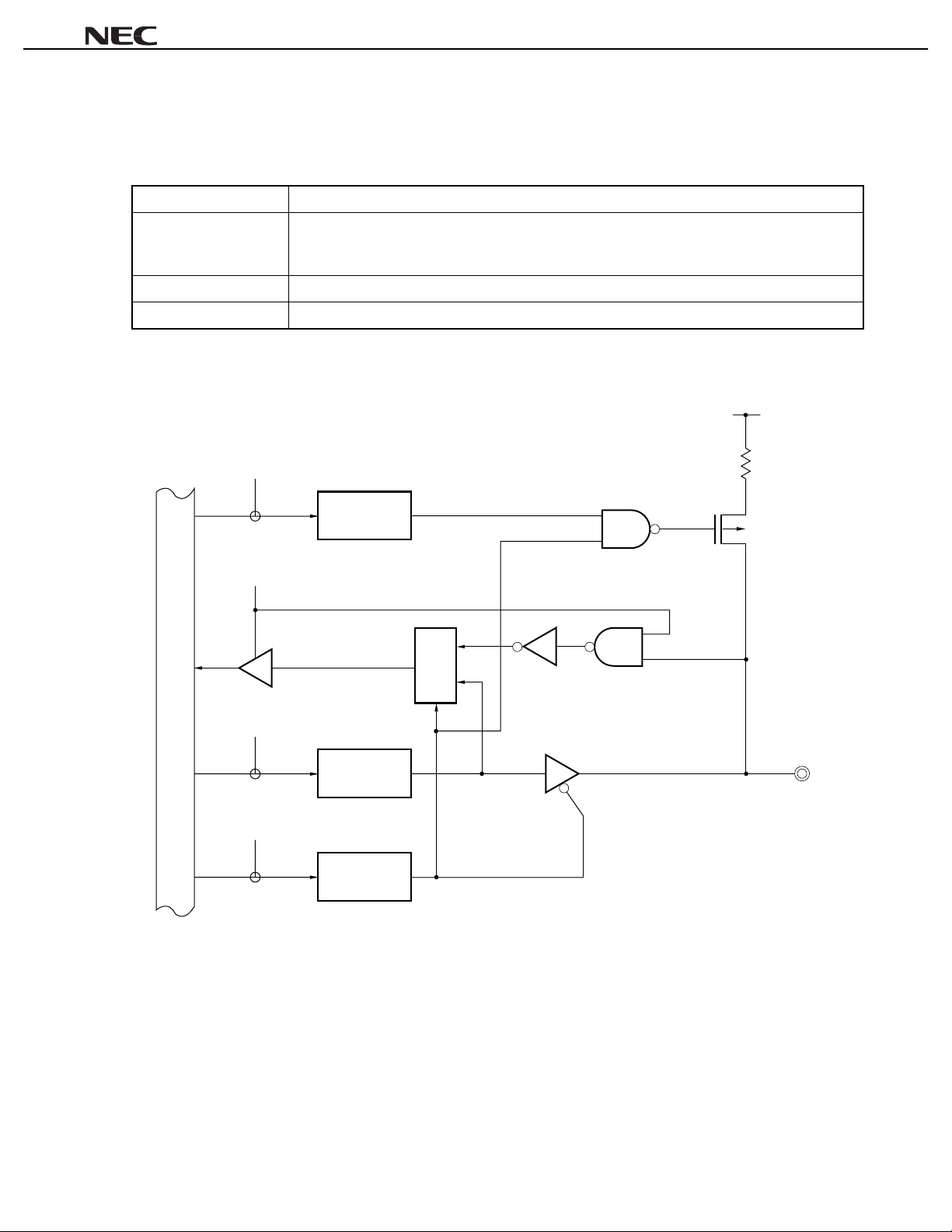

Figure 3-1. I/O Circuit Type (1/2)

Type 2 Type 5

IN

Output

disable

Schmitt-triggered input with hysteresis characteristics.

Input

enable

Data

V

DD

P-ch

IN/OUT

N-ch

V

SS

Preliminary Product Information U14411EJ1V0PM00

11

Page 12

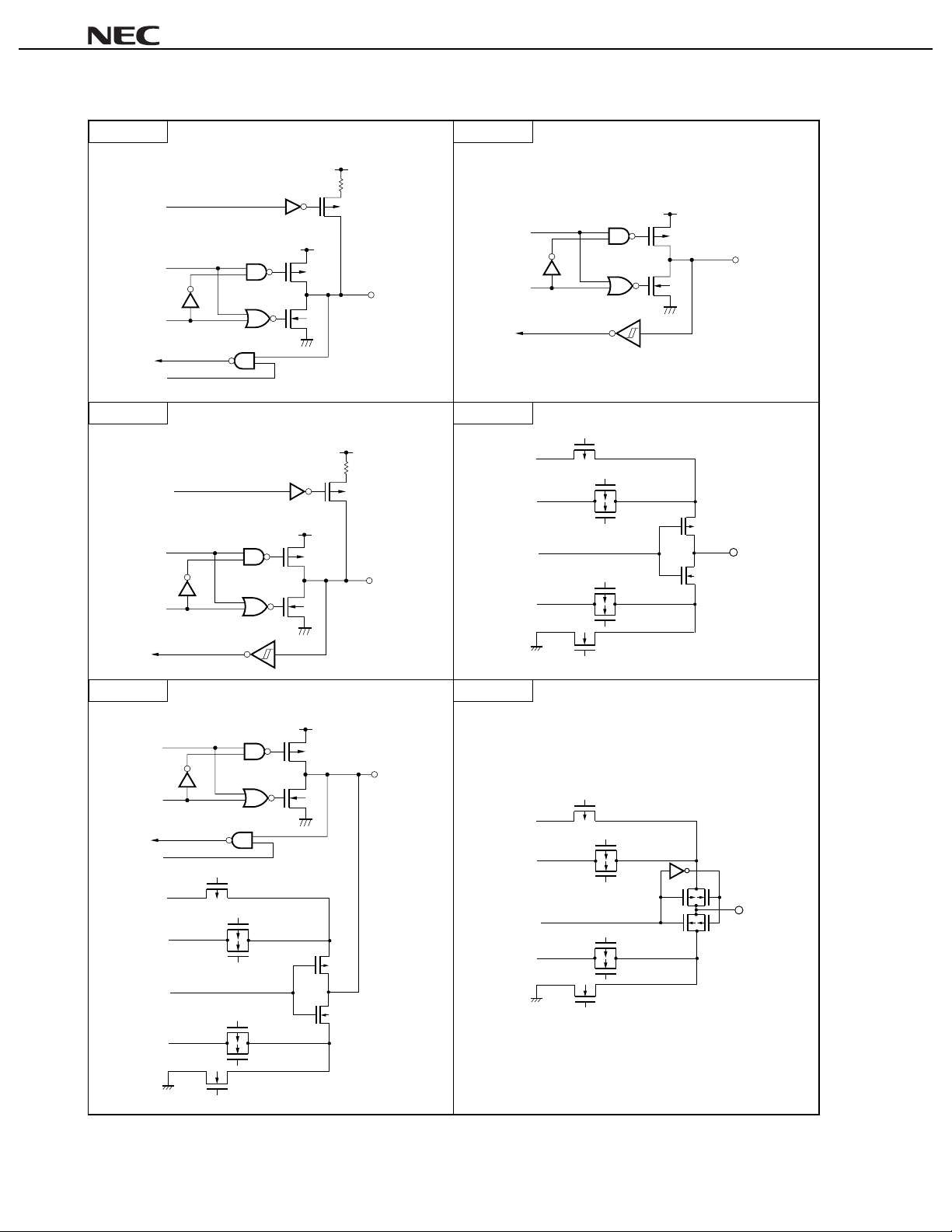

Figure 3-1. I/O Circuit Type (2/2)

Type 5-A Type 8

V

DD

µµµµ

PD78F9328

Pull-up

enable

Data

Output

disable

V

SS

V

DD

P-ch

N-ch

P-ch

IN/OUT

Data

Output

disable

Input

enable

Type 8-A Type 17-D

DD

V

V

Pull-up

enable

Data

V

DD

P-ch

P-ch

VLC3

SEG

IN/OUT

Output

disable

N-ch

V

SS

V

LC0

data

LC2

P-ch

P-ch

N-ch

N-ch

P-ch

N-ch

V

DD

P-ch

IN/OUT

N-ch

V

SS

P-ch

OUT

N-ch

Type 17-G Type 18-B

DD

V

Data

P-ch

IN/OUT

Output

disable

N-ch

VSS

Input

enable

LC0

V

VLC1

P-ch

P-ch

N-ch

P-ch

COM

data

V

SEG

data

N-ch

V

LC2

P-ch

N-ch

N-ch

V

SS

SS

V

V

LC0

LC1

V

P-ch

P-ch

N-ch

P-ch

N-ch

OUT

P-ch

LC2

N-ch

P-ch

N-ch

N-ch

V

SS

Remark

12

V

LC1

: V

LC0

× 2/3, V

LC2

LC0

: V

/3

Preliminary Product Information U14411EJ1V0PM00

Page 13

µµµµ

PD78F9328

4. CPU ARCHITECTURE

4.1 Memory Space

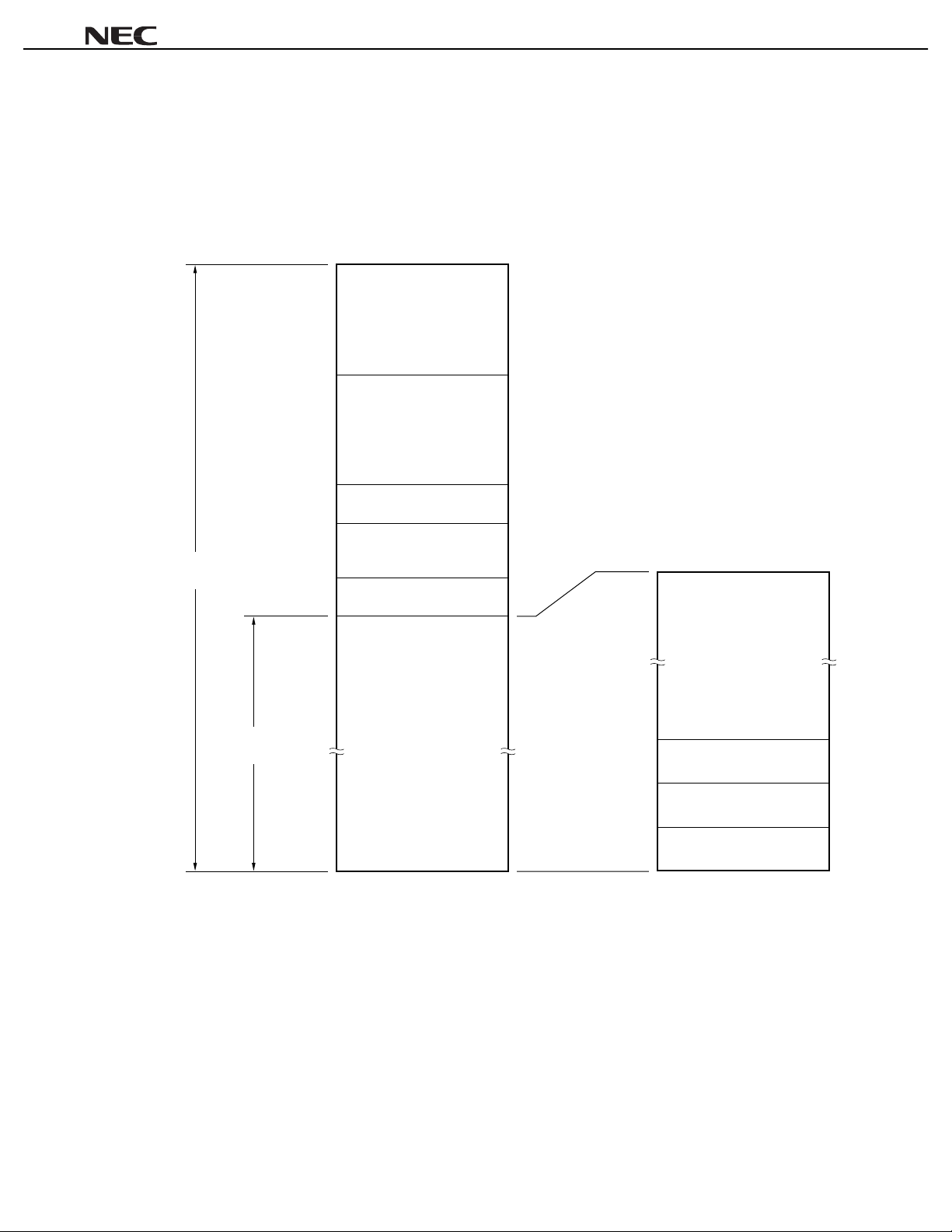

The µPD78F9328 is provided with 64 Kbytes of accessible memory space. Figure 4-1 shows the memory map.

Figure 4-1. Memory Map

F F F F H

Special function registers

256 × 8 bits

F F 0 0 H

F E F F H

Internal high-speed RAM

512 × 8 bits

F D 0 0 H

Data memory

space

F C F F H

F A 1 8 H

F A 1 7 H

F A 0 0 H

F 9 F F H

8 0 0 0 H

7 F F F H

Reserved

LCD display RAM

24 × 8 bits

7 F F F H

Reserved

Program

memory space

0 0 0 0 H

Flash memory

32 K × 8 bits

0 0 8 0 H

0 0 7 F H

0 0 4 0 H

0 0 3 F H

0 0 1 4 H

0 0 1 3 H

0 0 0 0 H

Program area

CALLT table area

Program area

Vector table area

Preliminary Product Information U14411EJ1V0PM00

13

Page 14

µµµµ

PD78F9328

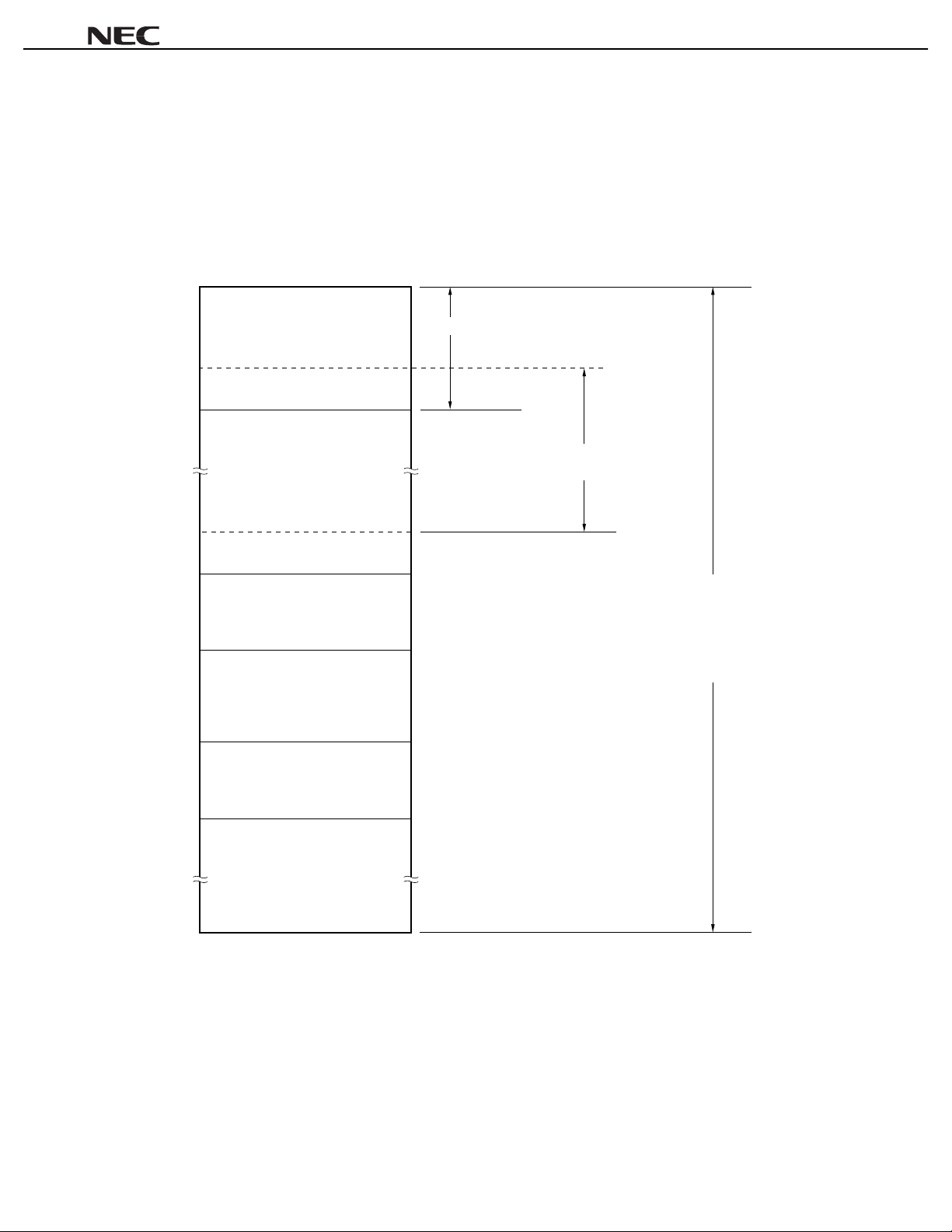

4.2 Data Memory Addressing

The µPD78F9328 is provided with a variety of addressing modes to improve the operability of the memory. In the

area that incorporates data memory (FD00H to FFFFH) in particular, specific addressing modes that correspond to

the particular functions of an area, such as the special function registers (SFRs), are available. Figure 4-2 shows the

data memory addressing modes.

Figure 4-2. Data Memory Addressing Modes

F F F F H

Special function registers (SFRs)

256 × 8 bits

F F 2 0 H

F F 1 F H

F F 0 0 H

F E F F H

SFR addressing

F E 2 0 H

F E 1 F H

F D 0 0 H

F C F F H

F A 1 8 H

F A 1 7 H

F A 0 0 H

F 9 F F H

8 0 0 0 H

7 F F F H

Internal high-speed RAM

512 × 8 bits

Reserved

LCD display RAM

24 × 8 bits

Reserved

Flash memory

32 K × 8 bits

Short direct

addressing

Direct addressing

Register indirect

addressing

Based addressing

14

0 0 0 0 H

Preliminary Product Information U14411EJ1V0PM00

Page 15

µµµµ

PD78F9328

4.3 Processor Registers

4.3.1 Control registers

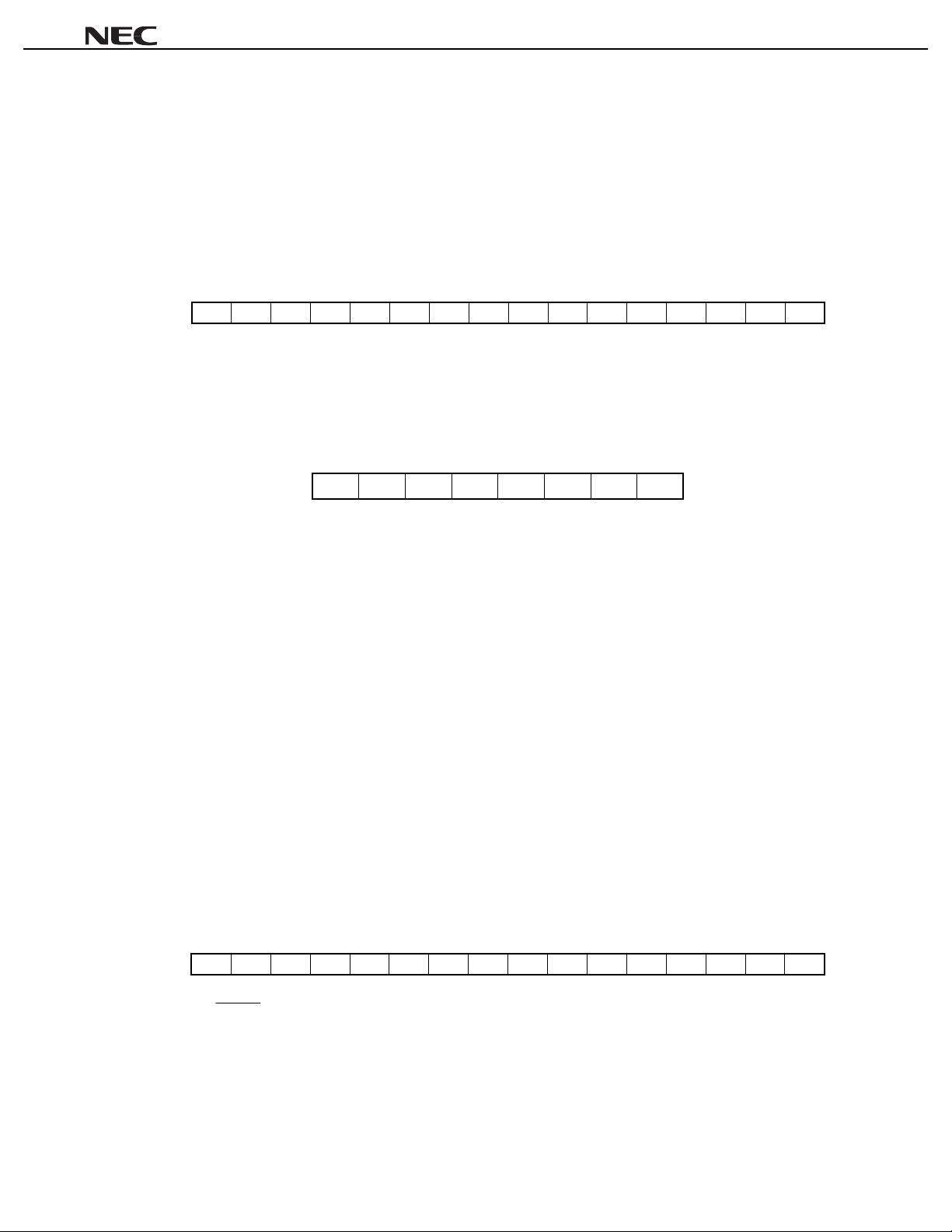

(1) Program counter (PC)

The PC is a 16-bit register that holds the address information of the next program to be executed.

Figure 4-3. Program Counter Configuration

PC14PC15PC PC13 PC12 PC11 PC10 PC9 PC8 PC7 PC6 PC5 PC4 PC3 PC2 PC1 PC0

(2) Program status word (PSW)

The PSW is an 8-bit register that indicates the status of the CPU according to the results of instruction execution.

Figure 4-4. Program Status Word Configuration

70

IE Z 0 AC 0 0 1 CY

015

(a) Interrupt enable flag (IE)

This flag controls the interrupt request acknowledgement of the CPU.

(b) Zero flag (Z)

This flag is set (1) if the result of an operation is zero; otherwise it is reset (0).

(c) Auxiliary carry flag (AC)

AC is set (1) if the result of the operation has a carry from bit 3 or a borrow at bit 3; otherwise it is reset (0).

(d) Carry flag (CY)

CY is used to indicate whether an overflow or underflow has occurred during the execution of a subtract or

add instruction.

(3) Stack pointer (SP)

The SP is a 16-bit register that holds the start address of the stack area. Only the internal RAM area (FD00H to

FEFFH) can be specified as the stack area.

Figure 4-5. Stack Pointer Configuration

SP14SP15SP SP13 SP12 SP11 SP10 SP9 SP8 SP7 SP6 SP5 SP4 SP3 SP2 SP1 SP0

015

Caution RESET input makes the SP contents undefined, so be sure to initialize the SP before instruction

execution.

Preliminary Product Information U14411EJ1V0PM00

15

Page 16

µµµµ

PD78F9328

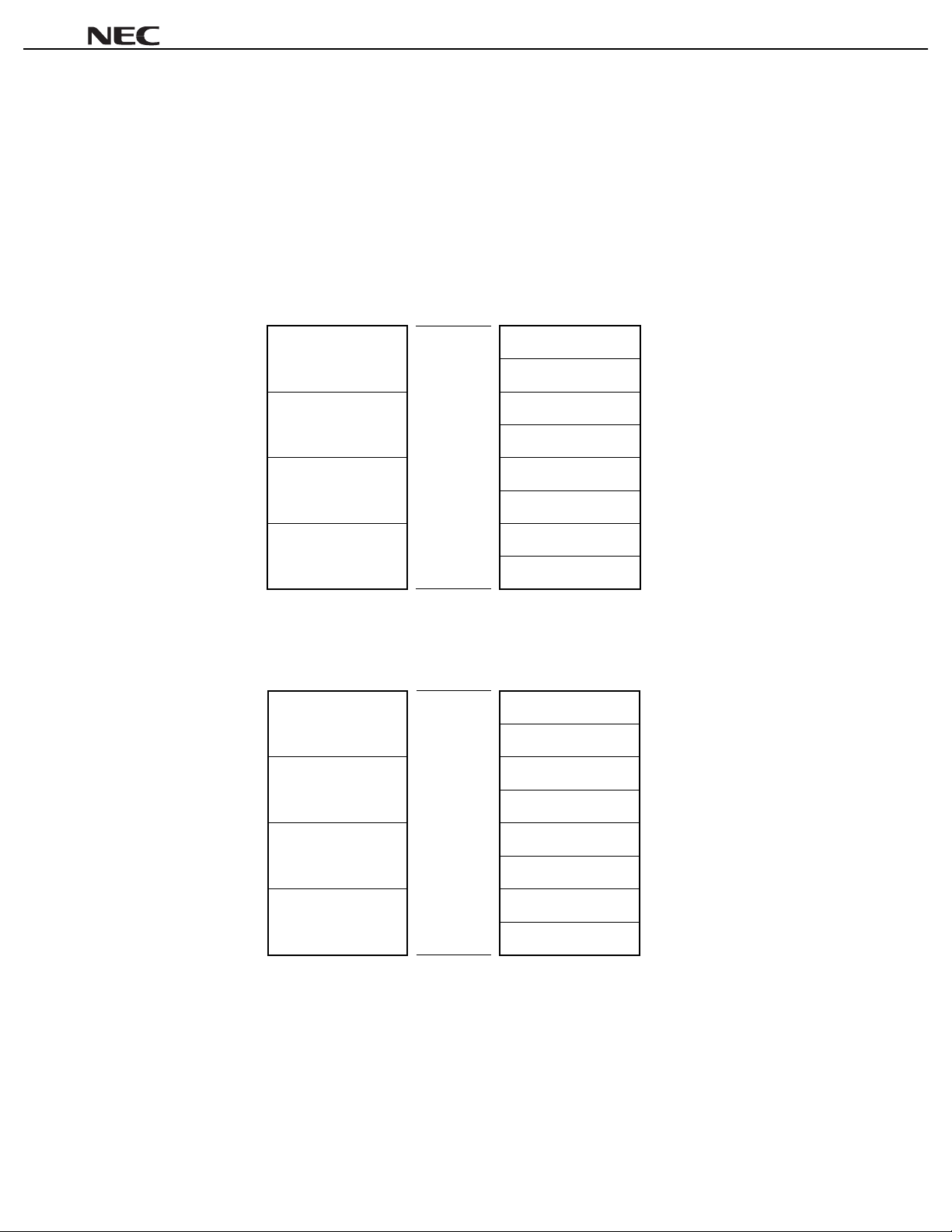

4.3.2 General-purpose registers

PD78F9328 has eight 8-bit general-purpose registers (X, A, C, B, E, D, L, and H).

The

µ

These registers can be used either singly as 8-bit registers or in pairs as 16-bit registers (AX, BC, DE, and HL),

and can be described in terms of function names (X, A, C, B, E, D, L, H, AX, BC, DE, and HL) and absolute names

(R0 to R7 and RP0 to RP3).

Figure 4-6. General-Purpose Register Configuration

(a) Absolute register names

16-bit processing

RP3

RP2

RP1

RP0

15 0

(b) Functional register names

16-bit processing

HL

8-bit processing

R7

R6

R5

R4

R3

R2

R1

R0

70

8-bit processing

H

L

16

DE

BC

AX

15 0

Preliminary Product Information U14411EJ1V0PM00

D

E

B

C

A

X

70

Page 17

µµµµ

PD78F9328

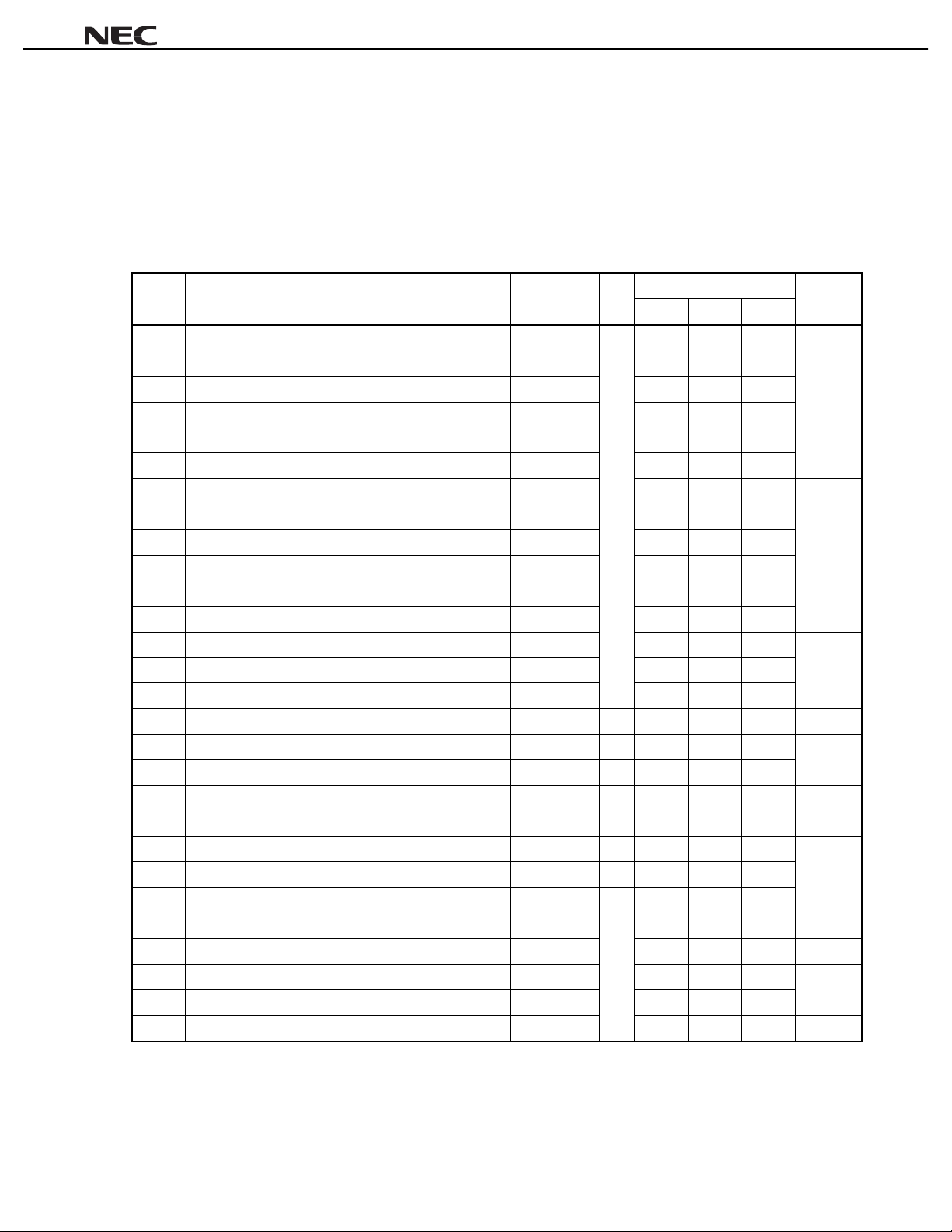

4.3.3 Special function registers (SFRs)

Special function registers are used as peripheral hardware mode registers and control registers, and are mapped

in the 256-byte space from FF00H to FFFFH.

Note that the bit number of a bit name that is a reserved word in the RA78K0S and defined under the header file

“sfrbit.h” in the CC78K0S appears enclosed in a circle in the register formats. Refer to the register formats in

PERIPHERAL HARDWARE FUNCTIONS

.

Table 4-1. Special Function Registers (1/2)

5.

FF00H Port 0 P0

FF01H Port 1 P1

FF02H Port 2 P2

FF03H port 4 P4

FF05H Port 6 P6

FF08H Port 8 P8

FF20H Port mode regi ster 0 PM0

FF21H Port mode regi ster 1 PM1

FF22H Port mode regi ster 2 PM2

FF24H Port mode regi ster 4 PM4

FF26H Port mode regi ster 6 PM6

FF28H Port mode regi ster 8 PM8

FF32H Pull-up res i s tor option register B2 PUB2

FF4AH Wat ch timer mode control register WTM

FF58H Port func tion register 8 PF8

FF63H 8-bit com pare regi ster 30 CR30 W

FF64H 8-bit tim er c ounter 30 TM30 R

FF65H 8-bit ti m er m ode control register 30 TMC30 R/W

FF66H 8-bit com pare regi ster 40 CR40

FF67H 8-bit H wi dth compare register 40 CRH40

FF68H 8-bit tim er c ounter 40 TM40 R

FF69H 8-bit ti m er m ode control register 40 TMC40 R/W

FF6AH Carrier generator output control register 40 TCA40 W

FF72H Serial operat i on m ode regi ster 10 CSIM10

FF74H Transmis sion/reception shift register 10 SIO10

FFB0H LCD display mode register 0 LCDM0

FFB2H LCD clock control register 0 LCDC0

FFDDH Power-on-cl ear regi ster 1 POCF1

R/W

W

R/W

Bit Unit for Manipulati onAddress Special Function Regist er (SFR) Name S ymbol R/W

1 Bit 8 Bits 16 Bits

√√−

√√−

√√−

√√−

√√−

√√−

√√−

√√−

√√−

√√−

√√−

√√−

√√−

√√−

√√−

−√−

−√−

√√−

−√−

−√−

−√−

√√−

√√−

√√−

√√−

√√−

√√−

√√−

After

Reset

00H

FFH

00H

Undefined

00H

Undefined

00H

Undefined

00H

Note

00H

This value is 04H only after a power-on-clear reset.

Note

Preliminary Product Information U14411EJ1V0PM00

17

Page 18

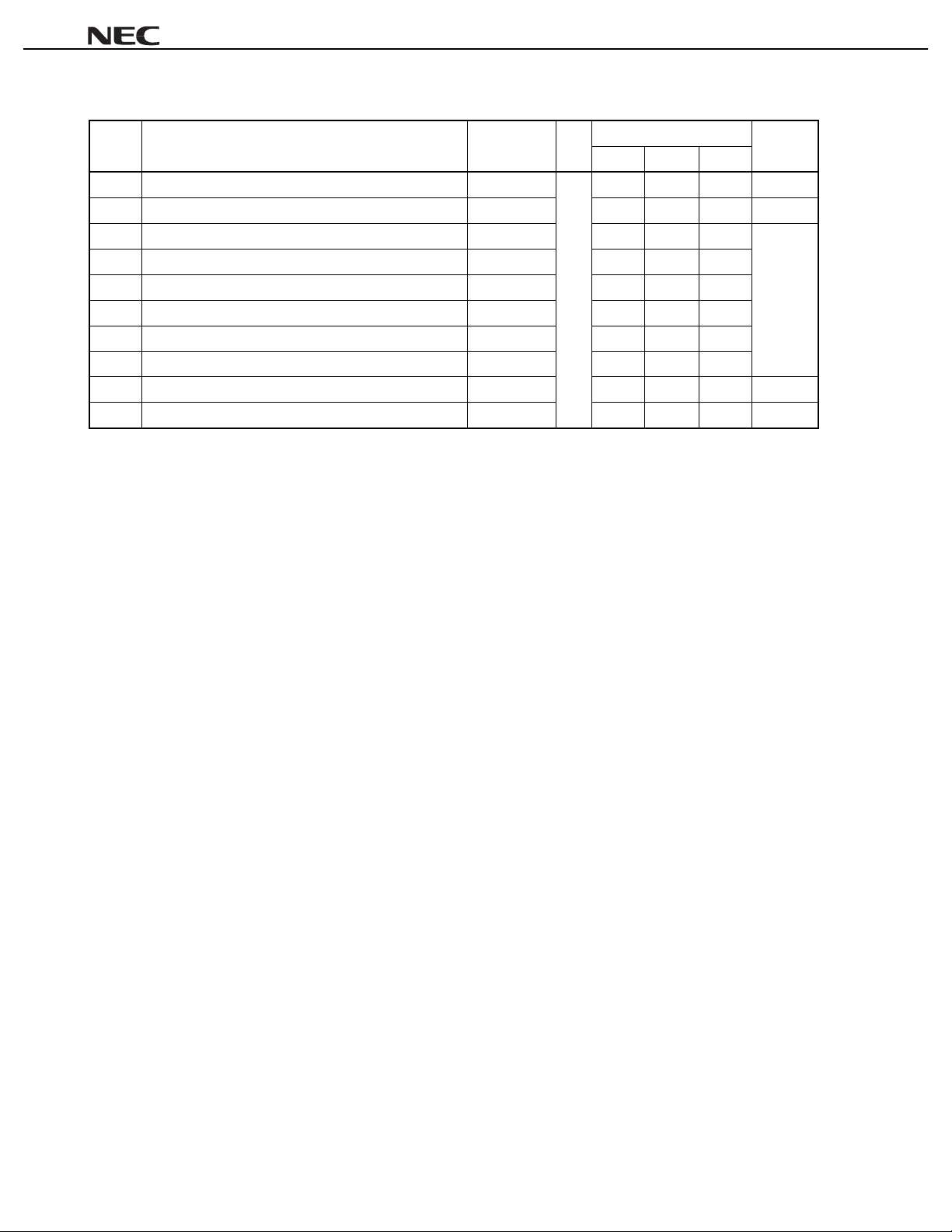

Table 4-1. Special Function Registers (2/2)

µµµµ

PD78F9328

FFE0H Interrupt request flag register 0 IF0

FFE4H Interrupt mask flag register 0 MK0

FFECH External interrupt m ode regi ster 0 INTM0

FFF0H Subclock oscillation mode register SCKM

FFF2H Subclock control register CSS

FFF5H Key return mode register 00 KRM00

FFF7H Pull-up resistor option register 0 PU0

FFF9H Watchdog timer mode register WDTM

FFFAH Oscillation stabilization time selection register OSTS

FFFBH Processor clock control register PCC

Bit Unit for Manipulati onAddress Special Function Regist er (SFR) Name S ymbol R/ W

1 Bit 8 Bits 16 Bits

R/W

√√−

√√−

−√−

√√−

√√−

√√−

√√−

√√−

−√−

√√−

After

Reset

00H

FFH

00H

04H

02H

18

Preliminary Product Information U14411EJ1V0PM00

Page 19

µµµµ

PD78F9328

5. PERIPHERAL HARDWARE FUNCTIONS

5.1 Ports

5.1.1 Port functions

Various kinds of control operations are possible using the ports provided in the

illustrated in Figure 5-1 and their functions are listed in Table 5-1.

A number of alternate functions are also provided, except for those ports functioning as digital I/O ports. Refer to

3. PIN FUNCTIONS

for details of the alternate function pins.

Figure 5-1. Ports

PD78F9328. These ports are

µ

Port 4

Port 6

Port 8

P40

P43

P60

P61

P80

P85

P00

P03

P10

P11

P20

P22

Port 0

Port 1

Port 2

Preliminary Product Information U14411EJ1V0PM00

19

Page 20

Table 5-1. Port Functions

Port Name Pin Name Function

Port 0 P00 to P03 This is an I/O port f or whi ch input and output can be specified i n 1-bi t units.

When used as an input port, on-chip pull -up resistors can be specifi ed using pull-up

resistor option register 0 (PU0).

Port 1 P10, P11 This is an I/O port for whi ch input and output can be specifi ed i n 1-bi t units.

When used as an input port, on-chip pull -up resistors can be specifi ed using pull-up

resistor option register 0 (PU0).

Port 2 P20 to P22 This is an I/O port f or whi ch input and output can be specified i n 1-bi t units.

When used as an input port, on-chip pull -up resistors can be specifi ed using pull-up

resistor option register B2 (PUB2).

Port 4 P40 to P43 This is an I/O port f or whi ch input and output can be specified i n 1-bi t units.

When used as an input port, on-chip pull -up resistors can be specifi ed using pull-up

resistor option register 0 (PU0), or key return mode register 00 (KRM 00).

Port 6 P60, P61 This is an I/O port for whi ch input and output can be specifi ed i n 1-bi t units.

Port 8 P80 to P85 This is an I/O port f or whi ch input and output can be specified i n 1-bi t units.

µµµµ

PD78F9328

20

Preliminary Product Information U14411EJ1V0PM00

Page 21

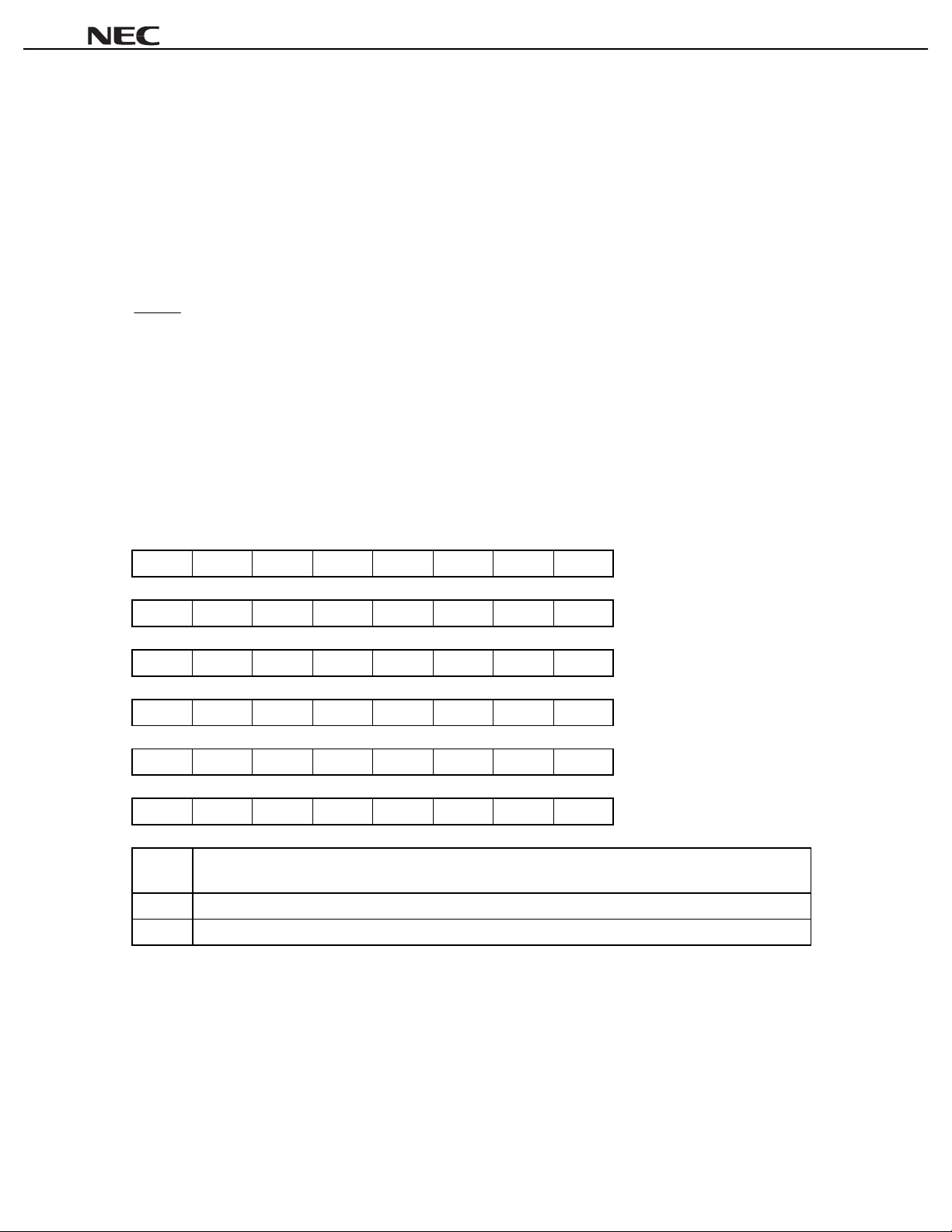

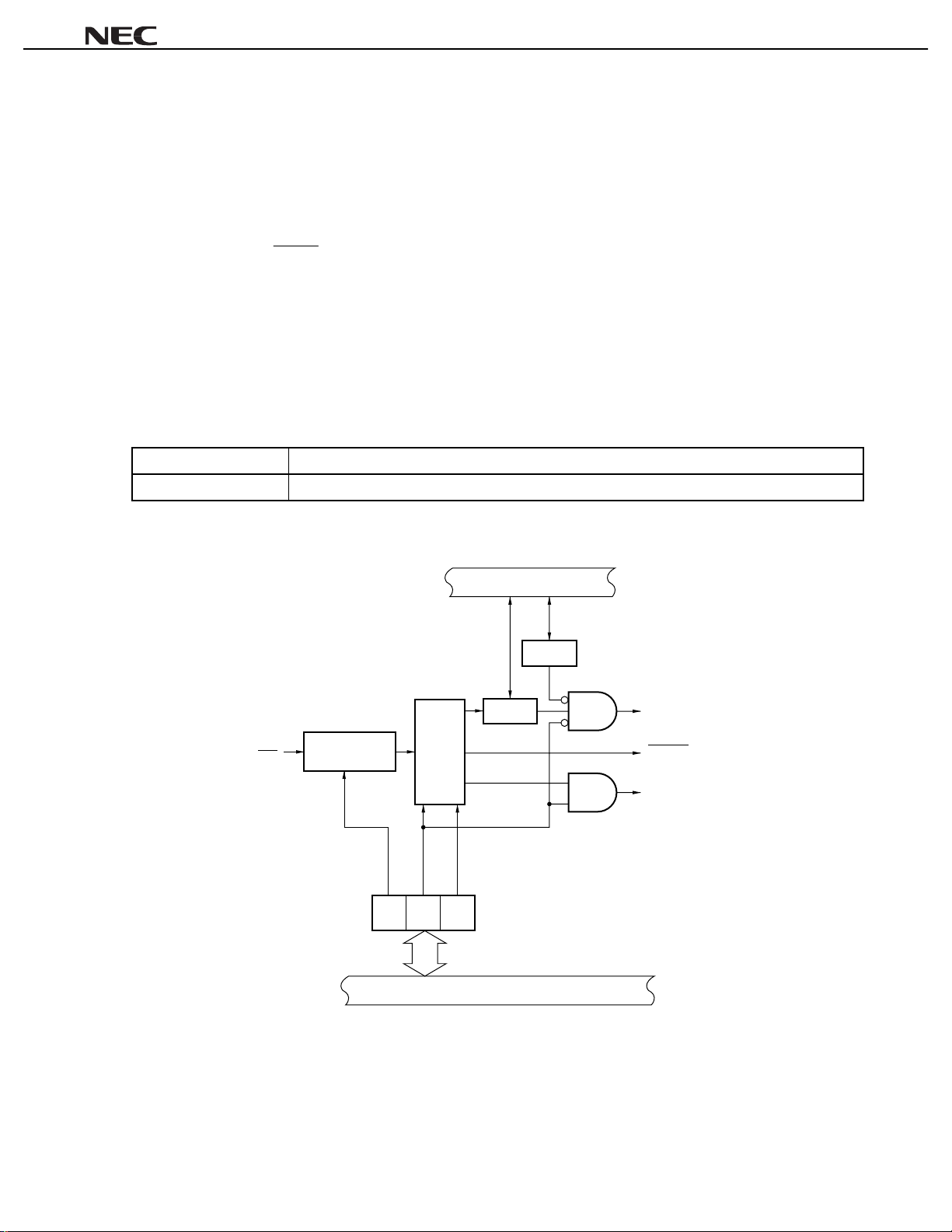

5.1.2 Port configuration

The ports consist of the following hardware.

Table 5-2. Port Configuration

Item Configuration

Control registers Port mode registers (PMm: m = 0 to 2, 4, 6, 8)

Pull-up resistor option registers (PU0, PUB2)

Port function regist er 8 (P F8)

Ports Total: 21 (CMOS I/O: 21)

Pull-up resistors Total: 13 (software control: 13)

Figure 5-2. Basic Configuration of CMOS Port

WR

PUm

µµµµ

PD78F9328

DD

V

Internal bus

WR

WR

WR

PU×

PORTm

Selector

PORTm

Output latch

Pmn

PMm

PMmn

P-ch

Pmn

Caution Figure 5-2 shows the basic configuration of a CMOS I/O port. This configuration differs

depending on the functions of alternate function pins. Also, an on-chip pull-up resistor can be

connected to port 4 by means of a setting in key return mode register 00 (KRM00).

Remark

PU×: Pull-up resistor option register (× = 0, B2)

PMmn: Bit n of port mode register m (m = 0 to 2, 4, 6, 8 n = 0 to 5)

Pmn: Bit n of port m

RD: Port read signal

WR: Port write signal

Preliminary Product Information U14411EJ1V0PM00

21

Page 22

5.1.3 Port function control registers

The ports are controlled by the following three types of registers.

Port mode registers (PM0 to PM2, PM4, PM6, PM8)

•

Pull-up resistor option registers (PU0, PUB2)

•

Port function register 8 (PF8)

•

(1) Port mode registers (PM0 to PM2, PM4, PM6, PM8)

Input and output can be specified in 1-bit units.

These registers can be set using a 1-bit or 8-bit memory manipulation instruction.

RESET input sets these registers to FFH.

When using the port pins as their alternate functions, set the output latch as shown in Table 5-3.

Caution Because P61 functions alternately as an external interrupt input, when the output level

changes after the output mode of the port function is specified, the interrupt request flag will

be inadvertently set. Therefore, be sure to preset the interrupt mask flag (PMK0) before

using the port in output mode.

µµµµ

PD78F9328

Figure 5-3. Port Mode Register Format

Symbol76543210AddressAfter resetR/W

PM0 1 1 1 1 PM03 PM02 PM01 PM00 FF20H FFH R/W

PM1111111PM11PM10FF21HFFHR/W

PM2 1 1 1 1 1 PM22 PM21 PM20 FF22H FFH R/W

PM4 1 1 1 1 PM43 PM42 PM41 PM40 FF24H FFH R/W

PM6111111PM61PM60FF26HFFHR/W

PM8 1 1 PM85 PM84 PM83 PM82 PM81 PM80 FF28H FFH R/W

PMmn Pmn pin input/output mode s el ection

(m = 0 to 2, 4, 6, 8 n = 0 to 5)

0 Output mode (output buffer on)

1 Input mode (output buffer off )

22

Preliminary Product Information U14411EJ1V0PM00

Page 23

µµµµ

PD78F9328

Table 5-3. Port Mode Registers and Output Latch Settings When Using Alternate Functions

Alternate FunctionPin Name

Name I/O

P20 SCK10

P21 SO10 Output 0 1

P22 SI10 Input 1

P40 to P43 KR00 to KR03 Input 1

P60 TO40 Output 0 0

P61 INT Input 1

P80 to P85

Note

Remark

S22 to S17

When using P80 to P85 pins as S22 to S17, set port function register 8 (PF8) to 3FH.

: don’t care

×

Note

Input 1

Output 0 1

Output

PM

××

××

P

PM××: Port mode register

P××: Port output latch

(2) Pull-up resistor option register 0 (PU0)

This register sets whether to use on-chip pull-up resistors for ports 0, 1, and 4 on a port by port basis. An onchip pull-up resistor can be used only for those bits set to the input mode of a port for which the use of the onchip pull-up resistor has been specified using PU0.

For those bits set to the output mode, on-chip pull-up resistors cannot be used, regardless of the setting of

PU0. This also applies to alternate-function pins used as output pins.

PU0 is set using a 1-bit or 8-bit memory manipulation instruction.

RESET input sets this register to 00H.

××

×

×

×

×

Figure 5-4. Format of Pull-Up Resistor Option Register 0

Symbol 7 6 5 <4> 3 2 <1> <0> Address After reset R/W

PU0 0 0 0 PU04 0 0 PU01 PU00 FFF7H 00H R/W

PU0m Port m on-chip pull-up resistor selection

(m = 0, 1, 4)

0 An on-chip pull-up resistor is not connected

1 An on-chip pull-up resistor is connected

Caution Always set bits 2, 3, and 5 to 7 to 0.

Preliminary Product Information U14411EJ1V0PM00

23

Page 24

µµµµ

PD78F9328

(3) Pull-up resistor option register B2 (PUB2)

This register sets whether to use on-chip pull-up resistors for P20 to P22 in bit units. An on-chip pull-up

resistor can be used only for those bits set to the input mode of a port for which the use of the on-chip pull-up

resistor has been specified using PUB2.

For those bits set to the output mode, on-chip pull-up resistors cannot be used, regardless of the setting of

PUB2. This also applies to alternate-function pins used as output pins.

PUB2 is set using a 1-bit or 8-bit memory manipulation instruction.

RESET input sets this register to 00H.

Figure 5-5. Format of Pull-Up Resistor Option Register B2

Symbol 7 6 5 4 3 <2> <1> <0> Address After reset R/W

PUB2 0 0 0 0 0 PUB22 PUB21 PUB20 FF32H 00H R/W

PUB2n P2n on-chip pull-up resistor s el ection

(n = 0 to 2)

0 An on-chip pull-up resistor is not connected

1 An on-chip pull-up resistor is connected

Caution Always set bits 3 to 7 to 0.

(4) Port function register 8 (PF8)

This register sets the port function of port 8 in 1-bit units.

The pins of port 8 are selected as either LCD segment signal outputs or general-purpose port pins according

to the setting of PF8.

PF8 can be set using a 1-bit or 8-bit memory manipulation instruction.

RESET input sets this register to 00H.

Figure 5-6. Format of Port Function Register 8

Symbol76543210AddressAfter resetR/W

PF8 0 0 PF85 PF84 PF83 PF82 PF81 PF80 FF58H 00H R/W

PF8n P8n port function (n = 0 to 5)

0 Operates as a general-purpose port

1 Operates as an LCD segment signal output

24

Preliminary Product Information U14411EJ1V0PM00

Page 25

µµµµ

PD78F9328

5.2 Clock Generator

5.2.1 Clock generator function

The clock generator generates the clock pulse to be supplied to the CPU and peripheral hardware.

There are two types of system clock oscillators:

Main system clock oscillator (ceramic/crystal resonator)

•

This circuit generates a frequency of 1.0 to 5.0 MHz. Oscillation can be stopped by executing the STOP

instruction or by means of a processor clock control register (PCC) setting.

Subsystem clock oscillator

•

This circuit generates a frequency of 32.768 kHz. Oscillation can be stopped using the subclock oscillation

mode register (SCKM).

5.2.2 Clock generator configuration

The clock generator consists of the following hardware.

Table 5-4. Clock Generator Configuration

Item Configuration

Control registers Processor clock control register (PCC)

Subclock oscillation mode register (SCKM)

Subclock control register (CSS)

Oscillators Main system clock oscillator

Subsystem clock oscillator

Preliminary Product Information U14411EJ1V0PM00

25

Page 26

Internal bus

Figure 5-7. Clock Generator Block Diagram

µµµµ

PD78F9328

XT1

XT2

X1

X2

FRC

SCC

Subsystem

clock

oscillatior

Main system

clock

oscillator

STOP

Subclock oscillation mode

register (SCKM)

f

XT

X

f

MCC

PCC1

1/2

Watch timer

LCD controller/driver

Prescaler

f

X

2

2

f

XT

2

Standby

control

circuit

Clock to peripheral hardware

Wait

control

circuit

CPU clock

CPU

)

(f

Selector

CLS

CSS0

Processor clock control

register (PCC)

Subclock control

register (CSS)

Internal bus

26

Preliminary Product Information U14411EJ1V0PM00

Page 27

µµµµ

PD78F9328

5.2.3 Clock generator control registers

The clock generator is controlled by the following three registers.

Processor clock control register (PCC)

•

Subclock oscillation mode register (SCKM)

•

Subclock control register (CSS)

•

(1) Processor clock control register (PCC)

This register is used to select the CPU clock and set the frequency division ratio.

PCC is set using a 1-bit or 8-bit memory manipulation instruction.

RESET input sets this register to 02H.

Figure 5-8. Format of Processor Clock Control Register

Symbol <7> 6 5 4 3 2 1 0 Address After reset R/W

PCC MCC 0 0 0 0 0 PCC1 0 FFFBH 02H R/W

MCC Main system clock oscillator operation control

0 Operation enabled

1 Operation stopped

CPU

CSS0 PCC1

00f

01

1×f

The CPU clock is selected by a combination of flag settings in the PCC and CSS registers. (Refer to

Note

X

X

f

XT

CPU clock (f

(0.2 µs) 0.4 µs

/22 (0.8 µs)

/2 (61 µs) 122 µs

) selection

5.2.3 (3) Subclock control register (CSS)

Note

Minimum instructi on execution time: 2f

1.6

s

µ

.)

Cautions 1. Always set bits 0 and 2 to 6 to 0.

2. MCC can be set only when the subsystem clock is selected as the CPU clock. Setting

MCC to 1 while the main system clock is operating is invalid.

X

: Main system clock oscillation frequency

Remarks 1.

f

fXT: Subsystem clock oscillation frequency

2.

The parenthesized values apply to operation at fX = 5.0 MHz or fXT = 32.768 kHz.

3.

CPU

Preliminary Product Information U14411EJ1V0PM00

27

Page 28

µµµµ

PD78F9328

(2) Subclock oscillation mode register (SCKM)

This register is used to select a feedback resistor for the subsystem clock and control the oscillation of the

clock.

SCKM is set using a 1-bit or 8-bit memory manipulation instruction.

RESET input sets this register to 00H.

Figure 5-9. Format of Subclock Oscillation Mode Register

Symbol 7 6 5 4 3 2 1 <0> Address After res et R/W

SCKM 0 0 0 0 0 0 FRC SCC FFF0H 00H R/W

FRC F eedback resistor selecti on

0 An on-chip feedback resis t or i s used

1 An on-chip feedback resis t or i s not used

SCC Control of subsystem clock oscillator operation

0 Operation enabled

1 Operation stopped

Caution Always set bits 2 to 7 to 0.

28

Preliminary Product Information U14411EJ1V0PM00

Page 29

µµµµ

PD78F9328

(3) Subclock control register (CSS)

This register is used to specify whether the main system or subsystem clock oscillator is selected and to

indicate the operating status of the CPU clock.

CSS is set using a 1-bit or 8-bit memory manipulation instruction.

RESET input sets this register to 00H.

Figure 5-10. Format of Subclock Control Register

Symbol76543210AddressAfter resetR/W

Note

CSS 0 0 CLS CSS0 0 0 0 0 FFF2H 00H

CLS CPU clock operating status

0 Operating on the output of the (divi ded) main system clock

1 Operating on the output of the subsystem clock

CSS0 Selection of main system clock or subsystem clock oscillator

0 Main system clock oscillator (divided) output

1 Subsystem clock oscillator output

R/W

Bit 5 is read-only.

Note

Caution Always set bits 0 to 3, 6, and 7 to 0.

Preliminary Product Information U14411EJ1V0PM00

29

Page 30

5.3 8-Bit Timer 30, 40

5.3.1 Functions of 8-bit timer 30, 40

The 8-bit timer in the

table are possible by means of mode register settings.

PD78F9328 has 2 channels (timer 30 and timer 40). The operation modes in the following

µ

Table 5-5. List of Modes

µµµµ

PD78F9328

Channel

Mode

8-bit timer counter mode

(discrete mode)

16-bit timer counter mode

(cascade connection mode)

Carrier generator mode

PWM output mode –

Timer 30 Timer 40

√√

(1) 8-bit timer counter mode (discrete mode)

The timer can be used for the following functions in this mode.

8-bit resolution interval timer

•

8-bit resolution square wave output (timer 40 only)

•

(2) 16-bit timer counter mode (cascade connection mode)

These timers can be used for 16-bit timer operations via a cascade connection.

The timer can be used for the following functions in this mode.

16-bit resolution interval timer

•

16-bit resolution square wave output

•

√

√

√

(3) Carrier generator mode

In this mode the carrier clock generated by timer 40 is output in the cycle set by timer 30.

(4) PWM output mode

In this mode, a pulse with an arbitrary duty ratio, which is set by timer 40, is output.

30

Preliminary Product Information U14411EJ1V0PM00

Page 31

5.3.2 Configuration of 8-bit timer 30, 40

8-bit timers 30 and 40 consist of the following hardware.

Table 5-6. Configuration of 8-Bit Timer 30, 40

Item Configuration

Timer counter 8 bits × 2 (TM30, TM40)

Registers Com pare regi sters: 8 bits × 3 (CR30, CR40, CRH40)

Timer outputs 1 (TO40)

Control registers 8-bit timer mode control register 30 (TMC30)

8-bit timer mode control register 40 (TMC40)

Carrier generator output control register 40 (TCA40)

Port mode register 6 (PM6)

µµµµ

PD78F9328

Preliminary Product Information U14411EJ1V0PM00

31

Page 32

32

Figure 5-11. Block Diagram of Timer 30

Internal bus

8-bit timer mode control registedr 30

(TMC30)

TCE30

Preliminary Product Information U14411EJ1V0PM00

Bit 7 of TM40

(from Figure

Timer 40 interrupt request signal

Carrier clock (in carrier generator mode)

(in other than carrier generator mode)

(from Figure 5-12 (B))

or timer 40 output signal

(from Figure 5-12 (C))

5-12 (A))

fX/2

fX/2

6

8

Selector

Selector

From Figure 5-12 (D)

Count operation start signal

(for cascade connection)

TCL301

Selector

TCL300

TMD300

Decoder

Cascade connection mode

8-bit compare register 30

(CR30)

Match

8-bit timer counter 30

(TM30)

Clear

Selector

From Figure 5-12 (E)

Timer 40 match signal

(in cascade connection mode)

OVF

To Figure 5-12 (G)

Timer 30 match signal

(in carrier generator mode)

Internal reset signal

INTTM30

µµ

µ

µ

PD78F9328

To Figure 5-12 (F)

Timer 30 match signal

(in cascade connection mode)

Page 33

8-bit timer mode control

register 40 (TMC40)

TCE40

TCL402 TCL401 TCL400

TMD401

TMD400

Figure 5-12. Block Diagram of Timer 40

Internal bus

TOE40

8-bit H width compare

register 40 (CRH40)

Carrier generator output

control register 40 (TCA40)

8-bit compare

register 40 (CR40)

RMC40

NRZB40

NRZ40

Decoder

Preliminary Product Information U14411EJ1V0PM00

f

fX/2

fX/2

X

2

2

f

X

/2

3

fX/2

4

fX/2

Prescaler

Selector

To Figure 5-11 (D)

Count operation start signal to timer 30

(in cascade connection mode)

Carrier generator mode

PWM mode

Cascade connection mode

8-bit timer counter 40

(TM40)

Clear

Match

Selector

F/F

OVF

Reset

To Figure 5-11 (E)

TM40 timer counter match signal

(in cascade connection mode)

Output control

circuit

Note

From Figure 5-11 (G)

Timer counter match signal from

timer 30 (in carrier generator mode)

TO40/P60

To Figure 5-11 (C)

Carrier clock (in carrier generator mode)

or timer 40 output signal

(in other than carrier generator mode)

To Figure 5-11 (A)

Bit 7 of TM40

(in cascade connection mode)

Internal reset signal

INTTM40

To Figure 5-11 (B)

Timer 40 interrupt request signal

count clock input

signal to TM30

µµ

µ

µ

PD78F9328

33

Note Refer to Figure 5-13 for details.

To Figure 5-11 (F)

TM30 match signal

(in cascade connection mode)

Page 34

Figure 5-13. Block Diagram of Output Control Circuit (Timer 40)

µµµµ

PD78F9328

TOE40

F/F

RMC40

Carrier generator mode

NRZ40

Selector

P60

output latch

PM60

TO40/P60

Carrier clock (in carrier generator mode)

or timer 40 output signal

(in other than carrier generator mode)

(1) 8-bit compare register 30 (CR30)

A value specified in CR30 is compared with the count value in 8-bit timer counter 30 (TM30), and if they

match, an interrupt request (INTTM30) is generated.

CR30 is set using an 8-bit memory manipulation instruction.

RESET input makes this register undefined.

Caution CR30 cannot be used in carrier generator mode or PWM output mode.

(2) 8-bit compare register 40 (CR40)

A value specified in CR40 is compared with the count value in 8-bit timer counter 40 (TM40), and if they

match, an interrupt request (INTTM40) is generated. When operating as a 16-bit timer in cascade

connection with TM30, an interrupt request (INTTM40) is only generated if both CR30 and TM30, and CR40

and TM40 match simultaneously (INTTM30 is not issued).

CR40 is set using an 8-bit memory manipulation instruction.

RESET input makes this register undefined.

(3) 8-bit H width compare register (CRH40)

In carrier generator mode or PWM output mode, a timer output high-level width can be set by writing a value

to CRH40.

CRH40 is set using an 8-bit memory manipulation instruction.

RESET input makes this register undefined.

34

Preliminary Product Information U14411EJ1V0PM00

Page 35

(4) 8-bit timer counter 30, 40 (TM30, TM40)

This is an 8-bit register for counting the count pulses.

TM30 and TM40 can be read with a 1-bit or 8-bit memory manipulation instruction.

RESET input sets these registers to 00H.

The conditions under which TM30 and TM40 are cleared to 00H are listed below.

(a) Discrete mode

(i) TM30

Upon a reset

•

When TCE30 (bit 7 of 8-bit timer mode control register 30 (TMC30)) is cleared to 0

•

Upon a match between TM30 and CR30

•

If the TM30 count value overflows

•

(ii) TM40

Upon a reset

•

When TCE40 (bit 7 of 8-bit timer mode control register 40 (TMC40)) is cleared to 0

•

Upon a match between TM40 and CR40

•

If the TM40 count value overflows

•

µµµµ

PD78F9328

(b) Cascade connection mode (TM30 and TM40 cleared to 00H simultaneously)

Upon a reset

•

When the TCE40 flag is cleared to 0

•

Upon a simultaneous match between TM30 and CR30, and TM40 and CR40

•

If the TM30 and TM40 count values overflow simultaneously

•

(c) Carrier generator/PWM output mode (TM40 only)

Upon a reset

•

When the TCE40 flag is cleared to 0

•

Upon a match between TM40 and CR40

•

Upon a match between TM40 and CRH40

•

If the TM40 count value overflows

•

Preliminary Product Information U14411EJ1V0PM00

35

Page 36

5.3.3 8-bit timer 30, 40 control registers

8-bit timers 30 and 40 are controlled by the following 4 registers.

8-bit timer mode control register 30 (TMC30)

•

8-bit timer mode control register 40 (TMC40)

•

Carrier generator output control register 40 (TCA40)

•

Port mode register 6 (PM6)

•

µµµµ

PD78F9328

36

Preliminary Product Information U14411EJ1V0PM00

Page 37

µµµµ

PD78F9328

(1) 8-bit timer mode control register 30 (TMC30)

This register is used to control the timer 30 count clock and operation mode settings.

TMC30 is set using a 1-bit or 8-bit memory manipulation instruction.

RESET input sets this register to 00H.

Figure 5-14. Format of 8-Bit Timer Mode Control Register 30

Symbol <7> 6 5 4 3 2 1 0 Address After reset R/W

TMC30 TCE30 0 0 TCL301 TCL300 0 TMD300 0 FF65H 00H R/W

TCE30

0 TM30 count v al ue cleared and operation stopped

1 Count operation st arts

TCL301 TCL300 Timer 30 count clock selection

X

/26 (78.1 kHz)

00

01

1 0 Timer 40 match signal

1 1 Carrier clock (in carrier generator mode) or timer 40 output signal (in other than carrier generator

TMD300 TMD401 TMD400

0 0 0 Disc ret e m ode

1 0 1 Cascade c onnection mode

0 1 1 Carrier generator mode

0 1 0 PWM output mode

Other than above Setting prohibited

f

X

/28(19.5 kHz)

f

mode)

TM30 count control operation

Timer 30, timer 40 operation mode sel ection

Note 1

Note 2

Notes 1.

The TCE30 setting will be ignored in cascade mode because in this case the count operation is

controlled by TCE40 (bit 7 of TMC40).

The operation mode selection is made using a combination of TMC30 and TMC40 register settings.

2.

Caution In cascade connection mode, the timer 40 output signal is forcibly selected for the count

clock.

X

: Main system clock oscillation frequency

Remarks 1.

f

The parenthesized values apply to operation at fX = 5.0 MHz

2.

Preliminary Product Information U14411EJ1V0PM00

37

Page 38

µµµµ

PD78F9328

(2) 8-bit timer mode control register 40 (TMC40)

This register is used to control the timer 40 count clock and operation mode settings.

TMC40 is set using a 1-bit or 8-bit memory manipulation instruction.

RESET input sets this register to 00H.

Figure 5-15. Format of 8-Bit Timer Mode Control Register 40

Symbol <7> 6 5 4 3 2 1 <0> Address After reset R/W

TMC40 TCE40 0 TCL402 TCL401 TCL400 TMD401 TMD400 TOE40 FF69H 00H R/W

TCE40

0 TM40 count v al ue cleared and operation stopped (in cascade c onnection mode, the count value of TM 30 i s

cleared at the same time)

1 Count operation st arts (in cascade connection m ode, the count operation of TM30 starts at the same time)

TCL402 TCL401 TCL400 Timer 40 count clock selec tion

000f

001

010f

011

100

101

Other than above Setting prohibited

TMD300 TMD401 TMD400

0 0 0 Disc ret e m ode

1 0 1 Cascade c onnection mode

0 1 1 Carrier generator mode

0 1 0 PWM output mode

Other than above Setting prohibited

X

(5 MHz)

X

/22 (1.25 MHz)

f

X

/2 (2.5 MHz)

X

/22 (1.25 MHz)

f

X

/23 (625 kHz)

f

X

/24 (313 kHz)

f

TM40 count control operation

Timer 30, timer 40 operation mode sel ection

Note 1

Note 2

38

TOE40 Timer output control

0 Output disabl ed (port mode)

1 Output enabled

Notes 1.

The TCE30 setting will be ignored in cascade mode because in this case the count operation is

controlled by TCE40 (bit 7 of TMC40).

The operation mode selection is made using a combination of TMC30 and TMC40 register settings.

2.

X

: Main system clock oscillation frequency

Remarks 1.

f

The parenthesized values apply to operation at fX = 5.0 MHz

2.

Preliminary Product Information U14411EJ1V0PM00

Page 39

µµµµ

PD78F9328

(3) Carrier generator output control register 40 (TCA40)

This register is used to set the timer output data in the carrier generator mode.

TCA40 is set using a 1-bit or 8-bit memory manipulation instruction.

RESET input sets this register to 00H.

Figure 5-16. Format of Carrier Generator Output Control Register 40

Symbol76543<2><1><0>AddressAfter resetR/W

TCA4000000RMC40NRZB40NRZ40FF6AH00HW

RMC40 Remote controller output control

0 When NRZ40 = 1, a carrier puls e i s output to the TO40/P60 pin

1 When NRZ40 = 1, a high level i s output to the TO40/P60 pin

NRZB40 This bit stores the data that NRZ40 will output next. Data is t rans ferred to NRZ40 upon the generation of a

timer 30 match signal.

NRZ40 No return, zero data

0 A low level i s output (the carrier clock i s stopped)

1 A carrier puls e i s output

(4) Port mode register 6 (PM6)

This register is used to set port 6 to input or output in 1-bit units.

When the TO40/P60 pin is used as a timer output, set the PM60 and P60 output latches to 0.

PM6 is set using a 1-bit or 8-bit memory manipulation instruction.

RESET input sets this register to FFH.

Figure 5-17. Format of Port Mode Register 6

Symbol76543210AddressAfter resetR/W

PM6111111PM61PM60FF26HFFHR/W

PM6n Input/output mode of pin P6n (n = 0, 1)

0 Output mode (output buffer on)

1 Input mode (output buffer off)

Preliminary Product Information U14411EJ1V0PM00

39

Page 40

5.4 Watch Timer

5.4.1 Watch timer functions

The watch timer has the following functions.

Watch timer

•

Interval timer

•

The watch and interval timers can be used at the same time.

Figure 5-18 shows a block diagram of the watch timer.

Figure 5-18. Watch Timer Block Diagram

Clear

7

fX/2

f

W

f

XT

Selector

f

W

f

4

2

2

9-bit prescaler

W

f

W

f

5

W

6

7

2

2

f

W

f

W

8

2

9

2

µµµµ

PD78F9328

5-bit counter INTWT

Clear

Selector

WTM7 WTM6 WTM5 WTM4 WTM1

Watch timer mode control

register (WTM)

Internal bus

INTWTI

WTM0

40

Preliminary Product Information U14411EJ1V0PM00

Page 41

µµµµ

PD78F9328

(1) Watch timer

An interrupt request (INTWT) is generated at 0.5-second intervals using the 4.19-MHz main system clock or

32.768-kHz subsystem clock.

Caution When the main system clock is operating at 5.0 MHz, it cannot be used to generate a 0.5-second

interval. In this case, the subsystem clock, which operates at 32.768 kHz, should be used

instead.

(2) Interval timer

The interval timer is used to generate an interrupt request (INTWTI) at preset intervals.

Table 5-7. Interval Time of Interval Timer

Interval Time At f

W

24 × 1/f

W

25 × 1/f

W

26 × 1/f

W

27 × 1/f

W

28 × 1/f

W

29 × 1/f

Remarks 1.

2.

3.

W

: Watch timer clock frequency (fX/27 or fXT)

f

fX: Main system clock oscillation frequency

fXT: Subsystem clock oscillation frequency

X

= 5.0 MHz Operation At fX = 4.19 MHz Operation At fXT = 32.768 kHz Operation

409.6 µs 488 µs 488 µs

819.2 µs 977 µs 977 µs

1.64 ms 1.95 ms 1.95 ms

3.28 ms 3.91 ms 3.91 ms

6.55 ms 7.81 ms 7.81 ms

13.1 ms 15.6 ms 15.6 ms

5.4.2 Watch timer configuration

The watch timer consists of the following hardware.

Table 5-8. Watch Timer Configuration

Item Configuration

Counter 5 bits × 1

Prescaler 9 bits × 1

Control register Watch timer mode c ontrol register (WTM)

Preliminary Product Information U14411EJ1V0PM00

41

Page 42

µµµµ

PD78F9328

5.4.3 Watch timer control register

The following register controls the watch timer.

Watch timer mode control register (WTM)

•

(1) Watch timer mode control register (WTM)

This register is used to enable/disable the count clock and operation of the watch timer and set the interval

time of the prescaler and operation control of the 5-bit counter.

WTM is set using a 1-bit or 8-bit memory manipulation instruction.

RESET input sets this register to 00H.

Figure 5-19. Format of Watch Timer Mode Control Register

Symbol 7 6 5 4 3 2 <1> <0> Address After reset R/W

WTM WTM7 WTM6 WTM5 WTM4 0 0 WTM1 WTM0 FF4AH 00H R/W

WTM7 Watch timer count clock (fW) selection

X

/27(39.1 kHz)

f

0

1fXT(32.768 kHz)

WTM6 WTM5 WTM4 Prescaler interval time selection

4

W

/f

000

001

010

011

100

101

2

5

W

/f

2

6

W

/f

2

7

W

/f

2

8

W

/f

2

9

W

/f

2

Other than above Setting prohibited

WTM1 5-bit counter operation control

0 Cleared after operation stopped

1Start

WTM0 Watch timer operat i on enabl e

0 Operation s topped (both prescaler and timer cleared)

1 Operation enabled

W

: Watch timer clock frequency (fX/27 or fXT)

Remarks 1.

f

fX: Main system clock oscillation frequency

2.

fXT: Subsystem clock oscillation frequency

3.

The parenthesized values apply to operation at fX = 5.0 MHz or fXT = 32.768 kHz.

4.

42

Preliminary Product Information U14411EJ1V0PM00

Page 43

µµµµ

PD78F9328

5.5 Watchdog Timer

5.5.1 Watchdog timer functions

The watchdog timer has the following functions.

(1) Watchdog timer

The watchdog timer is used to detect a program runaway. If a runaway is detected, either a non-maskable

interrupt or the RESET signal can be generated.

(2) Interval timer

The interval timer is used to generate interrupts at preset intervals.

5.5.2 Watchdog timer configuration

The watchdog timer consists of the following hardware.

Table 5-9. Watchdog Timer Configuration

Item Configuration

Control register Watchdog timer mode register (WDTM)

Figure 5-20. Watchdog Timer Block Diagram

Internal bus

WDTMK

WDTIF

f

X

4

2

7-bit counter

Clear

RUN

Control circuit

WDTM4 WDTM3

Watchdog timer mode register

(WDTM)

INTWDT

maskable

interrupt request

RESET

INTWDT

non-maskable

interrupt request

Internal bus

Preliminary Product Information U14411EJ1V0PM00

43

Page 44

µµµµ

PD78F9328

5.5.3 Watchdog timer control register

The watchdog timer is controlled by the following register.

Watchdog timer mode register (WDTM)

•

(1) Watchdog timer mode register (WDTM)

This register is used to set the watchdog timer operation mode and whether to enable or disable counting.

WDTM is set using a 1-bit or 8-bit memory manipulation instruction.

RESET input sets this register to 00H.

Figure 5-21. Format of Watchdog Timer Mode Register

Symbol <7> 6 5 4 3 2 1 0 Address After reset R/W

WDTM RUN 0 0 WDTM4 WDTM3 0 0 0 FFF9H 00H R/W

RUN

0 Counting stopped

1 Counter cleared and counting starts

WDTM4 WDTM3

0 0 Operation stopped

01

1 0 Watchdog timer mode 1 (when an overflow occurs, a non-maskable i nterrupt is generated)

1 1 Watchdog timer mode 2 (when an overflow occurs, a reset operation i s activated)

Notes 1.

Once the RUN bit has been set (1), it is impossible to clear it (0) by software. Consequently, once

Interval timer mode (when an overf l ow occurs, a maskable interrupt i s generated)

Watchdog timer operation selec tion

Watchdog timer operation mode sel ection

Note 1

Note 2

Note 3

counting begins, it cannot be stopped by any means other than RESET input.

Once WDTM3 and WDTM4 have been set (1), it is impossible to clear them (0) by software.

2.

The interval timer starts operating as soon as the RUN bit is set to 1.

3.

Cautions 1. When the RUN bit is set to 1, and the watchdog timer is cleared, the actual overflow time

will be up to 0.8% shorter than the time specified by the watchdog timer clock selection

register.

2. To use watchdog timer mode 1 or 2, be sure to set WDTM4 to 1 after confirming that

WDTIF (bit 0 of interrupt request flag 0 (IF0)) has been set to 0. If WDTIF is 1, selecting

watchdog timer mode 1 or 2 causes a non-maskable interrupt to be generated the instant

rewriting ends.

44

Preliminary Product Information U14411EJ1V0PM00

Page 45

µµµµ

PD78F9328

5.6 Serial Interface 10

5.6.1 Functions of serial interface 10

Serial interface 10 has the following two modes.

Operation stopped mode

•

3-wire serial I/O mode

•

(1) Operation stopped mode

This mode is used to minimize power consumption when serial transfer is not performed.

(2) 3-wire serial I/O mode (switchable between MSB-first and LSB-first transmission)

This mode is used to transmit 8-bit data, using three lines: a serial clock line (SCK10) and two serial data lines

(SI10 and SO10).

As 3-wire serial I/O mode supports simultaneous transmission and reception, the time required for data

processing can be reduced.

In 3-wire serial I/O mode, it is possible to select whether 8-bit data transmission begins with the MSB or LSB,

allowing serial interface 10 to be connected to any device regardless of whether that device is designed for

MSB-first or LSB-first transmission.

3-wire serial I/O mode is effective for connecting peripheral I/O circuits and display controllers having

conventional clock synchronous serial interfaces, such as those of the 75XL, 78K, and 17K Series devices.

5.6.2 Configuration of serial interface 10

Serial interface 10 consists of the following hardware.

Table 5-10. Configuration of Serial Interface 10

Item Configuration

Register Transmission/reception shift regi ster 10 (SIO10)

Control register Serial operation mode regis ter 10 (CSIM10)

(1) Transmission/reception shift register 10 (SIO10)

This is an 8-bit register used for parallel/serial data conversion and for serial transmission or reception in

synchronization with the serial clock.

SIO10 is set using an 8-bit memory manipulation instruction.

RESET input makes this register undefined.

Preliminary Product Information U14411EJ1V0PM00

45

Page 46

46

Preliminary Product Information U14411EJ1V0PM00

SI10/P22

SO10/P21

PM21

Figure 5-22. Block Diagram of Serial Interface 10

Serial operation mode register 10

CSIE10

(CSIM10)

TPS101

TPS100

DIR10

Internal bus

CSCK10

Transmission/reception shift

register 10 (SIO10)

SCK10/P20

PM20

Serial clock counter

Clock control

circuit

F/F

Selector

Interrupt request

generator

fX/2

fX/2

Selector

TPS101

TPS100

INTCSI10

2

3

µµ

µ

µ

PD78F9328

Page 47

µµµµ

PD78F9328

5.6.3 Control register for serial interface 10

Serial interface 10 is controlled by the following register.

Serial operation mode register 10 (CSIM10)

•

Figure 5-23. Format of Serial Operation Mode Register 10

Symbol <7> 6 5 4 3 2 1 0 Address After reset R/W

CSIM10 CSIE10 0 TPS101 TPS 100 0 DI R10 CSCK10 0 FF72H 00H R/W

CSIE10 3-wire serial I/O mode operation c ontrol

0 Operat i on stopped

1 Operat i on enabl ed

TPS101 TPS100 Selecti on of count clock when internal clock selected

X

/22 (1.25 MHz)

00

01

Other than above Setting prohi bi t ed

f

X

/23 (625 kHz)

f

DIR10 First-bit specification

0MSB

1LSB

CSCK10 SIO10 clock selection

0 External clock pulse input to the SCK10 pin

1 Internal clock selected wi t h TPS100, TPS101

Cautions 1. Bits 0, 3 and 6 must be fixed to 0.

2. Be sure to switch to operation mode after stopping the serial transmission/reception

operation.

X

: Main system clock oscillation frequency

Remarks 1.

f

The parenthesized values apply to operation at fX = 5.0 MHz.

2.

Preliminary Product Information U14411EJ1V0PM00

47

Page 48

Table 5-11. Operation Mode Settings for Serial Interface 10

(1) Operation stopped mode

µµµµ

PD78F9328

CSIM10

CSIE10

DIR10

CSCK10

0

×

×

(2) 3-wire serial I/O mode

CSIM10

CSIE10

Notes 1.

DIR10

CSCK10

1

0

0

1

1

0

1

Can be used freely as a port

Can be used as P22 (CMOS I/O) only when transmitting

2.

PM22

Note 1

×

PM22

Note 2

1

P22

PM21

Note 1

Note 1

×

×

P22

PM210P211PM20

Note 2

×

P21

Note 1

×

PM20

Note 1

×

1

0

1

0

P20

Note 1

×

P20

First

Bit

−

Shift

Clock

−

P22/SI10

Pin Function

P21/SO10

Pin Function

P20/SCK10

Pin Function

P22 P21 P20

Setting prohibitedOther than above

First

×

MSB

Bit

Shift

Clock

External

clock

1

Internal

P22/SI10

Pin Function

Note 2

SI10

P21/SO10

Pin Function

SO10

(CMOS output)

P20/SCK10

Pin Function

SCK10 input

SCK10 output

clock

×

LSB

External

SCK10 input

clock

1

Internal

SCK10 output

clock

Setting prohibitedOther than above

Remark