NEC UPD70216HLP-20, UPD70216HLP-16, UPD70208HLP-10, UPD70208HLP-12, UPD70208HGK-20-9EU Datasheet

...

DATA SHEET

MOS INTEGRATED CIRCUIT

µ

PD70208H, 70216H

V40HLTM, V50HL

TM

16/8, 16-BIT MICROPROCESSOR

DESCRIPTION

The µPD70208H (V40HL) is a high-speed, low-power 16-/8-bit microprocessor based on the µPD70208 (V40TM) with

16-bit architecture, 8-bit data bus, and general-purpose peripheral functions.

µ

PD70216H (V50HL) is a high-speed, low-power 16-bit microprocessor based on the µPD70216 (V50TM) with 16-

The

bit architecture, 16-bit data bus, and general-purpose peripheral functions.

The V40HL and V50HL offer 20 MHz operation, and in addition to the conventional standby functions, also allows the

clock to be stopped by the use of fully static internal circuitry, thus achieving greatly reduced power consumption. It is also

capable of 3 V operation in addition to the previous 5 V operation, making it ideally suited to battery driven systems.

Details are given in the following manuals. Be sure to read when carrying out design work.

• V40HL, V50HL User’s Manual – Hardware (U11610E)

TM

• 16-bit V series

FEATURES

User’s Manual – Instruction (U11301J: Japanese version)

• High-speed, low-power version of V40 and V50

• High-performance CPU (V20

• Minimum instruction execution time: 100 ns (20 MHz, 5 V)

• Memory addressing space: 1M bytes

• High-speed multiply/divide instructions: 0.95 to 2.8

• Maskable (ICU) & non-maskable (NMI) interrupt inputs

•µPD8080AF emulation function

• Standby functions, clock stoppage capability

TM

/V30TM software compatible)

200 ns (10 MHz, 3 V)

1.9 to 5.6 µs (10 MHz, 3 V)

µ

s (20 MHz, 5 V)

• Standard peripheral LSI functions on chip

• Clock generator (CG)

• Programmable wait control unit (WCU)

• Refresh control unit (REFU)

µ

• Timer/counter unit (TCU) ···

• Serial control unit (SCU) ··· µPD71051 subset

• Interrupt control unit (ICU) ··· µPD71059 subset

• DMA control unit (DMAU) ··· µPD71071/71037 subset (functions of either selectable)

PD71054 subset

• Operating frequency: 10/12.5/16/20 MHz (at 5 V, with 20/25/32/40 MHz supplied externally)

5/6.25/8/10 MHz (at 3 V, with 10/12.5/16/20 MHz supplied externally)

The information in this document is subject to change without notice. Before using this document, please

confirm that this is the latest version.

Not all devices/types available in every country. Please check with local NEC representative for availability

and additional information.

Document No. U13225EJ4V0DS00 (4th edition)

Date Published April 1999 N CP(K)

Printed in Japan

The mark shows the the major revised points.

©

1995

µ

PD70208H, 70216H

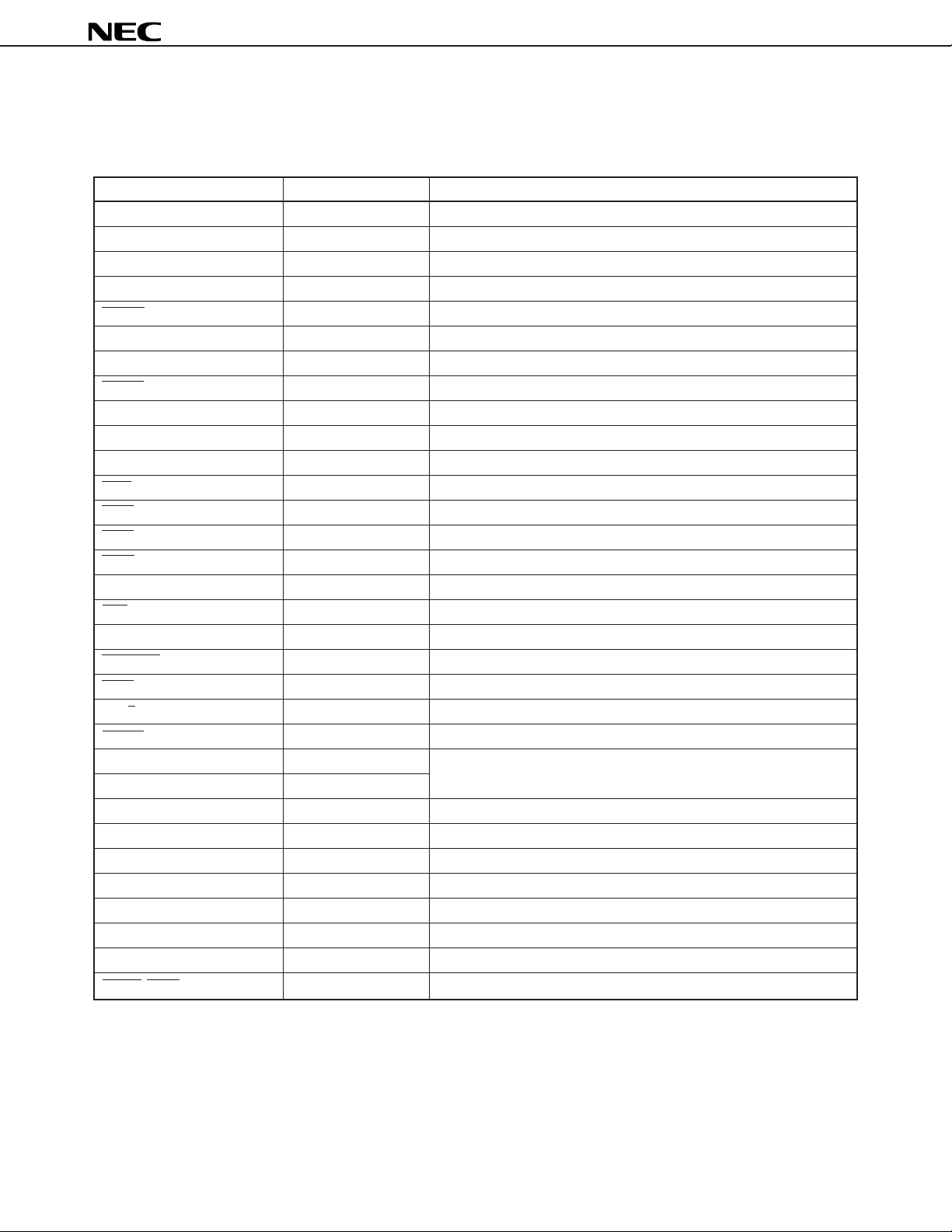

ORDERING INFORMATION

(1) V40HL

Part Number Package Frequency (MHz)

µ

PD70208HGF-10-3B9 80-pin plastic QFP (14 × 20 mm) 10

(Resin thickness 2.7 mm)

µ

PD70208HGF-12-3B9 80-pin plastic QFP (14 × 20 mm) 12.5

(Resin thickness 2.7 mm)

µ

PD70208HGF-16-3B9 80-pin plastic QFP (14 × 20 mm) 16

(Resin thickness 2.7 mm)

µ

PD70208HGF-20-3B9 80-pin plastic QFP (14 × 20 mm) 20

(Resin thickness 2.7 mm)

µ

PD70208HGK-10-9EU 80-pin plastic TQFP (Fine pitch) (12 × 12 mm) 10

(Resin thickness 1.0 mm)

µ

PD70208HGK-12-9EU 80-pin plastic TQFP (Fine pitch) (12 × 12 mm) 12.5

(Resin thickness 1.0 mm)

µ

PD70208HGK-16-9EU 80-pin plastic TQFP (Fine pitch) (12 × 12 mm) 16

(Resin thickness 1.0 mm)

µ

PD70208HGK-20-9EU 80-pin plastic TQFP (Fine pitch) (12 × 12 mm) 20

(Resin thickness 1.0 mm)

µ

PD70208HLP-10 68-pin plastic QFJ (950 × 950 mil) 10

µ

PD70208HLP-12 68-pin plastic QFJ (950 × 950 mil) 12.5

µ

PD70208HLP-16 68-pin plastic QFJ (950 × 950 mil) 16

µ

PD70208HLP-20 68-pin plastic QFJ (950 × 950 mil) 20

Max. Operating

(2) V50HL

Part Number Package Frequency (MHz)

µ

PD70216HGF-10-3B9 80-pin plastic QFP (14 × 20 mm) 10

(Resin thickness 2.7 mm)

µ

PD70216HGF-12-3B9 80-pin plastic QFP (14 × 20 mm) 12.5

(Resin thickness 2.7 mm)

µ

PD70216HGF-16-3B9 80-pin plastic QFP (14 × 20 mm) 16

(Resin thickness 2.7 mm)

µ

PD70216HGF-20-3B9 80-pin plastic QFP (14 × 20 mm) 20

(Resin thickness 2.7 mm)

µ

PD70216HGK-10-9EU 80-pin plastic TQFP (Fine pitch) (12 × 12 mm) 10

(Resin thickness 1.0 mm)

µ

PD70216HGK-12-9EU 80-pin plastic TQFP (Fine pitch) (12 × 12 mm) 12.5

(Resin thickness 1.0 mm)

µ

PD70216HGK-16-9EU 80-pin plastic TQFP (Fine pitch) (12 × 12 mm) 16

(Resin thickness 1.0 mm)

µ

PD70216HGK-20-9EU 80-pin plastic TQFP (Fine pitch) (12 × 12 mm) 20

(Resin thickness 1.0 mm)

µ

PD70216HLP-10 68-pin plastic QFJ (950 × 950 mil) 10

µ

PD70216HLP-12 68-pin plastic QFJ (950 × 950 mil) 12.5

µ

PD70216HLP-16 68-pin plastic QFJ (950 × 950 mil) 16

µ

PD70216HLP-20 68-pin plastic QFJ (950 × 950 mil) 20

Max. Operating

2

Data Sheet U13225EJ4V0DS00

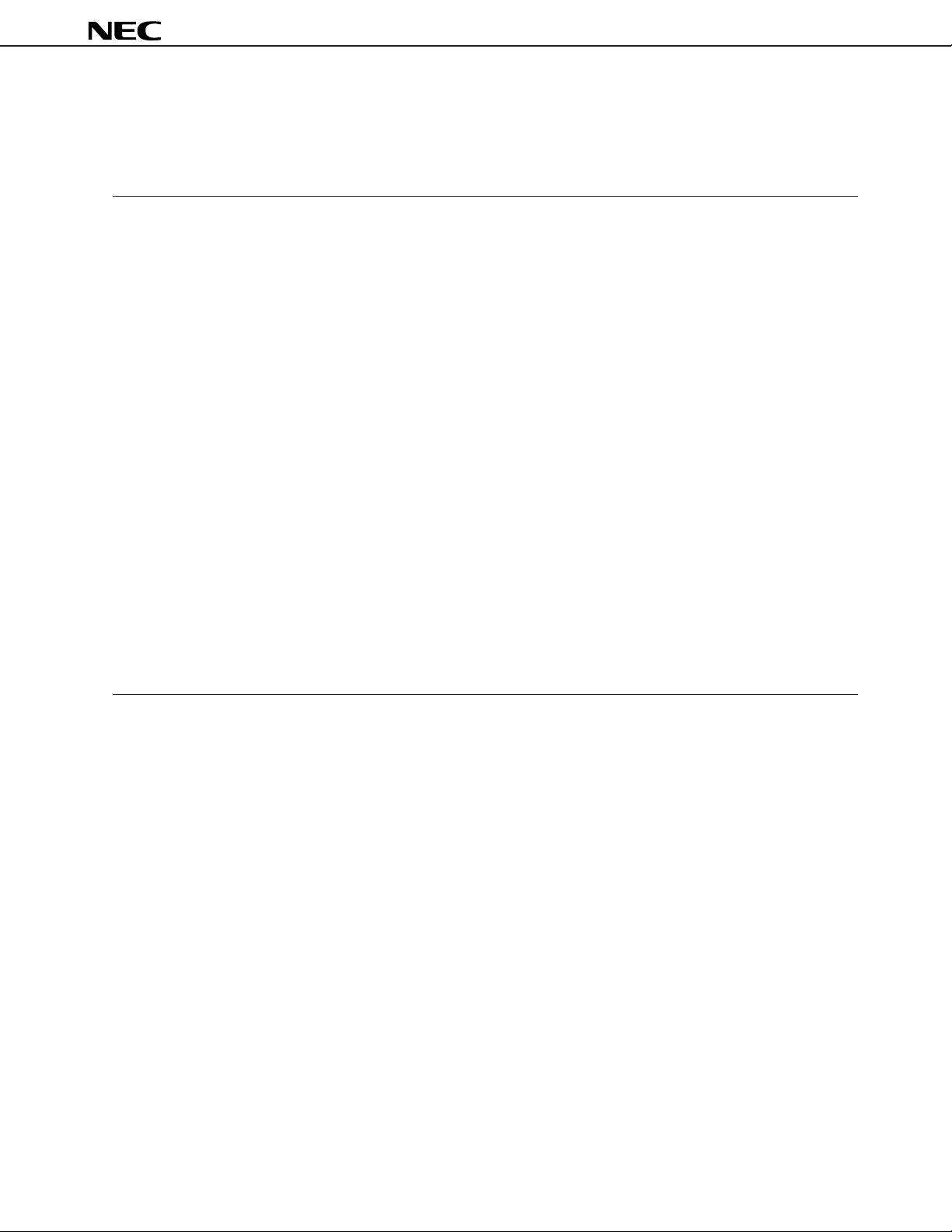

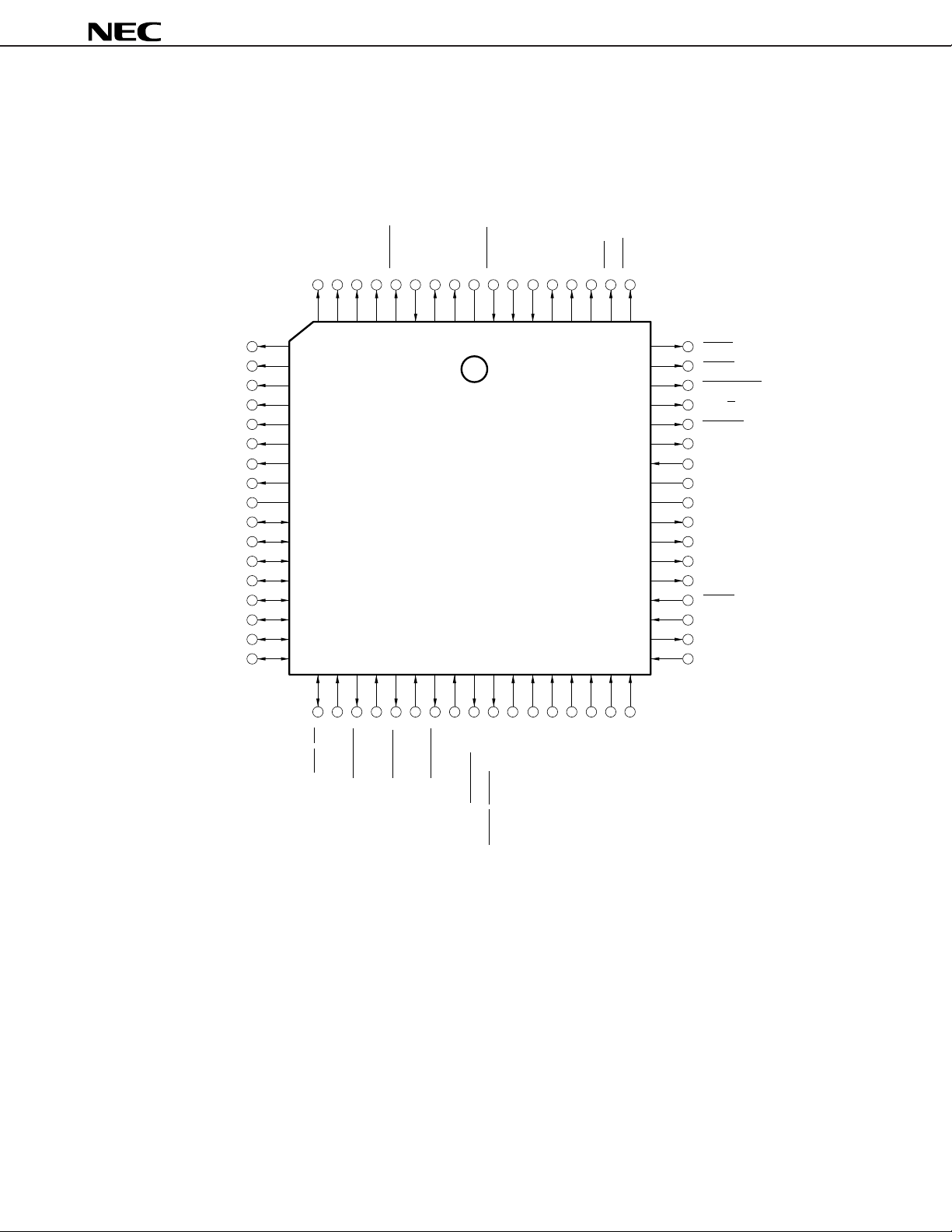

PIN CONFIGURATION (Top View)

(1) V40HL

• 80-pin Plastic QFP (14 × 20 mm)

µ

PD70208HGF-10-3B9

µ

PD70208HGF-12-3B9

µ

PD70208HGF-16-3B9

µ

PD70208HGF-20-3B9

A17/PS1

A18/PS2

A19/PS3

REFRQ

HLDRQ

HLDAK

RESOUT

VDDVDDRESET

READY

NMI

BS2

BS1

µ

PD70208H, 70216H

BS0

MRD

A16/PS0

NC

A15

A14

A13

A12

A11

A10

A9

A8

GND

NC

GND

AD7

AD6

AD5

AD4

AD3

AD2

AD1

AD0

NC

NC

END/TC

80 79 78 77 76 75 74 73 72 71 70 69 68 67 66 65

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

IORD

NC

MWR

IOWR

BUSLOCK

BUFR/W

BUFEN

CLKOUT

X1

X2

GND

NC

GND

High

ASTB

QS0

QS1

POLL

TCTL2

TOUT2

TCLK

NC

INTP7

INTP6

D

D

IC

X

X

DMAAK1

DMARQ0

DMARQ1

DMAAK0

DMAAK2

DMARQ2

DMARQ3/R

DMAAK3/T

INTAK/SRDY/TOUT1

Caution Leave IC pin open.

Data Sheet U13225EJ4V0DS00

DD

V

INTP1

INTP2

INTP3

INTP4

INTP5

3

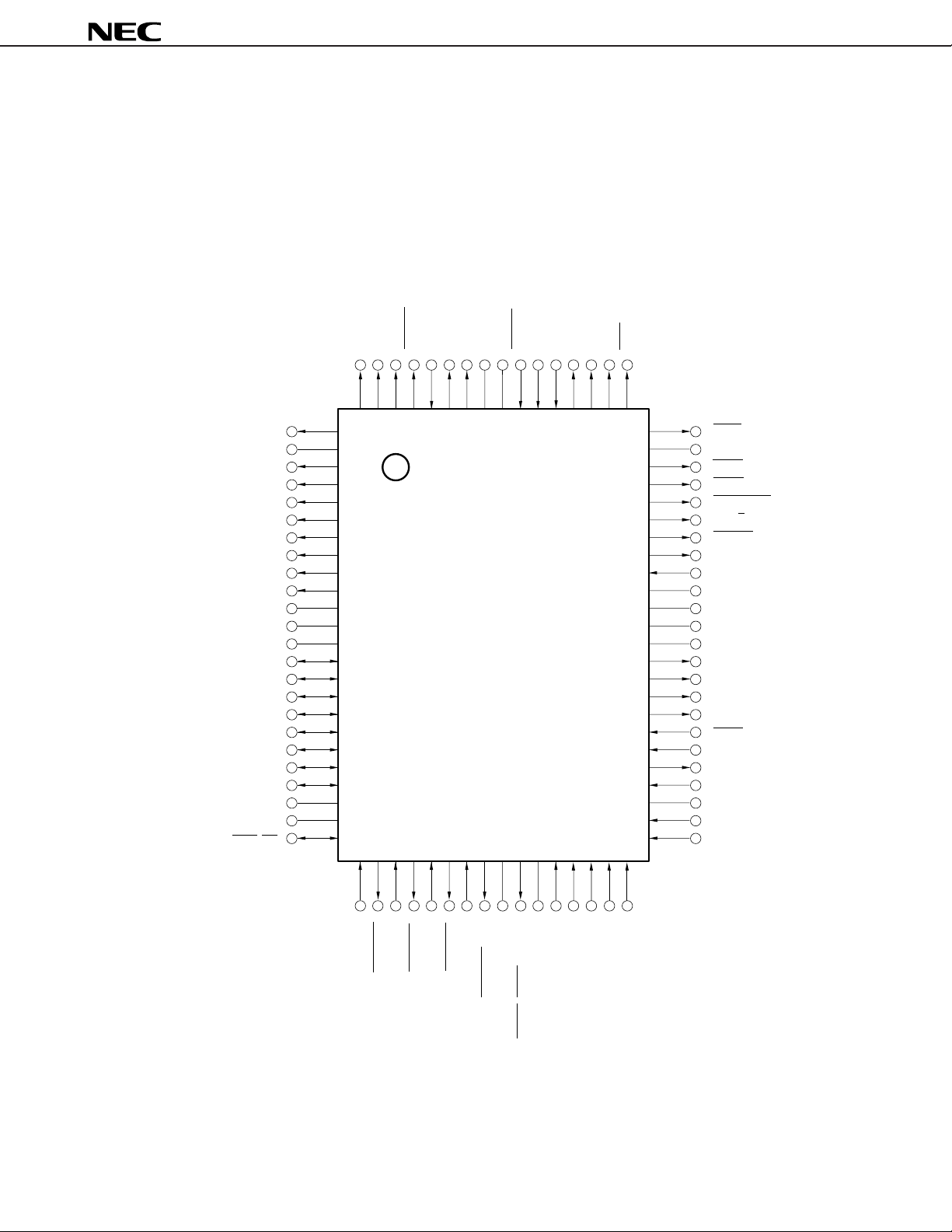

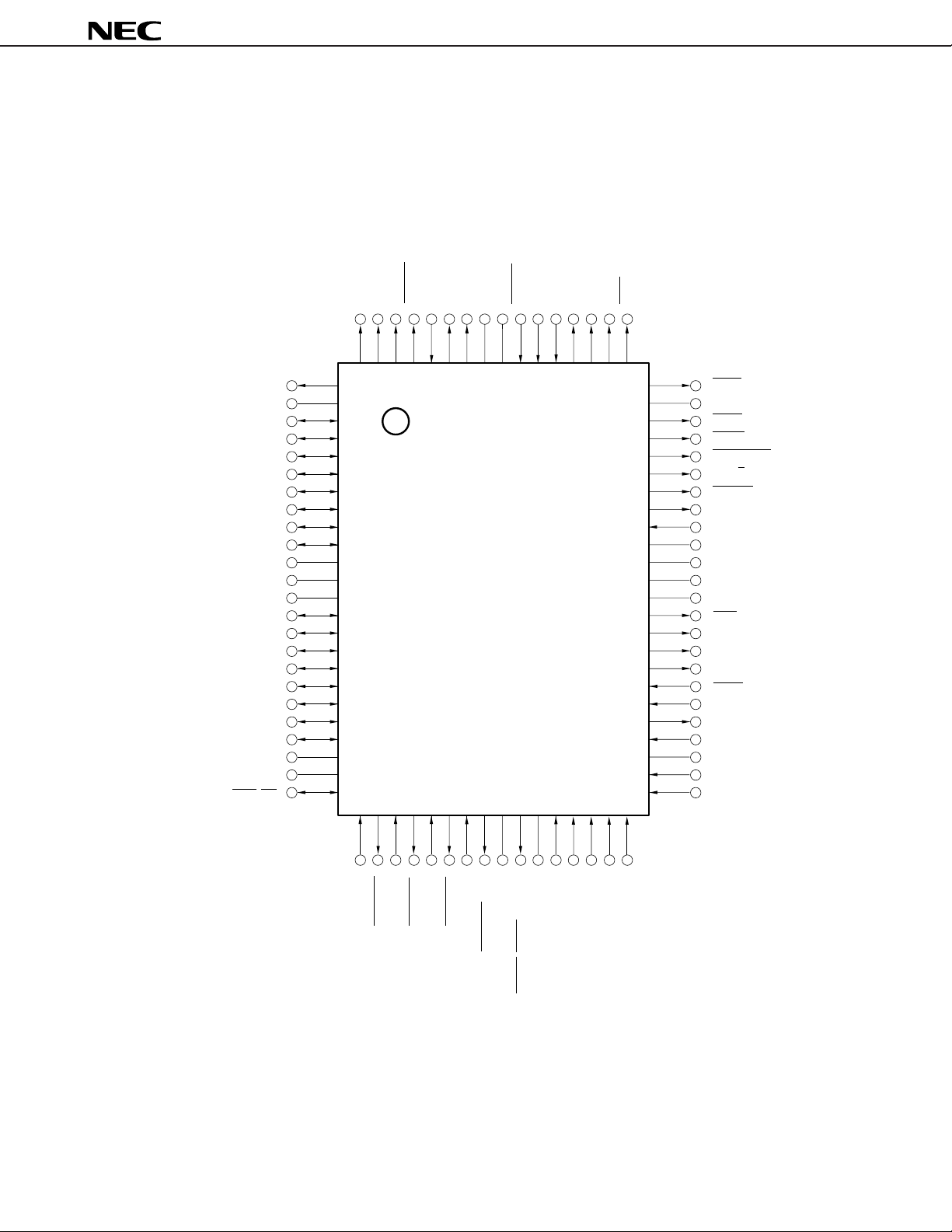

• 80-pin Plastic TQFP (Fine pitch) (12 × 12 mm)

µ

PD70208HGK-10-9EU

µ

PD70208HGK-12-9EU

µ

PD70208HGK-16-9EU

µ

PD70208HGK-20-9EU

NC

A16/PS0

A17/PS1

A18/PS2

A19/PS3

REFRQ

HLDRQ

HLDAK

80 79 78 77 76 75 74 73 72 71 70 69 68 67 66 65 64 63 62 61

A15

NC

A14

A13

A12

A11

A10

A9

A8

GND

GND

AD7

AD6

AD5

AD4

AD3

AD2

AD1

AD0

NC

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40

RESOUT

VDDVDDRESET

READY

NMI

BS2

BS1

BS0

MRD

µ

PD70208H, 70216H

IORD

NC

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

NC

MWR

IOWR

BUSLOCK

BUFR/W

BUFEN

CLKOUT

X1

X2

GND

GND

High

ASTB

QS0

QS1

POLL

TCTL2

TOUT2

TCLK

NC

D

D

NC

END/TC

DMARQ0

4

DMAAK1

DMARQ1

DMAAK0

Data Sheet U13225EJ4V0DS00

X

DMAAK2

DMARQ2

DMARQ3/R

DD

X

V

INTP1

INTP2

DMAAK3/T

INTAK/SRDY/TOUT1

INTP3

INTP4

INTP5

INTP6

NC

INTP7

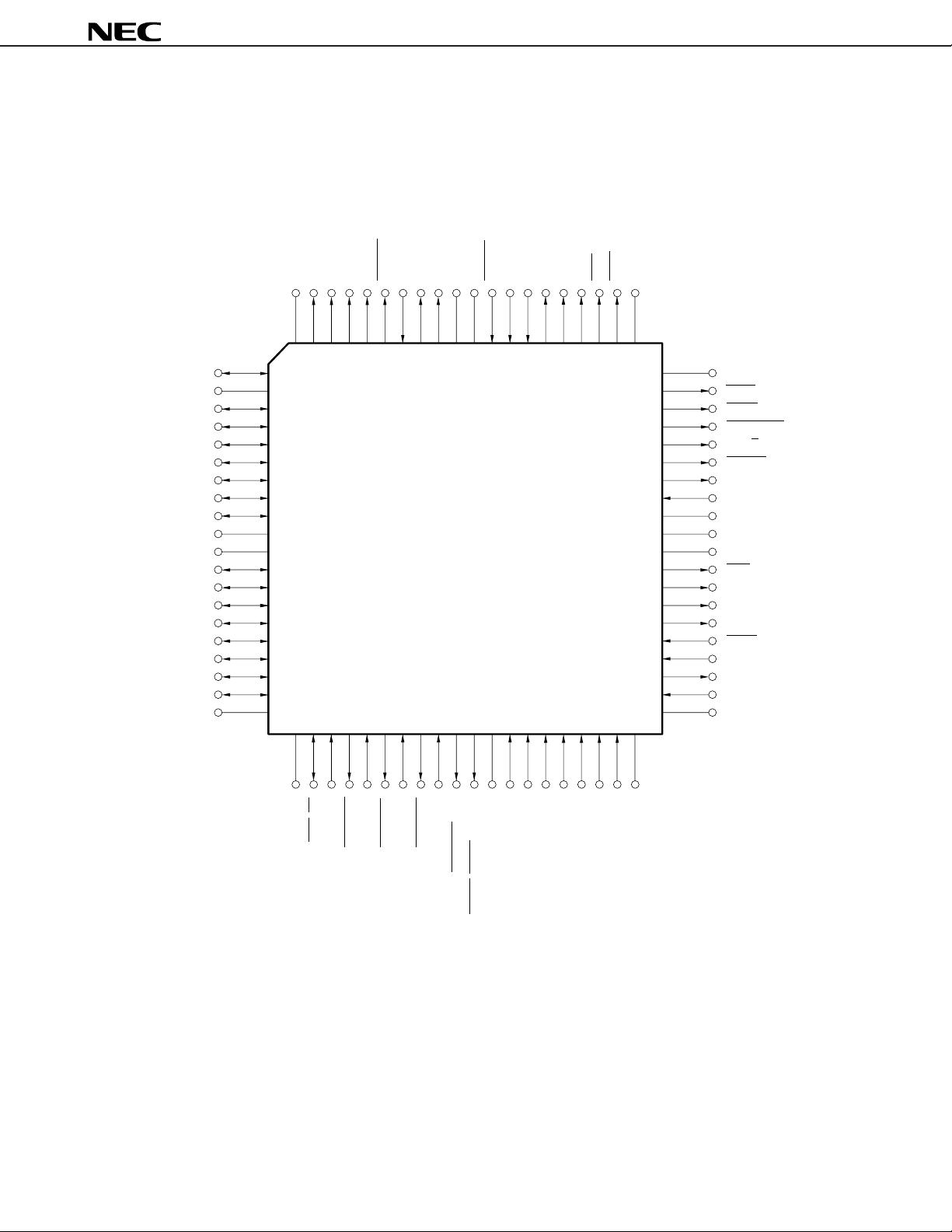

• 68-pin Plastic QFJ (950 × 950 mil)

µ

PD70208HLP-10

µ

PD70208HLP-12

µ

PD70208HLP-16

µ

PD70208HLP-20

A16/PS0

A17/PS1

A18/PS2

A19/PS3

REFRQ

HLDRQ

HLDAK

RESOUT

VDDRESET

READY

NMI

BS2

BS1

BS0

µ

PD70208H, 70216H

MRD

IORD

A15

A14

A13

A12

A11

A10

A9

A8

GND

AD7

AD6

AD5

AD4

AD3

AD2

AD1

AD0

9 8 7 6 5 4 3 2 1 68 67 66 65 64 63 62 61

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43

XD

XD

INTP1

INTP2

END/TC

DMARQ0

DMAAK1

DMARQ1

DMAAK0

DMAAK2

DMARQ2

DMARQ3/R

DMAAK3/T

INTP3

INTP4

INTP5

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

INTP6

INTP7

MWR

IOWR

BUSLOCK

BUFR/W

BUFEN

CLKOUT

X1

X2

GND

High

ASTB

QS0

QS1

POLL

TCTL2

TOUT2

TCLK

INTAK/SRDY/TOUT1

Data Sheet U13225EJ4V0DS00

5

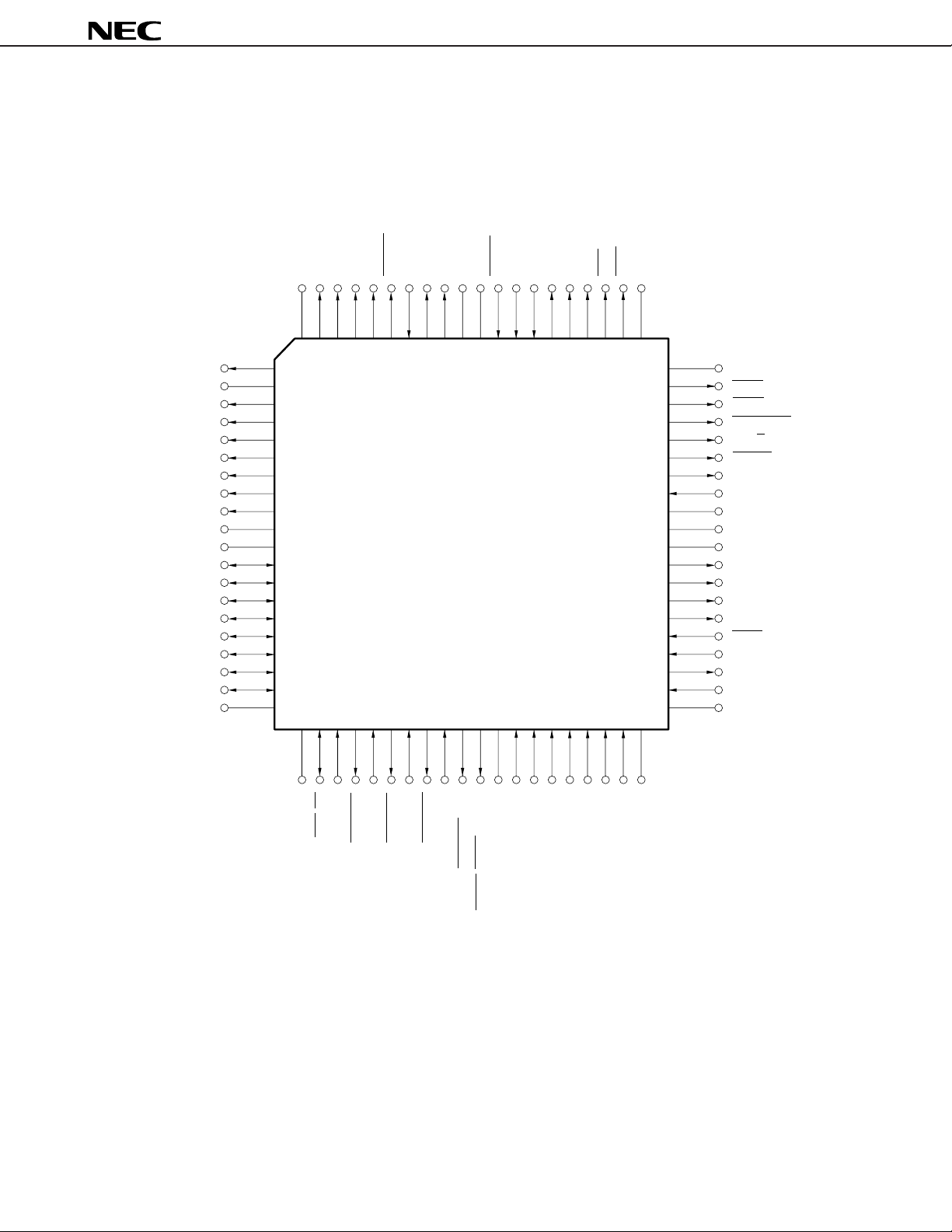

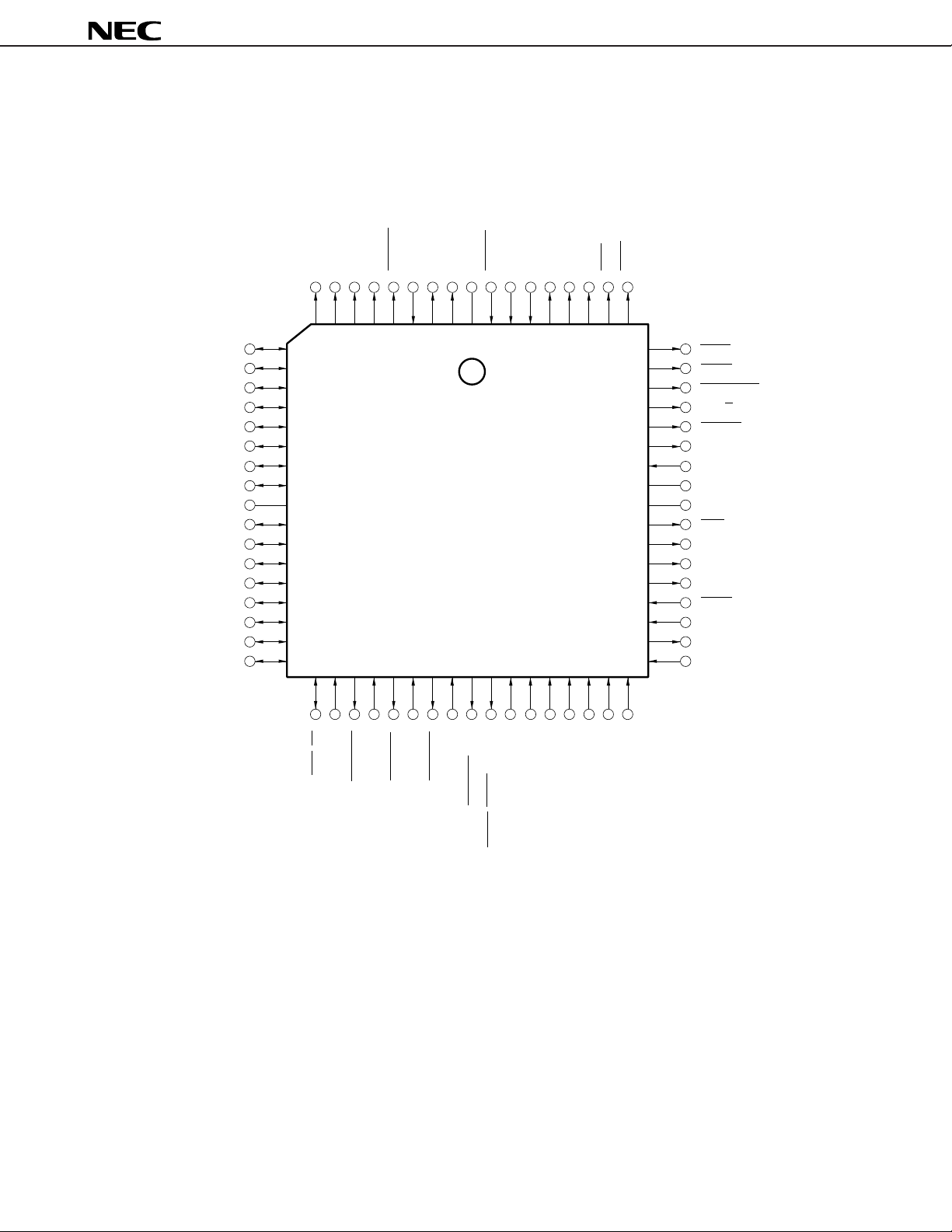

(2) V50HL

• 80-pin Plastic QFP (14 × 20 mm)

µ

PD70216HGF-10-3B9

µ

PD70216HGF-12-3B9

µ

PD70216HGF-16-3B9

µ

PD70216HGF-20-3B9

A17/PS1

A18/PS2

A19/PS3

REFRQ

HLDRQ

HLDAK

RESOUT

VDDVDD

RESET

READY

NMI

BS2

BS1

µ

PD70208H, 70216H

BS0

MRD

A16/PS0

NC

AD15

AD14

AD13

AD12

AD11

AD10

AD9

AD8

GND

NC

GND

AD7

AD6

AD5

AD4

AD3

AD2

AD1

AD0

NC

NC

END/TC

80 79 78 77 76 75 74 73 72 71 70 69 68 67 66 65

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

IORD

NC

MWR

IOWR

BUSLOCK

BUFR/W

BUFEN

CLKOUT

X1

X2

GND

NC

GND

UBE

ASTB

QS0

QS1

POLL

TCTL2

TOUT2

TCLK

NC

INTP7

INTP6

DD

IC

DMARQ0

DMARQ1

DMAAK0

DMAAK1

DMAAK2

DMARQ2

XD

DMAAK3/T

DMARQ3/RXD

V

INTP1

INTP2

INTP3

INTP4

INTAK/SRDY/TOUT1

INTP5

Caution Leave IC pin open.

6

Data Sheet U13225EJ4V0DS00

• 80-pin Plastic TQFP (Fine pitch) (12 × 12 mm)

µ

PD70216HGK-10-9EU

µ

PD70216HGK-12-9EU

µ

PD70216HGK-16-9EU

µ

PD70216HGK-20-9EU

NC

A16/PS0

A17/PS1

A18/PS2

A19/PS3

REFRQ

HLDRQ

HLDAK

80 79 78 77 76 75 74 73 72 71 70 69 68 67 66 65 64 63 62 61

AD15

NC

AD14

AD13

AD12

AD11

AD10

AD9

AD8

GND

GND

AD7

AD6

AD5

AD4

AD3

AD2

AD1

AD0

NC

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40

RESOUT

VDDVDDRESET

READY

NMI

BS2

BS1

BS0

MRD

µ

PD70208H, 70216H

IORD

NC

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

NC

MWR

IOWR

BUSLOCK

BUFR/W

BUFEN

CLKOUT

X1

X2

GND

GND

UBE

ASTB

QS0

QS1

POLL

TCTL2

TOUT2

TCLK

NC

NC

END/TC

DMARQ0

D

D

X

X

DMAAK1

DMARQ1

DMAAK0

DMAAK2

DMARQ2

DMAAK3/T

DMARQ3/R

Data Sheet U13225EJ4V0DS00

DD

V

INTP1

INTP2

INTP3

INTP4

INTP5

INTAK/SRDY/TOUT1

INTP6

INTP7

NC

7

• 68-pin Plastic QFJ (950 × 950 mil)

µ

PD70216HLP-10

µ

PD70216HLP-12

µ

PD70216HLP-16

µ

PD70216HLP-20

A16/PS0

A17/PS1

A18/PS2

A19/PS3

REFRQ

HLDRQ

HLDAK

RESOUT

VDDRESET

READY

NMI

BS2

BS1

BS0

µ

PD70208H, 70216H

MRD

IORD

AD15

AD14

AD13

AD12

AD11

AD10

AD9

AD8

GND

AD7

AD6

AD5

AD4

AD3

AD2

AD1

AD0

9 8 7 6 5 4 3 2 1 68 67 66 65 64 63 62 61

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43

D

D

X

X

INTP1

INTP2

END/TC

DMARQ0

DMAAK1

DMARQ1

DMAAK0

DMAAK2

DMARQ2

DMARQ3/R

DMAAK3/T

INTP3

INTP4

INTP5

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

INTP6

INTP7

MWR

IOWR

BUSLOCK

BUFR/W

BUFEN

CLKOUT

X1

X2

GND

UBE

ASTB

QS0

QS1

POLL

TCTL2

TOUT2

TCLK

INTAK/SRDY/TOUT1

8

Data Sheet U13225EJ4V0DS00

PIN NAMES

A8-A15 : Address Bus

A16/PS0-A19/PS3 : Address/Processor Status

AD0-AD15 : Address Bus/Data Bus

ASTB : Address Strobe

BS0-BS2 : Bus Status

BUFEN : Buffer Enable

BUFR/W : Buffer Read/Write

BUSLOCK : Bus Lock

CLKOUT : Clock Output

DMAAK0-DMAAK2 : DMA Acknowledge

DMAAK3/TXD : DMA Acknowledge/Transmit Data

DMARQ0-DMARQ2 : DMA Request

DMARQ3/RXD : DMA Request/Receive Data

END/TC : End/Terminal Count

GND : Ground

High : High Level Output

HLDAK : Hold Acknowledge

HLDRQ : Hold Request

IC : Internally Connected

INTAK/SRDY/TOUT1 : Interrupt Acknowledge/Serial Ready/Timer Output 1

INTP1-INTP7 : Interrupt Request from Peripherals

IORD : I/O Read

IOWR : I/O Write

MRD : Memory Read

MWR : Memory Write

NC : No Connection

NMI : Non-Maskable Interrupt Request

POLL : Poll

QS0, QS1 : Queue Status

READY : Ready

REFRQ : Refresh Request

RESET : Reset

RESOUT : Reset Output

TCLK : Timer Clock

TCTL2 : Timer Control 2

TOUT2 : Timer Output 2

UBE : Upper Byte Enable

DD : Power Supply

V

X1, X2 : Crystal

µ

PD70208H, 70216H

Data Sheet U13225EJ4V0DS00

9

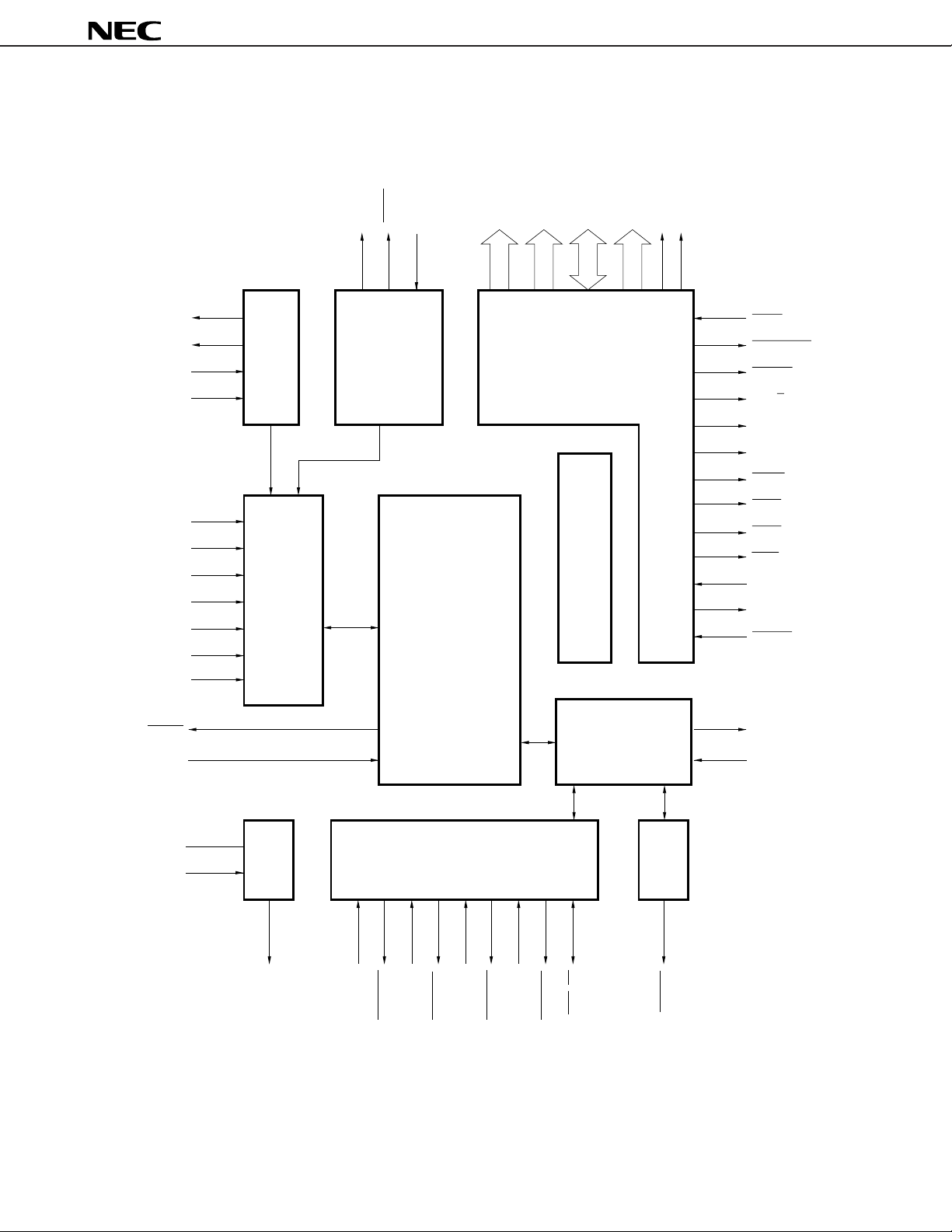

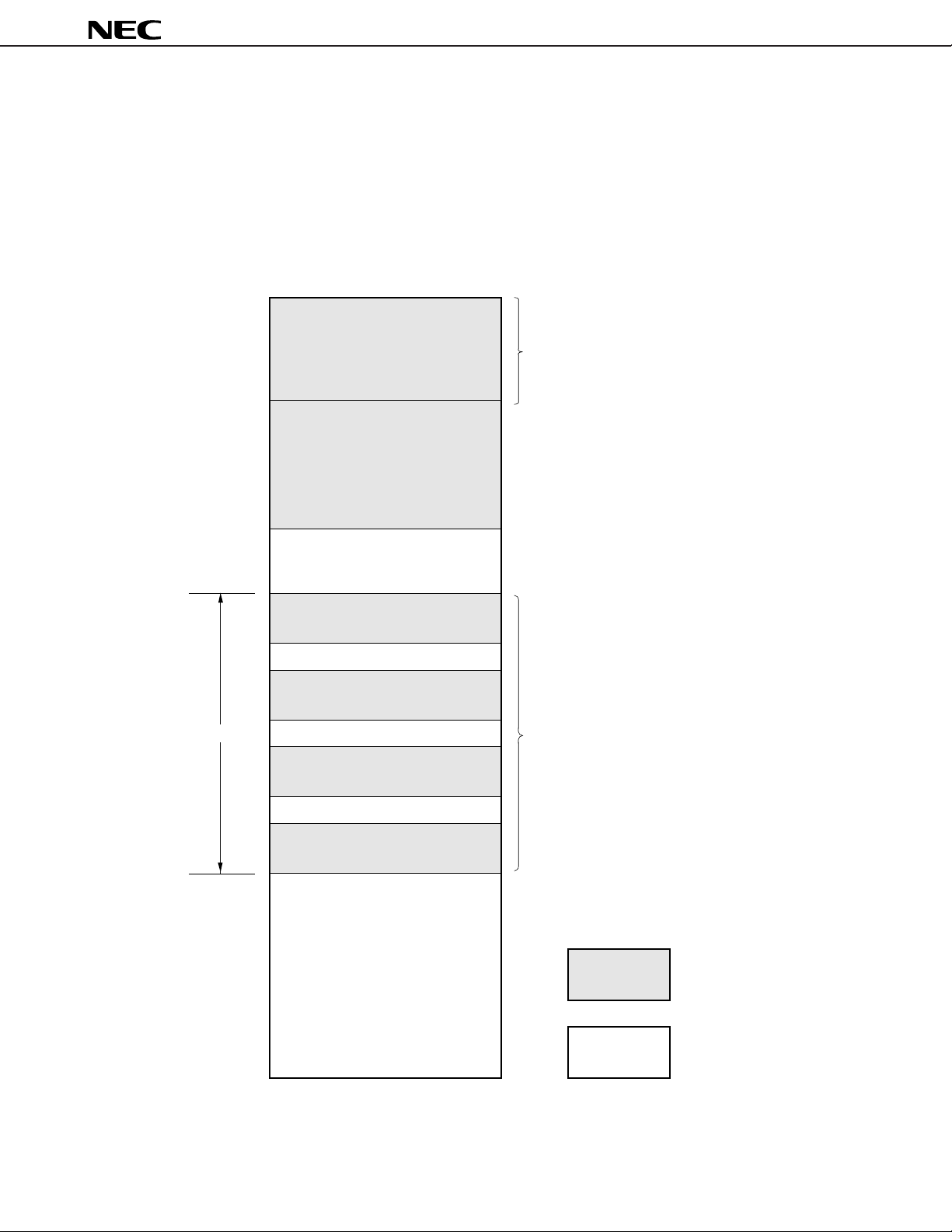

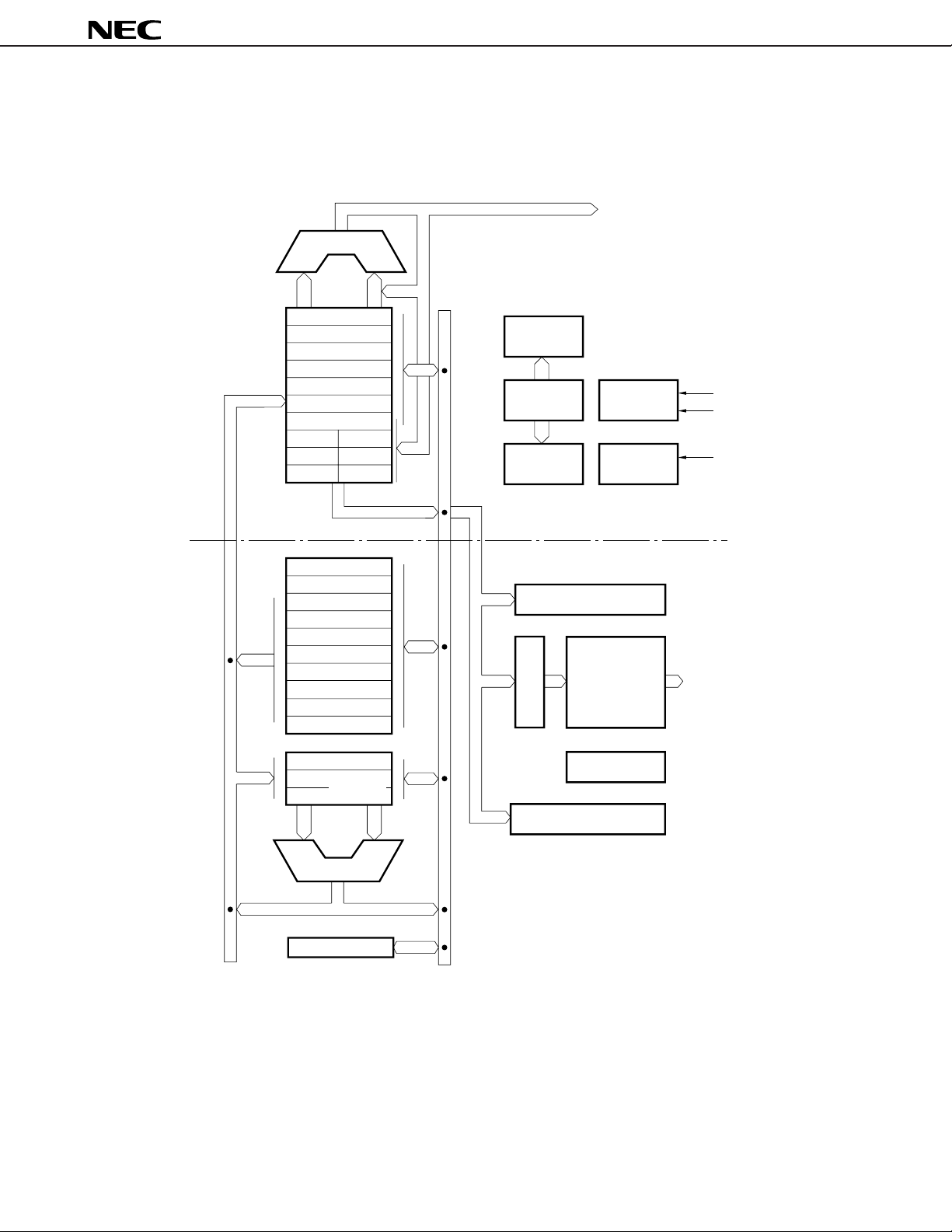

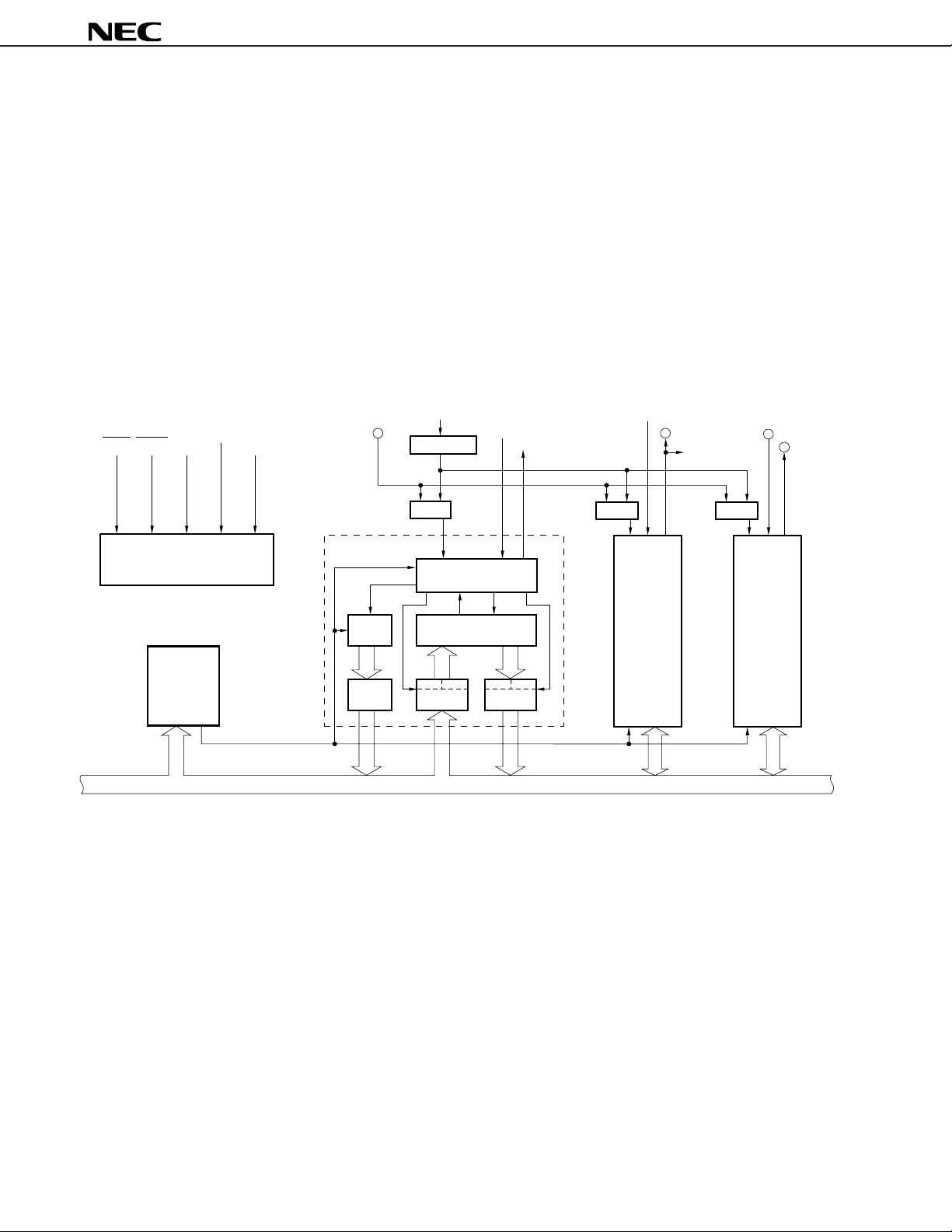

BLOCK DIAGRAM

(1) V40HL

µ

PD70208H, 70216H

TOUT2

TOUT1

TCTL2

TCLK

INTP7

INTP6

INTP5

INTP4

INTP3

INTP2

TCU

ICU

XD

T

SCU

SRDY

XD

R

CPU

A16/PS0-A19/PS3

A8-A15

WCU

AD0-AD7

BIU

QS1

BS0-BS2

QS0

POLL

BUSLOCK

BUFEN

BUFR/W

High

ASTB

IOWR

IORD

MWR

MRD

READY

RESOUT

RESET

INTP1

INTAK

NMI

X2

X1

CG

CLKOUT

DMAAK0

DMARQ0

DMAU

DMAAK1

DMARQ1

DMAAK2

DMARQ2

DMARQ3

CPU : Central Processing Unit REFU : Reflesh Control Unit

CG : Clock Generator TCU : Timer/Count Unit

BIU : Bus Interface Unit SCU : Serial Control Unit

BAU : Bus Arbitration Unit ICU : Interrupt Control Unit

WCU : Wait Control Unit DMAU : DMA Control Unit

10

Data Sheet U13225EJ4V0DS00

END/TC

DMAAK3

BAU

HLDAK

HLDRQ

REFU

REFRQ

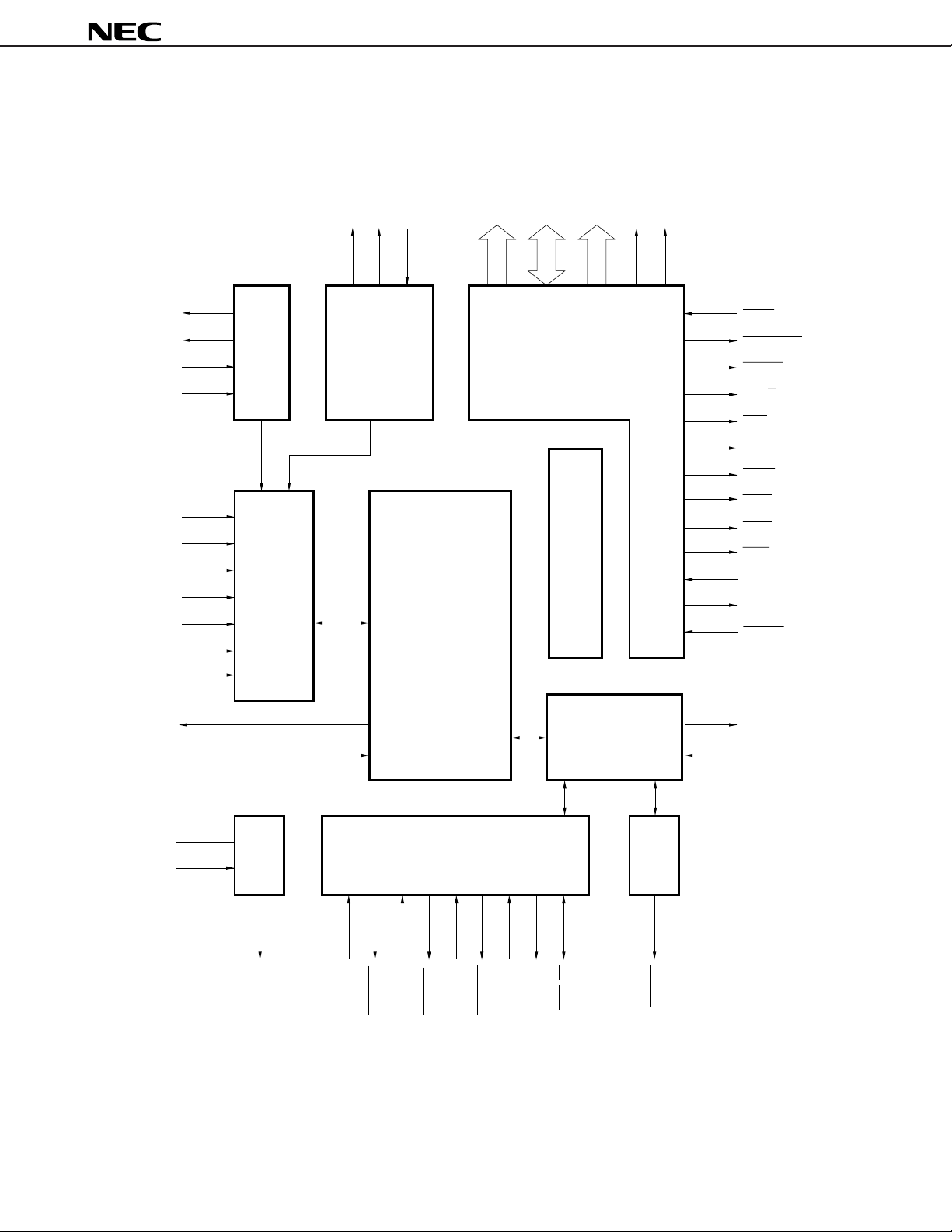

(2) V50HL

µ

PD70208H, 70216H

TOUT2

TOUT1

TCTL2

TCLK

INTP7

INTP6

INTP5

INTP4

INTP3

INTP2

TCU

ICU

XD

T

SCU

SRDY

RXD

CPU

A16/PS0-A19/PS3

AD0-AD15

BIU

WCU

BS0-BS2

QS1

QS0

POLL

BUSLOCK

BUFEN

BUFR/W

UBE

ASTB

IOWR

IORD

MWR

MRD

READY

RESOUT

RESET

INTP1

INTAK

NMI

X2

X1

CG DMAU

CLKOUT

DMAAK0

DMARQ0

DMAAK1

DMARQ1

DMARQ2

DMAAK2

DMARQ3

END/TC

DMAAK3

BAU

HLDAK

HLDRQ

REFU

REFRQ

Data Sheet U13225EJ4V0DS00

11

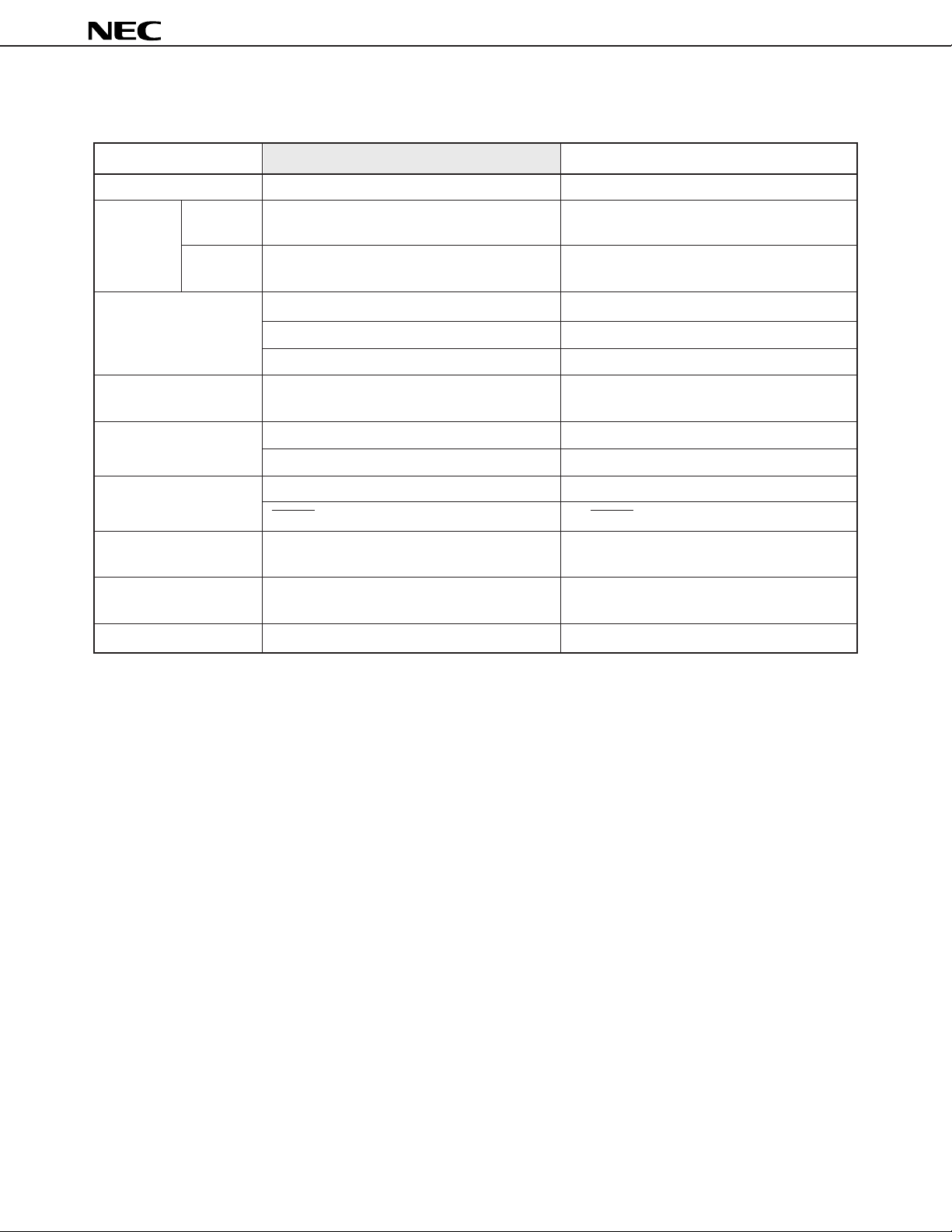

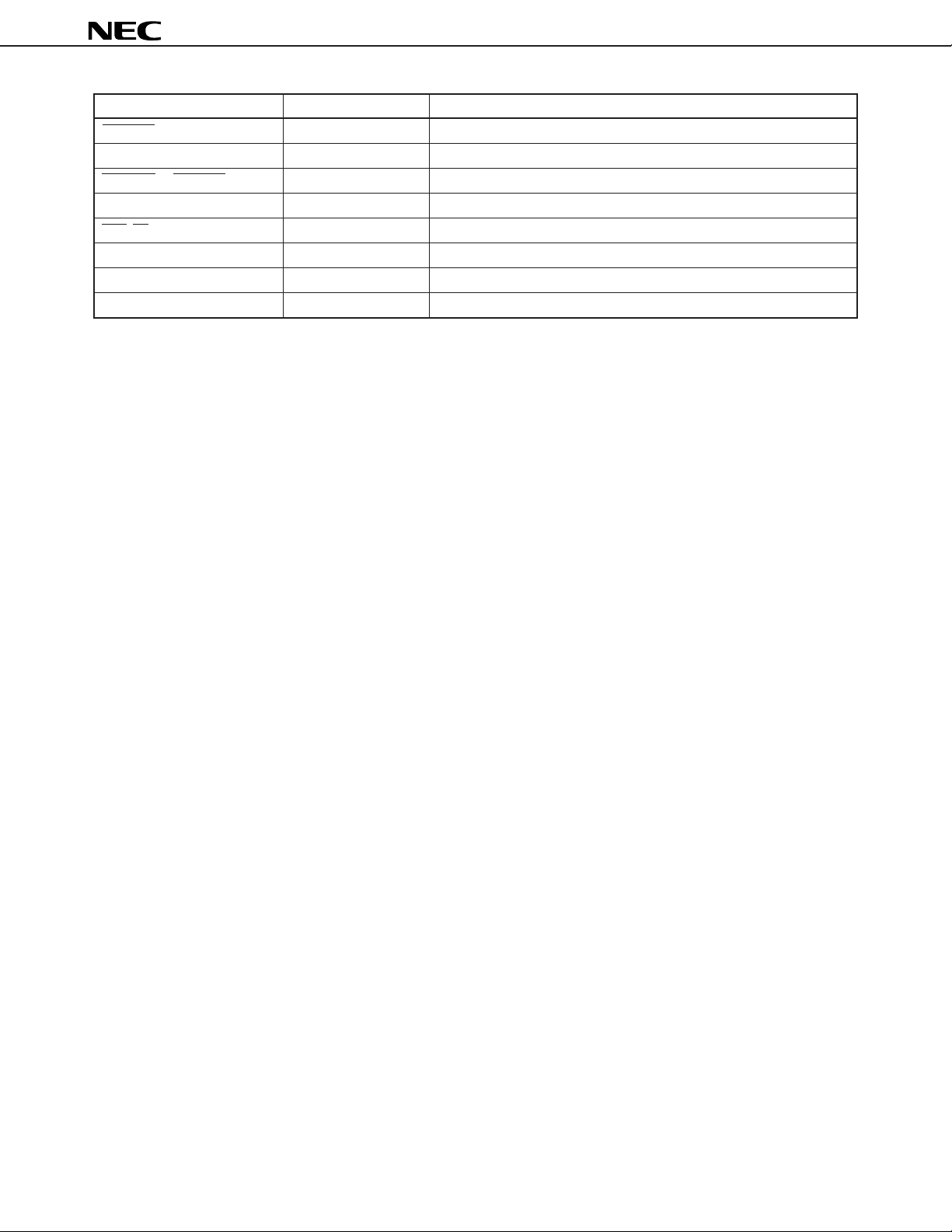

DIFFERENCES FROM V40 AND V50

Item V40, V50V40HL, V50HL

µ

PD70208H, 70216H

Operating supply voltage

Operating

frequency

Clock generator

(CG)

Internal I/O relocation

function

Wait control unit (WCU)

Refresh control unit

(REFU)

Serial control unit (SCU)

DMA control unit (DMAU)

Standby functions

VDD = 5 V

VDD = 3 V

3 V, 5 V

MAX. : 10, 12.5, 16, 20 MHz

MIN. : DC

MAX. : 5, 6.25, 8, 10 MHz

MIN. : DC

Variable scaling factor

Variable instruction cycle time

Maximum input frequency: 40 MHz

Switchable 8-bit boundary or 16-bit boundary

relocation function

Memory space: 5 divisions

I/O space: 3 divisions

Refresh address: 16 bits

REFRQ extended timing supported

Dedicated baud rate generator incorporated

µ

PD71071/71037 subset (either function

selectable)

HALT mode, STOP mode

Note 1

Note 2

5 V

MAX. : 8, 10 MHz

MIN. : 2 MHz

No operation

Fixed scaling factor

Fixed instruction cycle time

Maximum input frequency: 20 MHz

V40: Relocation possible on 8-bit boundary

V50: Relocation possible on 16-bit boundary

Memory space: 3 divisions

I/O space: Not divided

Refresh address: 9 bits

No REFRQ extended timing

No dedicated baund rate generator

incorporated

µ

PD71071 subset

HALT mode only

Notes 1. Divided into 3 when a reset is performed.

2. Not divided when a reset is performed.

12

Data Sheet U13225EJ4V0DS00

µ

PD70208H, 70216H

CONTENTS

1. PIN FUNCTIONS ................................................................................................................................... 15

1.1 LIST OF PIN FUNCTIONS........................................................................................................................... 15

1.2 PROCESSING OF UNUSED PINS.............................................................................................................. 17

2. MEMORY AND I/O CONFIGURATION ................................................................................................ 19

2.1 MEMORY SPACE......................................................................................................................................... 19

2.2 I/O SPACE .................................................................................................................................................... 21

3. CPU ........................................................................................................................................................ 22

4. CG (CLOCK GENERATOR) ................................................................................................................. 24

5. BIU (BUS INTERFACE UNIT) .............................................................................................................. 24

6. BAU (BUS ARBITRATION UNIT) ........................................................................................................ 25

7. WCU (WAIT CONTROL UNIT) ................................................................................................................ 27

7.1 FEATURES ................................................................................................................................................... 27

7.2 RELATION BETWEEN WCU AND READY PIN ........................................................................................ 28

8. REFU (REFRESH CONTROL UNIT).................................................................................................... 29

8.1 FEATURES ................................................................................................................................................... 29

8.2 REFRESH OPERATIONS ............................................................................................................................ 29

9. TCU (TIMER/COUNTER UNIT) ............................................................................................................ 30

9.1 FEATURES ................................................................................................................................................... 30

9.2 TCU INTERNAL BLOCK DIAGRAM........................................................................................................... 30

10. SCU (SERIAL CONTROL UNIT) .......................................................................................................... 31

10.1 FEATURES ................................................................................................................................................... 31

10.2 SCU INTERNAL BLOCK DIAGRAM ........................................................................................................... 31

11. ICU (INTERRUPT CONTROL UNIT) .................................................................................................... 32

11.1 FEATURES ................................................................................................................................................... 32

11.2 ICU INTERNAL BLOCK DIAGRAM ............................................................................................................ 32

12. DMAU (DMA CONTROL UNIT) ............................................................................................................ 33

12.1 FEATURES ................................................................................................................................................... 33

12.2 DMAU INTERNAL BLOCK DIAGRAM ....................................................................................................... 33

13. STANDBY FUNCTIONS........................................................................................................................ 34

14. RESET OPERATION ............................................................................................................................. 3 4

15. INSTRUCTION SET............................................................................................................................... 35

Data Sheet U13225EJ4V0DS00

13

µ

PD70208H, 70216H

16. ELECTRICAL SPECIFICATIONS......................................................................................................... 66

16.1 AT 5 V OPERATION .................................................................................................................................... 66

16.2 AT 3 V OPERATION .................................................................................................................................... 75

17. PACKAGE DRAWINGS ........................................................................................................................ 100

18. RECOMMENDED SOLDERING CONDITIONS ................................................................................... 103

14

Data Sheet U13225EJ4V0DS00

µ

PD70208H, 70216H

1. PIN FUNCTIONS

1.1 LIST OF PIN FUNCTIONS

Pin Name Input/Output Function

Note 3

Note 3

Note 3

Note 3

Note 3

Note 2, 3

Note 2, 3

Note 3

Note 3

Note 3

Note 1, 3

Note 3

3-state I/O Time-division address/data bus

3-state I/O Time-division address/data bus

3-state output Address bus

3-state output Time-division address/processor status

3-state output Memory read strobe

3-state output Memory read strobe

3-state output I/O read strobe

3-state output I/O write strobe

3-state output Data bus upper byte enable

3-state output High level output

3-state output Bus lock

3-state output Buffer read/write

3-state output Buffer enable

3-state output Bus status

AD0 to AD15

AD0 to AD7

A8 to A15

A16/PS0 to A19/PS3

REFRQ Output Refresh request

HLDRQ Input Bus hold request

HLDAK Output Bus hold acknowledge

RESET Input Reset

RESOUT Output System reset output

READY Input Bus cycle end

NMI Input Non-maskable interrupt

MRD

MWR

IORD

IOWR

ASTB Output Address strobe

Note 1, 3

UBE

Note 2

High

BUSLOCK

POLL Input Floating-point operation processor polling

BUFR/W

BUFEN

X1 Input Crystal/external clock

X2 —

CLKOUT Output Clock output

BS0 to BS2

QS0, QS1 Output Queue status

TOUT2 Output Timer 2 output

TCTL2 Input Timer 2 control

TCLK Input Timer clock

INTP1 to INTP7 Input Maskable interrupts

INTAK/SRDY/TOUT1 Output Interrupt acknowledge/serial reception ready/timer 1 output

Notes 1. V50HL only

2. V40HL only

3. These pins are provided with a latch. Therefore, when they go into a high-impedance state, they hold

the status before the high-impedance state until driven by an external device. It is not necessary to pull

up or down the data bus. To invert the level of the pin that goes into a high-impedance state by an

external device, a drive current higher than the latch invert current (I

Data Sheet U13225EJ4V0DS00

ILH, IILL) is necessary.

15

µ

PD70208H, 70216H

Pin Name Input/Output Function

DMAAK3/TXD Output DMA acknowledge 3/serial transmit data

DMARQ3/RXD Input DMA request 3/serial receive data

DMAAK0 to DMAAK2 Output DMA acknowledge

DMARQ0 to DMARQ2 Input DMA request

END/TC I/O DMA service forcible termination/DMA service completion

VDD — Positive power supply pin

GND — Ground potential pin

IC — Internal connection pin (External connection impossible)

16

Data Sheet U13225EJ4V0DS00

µ

PD70208H, 70216H

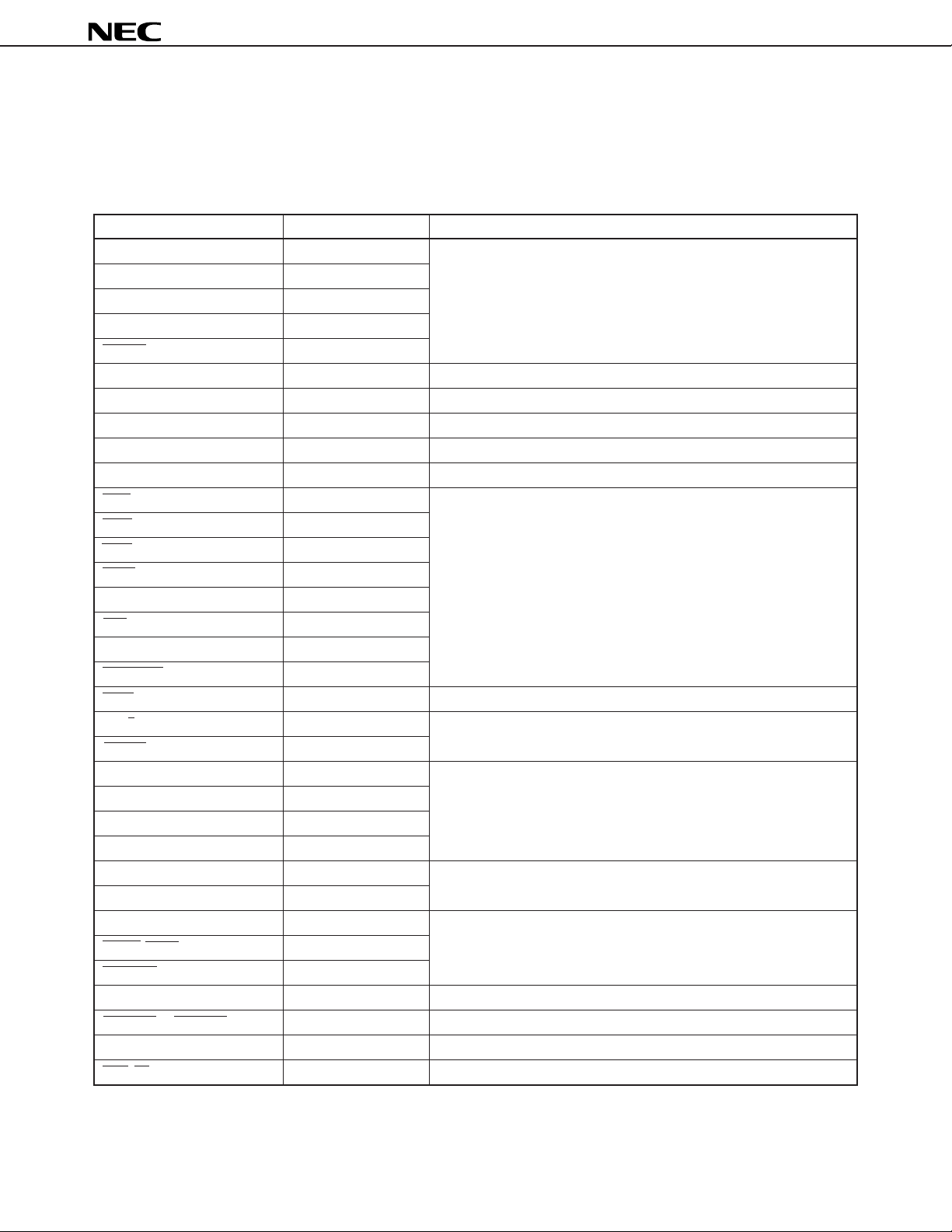

1.2 PROCESSING OF UNUSED PINS

Table 1-1 shows the processing (recommended connection) of the unused pins. Use of a resistor with a resistance of

1 to 10 kΩ is recommended to connect these pins to VDD or GND via resistor.

Table 1-1. Processing of Unused Pins

Pin Name Input/Output Recommended Connection

AD0 to AD15

AD0 to AD7

A8 to A15

A16/PS0 to A19/PS3 3-state output

REFRQ Output

HLDRQ Input Connect to GND via resistor

HLDAK Output Open

RESOUT Output Open

READY Input Connect to VDD via resistor

NMI Input Connect to GND via resistor

MRD 3-state output Open

MWR 3-state output

IORD 3-state output

IOWR 3-state output

ASTB Output

Note 1

UBE

Note 2

High

BUSLOCK 3-state output

POLL Input Connect to GND via resistor

BUFR/W 3-state output Open

BUFEN 3-state output

CLKOUT Output Open

BS0 to BS2 3-state output

QS0, QS1 Output

TOUT2 Output

TCTL2 Input Connect to GND via resistor

TCLK Input

INTP1 to INTP7 Input Open

INTAK/SRDY/TOUT1 Output

DMAAK3/TxD Output

DMARQ3/RxD Input Connect to GND via resistor

DMAAK0 to DMAAK2 Output Open

DMARQ0 to DMARQ2 Input Connect to GND via resistor

END/TC I/O Individually connect to VDD via resistor

Note 1

Note 2

Note 2

3-state I/O Open

3-state I/O

3-state output

3-state output

Output

Notes 1. V50HL only

2. V40HL only

Data Sheet U13225EJ4V0DS00

17

µ

PD70208H, 70216H

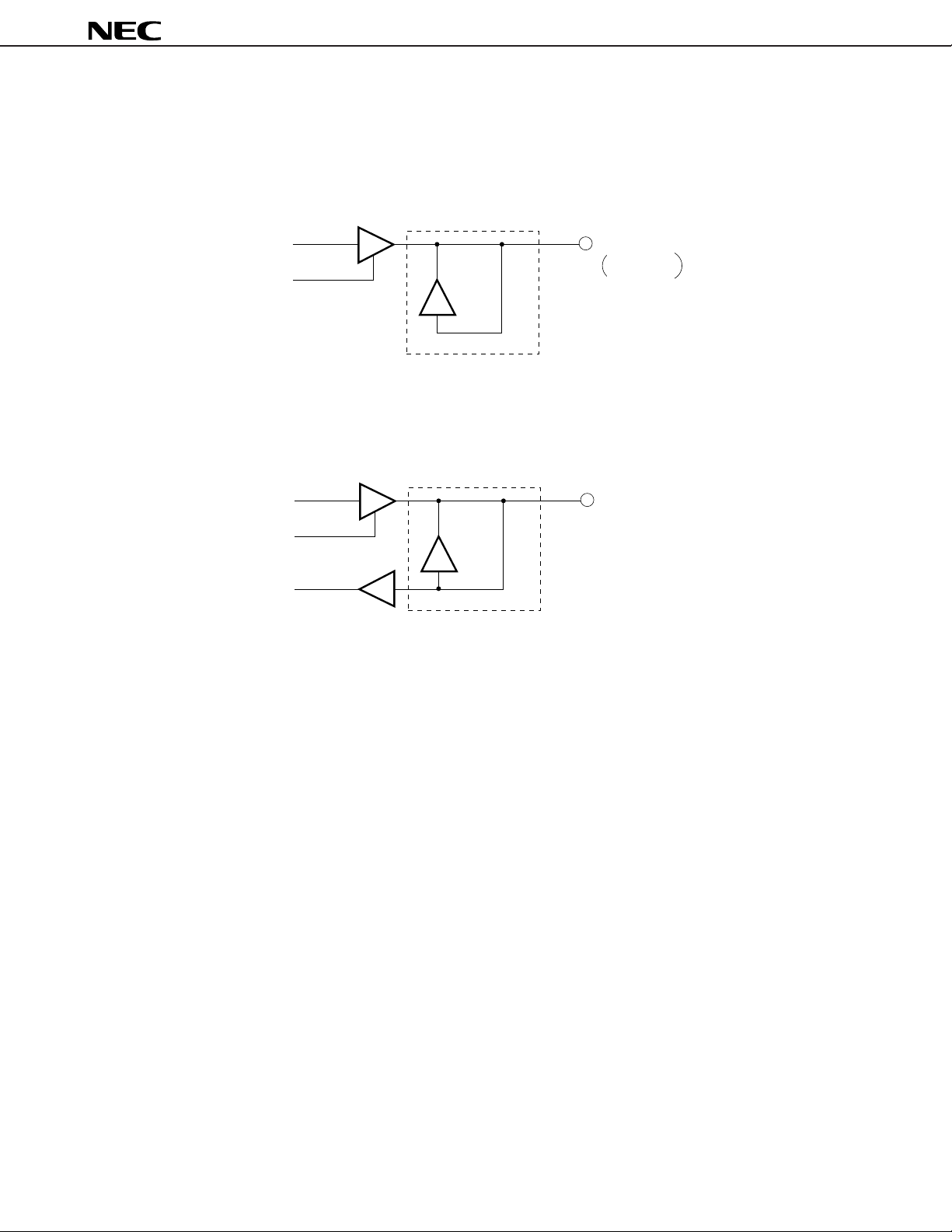

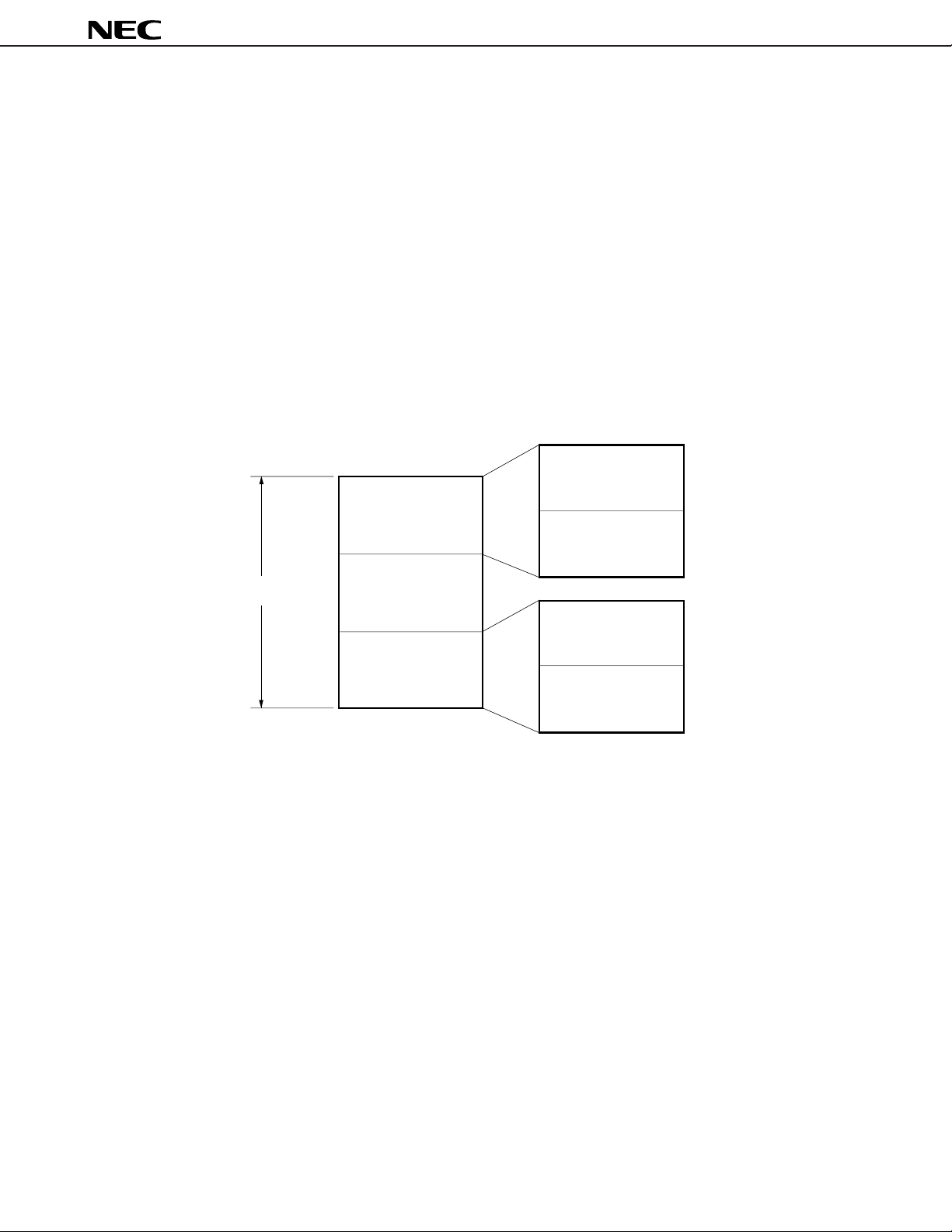

Remark The circuit configuration of the latch is as illustrated below. To invert the level of the pin with a latch, a drive

current higher than the latch invert current is necessary.

(1) Output pin

(2) I/O pin

Hi-Z

control

Hi-Z

control

Output buffer

Output buffer

Input buffer

Latch

Output pin

address bus,

control bus

Latch

I/O pin

(data bus)

18

Data Sheet U13225EJ4V0DS00

2. MEMORY AND I/O CONFIGURATION

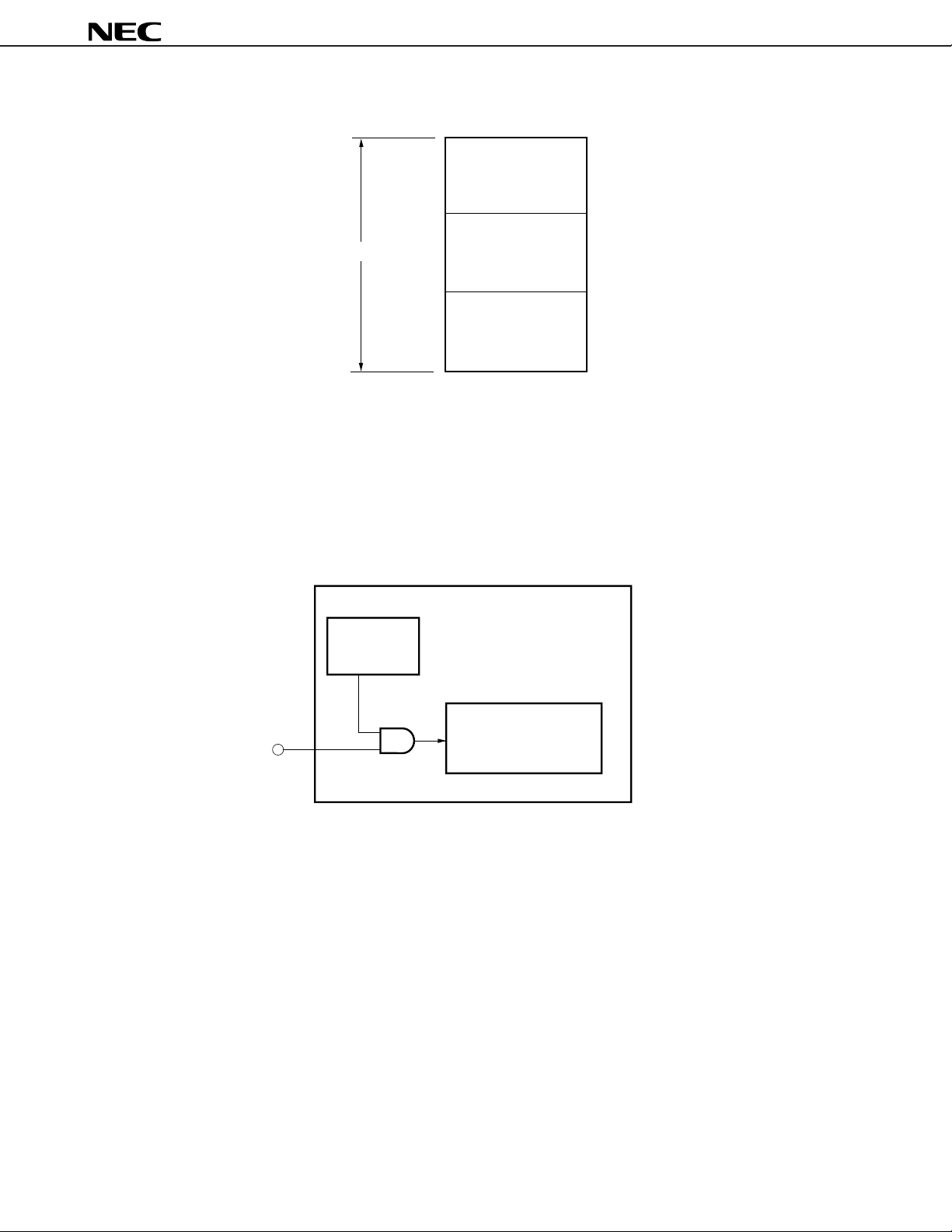

2.1 MEMORY SPACE

The V40HL and V50HL can access a 1M-byte (512K-word) memory space.

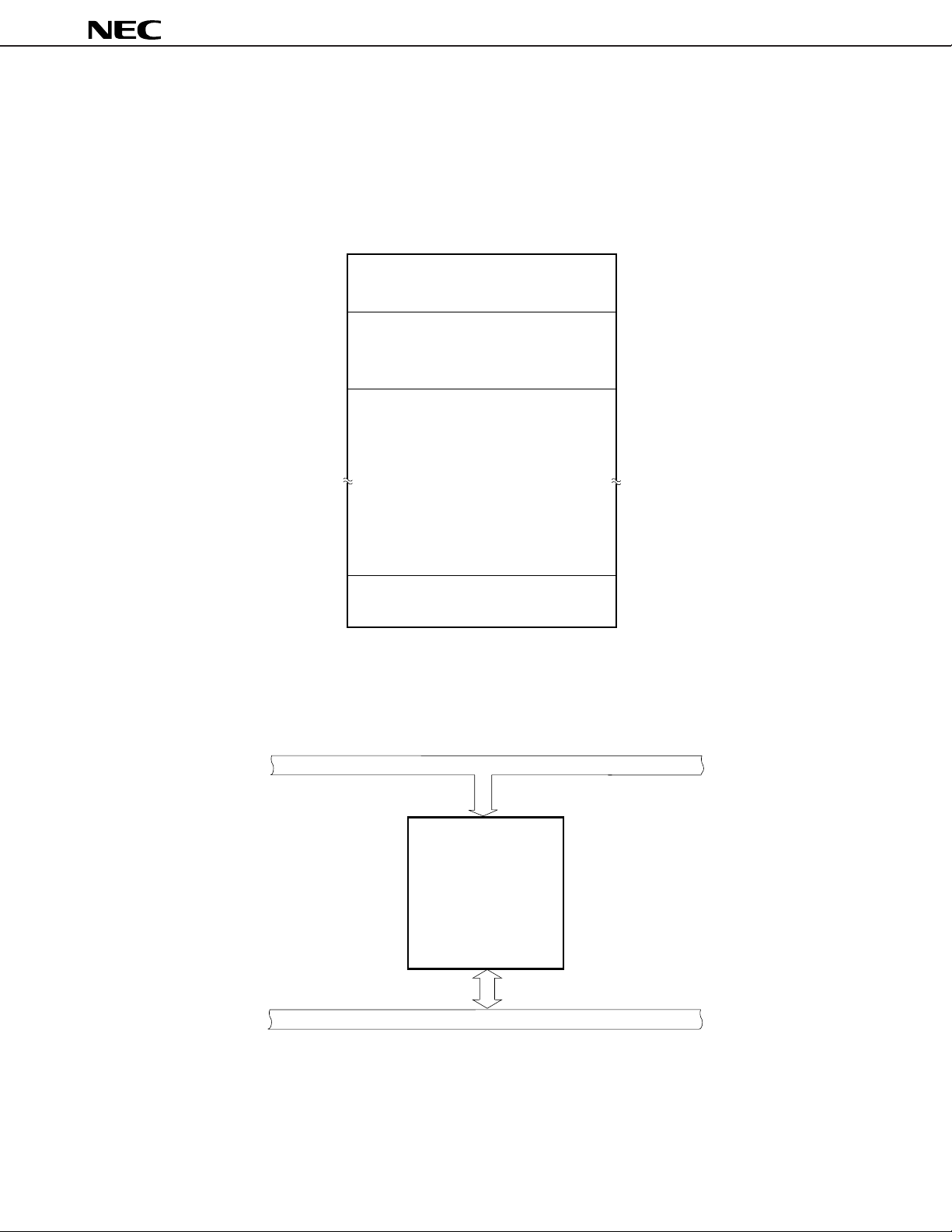

Figure 2-1. Memory Map

FFFFFH

Reserved

FFFFCH

FFFFBH

Dedicated

FFFF0H

FFFEFH

General Use

µ

PD70208H, 70216H

A0-A19

00400H

003FFH

Interrupt Vector Table

00000H

Figure 2-2. Interface with Memory (1/2)

(a) V40HL

Address Bus (20)

Memory

1M Byte

8

D0-D7

Data Bus (8)

Data Sheet U13225EJ4V0DS00

19

Figure 2-2. Interface with Memory (2/2)

(b) V50HL

µ

PD70208H, 70216H

A1-A19

A0

UBE

D0-D15

Address Bus (19)

19 19

BSEL BSEL

Memory

Upper Bank

512K Byte

D8-D15 D0-D7

8

Data Bus (16)

Memory

Lower Bank

512K Byte

8

20

Data Sheet U13225EJ4V0DS00

µ

PD70208H, 70216H

2.2 I/O SPACE

In the V40HL and V50HL, I/Os up to 64K bytes (32K words) can be accessed in an area independent of the memory.

The various on-chip peripheral LSIs are set by accessing the system I/O area.

Extended functions added to those of the V40 and V50 are mapped onto unused V40 and V50 registers and the reserved

area.

The I/O map is shown in Figure 2-3.

Figure 2-3. I/O Map

FFFFH

Area used for setting of I/O boundary,

System I/O Area

FFE0H

FFDFH

Reserved Area

WCU, REFU, baud rate generator, etc.,

and DMAU, ICU, TCU and SCU allocation.

FF00H

FEFFH

256 Bytes

DMAU

ICU

The DMAU, ICU, TCU and SCU

are allocated within any 256 bytes.

TCU

SCU

Internal I/O Area

0000H

Data Sheet U13225EJ4V0DS00

External I/O Area

21

µ

PD70208H, 70216H

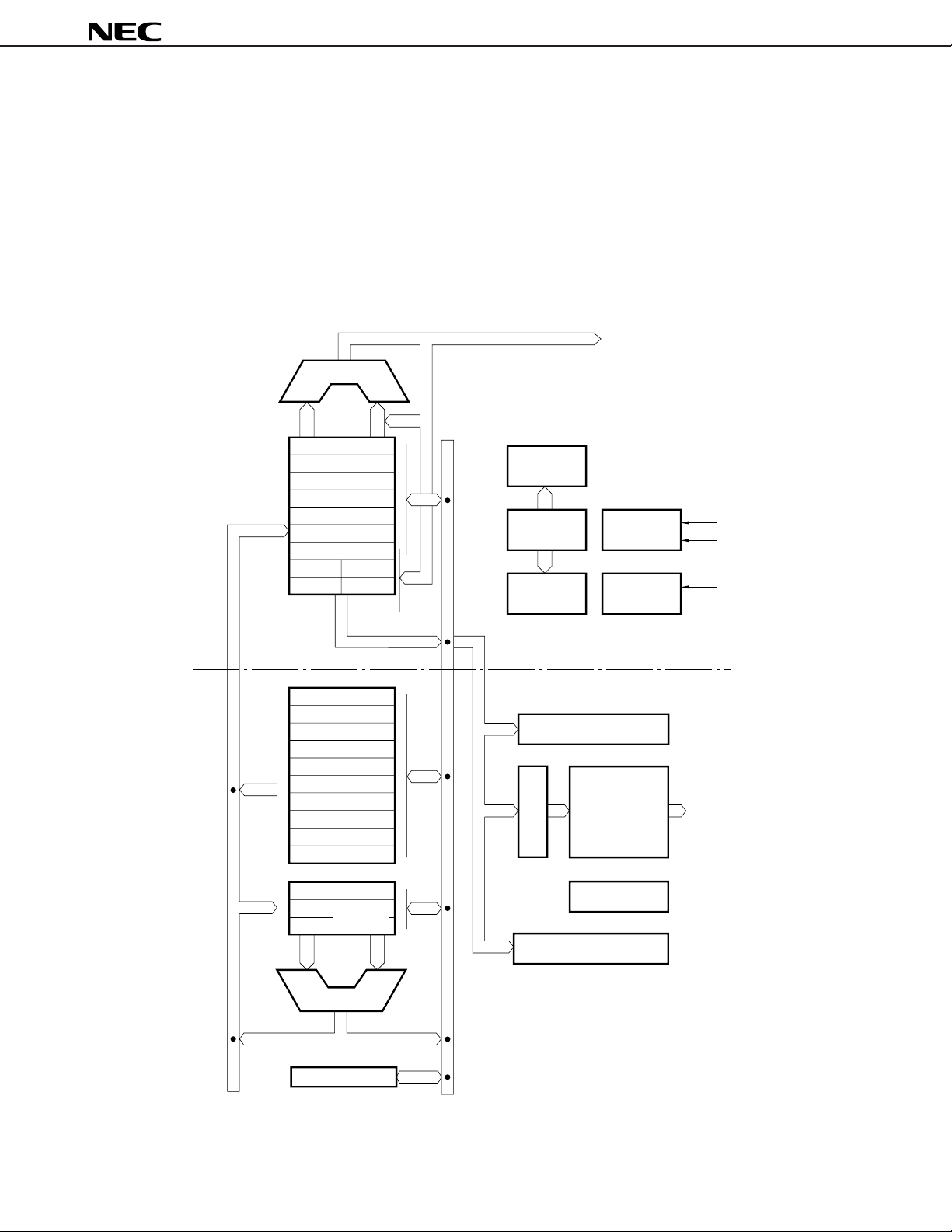

3. CPU

The CPU has the same functions as the V20HLTM and V30HLTM. In hardware terms, there are some changes regarding

the use of the bus with on-chip peripherals, but in software terms the CPU is fully compatible.

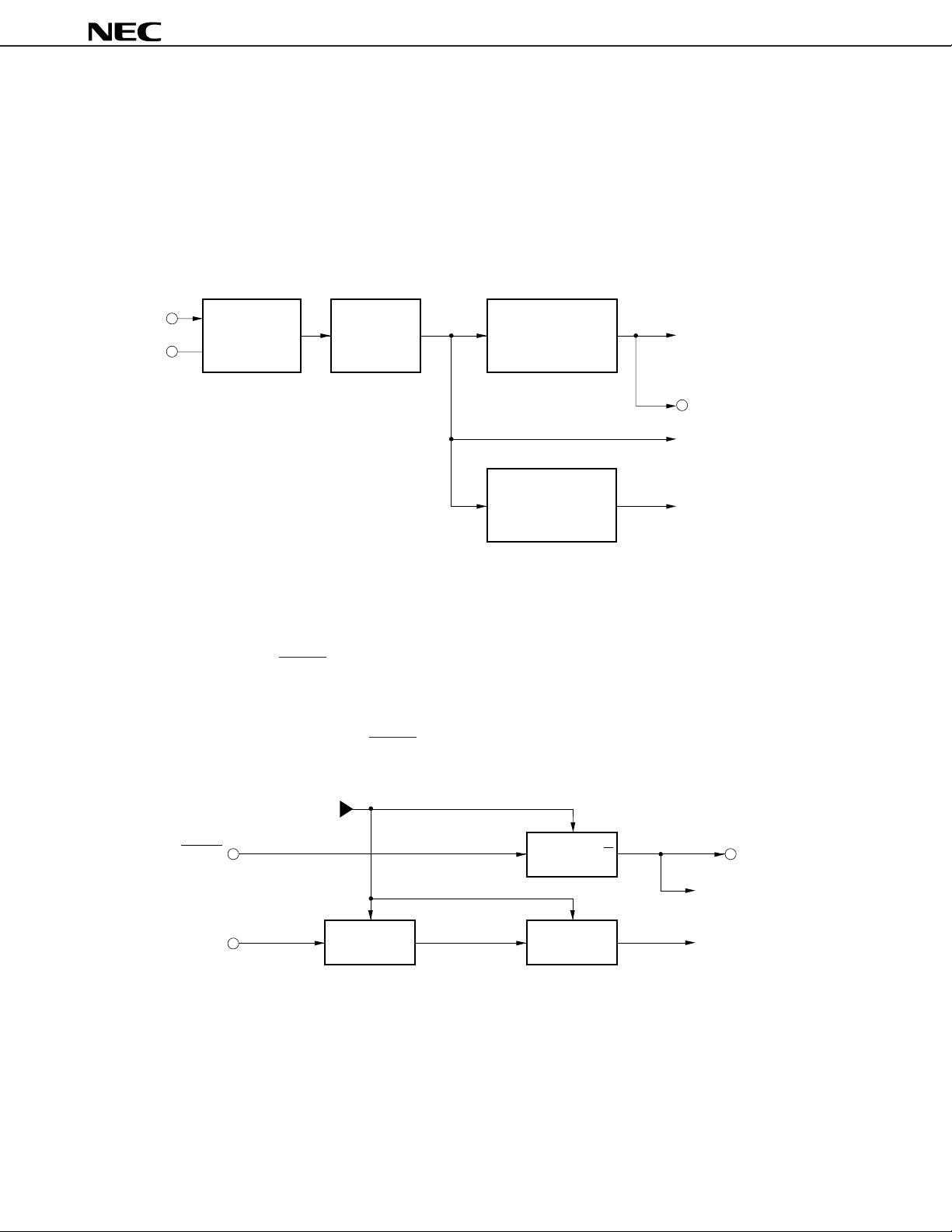

The internal block diagram of the CPU is shown in Figure 3-1.

Figure 3-1. Internal Block Diagram of CPU (1/2)

(a) V40HL

Internal Address/Data Bus (20)

To BIU

ADM

TC

TA

TB

Q0

Q2

PS

SS

DS0

DS1

PFP

DP

TEMP

LC

PC

AW

BW

CW

DW

IX

IY

BP

SP

SHIFTER

Q1

Q3

T-STATE

CONTROL

CYCLE

DECISION

QUEUE

CONTROL

EFFECTIVE ADDRESS

GENERATOR

ADDRESS

REGISTER

µ

Queue Data Bus (8)

INSTRUCTION DECODER

INTERRUPT

CONTROL

STANDBY

CONTROL

INSTRUCTION

µ

ROM

SEQUENCE

µ

CONTROL

BCU

EXU

29

Micro Data Bus

NMI

INT

(From ICU)

CLOCK

(From CG)

22

Sub Data Bus

(16)

ALU

PSW

Main Data Bus

(16)

Data Sheet U13225EJ4V0DS00

Figure 3-1. Internal Block Diagram of CPU (2/2)

(b) V50HL

Internal Address/Data Bus (20)

To BIU

ADM

µ

PD70208H, 70216H

PS

SS

DS0

DS1

PFP

DP

TEMP

Q0

Q2

Q4 Q5

LC

PC

AW

BW

CW

DW

IX

IY

BP

SP

TC

TA

SHIFTER

TB

Q1

Q3

T-STATE

CONTROL

CYCLE

DECISION

QUEUE

CONTROL

EFFECTIVE ADDRESS

GENERATOR

ADDRESS

REGISTER

µ

Queue Data Bus (8)

INSTRUCTION DECODER

INTERRUPT

CONTROL

STANDBY

CONTROL

INSTRUCTION

µ

ROM

SEQUENCE

µ

CONTROL

BCU

EXU

29

Micro Data Bus

NMI

INT

(From ICU)

CLOCK

(From CG)

Sub Data Bus

(16)

ALU

PSW

Main Data Bus

(16)

Data Sheet U13225EJ4V0DS00

23

µ

PD70208H, 70216H

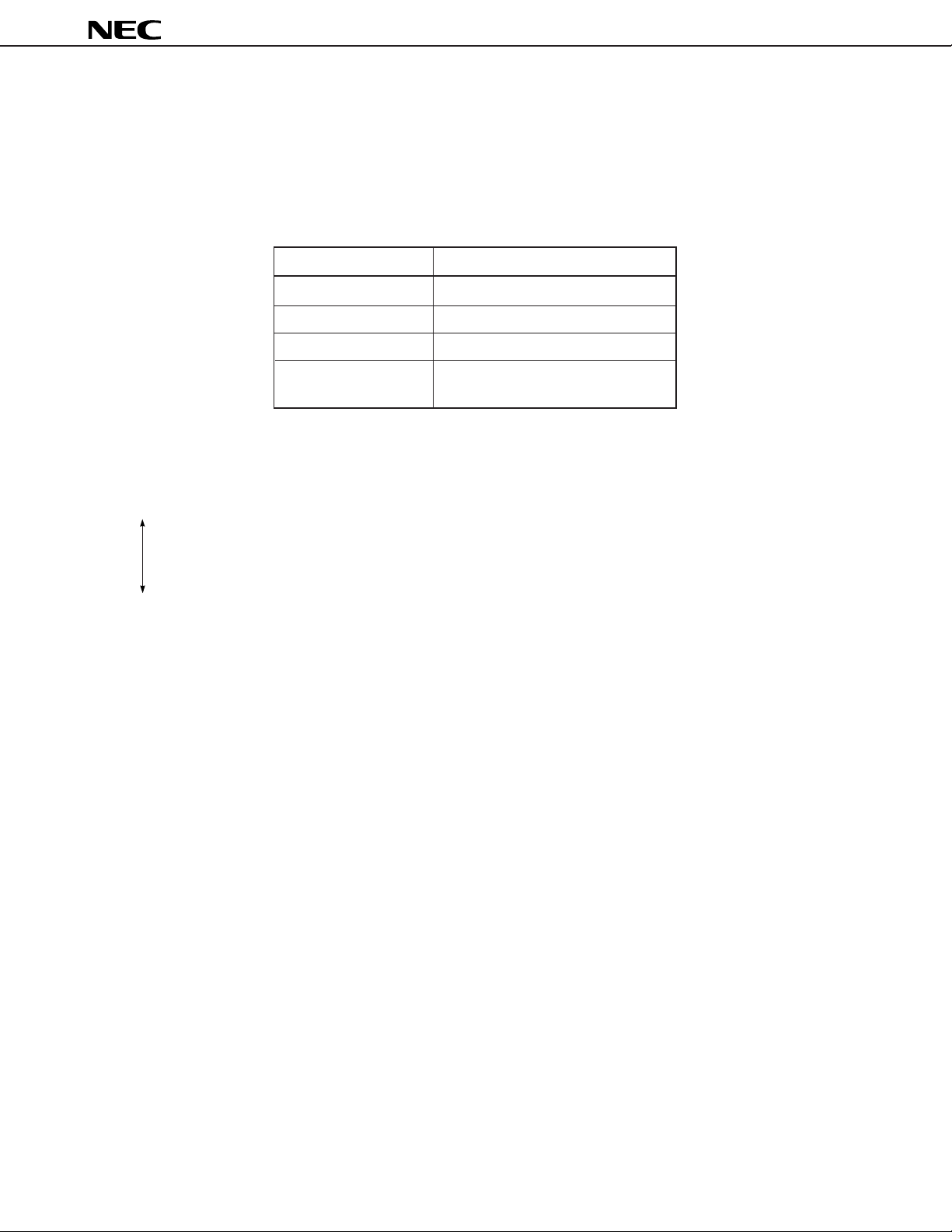

4. CG (CLOCK GENERATOR)

The CG generates a clock at a frequency of 1/2, 1/4, 1/8 or 1/16 that of the crystal and oscillator connected to the X1

and X2 pins, supplies it as the CPU operating clock and outputs it externally as the CLKOUT pin output.

The interrupt cycle time can be changed according to the oscillator scaling factor. The scaling factor can be set by a

system I/O area register.

Figure 4-1. Internal Block Diagram of CG

X1

X2

Oscillator

f

XX

Divide-by-2

Scaler

Divide-by-1-to-8

Scaler

Divide-by-2-to-16

Scaler

f

X

CPU, DMAU, REFU, SCU

CLKOUT

Baud Rate Counter (BRC)

TCU

5. BIU (BUS INTERFACE UNIT)

The BIU controls the data bus, address bus and control bus pins. These buses are used by the CPU, DMAU (DMA control

unit) and REFU (refresh control unit).

The BIU synchronizes the RESET input signal and READY input signal using the CLOCK signal generated by the clock

generator (CG). In addition to being supplied to the inside of the V40HL and V50HL, the synchronized reset signal is also

output externally from the RESOUT pin. The synchronized READY signal is supplied to the internal CPU, DMAU and REFU.

Figure 5-1. RESET and READY Signal Synchronization

24

RESET

READY

CLOCK

CK ↑

QD

Data Sheet U13225EJ4V0DS00

CK ↓

CK ↓

QD

QD

RESOUT

To Internal Units

To Internal Units

6. BAU (BUS ARBITRATION UNIT)

The BAU performs bus arbitration among bus masters.

A list of bus masters (units which can acquire the bus) is shown below.

Table 6-1. Bus Masters

Bus Master Bus Cycle

µ

PD70208H, 70216H

CPU

DMAU

REFU

External bus master

(HLDRQ pin input)

The relative priorities of the bus masters are shown below.

High CPU (when BUSLOCK prefix is used)

REFU (highest priority: when given number of requests are reached)

DMAU

HLDRQ pin

CPU (normal CPU cycle)

Low REFU (lowest priority: cycle steal)

BAU bus arbitration is performed as follows.

A bus master such as the CPU, DMAU, REFU, etc., incorporated in the V40HL and V50HL normally release the bus at

the end of the bus cycle currently being executed, as shown in Figure 6-1. However, in the case of a bus master connected

to the HLDRQ pin, or cascaded external DMA controllers, for instance, the situation is as shown in Figure 6-2. The V40HL

and V50HL request return of the bus by inactivating the acknowledge signal (HLDAK), and on receiving this request, the

external bus master holding the bus should release the bus by dropping the bus hold request signal (HLDRQ). The V40HL

and V50HL-internal bus master with the highest priority is kept waiting until the bus hold request signal is dropped. This

is called a bus wait operation.

Program fetch, data read/write

DMA cycle

Refresh cycle

Bus cycle driven by external device

Data Sheet U13225EJ4V0DS00

25

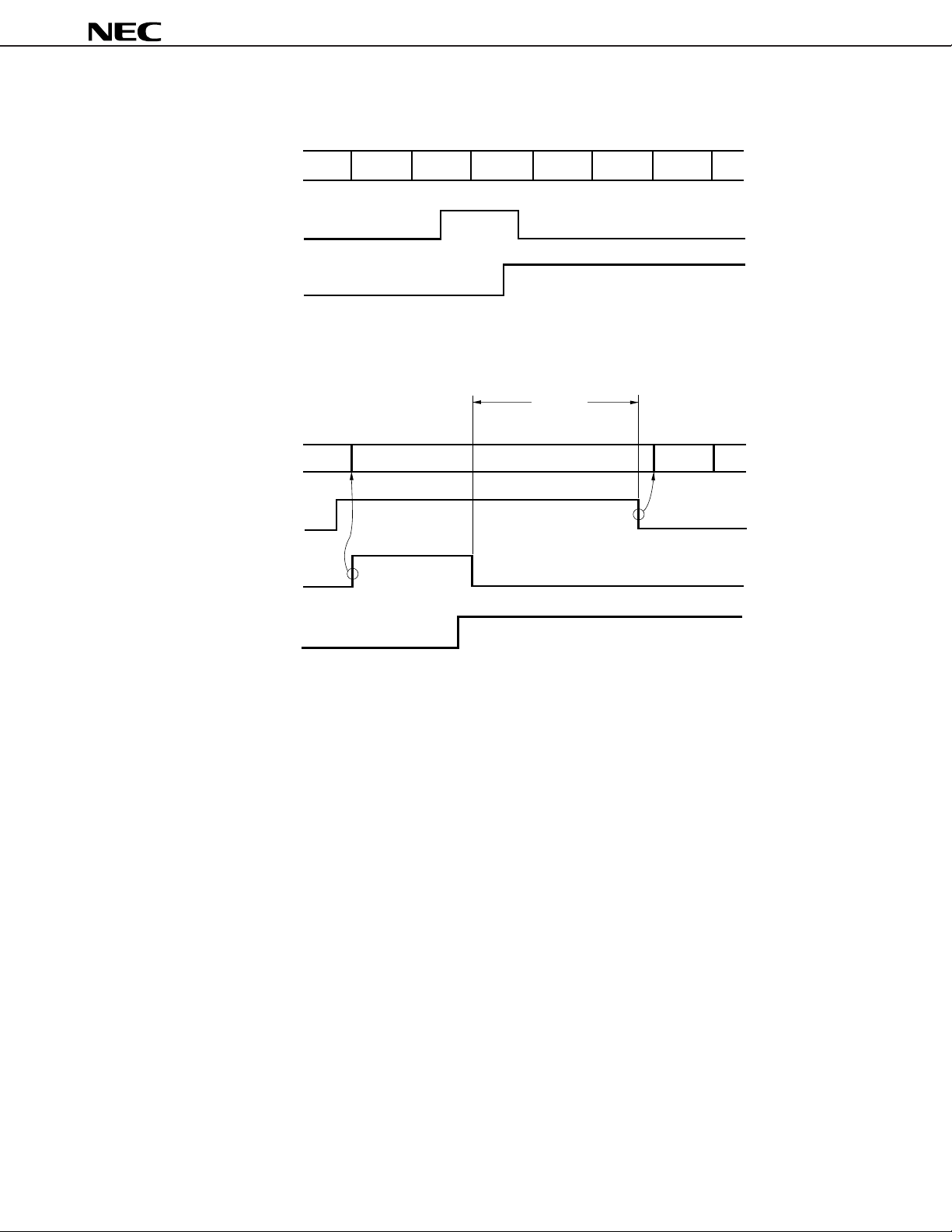

Figure 6-1. Internal Bus Cycles

µ

PD70208H, 70216H

Bus Cycle

Internal DMA Request

Internal Refresh Request

(Highest Priority)

Bus Cycle

HLDRQ Pin

HLDAK Pin

CPU CPU DMA Refresh Refresh Refresh

Figure 6-2. Bus Wait Operation

Bus Wait

Bus Release Refresh

Note

Internal Refresh Request

(Highest Priority)

Note The period in which the external bus master which has been given the bus after its release by the V40HL and

V50HL can use the bus.

26

Data Sheet U13225EJ4V0DS00

µ

PD70208H, 70216H

7. WCU (WAIT CONTROL UNIT)

The WCU has the function of automatically inserting a wait state (TW) of 0 to 3 clock cycles in a CPU, DMAU or REFU

bus cycle.

7.1 FEATURES

Automatic setting of 0 to 3 waits for a CPU memory bus cycle

•

1M-byte memory space can be divided into 5

•

64K-byte I/O space can be divided into 3

•

Automatic setting of 0 to 3 waits for an external I/O cycle

•

Automatic setting of 0 to 3 waits for a DMA cycle

•

Automatic setting of 0 to 3 waits for a refresh cycle

•

Same as V40 and V50 directly after a reset (memory space divided into 3, no division of I/O space)

•

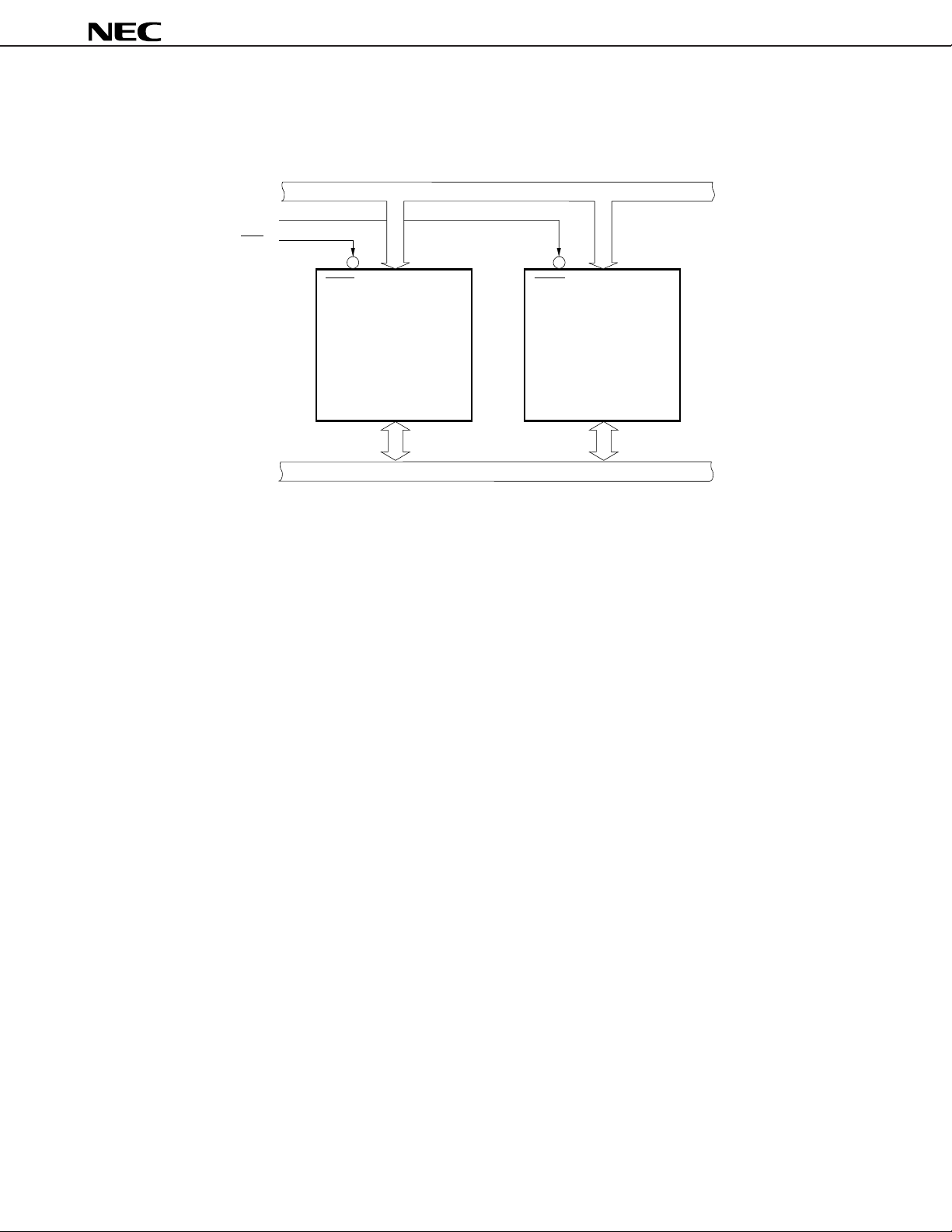

Figure 7-1. Example of Memory Space Division

Upper Sub

FFFFFH

Memory Block

Upper Memory Block

1 M-Byte

Memory Area

00000H

Remark The division specification and the size of each block are set by means of a system I/O area register.

Middle Memory Block

Lower Memory Block

Lower Sub

Memory Block

Data Sheet U13225EJ4V0DS00

27

Figure 7-2. Example of I/O Space Division

FFFFH

Upper I/O Block

µ

PD70208H, 70216H

64K-Byte I/O Area

0000H

Remark The division specification and the size of each block are set by means of a system I/O area register.

7.2 RELATION BETWEEN WCU AND READY PIN

When wait cycles exceeding 3 clock cycles are necessary, the WCU and the READY signal pin can be used in

combination. The number of wait cycles specified by the WCU set value or the number of wait cycles under READY control,

whichever is larger, is inserted.

Figure 7-3. WCU and READY Control

WCU

Middle I/O Block

Lower I/O Block

V40HL/V50HL

28

READY

Bus Control

Data Sheet U13225EJ4V0DS00

µ

PD70208H, 70216H

8. REFU (REFRESH CONTROL UNIT)

The REFU generates refresh cycles required for refreshing of external DRAM. Refresh enabling/disabling and the refresh

interval can be set programmably.

8.1 FEATURES

Lowest-priority refreshing/highest-priority refreshing

•

7-refresh queue

•

16-bit refresh address

•

REFRQ extended timing supported (REFRQ active from T1 state)

•

8.2 REFRESH OPERATIONS

The REFU has two priorities. Normally, it has the lowest priority, and a refresh cycle cannot be started unless the bus

is completely idle. However, if there are 7 or more pending refresh requests, it is given the highest priority, and it requests

the bus master holding the bus to relinquish it. (See 6. BAU.)

The refresh address is output on A0 to A15. Every refresh cycle the refresh address is incremented by 1 (for the V40HL)

or by 2 (for the V50HL), and the next refresh address is generated.

In a refresh cycle, a low-level signal is output on the low address pins (A16 to A19).

This refresh address is not affected by a reset. When the device is powered on, the refresh address is undefined.

Data Sheet U13225EJ4V0DS00

29

µ

PD70208H, 70216H

9. TCU (TIMER/COUNTER UNIT)

The TCU incorporates 3 counters, and can be used as a timer, event counter, rate generator, etc. Functionally it is a

subset of the

9.1 FEATURES

3 × 16-bit counters

•

Six programmable count modes

•

Binary/BCD count

•

Multiple latch command

•

Choice of two input clocks: internal/external

•

9.2 TCU INTERNAL BLOCK DIAGRAM

µ

PD71054.

IORDIOWR

Read/Write Control

Register)

Note 1

TMD

(Mode

Note 2

TCU

Selection

Signal

TCLK

(External)

TCT #0

Status

Register

(8)

Status

Latch

(8) (8) (8)

CLOCK

Prescaler

Down Counter (16)

H(8) L(8)

Count

Register

Internal Data Bus

Notes 1. A0 or A1 (Set by a system I/O area register)

2. A1 or A2 (Set by a system I/O area register)

Control Logic

(16)

H(8) L(8)

TCTL0=High

TOUT0 (To INTL0)

(16)

Count

Latch

TCTL1=High

TOUT1

(External

)

TCTL2

To INTL2/SCU

SWSWSW

TCT #1 TCT #2

(External)

TOUT2

(External)

30

Data Sheet U13225EJ4V0DS00

µ

PD70208H, 70216H

10. SCU (SERIAL CONTROL UNIT)

The SCU performs control of serial communication (asynchronous). Its functions are a subset of the µPD71051 excluding

synchronous communication. Also, what was the control word register in the

command register and a mode register.

10.1 FEATURES

Dedicated baud rate generator incorporated (using internal clock)

•

Asynchronous serial communication

•

Clock rate: baud rate × 16, × 64

•

Baud rate: DC – 500 kbps

•

Character length: 7/8 bits

•

Transmit stop bits: 1/2 bits

•

Break transmission

•

Automatic break detection

•

Full-duplex double-buffer system

•

Parity addition/checking

•

Error detection: parity, overrun, framing

•

Interrupt generation maskable

•

µ

PD71051 has been divided into two: a

10.2 SCU INTERNAL BLOCK DIAGRAM

SST

Status Register

SCM

Command Register

SRB

Receive Data Buffer

STB

Transmit Data Buffer

Internal Data Bus

SMD

Mode Register

From CG

Baud Rate

Generator

RESET CLOCK

Read/Write

Control

SCU Status Control Bus

(8)

(8)

Receiver

(Including Receive Buffer)

Transmitter

(Including Transmit Buffer)

Selector

RTCLK

From TCU

(TOUT1 Output)

IORD

IOWR

Note 1

Note 2

SCU Selection Signal

SRDY (External)

R

X

D (External)

T

X

D (External)

SIMK

Interrupt Mask Register

Notes 1. A0 or A1 (Set by a system I/O area register)

2. A1 or A2 (Set by a system I/O area register)

Data Sheet U13225EJ4V0DS00

Interrupt

Generation Logic

SINT (To INTL1)

31

µ

PD70208H, 70216H

11. ICU (INTERRUPT CONTROL UNIT)

The ICU arbitrates among up to 8 interrupt requests (maskable interrupts) generated inside and outside the V40HL and

V50HL, and transfers one of them to the CPU. The ICU functions comprise the functions of the V40HL and V50HL minus

those functions not required by the V40HL and V50HL.

11.1 FEATURES

8 interrupt inputs

•

µ

PD71059 cascading possible

•

Edge- or level-triggered request input

•

(input from internally connected TCU is edge-triggered only)

Interrupt requests individually maskable

•

Programmable interrupt request priority order

•

Polling operation capability

•

11.2 ICU INTERNAL BLOCK DIAGRAM

Initialize &

Command Word

IORD

IOWR

Note 1

Note 2

ICU Selection Signal

Read/Write

Control

Register Group

Interrupt

In-Service

Register

(IIS)

Internal Data Bus

Notes 1. A0 or A1 (Set by a system I/O area register)

2. A1 or A2 (Set by a system I/O area register)

Control Logic

Priority

Determination Logic

Interrupt

Mask

Register

(IMK)

Slave Control

Interrupt

Request

Register

(IRQ)

INTL0

INTL1

INTL2

INTL3

INTL4

INTL5

INTL6

INTL7

SA0

SA1

To BIU

SA2

INTAK (From CPU)

INT (To CPU)

TOUT0 (From TCU)

SINT (From SCU)

TOUT1 (From TCU)

SW

SW

INTP1

INTP2

INTP3

INTP4

INTP5

INTP6

INTP7

A8

A9

A10

External Pins

32

Data Sheet U13225EJ4V0DS00

µ

PD70208H, 70216H

12. DMAU (DMA CONTROL UNIT)

The DMAU has 4 DMA channels, and provides the functions (subset) of two LSIs, the µPD71071 and µPD71037.

12.1 FEATURES

Two operating modes (µPD71071 mode, µPD71037 mode)

•

20-bit address register

•

16-bit count register

•

Four independent DMA channels

•

Byte transfer/word transfer selectable

•

Three transfer modes (settable on an individual channel basis)

•

Single transfer mode, demand transfer mode, block transfer mode

Two bus modes (common to all channels: in µPD71037 mode, bus release mode only)

•

Bus release mode

Bus hold mode

DMA requests maskable on an individual channel basis

•

Auto initialization function

•

Transfer address increment/decrement

•

Two channel priority systems (fixed priority/rotating priority)

•

TC output at end of transfer

•

Forced termination of service by END input

•

Cascading capability

•

12.2 DMAU INTERNAL BLOCK DIAGRAM

Internal Address Bus

Internal Data Bus

Internal Control Bus

BUSRQ

BAU

BUSAK

DMARQ0DMARQ3

External

pins

DMAAK0DMAAK3

END/TC

(20)

(8)

Internal Bus

Interface

Priority Control

DMAU Address Bus (20)

Address

Registers

DMAU Data Bus

Count

Registers

Terminal Count

Address Increment/

Decrement

(20)

Current Address (20 × 4)

Base Address (20 × 4)

Base Count (16 × 4)

Current Count (16 × 4)

Count Decrementer

(16)

Control Register Group

Channel

Device Control

Status

Mode Control

Mask

Request

Note 1

Note 2

(4)

(10)

(8)

(7 × 4)

(4)

(4)

Notes 1. In µPD71071 mode

µ

2. In

PD71037 mode

Data Sheet U13225EJ4V0DS00

33

µ

PD70208H, 70216H

13. STANDBY FUNCTIONS

The V40HL and V50HL have two modes, the HALT mode and STOP mode, as standby functions.

(1) HALT mode

When the HALT instruction is executed, the clock to internal CPU circuitry (excluding the HALT mode release circuit)

is stopped.

(2) STOP mode

When the HALT instruction is executed, all clocks to the CPU and internal I/Os are stopped.

STOP mode should be used when a resonator is connected to the X1 and X2 pins.

Remark Switching between HALT mode and STOP mode is performed by setting a system I/O area register.

14. RESET OPERATION

When the RESET pin is driven low and this level is held for 4 clock cycles or more from the fall of the signal, the CPU

and on-chip peripheral LSIs are reset.

When the RESET pin subsequently returns to the high level, the CPU begins an instruction prefetch from address

FFFF0H.

When the V40HL and V50HL are reset, its status is fully compatible with the V40 and V50.

Extended functions added to those of the V40 and V50 are mapped onto unused V40 and V50 registers and the reserved

area.

Table 14-1 shows the main statuses of the on-chip peripheral LSIs when a reset is performed.

Table 14-1. Main Statuses of On-Chip Peripheral LSIs After Reset

WCU

REFU

SCU

DMAU

Memory, external I/O, DMA & refresh : 3-wait insertion

Upper & lower memory blocks : set to 512 KB

Refresh cycle : set to 72 clock cycles

Refresh enabling/disabling : not affected by reset

Baud rate : x 64

Character : 7 bits

Parity : None

Stop bits : 1 bit

Break detection : None

µ

PD71071 mode

Demand mode

Auto initialization disabled

Verify transfer, byte transfer

Bus release mode

DMA enabled

Caution When a reset is performed, the SCU, TCU, ICU and DMAU cannot be used.

34

Data Sheet U13225EJ4V0DS00

15. INSTRUCTION SET

Table 15-1. Operand Type Legend

µ

PD70208H, 70216H

Identifier

reg

reg’

reg8

reg8’

reg16

reg16’

dmem

mem

mem8

mem16

mem32

imm

imm3

imm4

imm8

imm16

acc

sreg

src-table

src-block

dst-block

near-proc

far-proc

near-label

short-label

far-label

memptr16

memptr32

regptr16

pop-value

fp-op

R

Description

8/16-bit general register

(destination register in an instruction using two 8/16-bit general registers)

Source register in an instruction using two 8/16-bit general registers

8-bit general register

(destination register in an instruction using two 8-bit general registers)

Source register in an instruction using two 8-bit general registers

16-bit general register

(destination register in an instruction using two 16-bit general registers)

Source register in an instruction using two 16-bit general registers

8/16-bit memory location

8/16-bit memory location

8-bit memory location

16-bit memory location

32-bit memory location

Constant in range 0 to FFFFH

Constant in range 0 to 7

Constant in range 0 to FH

Constant in range 0 to FFH

Constant in range 0 to FFFFH

Accumulator AW or AL

Segment register

Name of 256-byte conversion translation table

Name of block addressed by register IX

Name of block addressed by register IY

Procedure in current program segment

Procedure in a different program segment

Label in current program segment

Label in range –128 to +127 bytes from end of instruction

Label in a different program segment

Word containing location offset in a different program segment to which control is to be shifted and segment

base address

Doubleword containing location offset in a different program segment to which control is to be shifted and

segment base address

General register containing location offset in a different program segment to which control is to be shifted

Number of bytes to be removed from stack (0 to 64K, normally an even number)

Immediate value which identifies external floating-point operation coprocessor operation code

Register set

Data Sheet U13225EJ4V0DS00

35

Table 15-2. Operation Code Legend

µ

PD70208H, 70216H

Identifier

W

reg

reg’

mem

mod

s

X, XXX, YYY, ZZZ

Description

Byte/word specification bit (0: byte, 1: word). However, when s =1, byte data of sign extension is 16-bit

operand if W = 1.

Register field (000 to 111)

Register field (000 to 111) (source register in instruction which uses two registers)

Memory field (000 to 111)

Mode field (00 to 10)

Sign-extended specification bit (0: without sign extension, 1: with sign extension)

Data used to determine external floating-point coprocessor operation code

36

Data Sheet U13225EJ4V0DS00

AW

AH

AL

BW

CW

CL

DW

BP

SP

PC

PSW

IX

IY

PS

SS

DS0

DS1

AC

CY

P

S

Z

DIR

IE

V

BRK

MD

...

(

)

disp

ext-disp8

temp

TA

TB

TC

tmpcy

seg

offset

←

+

–

×

÷

%

∨

∨

∨

××H

××××H

Table 15-3. Operand Description Legend

Accumulator (16-bit)

Accumulator (high-order byte)

Accumulator (low-order byte)

Register BW (16-bit)

Register CW (16-bit)

Register CL (low-order byte)

Register DW (16-bit)

Base pointer (16-bit)

Stack pointer (16-bit)

Program counter (16-bit)

Program status word (16-bit)

Index register (source) (16-bit)

Index register (destination) (16-bit)

Program segment register (16-bit)

Stack segment register (16-bit)

Data segment 0 register (16-bit)

Data segment 1 register (16-bit)

Auxiliary carry flag

Carry flag

Parity flag

Sign flag

Zero flag

Direction flag

Interrupt enable flag

Overflow flag

Break flag

Mode flag

Contents of memory indicated by contents of ( )

Displacement (8/16-bit)

16 bits with 8-bit displacement sign-extended

Temporary register (8/16/32-bit)

Temporary register A (16-bit)

Temporary register B (16-bit)

Temporary register C (16-bit)

Temporary carry flag (1-bit)

Immediate segment data (16-bit)

Immediate offset data (16-bit)

Transfer direction

Addition

Subtraction

Multiplication

Division

Modulo

Logical product

Logical sum

Exclusive logical sum

Two-digit hexadecimal number

Four-digit hexadecimal number

µ

PD70208H, 70216H

DescriptionIdentifier

Data Sheet U13225EJ4V0DS00

37

Table 15-4. Flag Operation Legend

Identifier Description

(Blank) No change

0 Cleared to 0

1 Set to 1

× Set or cleared depending upon result

U Undefined

R Previously saved value is restored

Table 15-5. Memory Addressing

µ

PD70208H, 70216H

mem

000

001

010

011

100

101

110

111

mod

BW + IX

BW + IY

BP + IX

BP + IY

IX

IY

DIRECT ADDRESS

BW

00

BW + IX + disp 8

BW + IY + disp 8

BP + IX + disp 8

BP + IY + disp 8

IX + disp 8

IY + disp 8

BP + disp 8

BW + disp 8

Table 15-6. 8/16-Bit General Register Selection

reg, reg’ W=0 W=1

000 AL AW

001 CL CW

010 DL DW

011 BL BW

100 AH SP

101 CH BP

110 DH IX

111 BH IY

01 10

BW + IX + disp 16

BW + IY + disp 16

BP + IX + disp 16

BP + IY + disp 16

IX + disp 16

IY + disp 16

BP + disp 16

BW + disp 16

Table 15-7. Segment Register Selection

sreg

00 DS1

01 PS

10 SS

11 DS0

38

Data Sheet U13225EJ4V0DS00

µ

PD70208H, 70216H

The instruction set is shown in tabular form on the following pages.

Clock cycle shown in table is the time required for execution of instruction by the execution unit and is based on the

following conditions.

• Prefetch time and wait time for using bus, etc. are not included.

• 0 wait is assumed for memory access. That is, the clock number of one bus cycle is four clock cycle.

• 0 wait is assumed for I/O access.

• Primitive block transfer instruction and primitive input/output instruction is included repeat prefixes.

The number of clock cycle of instruction with byte processing and word processing (with W bit) is shown as the followings.

(1) V40HL

On the left of "/" : The value corresponding to byte processing (W= 0) or word processing (W = 1) of even

address

On the right of "/": The value corresponding to word processing (W =1) of odd address

For the clock of block transfer related instruction of V40HL, see Table 15-8.

Table 15-8. Number of Clock Cycles in Block Transfer Related Instruction (V40HL)

Instruction

Byte Processing (W = 0) Word Processing (W = 1)

MOVBK 9 + 8 × rep 9 + 16 × rep

(9) (17)

CMPBK 7 + 14 × rep 7 + 22 × rep

(13) (21)

CMPM 7 + 10 × rep 7 + 14 × rep

(7) (11)

LDM 7 + 9 × rep 7 + 13 × rep

(7) (11)

STM 5 + 4 × rep 5 + 8 × rep

(5) (9)

INM 9 + 8 × rep 9 + 16 × rep

(10) (18)

OUTM 9 + 8 × rep 9 + 16 × rep

(10) (18)

Number of Clock Cycles

Remark The figures in parentheses apply to one-time processing only.

Data Sheet U13225EJ4V0DS00

39

µ

PD70208H, 70216H

(2) V50HL

On the left of "/" : The value corresponding to byte processing (W= 0) or word processing (W = 1) of even

address

On the right of "/" : The value corresponding to word processing (W =1) of odd address

For the clock of block transfer related instruction of V50HL, see Table 15-9.

Table 15-9. Number of Clock Cycles in Block Transfer Related Instruction V50HL (1/2)

Number of Clock Cycles

Instruction Byte Processing Word Processing (W = 1)

(W = 0) Odd/Odd Address Odd/Even Address Even/Even Address

MOVBK 9 + 8 × rep 9 + 16 × rep 9 + 12 × rep 9 + 8 × rep

(9) (17) (13) (9)

CMPBK 7 + 14 × rep 7 + 22 × rep 7 + 18 × rep 7 + 14 × rep

(13) (21) (17) (13)

INM 9 + 8 × rep 9 + 16 × rep 9 + 12 × rep 9 + 8 × rep

(10) (18) (14) (10)

OUTM 9 + 8 × rep 9 + 16 × rep 9 + 12 × rep 9 + 8 × rep

(10) (18) (14) (10)

Remark The figures in parentheses apply to one-time processing only.

Table 15-9. Number of Clock Cycles in Block Transfer Related Instruction (V50HL) (2/2)

Number of Clock Cycles

Instruction Byte Processing Word Processing (W = 1)

(W = 0) Odd Address Even Address

CMPM 7 + 10 × rep 7 + 14 × rep 7 + 10 × rep

(7) (11) (7)

LDM 7 + 9 × rep 7 + 13 × rep 7 + 9 × rep

(7) (11) (7)

STM 5 + 4 × rep 5 + 8 × rep 5 + 4 × rep

(5) (9) (5)

Remark The figures in parentheses apply to one-time processing only.

40

Data Sheet U13225EJ4V0DS00

Instruction

Group

Data Sheet U13225EJ4V0DS00

Mnemonic Operand(s) Operation

MOV

Data transfer instructions

LDEA

TRANS

XCH

reg, reg’

mem, reg

reg, mem

mem, imm

reg, imm

acc, dmem

dmem, acc

sreg, reg16

sreg, mem16

reg16, sreg

mem16, sreg

DS0, reg16,

mem32

DS1, reg16,

mem32

AH, PSW

PSW, AH

reg16, mem16

src-table

reg, reg’

mem, reg

reg, mem

AW, reg16

reg16, AW

Operation Code Flags

76543210 76543210

1000101W

1000100W

1000101W

1100011W

1011W reg

1010000W

1010001W

10001110

10001110

10001100

10001100

11000101

11000100

10011111

10011110

10001101

11010111

1000011W

1000011W

10010 reg

11 reg reg’

mod reg mem

mod reg mem

mod

000mem

110 sreg reg

mod 0 sreg mem

110 sreg reg

mod

0 sreg mem

mod reg mem

mod reg mem

mod reg mem

1 1 reg reg’

mod reg mem

Bytes

2

2-4

2-4

3-6

2-3

3

3

2

2-4

2

2-4

2-4

2-4

1

1

2-4

1

2

2-4

1

Clock Cycles

V40HL V50HL

2

2

7/11

10/14

9/13

10/14

9/13

13/21

14

12

25

25

7/11

10/14

9/13

4

4

10/14

9/13

2

2

10/14

2

2

8/12

17/25

17/25

2

2

3

3

4

4

9

9

3

3

13/21

3

3

reg ← reg’

(mem) ← reg

reg ← (mem)

(mem) ← imm

reg ← imm

If W=0: AL ← (dmem)

If W=1: AH ← (dmem + 1), AL ← (dmem)

If W=0: (dmem) ←AL

If W=1: (dmem + 1) ← AH, (dmem) ←AL

sreg ← reg16 sreg:SS, DS0, DS1

sreg ← (mem16) sreg:SS, DS0, DS1

reg16 ← sreg

(mem16) ← sreg

reg16← (mem32)

DS0 ← (mem32 + 2)

reg16 ← (mem32)

DS1 ← (mem32 + 2)

AH ← S, Z, ×, AC, ×, P, ×, CY

S, Z, ×, AC, ×, P, ×, CY← AH

reg16 ←mem16

AL← (BW + AL)

reg ↔ reg’

(mem) ↔ reg

AW ↔ reg16

AC CY V P S Z

×× ×××

µ

PD70208H, 70216H

41

42

Instruction

Group

Data Sheet U13225EJ4V0DS00

Mnemonic Operand(s)

REPC

REPNC

REP

REPE

Repeat prefixes

REPZ

REPNE

REPNZ

MOVBK

CMPBK

CMPM

LDM

Primitive block transfer instructions

STM

dst-block,

src-block

src-block,

dst-block

dst-block

src-block

dst-block

Operation Code Flags

76543210

01100101

01100100

11110011

11110010

1010010W

1010011W

1010111W

1010110W

1010101W

76543210

Bytes

1

1

1

1

1

1

1

1

1

Clock Cycles

V40HL V50HL

2

2

2

2

See

Table

15-8

See

Table

15-8

See

Table

15-8

See

Table

15-8

See

Table

15-8

2

2

2

2

See

Table

15-9

See

Table

15-9

See

Table

15-9

See

Table

15-9

See

Table

15-9

Operation

While CW ≠ 0, the following byte primitive block transfer

instruction is executed and CW is decremented (–1).

If there is a pending interrupt, it is serviced.

If CY ≠ 1 the loop is exited.

Same as above

If CY ≠ 0 the loop is exited.

While CW ≠ 0, the following byte primitive block transfer

instruction is executed and CW is decremented (–1).

If there is a pending interrupt, it is serviced.

If the primitive block transfer instruction is CMPBK or

CMPM and Z ≠ 1 the loop is exited.

Same as above

If Z ≠ 0 the loop is exited.

If W = 0: (IY) ← (IX)

DIR = 0 : IX ← IX + 1, IY ← IY + 1

DIR = 1 : IX ← IX – 1, IY ← IY – 1

If W = 1: (IY + 1, IY) ← (IX + 1, IX)

DIR = 0 : IX ← IX + 2, IY ← IY + 2

DIR = 1 : IX ← IX – 2, IY ← IY – 2

If W = 0: (IX) – (IY)

DIR = 0 : IX ← IX + 1, IY ← IY + 1

DIR = 1 : IX ← IX – 1, IY ← IY – 1

If W = 1: (IX + 1, IX) – (IY + 1, IY)

DIR = 0 : IX ← IX + 2, IY ← IY + 2

DIR = 1 : IX ← IX – 2, IY ← IY – 2

If W = 0: AL – (IY)

DIR = 0 : IY ← IY + 1; DIR = 1 : IY ← IY – 1

If W = 1: AW – (IY + 1, IY)

DIR = 0 : IY ← IY + 2; DIR = 1 : IY ← IY – 2

If W = 0: AL ← (IX)

DIR = 0 : IX ← IX + 1; DIR = 1 : IX ← IX – 1

If W = 1: AW ← (IX + 1, IX)

DIR = 0 : IX + 2; DIR = 1 : IX ← IX – 2

If W = 0: (IY) ← AL

DIR = 0 : IY ← IY + 1; DIR = 1 : IY ← IY – 1

If W = 1: (IY + 1, IY) ← AW

DIR = 0 : IY ← IY + 2; DIR = 1 : IY ← IY – 2

AC CY V P S Z

ЧЧЧЧЧЧ

ЧЧЧЧЧЧ

µ

PD70208H, 70216H

Instruction

Group

Data Sheet U13225EJ4V0DS00

Mnemonic Operand(s)

INS

EXT

Bit field manipulation

instructions

IN

OUT

Input/output instructions

INM

OUTM

Primitive input/output

instructions

reg8, reg8’

reg8, imm4

reg8, reg8’

reg8, imm4

acc, imm8

acc, DW

imm8, acc

DW, acc

dst-block,

DW

DW,

src-block

Operation Code Flags

76543210

00001111

1 1 reg’ reg

00001111

11000 reg

00001111

1 1 reg’ reg

00001111

11000 reg

1110010W

1110110W

1110011W

1110111W

0110110W

0110111W

76543210

00110001

00111001

00110011

00111011

Bytes

3

4

3

4

2

1

2

1

1

1

Clock Cycles

V40HL V50HL

35-133

31-117/

35-133

35-133

31-117/

35-133

34-59

26-55/

34-59

34-59

26-55/

34-59

9/13

8/12

8/12

8/12

See

Table

15-9

See

Table

15-9

Note

Note

Note

Note

9/13

8/12

8/12

8/12

See

Table

15-8

See

Table

15-8

Operation

16-bit field ← AW

16-bit field ← AW

AW ← 16-bit field

AW ← 16-bit field

If W = 0: AL ← (imm8)

If W = 1: AH ← (imm8 + 1), AL ← (imm8)

If W = 0: AL ← (DW)

If W = 1: AH ← (DW + 1), AL ← (DW)

If W = 0: (imm8) ← AL

If W = 1: (imm8 + 1) ← AH, (imm8) ← AL

If W = 0: (DW) ← AL

If W = 1: (DW + 1) ← AH, (DW) ← AL

If W = 0: (IY) ← (DW)

DIR = 0 : IY ← IY + 1 ; DIR = 1 : IY ← IY – 1

If W = 1: (IY + 1, IY) ← (DW + 1, DW)

DIR = 0 : IY ← IY + 2 ; DIR = 1 : IY ← IY – 2

If W = 0: (DW) ← (IX )

DIR = 0 : IX ← IX + 1 ; DIR = 1 : IX ← IX – 1

If W = 1: (DW + 1, DW) ← (IX + 1, IX)

DIR = 0 : IX ← IX + 2 ; DIR = 1 : IX ← IX – 2

AC CY V P S Z

µ

PD70208H, 70216H

43

Note In case of IN/OUT instruction to internal DMAU, the number of word processing clock cycles applied is always that to the right of "/".

44

Instruction

Group

Data Sheet U13225EJ4V0DS00

Mnemonic Operand(s) Operation

ADD

ADDC

SUB

Addition/subtraction instructions

SUBC

reg, reg’

mem, reg

reg, mem

reg, imm

mem, imm

acc, imm

reg, reg’

mem, reg

reg, mem

reg, imm

mem, imm

acc, imm

reg, reg’

mem, reg

reg, mem

reg, imm

mem, imm

acc, imm

reg, reg’

mem, reg

reg, mem

reg, imm

mem, imm

acc, imm

Operation Code Flags

76543210 76543210

0000001W

0000000W

0000001W

100000sW

100000sW

0000010W

0001001W

0001000W

0001001W

100000s W

100000sW

0001010W

0010101W

0010100W

0010101W

100000sW

100000sW

0010110W

0001101W

0001100W

0001101W

100000sW

100000sW

0001110W

1 1 reg reg’

mod reg mem

mod reg mem

11000 reg

mod

000 mem

1 1 reg reg’

mod reg mem

mod reg mem

11010 reg

mod

010

mem

1 1 reg reg’

mod reg mem

mod reg mem

11101 reg

mod

101

mem

1 1 reg reg’

mod reg mem

mod reg mem

11011 reg

mod

011 mem

Bytes

2

2-4

2-4

3-4

3-6

2-3

2

2-4

2-4

3-4

3-6

2-3

2

2-4

2-4

3-4

3-6

2-3

2

2-4

2-4

3-4

3-6

2-3

Clock Cycles

V40HL V50HL

2

13/21

10/14

4

15/23

4

2

13/21

10/14

4

15/23

4

2

13/21

10/14

4

15/23

4

2

13/21

10/14

4

15/23

4

2

13/21

10/14

4

15/23

4

2

13/21

10/14

4

15/23

4

2

13/21

10/14

4

15/23

4

2

13/21

10/14

4

15/23

4

reg ← reg + reg’

(mem) ← (mem) + reg

reg ← reg + (mem)

reg ← reg + imm

(mem) ← (mem) + imm

If W = 0: AL ← AL + imm

If W = 1: AW ← AW + imm

reg ← reg + reg’+ CY

(mem) ← (mem) + reg + CY

reg ← reg + (mem) + CY

reg ← reg + imm + CY

(mem) ← (mem) + imm + CY

If W = 0: AL ← AL + imm + CY

If W = 1: AW ← AW + imm + CY

reg ← reg – reg’

(mem) ← (mem) – reg

reg ← reg – (mem)

reg ← reg – imm

(mem) ← (mem) – imm

If W = 0: AL ← AL – imm

If W = 1: AW ← AW – imm

reg ← reg – reg’– CY

(mem) ← (mem) – reg – CY

reg ← reg – (mem) – CY

reg ← reg – imm – CY

(mem) ← (mem) – imm – CY

If W = 0: AL ← AL – imm – CY

If W = 1: AW ← AW imm– CY

AC CY V P S Z

ЧЧЧЧЧЧ

ЧЧЧЧЧЧ

ЧЧЧЧЧЧ

ЧЧЧЧЧЧ

ЧЧЧЧЧЧ

ЧЧЧЧЧЧ

ЧЧЧЧЧЧ

ЧЧЧЧЧЧ

ЧЧЧЧЧЧ

ЧЧЧЧЧЧ

ЧЧЧЧЧЧ

ЧЧЧЧЧЧ

ЧЧЧЧЧЧ

ЧЧЧЧЧЧ

ЧЧЧЧЧЧ

ЧЧЧЧЧЧ

ЧЧЧЧЧЧ

ЧЧЧЧЧЧ

ЧЧЧЧЧЧ

ЧЧЧЧЧЧ

ЧЧЧЧЧЧ

ЧЧЧЧЧЧ

ЧЧЧЧЧЧ

ЧЧЧЧЧЧ

µ

PD70208H, 70216H

Instruction

Group

Data Sheet U13225EJ4V0DS00

Mnemonic Operand(s)

ADD4S

SUB4S

CMP4S

ROL4

BCD operation instructions

ROR4

INC

DEC

Increment/decre-

ment instructions

reg8

mem8

reg8

mem8

reg8

mem

reg16

reg8

mem

reg16

Operation Code Flags

76543210

00001111

00001111

00001111

00001111

11000 reg

00001111

mod

000 mem

00001111

11000 reg

00001111

mod

000 mem

11111110

1111111W

01000 reg

11111110

1111111W

01001 reg

76543210

00100000

00100010

00100110

00101000

00101000

00101010

00101010

11000 reg

mod

000 mem

11001 reg

mod

001 mem

Bytes

2

2

2

3

3-5

3

3-5

2

2-4

1

2

2-4

1

Clock Cycles

V40HL

19 × n

19 × n

19 × n

+ 7

+ 7

+ 7

13

25

17

29

2

13/21

2

2

13/21

2

V50HL

19 × n

+ 7

19 × n

+ 7

19 × n

+ 7

13

25

17

29

2

13/21

2

2

13/21

2

dst BCD string ← dst BCD string + src BCD string*

dst BCD string ← dst BCD string – src BCD string*

dst BCD string – src BCD string*

ALL

ALL Lower

ALL Lower

ALL

reg8 ← reg8 + 1

(mem) ← (mem) + 1

reg16 ← reg16 + 1

reg8 ← reg8 – 1

(mem) ← (mem) – 1

reg16 ← reg16 – 1

reg

Upper

mem

Upper

Upper

Upper

Operation

Lower

reg

mem

Lower

n: 1/2 the number of BCD digits

* The number of BCD digits is given by the CL register: a value between 1 and 254 can be set.

AC CY V P S Z

U × UUU×

U×UUU×

U×UUU×

×××××

×××××

×××××

×××××

×××××

×××××

µ

PD70208H, 70216H

45

46

Instruction

Group

Data Sheet U13225EJ4V0DS00

Mnemonic Operand(s) Operation

MULU

MUL

Multiplication instructions

reg8

mem8

reg16

mem16

reg8

mem8

reg16

mem16

reg16,

(reg16’,)

imm8

reg16,

mem16,

imm8

reg16,

(reg16’,)

imm16

reg16,

mem16,

imm16

Operation Code Flags

76543210 76543210

11110110

11110110

11110111

11110111

11110110

11110110

11110111

11110111

01101011

Note

01101011

01101001

Note

01101001

1110 0 reg

mod

100 mem

1110 0 reg

mod

100 mem

1110 1 reg

mod

10 1 mem

1110 1 reg

mod

10 1 mem

1 1 reg reg’

mod reg mem

1 1 reg reg’

mod reg mem

Bytes

2

2-4

2

2-4

2

2-4

2

2-4

3

3-5

4

4-6

Clock Cycles

V40HL V50HL

21-22

21-22

26-27

26-27

29-30

29-30

38-39

34-35/

38-39

33-39

33-39

38-44

38-44

41-47

41-47

50-56

46-52/

50-56

28-34

28-34

37-43

33-39/

37-43

36-42

36-42

45-51

41-47/

45-51

AW ← AL × reg8

AH = 0: CY ← 0, V ← 0

AH ≠ 0: CY ← 1, V ← 1

AW ← AL × (mem8)

AH = 0: CY ← 0, V ← 0

AH ≠ 0: CY ← 1, V ← 1

DW, AW ← AW × reg16

DW = 0: CY ← 0, V ← 0

DW ≠ 0: CY ← 1, V ← 1

DW, AW ← AW × (mem16)

DW = 0: CY ← 0, V ← 0

DW ≠ 0: CY ←1, V ← 1

AW ←AL × reg8

AH = AL sign extension: CY ← 0, V ← 0

AH ≠ AL sign extension: CY ← 1, V ← 1

AW ← AL × (mem8)

AH = AL sign extension: CY ← 0, V ← 0

AH ≠ AL sign extension: CY ← 1, V ← 1

DW, AW ← AW × reg16

DW = AW sign extension: CY ← 0, V ← 0

DW ≠ AW sign extension: CY ← 1, V ← 1

DW, AW ← AW × (mem16)

DW = AW sign extension: CY ← 0, V ← 0

DW ≠ AW sign extension: CY ← 1, V ← 1

reg16 ← reg16’ × imm8

Product ≤ 16 bits : CY ← 0, V ← 0

Product > 16 bits : CY ← 1, V ← 1

reg16 ← (mem16) × imm8

Product ≤ 16 bits : CY ← 0, V ← 0

Product > 16 bits : CY ← 1, V ← 1

reg16 ← reg16’ × imm16

Product ≤ 16 bits : CY ← 0, V ← 0

Product > 16 bits : CY ← 1, V ← 1

reg16 ← (mem16) × imm16

Product ≤ 16 bits : CY ← 0, V ← 0

Product > 16 bits : CY ← 1, V ← 1

AC CY V P S Z

U ××UUU

U××UUU

U××UUU

U××UUU

U××UUU

U××UUU

U××UUU

U××UUU

U××UUU

µ

PD70208H, 70216H

U××UUU

U××UUU

U××UUU

Note The 2nd operand can be omitted, in which case the same register as the 1st operand is taken as being specified.

Instruction

Group

Data Sheet U13225EJ4V0DS00

Mnemonic Operand(s)

DIVU

Unsigned division instructions

reg8

mem8

reg16

mem16

Operation Code Flags

76543210 76543210

11110110

11110110

11110111

11110111

11110 reg

mod

110 mem

11110 reg

mod

110 mem

Bytes

2

2-4

2

2-4

Clock Cycles

V40HL V50HL

19

24

25

34

19

24

25

30/34

Operation

temp ← AW

If temp ÷ reg8 ≤ FFH

AH ← temp%reg8, AL ←temp ÷ reg8

If temp ÷ reg8 > FFH

TA ← (001H, 000H), TC ← (003H, 002H)

SP ← SP – 2, (SP + 1, SP) ← PSW, IE ← 0, BRK ← 0

SP ← SP – 2, (SP + 1, SP) ← PS, PS ← TC

SP ← SP – 2, (SP + 1, SP) ← PC, PC ← TA

temp ← AW

If temp ÷ (mem8) ≤ FFH

AH ← temp%(mem8), AL ←temp ÷ (mem8)

If temp ÷ (mem8) > FFH

TA ← (001H, 000H), TC ← (003H, 002H)

SP ← SP – 2, (SP + 1, SP) ← PSW, IE ← 0, BRK ← 0