NEC UPD16856GS Datasheet

DATA SHEET

MOS INTEGRATED CIRCUIT

µµµµ

PD16856

MONOLITHIC CD-ROM 3-PHASE SPINDLE MOTOR DRIVER

The µPD16856 is a CD-ROM 3-phase spindle motor driver consisting of a CMOS controller and MOS bridge

outputs.

By employing 3-phase full-wave PWM as the drive method and MOS FETs at the output stage, it has been

possible to reduce the power consumption of the µPD16856 ever further than the conventional linear drive drivers

that use bipolar transistors.

By using a 30-pin shrink SOP package, a more compact-size has been achieved.

FEATURES

• Supply voltage for controller block: 5 V, supply voltage for output block: 12 V

3 V input available for the input interface

• Low on-state resistance (total on-state resistance of upper and lower MOS FETs) RON = 1.3 Ω (TYP.)

• Low power consumption due to 3-phase full-wave PWM drive method

• On-chip hole bias switch (linked with STB pin)

• On-chip IND (FG) pulse switching function, 1-phase output or 3-phase composite output

• START/STOP pin included, acting as a brake during STOP

• Standby pins included, turning off internal circuit in standby

• Low current consumption: IDD = 3 mA (Max.), IDD

• On-chip thermal shutdown circuit

• On-chip current limiting circuit; reference voltage can be set externally

• On-chip low voltage malfunction prevention circuit

• On-chip reverse rotation prevention circuit

• 30-pin plastic shrink SOP (300 mil)

ORDERING INFORMATION

Part Number Package

µ

PD16856GS 30-pin shrink SOP (0.8-mm pi t ch, 300 mil)

(ST)

= 1 µA (Max.)

Document No. S13447EJ1V0DS00 (1st edition)

Date Published April 1999 N CP(K)

Printed in Japan

The information in this document is subject to change without notice.

©

1999

µµµµ

PD16856

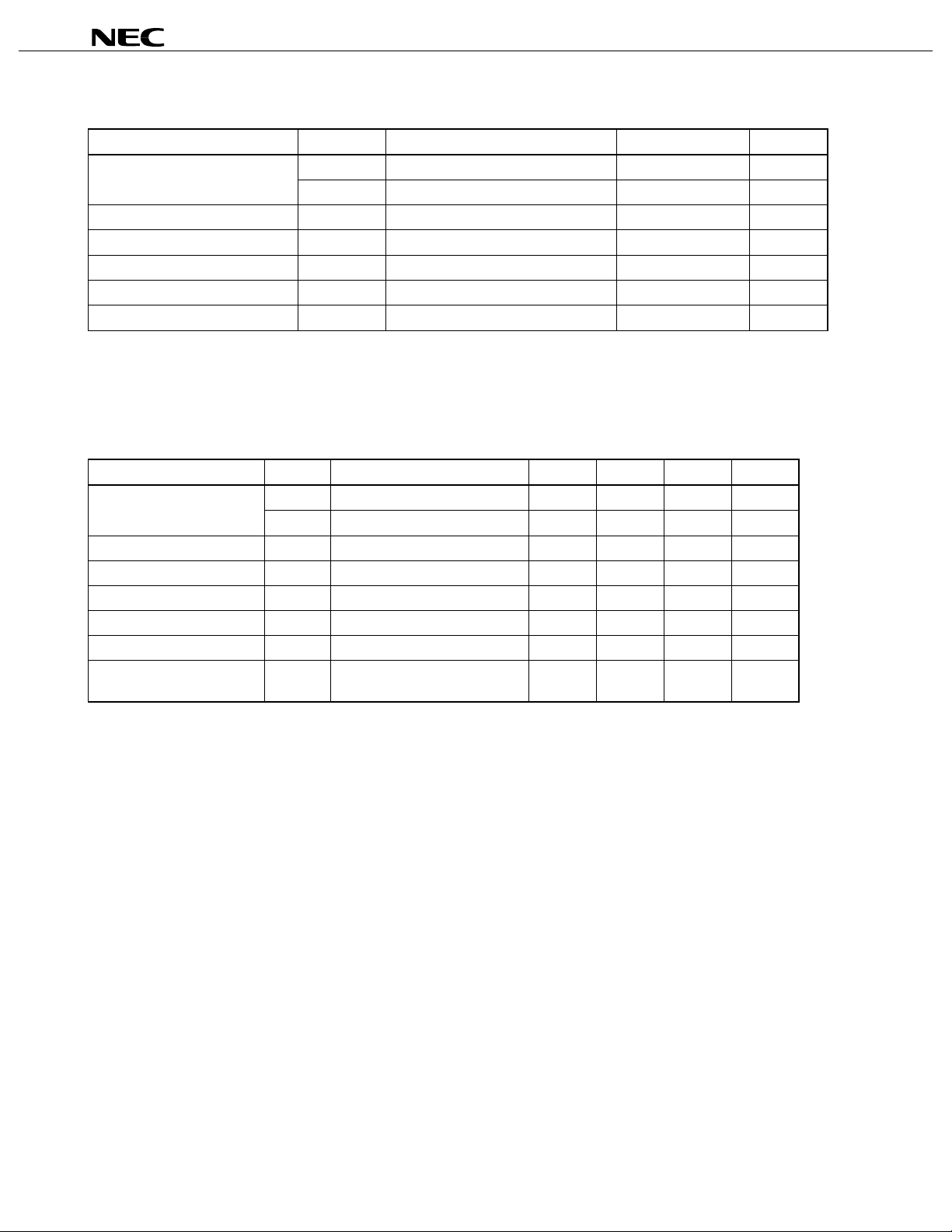

ABSOLUTE MAXIMUM RATINGS (TA = 25

Parameter Symbol Conditions Ratings Unit

DD

Supply voltage

Input voltage V

Instantaneous output c urrent

Power consumption

Note 2

Note 1

Peak channel temperature T

Storage temperature range T

Notes 1.

Allowable current per phase while on-board

When mounted on glass epoxy board (100 mm × 100 mm × 1 mm)

2.

V

M

V

IN

DR (pulse)

I

T

P

CH (MAX)

stg

RECOMMENDED OPERATING RANGE

Parameter Symbol Conditions MIN. TYP. MAX. Unit

DD

V

M

V

Output current (DC) I

Instantaneous output c urrent IDR

Hole bias current I

IND pin output current I

CL pin input voltage V

Operating temperature

range

DR (DC)

HB

FG

CL

A

T

(pulse)

PW ≤ 5 ms, Duty ≤ 10%

C)

°°°°

PW ≤ 5 ms, Duty ≤ 30%

0.5 to +6.0 V

−

0.5 to +13.5 V

−

DD

0.5 to V

−

+ 0.5 V

2.0 A/phase

±

1.0 W

150

55 to +150

−

4.5 5.0 5.5 VSupply voltage

10.8 12.0 13.2 V

0.5 A/Phase

±

1.5 A/Phase

±

10 15 mA

0

2.5

±

5mA

±

0.1 0.4 V

20 75

−

C

°

C

°

C

°

2

Data Sheet S13447EJ1V0DS00

µµµµ

PD16856

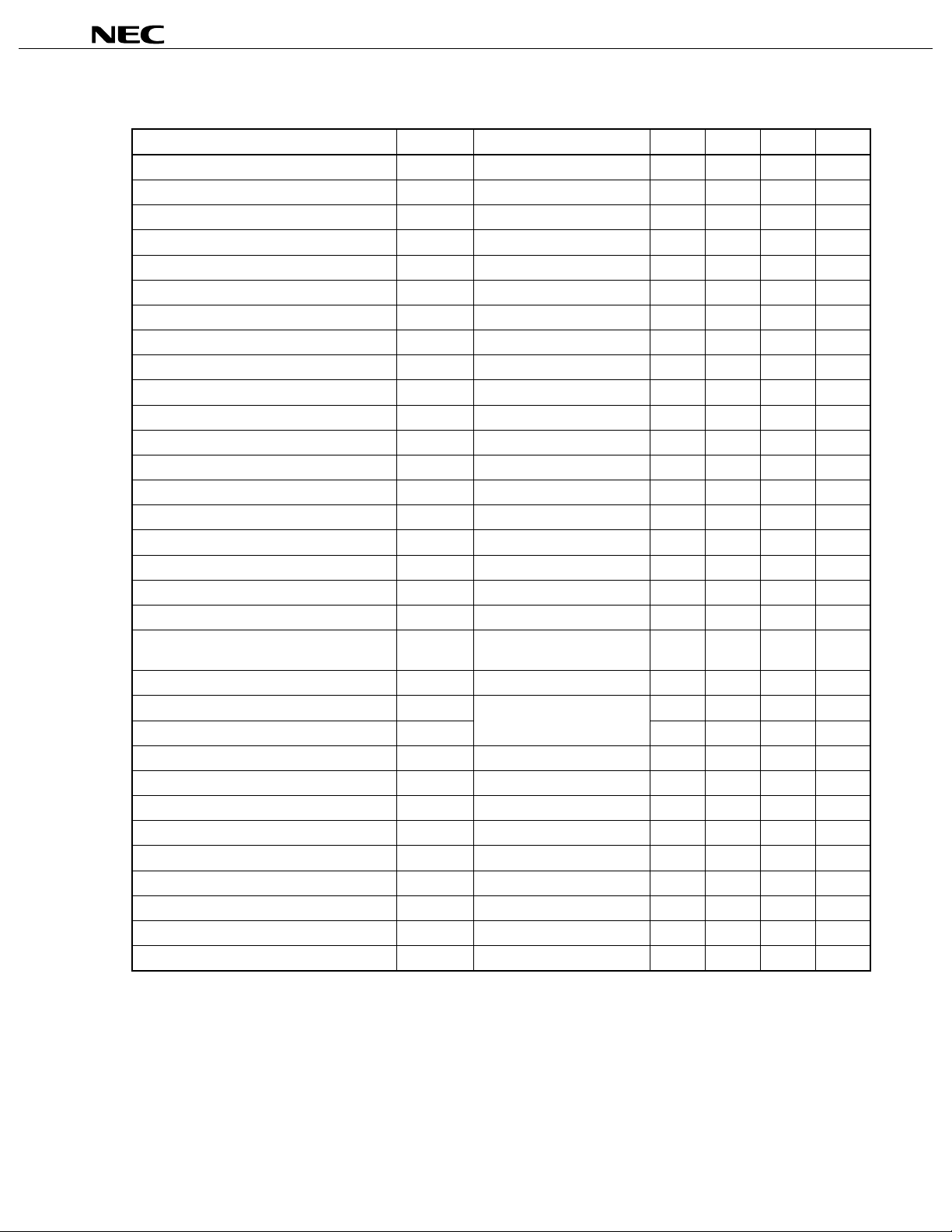

ELECTRICAL SPECIFICATIONS (UNLESS OTHERWISE SPECIFIED, TA = 25

C, VDD = 5 V, VM = 12 V)

°°°°

Parameter Symbol Conditions MIN. TYP. MAX. Unit

[General]

Current consumption 1 (during operation) I

DD

Current consumption (in standby) IDD

(ST)

STB = V

STB = GND 1.0

DD

1.5 3.0 mA

[ST/SP, STB, REV, FGsel]

Input voltage, high V

Input voltage, low V

Input pull-down resistor R

IH

IL

IND

1.8 V

120 k

DD

0.8 V

[Controller block]

Triangle wave oscillation frequency f

PWM

CT = 100 pF 75 kHz

[Hole amplifier]

Common mode input voltage range V

Hysteresis volt age V

Input bias current I

Hch

Hhys

Hbias

1.0 3.5 V

VH = 2.5 V 15 mV

1.0

[Hole bias block]

Hole bias voltage V

HB

IHB = 10 mA 0.3 0.5 V

[FG output]

IND-pin voltage, high V

IND-pin voltage, low V

FG_H

FG_L

IFG = −2.5 mA 4.0 V

IFG = +2.5 mA 0.5 V

[Output block]

Output on-state resistance (upper stage +

lower stage)

Leakage current during OFF IDR

Output turn-on time t

Output turn-off time t

R

ONH

OFFH

ON

(OFF)

IDR = 200 mA

A

T

= −20°C to +75°C

1.3 1.8

In standby 10

RM = 5

Ω

Star connection

1.0 2.0

1.0 2.0

[Torque command]

Control reference input voltage range ECR 0.3 4.0 V

Control input voltage range EC 0.3 4.0 V

Input current I

Input voltage differenc e ECR-EC

IN

Note

DUTY = 100% 1.0 V

30 50

Dead zone (+) EC_d+ 1.5 V ≤ ECR ≤ 2.5 V 0 50 100 mV

Dead zone (−)EC_d

1.5 V ≤ ECR ≤ 2.5 V 0

−

50

−

100 mV

−

[Overcurrent detection bl ock]

Input offset volt age V

IO

15 +15 mV

−

A

µ

V

Ω

A

µ

Ω

A

µ

s

µ

s

µ

A

µ

Dead zone not included.

Note

Remarks 1.

The thermal shutdown circuit (T.S.D.) operates with T

The low-voltage malfunction prevention circuit (UVLO) operates with a voltage of 4 V

2.

CH

> 150°C.

Data Sheet S13447EJ1V0DS00

TYP

.

3

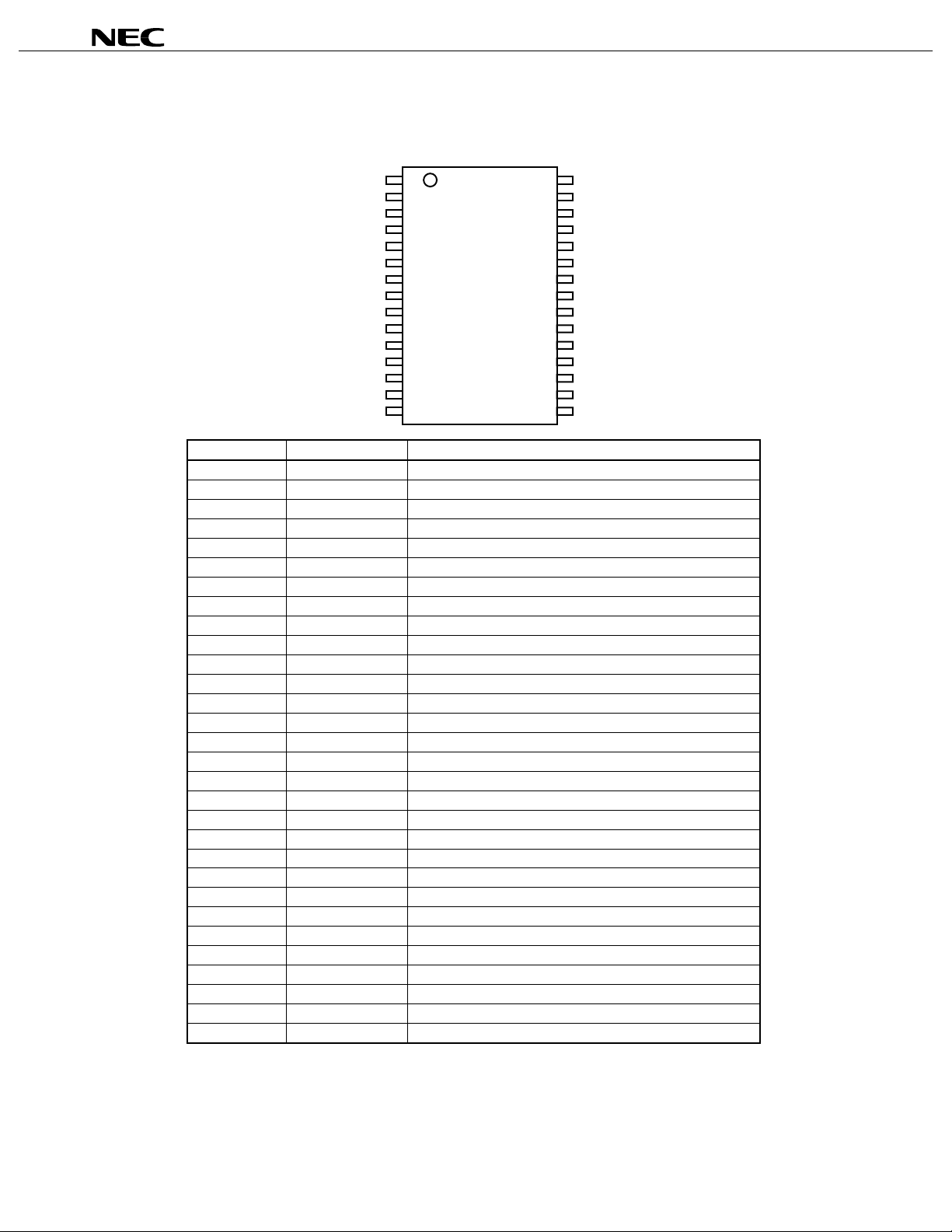

PIN FUNCTIONS

Package: 30-pin Shrink SOP (300 mil)

µµµµ

PD16856

IND

STB

V

V

OUT2

RF

RF

OUT1

V

V

OUT0

RF

RF

SEN

I

CL

1

2

3

M

4

M

5

6

7

8

9

M

10

M

11

12

13

14

15

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

EC

ECR

DD

V

CT

H2+

H2–

H1+

H1–

H0+

H0–

HB

FGsel

ST/SP

REV

GND

Pin No. Pin Name Pin Function

1 IND Index signal out put pin

2 STB Standby operation input pin

3V

4V

M

M

Supply input pin for motor block (12 V)

Supply input pin for motor block (12 V)

5 OUT2 Motor connection pin

6 RF 3-phase bridge common pin

7 RF 3-phase bridge common pin

8 OUT1 Motor connection pin

9V

10 V

M

M

Supply input pin for motor block (12 V)

Supply input pin for motor block (12 V)

11 OUT0 Motor connection pin

12 RF 3-phase bridge common pin

13 RF 3-phase bridge common pin

14 I

SEN

Sense resistor connection pin

15 CL Overcurrent detection voltage input pin

16 GND GND pin

17 REV Reverse rotation input pin (reverse brake pin)

18 ST/SP Start/stop input pin

19 FGsel IND pulse selection pin

20 HB Hole bias pin

21 H0

−

Hole signal input pin

22 H0+ Hole signal input pin

23 H1

−

Hole signal input pin

24 H1+ Hole signal input pin

25 H2

−

Hole signal input pin

26 H2+ Hole signal input pin

27 CT Oscillation frequency setup c apacitor connection pin

28 V

DD

Controller block supply i nput pi n (5 V)

29 ECR Control reference voltage input pi n

30 EC Control voltage input pin

Caution When there is more than one pin of the same kind of pin (VM and RF), all pins should be connected

to their targets.

4

Data Sheet S13447EJ1V0DS00

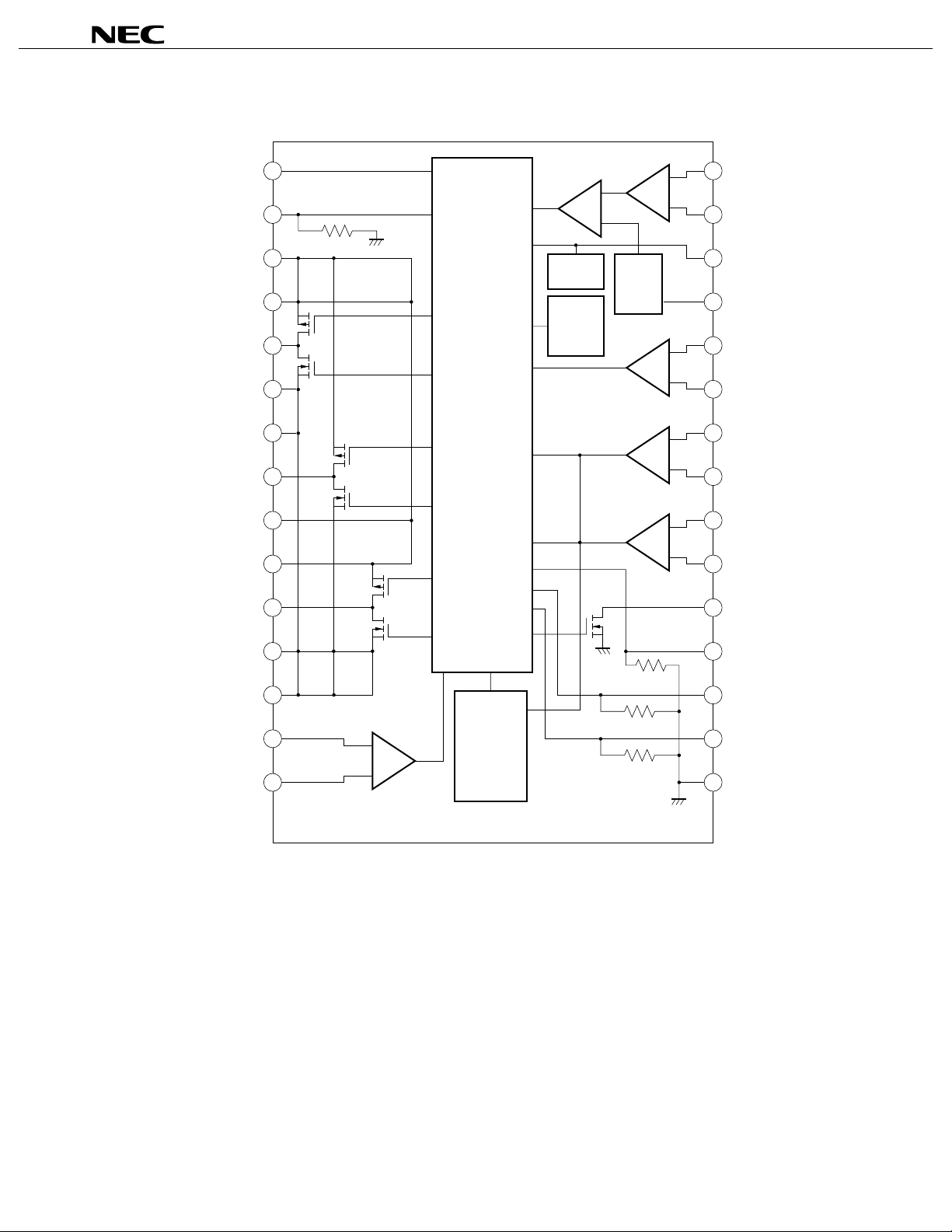

BLOCK DIAGRAM

µµµµ

PD16856

IND

STB

V

V

OUT2

RF

RF

OUT1

V

V

OUT0

RF

1

2

M

3

M

4

Q5

5

UVLO

T.S.D

OSC

+

30

29

28

27

26

EC

ECR

V

DD

C

T

H2+

Q6

6

Phase

–

25

H2–

excitation

pulse

7

generator

+

24

H1+

Q3

8

–

23

H1–

Q4

M

9

M

10

+

–

22

21

H0+

H0–

Q1

11

12

Q2

Ganged

with STB

20

19

HB

FGsel

I

RF

SEN

13

14

Reverse

rotation

18

17

ST/SP

REV

detection

CL

15

circuit

16

GND

Caution When there is more than one pin of the same kind of pin (VM and RF), all pins should be connected

to their targets.

Data Sheet S13447EJ1V0DS00

5

Loading...

Loading...