NEC UPD16335 Datasheet

DATA SHEET

MOS INTEGRATED CIRCUIT

µ

PD16335

96-Bit AC-PDP DRIVER

The µPD16335 is a high-voltage CMOS driver designed for flat display panels such as PDPs, VFDs and ELs. It

consists of a 96-bit bi-directional shift register, 96-bit latch and high-voltage CMOS driver. The logic block is designed

to operate using a 5-V power supply enabling direct connection to a gate array or a microcontroller. In addition, the

µ

PD16335 achieves low power dissipation by employing CMOS structure while having a high withstand voltage output

(80 V, +50/–75 mA).

FEATURES

• Selectable by IBS pin; three 32-bit bi-directional shift register circuits configuration or six 16-bit bi-directional shift

register circuits configuration

• Data control with transfer clock (external) and latch

• High-speed data transfer (f

• High withstand output voltage (80 V, +50/–75 mA

• 5 V CMOS input interface

• High withstand voltage CMOS structure

• Capable of reversing all driver outputs by PC pin

max. = 25 MHz min. at data fetch)

(fmax. = 16 MHz min. at cascade connection)

MAX.)

ORDERING INFORMATION

Part Number Package

µ

PD16335 COB

Note Please consult with an NEC sales representative about COB.

Note

Document No. S12192EJ2V0DS00 (2nd edition)

Date Published May 1998 N CP(K)

Printed in Japan

©

1998

BLOCK DIAGRAM (IBS = H, 3-BIT INPUT, 32-BIT LENGTH SHIFT REGISTER)

OE

PC

BLK

LE

SR1

L

A

1

A

1

CLK CLK

R/L

B

A

1

2

R/L

B

A

1

2

CLK

R/L

B

2

A

3

B

2

A

3

CLK

R/L

B

3

B

3

SR2

SR3

1

S

S

4

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

94

S

2

S

S

5

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

S

95

3

S

S

6

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

S

96

S

S

S

S

S

S

1

1

2

.

.

.

3

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

94

.

.

.

95

.

96

L

96

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

µ

PD16335

V

DD2

1

O

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

V

SS2

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

V

DD2

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

O

96

SRn: 32-bit shift register

V

SS2

2

BLOCK DIAGRAM (IBS = L, 6-BIT INPUT, 16-BIT LENGTH SHIFT REGISTER)

OE

PC

µ

PD16335

BLK

LE

SR1

A

1

A

1

CLK CLK S

R/L

B

1

R/L

B

S

1

SR2

A

2

A

2

CLK S

R/L

B

2

S

B

2

SR3

A

3

A

3

CLK S

R/L

B

3

S

B

3

SR4

A

4

A

4

CLK S

R/L

B

4

S

B

4

SR5

A

5

A

5

CLK S

R/L

B

5

S

B

5

SR6

A

6

A

6

CLK S

R/L

B

6

S

B

6

V

DD2

1

S

7

.

.

.

91

2

S

8

.

.

.

92

3

S

9

.

.

.

93

4

S

10

.

.

.

94

5

S

11

.

.

.

95

6

S

12

.

.

.

96

S

S

S

S

S

S

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

S

S

S

S

LE

1

2

1

L

3

.

4

.

.

.

.

5

.

.

.

.

6

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

93

.

.

.

.

94

.

.

.

95

.

96

L

96

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

V

DD2

O

1

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

V

SS2

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

O

96

SRn: 16-bit shift register

V

SS2

3

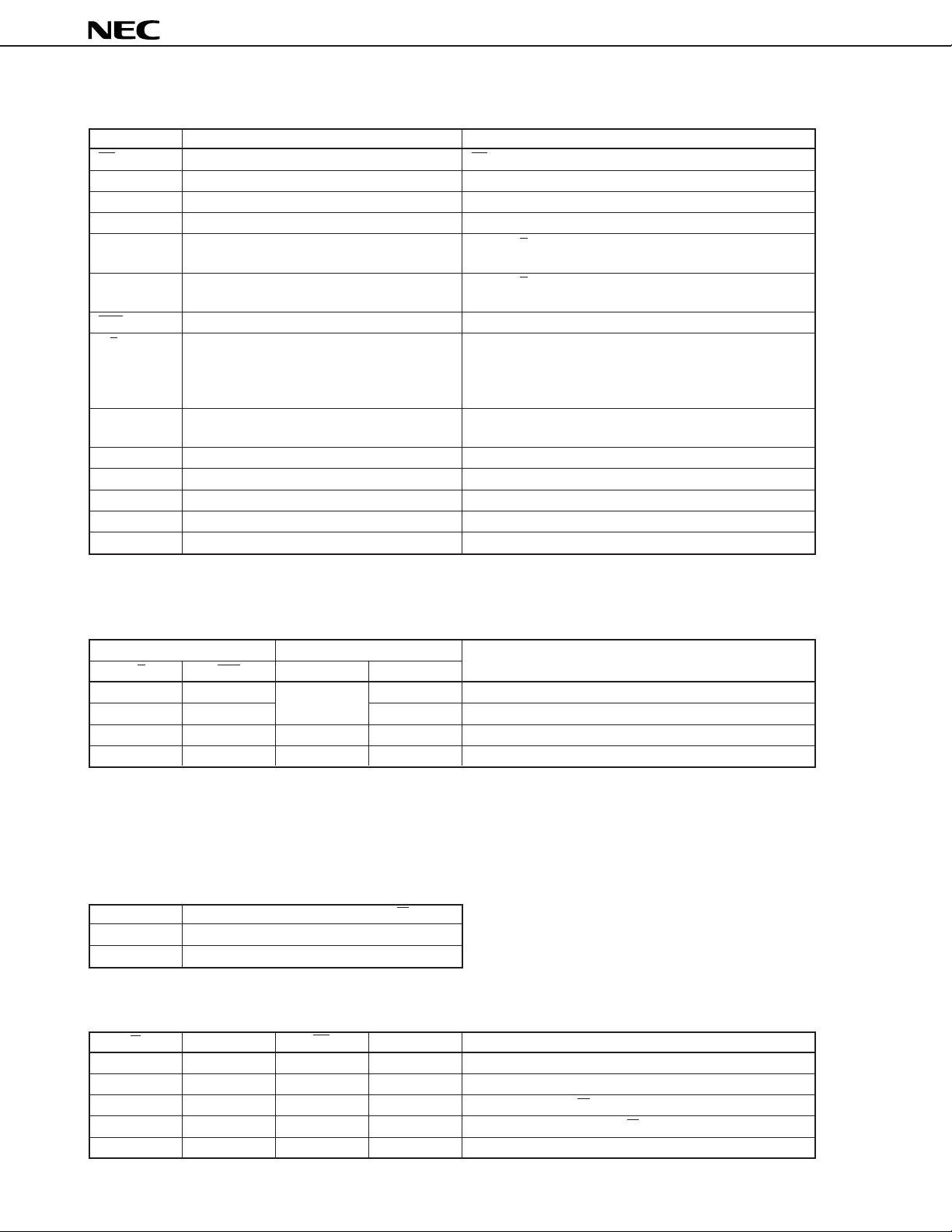

PIN DESCRIPTION

Symbol Pin Name Description

PC Polarity change input PC = L: All driver output invert

BLK Blank input BLK = H: All output = H or L

LE Latch enable input Data latch by rising edge of this signal.

OE Output enable Make output high impedance by input H

A1 to A3 (6) RIGHT data input/output

B1 to B3 (6) LEFT data input/output

CLK Clock input Shift executed on fall

R/L Shift control input Right shift mode when R/L = H

IBS Input mode switch H: 32-bit length shift register, 3-bit input

O1 to O96 High withstand voltage output 80 V, +50/–75 mA MAX.

VDD1 Power supply for logic block 5 V ±10%

VDD2 Power supply for driver block 10 to 70 V

VSS1 Logic GND Connect to system GND

VSS2 Driver GND Connect to system GND

Note When input mode is 3-bit, set unused input and output pins “L” level.

Note

Note

When R/L = H (values in parentheses are for 6-bit input)

A1 to A3 (6): Input B1 to B3 (6): Output

When R/L = L (values in parentheses are for 6-bit input)

A1 to A3 (6): Output B1 to B3 (6): Input

SR1: A1 → S1 ··· S94 → B1 (Same direction for SR2 to SR6)

Left shift mode when R/L = L

SR1: B1 → S94 ··· S1 → A1 (Same direction for SR2 to SR6)

L: 16-bit length shift register, 6-bit input

µ

PD16335

TRUTH TABLE 1 (Shift Register Block)

Input Output

R/L CLK A B

H ↓ Input Output

H H or L Output Hold

L ↓ Output

L H or L Output Hold

Note 2

Note 1

Input Left shift execution

Right shift execution

Notes 1. The data of S91 to S93 (S85 to S90) shifts to S94 to S96 (S91 to S96) and is output from B1 to B3 (B1 to B6)

at the falling edge of the clock, respectively. (Values in parentheses are for 6-bit input)

2. The data of S4 to S6 (S7 to S12) shifts to S1 to S3 (S1 to S6) and is output from A1 to A3 (A1 to A6) at the

falling edge of the clock, respectively (Values in parentheses are for 6-bit input)

Shift Register

TRUTH TABLE 2 (Latch Block)

LE Output State of Latch Block (Ln)

↑ Latch Sn data

H or L Hold latch data

TRUTH TABLE 3 (Driver Block)

Ln BLK PC OE Output State of Driver Block

X H H L H (All driver outputs: H)

X H L L L (All driver outputs: L)

X L H L Output latch data (Ln)

X L L L Output inverted latch data (Ln)

X X X H Set output impedance high

X: H or L, H: High level, L: Low level

4

Loading...

Loading...