DATA SHEET

MOS INTEGRATED CIRCUIT

µ

PD16326A

32-BIT FLUORESCENT DISPLAY TUBE DRIVER

The µPD16326A is a fluorescent display tube driver using a high breakdown voltage CMOS process. It consists

of 32-bit bidirectional shift registers, a latch circuit, and a high breakdown voltage CMOS driver block. The logic block

operates on a 5 V power supply designed to be connected directly to a microcontroller (CMOS level input). The driver

block has a 150 V and 20 mA high breakdown voltage output, and both the logic block and driver block consist of CMOS,

allowing operation with low power consumption.

FEATURES

• High breakdown voltage CMOS structure

• High breakdown voltage, high current output (150 V, 20 mA)

• 32-bit bidirectional shift registers on chip

• Data control by transfer clock (external) and latch

• High-speed data transfer capability (f

• Wide operating temperature range (T

max = 8.0 MHz MIN)

A = –40 to 85 ˚C)

ORDERING INFORMATION

Part Number Package

µ

PD16326AGB-3B4 44-pin plastic QFP (4-direction leads)

Document No. S11760EJ1V0DS00 (1st edition)

Date Published December 1997 N

Printed in Japan

©

1997

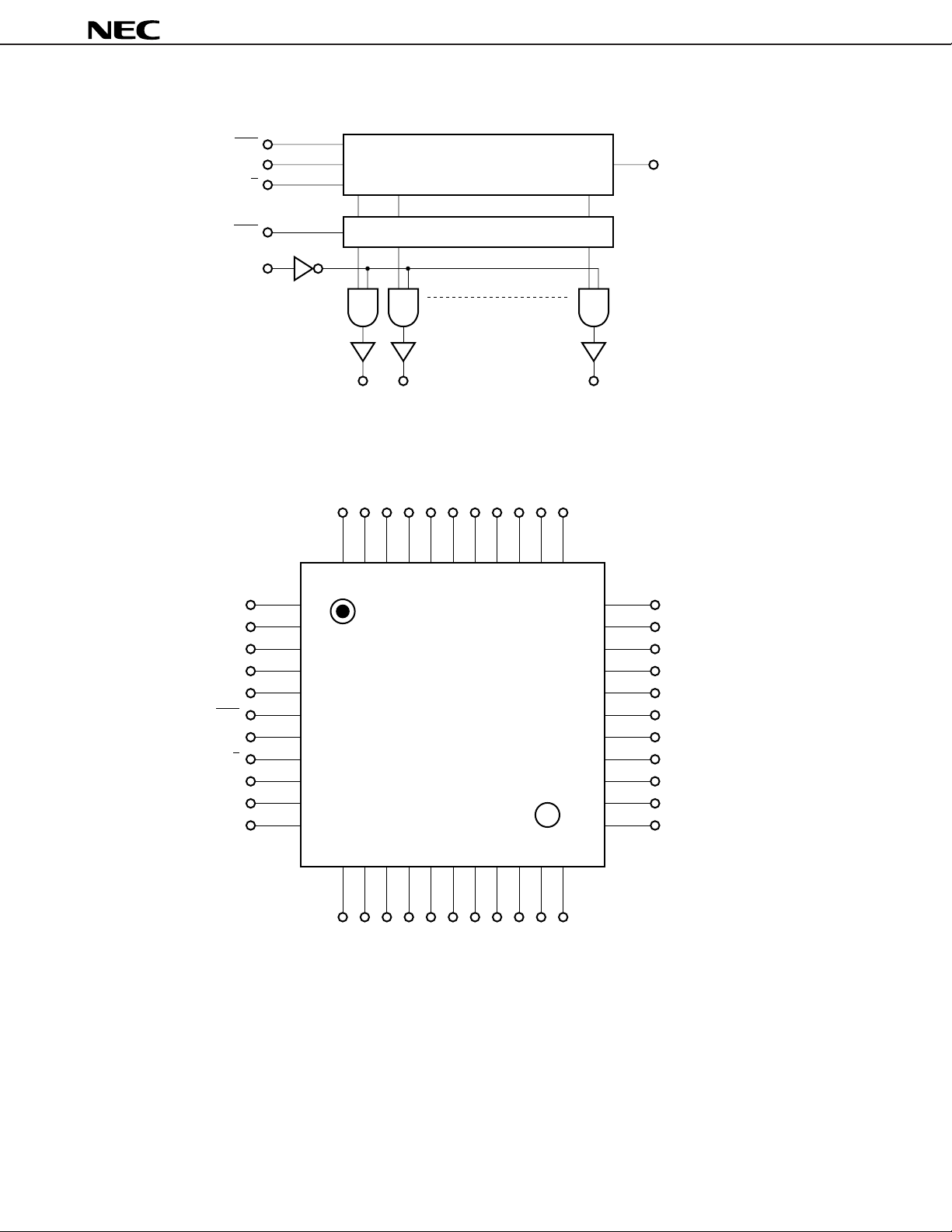

BLOCK DIAGRAM

CLK

R/L

µ

PD16326A

A

32-bit bidirectional shift registers

B

STB

BLK

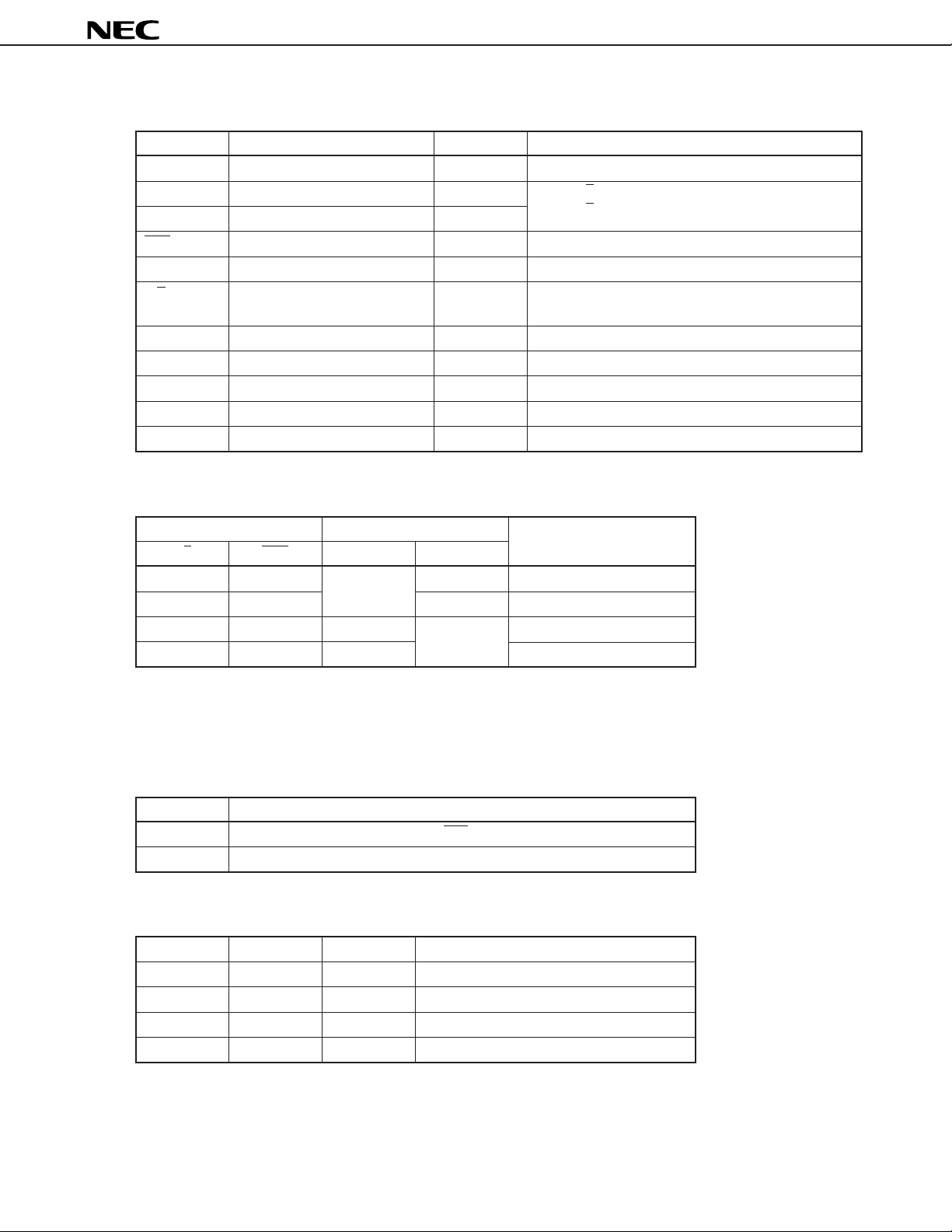

PIN CONFIGURATION (Top View)

V

DD2

V

SS2

BLK

STB

CLK

V

SS1

R/L

V

DD1

SS2

V

A

B

1

2

3

4

5

6

7

8

9

10

11

32-bit latch

1

O

O

O1O2O3O4O5O6O7O8O9O10O

2

11

4443424140393837363534

O

33

32

31

30

29

28

27

26

25

24

23

32

O

12

O

13

O

14

O

15

O

16

O

17

O

18

O

19

O

20

O

21

O

22

1213141516171819202122

DD2

O32O31O30O29O28O27O26O25O24O

V

23

Remark Be sure to enter the power to VDD1, logic signal, and VDD2, in that order, and turn off the power in the reverse

order.

2

µ

PIN DESCRIPTION

Pin Symbol Pin Name Pin Number Description

STB Latch strobe input 5 H: Data through L: Data retention

A RIGHT data input 3 When R/L = H, A: Input B: Output

B LEFT data input 10

CLK Clock input 6 Shift is executed on a fall.

BLK Blanking input 4 H: O1 to O32: ALL “L”

R/L Shift control input 8 H: Right shift mode A → O1 ... O32 → B

O1 to O32 High breakdown voltage output 13 - 44 130 V, 20 mA MAX

VDD1 Logic block power supply 9 5 V ±10 %

VDD2 Driver block power supply 1, 12 30 to 130 V

VSS1 Logic ground 5 Connected to system GND

VSS2 Driver ground 2, 11 Connected to system GND

TRUTH TABLE 1 (SHIFT REGISTER BLOCK)

When R/L = L, A: Output B: Input

L: Left shift mode B → O32 ... O1 → A

PD16326A

Input Output

R/L CLK A B

H ↓ Input Output

H H or L Output Retained

L ↓ Output

L H or L Output Retained

Note 2

Note 1

Input Execution of left shift

Shift Register

Execution of right shift

Notes 1. On a clock fall, the data items of S31 are shifted to S32, and output from B.

2. On a clock fall, the data items of S2 are shifted to S1, and output from A.

TRUTH TABLE 2 (LATCH BLOCK)

STB Operation

L Retains Sn data immediately before STB becomes L.

H Outputs shift register data.

TRUTH TABLE 3 (DRIVER BLOCK)

Note

Ln

××H L (all driver outputs: L)

× L L Outputs Sn data on STB fall.

LHLL

HHLH

STB BLK Driver output state

Note Ln: Latch output

Remark × = H or L, H = high level, L = Low level

3

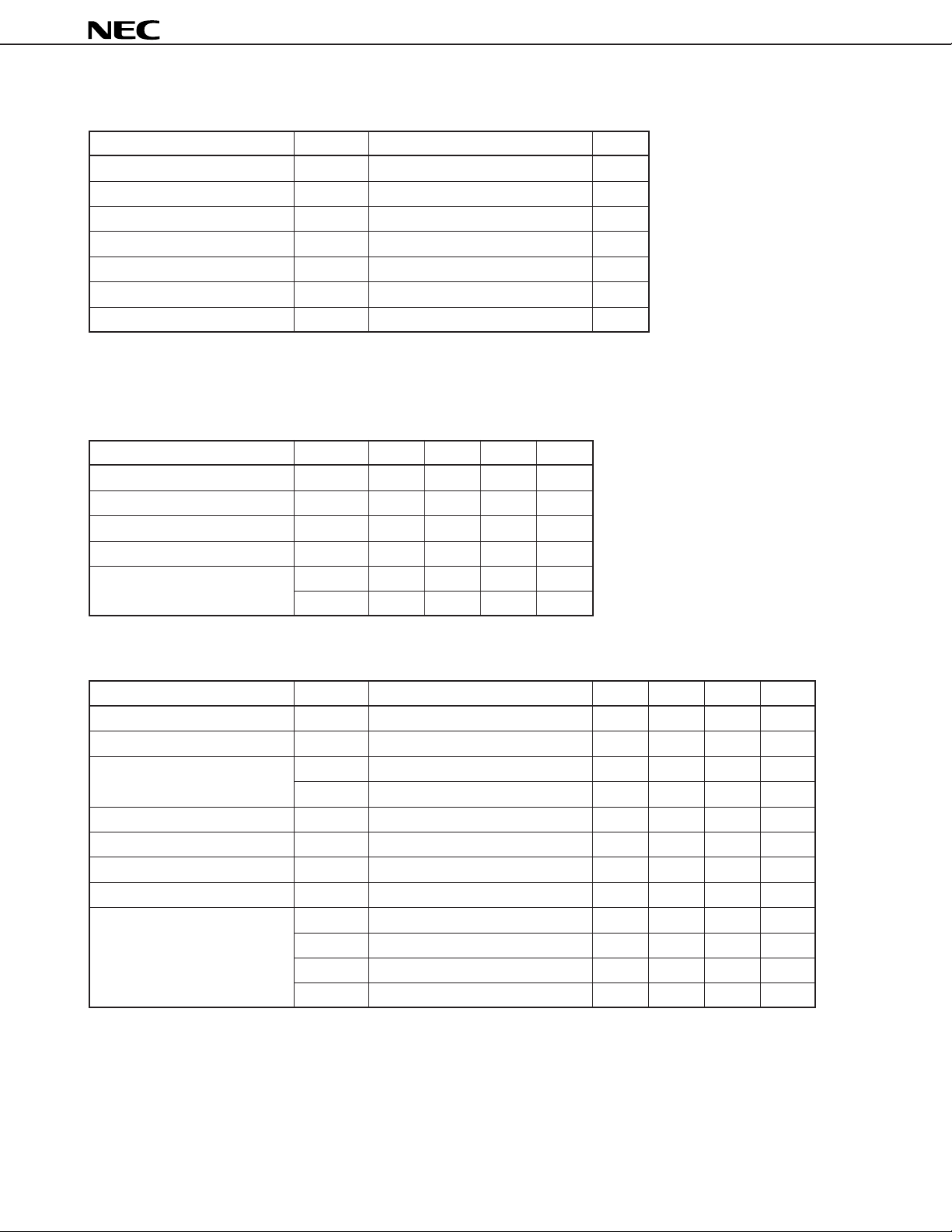

ABSOLUTE MAXIMUM RATINGS (TA = 25 ˚C, VSS = 0 V)

Item Symbol Rating Unit

Logic block supply voltage VDD1 –0.5 to +7.0 V

Driver block supply voltage VDD2 –0.5 to +150 V

Logic block input voltage VI –0.5 to VDD1 + 0.5 V

Driver block output current IO 20 mA

Package allowable power dissipation

Operating ambient temperature

Storage temperature Tstg –65 to +150 ˚C

PD 800

TA –40 to +85 ˚C

Note

mW

Note When TA ≥ 25 °C, load should be alleviated at a rate of –8.0 mW/°C. (Tj = 125 °C (MAX.))

RECOMMENDED OPERATING RANGE (TA = – 40 to +85 ˚C, VSS = 0 V)

Item Symbol MIN. TYP. MAX. Unit

Logic block supply voltage VDD1 4.5 5.0 5.5 V

Driver block supply voltage VDD2 30 130 V

Input voltage high VIH 0.7·VDD1 VDD1 V

Input voltage low VIL 0 0.2·VDD1 V

Driver output current IOH –10 mA

IOL +2.5 mA

µ

PD16326A

ELECTRICAL SPECIFICATIONS (TA = 25 ˚C, VDD1 = 4.5 to 5.5 V, VDD2 = 130 V, VSS = 0 V)

Item Symbol Condition MIN. TYP. MAX. Unit

Output voltage high VOH1 Logic, IOH = –1.0 mA 0.9·VDD1 VDD1 V

Output voltage low VOL1 Logic, IOL = 1.0 mA 0 0.1·VDD1 V

Output voltage high VOH21 O1 to O40, IOH = –0.5 mA 126 V

VOH22 O1 to O40, IOH = –5.0 mA 120 V

Output voltage low VOL2 O1 to O40, IOL = 0.5 mA 2.5 V

Input leakage current IIL VI = VDD1 or VSS1 ±1.0

Input voltage high VIH 0.7·VDD1 VDD1 V

Input voltage low VIL 0 0.2·VDD1 V

Static consumption current IDD1 Logic, TA = –40 to +85 ˚C 1 000

IDD1 Logic, TA = 25 ˚C 100

IDD2 Driver, TA = –40 to +85 ˚C 1 000

IDD2 Driver, TA = 25 ˚C 100

µ

A

µ

A

µ

A

µ

A

µ

A

4

Loading...

Loading...