NEC UPC8100GR-E2, UPC8100GR Datasheet

DATA SHEET

BIPOLAR ANALOG INTEGRATED CIRCUIT

µ

PC8100GR

SILICON UP/DOWN CONVERTERS IC

FOR 800 MHz to 900 MHz MOBILE COMMUNICATIONS

DESCRIPTION

µ

PC8100GR is a silicon monolithic integrated circuit designed as up/down converters for 800 MHz to 900 MHz mobile

communications, mainly CT2. This IC consists of upconverter and downconverter, which are packaged in 20 pin SSOP.

Quadrature modulator IC (µPC8101GR) is also available as for kit-use with this IC. So, these pair devices contribute to

make RF block small, high-performance and low power-consumption.

This product is manufactured using NEC’s 20 GHz f

passivation film and gold electrodes. These materials can protect chip surface from external pollution and prevent corrosion

and migration. Thus, this product has excellent performance, uniformity and reliability.

T NESAT

III silicon bipolar process. This process uses silicon nitride

FEATURES

• Operating frequency – fRF = 800 MHz to 900 MHz, fIF = 50 MHz to 150 MHz, fLo = 650 MHz to 1 050 MHz

• Upconverter and downconverter are integrated in 1 chip.

• 20 pin SSOP suitable for high-density surface mounting.

• Wide operating voltage V

• Equipped with Power Save Function.

• Excellent linearity

CC = 2.7 to 4.5 V

APPLICATIONS

• Typical application – Digital cordless phone CT2.

• Further application – Digital cellular, etc.

ORDERING INFORMATION

PART NUMBER PACKAGE SUPPLYING FORM

µ

PC8100GR-E2 20 pin plastic SSOP Embossed tape 12 mm wide. QTY 2.5 kp/Reel.

(225 mil) Pin 1 indicates roll-in direction of tape.

Remark To order evaluation samples, please contact your local NEC sales office. (Order number: µPC8100GR)

The information in this document is subject to change without notice. Before using this document, please

confirm that this is the latest version.

Not all devices/types available in every country. Please check with local NEC representative for availability

and additional information.

Document No. P10817EJ3V0DS00 (3rd edition)

Date Published October 1999 N CP(K)

Printed in Japan

Caution electro-static sensitive devices

The mark shows major revised points.

©

1995,1999

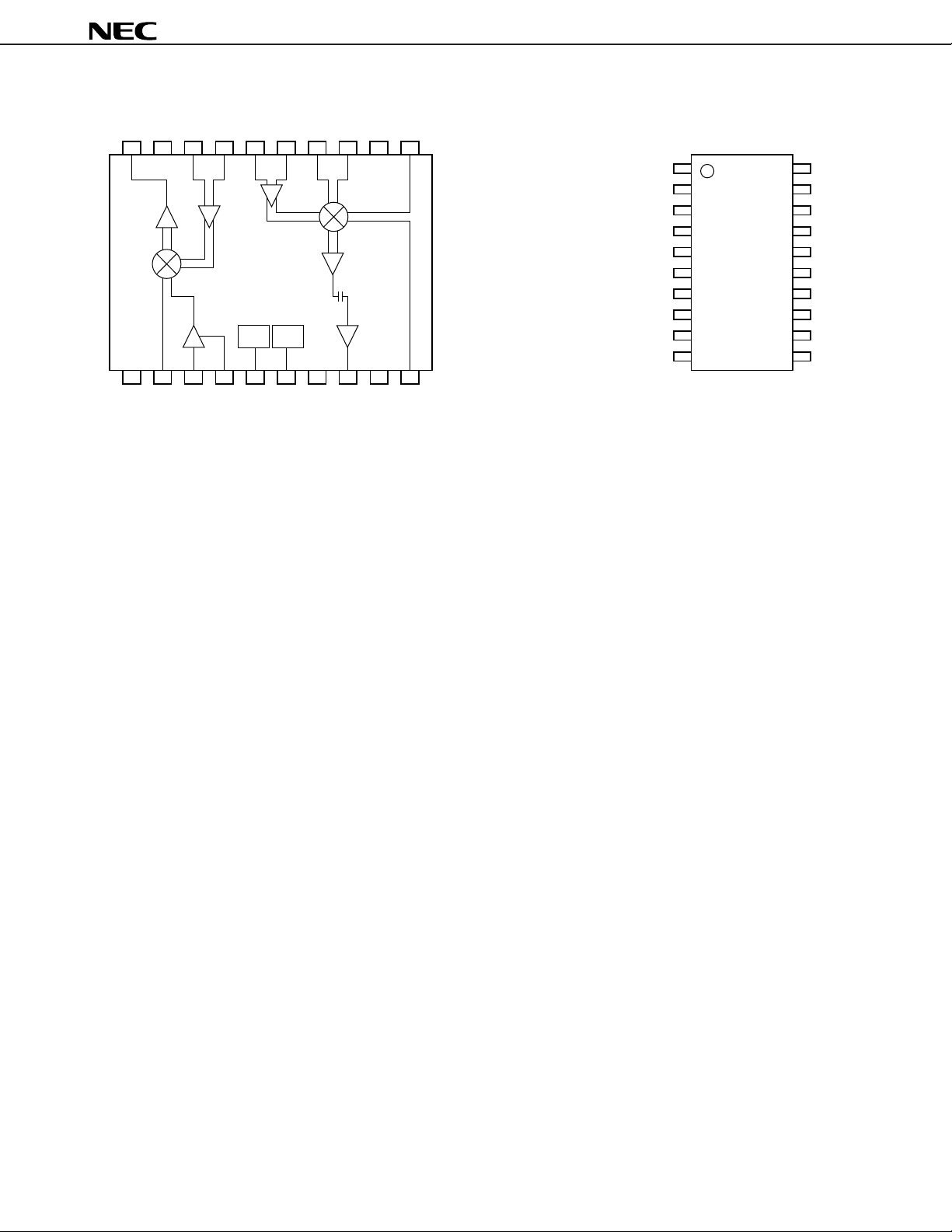

INTERNAL BLOCK DIAGRAM AND PIN CONNECTIONS

µ

PC8100GR

20 19 18 17 16 15 14 13 12 11

REG. REG.

12345678 910

1.

GND

2.

RF BYPASS

3.

RF INPUT

4.

PEAKING OUT

5.

P/S (for DOWN CONV.)

6.

P/S (for UP CONV.)

CC

(for UP CONV.)

7.

V

RF OUTPUT

8.

GND

9.

MIX OUTPUT1

10.

MIX OUTPUT2

11.

GND

12.

IF BYPASS

13.

IF INPUT

14.

OSC INPUT (for UP CONV.)

15.

OSC BYPASS (for UP CONV.)

16.

OSC BYPASS (for DOWN CONV.)

17.

OSC INPUT (for DOWN CONV.)

18.

CC

(for DOWN CONV.)

V

19.

IF OUTPUT

20.

10

(Top View)

1

2

3

4

5

6

7

8

9

20

19

18

17

16

15

14

13

12

11

2

Data Sheet P10817EJ3V0DS00

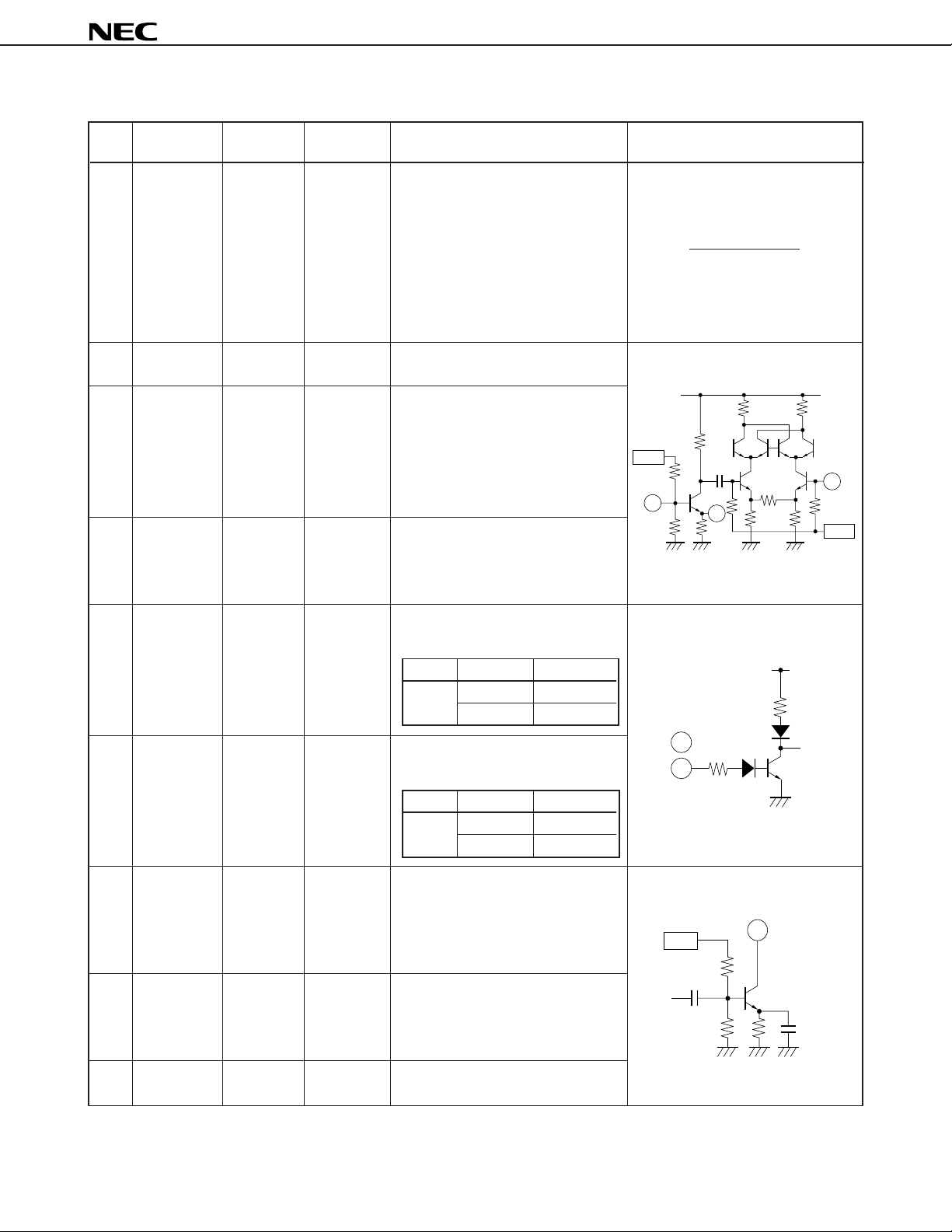

PIN EXPLANATION

µ

PC8100GR

PIN

ASSIGNMENT

NO.

1 GND 0.0 –

2 RF bypass – 1.1

3 RF input – 0.9

4 Peaking out – 0.12

APPLIED

VOLTAGE (V)

PIN VOLTAGE

(V)

FUNCTION AND APPLICATION EQUIVALENT CIRCUIT

Ground for downconverter.

Must be connected to the system ground

with minimum inductance. Ground pattern on the board should be formed as

wide as possible.

(Track length should be kept as short as

possible.)

Bypass of RF input for downconverter.

This pin is RF input for downconverter

designed as double balanced mixer.

This high-impedance input should be

matched with external chip inductor. (eg

4.7 nH).

Open emitter pin of low noise amplifier.

Grounded with capacitor (eg 3 pF) and

register (eg 22 Ω) serially.

REG.

3

4

CC

V

2

REG.

5

Power-save pin

for

downconverter

6

Power-save pin

for

upconverter

7VCC for 2.7 to 4.5 –

upconverter

8 RF output same as –

0 to 4.5 –

0 to 4.5 –

VCC through

intactor

This pin can control downconverter’s

ON/OFF operation with bias as follows;

Bias: V Operation

VPS

This pin can control upconverter’s ON/

OFF operation with bias as follows;

V

PS

Supply voltage for upconverter.

Must be connected bypass capacitor

(e.g 1 000 pF) to minimize ground impedance.

F output from upconverter.

Connect the VCC through inductor (eg 15

nH).

≥1.8 ON

0 to 1.0 OFF

Bias: V Operation

≥1.8 ON

0 to 1.0 OFF

5

6

REG.

or

8

9 GND 0.0 –

Ground for RF amplifier of upconverter.

Data Sheet P10817EJ3V0DS00

3

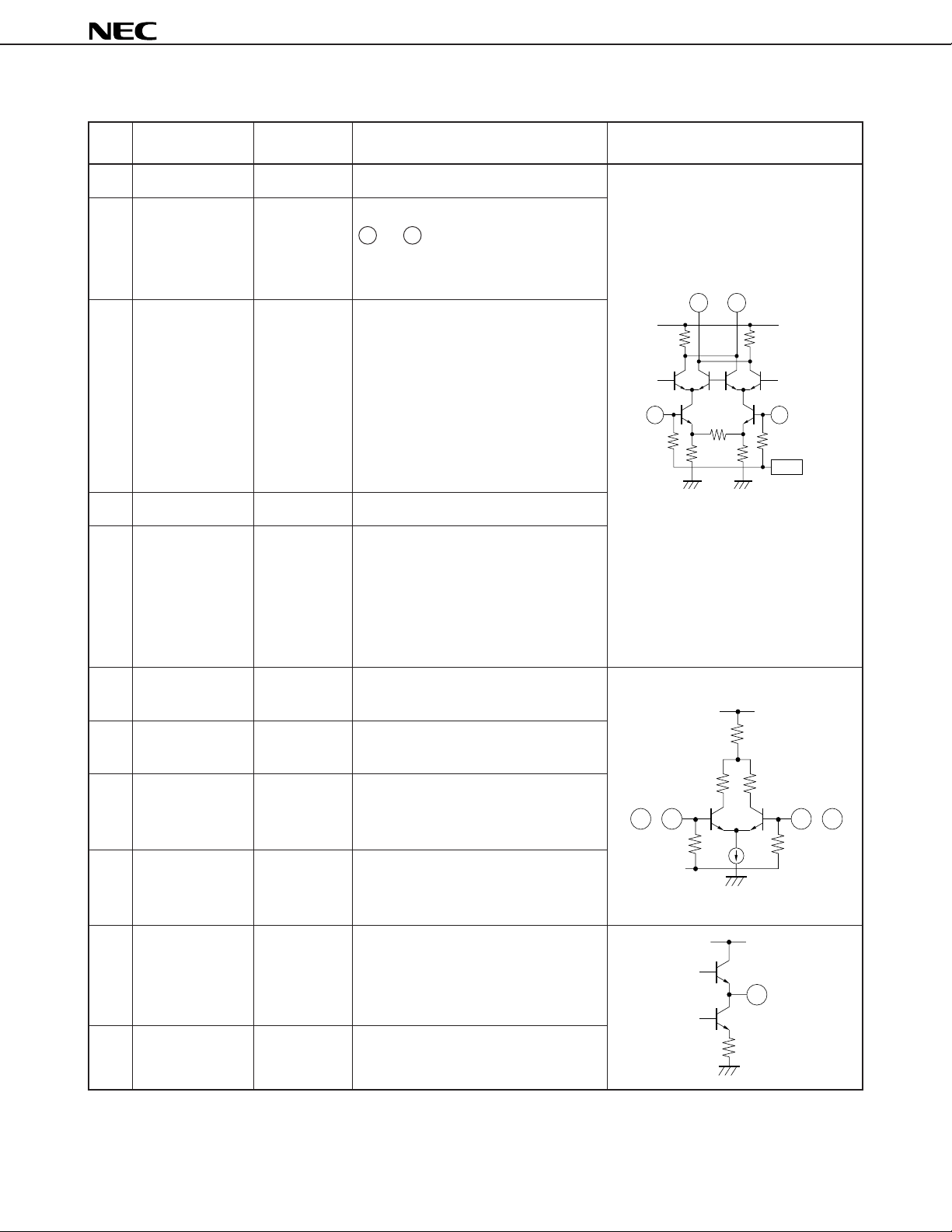

PIN EXPLANATION

µ

PC8100GR

PIN

NO. (V)

ASSIGNMENT

10 MIX OUT 1 2.3

11 MIX OUT 2 2.3

12 GND 0*

13 IF bypass 1.03

14 IF input 1.03

PIN VOLTAGE

FUNCTION AND APPLICATION EQUIVALENT CIRCUIT

Mixer output from upconverter.

Mixer output from upconverter.

10 and 11 pins should be externally

equipped with tank circuit of inductor (eg

4.7 nH) and capacitor (eg 3.5 pF).

10 11

Ground for oscillator buffer amplifier and

mixer of upconverter.

Must be connected to the system ground

with minimum inductance. Ground

pattern on the board should be formed

as wide as possible.

(Track length should be kept as short as

possible.)

Bypass of IF input for upconverter.

This pin is IF input for upconverter

designed as double balanced mixer.

This high-impedance input should be

externally equipped with matching circuit

of inductor (eg 220 nH) and capacitor

(eg 1.5 pF).

14

V

CC

13

REG.

15 OSC input 1.8

(for upconverter)

16 OSC bypass 1.8

(for upconverter)

17 OSC bypass 1.85

(for downconverter)

18 OSC input 1.85

(for downconverter)

19 VCC supply for 2.7 to 4.5*

for downconverter

20 IF output 1.45

* Externally supply voltage

Local oscillator input for upconverter. Required for matching with register 51 Ω.

Bypass of local oscillator input for

upconverter.

Bypass of local oscillator input for

downconverter.

Local oscillator input for downconverter. Required for matching with

register 51 Ω.

Supply voltage for downconverter.

It must be connected bypass capacitor

(e.g 1 000 pF) to minimize ground

impedance.

IF output from downconverter.

V

CC

,

1815

,

1716

VCC

20

4

Data Sheet P10817EJ3V0DS00

µ

PC8100GR

ABSOLUTE MAXIMUM RATINGS

Supply Voltage VCC TA = +25 °C 5.0 V

Power Dissipation P

D Mounted on 50 × 50 × 1.6 mm double copper 530 mW

of package allowance clad epoxy glass board at TA = +70 °C

Operating Temperature Topt –20 to +70 °C

Storage Temperature T

stg –65 to +150 °C

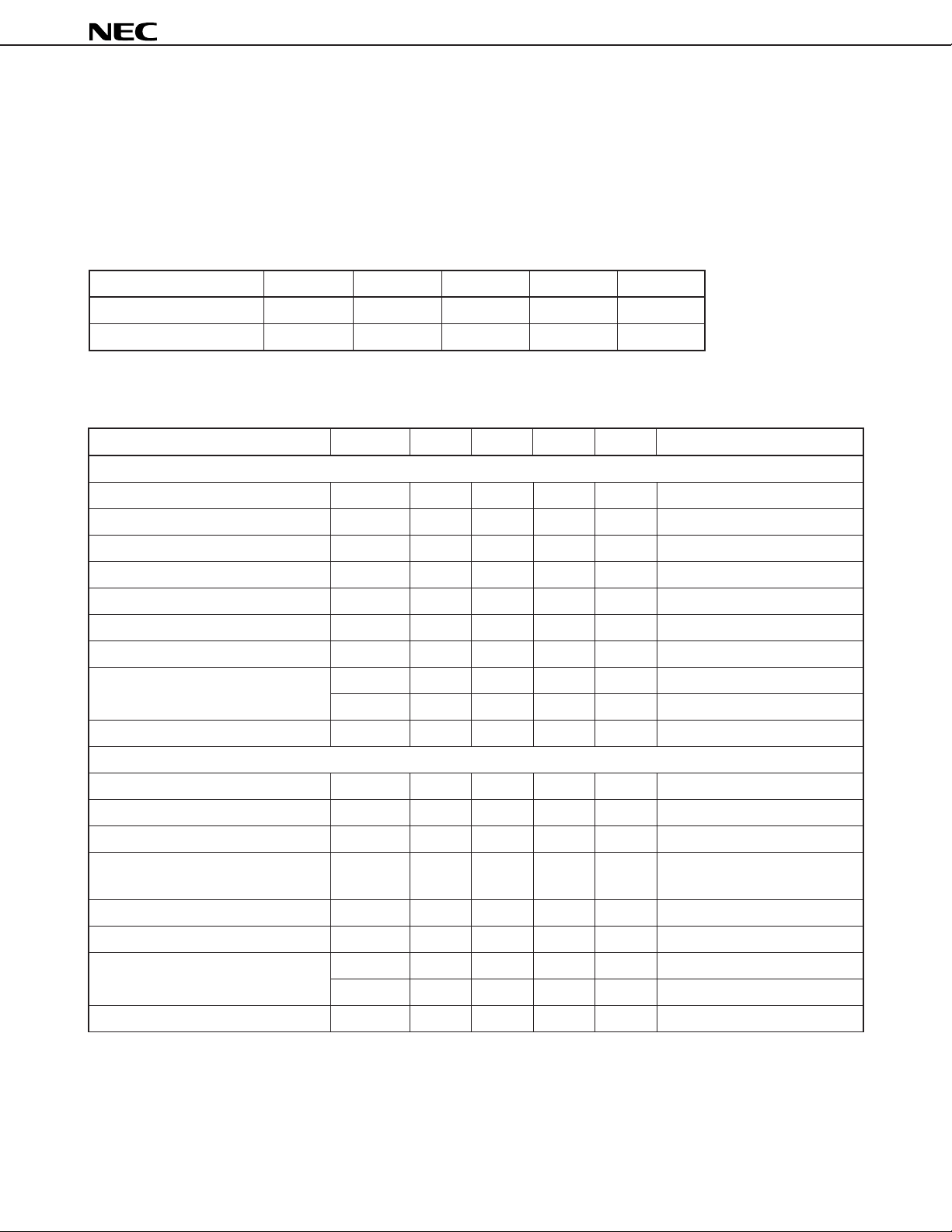

RECOMMENDED OPERATING CONDITIONS

PARAMETERS SYMBOL MIN. TYP. MAX. UNIT

Supply Voltage VCC 2.7 3.0 4.5 V

Operating Temperature Topt –20 +25 +70 °C

ELECTRICAL CHARACTERISTICS (TA = +25 °C, VCC = 2.7 V, ZL = ZS = 50 Ω, unless otherwise specified;

VP/S ≥ 1.8 V)

PARAMETERS SYMBOL MIN. TYP. MAX. UNIT TEST CONDITIONS

UPCONVERTER BLOCK*

1

Circuit current ICC 13.0 25.0 35.0 mA No input signal

Conversion gain CG 17.5 20.5 25.5 dB PIFin = –40 dBm

RF output level PRFout 0 3 dBm PIFin = –10 dBm, 50 Ω load

Noise figure NF 13 18 dB DSB mode

Local leakage at RFout Lorf –25.0 –10.0 dBm PIFin = –10 dBm

IF leakage at RFout IFrf –12.0 –5.0 dBm PIFin = –10 dBm

Circuit current in power-save mode*

Power-save control voltage VP/S(ON) 1.8 4.5 V

Rise up time T up 2.5 5.0

DOWNCONVERTER BLOCK*

Circuit current ICC 8.0 15.0 22.0 mA No input signal

Conversion gain CG 15.0 18.0 23.0 dB PRFin = –40 dBm

IF output level PIFout –4.5 –2.0 dBm PRFin = –10 dBm, 50 Ω load

3rd order intermodulation distortion IM3 –45.0 –49.0 dBc

Noise figure NF 7.5 10 dB DSB mode

Circuit current in power-save mode*

3

ICC(P/S) 220 350

VP/S(OFF) 1.0 V

2

3

ICC(P/S) 220 350

µ

A 6PIN(P/S) ≤ 1.0 V

µ

s

fRFin1 = 866.4 MHz, PRFin1 = –40 dBm

fRFin2 = 866.8 MHz, PRFin2 = –40 dBm

µ

A 5PIN(P/S) ≤ 1.0 V

Power-save control voltage VP/S(ON) 1.8 4.5 V

VP/S(OFF) 1.0 V

Rise up time T up 2.5 5.0

*1 :fIFin = 150.05 MHz, fRFout = 864.05 to 868.05 MHz

fLoin = 1014.10 to 1018.1 MHz (–9 dBm)

*2 :fRFin = 864.05 to 868.05 MHz, fIFout = 150.05 MHz

fLoin = 1014.10 to 1018.1 MHz (–9 dBm)

*3 : Circuit current in power-save mode is total value of upconverter+downconverter

Data Sheet P10817EJ3V0DS00

µ

s

5

Loading...

Loading...