NEC NL6448AC33-29 Datasheet

DATA SHEET

TFT COLOR LCD MODULE

NL6448AC33-29

26 cm (10.4 inches), 640

××××

480 pixels, 262,144 colors,

Incorporated two-lamp/Edge-light type backlight

Ultra Wide viewing angle

DESCRIPTION

NL6448AC33-29 is a TFT (thin film transistor) active matrix color liquid crystal display (LCD) comprising

amorphous silicon TFT attached to each signal electrode, a driving circuit and a backlight. NL6448AC33-29 has a

built-in backlight. Backlight includes long-life-lamps and the lamps are replaceable.

The 26 cm (10.4 inches) diagonal display area contains 640 × 480 pixels and can display 262,144 colors

simultaneously.

NL6448AC33-29 is suitable for industrial application use, because the viewing angle is ultra wide and the

luminance is high. Also the viewing direction is selectable either upper or lower side changing scan direction.

FEATURES

• Ultra wide viewing angle with lateral electric field

• High luminance (250 cd/m2, typ.)

• Low reflection

• 6-bit digital RGB interface

• Data enable (DE) function

• Incorporated edge type backlight with lamps (Two

lamps, with inverter)

• Lamp holder replaceable (Type No.: 104LHS31)

• Reversible scan direction

• Variable luminance control

• Easy to assemble a touch panel

• No antiglare treatment

APPLICATIONS

• Display terminals for control system

• Monitors for process controller

• Industrial PC

Document No. EN0439EJ1V0DS00

Date Published May 1999 P

Printed in Japan

The information in this document is subject to change without notice.

1999©

NL6448AC33-29

STRUCTURE AND FUNCTIONS

A color TFT (thin film transistor) LCD module is comprised of a TFT liquid crystal panel structure, LSIs for driving

the TFT array, and a backlight assembly. The TFT panel structure is created by sandwiching liquid crystal material

in the narrow gap between a TFT array glass substrate and a color filter glass substrate. After the driver LSIs are

connected to the panel, the backlight assembly is attached to the backside of the panel.

RGB (red, green, blue) data signals from a source system is modulated into a form suitable for active matrix

addressing by the onboard signal processor and sent to the driver LSIs which in turn addresses the individual TFT

cells.

Acting as an electro-optical switch, each TFT cell regulates light transmission from the backlight assembly when

activated by the data source. By regulating the amount of light passing through the array of red, green, and blue

dots, color images are created with clarity.

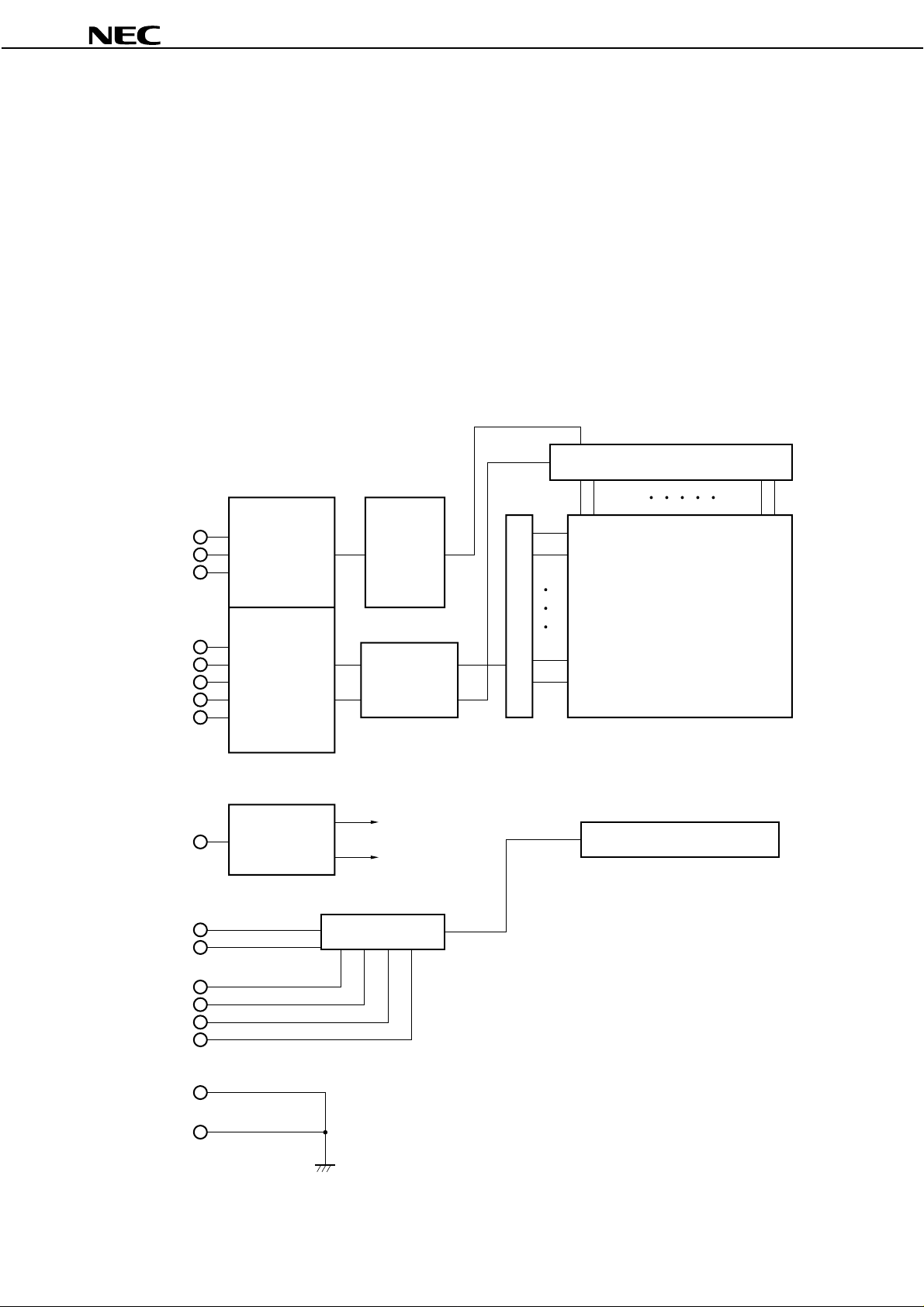

BLOCK DIAGRAM

<1> In case of use the inverter of NEC

H-driver

R0 - R5

G0 - G5

B0 - B5

CLK

Hsync

Vsync

DPS

DE

V

CC

VDDB

GNDB

Digital

signal

processor

LCD timing

controller

Power

supply

circuit

Level

shift

Scan select

LSIs

Drivers

Inverter

V-driver

TFT LCD panel

H: 640 × 3 (R, G, B)

480 lines

V: 480

1920 lines

Backlight

2

BRTHL

BRTC

BRTH

BRTL

Frame

GND (SG)

Both frame and GNDB (Backlight ground) are not contacted to the lamp holder.

Note

Data Sheet EN0439EJ1V0DS00

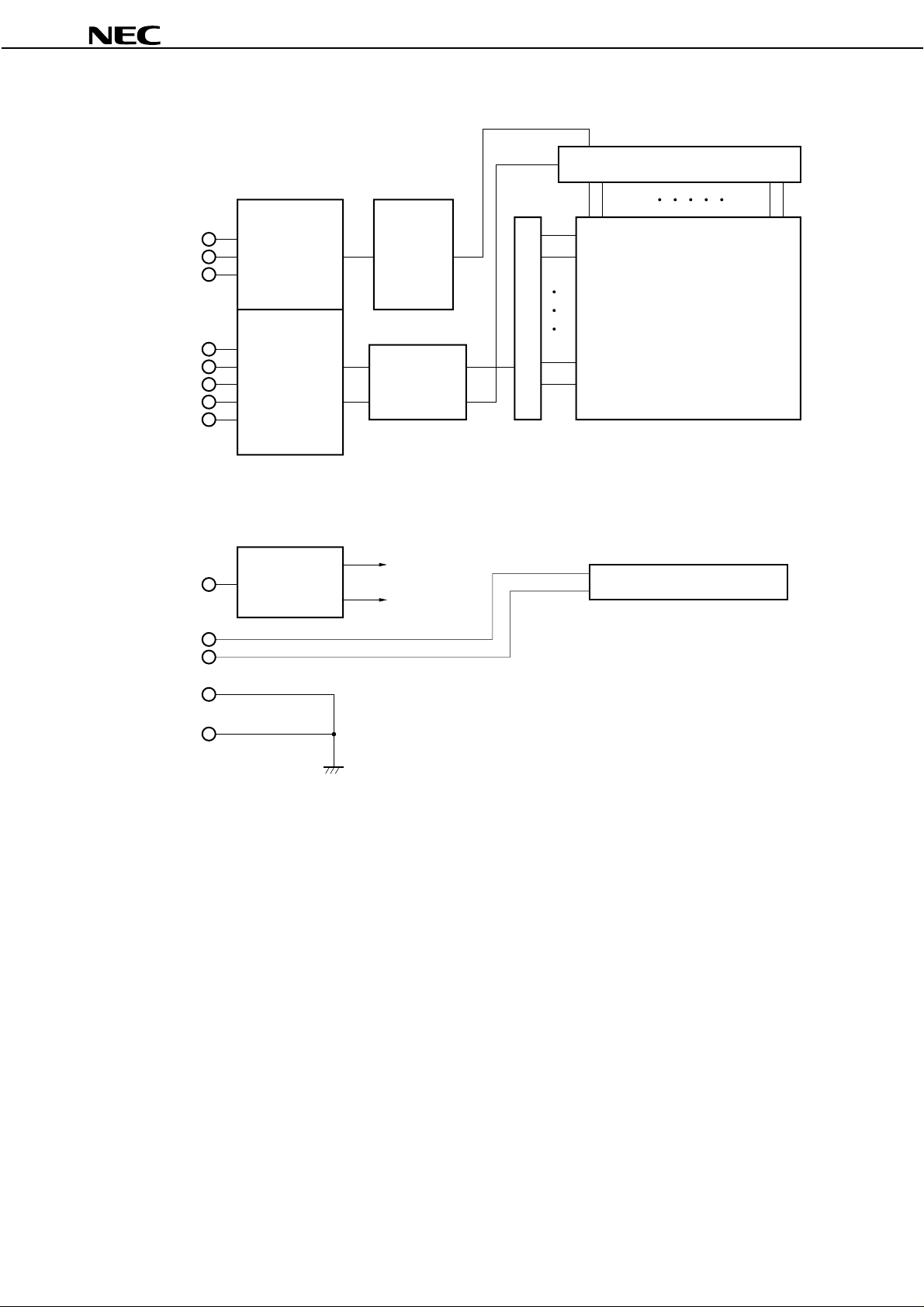

<2> In case of use the inverter of customers

NL6448AC33-29

H-driver

R0 - R5

G0 - G5

B0 - B5

CLK

Hsync

Vsync

DPS

DE

V

CC

VH

VL

Digital

signal

processor

LCD timing

controller

Power

supply

circuit

Level

shift

Scan select

LSIs

Drivers

V-driver

TFT LCD panel

H: 640 × 3 (R, G, B)

480 lines

V: 480

1920 lines

Backlight

Frame

GND (SG)

Both frame and GNDB (Backlight ground) are not contacted to the lamp holder.

Note

Data Sheet EN0439EJ1V0DS00

3

NL6448AC33-29

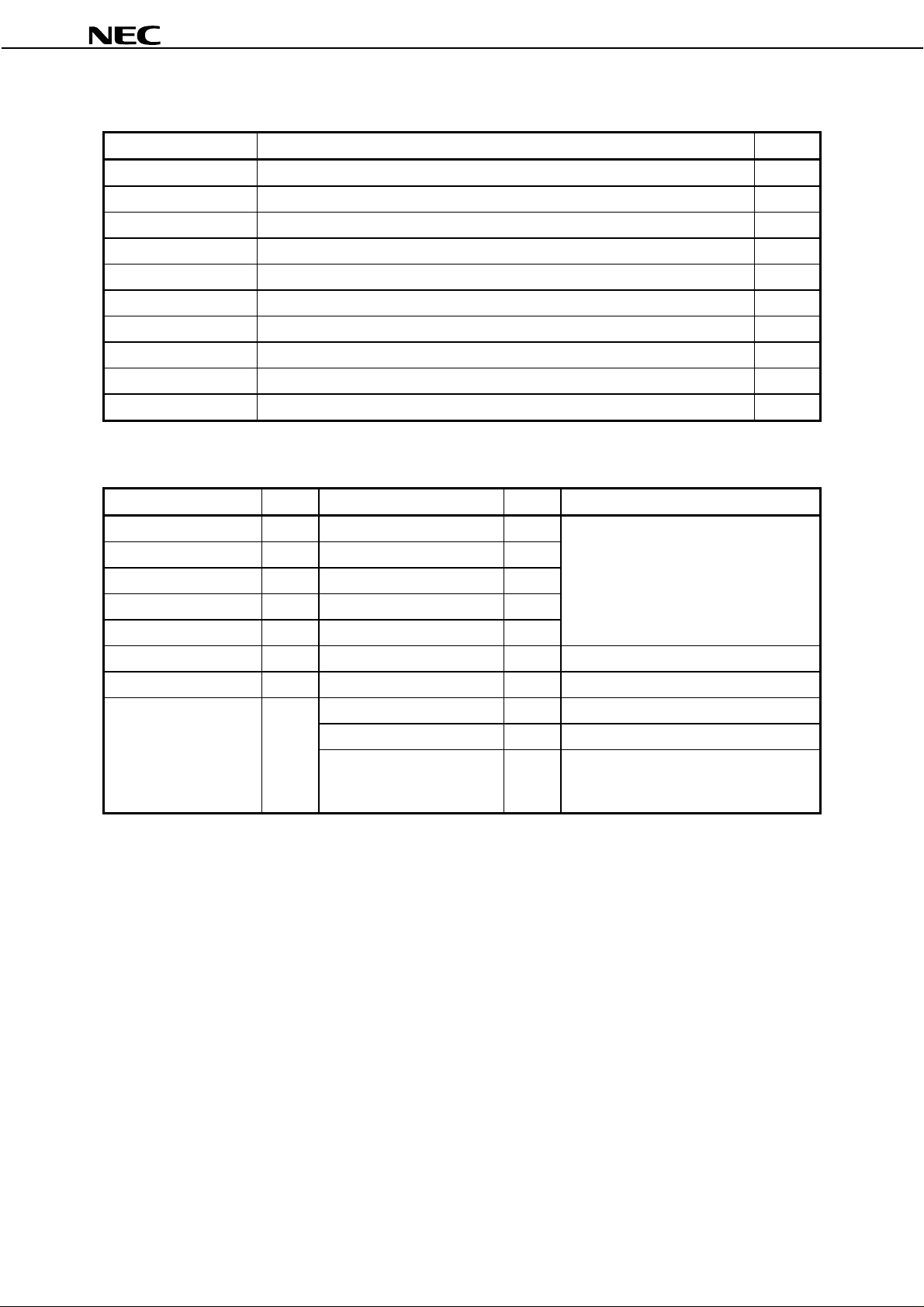

OUTLINE OF CHARACTERISTICS (at room temperature)

Display area 211.2 (H) × 158.4 (V) mm

Drive system a-Si TFT active matrix

Display colors 262,144 colors

Number of pixels 640 × 480 pixels

Pixel arrangement RGB vertical stripe

Pixel pitch 0.33 (H) × 0.33 (V) mm

Module size 243.0 (H) × 185.1 (V) × 10.5 typ. (D) mm

Inverter size 25.0 (H) × 105.0 (V) × 10.2 max. (D) mm

Weight 510 g (typ.) + 15 g (typ., inverter)

Contrast ratio 150 : 1 (typ.)

Viewing angle (more than the contrast ratio of 10 : 1)

Horizontal : 80° (typ., left side, right side)

Vertical : 80° (typ., up side, down side)

Designed viewing direction Optimum grayscale (

Color gamut 45% (typ., At center, to NTSC)

Response time 50 ms (typ.), black to white

Luminance 250 cd/m

Signal system 6-bit digital signals for each of RGB primary colors, synchronous signals

(Hsync, Vsync), dot clock (CLK)

Supply voltages 3.3 V [5.0 V] (Logic, LCD driving), 12.0 V (Backlight)

Backlight Edge light type, two cold cathode fluorescent lamp

Power consumption 7.1 W (typ., 3.3 V, 12.0 V)

2

(typ.)

= 2.2): perpendicular

γ

4

Data Sheet EN0439EJ1V0DS00

NL6448AC33-29

GENERAL SPECIFICATIONS

Item Specification Unit

Module size 243.0 ± 0.5 (H) × 185.1 ± 0.5 (V) × 11.2 max. (D) mm

Inverter size 25.0 ± 0.5 (H) × 105.0 (V) × 10.2 max. (D) mm

Display area 211.2 (H) × 158.4 (V) mm

Number of dots 640 × 3 (H) × 480 (V) dot

Number of pixels 640 (H) × 480 (V) pixel

Dot pitch 0.11 (H) × 0.33 (V) mm

Pixel pitch 0.33 (H) × 0.33 (V) mm

Pixel arrangement RGB (Red, Green, Blue) vertical stripe –

Display colors 262,144 color

Weight Module: 530 (max.) + Inverter: 20 (max.) g

ABSOLUTE MAXIMUM RATINGS

+0.7

–0.3

Parameter Symbol Rating Unit Remarks

Supply voltage V

Input voltage V

CC

I

–0.3 to 6.5 V

–0.3 to 6.5 V

a

= 25°C

T

I

– VCC < 0.3

V

Supply voltage VDDB –0.3 to 15.0 V

Input voltage BRTC –0.3 to 7.0 V

Lamp voltage VL 2000 Vrms

RH

ST

OP

≤

95% relative humidity – T

≤

85% relative humidity – 40 < T

–20 to 60 °C

0 to 50 °C

Absolute humidity shall not

a

exceed T

= 50°C,

Module surface

a

≤ 40°C

a

–T

> 50°C

a

≤ 50°C

Storage temp. T

Operating temp. T

Humidity

(No condensation)

85% relative humidity level.

Measured at the display area

Note

−

Note

Data Sheet EN0439EJ1V0DS00

5

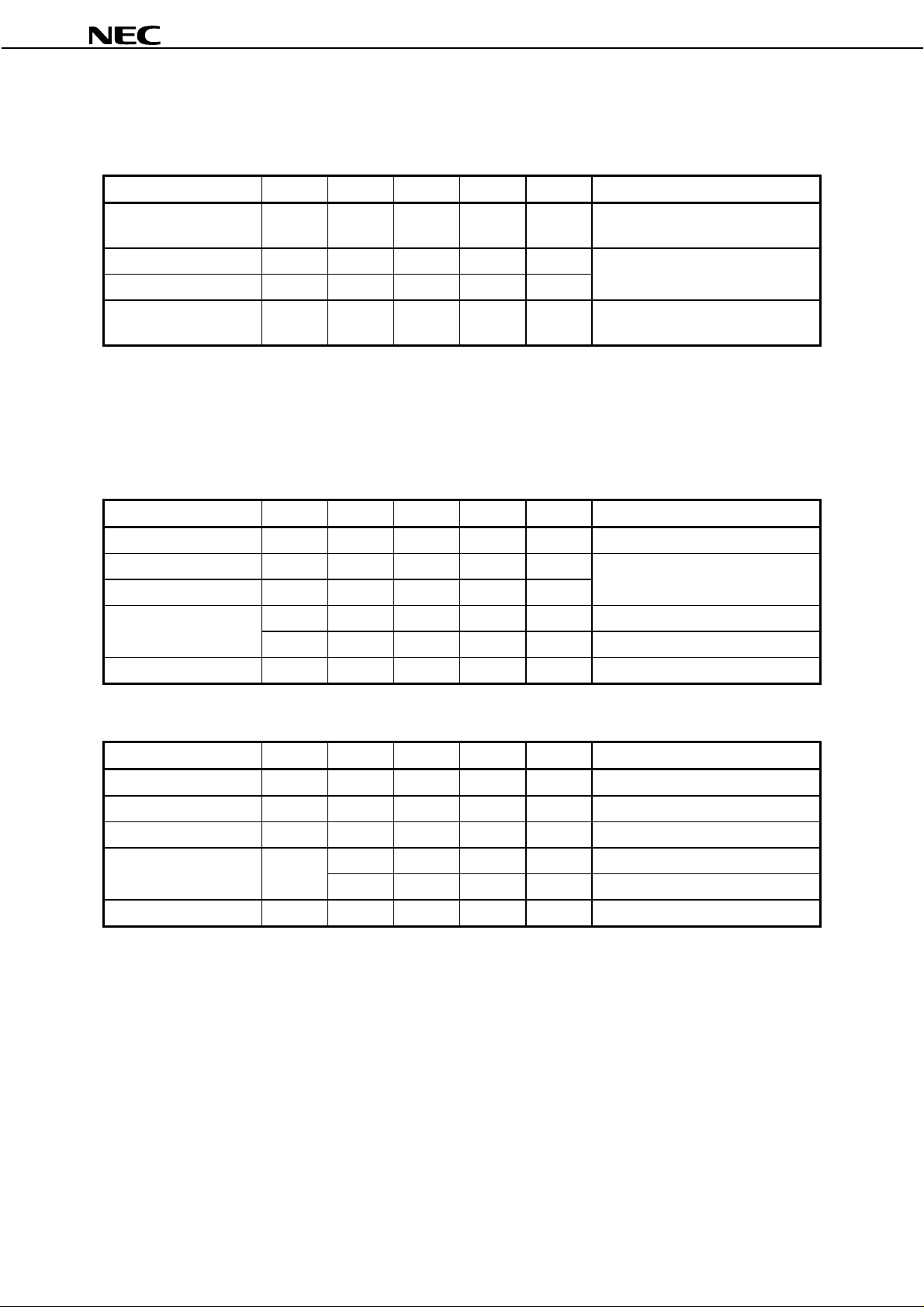

ELECTRICAL CHARACTERISTICS

(1) Logic, LCD driving

Parameter Symbol MIN. TYP. MAX. Unit Remarks

NL6448AC33-29

Ta = 25°C

Supply voltage V

Logic input Low voltage V

Logic input High voltage V

Supply current I

Checkered flag pattern (in EIAJ ED-2522)

Note

CC

IL

IH

CC

3.0

(4.75)

3.3

(5.0)

0–V

VCC × 0.7 – 5.25 V

Note

–

–

400

(300)

3.6

(5.25)

CC

× 0.3 V

600

(400)

VVCC = 3.3 V

CC

= 5.0 V)

(V

mA V

CC

(V

= 3.3 V

CC

= 5.0 V)

(2) Backlight

<1> Inventer

Parameter Symbol MIN. TYP. MAX. Unit Remarks

Supply voltage VDDB 11.4 12.0 12.6 V –

Logic input “L” voltage V

Logic input “H” voltage V

voltage

Supply current IDDB – 480 – mA 250 cd/m

IL

IH

0–0.8V

2.0 – 5.0 V

– – 2.5 – V Minimum luminanceLuminance control

– – 1.2 – V Maximum luminance

2

BRTC

a

= 25°C

T

<2> Lamp

Parameter Symbol MIN. TYP. MAX. Unit Remarks

Lamp current IL 2.0 × 2 5.0 × 2 – mArms With two lamps

Lamp voltage VL – 510 – Vrms IL = 5 mArms

Power supply PL – 2. 55 – W –

840 – – mA Ta = 25°CLamp turn on voltage Vs

a

1265 – – mA T

Oscillator frequency Ft 50 54 58 kHz

Recommended value of “Ft”

Note

= 0°C

Note

• Ft is within the specification.

• Ft = 1/4 th × (2n – 1) th: Hsync period

n : a natural number (1, 2, 3, ···)

If Ft is out of the recommended value, interference between Ft frequency and Hsync frequency may

cause beat on the display.

6

Data Sheet EN0439EJ1V0DS00

SUPPLY VOLTAGE SEQUENCE

NL6448AC33-29

The supply voltage for input signals should

CC

be the same as V

Apply VDDB within the LCD operation period.

2.

.

When the backlight turns on before LCD

operation or the LCD operation turns off

before the backlight turns off, the display

Signals

V

Notes 1, 2,3

3.0 V (4.75 V)

CC

0 < t < 35 ms 0 < t < 35 ms

VALID

ON OFF

3.0 V (4.75 V)

Notes 1.

Time

may momentarily become white.

While the power is off, please keep whole

3.

signals (Hsync, Vsync, CLK, DE, and DATA)

at low level or high impedance.

INTERFACE AND PIN CONNECTION

(1) Interface signals, power supply

Module side connector Mating connector

CN1 ··· DF9C-31P-1V (No.1 to 31) DF9-31S-1V, DF9M-31S-1R ······(1)

IL-310-T31S-VF ·························(2)

Supplier: (1) HIROSE ELECTRIC CO., LTD., (2) Japan Aviation Electronics Industry Limited (JAE)

Pin No. Symbol Function Pin No. S ym bol Function

1GND

Ground (SG)

Note 4

19 GND

2 CLK Dot cl ock 20 B0 Blue data (LSB)

3 Hsync Horizontal sync. 21 B1 Blue data

4 Vsync Vertical sync. 22 B2 Blue data

Note 4

5GND

Ground

23 B3 Blue data

6 R0 Red dat a (LSB ) 24 B4 Blue data

7 R1 Red dat a 25 B5 Blue data (MSB)

8 R2 Red data 26 GND

9 R3 Red dat a 27 DE

10 R4 Red dat a 28 V

11 R5 Red dat a (MSB ) 29 V

Note 4

12 GND

Ground

30 N. C. Non-connection

CC

CC

13 G0 Green data (LSB) 31 DPS

Note 4

Ground

Note 4

Ground

Data enable

Power supply

Power supply

Note 2

Note 1

Note 1

Scan direction select

Note 3

14 G1 Green data

15 G2 Green data

16 G3 Green data

17 G4 Green data

18 G5 Green data (MSB)

LSB : Least Significant Bit

MSB : Most Significant Bit

Data Sheet EN0439EJ1V0DS00

7

CC

: All VCC terminals should be connected to 3.3 V or 5.0 V.

Notes 1.

V

DE: DE/Fixed mode select is as follows.

2.

Data enabled signal = DE mode

CC

or Open = Fixed mode

V

DPS: DPS changes display scan direction.

3.

GND or Open = Scan direction will be decided by the setting of SW1.

CC

V

= Reverse scan

INPUT SIGNAL TIMING See (4) DISPLAY POSITION about another way for reversible scan. (DPS is

Open)

CC

When DPS is V

, reverse scan is selected even if SW1 is set at normal scan.

When DPS is GND, normal scan is selected even if SW1 is set at reverse scan.

GND is connected to the frame of the LCD module.

4.

(2) Inverter

• Inverter side connector 1 Mating connector 1

CN1 ··· LZ-5P-SL-SMT LZ-5S-SC3

Supplier: Japan Aviation Electronics Industry Limited (JAE)

NL6448AC33-29

Pin No. Symbol Function Pin No. Symbol Function

1V

2V

3 GNDB Backlight ground

Note

DD

B Power supply 4 GNDB Backlight ground

DD

B Power supply 5 B RTHL

High luminance (100%): BRTHL = High or open

Luminance select

Low luminance (60%): BRTHL = Low (GNDB level)

• Inverter side connector 2 Mating connector 2

CN3 ··· IL-Z-3PL-SMTY IL-Z-3S-S125C3

Supplier: Japan Aviation Electronics Industry Limited (JAE)

Pin No. Symbol Function

1BRTC

2BRTH

3BRTL

Notes 1.

C-MOS level

Backlight ON/OFF signal

Luminance control input

Luminance control input

Note 1

Note 2

Note 2

Backlight ON : BRTC = High or open

Backlight OFF: BRTC = Low

<1> A way of luminance control by a variable resistor

2.

This way works when BRTHL (No.5 pin) of CN1 is opened.

Note

BRTL BRTH

R

Mating variable resistor

Minimum luminance (50%)

Maximum luminance (100%)

: 10 kΩ ±5%

: R = 0 Ω

: R = 10 kΩ

<2> A way of luminance control by a voltage

This way works when BRTHL and BRTL are opened. The range of input voltage between

BRTH and GNDB is as follows.

Minimum luminance (50%) : 2.5 V

Maximum luminance (100%): ≤ 1.2 V

8

Data Sheet EN0439EJ1V0DS00

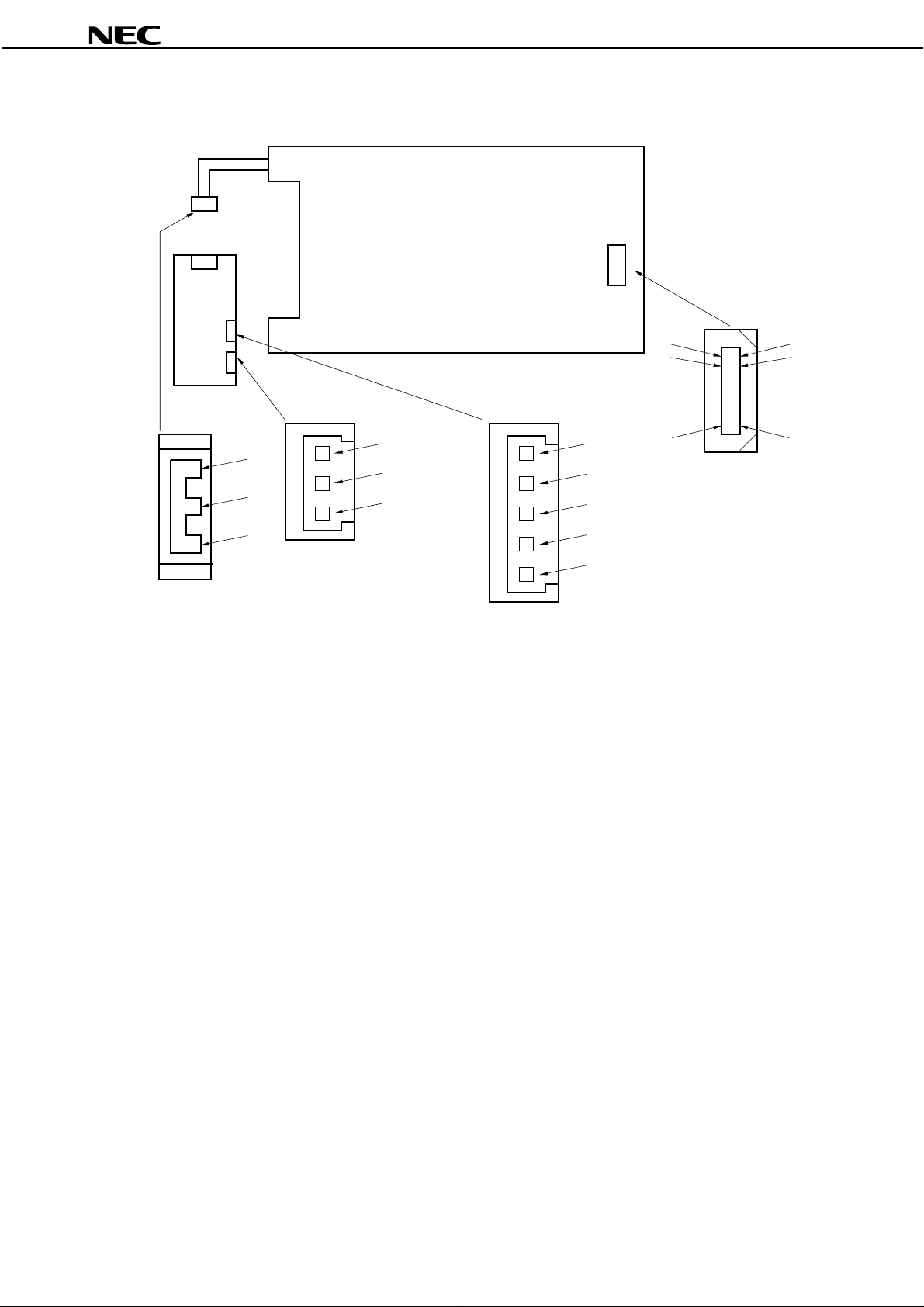

CN2

<3> Connector location

Inverter

Upper side

LCD Module

<Rear view>

NL6448AC33-29

CN1

CN1

CN3

<Pin arrangement of CN3>

<Pin arrangement of CN2>

1

Lower side

1

2

3

1

2

3

<Pin arrangement of CN1>

1

2

3

4

5

3

•

•

•

•

•

31

<Pin arrangement of CN1>

2

4

•

•

•

•

•

30

Data Sheet EN0439EJ1V0DS00

9

Loading...

Loading...